### DEVELOPMENT OF A NEW CURRENT CONTROLLED PULSE WIDTH MODULATOR FOR VOLTAGE SOURCE INVERTERS

A Thesis Submitted to the Department of Electrical and Electronic Engineering in Partial Fulfillment of the Requirement for the Degree of DOCTOR OF PHILOSOPHY

Kazi Mujibur Rahman

Department of Electrical and Electronic Engineering BANGLADESH UNIVERSITY OF ENGINEERING AND TECHNOLOGY

The thesis titled **Development of a New Current Controlled Pulse Width Modulator for Voltage Source Inverters** Submitted by Kazi **Mujibur Rahman** Roll No: 01/EEE/Ph.D. Session 1992-93-94 has been accepted as satisfactory in partial fulfillment of the requirement for the degree of DOCTOR OF PHILOSOPHY on June 01, 2000.

#### BOARD OF EXAMINERS

ï

Dr. M. Rezwan Khan Professor, Department of EEE, BUET

nachondhur 2.

Dr. M. A. Choudhury Professor, Department of EEE, BUET

fost am

Dr. A. B. M. Siddique Hossain Professor, Department of EEE, BUET

Dr. Md Quamrul Ahsan Professor, Department of EEE, BUET

EBass

Dr. Enamul Basher Professor, Department of EEE, BUET

6.

7.

1.

3.

4.

5.

Dr. S.M. Lutful Kabir Professor, Department of EEE, BUET

Klian

usain

Dr. Shahidul Islam Khan Professor and Head, Department of EEE, BUET

8.

Dr. Iqbal Husain Associate Professor, Department of EE University of Akron, Akron, Ohio, USA.

Chairman

Member (Co-supervisor)

Member

Member

Member

Member

Member (Ex-officio)

Member (External)

D

## Declaration

It is hereby declared that this thesis or any part of it has not been submitted elsewhere for the award of any degree or diploma.

í,

Signature of the supervisor

1-6-2000

Dr. M. Rezwan Khan Professor Department of Electrical and Electronic Engineering BUET, Dhaka-1000.

Signature of the candidate

- 1.6.2000

Kazi Mujibur Rahman

## Acknowledgements

The author expresses his gratitude to his supervisor Professor M. Rezwan Khan for his friendly supervision and invaluable assistance in the process of completing this work. The author also appreciates co-supervisor Professor M. A. Choudhury for his assistance, support, suggestions, encouragement and cooperation throughout the progress of the research. The author appreciates Professor M. A. Rahman of Memorial University of Newfound-land, Canada, for his helpful suggestions, discussions and comments. His constructive suggestions and supply of research materials are gratefully acknowledged.

The author acknowledges the valuable discussions and suggestions made by the members of the Doctoral Committee – Professors Dr. Md. Quamrul Ahsan, Dr. Enamul Basher, Dr. S. M. Lutful Kabir and Dr. S. Shahnawaz Ahmed at various stages of this work.

Thanks are also due to Professor Dr. A. B. M. Siddique Hossain whose constant support is deeply appreciated. The author would like to thank the Committee of Advance Studies and Research of BUET for financial support towards completion of the research work. Sincerest thanks to all of those who extended their hands, directly or indirectly to complete this research work.

The author pays his profound gratitude to his parents, relatives and friends for their inspiration towards the completion of this work. Finally, the family's co-operation throughout the entire period of the work is acknowledged.

iv

### Abstract

This thesis is concerned with the improvement of current controllers for use with voltage source inverters. Analysis of hysteresis current controller (HCC) is presented. The common problems of non-uniform and burst switching of scalar type controllers (hysteresis current controller and ramp comparison controller (RCC)) are addressed. An improved model of HCC, referred to as PRC is proposed for uniform switching frequency operation. Theoretical basis is established where, an add-on function of programmed amplitude and slope can keep the switching frequency of HCC to a predefined value. In addition to uniform switching frequency operation, the proposed model has significant improvement on the total harmonic distortion coefficient. Analysis of the predictive controller is also made in this research. The shoot through current behavior of predictive controller is improved by the use of a voltage vector limiter. A generalized approach is proposed for the design of the proposed predictive controller with inductive load. Separate schemes are proposed for implementation of PRC and predictive controllers based on general purpose PC architecture. Incorporating the merits of both PRC and predictive controller, a new and novel current controller (referred to as NEW-CC) is developed in this work. This controller operates on regular sampled basis and predicts pulse widths of individual phases once on each carrier period. The load parameters are tracked on each fundamental as well as carrier cycles. Uniform switching as well as shoot through current limiting is achieved in this new controller. The performance of this new controller is compared with the other current controllers and is found to give better performance. The new current controller has lower total harmonic distortion than other current controllers. This controller do not have sub-harmonics in the load current spectrum as is normally encountered in scalar type current controllers at large bands. The new current controller has been experimentally tested. Its performance is in good agreement with the theoretical results.

# Contents

|   | Ack             | nowled | lgement                             | iv  |

|---|-----------------|--------|-------------------------------------|-----|

|   | Abs             | tract  |                                     | v   |

|   | $\mathbf{List}$ | of Ab  | breviations                         | ix  |

|   | List            | of Pri | incipal Symbols                     | xi  |

|   | List            | of Tal | bles                                | xiv |

|   | List            | of Fig | jures                               | xvi |

| 1 | Intr            | oducti | on                                  | 1   |

|   | 1.1             | Gener  | ral                                 | 1   |

|   | 1.2             | Invert | ter Types and Controls              | 2   |

|   | 1.3             | Pulse  | Width Modulation (PWM) Techniques   | 3   |

|   |                 | 1.3.1  | Voltage Reference PWM               |     |

|   |                 | 1.3.2  | Need for Current Control            | 6   |

|   | 1.4             | Currei | nt Reference PWM                    | 7   |

|   | 1.5             | Litera | ture Review of Current Controllers  | 8   |

|   |                 | 1.5.1  | Hysteresis Current Controllers      | 8   |

|   |                 | 1.5.2  | Ramp Comparison Current Controllers | 12  |

|   |                 | 1.5.3  | Predictive Current Controllers      | 14  |

|   | 1.6             |        | em Identification                   |     |

|   | 1.7             | Contri | bution                              | 16  |

|   |                 | Probl  | em Identification                   | •   |

٨

|   | 1.8 | Thesis  | Outline                                                        | 17 |

|---|-----|---------|----------------------------------------------------------------|----|

| 2 | Dev | elopm   | ent of a Programmed Ramp Current Controller                    | 19 |

|   | 2.1 | Introd  | uction                                                         | 19 |

|   | 2.2 | Analy   | sis of Conventional HCC                                        | 21 |

|   | 2.3 | Contro  | oller Scheme                                                   | 28 |

|   |     | 2.3.1   | Performance Study                                              | 28 |

|   | 2.4 | Perfor  | mance Comparison of AMPRC and PRC with HCC                     | 46 |

|   | 2.5 | Conclu  | usion                                                          | 47 |

| 3 | Imp | orovem  | ent of Conventional Predictive Current Controllers by Impos-   |    |

|   | ing | New O   | Constraint                                                     | 49 |

|   | 3.1 | Introd  | uction                                                         | 49 |

|   | 3.2 | Analy   | sis of Predictive Current Controller with equivalent R-L load  | 50 |

|   |     | 3.2.1   | Method 1: Vector Prediction Based on Load Parameters and Feed- |    |

|   |     |         | back Currents                                                  | 53 |

|   |     | 3.2.2   | Method 2: Vector Prediction Based on Load Parameters and Ref-  |    |

|   |     |         | erence Current                                                 | 54 |

|   |     | 3.2.3   | Modulation Process                                             | 55 |

|   | 3.3 | Impro   | vement of Dynamic Performance                                  | 58 |

|   | 3.4 | Propo   | sed Controller Scheme                                          | 59 |

|   | 3.5 | Perfor  | mance Study                                                    | 60 |

|   |     | 3.5.1   | Space Voltage Vector Computed by Method 1                      | 60 |

|   |     | 3.5.2   | Space Voltage Vector Computed by Method 2                      | 61 |

|   | 3.6 | Respo   | nse in Case of Large Disturbance                               | 71 |

|   | 3.7 | Concl   | usion                                                          | 72 |

| 4 | Nev | w and I | Novel Regular Sampled Current Controller for Voltage Source    | !  |

|   | Inv | erters  |                                                                | 74 |

|   | 4.1 | Introd  | luction                                                        | 74 |

|   | 4.2 | Curre   | nt in the R-L Load with a Step Voltage Input                   | 76 |

.

.

•

| 4.3  | Analy   | sis of Regular Sampled Current Controller                          | 77  |

|------|---------|--------------------------------------------------------------------|-----|

| 4.4  | Curre   | nt Ripple                                                          | 79  |

|      | 4.4.1   | Maximum and Minimum Ripples                                        | 81  |

| 4.5  | Applie  | cation of the Current Controller to Three Phase Inverter with Star |     |

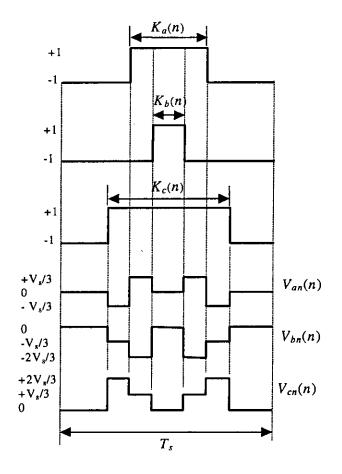

|      | Conne   | ected Load                                                         | 82  |

|      | 4.5.1   | Phase Voltages in Star Connected Load with Insulated Neutral       | 83  |

|      | 4.5.2   | Duty Cycles in NEW-CC for Neutral Insulated System                 | 87  |

| 4.6  | Estim   | ation of R-L Parameters of the Load                                | 88  |

|      | 4.6.1   | R-L Parameter Estimation on Carrier Cycle Basis from Two Phase     |     |

|      |         | Data                                                               | 88  |

|      | 4.6.2   | R-L Parameter Estimation on Fundamental Cycle Basis from Fourier   |     |

|      |         | Analysis                                                           | 89  |

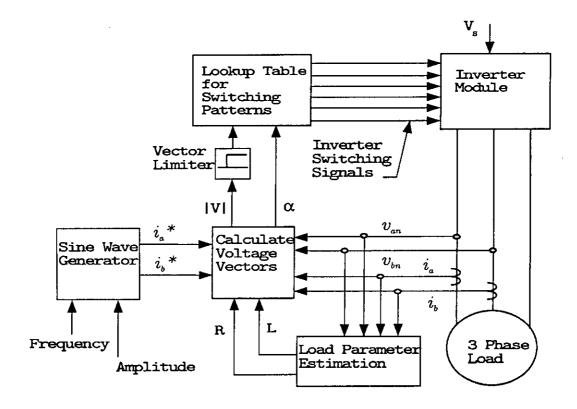

| 4.7  | Contro  | oller Scheme                                                       | 91  |

|      | 4.7.1   | Real Time PWM Waveform Generation                                  | 94  |

| 4.8  | Data .  | Acquisition for Load Current                                       | 96  |

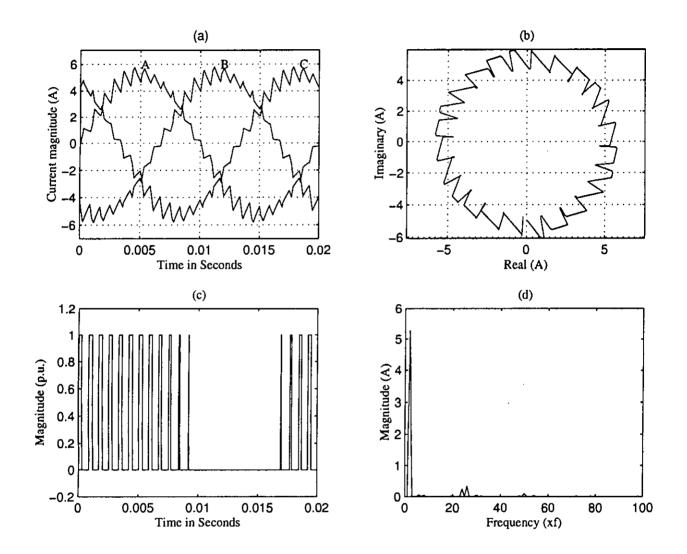

| 4.9  | Perfor  | mance Study                                                        | 97  |

|      | 4.9.1   | Performance at Standstill (Slip = $1.0$ )                          | 100 |

|      | 4.9.2   | Performance at Running Condition (Slip = $0.05$ )                  | 104 |

| 4.10 | Steady  | y State Waveforms of the NEW-CC                                    | 106 |

| 4.11 | Start-  | up Waveforms                                                       | 112 |

| 4.12 | Dynar   | mic Response                                                       | 117 |

| 4.13 | Comp    | arison of the NEW-CC with Other Conventional Current Controllers   | 121 |

| 4.14 | Concl   | usion                                                              | 122 |

| ~    |         |                                                                    | 124 |

|      | iclusio |                                                                    |     |

| 5.1  |         | usion                                                              |     |

| 5.2  | Futur   | e Works                                                            | 120 |

| Bib  | liograj | phy                                                                | 128 |

5 se

5

# List of Abbreviations

| ADC    | Analog to digital converter                       |

|--------|---------------------------------------------------|

| AMPRC  | Amplitude modulated programmable ramp controller  |

| ASIC   | Application specific integrated circuits          |

| BJT    | Bipolar junction transistor                       |

| CSI    | Current source inverter                           |

| DAS    | Data acquisition system                           |

| DSP    | Digital signal processor                          |

| GTO    | Gate turn off thyristor                           |

| HCC    | Hysteresis current controller                     |

| IGBT   | Insulated gate bipolar transistor                 |

| IGCT   | Insulated gate controlled transistor              |

| KW     | Kilo-watt                                         |

| LSI    | Large scale integration                           |

| MCT    | MOS controlled thyristor                          |

| MOSFET | Metal oxide semiconductor field effect transistor |

| MSF    | Maximum switching frequency                       |

| NEW-CC | New current controller                            |

| RCC    | Ramp comparison controller                        |

| RMS    | Root mean square                                  |

| RSPWM  | Regular sampled PWM                               |

| PC     | Personal computer                                 |

| PI     | Proportional integral                             |

| PLL    | Phase locked loop                                 |

|        |                                                   |

í

| PRC    | Programmable ramp controller      |

|--------|-----------------------------------|

| PWM    | Pulse width modulation            |

| SIT    | Static induction transistor       |

| SITH   | Static induction thyristor        |

| SCR    | Silicon controlled rectifier      |

| SPWM   | Sine pulse width modulation       |

| SHEPWM | Specific harmonic elimination PWM |

| SPDT   | Single pole double throw          |

| THD    | Total harmonic distortion         |

| TI     | Texas instruments                 |

| VCO    | Voltage controlled oscillator     |

| VLSI   | Very large scale integration      |

| VSI    | Voltage source inverter           |

# List of Principal Symbols

| lpha           | Modulation angle                                       |

|----------------|--------------------------------------------------------|

| β              | HCC band                                               |

| $Counter_a(n)$ | A counter related to Phase A at the $n^{th}$ PWM pulse |

| $Counter_b(n)$ | A counter related to Phase B at the $n^{th}$ PWM pulse |

| $Counter_c(n)$ | A counter related to Phase C at the $n^{th}$ PWM pulse |

| $D_1 - D_6$    | Free-wheeling diodes of inverter                       |

| $\Delta I_t$   | Amplitude of triangular carrier signal                 |

| $Data_a(n,r)$  | Real time data signal for Phase A                      |

| $Data_b(n,r)$  | Real time data signal for Phase B                      |

| $Data_a(n,r)$  | Real time data signal for Phase C                      |

| Data(n,r)      | Combined real time signal data                         |

| f              | Reference frequency                                    |

| $f_0$          | Fundamental frequency                                  |

| fs             | Switching frequency                                    |

| $f_{sn}$       | MSF at normalized THD                                  |

| G              | A constant                                             |

| <i>i</i> *     | Reference current                                      |

| $i^*(n)$       | $n^{th}$ sample of combined reference current vector   |

| $i_a^*(n)$     | $n^{th}$ sample of Phase A reference current           |

| $i_b^*(n)$     | $n^{th}$ sample of Phase B reference current           |

| $i_c^*(n)$     | $n^{th}$ sample of Phase C reference current           |

| i(n)           | $n^{th}$ sample of combined load current vector        |

| $I_m$          | Reference current maximum value                        |

xi ·

:

| $I_{rms}$      | RMS value of load current                          |

|----------------|----------------------------------------------------|

| $I_{a1}, I_1$  | Maximum value of fundamental load current          |

| $i_a$          | Phase A load current                               |

| $i_a(n)$       | $n^{th}$ sample of Phase A load current            |

| $i_{b}$        | Phase B load current                               |

| $i_b(n)$       | $n^{th}$ sample of Phase B load current            |

| $i_c$          | Phase C load current                               |

| $i_{c}(n)$     | $n^{th}$ sample of Phase C load current            |

| $i_a^+$        | Rising current segment (load current)              |

| $i_a^-$        | Falling current segment (load current)             |

| $\mathfrak{S}$ | Imaginary part                                     |

| K(n)           | Duty cycle at the $n^{th}$ switching period        |

| $K_a(n)$       | Duty cycle for Phase A                             |

| $K_b(n)$       | Duty cycle for Phase B                             |

| $K_c(n)$       | Duty cycle for Phase C                             |

| L              | Inductance per phase of the star connected load    |

| $L_{new}$      | Current value of load inductance                   |

| $L_{old}$      | Previous value of load resistance                  |

| m              | Slope of load current                              |

| $m_t$          | Slope of triangular carrier signal                 |

| $m_t^+$        | Positive slope of triangular carrier signal        |

| $m_t^-$        | Negative slope of triangular carrier signal        |

| n              | Sample number                                      |

| $N_{max}$      | Total number of PWM pulses in a fundamental period |

| ω              | Angular frequency of reference signal              |

| p              | Sector number                                      |

| $Q_1 - Q_6$    | Inverter switches (transistors)                    |

| R              | Resistance per phase of the star connected load    |

| $R_{new}$      | Current value of load resistance                   |

| Rold           | Previous value of load resistance                  |

|                |                                                    |

مر ،

Ç

Þ

xii

| Я                        | Real part                                                     |

|--------------------------|---------------------------------------------------------------|

| r <sub>max</sub>         | Real time data samples in a carrier period                    |

| $S_A - S_C$              | SPDT switches of phases A, B and C                            |

| $T, T_s$                 | Switching period                                              |

| $t_1,T_1$                | ON time duration in a switching period                        |

| $t_2, T_2$               | OFF time duration in a switching period                       |

| $t_x$                    | Time related to $V_x$                                         |

| $t_y$                    | Time related to $V_y$                                         |

| $t_z$                    | Free-wheeling time in a period $(T_s)$                        |

| $t_{c1}$                 | Rise time of triangular carrier signal in $T_t$               |

| $t_{c2}$                 | Fall time of triangular carrier signal in $T_t$               |

| . T <sub>t</sub>         | Period of triangular carrier signal                           |

| $T_{lock}$               | Lockout time                                                  |

| au                       | Time duration by which a data is latched to the parallel port |

| θ                        | Load power factor angle                                       |

| $	heta_1$                | Phase angle of Phase voltage (fundamental)                    |

| $	heta_2$                | Phase angle of load current (fundamental)                     |

| $V_s, V_a$               | Inverter dc supply voltage                                    |

| V(n)                     | $n^{th}$ sample of combined voltage vector                    |

| $V_1 - V_6$              | Inverter voltage vectors                                      |

| $V_x$                    | Contribution of $V(n)$ on the adjacent right arm vector       |

| $V_y$                    | Contribution of $V(n)$ on the adjacent left arm vector        |

| $V_{an}, V_{bn}, V_{cn}$ | Inverter output voltage for Phases A, B, C (line to neutral)  |

| Ζ                        | Load impedance                                                |

| $Z_{new}$ .              | Current value of load impedance                               |

| $Z_{old}$                | Previous value of load impedance                              |

(\_

١.

xiii

# List of Tables

ni i X

-1...

.

| 2.1 | Performance comparison between PRC and HCC for opera-                                                                |     |

|-----|----------------------------------------------------------------------------------------------------------------------|-----|

|     | TION WITH A THREE PHASE INVERTER WITH STAR CONNECTED LOAD                                                            |     |

|     | having $V_s = 240$ V, R = 8 $\Omega$ , L = 0.0191H, $f = 50$ Hz and $I_m = 5$ A.                                     | 46  |

| 3.1 | Inverter switching states and dominant voltage vectors                                                               | 52  |

| 3.2 | Switching states and active voltage vectors in different sec-                                                        |     |

|     | TORS OF THE COMPLEX PLANE                                                                                            | 55  |

| 3.3 | State assignment of inverter switches for two level PWM at                                                           |     |

|     | DIFFERENT SECTORS OF THE VOLTAGE VECTOR $V(n)$ AND TIME ZONES.                                                       | 58  |

| 3.4 | Load parameters used for simulation of the proposed predic-                                                          |     |

|     | TIVE CONTROLLER                                                                                                      | 61  |

| 3.5 | LOAD CURRENT SPECTRUM COMPARISON                                                                                     | 62  |

| 3.6 | Current overshoots with large disturbance (at 90°) with $V_s$                                                        |     |

|     | = 240V, R = 8 $\Omega$ , L = 19.1mH, E = 40V, f = 50Hz, $f_s$ = 1200Hz.                                              | 72  |

| 4.1 | Data bits and port pin assignment of the inverter switches in                                                        |     |

|     | A PC BASED IMPLEMENTATION SCHEME                                                                                     | 94  |

| 4.2 | Three phase induction motor parameters at $f_b=50$ Hz                                                                | 99  |

| 4.3 | Performance data at steady state of the NEW-CC and other                                                             |     |

|     | Controllers: $V_s = 587V$ , $I_m = 2.0A$ , $f_s = 720Hz$ , $\beta = 0.1$ , slip =                                    |     |

|     | 1.0, for 1kW induction motor. $\ldots \ldots $ | 01  |

| 4.4 | Performance data at steady state of the NEW-CC and other                                                             |     |

|     | Controllers: $V_s = 587V$ , $I_m = 2.0A$ , $f_s = 900Hz$ , $\beta = 0.1$ , slip =                                    |     |

|     | 1.0, FOR 1KW INDUCTION MOTOR                                                                                         | .01 |

$\mathbf{xiv}$

| 4.5 | PERFORMANCE DATA AT STEADY STATE OF THE NEW-CC AND OTHER                          |

|-----|-----------------------------------------------------------------------------------|

| ·   | Controllers: $V_s = 587V$ , $I_m = 2.0A$ , $f_s = 900Hz$ , $\beta = 0.1$ , slip = |

|     | 0.05, for 1kW induction motor                                                     |

| 4.6 | STEADY STATE PERFORMANCE COMPARISON OF THE NEW-CC WITH                            |

|     | THE EXISTING CURRENT CONTROLLERS                                                  |

| 4.7 | DYNAMIC STATE PERFORMANCE COMPARISON OF NEW-CC WITH HCC,                          |

|     | RCC AND PREDICTIVE CONTROLLERS                                                    |

| 4.8 | Start-up performance comparison of NEW-CC with HCC, RCC                           |

|     | AND PREDICTIVE CONTROLLERS                                                        |

۲ ۱

.

.

÷

# List of Figures

-~<del>\*</del>

-,

۰.

¥

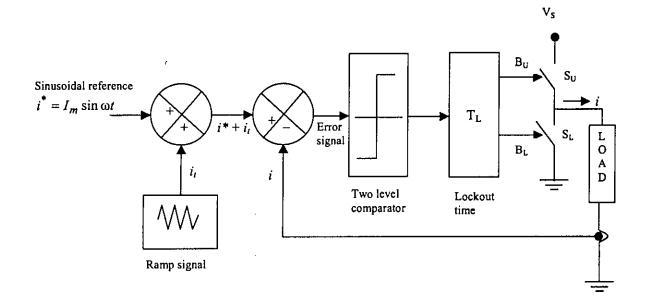

| 1.1 | Conventional Ramp Comparison Controller scheme.                                     | 13 |

|-----|-------------------------------------------------------------------------------------|----|

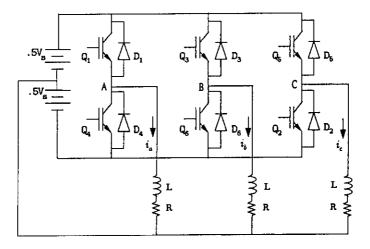

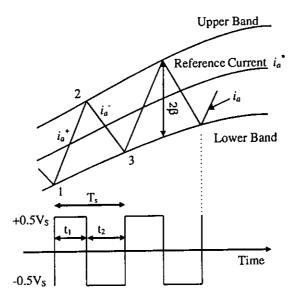

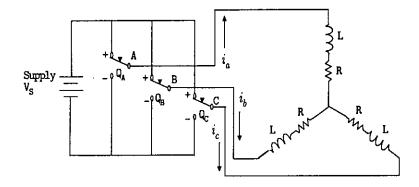

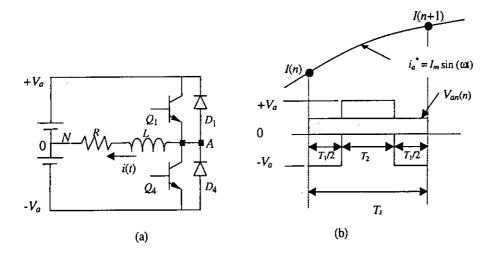

| 2.1 | Three phase inverter with star connected load and the neutral connected             |    |

|     | to the dc supply mid-point.                                                         | 21 |

| 2.2 | Current and voltage waveform of one phase (Phase A) of a voltage source             |    |

|     | inverter (VSI) with a current controller                                            | 22 |

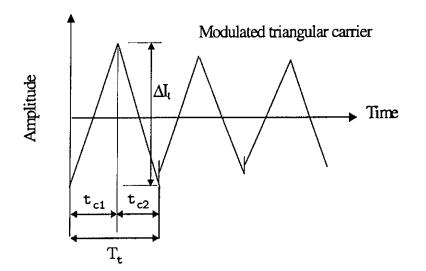

| 2.3 | Variable-slope amplitude modulated triangular waveform carrier to be added          |    |

|     | to a current controller                                                             | 24 |

| 2.4 | Implementation scheme of the proposed programmed ramp comparison cur-               |    |

|     | rent controller.                                                                    | 29 |

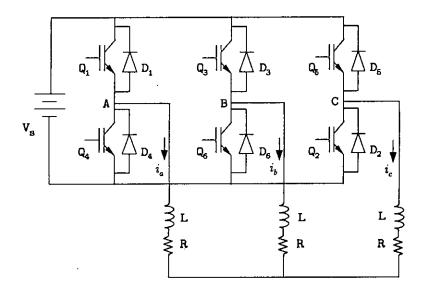

| 2.5 | Three phase voltage source inverter (VSI) with ideal (SPDT) switches in             |    |

|     | each phase connected to star connected $R - L$ load                                 | 30 |

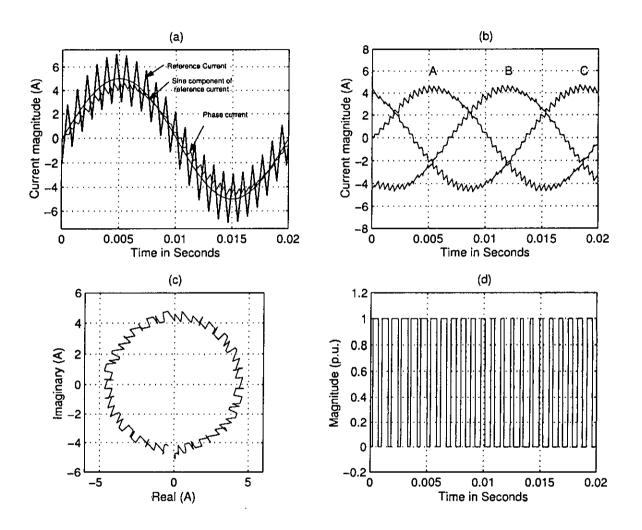

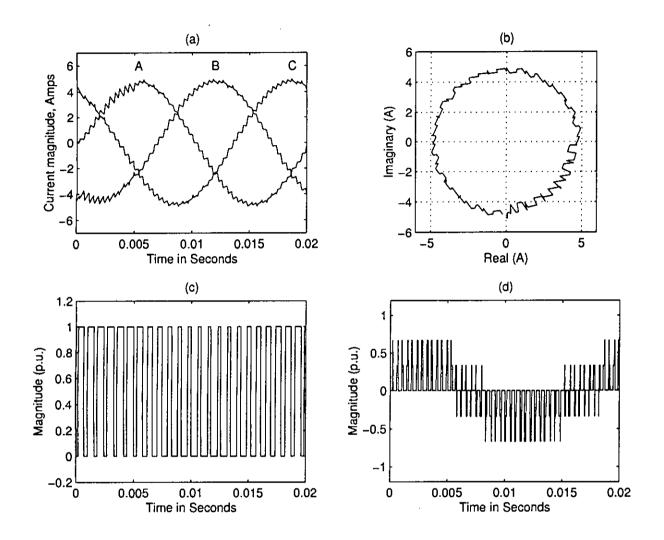

| 2.6 | Steady state response of the Amplitude Modulated Programmed Ramp                    |    |

|     | Comparison Controller (AMPRC) with $f = 50Hz$ , $R = 8\Omega$ , $L = 19.1mH$ ,      |    |

|     | $f_s = 1200 Hz$ , $V_s = 240 V$ , $I_m^* = 5 A$ : (a) Reference current and phase   |    |

|     | current (for phase A), (b) Load current waveforms for phases $A$ , $B$ and          |    |

|     | C , (c) Combined current vector in complex plane , (d) PWM switching                |    |

|     | pattern for switch $Q_1$                                                            | 32 |

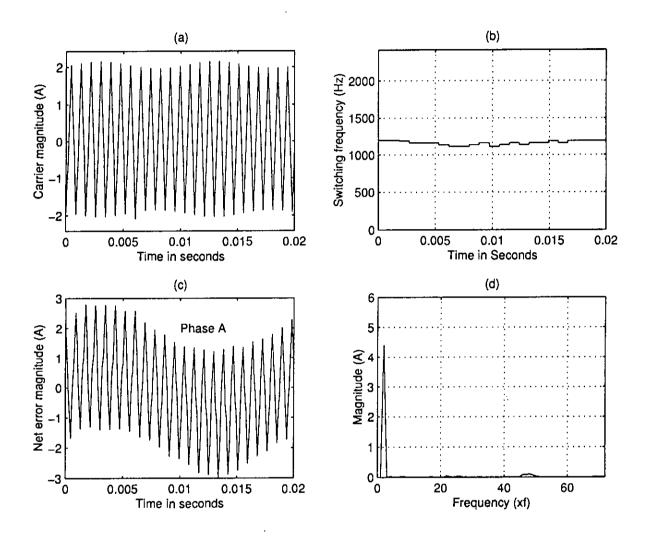

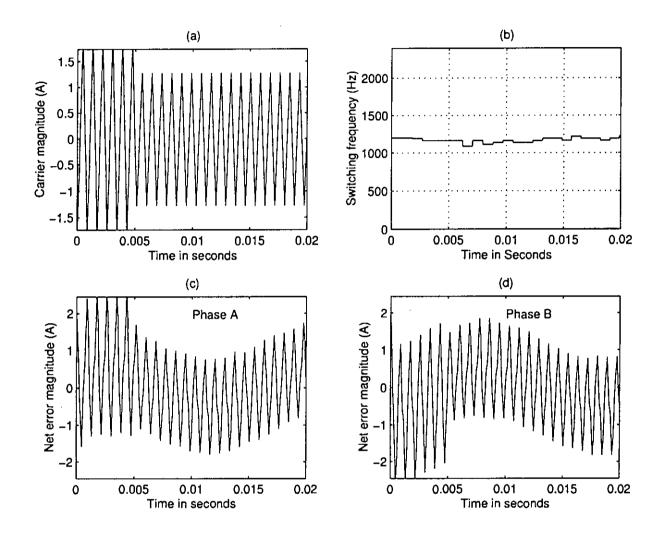

| 2.7 | Steady state response of the Amplitude Modulated Programmed Ramp                    |    |

|     | Comparison Controller (AMPRC) with $f = 50Hz$ , $R = 8\Omega$ , $L = 19.1mH$ ,      |    |

|     | $f_s = 1200 Hz$ , $V_s = 240 V$ , $I_m^* = 5 A$ : (a) Modulated ramp waveform , (b) |    |

|     | Switching frequency distribution over the fundamental period, (c) Net error         |    |

|     | signal for phase $A$ prior to comparator, (d) Spectrum of the load current.         | 33 |

xvi

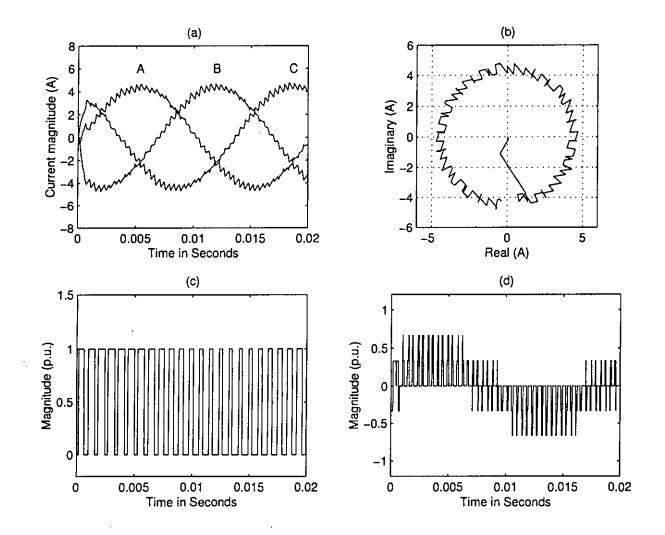

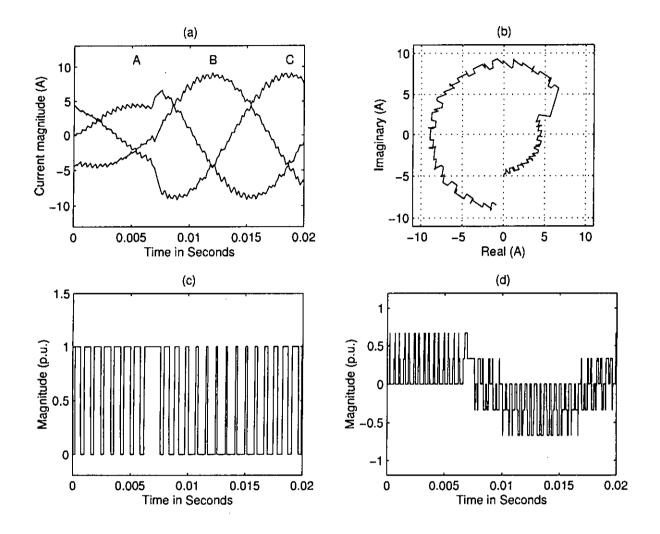

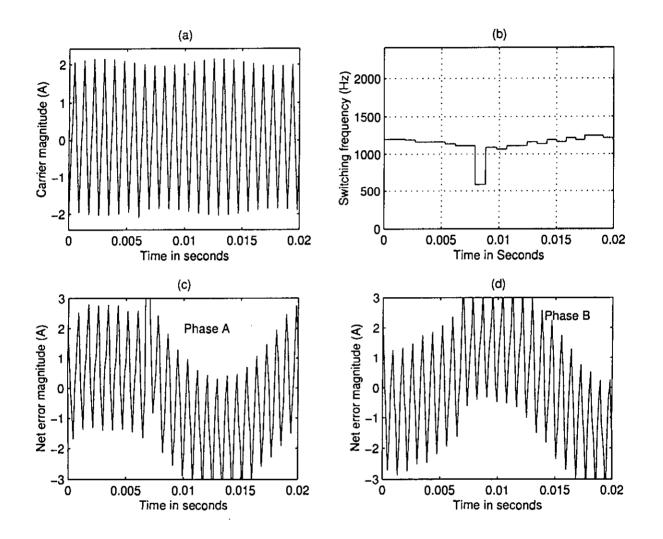

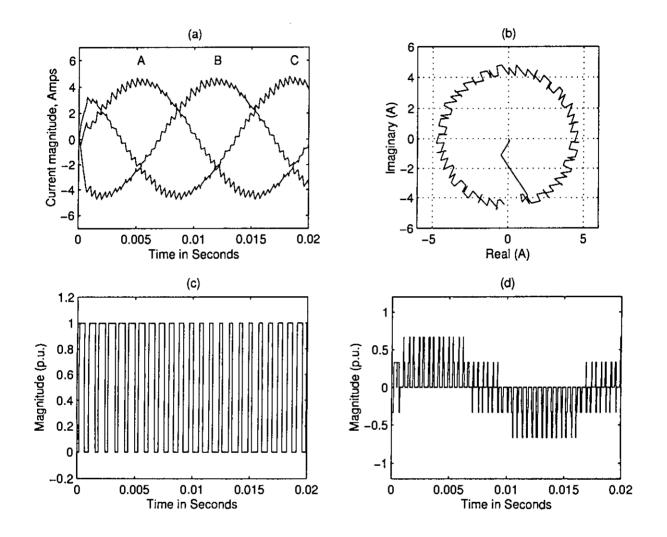

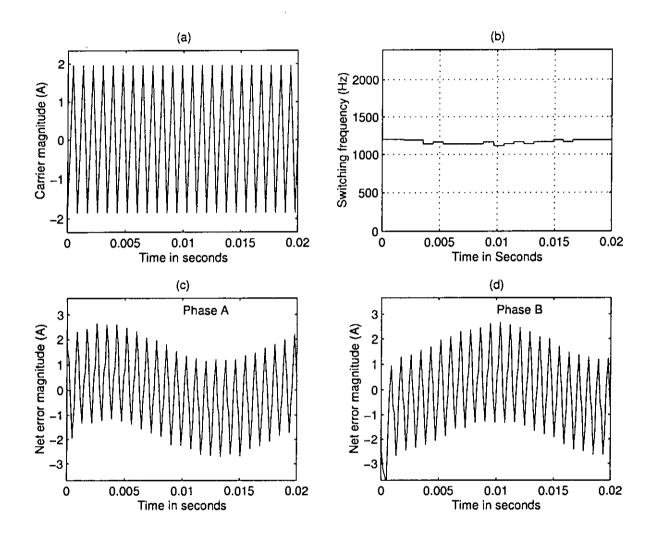

Start-up response of the Amplitude Modulated Programmed Ramp Com-2.8parison Controller (AMPRC) with f = 50Hz,  $R = 8\Omega$ , L = 19.1mH,  $f_s = 1200Hz, V_s = 240V, I_m^* = 5A$ : (a) Load current waveforms for phases A, B and C, (b) Combined current vector in complex plane, (c) PWM switching pattern for switch  $Q_1$ , (d) Line to neutral voltage waveform of 34 Start-up response of the Amplitude Modulated Programmed Ramp Com-2.9parison Controller (AMPRC) with f = 50Hz,  $R = 8\Omega$ , L = 19.1mH,  $f_s = 1200Hz, V_s = 240V, I_m^* = 5A$ : (a) Modulated ramp waveform , (b) Switching frequency distribution over fundamental period, (c) Net error signal for phase A prior to comparator, (d) Net error signal for phase B prior to comparator. 35 2.10 Dynamic response of the Amplitude Modulated Programmed Ramp Comparison Controller (AMPRC) with f = 50Hz,  $R = 8\Omega$ , L = 19.1mH,  $f_s = 1200Hz$ ,  $V_s = 240V$ ,  $I_m^* = 5A$  to 10A at 90°: (a) Load current waveforms for phases A, B and C, (b) Combined current vector in complex plane, (c) PWM switching pattern for switch  $Q_1$ , (d) Line to neutral voltage waveform of phase A in p.u. 36 2.11 Dynamic response of the Amplitude Modulated Programmed Ramp Comparison Controller (AMPRC) with f = 50Hz,  $R = 8\Omega$ , L = 19.1mH,  $f_s = 1200Hz$ ,  $V_s = 240\dot{V}$ ,  $I_m^* = 5A$  to 10A at  $90^0$ : (a) Modulated ramp waveform, (b) Switching frequency distribution over the fundamental period, (c) Net error signal for phase A prior to comparator, (d) Net error signal for phase B prior to comparator. . . . . . . . . . . . . 37 2.12 Steady state response of the Programmed Ramp Comparison Controller (PRC) with f = 50Hz,  $R = 8\Omega$ , L = 19.1mH,  $f_s = 1200Hz$ ,  $V_s =$ 240V,  $I_m^* = 5A$ : (a) Load current waveforms for phases A, B and C, (b) Combined current vector in complex plane, (c) PWM switching pattern for switch  $Q_1$ , (d) Line to neutral voltage waveform of phase A in p.u. . . 38

7

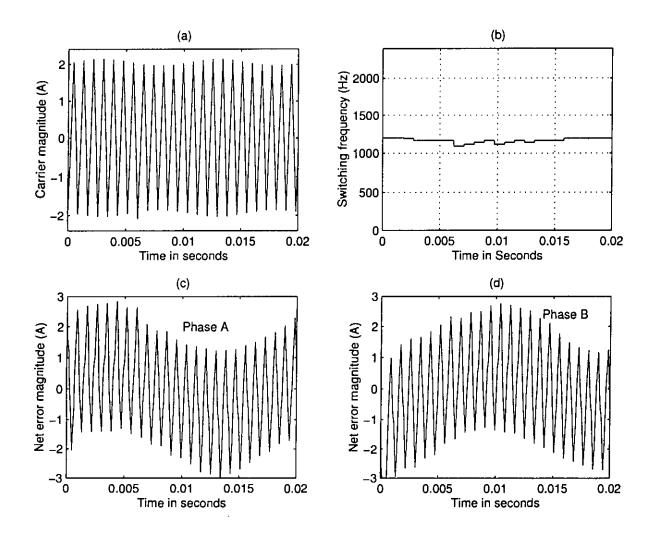

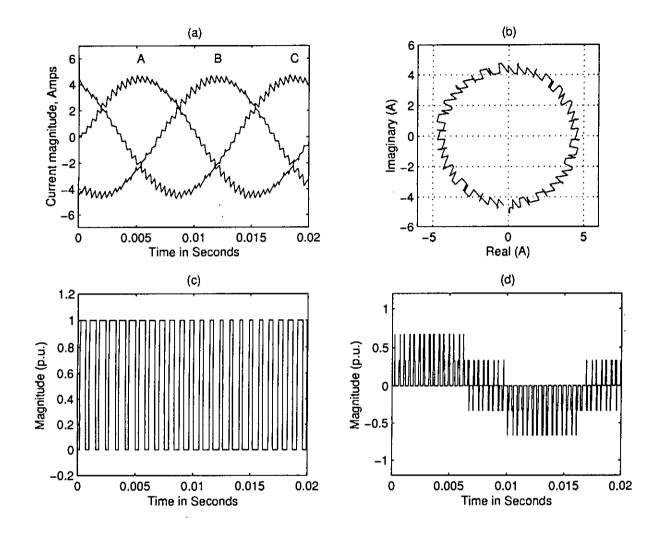

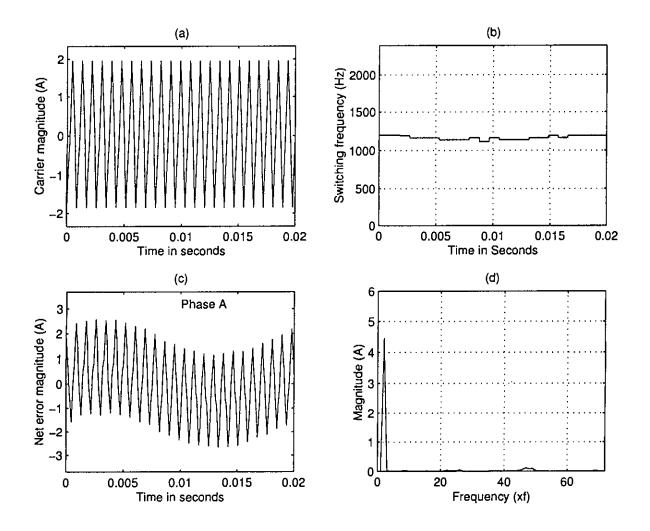

2.13 Steady state response of the Programmed Ramp Comparison Controller (PRC) with f = 50Hz,  $R = 8\Omega$ , L = 19.1mH,  $f_s = 1200Hz$ ,  $V_s =$ 240V,  $I_m^* = 5A$ : (a) Ramp waveform , (b) Switching frequency distribution over the fundamental period, (c) Net error signal for phase A prior to 39 comparator, (d) Spectrum of the load current. . . . . . . 2.14 Start-up response of the Programmed Ramp Comparison Controller (PRC) with f = 50Hz,  $R = 8\Omega$ , L = 19.1mH,  $f_s = 1200Hz$ ,  $V_s = 240V$ ,  $I_m^* = 5A$ : (a) Load current waveforms for phases A, B and C, (b) Combined current vector in complex plane , (c) PWM switching pattern for switch  $Q_1$  , (d) Line to neutral voltage waveform of phase A in p.u. 40 2.15 Start-up response of the Programmed Ramp Comparison Controller (PRC) with f = 50Hz,  $R = 8\Omega$ , L = 19.1mH,  $f_s = 1200Hz$ ,  $V_s = 240V$ ,  $I_m^* =$ 5A: (a) Ramp waveform, (b) Switching frequency distribution over the fundamental period, (c) Net error signal for phase A prior to comparator, 41 (d) Net error signal for phase B prior to comparator.  $\ldots$   $\ldots$   $\ldots$ 2.16 Dynamic response of Programmed Ramp Comparison Controller (PRC) with f = 50Hz,  $R = 8\Omega$ , L = 19.1mH,  $f_s = 1200Hz$ ,  $V_s = 240V$ ,  $I_m^* = 5A$ to 10A at 90°: (a) Load current waveforms for phases A, B and C, (b) Combined current vector in complex plane, (c) PWM switching pattern for switch  $Q_1$ , (d) Line to neutral voltage waveform of phase A in p.u. . 42 2.17 Dynamic response of the Programmed Ramp Comparison Controller (PRC) with f = 50Hz,  $R = 8\Omega$ , L = 19.1mH,  $f_s = 1200Hz$ ,  $V_s = 240V$ ,  $I_m^* = 5A$ to 10A at  $90^{\circ}$ : (a) Ramp waveform , (b) Switching frequency distribution over the fundamental period, (c) Net error signal for phase A prior to comparator, (d) Net error signal for phase B prior to comparator. 43 . . . .

| 2.18              | Dynamic response of the Programmed Ramp Comparison Controller (PRC)                                                                                                                                                                                                                                                             |                |

|-------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------|

|                   | with $f = 50Hz$ , $R = 8\Omega$ to $4\Omega$ at $90^{\circ}$ , $L = 19.1mH$ to $28.2mH$ at $90^{\circ}$ ,                                                                                                                                                                                                                       |                |

|                   | $f_s = 1200 Hz, V_s = 240 V, I_m^* = 5 A$ : (a) Load current waveforms for phases                                                                                                                                                                                                                                               |                |

|                   | A, B and C , (b) Combined current vector in complex plane , (c) PWM                                                                                                                                                                                                                                                             |                |

|                   | switching pattern for switch $Q_1$ , (d) Line to neutral voltage waveform of                                                                                                                                                                                                                                                    |                |

|                   | phase $A$ in p.u                                                                                                                                                                                                                                                                                                                | 44             |

| 2.19              | Dynamic response of the Programmed Ramp Comparison Controller (PRC)                                                                                                                                                                                                                                                             |                |

|                   | with $f = 50Hz$ , $R = 8\Omega$ to $4\Omega$ at $90^{\circ}$ , $L = 19.1mH$ to $28.2mH$ at $90^{\circ}$ ,                                                                                                                                                                                                                       |                |

|                   | $f_s = 1200 Hz$ , $V_s = 240V$ , $I_m^* = 5A$ : (a) Ramp waveform , (b) Switching                                                                                                                                                                                                                                               |                |

|                   | frequency distribution over the fundamental period, (c) Net error signal                                                                                                                                                                                                                                                        |                |

|                   | for phase $A$ prior to comparator, (d) Net error signal for phase $B$ prior to                                                                                                                                                                                                                                                  |                |

|                   | comparator.                                                                                                                                                                                                                                                                                                                     | 45             |

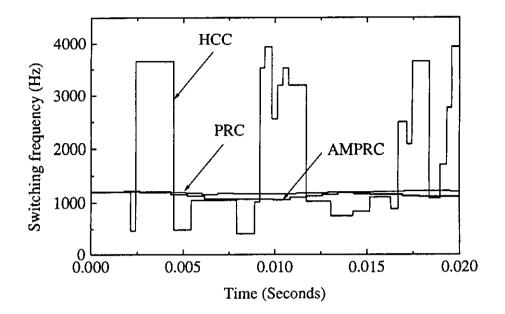

| 2.20              | Switching frequency distribution of PRC and HCC over a fundamental                                                                                                                                                                                                                                                              |                |

|                   | period for operation with a three phase inverter with star connected load                                                                                                                                                                                                                                                       |                |

|                   |                                                                                                                                                                                                                                                                                                                                 |                |

|                   | having $V_s = 240$ V, R = 8 $\Omega$ , L = 0.0191H, f = 50Hz and $I_m = 5$ A                                                                                                                                                                                                                                                    | 47             |

|                   | having $V_s = 240$ V, R = 8 $\Omega$ , L = 0.0191H, f = 50Hz and $I_m = 5$ A                                                                                                                                                                                                                                                    | 47             |

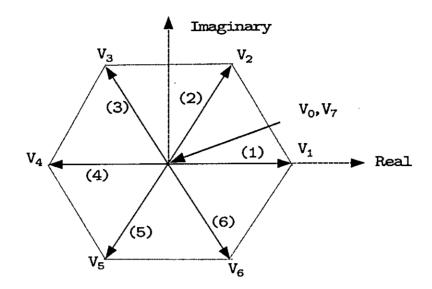

| 3.1               |                                                                                                                                                                                                                                                                                                                                 | 47<br>51       |

| 3.1<br>3.2        |                                                                                                                                                                                                                                                                                                                                 | 51             |

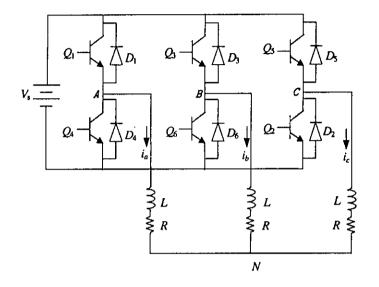

|                   | Three phase inverter with neutral unconnected star load                                                                                                                                                                                                                                                                         | 51             |

| 3.2               | Three phase inverter with neutral unconnected star load                                                                                                                                                                                                                                                                         | 51             |

| 3.2               | Three phase inverter with neutral unconnected star load                                                                                                                                                                                                                                                                         | 51             |

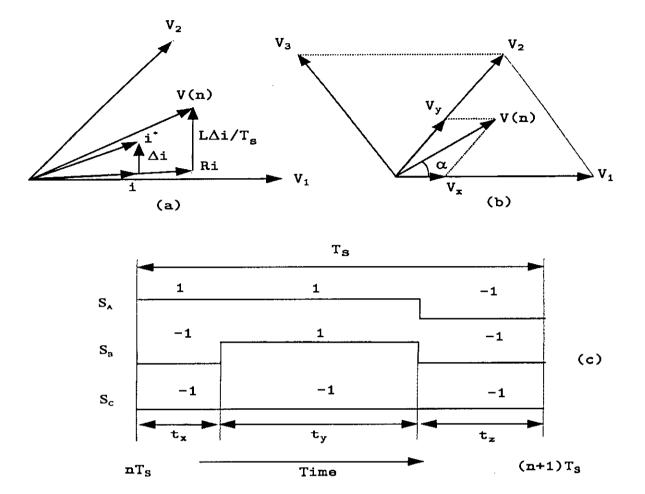

| 3.2               | Three phase inverter with neutral unconnected star load. $\dots$ $\dots$ $\dots$ $N$<br>Voltage vectors of a three phase inverter in the complex plane. $\dots$ $N$<br>Predictive current control scheme (a) Detailed vector diagram, (b) Vector<br>diagram showing projection of a typical vector $V(n)$ on the inverter state | 51<br>53       |

| 3.2               | Three phase inverter with neutral unconnected star load                                                                                                                                                                                                                                                                         | 51<br>53       |

| 3.2<br>3.3        | Three phase inverter with neutral unconnected star load                                                                                                                                                                                                                                                                         | 51<br>53       |

| 3.2<br>3.3        | Three phase inverter with neutral unconnected star load                                                                                                                                                                                                                                                                         | 51<br>53<br>56 |

| 3.2<br>3.3<br>3.4 | Three phase inverter with neutral unconnected star load                                                                                                                                                                                                                                                                         | 51<br>53<br>56 |

| 3.2<br>3.3<br>3.4 | Three phase inverter with neutral unconnected star load                                                                                                                                                                                                                                                                         | 51<br>53<br>56 |

| 3.2<br>3.3<br>3.4 | Three phase inverter with neutral unconnected star load                                                                                                                                                                                                                                                                         | 51<br>53<br>56 |

-

٠.

^ •••

\_

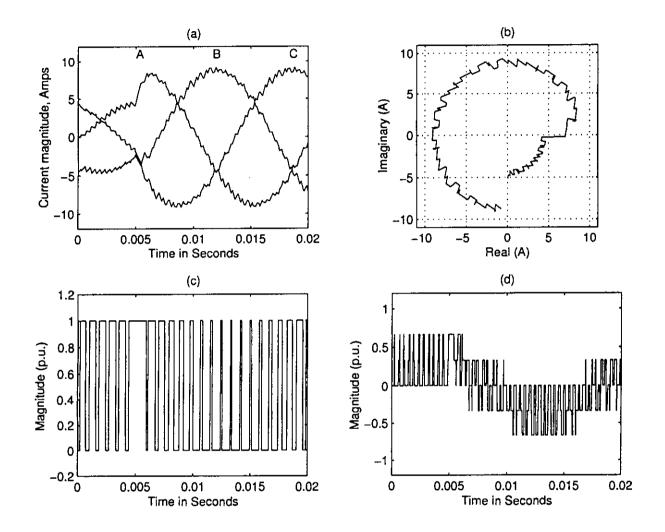

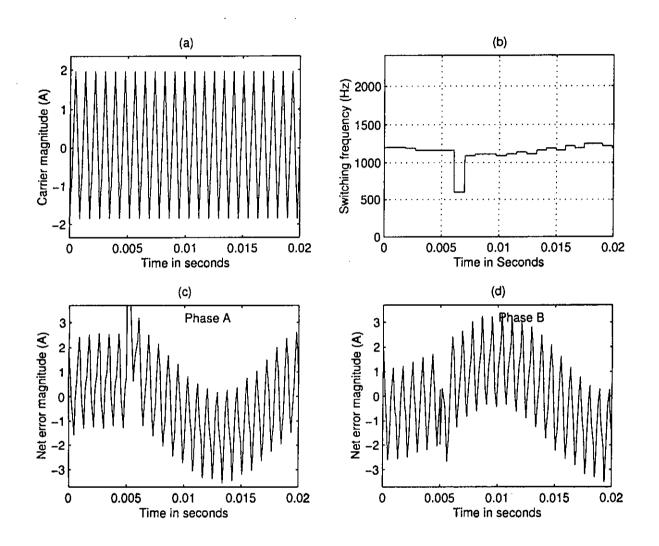

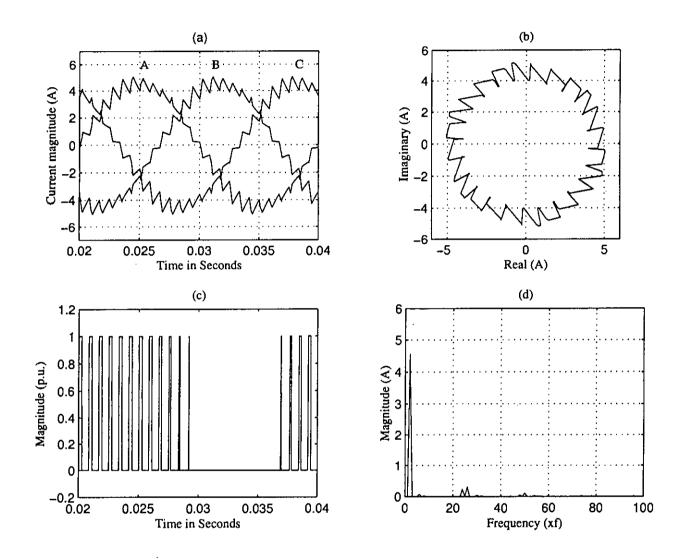

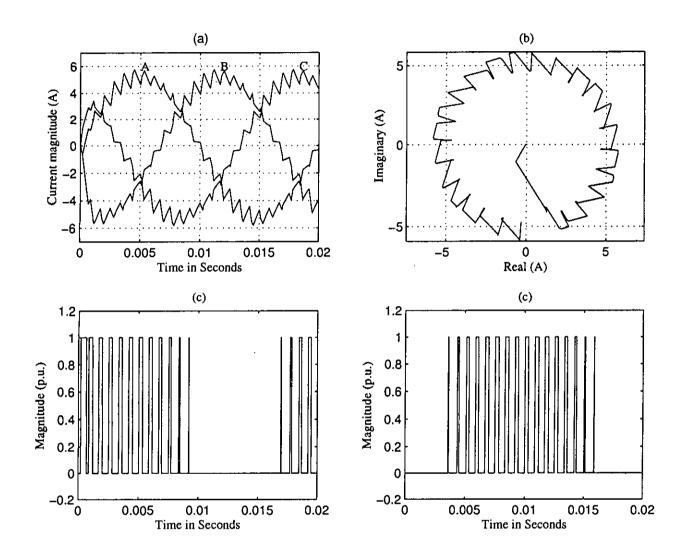

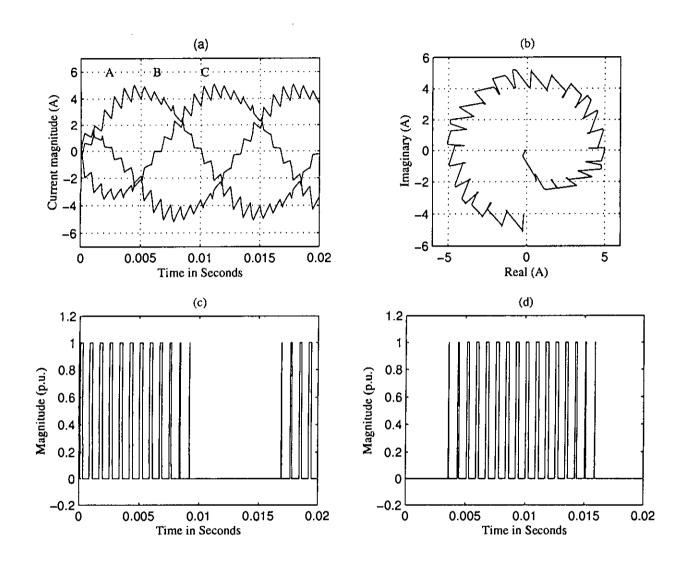

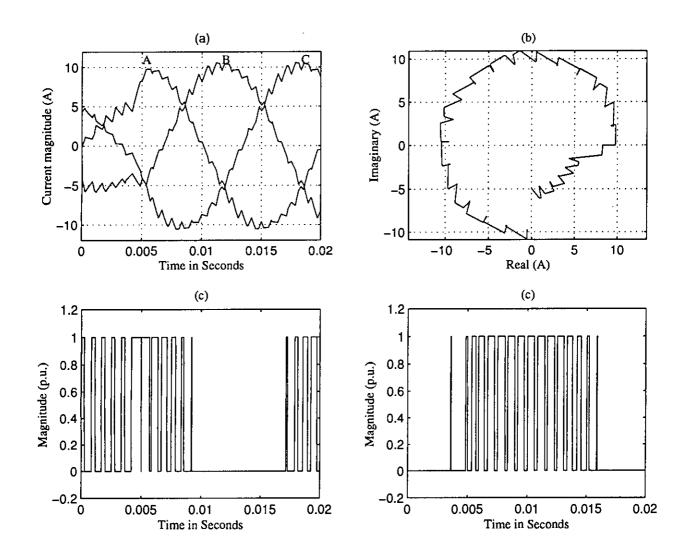

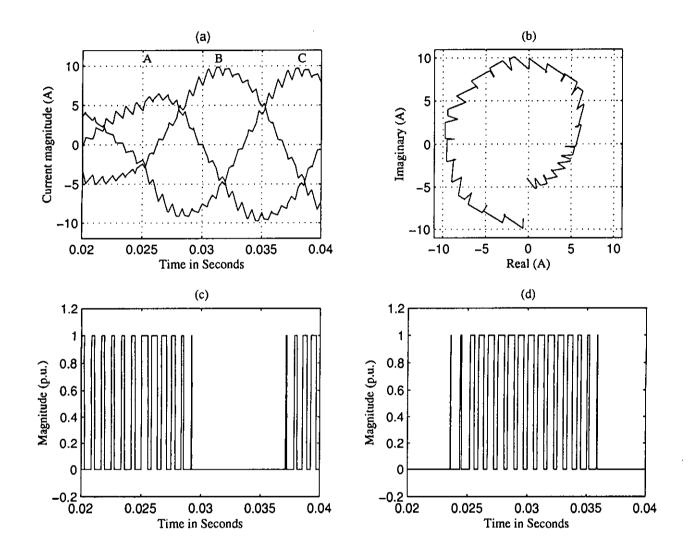

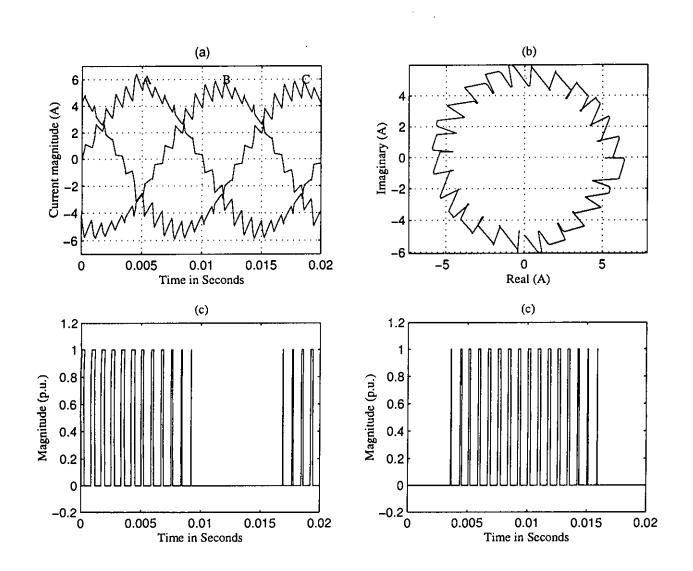

Steady state response of the proposed predictive controller (Method 2) 3.6 with  $R = 8\Omega$ , L = 19.1 mH, f = 50 Hz,  $f_s = 1200 \text{Hz}$ ,  $I_m = 5 \text{A}$ ,  $V_s = 240 \text{V}$ : (a) Load current waveforms, (b) Load current vector in complex plane, (c) PWM switching pattern for switch  $Q_1$ , (d) Load current spectrum. . . . 64 Startup response of the proposed predictive controller (Method 1) with 3.7 $R = 8\Omega$ , L = 19.1 mH, f = 50 Hz,  $f_s = 1200 Hz$ ,  $I_m = 5A$ ,  $V_s = 240 V$ : (a) Load current waveforms, (b) Load current vector in complex plane, (c) PWM switching pattern for switch  $Q_1$ , (d) PWM switching pattern for 65 switch  $Q_3$ ..... Startup response of the proposed predictive controller (Method 2) with 3.8  $R = 8 \Omega$ , L = 19.1 mH, f = 50 Hz,  $f_s = 1200 Hz$ ,  $I_m = 5A$ ,  $V_s = 240 V$ : (a) Load current waveforms, (b) Load current vector in complex plane, (c) PWM switching pattern for switch  $Q_1$ , (d) PWM switching pattern for 66 switch  $Q_1$ . Dynamic response of the proposed predictive controller (Method 1) for a 3.9 step change in current reference by 200% ( $I_m = 5A$  to 10A) with R = 8 $\Omega$  , L = 19.1mH, f = 50Hz,  $f_s$  = 1200Hz,  $V_s$  = 240V : (a) Load current waveforms, (b) Load current vector in complex plane, (c) PWM switching pattern for switch  $Q_1$ , (d) PWM switching pattern for switch  $Q_3$ . . . . . 67 3.10 Dynamic response of the proposed predictive controller (Method 2) for a step change in current reference by 200% ( $I_m = 5A$  to 10A) with R = 8 $\Omega$ , L = 19.1mH, f = 50Hz,  $f_s = 1200$ Hz,  $V_s = 240$ V : (a) Load current waveforms, (b) Load current vector in complex plane, (c) PWM switching pattern for switch  $Q_1$ , (d) PWM switching pattern for switch  $Q_1$ . . . . . 68 3.11 Dynamic response of the proposed predictive controller (Method 1) for a step change in load impedance ( $R = 8\Omega$  to  $4\Omega$ , L = 19.1mH to .096mH) with f = 50Hz,  $f_s = 1200$ Hz,  $I_m = 5$ A,  $V_s = 240$ V : (a) Load current waveforms, (b) Load current vector in complex plane, (c) PWM switching pattern for switch  $Q_1$ , (d) PWM switching pattern for switch  $Q_3$ . . . . . . 69

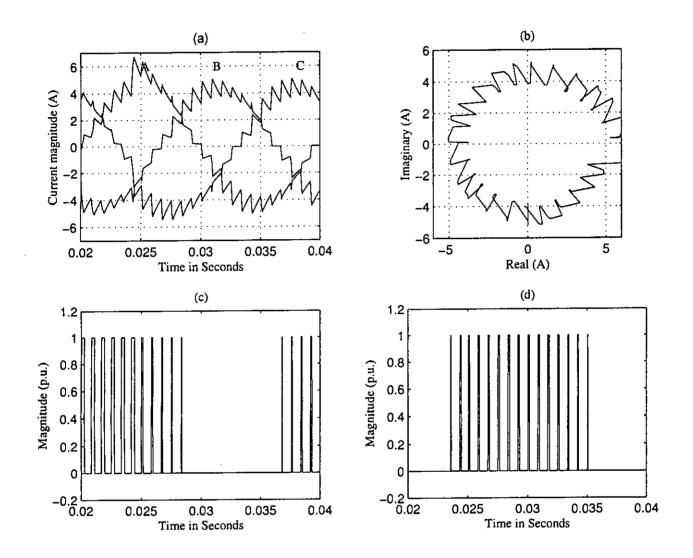

| <ul> <li>3.12 Dynamic response of the proposed predictive controller (Method 2) for a step change in load impedance (R = 8Ω to 4Ω, L = 19.1mH to .096mH) with f = 50Hz, f<sub>s</sub> = 1200Hz, I<sub>m</sub> = 5A, V<sub>s</sub> = 240V : (a) Load current waveforms, (b) Load current vector in complex plane, (c) PWM switching pattern for switch Q<sub>1</sub>, (d) PWM switching pattern for switch Q<sub>3</sub>, 70</li> </ul> | ì |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---|

| pattern for switch $Q_1$ , (d) PWM switching pattern for switch $Q_3$ 70                                                                                                                                                                                                                                                                                                                                                               |   |

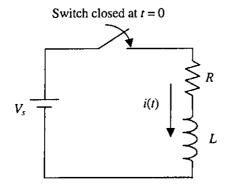

| 4.1 An unit step applied to an R-L load.                                                                                                                                                                                                                                                                                                                                                                                               | i |

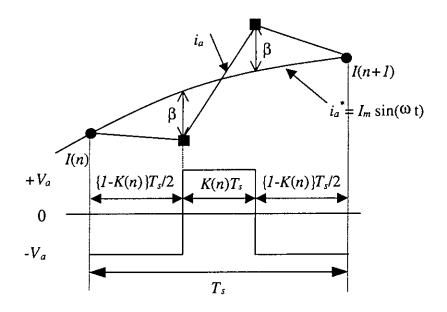

| 4.2 An $R - L$ load connected to a half bridge inverter and current waveform                                                                                                                                                                                                                                                                                                                                                           |   |

| to a two level PWM pulse                                                                                                                                                                                                                                                                                                                                                                                                               |   |

| 4.3 Current ripple in an R-L load with two level PWM                                                                                                                                                                                                                                                                                                                                                                                   |   |

| 4.4 A three phase inverter with star connected R-L load                                                                                                                                                                                                                                                                                                                                                                                | I |

| 4.5 Phase voltages in NEW-CC with star load (Neutral unconnected) 84                                                                                                                                                                                                                                                                                                                                                                   |   |

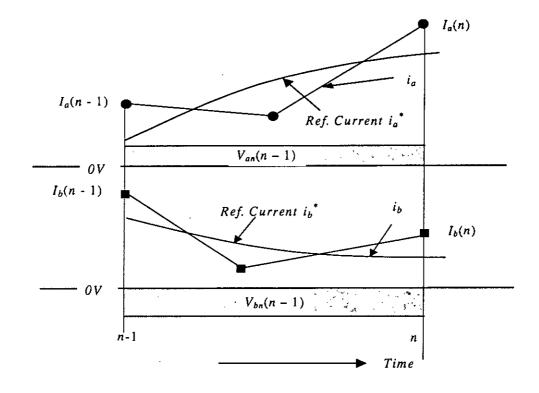

| 4.6 Load parameter estimation on carrier cycle basis.                                                                                                                                                                                                                                                                                                                                                                                  |   |

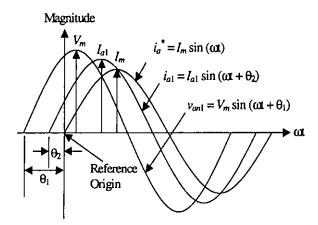

| 4.7 Waveforms showing relations between fundamental voltage, reference and                                                                                                                                                                                                                                                                                                                                                             |   |

| fundamental load currents                                                                                                                                                                                                                                                                                                                                                                                                              |   |

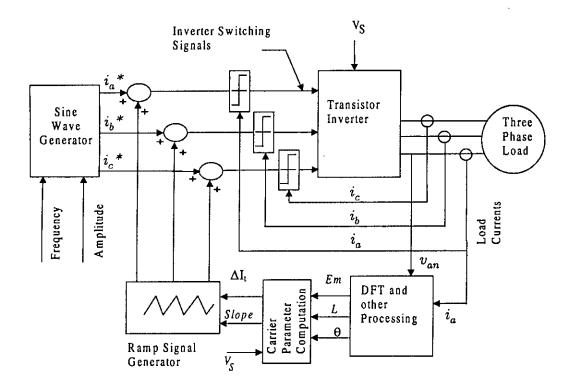

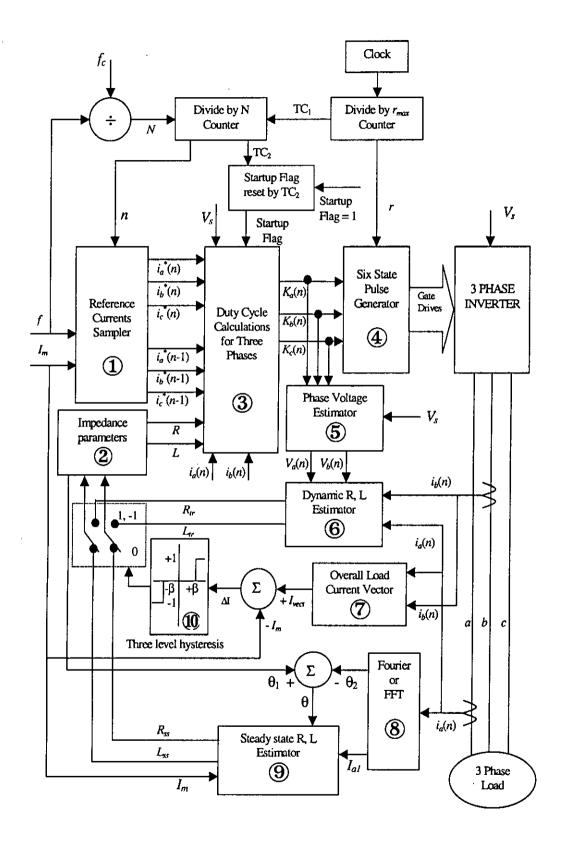

| 4.8 Scheme of the new current controller for three phase VSI                                                                                                                                                                                                                                                                                                                                                                           |   |

| 4.9 Real time control waveform for phase $A$ (two level PWM)                                                                                                                                                                                                                                                                                                                                                                           |   |

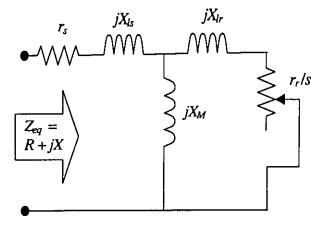

| 4.10 Equivalent circuit of an induction motor, (core loss shunt admittance ne-                                                                                                                                                                                                                                                                                                                                                         |   |

| glected)                                                                                                                                                                                                                                                                                                                                                                                                                               |   |

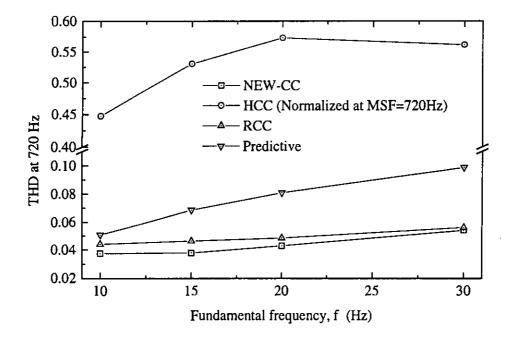

| 4.11 THD at MSF = 720Hz for 1kW 3-phase induction motor load at unity slip. 102                                                                                                                                                                                                                                                                                                                                                        |   |

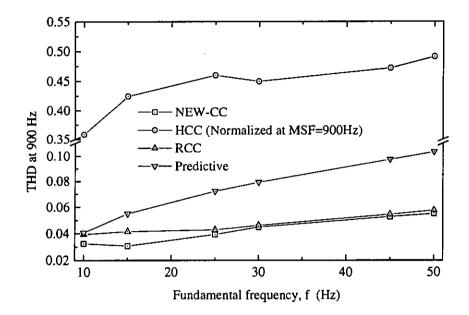

| 4.12 THD at MSF = 900Hz for 1kW 3-phase induction motor load at unity slip. 103                                                                                                                                                                                                                                                                                                                                                        |   |

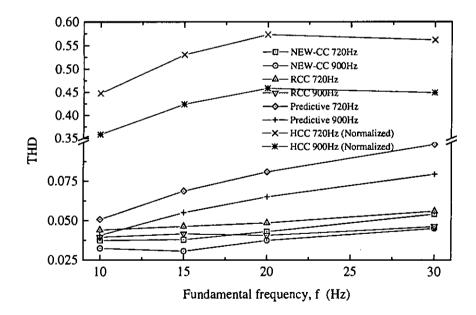

| 4.13 THD at different switching frequencies at unity slip                                                                                                                                                                                                                                                                                                                                                                              |   |

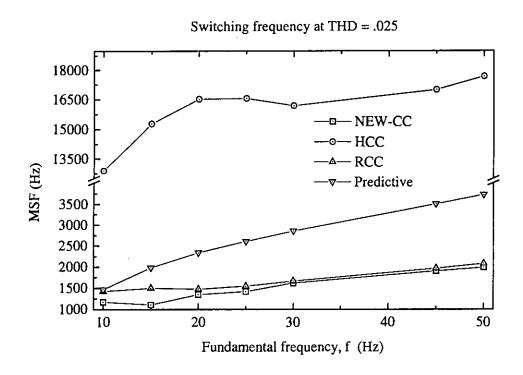

| 4.14 Maximum switching frequency (MSF) curves at $THD = 0.025$ at unity slip                                                                                                                                                                                                                                                                                                                                                           |   |

| for 1kW induction motor                                                                                                                                                                                                                                                                                                                                                                                                                |   |

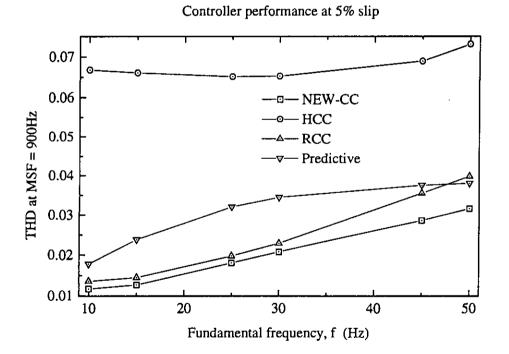

| 4.15 THD at MSF = 900Hz at Slip = 0.05 for 1kW induction motor 105                                                                                                                                                                                                                                                                                                                                                                     |   |

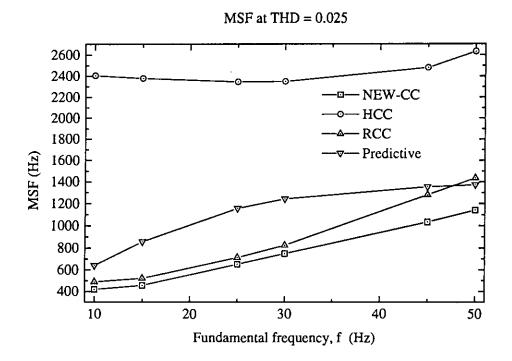

| 4.16 MSF at THD = $0.025$ at Slip = $0.05$ for 1kW induction motor 106                                                                                                                                                                                                                                                                                                                                                                 |   |

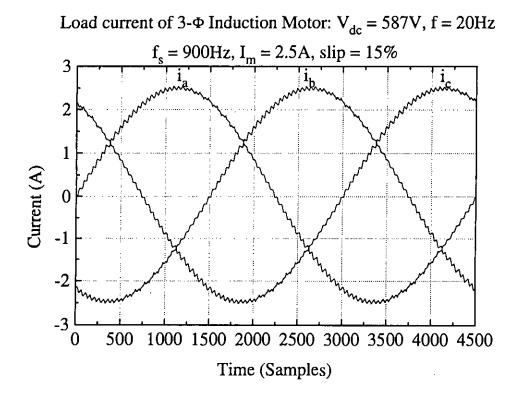

| 4.17 Motor phase currents at Slip = 0.15 with $V_s = 587$ V, f = 20Hz, $f_s = 900$ Hz,                                                                                                                                                                                                                                                                                                                                                 |   |

| $I_m = 2.5 A$                                                                                                                                                                                                                                                                                                                                                                                                                          |   |

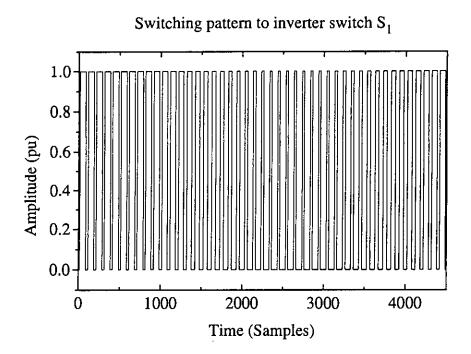

| 4.18 Switching waveform of $S_1$ of the inverter at Slip = 0.15 with $V_s = 587$ V, f                                                                                                                                                                                                                                                                                                                                                  |   |

| = 20Hz, $f_s = 900$ Hz, $I_m = 2.5$ A                                                                                                                                                                                                                                                                                                                                                                                                  | - |

ſ.

5

-

Ì

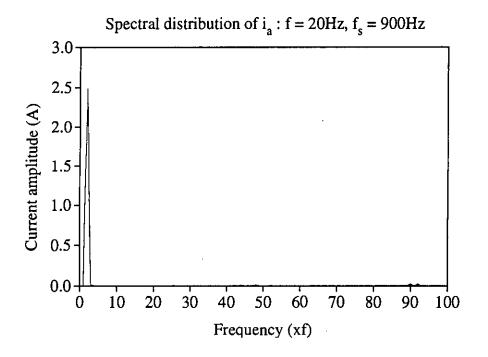

| 4.19 Spectrum of motor phase current at Slip = 0.15 with $V_s = 587V$ , f = 20Hz,                                                                                            |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 4.13 Spectrum of motor products $f_s = 900$ Hz, $I_m = 2.5$ A                                                                                                                |

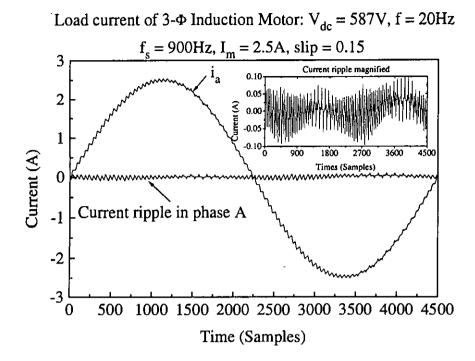

| 4.20 Motor phase current and current ripple at Slip = 0.15 with $V_s = 587V$ , f                                                                                             |

| $= 20 \text{Hz}, f_s = 900 \text{Hz}, I_m = 2.5 \text{A}. \dots \dots$ |

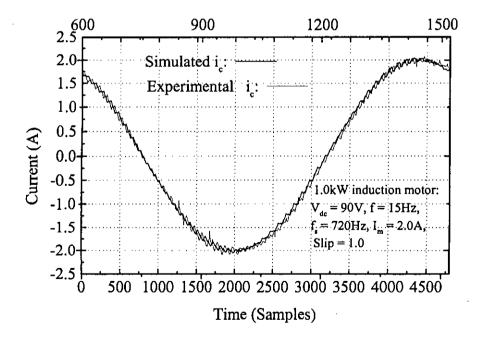

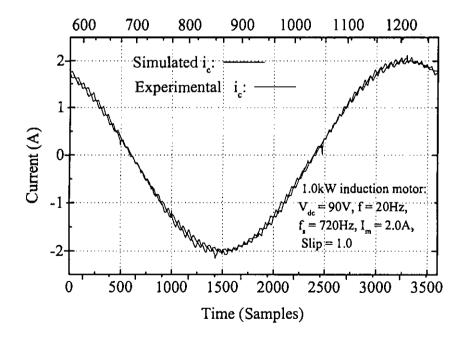

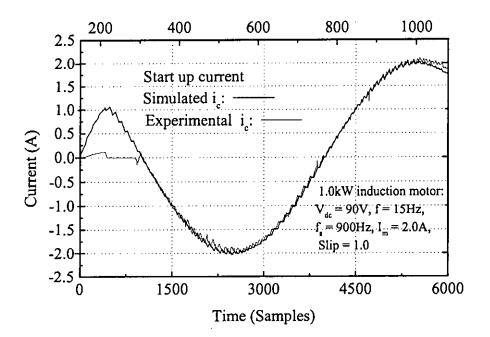

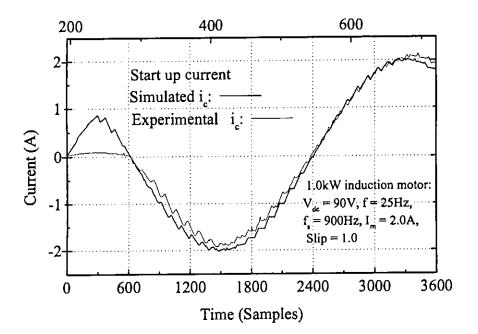

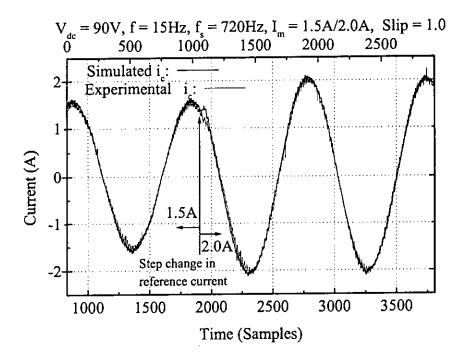

| 4.21 Simulated and experimental load current for $i_c$ at Slip = 1.0 with $V_s$ =                                                                                            |

| 90V, f = 15Hz, $f_s = 720$ Hz, $I_m = 2.0$ A                                                                                                                                 |

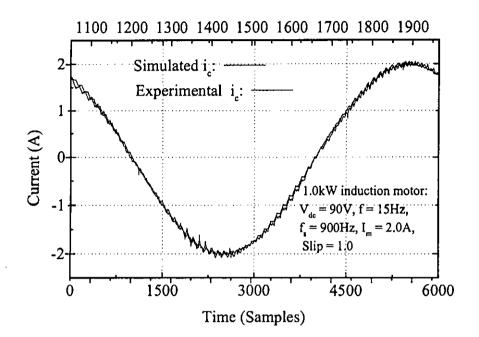

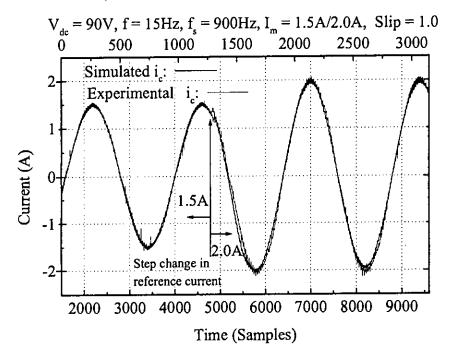

| 4.22 Simulated and experimental load current for $i_c$ at Slip = 1.0 with $V_s$ =                                                                                            |

| 90V, f = 15Hz, $f_s$ = 900Hz, $I_m$ = 2.0A                                                                                                                                   |

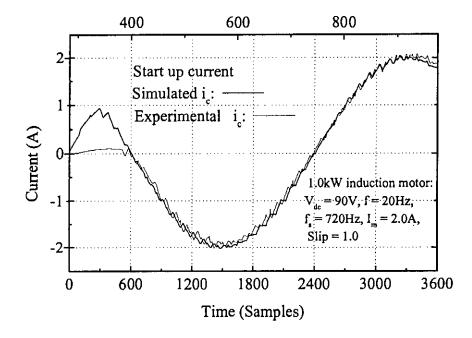

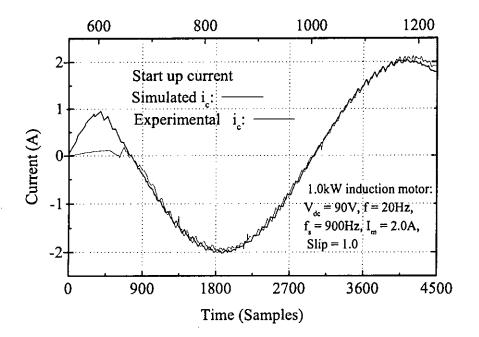

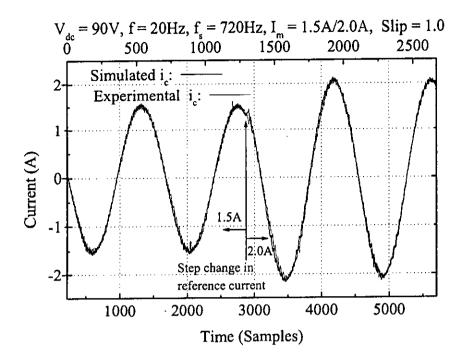

| 4.23 Simulated and experimental load current for $i_c$ at Slip = 1.0 with $V_s$ =                                                                                            |

| 90V, f = 20Hz, $f_s = 720$ Hz, $I_m = 2.0$ A                                                                                                                                 |

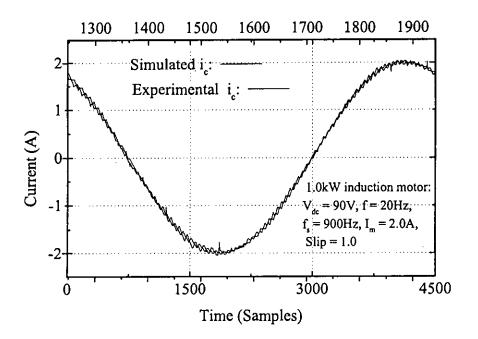

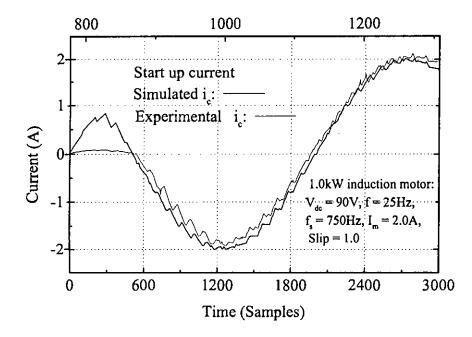

| 4.24 Simulated and experimental load current for $i_c$ at Slip = 1.0 with $V_s$ =                                                                                            |

| 90V, f = 20Hz, $f_s = 900$ Hz, $I_m = 2.0$ A                                                                                                                                 |

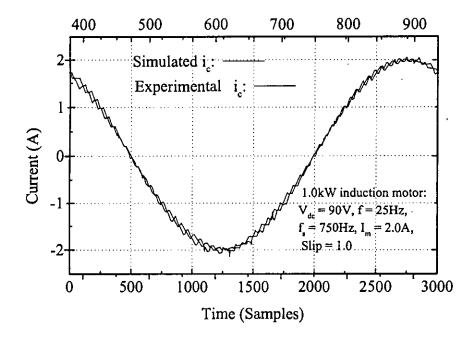

| 4.25 Simulated and experimental load current for $i_c$ at Slip = 1.0 with $V_s$ =                                                                                            |

| 90V, f = 25Hz, $f_s = 750$ Hz, $I_m = 2.0$ A                                                                                                                                 |

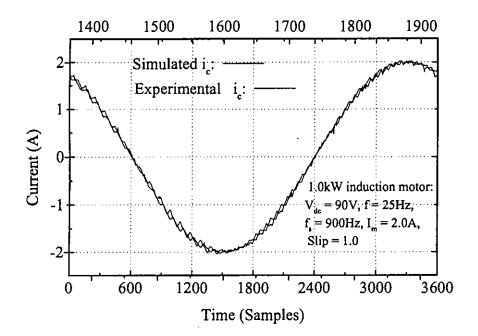

| 4.26 Simulated and experimental load current for $i_c$ at Slip = 1.0 with $V_s$ =                                                                                            |

| 90V, f = 25Hz, $f_s$ = 900Hz, $I_m$ = 2.0A                                                                                                                                   |

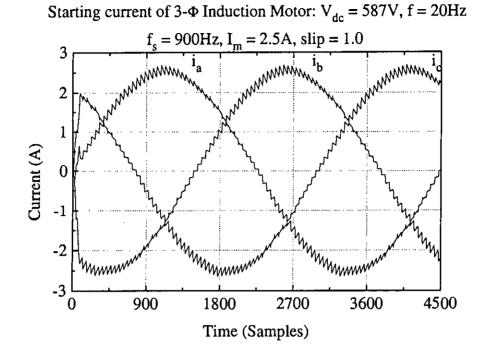

| 4.27 Motor starting current (Slip = 1.0) with $V_s = 587$ V, f = 20Hz, $f_s = 900$ Hz,                                                                                       |

| $I_m = 2.5 \text{A}.  \dots  \dots  \dots  \dots  \dots  \dots  \dots  \dots  \dots  $                                                                                       |

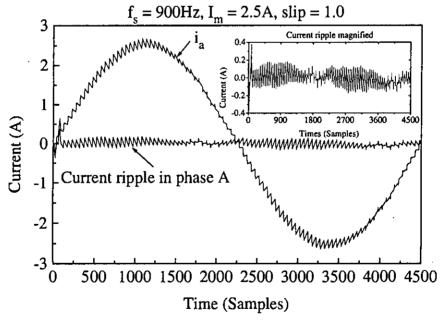

| 4.28 Starting phase current and current ripple (Slip = 1.0) with $V_s = 587$ V, f =                                                                                          |

| $20$ Hz, $f_s = 900$ Hz, $I_m = 2.5$ A                                                                                                                                       |

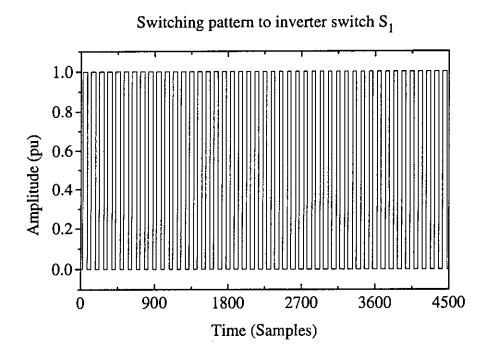

| 4.29 Start-up switching pattern of $S_1$ (Slip = 1.0) with $V_s = 587$ V, f = 20Hz,                                                                                          |

| $f_s = 900 \text{Hz}, I_m = 2.5 \text{A}.$                                                                                                                                   |

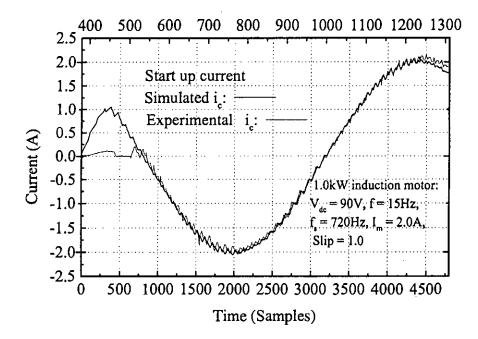

| 4.30 Experimental start-up current waveform of $i_c$ at Slip = 1.0 with $V_s = 90V$ ,                                                                                        |

| $f = 15Hz, f_s = 720Hz, I_m = 2.0A 114$                                                                                                                                      |

| 4.31 Experimental start-up current waveform of $i_c$ at Slip = 1.0 with $V_s = 90V$ ,                                                                                        |

| $f = 15$ Hz, $f_s = 900$ Hz, $I_m = 2.0$ A                                                                                                                                   |

| 4.32 Experimental start-up current waveform of $i_c$ at Slip = 1.0 with $V_s = 90V$ ,                                                                                        |

| $f = 20Hz, f_s = 720Hz, I_m = 2.0A 115$                                                                                                                                      |

| 4.33 Experimental start-up current waveform of $i_c$ at Slip = 1.0 with $V_s = 90V$ ,                                                                                        |

| $f = 20$ Hz, $f_s = 900$ Hz, $I_m = 2.0$ A                                                                                                                                   |

,

٦.

.

•

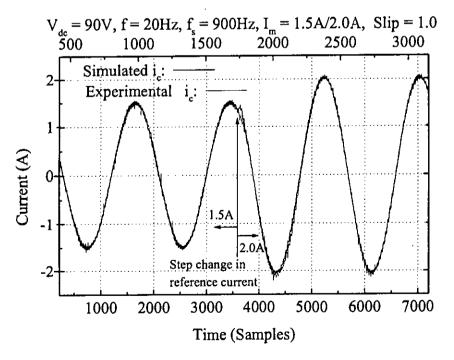

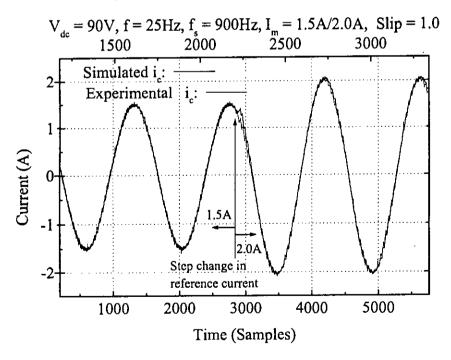

- 4.41 Experimental current waveform of  $i_c$  with a step change in current reference from  $I_m = 1.5$ A to 2.0A (Slip = 1.0,  $V_s = 90$ V, f = 25Hz,  $f_s = 900$ Hz.) . . 120

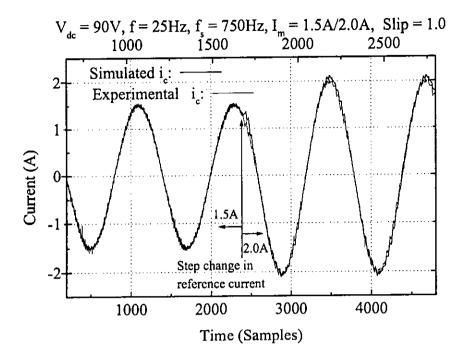

from  $I_m = 1.5$ A to 2.0A (Slip = 1.0,  $V_s = 90$ V, f = 25Hz,  $f_s = 750$ Hz.) . . 120

## Chapter 1

## Introduction

#### 1.1 General

The availability of power semiconductor switches in the late 1970's resulted in a major change in control and conversion of electrical power by electronics. Among the different static power converters, the dc-to-ac converter, called inverter has widespread application in various forms of power supplies, active power filters, high frequency heating and ac motor drives. Prior to the introduction of static power inverters, ac motors were considered as constant speed drives depending mainly on the frequency of the supply. In variable speed applications, dc motors were the only choice.

Variable frequency inverters have widened the application of ac motors in the industrial sector. The cage type three-phase induction motor is considered as the work-horse in the industry because of its robustness, reliability, efficiency and low cost. Before the mid 1980's analog and LSI (large scale integration) digital integrated circuits were used for control signal generation of inverters. A large number of integrated circuits were required for control purposes. The VLSI (very large scale integration) technology flourished in the late 1980's. The VLSI technology helped the design of powerful programmable devices such as microprocessors, digital signal processors and application-specific-integrated-circuits (ASIC). Inverter and motor drive controls using microprocessors have become the interest of engineers and researchers because of the advanced programmable features, flexibility in the implementation and the increasing trend of generalization.

1

The models of the inverter and ac motors are inherently non-linear. These models are associated with many interdependent parameters. An efficient scheme should have the capability of considering all the parameters to provide good system performance. The present trend of fast computing microprocessors is making the task of on-line implementation of the inverter operation and motor control an affordable one. Computation intensive schemes are getting widely used for real time implementation. New computation techniques are rapidly evolving to improve the steady state and dynamic performances of the inverter and drive systems.

The availability of high speed and high power semiconductor devices such as BJT, MOS-FET, IGBT, SITH, MCT, IGCT etc. allow higher switching frequencies with low losses. As a result, the application area of inverters has increased. On line control of voltage, frequency and current of an inverter during dynamic loading involves extensive computations, and requires complex schemes of implementation by a microprocessor and a digital signal processor. Researchers are trying to simplify complicated schemes with advanced/easy control algorithms. Continuous efforts are being made and newer schemes are evolving with better results but with new limitations. Because of the diversity of inverters and drive controls, various non-linear parallel control strategies such as neural network and fuzzy controller are also being advocated for new state and parameter estimation. There are different types of inverters for different applications. Control methods are also different for different inverter types.

#### **1.2** Inverter Types and Controls

The function of an inverter is to change a dc-input voltage to a symmetrical ac output voltage. The output voltage could be at a fixed or variable frequency. A variable output voltage can be obtained by varying the input dc voltage. On the other hand, if the dc input voltage is fixed and is not controllable, a variable output voltage can be obtained by varying the duty cycle of the inverter, which is normally accomplished by pulse-width-modulation (PWM) control of the inverter.

The output voltage waveforms of ideal inverters should be sinusoidal. However, the

waveforms of practical inverters are non-sinusoidal and contain harmonics. For low and medium-power applications, square-wave or quasi-square-wave voltages may be acceptable, but for high-power applications, sinusoidal waveforms with distortions as low as possible, are required. With the availability of high-speed power semiconductor devices, the harmonic contents of output voltage can be reduced significantly by switching techniques.

Inverters can broadly be classified into two types: single-phase inverters and three-phase inverters. In each type, controlled turn-on and turn-off devices (e.g., BJTs, MOSFETs, IGBTs, MCTs, SITs, GTOs) or forced-commutated thyristors can be used depending on applications. These inverters generally use PWM control signals for producing an ac output voltage. An inverter is called a voltage source inverter (VSI) if the input voltage remains constant or an inverter is called a current source inverter (CSI) if the input voltage remains constant or an inverter is called a current source inverter (CSI) if the input current is maintained constant. The structure of a CSI is costlier compared to VSI. Applications of CSI are limited to low-switching frequencies because of its current commutation requirement. On the other hand, VSI has large range of the switching frequency and modern high speed switching devices can be used in such inverters. For this reason, VSIs are preferred for most applications including ac motor drives. During the last three decades, different schemes of inverter control in voltage reference PWM and current reference PWM have been proposed for VSIs.

### 1.3 Pulse Width Modulation (PWM) Techniques

The output voltages of a modern power inverter are controlled by pulse width modulation (PWM) techniques. Many modulation techniques are available in the literature for the control of VSIs. A VSI can be operated in the output voltage or output current control modes. In either control modes, the schemes support reduction of low frequency harmonic contents by voltage or current reference PWM techniques. In a VSI inverter, the voltage reference PWM techniques basically control the inverter output voltage using standard schemes and do not have direct control over the load current. Their harmonic behaviours are well defined. On the other hand, a current-reference-modulation technique controls

the operation of the VSI by means of feedback from the load current and other system parameters. Current-reference-modulation techniques have control over the load current, but their implementation is complex compared to voltage reference schemes because of the feedback requirement.

#### **1.3.1** Voltage Reference PWM

The earliest modulation techniques applied to inverter operation are the single pulse and the multiple pulse modulations [1, 2]. These techniques are capable of providing inverter output voltages with low total harmonic contents. However, the output voltages contain low order harmonics that are harmful for drive applications. To overcome the effect of low order harmonics these techniques were replaced by the sinusoidal pulse width modulation (SPWM) [3].

In SPWM technique, the switching points of the PWM pattern (modulated wave) are obtained by comparing a sine wave with a high frequency triangular wave (carrier). Based on the carrier generation, there are different types of carrier waves [4-9]. The basic analog SPWM with asynchronous carrier generates sub-harmonics. Complex schemes are required to remove the sub-harmonics. Moreover, analog schemes are not suitable for inverter operation in wide range of frequency because of component drift and offset problem. The microprocessor implementation of the basic naturally sampled SPWM is difficult because of the involvement of transcendental equations in the computation of the switching points. However, schemes are available in the literature for implementation of naturally sampled SPWM with a microcomputer using advance computational algorithm [10]. Researchers have simplified the basic SPWM for use with a microprocessor.

The simplified numerical form of SPWM is popularly known as Regular Sampled PWM (RSPWM) [11]. The Regular Sampled PWM generates a stream of regularly spaced pulses whose widths are modulated by the amplitude of the sinusoidal modulating wave (fundamental voltage). The spectral distribution of RSPWM depends on the carrier frequency. The harmonic spectrum of the output waveform primarily contains the fundamental modulating frequency, the carrier, multiples of carrier and side bands. The harmonic contents are negligible at intermediate frequencies by the nature of the modulation process. By

choosing a relatively high carrier frequency a small filter is sufficient to filter out all the harmonic contents to acceptable range. Different schemes and implementation strategies are reported in the literature for RSPWM [12-29].

The Harmonic Minimized Sampled PWM (HMSPWM) is similar to RSPWM but, here, third harmonic is added intentionally to some extent to the sine-modulating wave. Third harmonics and its multiples cancels out in a star connected load with insulated neutral. For the same modulation index, HMSPWM gives higher voltage than RSPWM. It is observed that for HMSPWM, the output voltage maintains a linear relationship with the modulation index upto 120% [30], whereas, for RSPWM the linear relation holds upto 100%. The linear over-modulation feature of HMSPWM makes it suitable for certain applications (for example, in the constant power operating region of drives) requiring high voltages [30, 31].

The Specific Harmonic Elimination PWM (SHEPWM) generates a regularly sampled pulse stream and the switching edges are obtained analytically by eliminating certain specific harmonic contents [32-36]. This technique is particularly suitable for very high power drives where thyristors or GTO switches are the only choice (because of very high power handling requirement). The switching frequency is maintained as low as possible. The low order harmonic contents such as 5th, 7th, 11th, 13th, 17th, 19th harmonics are generally eliminated. The SHEPWM technique is computation intensive. These are generally calculated off-line and implemented with a microprocessor using ROM based look-up tables.

In Regular Sampled Harmonic Elimination PWM, the leading edge of a PWM pattern is calculated from the reference modulating signal and the trailing edge is determined from the shifted reference signal. The PWM pattern obtained in this technique is close to that obtained by SHEPWM [37]. The switching edges can be calculated on-line and the implementation scheme is similar to that of RSPWM.

The Delta Modulation (DM) technique is a simple scheme for generating switching waveforms of inverters [38]. The DM scheme is capable of on-line harmonic minimization. Tuning the feedback filter can control its performance. Several types of delta modulation have been investigated so far for various power converter operations including inverters [39-41]. The DM schemes have the disadvantages of non-uniform switching and suffer from sub-harmonic problems in case of wide bands.

Besides the above mentioned standard modulation techniques, there are some space vector PWM techniques commonly known as field oriented flux vector controllers [42-45]. The field oriented flux vector controllers are associated with ac motor drives and calculates the voltage vector from motor parameters, flux magnitude and position of the motor's shaft. The inverter switching states are selected from lookup tables with the information of the magnitude and position of the voltage vector. The PWM pattern for the inverter switches are close to regular sampled PWM. However, flux vector control techniques support linear over-modulation and hence are suitable for high-speed operation of motors (in constant power region). The vector controllers are computation intensive. The vector controllers are generally implemented with a Digital Signal Processor (DSP) and hence the overall cost of the controller is much greater than all other voltage reference controllers. However, now a days low cost DSPs are emerging.

#### **1.3.2** Need for Current Control

The VSI is composed of power semiconductor devices. Semiconductor switches do not have over current capability except the thyristor family. Thyristors such as silicon controlled rectifier (SCR) and gate turnoff thyristors (GTO) can withstand high surge current for few milliseconds but they are slow devices and hence are not suitable for modern drives requiring high switching frequencies. The current flow to the load in a VSI depends on the load characteristics as well as on the input supply voltage. If the load impedance is constant during the entire operating period of the inverter, the current flow through the inverter will be constant. On the other hand, if the load impedance varies over a wide range during the operation of the inverter there is the risk of over-current. For example, ac motors are highly non-linear and their equivalent impedance variation also occurs during load change in the steady state operating condition.

In a VSI fed ac motor drive, there exists over-current conditions and thus instantaneous over-current control is necessary so that the current does not exceed the current limit of the inverter switches. Sinusoidal current waveform is the requirement for smooth motor operation over wide speed range. If the motor phase current contains considerable harmonics, then there will be torque pulsation and noise. Hence, in high performance drive systems the PWM control technique should have a current limiting feature and lower harmonic distortion.

#### 1.4 Current Reference PWM

In the current reference techniques, a current controller forces the load current to follow the current command which is usually a sinusoid. Common strategies of current controllers can be classified as hysteresis controller, ramp comparison controller and predictive controller. In a hysteresis current controller (HCC) a PWM pattern is generated comparing a reference sinusoidal current waveform with the actual load current. Hysteresis comparators are used to impose a dead-band or hysteresis around the reference current. The PWM pattern forces the load current to follow the sinusoidal reference current limiting the current ripple within the hysteresis band. The hysteresis control scheme provides good dynamic performance [46-49], because it acts quickly. However, the main disadvantage of this type of controller is the variation of the switching frequency within the fundamental period. Also, the limit cycle behaviour is present in case of HCC.