#### 8085-BASED UNIVERSAL EPRON PROGRAMMER

BY

#### KHANDAKER ATWAR HOSSAIN

#### A PROJECT REPORT

SUBMITTED TO THE DEPARTMENT OF ELECTRICAL AND ELECTRONIC ENGINEERING, BANGLADESH UNIVERSITY OF ENGINEERING AND TECHNOLOGY IN PARTIAL FULFILMENT OF THE REQUIREMENT FOR THE

DEGREE OF

MASTER OF ENGINEERING

DEPARTMENT OF ELECTRICAL AND ELECTRONIC ENGINEERING

BANGLADESH UNIVERSITY OF ENGINEERING AND TECHNOLOGY

JANUARY, 1985.

#### CERTIFICATE

This is to certify that this project work was done by me and it has not been submitted elsewhere for the award of any degree or diploma.

Countersigned

(Dr. Syed Mahbubur Rahman) Supervisor.

Signature of candidate

Accepted as satisfactory for the partial fulfilment of the requirements for the degree of Master of Engineering in Electrical and Electronic Engineering.

#### EXAMINERS

1. (Dr. Syed Mahbubur Rahman)

Assistant Professor,

Computer Engineering Department

Bangladesh University of Engineering

and Technology, Dhaka, Bangladesh

Supervisor

2. (Dr. Shamsuddin Ahmed)

Dean

Faculty of Electrical and

Electronic Engineering,

Bangladesh University of Engineering

and Technology, Dhaka, Bangladesh

Member

3. (Dr. Syed Fazl-i Rahman)

Professor and Head,

Department of Electrical and

Electronic Engineering,

Bangladesh University of Engineering

and Technology, Dhaka, Bangladesh

Member

4. (Dr. Mahfuzur Rahman)

Professor and Head,

Computer Engineering Department

Bangladesh University of Engineering

and Technology, Dhaka, Bangladesh.

Member

DHAKA

JANUARY, 1985

# ALL PRAISES TO ALLAH, THE MERCIFUL

#### ACKNOWLEDGEMENT

The author expresses his indebtness and deep sense of gratitude to Dr. Syed Mahbubur Rahman, Assistant Professor of Computer Engineering Department, Bangladesh University of Engineering and Technology, Dhaka for his continuous guidance encouragement and help and continuous suggestions all along the course of this work.

The author wishes to express his great indebtness to Dr.

Shamsuddin Ahmed, Dean of the Faculty of Electrical and Electronic

Engineering for his interest in progressing the project work.

The author also expresses his greatfulness and thanks to Dr. S.F. Rahman, Head of the Department of Electrical and Electronic Engineering and to Dr. Mahfuzur Rahman, Head of the Department of Computer Engineering, who were kind enough to provide all the facilities of the Departments for this work.

The author expresses his indeptness to Mr. Abdul Hannan, Principal, Khulna Engineering College, for his keen interest and encouragement in pursuing the post graduate studies.

Microprocesser based designs require to store their eperating and additional programs in a permanent memory such as an EPROM. EPROM programmers are thus an essential requirement for any microprocessor based design. The present project work deals with the development of a 8085-based EPROM programmer, which can be used in Program, Verify, Read, Display, Copy and Frint Mode. Programs have been developed for the Intel 2716, 2732, 2764 and 27128 EPROMs. Since the programmer is software controlled, any type of EPROM can be programmed just with a little change in the control program of the EPROM programmer. The project work, besides, greatly encouraging microcomputer based designs, will also save buying of costly manufactured programmers available in foreign market.

# CONTENTS

| CHAPTER | l I  | INTRODUCTION                                                    |         | Page |

|---------|------|-----------------------------------------------------------------|---------|------|

|         | 1.1  |                                                                 |         |      |

|         |      |                                                                 | •••     | 1    |

|         | 1.2  | Non-volatile memory                                             | • • •   | 1    |

|         | 1.3  | Some available EPROM                                            | •••     | 2    |

|         | 14   | Aim of the project                                              |         | 3    |

| CHAPTER | II   | SEMICONDUCTOR MEMORY                                            |         |      |

|         | 2.1  | Read-only memory                                                |         | 5    |

|         |      | 2.1.1 Manufacture-programmed ROM characteristics                | • • •   | 6    |

|         |      | 2.1.2 Programmable read-only memo programming characteristics   | ry      | 8    |

|         |      | 2.1.3 Erasable programmable Read-<br>memory (EPROM) programming | only    |      |

|         |      | characteristics                                                 | • • • • | 11   |

|         | 2.2  | Erasure characteristics of the EPR                              | MC      | 14   |

| CHAPTER | III  | MICROCOMPUTER                                                   |         |      |

|         | 3.1  | Basic microcomputer organization                                |         | 17   |

|         | 3.2  | The Intel 8085 microprocessor                                   |         | 19   |

|         |      | 3.2.1 8085 architecture and its pin diagram                     |         | 19   |

| CHAPTER | IV   | INTERFACE WITH PERIPHERAL DEVICE                                |         | 24   |

| CHAPTER | V    | PROGRAMMING CHARACTERISTICS OF INTERPROMS                       | EL      |      |

|         | 5.1/ | Comparative study of Intel EPROMs                               |         | 28   |

|         | 5.2  | 27-series EPROM operation                                       |         | 29   |

|         |      | 5.2.1 Read mode                                                 |         | 30   |

|         |      | 5.2.2 Standby mode                                              |         | 30   |

|         |      | 5.2.3 Program inhibit mode                                      |         | 33   |

|         |      | 5.2.4 Program verify mode                                       |         | 33   |

|         |      | 5.2.5 Programming mode                                          |         | 77   |

# CONTENTS (Contd.)

| CHAPTER |                                                              |       | Page |

|---------|--------------------------------------------------------------|-------|------|

| 5.3     | Programming of 8-48 and 8748 EPROMs                          |       | 34   |

| CHAPTER | VI HARDWARE DESIGN OF EPROM PROGRAMMER                       |       |      |

| 6.1     | Functional description of EPROM program                      | mer   | 38   |

| 6.2     | Detail circuit diagram of the programme                      | r     | 40   |

|         | 6.2.1 Address decoder                                        |       | 40   |

|         | 6.2.2 I/O and Expansion buffer                               |       | 44   |

|         | 6.2.3 Address high and address low buff                      | er    | 45   |

|         | 6.2.4 The data latches                                       | •••   | 45   |

| *       | 6.2.5 Control latches                                        | •••   | 46   |

| 6.3     | Connection of KPROM pins                                     | • • • | 49   |

| CHAPTER | VII SOFTWARE DEVELOPMENT                                     |       |      |

| 7.1     | Function of the programmer                                   | •••   | 52   |

| 7.2     | Program development of the programmer                        |       | 53   |

|         | 7.2.1 Read sub program                                       |       | 55   |

|         | 7.2.2 Conversion of ASCII coded number to hexadecimal number | •••   | 58   |

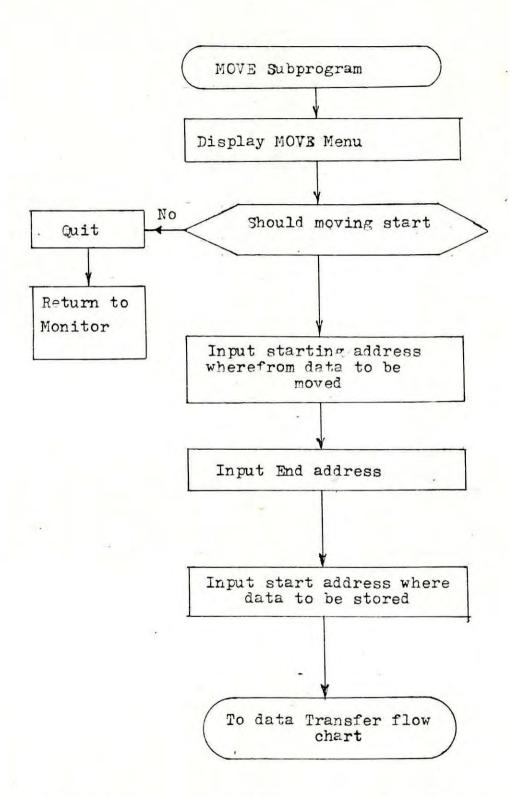

|         | 7.2.3 MOVE Subprogram                                        |       | 64   |

|         | 7.2.4 DISPLAY Subprogram                                     |       | 65   |

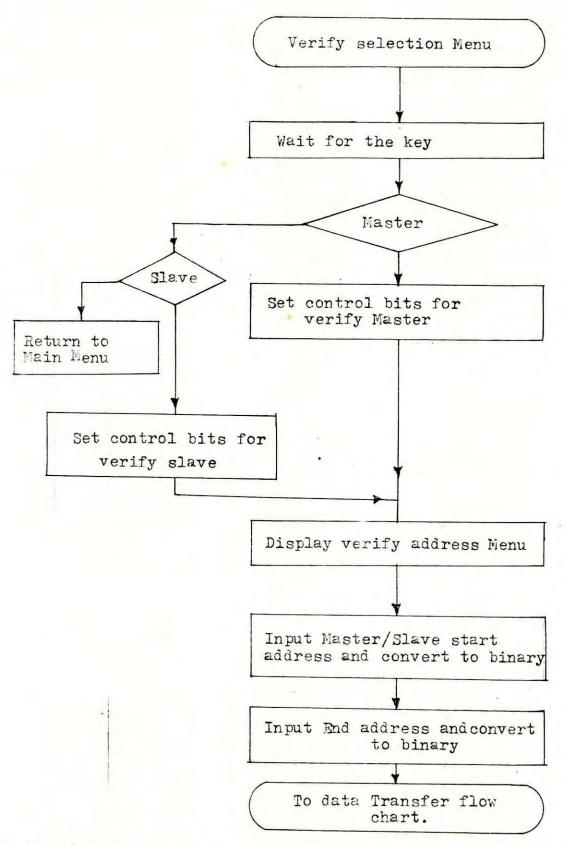

|         | 7.2.5 VERIFY Subprogram                                      |       | 68   |

|         | 7.2.6 PROGRAM Subprogram                                     |       | 71   |

|         | 7.2.7 COPY Subprogram                                        |       | 75   |

|         | 7.2.8 PRINT Subprogram                                       | •••   | 79   |

| CHAFTER | VIII DISCUSSION AND CONCLUSION                               |       |      |

|         | REFERENCES                                                   |       |      |

|         | APPENDIX - A                                                 |       |      |

Complete software program

## APPENDIX - B

- I. Pin diagram of IC Chips

- II. Pin diagrams of EPROMS.

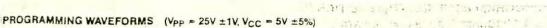

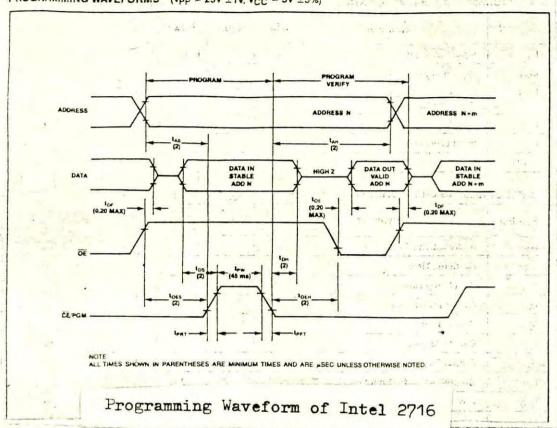

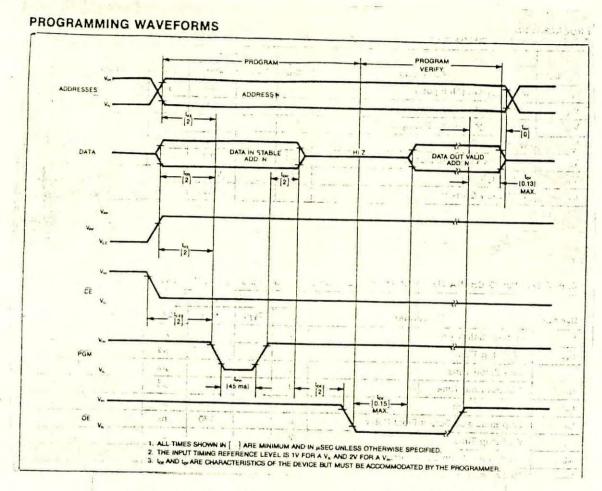

- III. Programming waveforms of EPROM

## APPENDIX - C

I. Printed circuit board design

#### CHAPTER - I

#### INTRODUCTION

#### 1.1 General Introduction

The advent of discrete semiconductors and the technological follow-on, e.g., the monolithic integrated circuits, have had significant impact on the performance, cost, reliability, maintainability, physical size, and architecture of central processing units of digital computer and allvarieties of digital systems.

The use of semiconductors has now started to spread to peripheral equipment and memory. When the memory elements are organized and combined in a particular arrangement, they are referred to as memory system.

# 1.2 Non-Volatile Memories

A memory section for storing permanent data, e.g., list of constants, tables of data conversion like trisonometric sine tables etc., and fixed computer programs like operating instructions, editor, monitor or utility programs, subroutins, keyboard encoder, character generator etc., do not require a write capability once it is loaded; thus time and cost may be saved by omitting the write feature. Such a storage device is called a Read-only Memory or ROM. The information stored in these devices will remain unchanged even if power is removed from the system which offers a considerable convenience. Moreover for data only occassionally changed, there are even cases between full write capability and the ROM. One such type is erasable programmable read-only memory

or EPROM.

EPROM has quickly found its popularity as a non-volatile temporary storage medium. More likely responsible is its attractive combination of field programmability, high density, and low power consumption when compared to bipolar fusible-link memories. Such devices, built with either p- or n- channel metal-oxide-semiconductor technology, have served well in prototyping microprocessor based system. There is an extra advantage for the user to see the actual silicon chip through the quartz window that lets the ultraviolet light for erasure.

## 1.3 Some Available EPROM Programmers

To program the EPROMs some devices are required known as EPROM programmer. Various types of EPROM programmer are available in the market. Performance of these programmers varies with the cost. These programmers are sometimes ON-line connected with the computer and sometimes independent units. Some available programmers are listed below along with their approximate prices.

- i. "Universal PROM programmer" by Intel corporation. It can program all kinds of EPROMs using different personality cards and programming adapter socket. It can be used as an independent unit and also micro-computer based with RS-232 cable. Price is around £ 1000.

- ii."PROM Programmer M9807" by Pro-Log Corporation. They

state "Built to handle the Programmable devices of today .... and tomorrow". Cost is above £ 1000.

iii. "EPROM Emulator and Programmer EP4000 produced by G.P. Industrial Electronics Ltd. It is a microprocessor controlled programmer which can program all the popular EPROMs of Intel Corporation. Cost is about £ 600.

iv. Rockwell International introduced an EPROM programmer with their microcomputer AIM-65<sup>9</sup>. It can program only the Intel 2716 EPROM. Duplication is not possible here.

v. H. Muller (Switzerland) designed an EFROM Programmer for the popular 2716 & 2732 EPROMs using timer, logic gate and other accessories. There is no scope of duplication. Material cost is around £  $25^{10}$ .

vi. H.S.Lynes (England) designed an EPROM Programmer to accommodate 2708, 2716 & 2732 EPROMs using drivers, latches etc. It is to be interfaced with microcomputer. Material cost is around £  $20^{11}$ .

## 1.4 Aim of the Project:

The EPROM Programmer to be designed is microcomputer controlled. It can be used for programming Intel 2716, 2732, and 2764 and 27128 EPROM and the EPROMs within the 8048H & 8087H microcomputer chips. An additional advantage over the available EPROM programmers is that with little modification

it can be used to program any type of EPROM available in the market. The 40 output ports should be connected to proper pins of the EPROM and a software with a little change should be written for the particular EPROM to be programmed.

EPROM is an essential part in all microcomputer based designs. As such the design of such a flexible EPROM programmer will greatly help the research works on the microcomputer designs. It will also replace the need for investment of quite a large amount of foreign exchange required for this purpose. With industrial backup commercial manufacturing may also be taken up.

# CHAPTER - II

#### SEMICONDUCTOR MEMORY

#### 2.1 Read-Only Memory

Semiconductor memories fall into two basic categories.

Read-only memories (ROMs) and Randam-access read/write memories (RAMs). ROM forms an important part of memory requirement in most microcomputer systems. This type of memory are also called fixed memory, permanent memory or read-only store (ROS).

In principle it is simply a special combination circuit because an input signal combination (address and entry) defines a unique output combination. The ROM can take a digital code at its input terminals and provide a unique digital code on its output terminals. The relationship between its input and output codes are relatively fixed, usually alterable only by slow techniques, and for this reason it is termed "read-only". The difference between read-only memory and read/write memory is the level of difficulty in changing the stored information.

The ROM, being a fixed memory, is non-volatile: i.e., loss of power or system malfunction does not change the contents of memory. The ROMs have the feature of random access, which means that the access time for a given memory location is the same as that for all other locations.

As a result of the recent advances in IC technology, ROMs exist in many forms. The technique employed for storing information in the ROM (called programming) provides a convenient method for classifying all ROMs into one of the following three

# categories4.

- 1. Programmed during manufacture

- 2. One-time programmable after manufacture by the user

- Programmable after manufacture with provision for erasing and reprogramming.

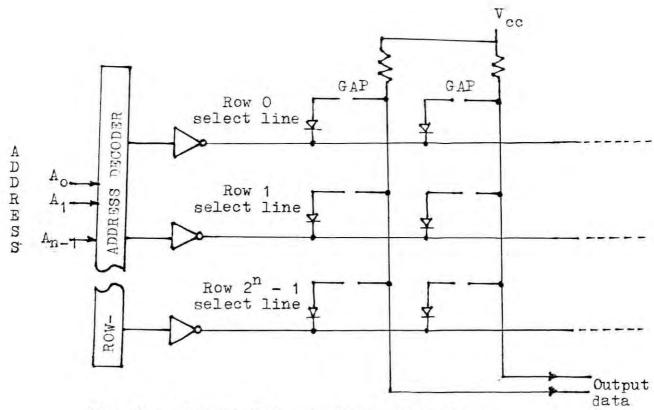

Provision for programming any of these three types commonly involves some sort of link, which may be opened or closed, between each row-select line and an input line of each OR gate. These units are then specified according to the information pattern that is to be programmed into the unit in a manner that depends upon the units type.

# 2.1.1 Manufacture-Programmed Read-Only Memory (ROM): Programming Characteristics.

ROMs are programmed usually as one of the final steps of their manufacture. The links are simply gaps that may be bridged by a final metalization pattern that is placed onto the circut according to the desired information to be programmed. This is done with a mask that determines the precise pattern, which is custom-made for a particular application. The mask is expensive to make but may be used to program any number of units. So this type of ROM is best suited for mass production.

An example of this first type of ROM unit using pn junction devices is shown in Fig.2.1. A diode is provided for each bit location in the unit. As can be seen a gap occurs in each path between a diode and the common line for a column. A value of "O"

Fig. 2.1 Circuit for a mask-programmed pn junction read-only memory unit.

is programmed into a particular bit position by bridging the corresponding gap, otherwise, the value of that bit is 1.

From the figure 2.1 it can be noticed that the common line of a column is normally pulled high by a resistor and that only the select line corresponding to the specified address can pull it low. If the gap to the diode connected to that select line is left open, then the common line remains high, corresponding to an output of "1". If the gap is closed on the otherhand, then the common line is pulled low by the select line, corresponding to an output of "0".

# 2.1.2 Programmable Read-Only Memory (PROM): Programming Characteristics

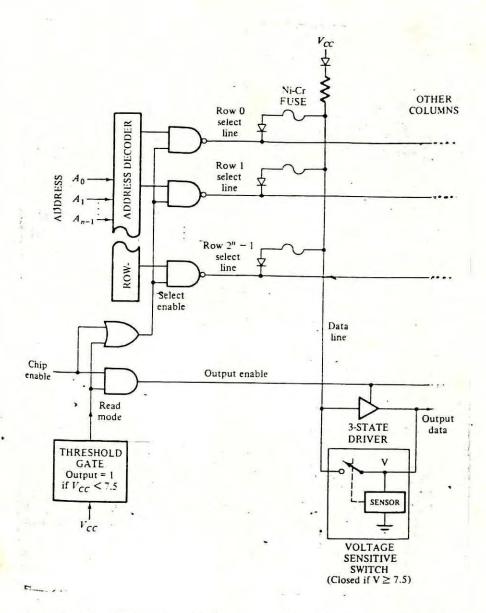

This type of ROM can be programmed one time by the user. It has generally a link that, after manufacture, can be altered one way, either from closed to open or vice verse. The most common way of doing this is to make the link from a fusible metal, such as NiCr, which can be selectively "blown" (i.e., open circuited) by supplying an external current of sufficient magnitude. An example of such a ROM unit is shown in Figure 2.2. The unit is similar to the previous example of a pn junction ROM unit, except that NiCr fuses are placed across the gaps and that there is provision for each of these fuses to be blown.

There are two modes of operation for this type of ROM:

- i. Read mode

- ii. Program mode

The mode at any time is determined by the value of the power-supply voltage  $V_{\rm cc}$ . For the read mode,  $V_{\rm cc}$  is placed at its normal value (e.g., 5 V); for the program mode,  $V_{\rm cc}$  is raised to higher voltage (e.g., 10 V). A threshold circuit is connected to  $V_{\rm cc}$  to generate the signal labled "Read Mode" which is logic-1 when the ROM unit is in the read mode of operation. This signal, Read Mode, is used in conjunction with an external signal, Chip Enable, to affect both the enabling of the row-select lines and the enabling of the output data lines.

Fig. 2.2 Circuit for a fusble-link programmable readonly memory unit.

Read mode: In this mode the row-select lines behave presisely the same way as in the preceding example of a pn junction ROM.

As can be seen in Fig. 2.2, NAND gates are inserted into the row-select lines. The second input line of each of these NAND gates, which is driven by the OR of Chip Enable and the signal Read Mode, will be at logic-1, since Read Mode is at logic-1. In this case the NAND gates simply invert the decoder outputs. The row-select line corresponding to the specified address is at logic-0, and all other row-select lines are at logic-1.

If the fuse is intact for a column and the selected row.

then the data line for that column is forced low (logic-0);

otherwise, the data line is pulled high (logic-1) by the pull-up

resistor. A 3-state driver is used to couple each column data

line to an overall output line labelled "Output Data". These

3-state drivers are controlled by a signal labeled "Output Enable",

which is the AND of Chip Enable and the signal Read Mode.

Program mode:- In this mode of operation, V<sub>cc</sub> is raised to a higher voltage (e.g., IOV). This affects the circuit in several ways. It causes the signal read mode to go to logic-O, which has two effects. First, the signal Select Enable is made to depend upon the external signal Chip Enable, thereby making the row-select line corresponding to the specified address to be logic-O only if Chip Enable is logic-1. Second, it causes the signal Output Enable to be logic-O, which disables the 3-state output drivers independent, of the value of Chip Enable. In addition

and most important, the row-select lines that do not correspond to the specified address are raised to higher voltage (e.g. 10V), since the gates that drive them use the power-supply voltage  $V_{\rm cc}$  to determine the logic-1 voltage level.

To cause a fuse to be blown, the desired address is specified, the Chip Enable line is then activated to enable the row-select lines, and then a specified current (approximately 50mA) is supplied from a current source to the appropriate Output Data line. This current passes through a voltage-sensitive switch to the data line of the corresponding column. The switch is a special circuit that closes when the voltage V applied by the current source exceeds a value somewhat higher than the maximum logic-1 level of 5V. The applied voltage will be sufficiently high if the specified current is made to flow. Once past the switch, the applied current flows through the fuse and diode that are connected to the row-select line that is low (logic-0). All other row-select lines are at approximately 10V and therefore draw an insignificant amount of applied current. After a short time the current causes the fuse to melt away. When a sufficient time has passed to allow for this, the Chip Enable line is deactivated. The process may then be repeated for other fuses that are to be blown in the same row and then for other rows. J

# 2.1.3 <u>Erasable Programmable Read-Only Memory (EPROM):</u> <u>Programming Characteristics.</u>

The third type of read-only memory unit, which can be programmed, erased, and reprogrammed, is refferred to as "erasable

programmable read-only memory" or in short EPROM. This type of unit generally makes use of a link that can be placed on one condition (say closed) on a selective basis and into the other condition (say open) on a collective basis. Programming such a unit consists of first placing all links collectively into a specific condition, which amounts to erasing any previous information content, and then placing desired links into the opposite state, one at a time.

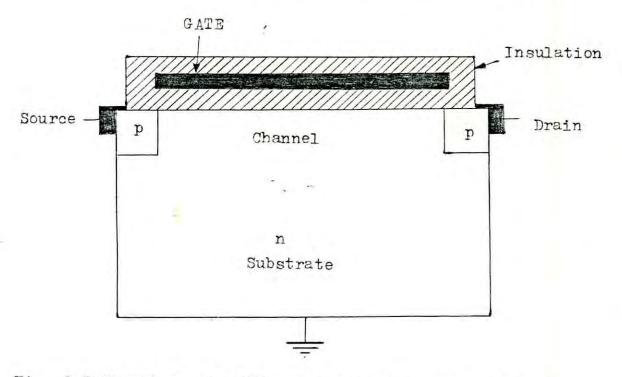

A notable example of a link that is used in EPROM units consists of a special type of MOS transistor having what is called a floating gate. A specific form of such a transistor is that of a p-channel normally-off (enhancement-mode) MOS transistor with its gate electrode surrounded by insulation, as shown is Fig.2.3.

The gate has no lead attached to it but may, however, be made to acquire a negative charge, as will be seen. When charged negatively, the gate induces a positive charge into the channel, just as it would if a negative potential with respect to the substrate were applied to the gate. With a positive charge in the channel the transistor is conductive. On the otherhand, if the gate has no regative charge, then no positive charge is induced into the channel and the transistor is not conductive.

Negative charge is supplied to the gate by injecting electrons from the drain through the insulation to the gate. This is done by applying a relatively high positive voltage to the source with respect to the drain.

The resulting electric field induces a relatively high positive voltage on the gate with respect to the drain.

Fig. 2.3 Floating-gate PMOS enhancement-mode transistor for EPROM units.

Roughly speaking, this voltage causes a breakdown to occur at the junction between the drain and the insulation, resulting in a flow of rather energetic electrons from the drain into the insulation. Owing to their energetic state, the electrons are able to drift through the insulation to the gate electrode. This electron charge on the gate will remain there almost indefinitely unless specifically removed. Charge is removed from the gate by irradiating the area with ultraviolet light, which imparts sufficient energy to each electron to bring it into a conductive energy band in the insulation. The electrons are then able to flow away from the gate owing to their mutual repulsion.

A read-only memory unit using these special transistors can be structured in a manner similar to the previous example of a MOSROM, which was shown in Fig. 2.1. In this case, each gap in the unit is bridged with one of these floating-gate transistors. In addition, circuitry is included that allows each floating-gate transistor to be selected for application of the necessary voltage to charge the gate. This selection process involves the address and output-data lines.

To program the resulting EPROM, all links are first opened (corresponding to logic-1) by irradiating the unit with ultraviolet light of sufficient intensity and duration. Then, for those bit positions that are to contain logic-0, the corresponding links are closed one at a time.

# 2.2 Erasure Characteristics of the EPROMs

The erasure characteristics of the Intel 27-series EPROMs and the EPROMs within the 8748 & 8048 micro-computer chips are such that erasure begins to occur when exposed to light with wave lengths shorter than approximately 4000 Angstrom (%). It should be noted that sunlight and certain types of fluorescent lamps have wavelengths in the 3000-4000 % range. Data show that constant exposure to room level fluorescent lighting could erase the typical EPROMs approximately in 3 years while it would take approximately one week to cause erasure when exposed to direct sunlight. If the EPROMs are to be exposed to these types of lighting conditions for extented periods of time, opaque labels

are available which should be placed over the chip window to prevent unintentional erasure.

The recommended erasure procedure for the EPROMs is exposure to shortwave ultraviolet lightwhich has a wavelength of 2537%. The integrated dose (i.e., UV intensity X exposure time) for erasure should be a minimum of 15 w-sec/cm². The erasure time with this dosage is approximately 15 to 20 minutes using an ultraviolet lamp with a 12,000 MV/cm² power rating. The chip should be placed within one inch of the lamp tubes during erasure. Some lamps have a filter on their tubes which should be removed before erasure<sup>5</sup>.

# CHAFTER - III

#### MICROCOMPUTER

#### 3.1 Basic Microcomputer Organization

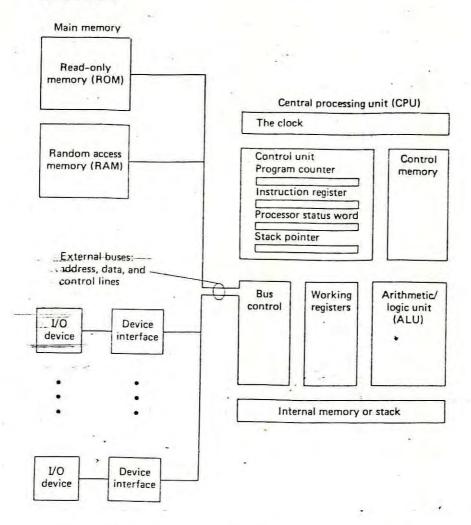

A microcomputer is a bus-oriented system of subassemblies that are implemented utilizing the technology of LSI. Functions of these subassemblies provide for manipulation of information, ordering the sequence of instruction execution, interpretation of instructions, control and timing of bus operation, storage of instructions and data, and communication between the computer and the external environment. The first four of these functions are frequently handled by a single subassembly known as a microprocessor. The storage function is handled by a memory subassembly. This subassembly may consists of ROM and/or RAM. The external communication is performed by a set of subassemblies known as input and output ports. Each port provides an interface between the microprocessor and some external device.

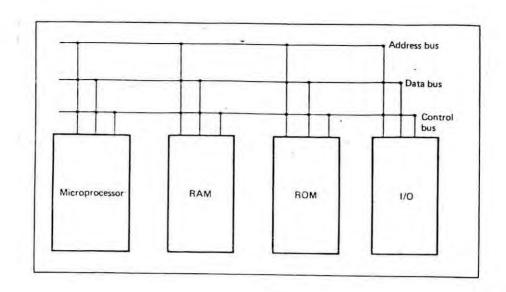

Figure 3.1 shows the general layout of a microcomputer and Fig.3.2 shows the basic blocks of an 8-bit microcomputer system. The various bases which connect these blocks are also shown. There are three buses:-

- 1. The address bus

- 2. The data bus

- 3. The control bus

These buses connect the microprocessor (CPU) to each of the ROM, RAM and I/O elements so that information transfer between the microprocessor and any of the other elements can take place.

Fig. 3.1 General layout of a microcomputer.

Note: The I/O device may be the Keyboard (Input), video display (Output), EPROM Programmer (Output).

Fig. 3.2 Block Diagram of a Typical Microcomputer

Address bus is used for transferring information from microprocessor to memory or I/O elements in one direction only. When the microprocessor wants to transfer information between itself and a certain memory location or I/O device, it generates the 16-bit address from an internal register on its 16 address pins  $A_O$  -  $A_{15}$ , which then appears on the address bus. These 16 address bits are then decoded to determine the desired memory location or I/O device. The decoding process normally requires hardware (decoder).

The data bus is a bidirectional bus. In 8085 microprocessor, the 8 data pins are used to sand lower 8 address bits in addition to data. That is the data pins are time-shared or multiplexed. When address bits are sent the address latch enable (ALE) pin becomes HIGH.

The control bus consists of a number of signals that are used to synchronize the operation of the individual micro-computer element. The microprocessor sands some of these signals to the other elements to indicate the type of operation being performed.

### 3.2 The Intel 8085 Microprocessor

The Microprocessor is the CPU of the microcomputer and is the combination of control unit and arithmatic and logic units. Therefore, the power of the microcomputer is determined by the capabilities of the microprocessor and its clock frequency determines the speed of the microcomputers. Microprocessor consists of logical components that enable it to function as a programmable logic processor. Some of the components, i.e., the program counter, stack and instruction register, provide for the management of a program. Other components, i.e., the ALU, Carry flip-flop, scratchpad register and data-address register provide for the manipulation of data. The remaining components, i.e., the decoder, timing and control unit specify and coordinate the operation of the other components. Internal pathways interconnect the components to provide for transferring data between designeated components. Connection of the microprocessor to other units (memory and I/O devices) is done with the address, data, and control buses.

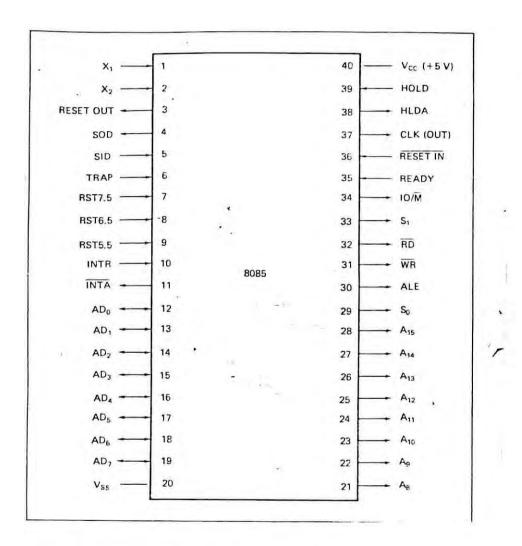

## 3.2.1 The 8085 Architecture and its Pin Function

Intel 8085 8-bit microprocessor is housed in a 40-pin dual-in-line (DIP) package. Fig. 3.3 shows the Intel 8085

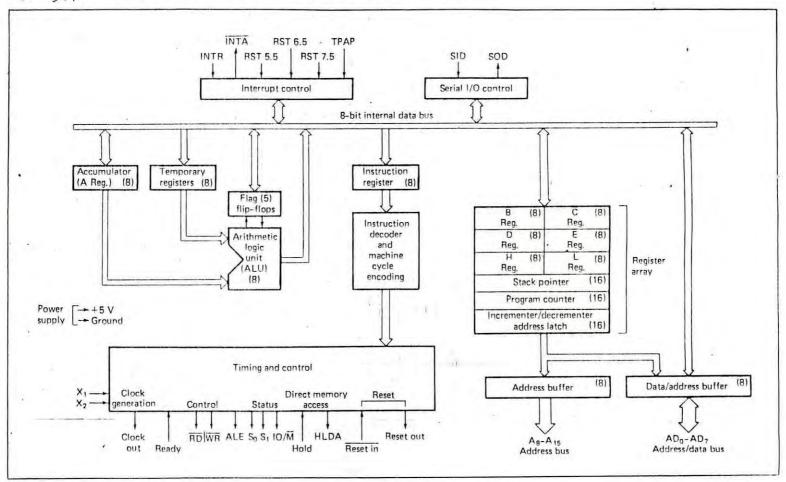

pin diagram and Fig. 3.4 shows the functional block diagram of the Intel 8085 microprocessor.

Fig. 3.3 Microprocessor signals and Pin Assignments

The internal organization or architecture of the Intel 8085 microprocessor is briefly discussed below.

It has a 16-bit program counter and address latch which

Figure 3.4 8085 Microprocessor Functional Block Diagram (Courtesy of Intel Corporation)

11

feed the dedicated address bus  $(A_{15} - A_8)$  and the dual purpose address/data bus  $(AD_7 - AD_0)$ . Parallel data enters and leaves the MPU via the multiplexed address/data bus  $(AD_7 - AD_0)$ . The address/data bus transmits an address when the ALE control line is HIGH and data when the ALE line is LOW.

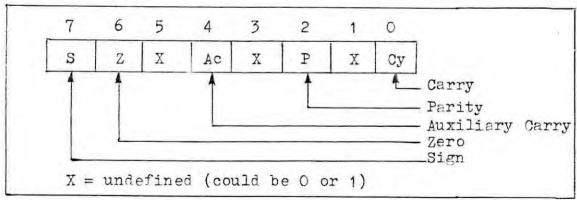

The 8-bit internal data bus carries input or output data throughout the unit. The data can flow from the internal data bus to the 8-bit accumulator or temporary register, flags, instruction register, interrupt control unit, serial I/O control unit, any of the general purpose registers (B,C,D,E,H and I), 16-bit stack pointer, 16-bit program counter, or 8-bit data/address buffer. The arithmetic-logic unit (ALU) is being fed by two 8-bit registers (accumulator and temporary register). The flag flip-flops have five status indicator as shown in Fig. 3.5. below.

Fig. 3.5 Format of Processor Status Word

The instruction register feeds the instruction decoder.

This instruction decoder interprets the current instruction and determines the microprogram to be followed or the machine

cycle encoding. The instruction decoder then instructs the timing and control section as to the sequence of events to be followed. The timing and control section coordinates actions of both processor and the peripheral.

The RD pin signal is outputted LOW during a memory or I/O READ operation. Similarly, the WR pin signal is outputted LOW during a memory or I/O WRITE. The IO/ $\overline{\rm M}$  signal is outputted high to indicate an I/O operation and is outputted low during a memory operation. The IO/ $\overline{\rm M}$ , S<sub>O</sub>, and S<sub>1</sub> are outputted during its internal operations as shown in Fig. 4.2. (Chapter-IV).

In the present project we have a microcomputer with the 16-bit address bus, 8-bit data bus, and with the necessary control signals (IORD, IOWR). The designed EPROM programmer is interfaced to these buses. The interfacing designs are described in the subsequent Chapters.

#### INTERPACING WITH PERIPHPRAT TWICE

In regard to microcomputer systems, interfacing can be separated into two areas of concern. One area involves the connection of the components, such as memory units and input/output registers, to the buses of a microprocessor. Such interfacing is primarily concerned with the timing and control of the buses and selection of a component so as to effect a data transfer at a given time between the selected component and the microprocessor.

The other area of concern involves interfacing components external to the microcomputer, such as peripheral devices, data channels etc. Such interfacing does not directly involve the buses of the microprocessor; so it is less structured. It is concerned with converting signals associated with the external components, which might be of any nature (including analog), to signals compatible with the buses and vice versa.

An input or output operation is the act of transferring data to or from a selected peripheral device. The microprocessor is the focus of all operation, so an input will mean data flows into the MPU whereas an cutput will mean data flows out of the MPU. Those locations where data is input from or output to are usually called input or output ports.

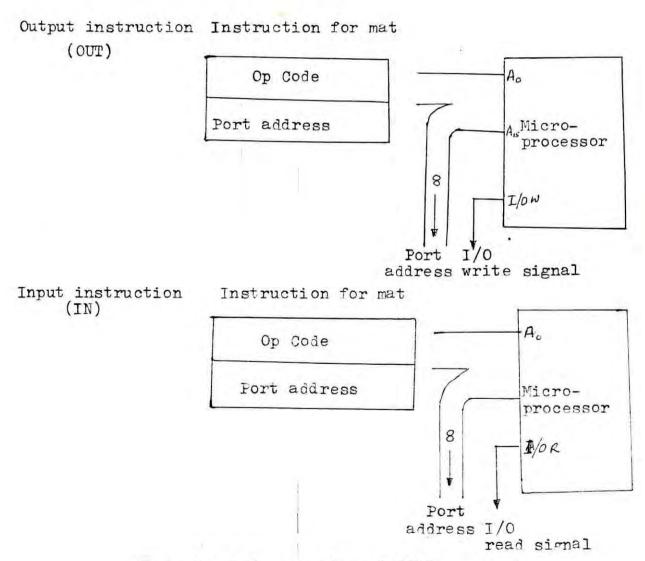

From the 8085 instruction sets, it appears that it uses the IN and OUT instructions for transferring data to and from I/O ports. These data transfer instructions are illustrated in Fig. 4.1. The output instruction is represented by OUT mnemonic

in assembly language program, while the input instruction uses the IN mnemonic. The instruction formats for these operations are also reproduced in the Fig. 4.1 showing the opcode followed by a device number or port address. The byte long port address can select one of 256 ( $2^8$ ) ports. Mostly the most significant 8 address lines ( $4_8$  -  $4_{15}$ ) are used for the port address.

Fig. 4.1 I/O operation of 8085

Fig. 4.1 also shows two additional output control signals added to the microprocessor. When using the OUT operation, a special input/output write  $(\overline{I/OW})$  signal is used. The IN operation also requires the use of a special output signal called input/output read  $(\overline{I/OR})$  signal. Both of these output signals are active LOW signals and are illustrated in Fig. 4.1. The status of the S<sub>o</sub>, S<sub>1</sub> and  $\overline{IO/M}$  pins during various read/write operations are shown in Fig. 4.2.

| 8085 control signals |    |    | Function              |

|----------------------|----|----|-----------------------|

| IO/M                 | 21 | 2° | rane of on            |

| 0                    | 0  | 1  | Memory write          |

| 0                    | 1  | 0  | Memory read           |

| 1                    | 0  | 1  | I/O write             |

| 1                    | 1  | 0  | I/O read              |

| 0                    | 1  | 1  | Op code fetch         |

| 1                    | 1  | 1  | Interrupt acknowledge |

Fig. 4.2 Control Signal table for I/O.

The data transfer using the IN and OUT instructions are classed as program-controlled I/O. Program instructions are controlling the transfer of data during IN and OUT operations. Program controlled I/O is divided into two techniques:

i. Standared I/O

ii. Memory Mapped I/O

The memory-mapped I/O technique is the most common and can be used with any microprocessor. The standard I/O techniques can be used only with microprocessors that have separate IN and OUT instructions as in the 8085 microprocessor.

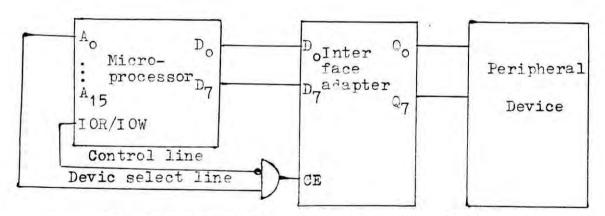

It is common to refer to an output as "an output to a peripheral device". In actual practice however, the output from the microprocessor is not directly to a peripheral device but to a memory device which stores the data for the peripheral unit. The intermediate blocks in Fig. 4.3 are the memory devices known as "input interface adapter" or "output interface adapter". It is common for I/O interface adaptor to have characteristics other than memory also.

Fig. 4.3 Connection with microprocessor of the peripheral

In the designed EPROM programmer, the peripheral is the EPROM to be programmed housed in the 40-pin socket. The address decoder together with the buffers and latches form the output interface adapter through which address, data and control singual pass to the EPROM. The buffers with the decoder form the 'input interface adapter' through which data to be read or verified is input to the microcomputer (Fig. Chapter-VI).

# CHAPTER - V PROGRAMMING CHARACTERISTICS OF INTEL EPROMS

# 5.1 Comparative Study of the Intel EPROMs

The EPROM Programmer can be used for programming the following type of EPROMs:-

- i. 16k (2k x 8) IV Erasable PROM: Intel 2716

- ii. 32k (4k x 8) UV Erasable PROM: Intel 2732

- iii. 64k (8k x 8) UV Erasable FROM: Intel 2764

- iv. 128k(16k x 8) UV Erasable PROM: Intel 27128

- v. 1k x 8 PROM within the Intel 8048H single component 8 bit microcomputer.

- vi. 1k x 8 PROM within the Intel 8748H sin-le-chip microcomputer.

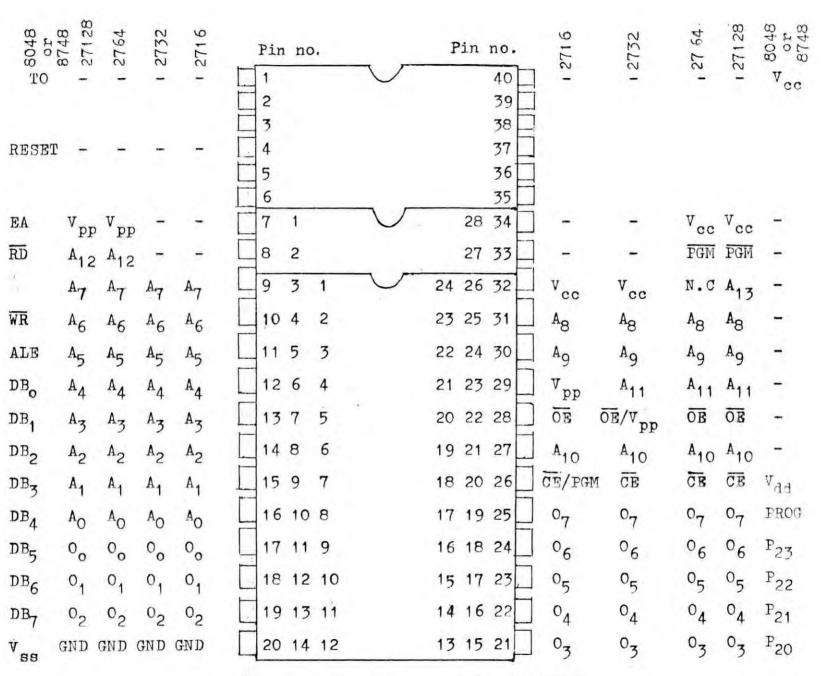

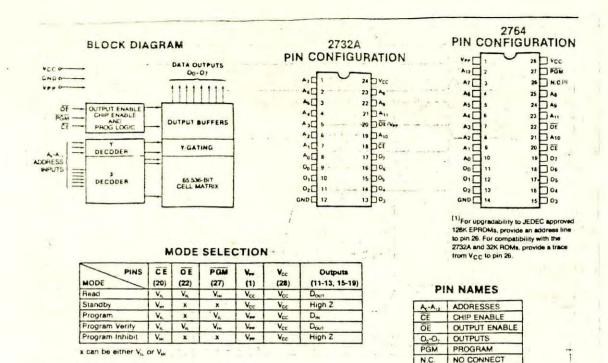

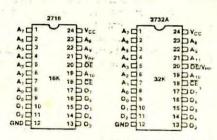

A comparative pin diagram of all the EPROMs is shown in Fig. 5.1. Individual pin diagrams, block diagrams and logic symbols of each of the above EPROMs are given in the appendix.

## 5.2 27-Series EPROM Operation

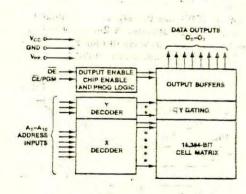

The EPROMs have the features of fast signle-address location programming and have, an access time from 250 ns to 650 ns and is ideal for use with the high-performance microprocessors. A block diagram is shown in Fig. 5.2 to represent the 27-series EPROMs.

The EPROMs have five modes of operation as listed in Table 5.1 the modes are briefly discussed below which will be helpful in the hardware design.

Fig. 5.1 Pin diagram of Intel EPROM

5.2.1 Read Mode: The 27-series EPROMs have two control functions, both of which must be satisfied in order to obtain data at the outputs. Chip Enable  $(\overline{CE})$  is the power control and should be used for device selection. Output Enable  $(\overline{OE})$  is the output control and should be used to gate data to the output pins, independent

Fig. 5.2 Block diagram of EPROMs.

of device selection.

5.2.2 Standby Mode:- The 27-series are placed in the standby mode by applying a TTL high signal to the  $\overline{\text{CE}}$  input. When in standby mode, the outputs are in a high impedance state, independent of  $\overline{\text{OE}}$  input.

TABLE 5.1 COMPARATIVE STUDY OF MODE SEFECTIONS FOR INTEL EPROMS

(28 pin configuration: EPROMs will be housed in the lower side of socket).

|                | Pins              | CE/PGM<br>(20)       | PGM (27) | OE/V               | V                  | Vcc               | Vcc  | V.nn             | Outputs         |  |

|----------------|-------------------|----------------------|----------|--------------------|--------------------|-------------------|------|------------------|-----------------|--|

| Mode           | Type of<br>EPROMs | (20)                 | (27)     | OE/V <sub>pp</sub> | (23)               | (24)              | (28) | V pp (1)         | 11-13,<br>15-19 |  |

|                | 2716              | VIL                  | -        | VIL                | +5                 | +5                | -    | -                |                 |  |

| READ           | 2732<br>2732A     | VIL                  | -        | VIL                | -                  | +5                | -    | <del>-</del>     | D               |  |

|                | 2764              | AlT                  | VIH      | VII                | -                  | -                 | +5   | +5               | Dout            |  |

|                | 27128             | VII                  | VIH      | VII                | *                  | o <del>le</del> n | +5   | +5               |                 |  |

|                | 2716              | AIH                  | -        | X                  | +5                 | +5                | -    | -                |                 |  |

| STAND-         | 2732<br>2732A     | AIH                  | -        | Х                  | -                  | +5                | -    | -                | High Z          |  |

| BY             | 2764              | ΔlH                  | X        | X                  | -                  | -                 | +5   | +5               |                 |  |

|                | 27128             | · A <sup>IH</sup>    | X        | X                  | -                  | -                 | +5   | +5               |                 |  |

|                | 2716              | Pulsed ${ m V_{IH}}$ | L -      | V <sub>IH</sub>    | +25                | +5                | -    | 7 <del>-</del> . |                 |  |

| PRO-<br>GRAM   | 2732<br>2732A     | VIH                  | -        | 25<br>21           | -                  | +5                | -    | -                | Din             |  |

| GILAN          | 2764              | V <sub>IL</sub>      | AIT      | AlH                | -                  | -                 | +5   | +21              | 1 111           |  |

|                | 27128             | v <sub>II</sub>      | VIIx     | VIH                | \ \ <del>-</del> \ |                   | +5   | +21              |                 |  |

| PRO-           | 2716              | V <sub>IL</sub>      | -        | VIL                | +25                | +5                | -    | -                |                 |  |

| GRAM<br>VERIFY | 2732<br>2732A     | $v_{\mathrm{IL}}$    | -        | v <sub>IL</sub>    | -                  | +5                | -    | -                | Dout            |  |

|                | 2764              | VIL                  | VIH      | VII                | -                  | -                 | #5-  | +21              |                 |  |

|                | 27128             | V <sub>IL</sub>      | VIH      | VIL                | -                  | -                 | +5-  | +21              |                 |  |

| PRO-           | 2716              | VIL                  | -        | VIL                | +25                | +5                | -    | -                |                 |  |

| GRAM<br>INHIB- | 2732<br>2732A     | v <sub>IH</sub>      |          | 25<br>21           | -                  | +5                | -    | -                | Hingh 2         |  |

| IT.            | 2764              | V <sub>IH</sub>      | X        | X                  | -                  | -                 | 5    | 21               |                 |  |

|                | 27128             | $v_{IH}$             | х        | X                  | -                  | -                 | 5    | 21               |                 |  |

### Contd. Table 5.1

- 1. X ---- don't care

- 2. Exceeding 22V on pin 1 ( $V_{pp}$ ) will damage the 2764 and 27128 while programming

- 3. In the program mode the 2732A OE/V<sub>pp</sub> input is pulsed from a TTL low level to 21V (25V for 2732). Exceeding 22V will damaged the 2732A.

- 4.  $V_{cc}$  must remain within 5  $\pm$  5% Volts.

- 5.  $V_{TL} = Input low voltage = 0.1V to 0.8V$

- 6. V<sub>TH</sub> = Input high voltage = 2V to 6V

- 7.  $V_{cc}$  must be applied simultaneously or before  $V_{pp}$  and removed simultaneously or after  $V_{pp}$ .

- 5.2.3 <u>Program Inhibit Mode:- Programming of multiple EPROMS</u> in parallel with different data is also accomplished. Except for  $\overline{\text{CE}}/\text{PGM}$  or  $\overline{\text{CE}}$  or  $\overline{\text{CE}}$  (or PGM)all like inputs (including  $\overline{\text{OE}}$ ) of the parallel 27 -EPROMS may be common. An active signal to the  $\overline{\text{CE}}$  pin of a particular EPROM will program that EPROM and others are inhibited from being programmed.

- 5.2.4 <u>Program Verify Mode:-</u> A verify should be performed on the programmed bits to determine that they were correctly programmed. The verify may be performed with  $V_{pp}$  at 25V (or 21V as the case may be). In case of 2716  $V_{pp}$  should be at 5V except during programming and program verify. In case of 2732, 2764 & 27128 the verify is accomplished with  $\overline{\text{OE}}$  &  $\overline{\text{CE}}$  at  $V_{TL}$  with PGM at  $V_{TH}$ .

- 5.2.5 <u>Programming Mode:-</u> Initially after each erasure, all bits of the EPROMs are in the "1" state. Data is introduced by selectively programming "0's" into the desired bit locations. Although "0's" will be programmed, both "1's" and "0's" may be present in the data word.

# a. Intel 2716 EPROM:

When the address and data are stable, a 50 msec, active-high, TTI program pulse is applied to the OE/PGM input.

### b. The 2732 EFROMs:

The 2732 & 2732A are in the programming mode when  $\overline{\text{OE}}/\text{V}_{\text{pp}}$  = 21V.

When the address and data are stable, a 50 msec, active-low, TTL program pulse is applied to the  $\overline{\text{CE}}$  input. The 2732A must not be programmed with a DC signal applied to the  $\overline{\text{CE}}$  input.

## c. The 2764 & 27128 EFROMs:

The 2764 & 27128 are in the programming mode when  $V_{\rm pp}$  = 21V

$\overline{\text{CE}} = \overline{\text{PGM}} = V_{T,T}$

For programming, CE should be kept TTI low at all times while  $V_{\rm pp}$  is kept at 21V. When address and data are stable, a 50 msec, active low, TTL program pulse is applied to  $\overline{\rm PGM}$  input.

For all the above EPROMs the data to be programmed is applied 8 bits in parallel to the data output pins. The levels required for the address and data inputs are all TTL. A program pulse must be applied at each address location to be programmed. Any location can be programmed at any time-either individually, sequentially or at random. The program pulse has a maximum width of 55 msec<sup>5</sup>.

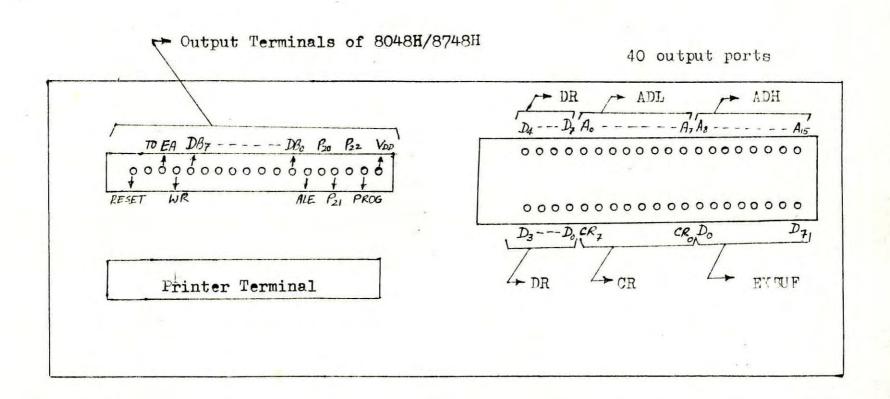

# 5.3 Programming of 8748H & 8048H EPROM

The programming process consists of:

- i. activating the program mode

- ii. applying an address

- iii. latching the address

- iv. applying data

- v. applying program pulse.

Each word is programmed completely before moving on to the next and is followed by a verification step. The following is a list of the pins used for programming and a description of their functions:

| Pins                             | Function                                          |

|----------------------------------|---------------------------------------------------|

| XTAL 1                           | Clock input 1 to 3 MHz                            |

| Reset                            | Initialization and address latching               |

| Test O                           | Selection of program or Verify mode               |

| EA                               | Activation of Program/Verify mode                 |

| BUS                              | Address and data input, data output during verify |

| P <sub>20</sub> -P <sub>22</sub> | Address input                                     |

| $v_{ m DD}$                      | Programming power supply                          |

| PROG                             | Program pulse input                               |

The program/verify sequence is:

- 1.  $V_{DD} = 5V$ , clock applied or internal oscillator operating  $R_{\text{p}} \overline{\text{Set}} = 0V$ , TEST 0 = 5V, EA = 5V, BUS and PROG floating,  $P_{10}$  and  $P_{11}$  must be tied to ground.

- 2. Insert 8748H in programming socket.

- 3. TEST 0= OV (select program mode).

- 4. EA = 18V (activate program mode)

- 5. Address applied to BUS and  $P_{20}$   $P_{22}$ .

- 6. RESET = 5V (latch address)

- 7. Data applied to BUS

- 8. V<sub>DD</sub> = 21V (programming power)

- 9. PROG = OV followed by one 50 msec pulse to 18V

- 10.  $V_{DD} = 5V$

- 11. TEST 0 = 5V (verify mode)

- 12. Read and verify data on BUS

- 13. TEST 0 = 0V

- 14. RESET= OV and repeat from step 5

- 15. Programmer should be at conditions of step 1 when the EPROMs are removed from socket.

### CHAPTER - VI

### HARDWARE DESIGN OF EPROM PROGRAMMER

### 6.1 Functional description of EPROM Programmer

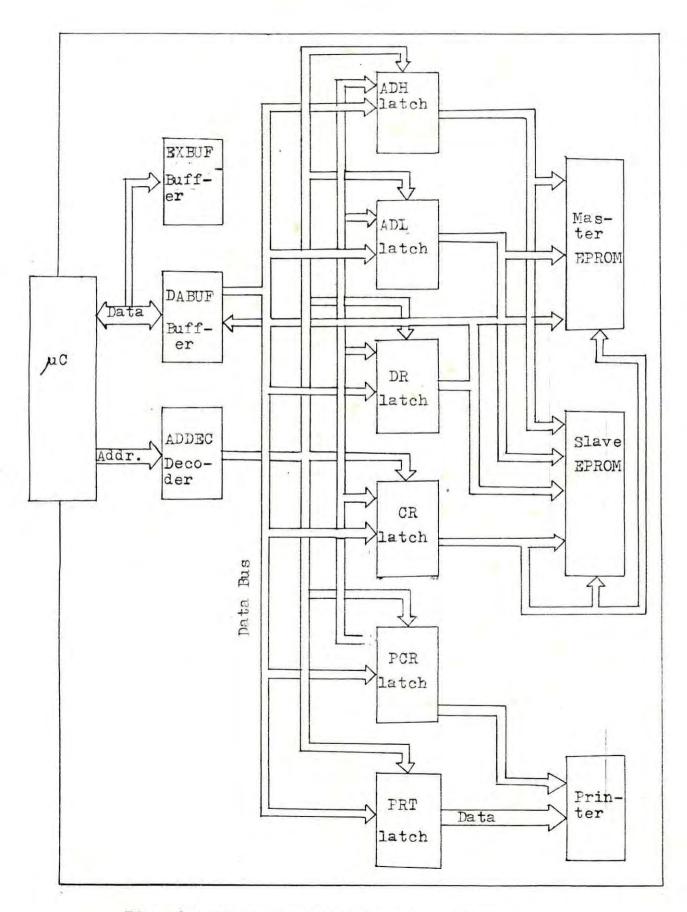

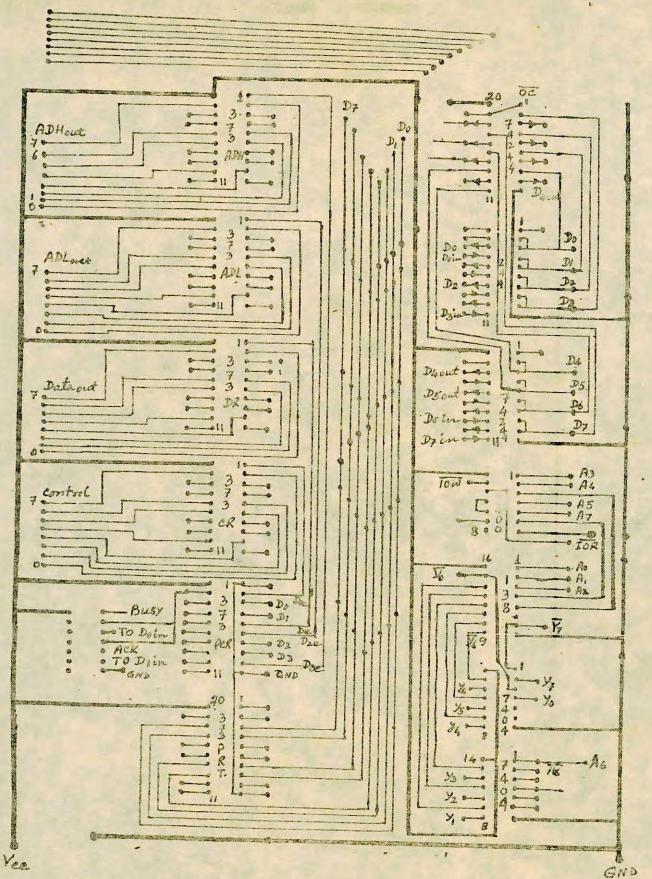

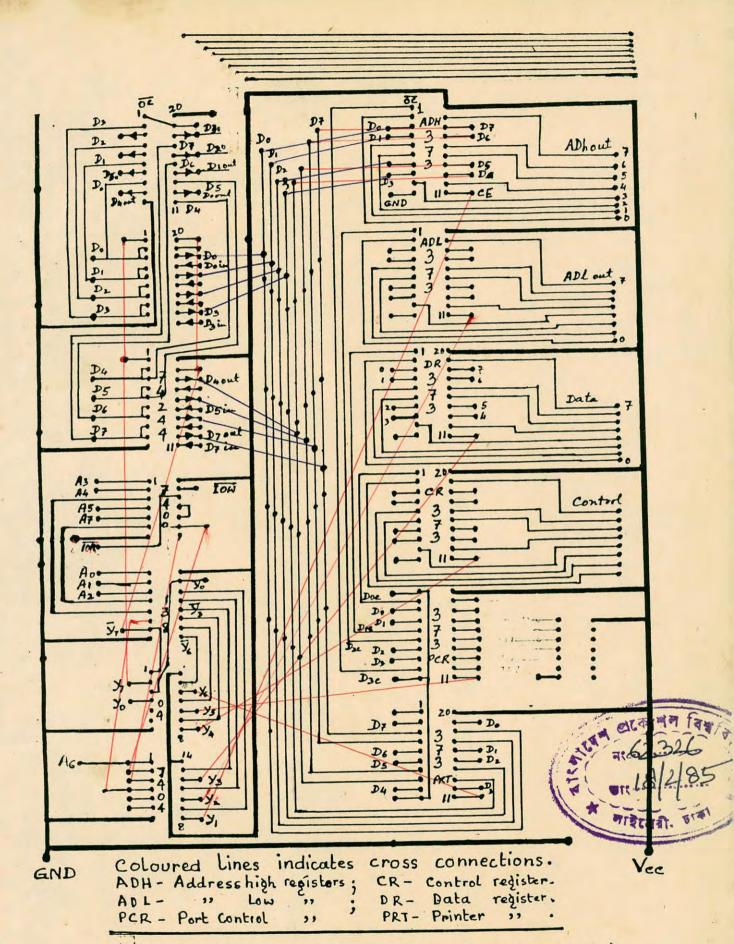

A simplified block diagram of the EPROM porgrammer is shown in Fig. 6.1 and consists of the following major blocks.

- a. The address decoder (ADDEC)

- b. The I/O data buffers (DABUF)

- c. The expansion buffer (EXBUF)

- d. The address latches

- i. Lower address latch (ADL)

- ii. Higher address latch (ADH)

- e. The data latch

- i. EPROM data latch (DR)

- ii. Frinter data latch (PRT)

- f. The control latches

- i. Port controlling latch (PCR)

- ii. EPROM controlling latch (CR)

The address decoder is used to select the address, data and control latches and the I/O buffers and the expansion buffer. The B8 to BF (Hexadecimal) address range is used by the address decoder for the selection purpose.

The I/O data Buffers are used for transferring data to and from the microcomputer. The expansion buffer is reserved for future expansion of the system.

Fig. 6.1 Block Diagram of EPROM Programmer

The control latches are used for sending various signals to the EPROMs for the mode selections and also for controlling the remaining latches. Control lines are program-controlled so that the Intel EPROM series (2716, 2732,2764, 27128 etc.) can be programmed.

The data latches are used to latch the data to be programmed and upon receiving output control  $(\overline{OC})$  signal they send the data to the desired location.

The address latches are used to latch the address of the location of the EPROM to be programmed and upon receiving the output control signal they put the address on the desired pins of the EPROM.

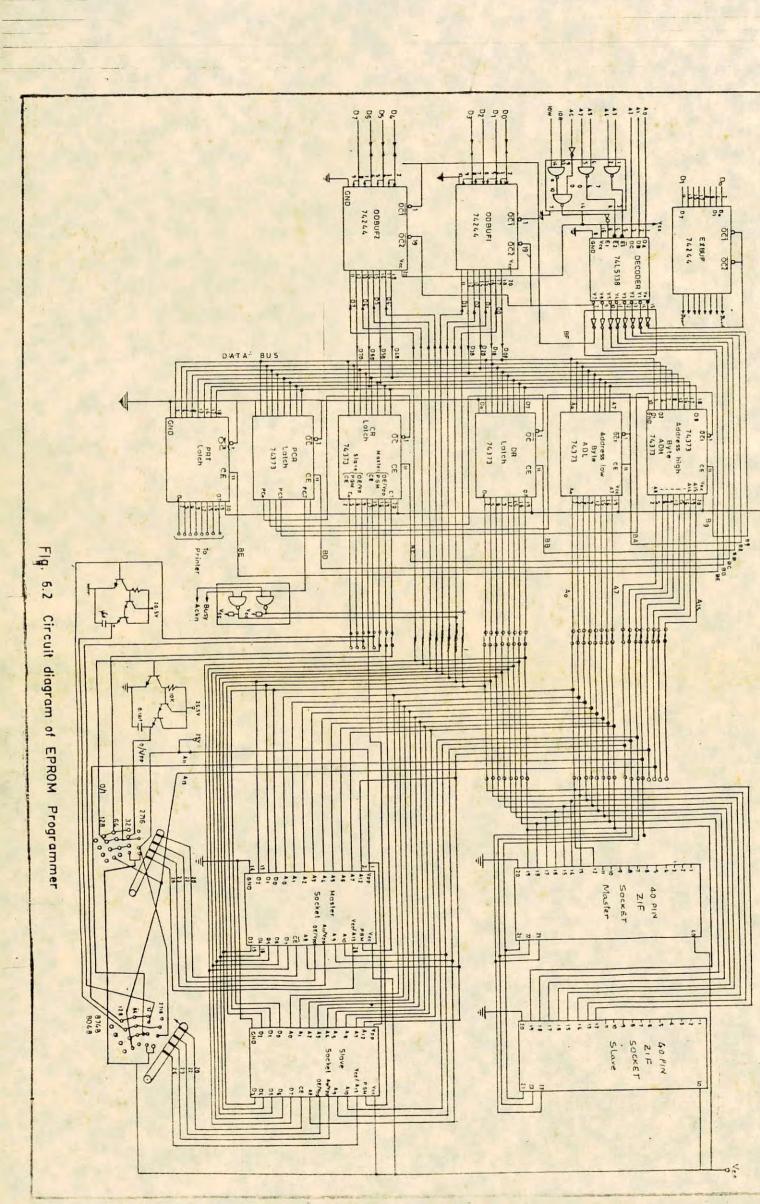

# 6.2 Detail Circuit Diagram of the EPROM Programmer

A detailed schematic diagram of the designed EPROM programmer is shown in Fig. 6.2. The description of each functional unit is given below.

# 6.2.1 The address decoder (ADDEC)

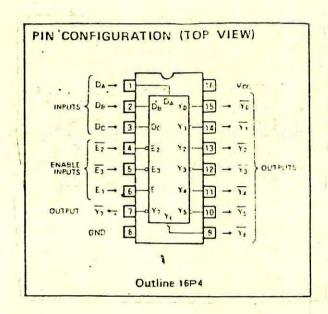

There are six latches and two sets of buffers in the designed programmer. Their address are to be B8 to BF. This is accomplished with the help of the 3-line to 8-line decoder (74LS138) IC Chip in conjunction with the 2-imput NAND gates. The pins  $D_A$ ,  $D_B$ ,  $D_C$  of the decoder are connected to the  $A_8$ ,  $A_9$  and  $A_{10}$  lines respectively of the address bus of the microcomputer.

The six outputs  $(\overline{Y}_1 \text{ to } \overline{Y}_6)$  bearing the address B9 to BE, of the decoder are connected to the chip Enable (CE) pin of the six latches, after being inverted by the 7404 inverter, as because the Chip Enable of the latches are active High. The addresses of all the latches and buffers are given in Table 6.1.

Table 6.1 Address of the Latches

| Sl.No. | Name of the latch/Buffer                 | Address designated (in hexadecimal) | CE/OC(Buffer<br>connec-<br>tion with<br>decoder pin |  |

|--------|------------------------------------------|-------------------------------------|-----------------------------------------------------|--|

| 1.     | I/O Data Buffer(DABUF1 & DABUF <b>2)</b> | B8                                  | Y <sub>0</sub> (Pin 15)                             |  |

| 2.     | Higher address latch(ADH)                | В9                                  | Y <sub>1</sub> (Pin 14)                             |  |

| 3.     | Lower address latch(ADL)                 | BA                                  | Y <sub>2</sub> (Pin 13)                             |  |

| 4.     | EPROM Data latch(DR)                     | BB                                  | Y <sub>3</sub> (Pin 12)                             |  |

| 5.     | EPROM controlling latch (CR)             | BC                                  | Y <sub>4</sub> (Pin 11)                             |  |

| 6.     | Port control latch(PCR)                  | BD                                  | Y <sub>5</sub> (Pin 10)                             |  |

| 7.     | Printer data latch(PRT)                  | BE                                  | Y <sub>6</sub> (Pin 9)                              |  |

| 8.     | Expansion Buffer(EXBUF)                  | BF                                  |                                                     |  |

If the CE pin of a particular latch is HIGH, the contents of the data bus will be latched in the register. The CE pin will be HIGH when the specified latch is addressed. This data will be outputted only when the output control  $(\overline{OC})$  pin is LOW. This  $\overline{OC}$  pin is controlled by the port control register (PCR).

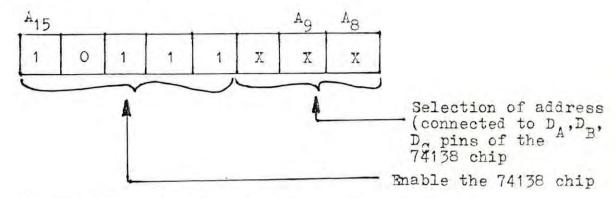

Using this decoder the following binary format of the high address bus (Fig. 6.3) may be used for address selection between B8 to BF.

Fig. 6.3 Addressing format of the address decoder.

The decoder should be enabled with the above address only during input/output operation i.e., when  $\overline{\text{IOR}} = 0$  or  $\overline{\text{IOW}} = 0$ .

The decoder for decoding the address has three enabling pins,  $\overline{\mathbb{E}}_3$ ,  $\overline{\mathbb{E}}_2$ , which are active low and  $\mathbb{E}_1$  which is active high. The decoder will output LOW at one of its 8 output pins depending on the value of  $\mathbb{D}_A$ ,  $\mathbb{D}_B$ ,  $\mathbb{D}_C$  inputs when all three pins  $\overline{\mathbb{E}}_3$ ,  $\overline{\mathbb{E}}_2$  and  $\mathbb{E}_1$  are activated.

The input to  $\overline{E}_3$  pin is from the output pin of a NAND gate whose inputs are  $A_{11}$  and  $A_{12}$  lines of the address bus and that to  $\overline{E}_2$  pin is from the output of another NAND gate whose inputs are  $A_{13}$  and  $A_{15}$  lines of the address bus. So  $\overline{E}_3$  and  $\overline{E}_2$  are selected only when  $A_{11} = 1$ ,  $A_{12} = 1$ ,  $A_{13} = 1$  and  $A_{15} = 1$ . Another logic circuit is necessary to select  $E_1$  such that  $E_1$  will be high only when  $A_6 = 0$  and IOR = 0/IOW = 0. Accordingly the input to  $E_1$  pin will come from a logic circuit which will follow the

its truth table and Karnangh map involving the don't care conditions as given in Fig. 6.4

| IOW | IOR | A <sub>14</sub> | Output E1 |

|-----|-----|-----------------|-----------|

| 0   | 0   | 0               | đ         |

| 0   | 0   | 1               | đ         |

| 0 . | 1   | 0               | 1         |

| 0   | 1   | 1               | 0         |

| 1   | 0   | 0               | 1         |

| 1   | 0   | 1               | 0         |

| 1   | 1   | 0               | 0         |

| 1   | 1   | 1               | 0         |

|                 | TOILLOW | TORION | TORIOW | TORIOW |

|-----------------|---------|--------|--------|--------|

| Ā <sub>14</sub> | d       | 1      |        | 1      |

| A <sub>14</sub> | đ       |        |        |        |

|                 | -       |        |        |        |

TORTOW TORTOW TORTOW TORTOW

Fig. 6.4(a) Truth table.

Fog. 6.4(b) Karnaugh map

The boolean function of the above truth table will be

$$E_{1} = \overline{A_{14}} \overline{10W} + \overline{A_{14}} \overline{10R}$$

$$= \overline{A_{14}} + \overline{10W} + \overline{10R}$$

$$= \overline{A_{14}} + \overline{10W} \cdot \overline{10R}$$

Fig. 6.5 Logic Circuit for the above truth table

Therefore the logic circuit becomes as shown in Fig. 6.5.

A<sub>14</sub>· IOW.IOR

# 6.2.2 I/O and Expansion Buffers (DABUF1, DABUF2, EXBUF)

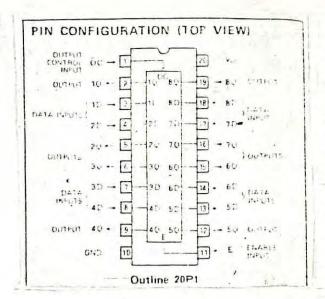

74LS244 buffers are used which has two control pins. Each control pin controls four bits of data. The  $\overline{\text{OC}1}$  controls four output bits and  $\overline{\text{OC}2}$  controls four input bits. Two buffers are used for handling eight outgoing and eight incoming bits. The two buffers DABUF1 and DABUF2 are used for transferring data to microcomputer received from the EPROM in case of reading and verifying the EPROM content and for receiving data from the microcomputer for onward transmission to different latches via the data bus. The address of these two bus buffers are B8. These buffers are designed to be always in the output mode by connecting the  $\overline{Y}_0$  output of the decoder after being inverted by the inverter to  $\overline{\text{OC}1}$  pins of the buffers. The output control pins  $\overline{\text{OC}1}$  and  $\overline{\text{OC}2}$  are active LOW.

For all OUT instructions (OUT B9 to OUT BF), the decoder ontput pin  $\overline{Y}_0$  (pin 15 of 74138) will be HIGH and after being inverted it will be LOW. Therefore these buffers will be always in the output mode and data will be outputted to the data bus from the microcomputer. The output pin  $\overline{Y}_0$  is directly connected to the output control  $\overline{OC2}$  pin of the buffers. So that when IN instruction to address B8 is executed only then the pin  $\overline{Y}_0$  is LOW and these buffers are in the input mode as  $\overline{OC2}$  is directly connected to  $\overline{Y}_0$  of decoder and data from the specified address of the EPROM will be inputted to the buffers and will be transmitted to the microprocessor. The output pin  $\overline{Y}_7$  is directly connected to the expansion buffer (EXBUF) and here 8-bit data can only be

outputted and cannot be inputted.

### 6.2.3 The Address High and Address Low Registers (ADL & ADH)

The address high latch (ADH) is used for latching the high byte address ( $A_8$ - $A_{15}$ ) and the latch ADL is used for latching low byte address ( $A_0$ - $A_7$ ) of the EPROM to be programmed. At first the high byte address of the location of the EPROM is loaded in the accumulator of the microprocessor. Then the content of the accumulator is transferred to the ADH latch using the instruction OUT B9. When OUT B9 instruction is used the  $\overline{\text{OC}1}$  pins of the two data buffers (DABUF1, DABUF2) LOW and the CE pin of the latch ADH is high and hence the content of the accumulator is transferred to the ADH latch and is latched there. In the same manner the LOW byte address of the location of the EPROM is latched in the ADL latch. Here the instruction transferring the low byte address is OUT BA. The  $\overline{\text{OC}}$  pin remains high so that output is 3-stated. The  $\overline{\text{OC}}$  pins of all the latches is controlled by the port control register (PCH) latch.

# 6.2.4 The Data latches (DR & PRT Latches)

The data to be transferred to the location specified by the content of the ADH and ADL latches is loaded in the accumulator and is transferred and latched in the Data register (DR)using the instruction OUT BB. Its output control  $(\overline{OC})$  pin also remains high. The output control  $\overline{OC}$  is activated by the second bit of the PCR latch.

In a similar way data is transferred to the latch PRT using the instruction OUT BE. It's  $\overline{OC}$  pin is grounded so that it is

of the latch PCR.

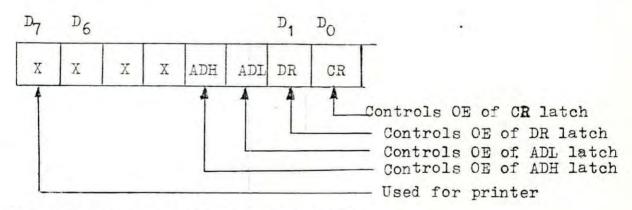

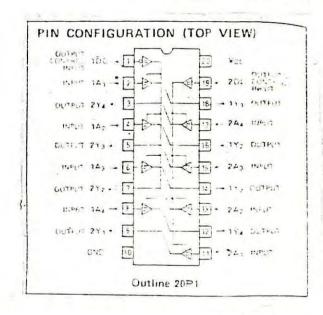

Port control latch (PCR) controls the output pin  $(\overline{OC})$  of the remaining latches. Control information is transferred to the PCR from accumulator using the instruction OUT BD. Output control pin  $(\overline{OC})$  is grounded so that whenever its chip enable (CE) pin is high, the content of the data bus is latched in the PCR and is outputted at the same time. The format of the Port control latch for output selection of the remaining latches are shown in Fig. 6.6.

Fig. 6.6 Format of Port control latch

When the output Q is Low, the corresponding latch outputs the latched data in it.

Table 6.2 Control Commands for Various Functions on the EPROMs

|                             | Type of             | Control Signal |          |                |          |          |                                     |          |          |     |

|-----------------------------|---------------------|----------------|----------|----------------|----------|----------|-------------------------------------|----------|----------|-----|

| Mode                        | EPROM               | Bit<br>7       | Bit<br>6 | Bit<br>5       | Bit<br>4 | Bit<br>3 |                                     | Bit<br>1 | Bit<br>O | Hex |

| READ<br>MASTER              | 2716<br>&<br>2732   | 1              | X        | 1              | 0        | Х        | 0                                   | Х        | X        |     |

|                             | 2764<br>&<br>27128  | 1              | X        | 1              | 0        | 1        | 0                                   | X        | X        |     |

| READ<br>SLAVE               | 2716 &<br>2732      | 0              | X        | 0              | 1        | X        | 1                                   | Х        | X        |     |

|                             | 2764 &<br>27128     | 0              | 1        | 0              | 1        | X        | 1                                   | X        | X        |     |

| PROGRAM<br>MASTER           | 2716                | 1              | X        | 1              | 1        |          | Pulsed<br>V <sub>IL</sub> to<br>VIH | X        | X        |     |

|                             | 2732                | 1              | X        | 1              | 0        | X        | 1                                   | X        | X        |     |

|                             | 2764<br>128         | 1              | 1        | 1              | 1        | 0        | 0                                   | X        | X        |     |

| PROGRAM<br>SLAVE            | 2716                | 1              | X F<br>V | ulsed<br>IL to | 1        | X        | , 1                                 | X        | Х        |     |

|                             | 2732                | 1              | X        | 1              | 1.       | 1        | 1                                   | X        | X        |     |

|                             | <b>2</b> 764<br>128 | 1              | 0        | 0              | 1        | 1        | 1                                   | X        | X        |     |

| PROGRAM.<br>V <b>B</b> RIFY | 2716                | 1              | X        | 1              | 0        | X        | 0                                   | X        | X        |     |

|                             | 2732                | 1              | X        | 1              | 0        | X        | 0                                   | X        | X        |     |

|                             | 2764<br>128         | 1              | X        | 1              | 0        | 1        | 0                                   | X        | Х        |     |

| PROGRAM                     | 2716                | 0              | X        | 0              | 1        | X        | 1                                   | X        | X        |     |

| VERIFY<br>SLAVE             | 2732                | 0              | X        | 0              | 1        | X        | 1                                   | X        | X        |     |

| mav n                       | 2764<br>128         | 0              | 1        | 0              | 1        | X        | 1                                   | X        | X        |     |

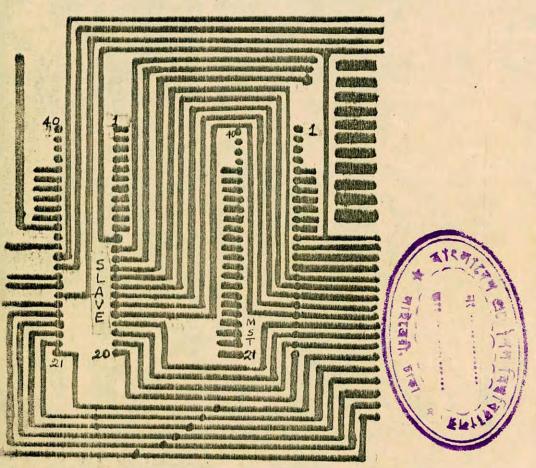

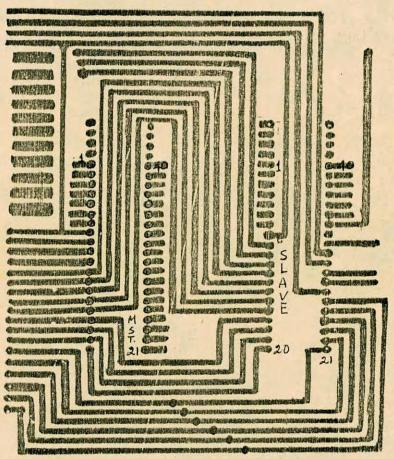

# 6.3 Connection of the EPROM Pins

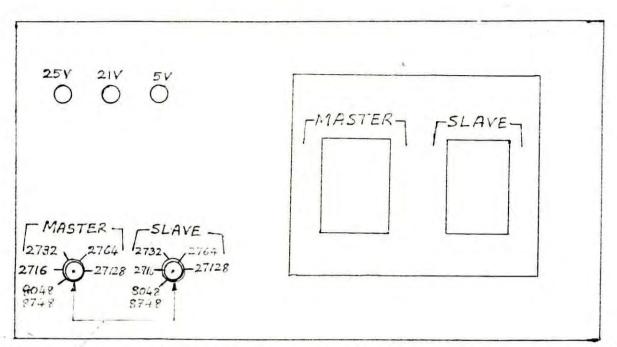

From a comparative study of the pin diagrams of all the EPROMS (Fig. 5.4) it can be seen that the 27-series EPROMS pin diagrams are almost similar. The difference in the pin connections are shown in Table 6.3. A MASTER IC socket (40 pin) and a SLAVE IC socket (40 pin) with zero insertion force (ZIF) are used for placing any of the EPROMS type during programming. The EPROMS are always placed at the bottom of the socket as shown in Fig. 5.1. Since the 8048H and 8748H microcomputer EPROMS differ significantly from the 27-series, a different connecter is used for programming but with the same ZIF socket. The two connecter connection can be seen from the detailed circuit diagram in Fig. 6.2.

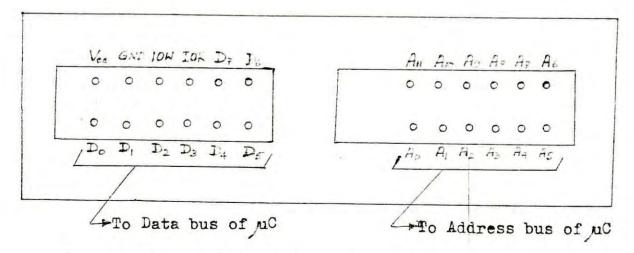

The address pins  $A_0$ - $A_7$  are connected to the 8 output pins  $D_0$ - $D_7$  of the ADL latch. The next three address pins  $A_8$ - $A_{10}$  and  $A_{12}$  are also connected permanently to the three lower output pins  $D_0$ - $D_2$  and  $D_4$  lines of the ADH latch. The  $A_{11}$  and  $A_{13}$  pins are connected to the  $D_3$  and  $D_5$  pins of the ADH latch via the selector switch because the connection of these pins are variable for diff. EPROMs.

The data pins  $D_0-D_7$  of EPROMs are connected to the output pins  $D_0-D_7$  of DR latch and also they are connected directly to the eight input pins of the buffers DABUFI & DABIUF2 so that the data can be inputted to the  $\mu$ C directly when needed. The data of either slave of Master EPROM will be inputted to the

Table 6.3 Difference in the Pin connections of different EPROM

| Pin No.<br>28-Pin Confi-<br>guration | Pin no.<br>24-Pin<br>configu-<br>ration | 2716              | 2732               | 2764             | 27128              | Comment                         |

|--------------------------------------|-----------------------------------------|-------------------|--------------------|------------------|--------------------|---------------------------------|

| 1                                    | -                                       | -                 | 1000               | v <sub>pp</sub>  | V <sub>pp</sub> }  | May be connected permanently to |

| 2                                    | -                                       |                   | <del>-</del>       | A12              | A <sub>12</sub>    | socket                          |

| 3-19                                 | 1 - 17                                  | $(A_0 - A_7)$ and | $(0_0 - 0_2)$ and  | GND and (03      | - 0 <sub>5</sub> ) | Same for all EPROMs             |

| 20                                   | 18                                      | CE/PGM            | CE                 | CE               | CE }               |                                 |

| 22                                   | 20                                      | OE                | OE/V <sub>pp</sub> | OE               | OE {               | Variable on type                |

| 23                                   | 21                                      | V <sub>pp</sub>   | A <sub>11</sub>    | A <sub>1 1</sub> | A 1 1              | of EPROM So a switch is to      |

| 26                                   | 24                                      | Vcc               | V <sub>ee</sub>    | n.c              | A <sub>13</sub>    | be used                         |

| 27                                   | 1.4.                                    | -                 | -                  | PGM              | PGM )              | May be connected                |

| 28                                   | -                                       | 4                 | -                  | v <sub>cc</sub>  | v <sub>cc</sub>    | permanently to socket.          |

microcomputer via the buffers depending on whose  $\overline{\texttt{OE}}$  enable is activated. The programming voltage is supplied to the programming pins in case of programming an EFROM at either Master or Slave location from an outside source of 25V or 21V as the case may be. Since the +25V V<sub>pp</sub> required by the EPROM must be off except when programming or verifying, the switch is designed to be in the off state when the processor is turned on. A high on the switch input turns it off.

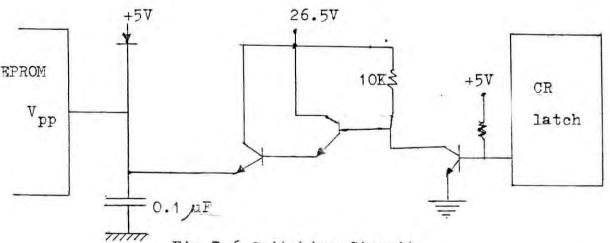

With the switch off, the diode to +5V turns on and supplies the  $V_{\rm pp}$  (for 2716) pin with the voltage required for normal read operation. This input is controlled by the CR register output. When the switch to 25V is on, the diode is reverse biased. The switching circuit is shown in Fig. 6.7.

Fig. 7.6 Switching Circuit

Due to voltage drop across transistor a higher voltage than 25V(or 21V) must be used as the switch supply. A 0.1  $\mu\text{F}$  capacitor on the  $V_{\text{pp}}$  pin helps prevent overshoot which might destory the EPROM during switching.

### CHAPTER - VII

### SOFTWARE DEVELOPMENT

### 7.1 Functions of the Programmer

The following operation will be performed by the microprocessor-based programmer.

- 1. Loading the data to be programmed from a selected input device (Tape, EPROM etc.) into the micro-computer memory.

- 2. Programming a segment of a PROM with the data which are stored begining at a specified address in the microcomputer memory.

- 3. Displaying the contents of a segment of a PROM at the Master or Slave location or of the main memory on the monitor screen.

- 4. Moving a block of data from one memory location to another memory location.

- 5. Transferring a block of data in a PROM into the microcomputer memory so that the contents of the PROM may be verified or examined through the system and may also be used to duplicate a PROM.

- 6. Transferring a block of data from a PROM to the printer to make a hardcopy of the content.

- 7. Comparing a block of data in a PROM with the contents of a segment of memory (Program Verification).

- 8. Verifying a segment of a PROM to see whether the segment is erased.

- 9. Printing the contents of a segment of memory.

Hardware has been designed so that data to be programmed into the EPROM can come from another ROM/EPROM or from RAM via CPU.

# 7.2 Program Development for the Programmer

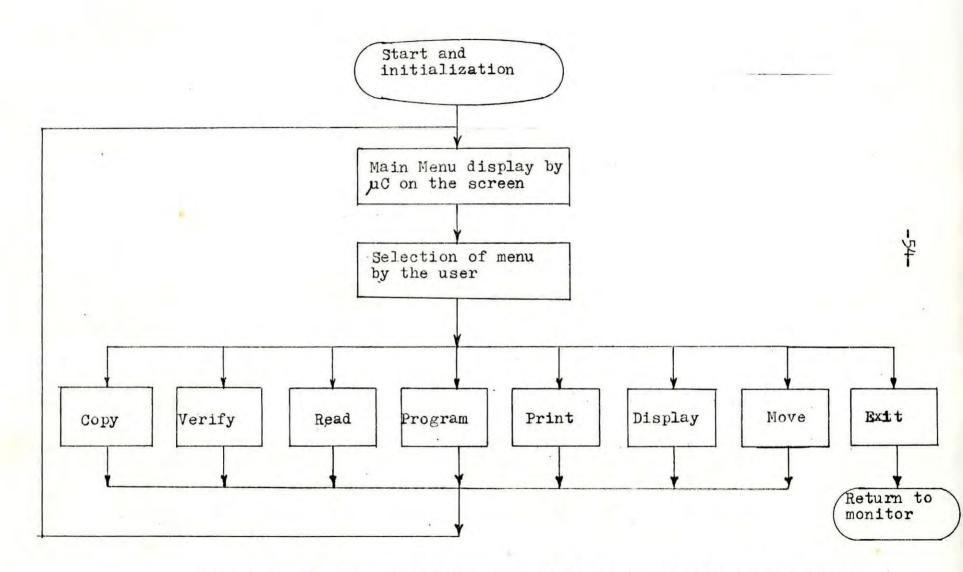

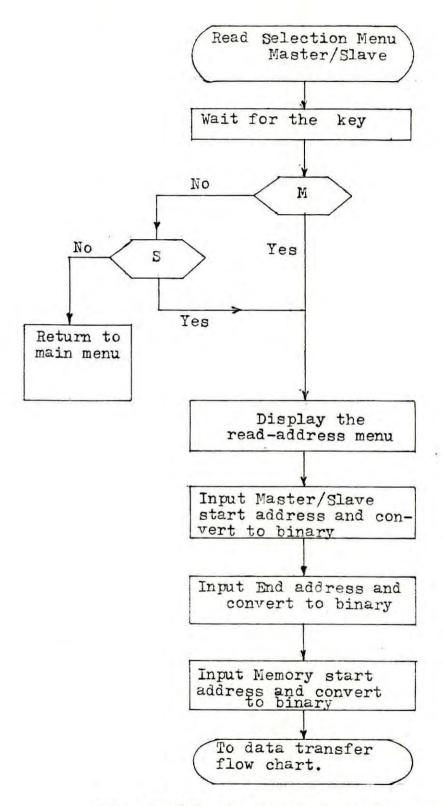

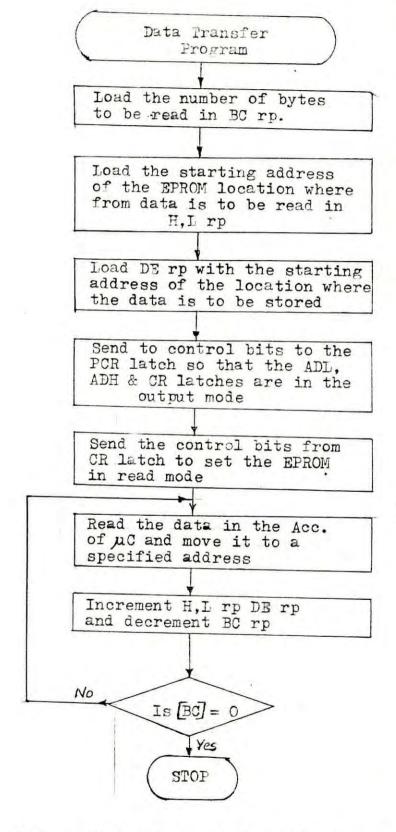

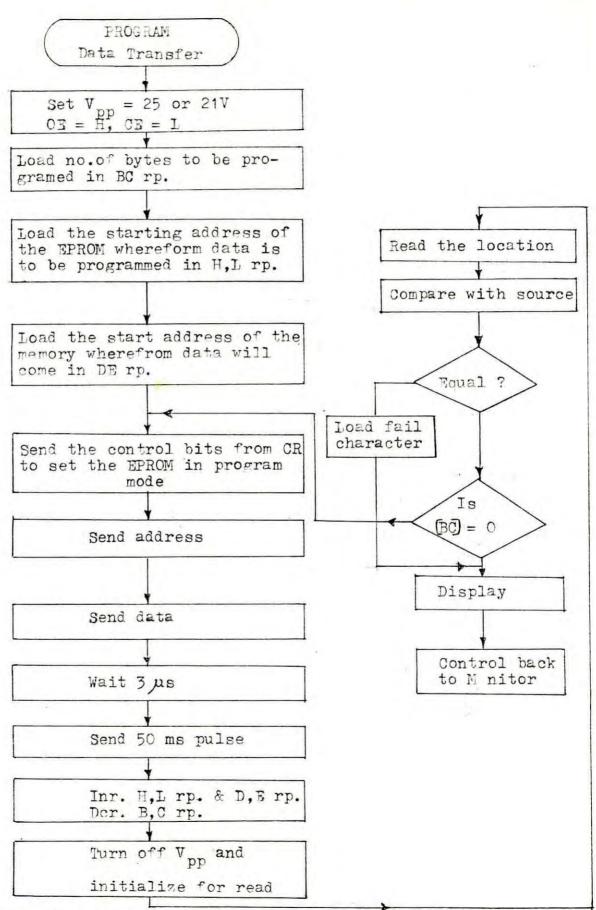

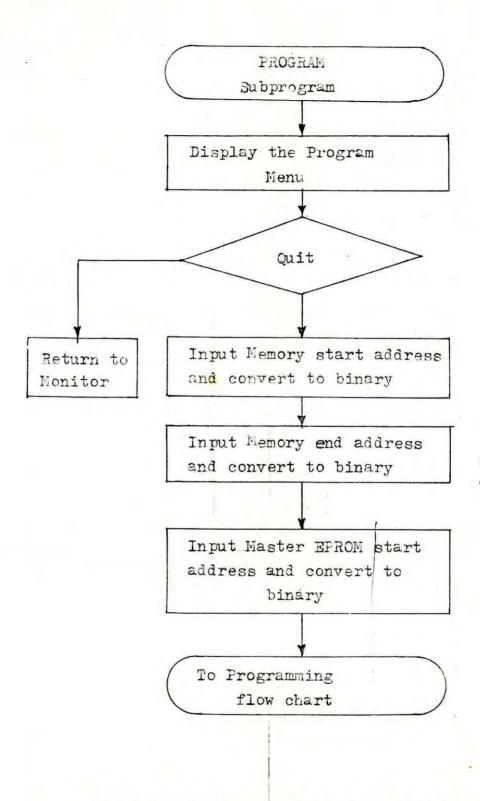

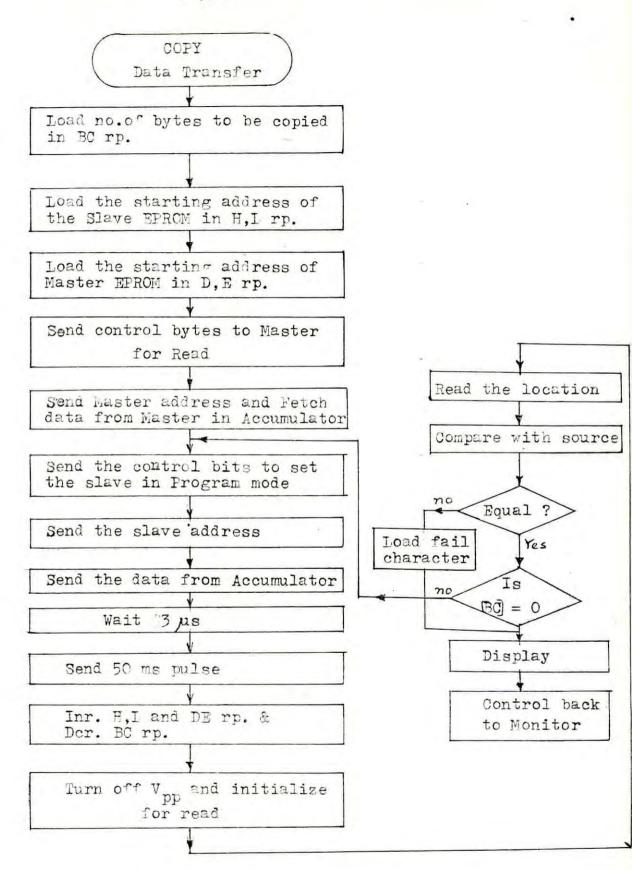

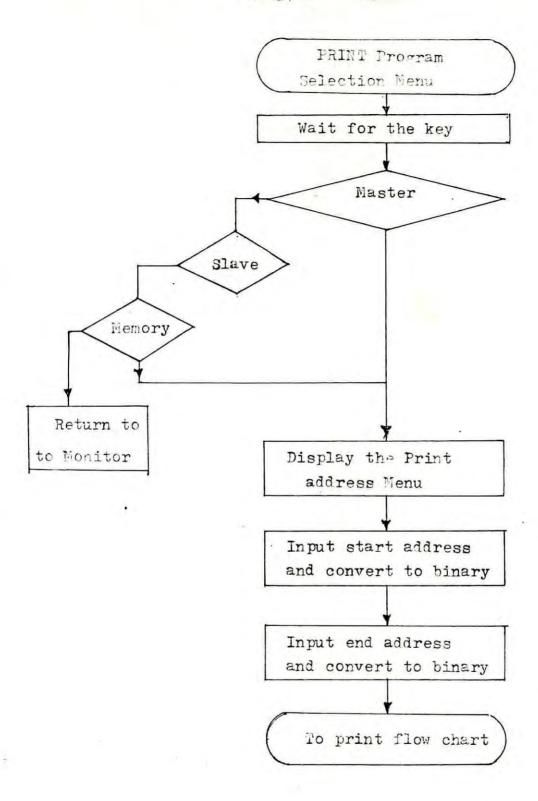

Flow diagram of the program to perform the functions described above is shown in Fig. 7.1. To perform the operations as shown in the flow diagram seven subprograms are used. These subprograms are called by the main program (Main Menu) as desired by the user. The names and functions of subprograms are as follows:

- i. READ: Used to read the contents of an EPROM at Master location or at slave location and store it to a desired memory location.

- ii. MOVE: Used for moving a block of data from a certain memory location to another location.

- iii. DISPLAY: Used to display the contents of an EPROM at Master location or at Slave location.

Fig. 7.1 Flow diagram of the program to perform different functions.

- iv. VERIFY: Used to verify if any desired segment of the EPROM at Slave or at Master location erased.

- v. COPY: Used for copying an EPROM in Slave location from an EPROM at Master location.

- vi. PROGRAM: Used for programming any segment of the EPROM at Master location from the main memory.

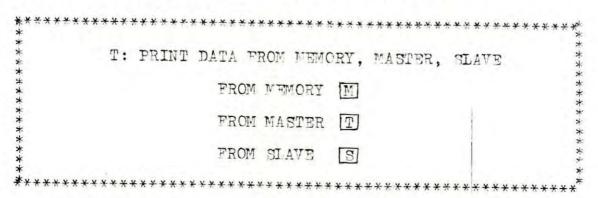

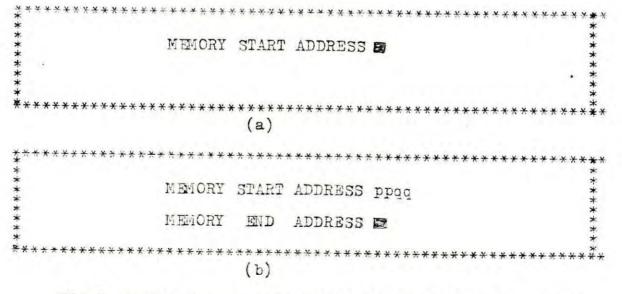

- vii. PRINT: Used for printing the data from the main memory or from EPROM at Master or Slave location.

The different variable names used in these subprograms are given in Table 7.1.

When the program is executed main Menu will be shown on the monitor screen of the system. The format of the main Menu as will be shown on the screen is shown in Fig.7.2. There are seven choices of operations to be performed as shown in the figure and for each choice there is a corresponding key to be pressed on the key board. After pressing a particular key the corresponding operation format for the corresponding function will be displayed on the screen. Now the different operations will be discussed in the following sections.

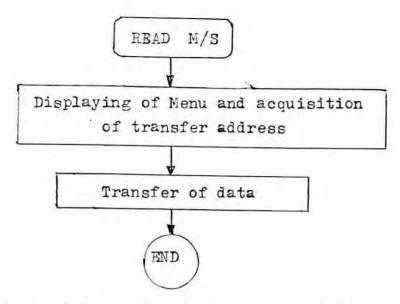

# 7.2.1 READ Subprogram

Read subprogram is used to read the contents of an EPROM at Slave or Master location and store it to a desired memory location. After the main Menu is displayed if the

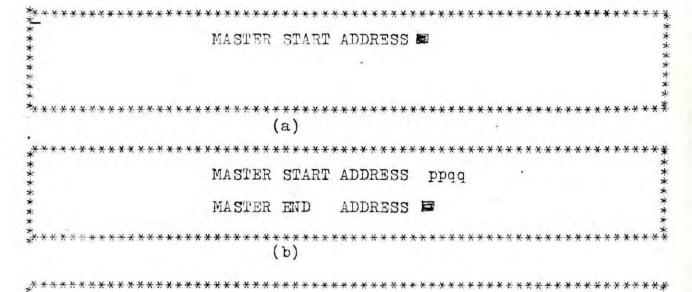

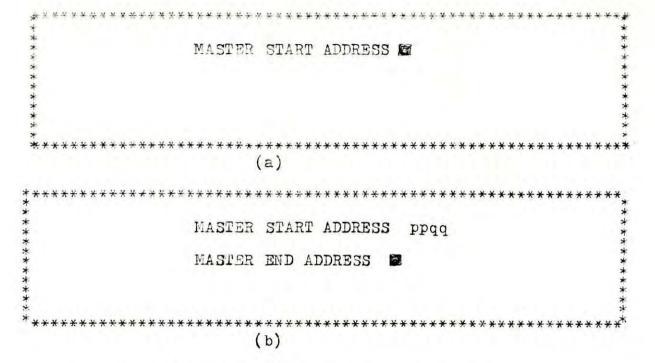

Once the source EPRCM is selected, the microcomputer waits for the start and end address of the EPROM and also for the destination address in the memory of the microcomputer starting from which data block from the EPROM will be stored. Each of the address will be entered by the user from the key board interactively The interaction of the user and the computer for transferring data from the Master EPROM is shown in Fig. 7.4(a), (b), (c). As each line of the prompt is displayed the corresponding address is to be entered with carriage return at the end. Next line appears only after the previous line is entered. The typed address can be corrected using the cursor movement.

MASTER START ADDRESS ppqq

MASTER END ADDRESS mmnn

TO MEMORY START ADDRESS

(c)

Fig. 7.4 Interactive displays of Master EPROM for READ operation.

An overall flow chart of the Read program is shown in Fig. 7.5(a).

Fig. 7.5 (a) Overall Flow Chart for READ Program

The detailed flow chart of read display menu. is shown in Fig. 7.5(b) and that of the actual data reading is given in Fig. 7.5(c). The detail program is given in the appendix.

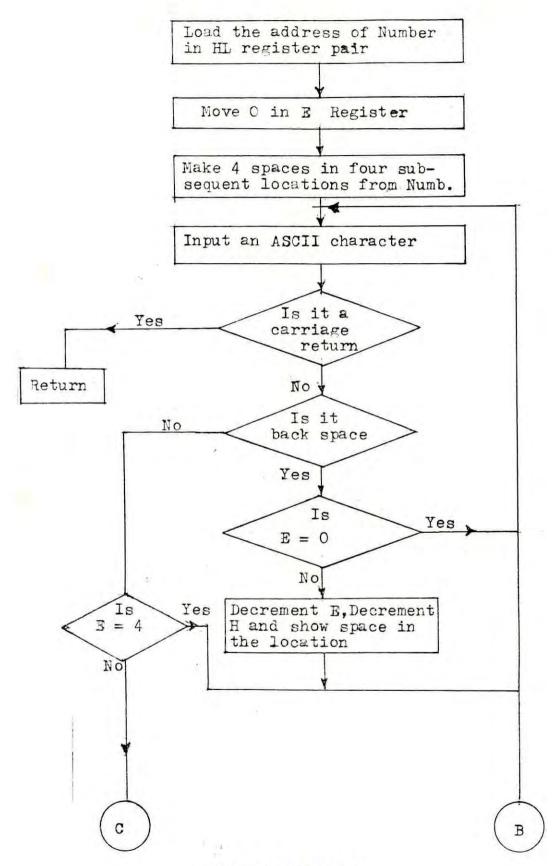

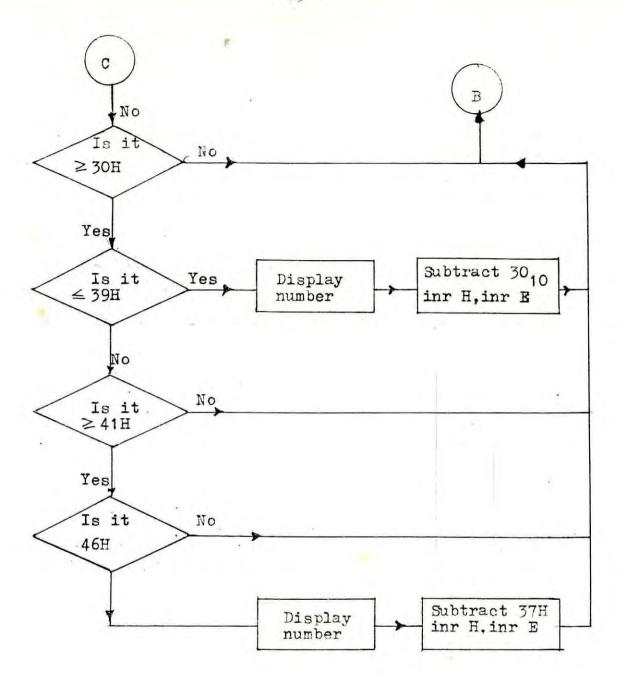

# 7.2.2 Conversion of an ASCII-coded hexadecimal number to its binary equivalent

Data to be read from Master from a certain address, to be programmed in Slave from certain address etc. are entered by punching the number on the key board manually. This number is to be stored in the specified address. A chart for the specified address and thier functions are given in the Table 7.2.

When a key containing a number is pressed its ASCII code is loaded in the accumulator. This ASCII code should be converted

Fig. 7.5(b) Display of Read Menu and acquisition of address flow chart.

READ an EFROM at Master/Slave location

Fig. 7.5(c) Flow chart for Data Transfer for READ operation.

to the corresponding number and then stored in the specified memory location. One byte should be stored in one memory location.

It can be seen from the Table that ASCII Code for the number 0 through 9 are 30 Hex to 39 Hex and A through F are 41 Hex through 46 Hex. So to convert 30H through 39H to number 0 through 9, 30H is to be subtracted or four high bits are to be cleared, and to make 41H to 46H to Hex number A through F, 37<sub>16</sub> is to be subtracted.

The flow chart for ASCII-code to binary conversion routine required for each entry of the address is shown in Fig. 7.6.

Fig.7.6 (Contd.)

Fig. 7.6 Flow chart for ASCII to binary conversion

### 7.2.3 MOVE Subprogram

It is used for transferring a block of data from a certain memory location to another memory location. After the main Menu is displayed on the screen, if the key M is pressed, the screen will display the MOVE Menu as shown in Fig. 7.7(a)

### M : MOVE DATA FROM MEMORY TO MEMORY

MEMORY START ADDRESS

Fig. 7.7(a)

The cursor will be at the position shown. The starting address will have to be entered manually. After entering the address if carriage return key is pressed the format shown in Fig. 7.7(b) will be displayed with the cursor shown at the position. Ending address will have to be entered manually.

# M : MOVE DATA FROM MEMORY TO MEMORY

MEMORY START ADDRESS ppgg

UNTIL E

Fig. 7.7(b) Interactive Displays of Move Menu

\*\*\*\*\*\*\*\*\*\*\*\*\*\*\*

The CR key will have to be pressed to get the next instruction and the farmat shown in Fig. 7.7(c) will be displayed. The memory starting address wherefrom the data is to be stored will have to be entered manually.

M : MOVE DATA FROM MEMORY TO MEMORY

MEMORY START ADDRESS ppag

\*\*\*\*\*\*\*\*\*\*\*\*\*\*\*\*\*\*\*\*\*\*<del>\*</del>

\*\*\*\*\*\*\*\*\*\*\*

UNTIL mmnn

TO MEMORY START ADDRESS

Fig. 7.7(c) Interactive Displays of Move Menu

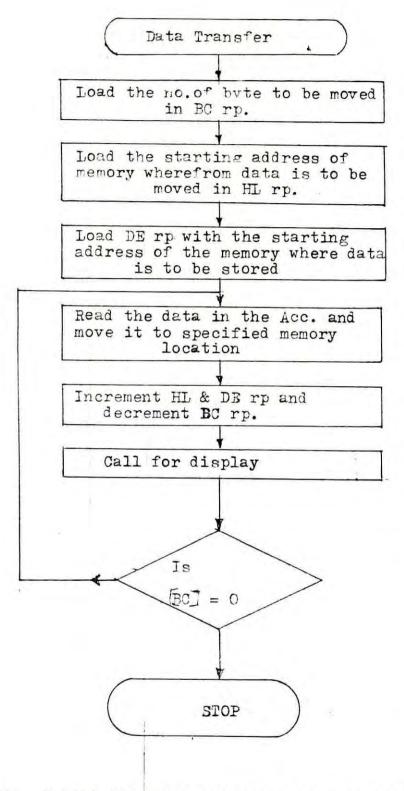

The flow chart consists of mainly two parts:

- i. Dispalying of the operating format and entering the starting and ending addresses.

- ii. Transferring the data from one location to another location.

The flow charts are shown in Fig. 7.8(a) and 7.8(b).

# 7.2.4 DISPLAY Subprogram

It is used to display the contents of an EPROM at Master location or at Slave location. In this operation the data is to be fetched from the EPROM at Master or slave location and is to be displayed on the screen instead of storing in the memory with the difference that in DISPLAY routine the contents are displayed instead of being stored and in READ operation the data are stored in memory.

The operation and flow chart are similar to the READ subprogram excepting that instead of moving the fetched data to the memory location it is displayed.

Fig. 7.8(a) Flow chart for MOVE Menu display and address entry.

Fig. 7.8(b) Flow Chart for Transfer of Data from Memory to Memory.

#### 7.2.5 VERIFY Subprogram

\*\*\*\*\*\*\*

It is used to verify whether any segment of an EPROM at Master or Slave location is erased. Here data is to be fetched from the EPROM and read and displayed on the screen to see whether EPROM is erased. After the main menu (Selection menu) is displayed on the screen, if the key V is pressed, verify Menu will be displayed as shown in Fig. 7.9(a).

\*\*\*\*\*\*\*\*\*

V. VERIFY MASTER/SLAVE EPROM ERASED

SELECT EPROM

MASTER [M]

SLAVE S

After the verify menu is displayed, if M is pressed the EPROM at Master location will be verified and if S is pressed the EPROM at slave location will be verified.

As in the case of READ, once the source EPROM is selected the microcomputer waits for the start and end address of the block of EPROM to be verified.

The figures that will be displayed after pressing the M key is shown in Fig. 7.10(a) and (b). Each of the addresses will have to be entered by the user from the key board interactively. Only four figures can be entered and may be corrected by shifting the cursor. Next line will be displayed only after the previous

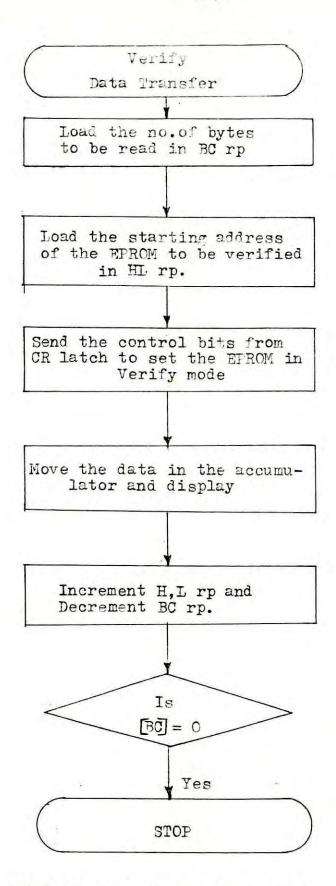

Fig. 7.11(a) Flow chart for displaying menu and acquisition of addresses for VERIFY.

Fig. 7.11(b) Flow Chart for Transferring data for VERIFY.

Fig. 7.10 Interactive Displays of Verify Menu

line is entered with carriage return at the end.

The detailed flow chart for displaying and address entering is shown in Fig. 7.11(a) and that of data transfer is shown in Fig. 7.11(b).

#### 7.2.6 PROGRAM Subprogram