## Development of an On-chip Current Mode Synchronous Step-up Converter without External Compensating Network and Slope Compensation.

A thesis submitted to the Department of Electrical and Electronic Engineering (EEE) of

Bangladesh University of Engineering and Technology (BUET) in partial fulfillment of the requirement for the degree of MASTER OF SCIENCE IN ELECTRICAL AND ELECTRONIC ENGINEERING

by

Mohiuddin Md. Hafiz

DEPARTMENT OF ELECTRICAL AND ELECTRONIC ENGINEERING (EEE) BANGLADESH UNIVERSITY OF ENGINEERING AND TECHNOLOGY (BUET) 2007

The thesis titled "Development of an On-chip Current Mode Synchronous Stepup Converter without external Compensating Network and Slope Compensation" submitted by Mohiuddin Mohammad Hafiz, Roll No.: 040406244P, Session: April 2004 has been accepted as satisfactory in partial fulfillment of the requirement for the degree of MASTER OF SCIENCE IN ELECTRICAL AND ELECTRONIC ENGINEERING on May 26, 2007.

## **BOARD OF EXAMINERS**

1.

Dr. A.B.M Harun Ur-Rashid Professor Department of Electrical and Electronic Engineering BUET, Dhaka---1000, Bangladesh. Chairman (Supervisor)

2. Head

Department of Electrical and Electronic Engineering BUET, Dhaka—1000, Bangladesh.

3.

Member

Member

(Ex-Officio)

Dr. Mohammad Ali Choudhur, Professor Department of Electrical and Electronic Engineering BUET, Dhaka—1000, Bangladesh.

4.

Dr. Md. Ashraful Hoque Professor Department of Electrical and Electronic Engineering IUT, Gazipur, Bangladesh. Member (External)

## DECLARATION

I hereby declare that this thesis or any part of it has not been submitted elsewhere for the award of any degree or diploma.

Signature of candidate

M. 26.05.07.

(Mohiuddin Md. Hafiz)

## DEDICATION

## To My Parents

## Acknowledgement

I would like to express my profound and sincere gratitude to my supervisor Dr. A.B.M Harun Ur-Rashid, Professor Department of Electrical and Electronic Engineering (EEE), Bangladesh University of Engineering and Technology (BUET), Dhaka, Bangladesh, whose patient guidance and encouraging attitude have motivated me much to have this thesis materialized.

I like to thank the present Head and Professor of the Department of Electrical and Electronic Engineering, BUET, Dr. Satya Prasad Majumder for providing me the lab facilities.

I would also like to express my wholehearted gratitude to Didar Islam, my employer, inventor of 'Qwik-Radio', and also holding 4 US patents, for his bold and dynamic decision to allow me to develop the system level design of the whole new idea of a chip, which is compatible to meet the industrial purposes and which outwits its presently existing competitors to a large extent. The aforementioned new idea is the core concept of this thesis.

I also take this opportunity to thank my colleagues specially Syed Jaffrey Al Kadry, Syed Mustafa Khelat Bari and Tanwir Zubayer Islam, for their constructive views and discussions about the development of this new system.

I am also grateful to all the members of my family especially to my father and mother for their cooperation and to my wife, Tania, for her unconditional support to accomplish this work.

Finally I am grateful to the Almighty for giving me the strength and courage to complete this thesis.

v

~?) {{}

## Abstract

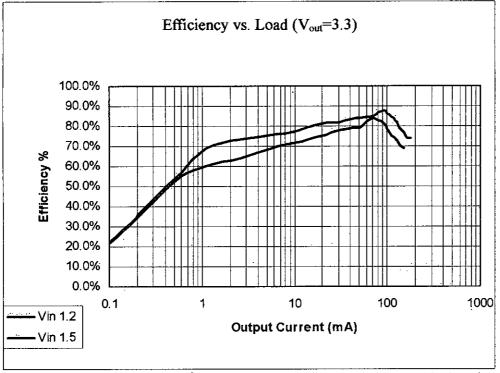

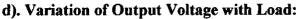

A monolithic current mode CMOS DC-DC converter with new control topology and integrated power switches has been developed in this thesis. A unified modulator model is also established for the topology, following the steps, used for deriving familiar models. System and circuit level implementation of the converter have been accomplished for the converter. Afterwards, this converter has been fabricated with a standard 0.5 µm CMOS process. The remarkable features of the converter are complete discharge of the output voltage, pulse-by-pulse current limiting, pulse-skipping mode in light load operation etc. Modulator gain Fm has been found to be a finite quantity and is independent of duty cycle, which reveals the fact that the control loop's stability is independent of compensating signal. In addition, no external components except the inductor and output capacitor and no extra I/O pins are needed for the current mode controller. The simulation and test data are in good agreement. The experiment results show that this converter operates around 1MHz with the supply voltage from 0.8V to 5V, which is suitable for single cell lithium-ion applications. The power efficiency is over 80% for load current from 50mA to 100mA, load regulation 1.6%, for the load variation 0-100mA.

## Contents

|    | Declaration                                    |                                                         | iii |  |

|----|------------------------------------------------|---------------------------------------------------------|-----|--|

|    | Ded                                            | ication                                                 | iv  |  |

|    | Acknowledgement<br>Abstract<br>List of Figures |                                                         | v   |  |

|    |                                                |                                                         | vi  |  |

|    |                                                |                                                         | ix  |  |

|    | List                                           | of Symbols                                              | xii |  |

| 1. | Intr                                           | oduction                                                | 1   |  |

|    | 1.1                                            | Background                                              | 1   |  |

|    | 1.2                                            | Compensation Issue                                      | 2   |  |

|    | 1.3                                            | The Recent Research Trend                               | 3   |  |

|    | 1.4                                            | Review of the Existing Compensation Techniques.         | 4   |  |

|    | 1.5                                            | Objective of This Thesis.                               | 4   |  |

| 2. | Cur                                            | rent Mode Converters in Brief                           | 5   |  |

|    | 2.1                                            | Synchronous Converter in Brief                          | 5   |  |

|    | 2.2                                            | Basic Idea about the Current Mode Converter.            | 5   |  |

|    | 2.3                                            | Deficiencies in Current Mode Control Mechanism & Their  | 8   |  |

|    |                                                | Remedies.                                               |     |  |

|    | 2.4                                            | Control Topologies & Conduction Modes.                  | 12  |  |

|    | 2.5                                            | PWM Switch Model in CCM.                                | 14  |  |

| 3. | The                                            | Proposed Converter                                      | 17  |  |

|    | 3.1                                            | The Architecture of the Proposed Converter              | 17  |  |

|    | 3.2                                            | The Basic Operation Principle.                          | 18  |  |

|    | 3.3                                            | The Topological Impact on the Current Loop Oscillation. | 20  |  |

|    | 3.4                                            | The Modulator Model.                                    | 22  |  |

|    | 3.5                                            | Other Necessary Information                             | 26  |  |

$\langle$

| 4. Implementation of the Proposed Converter |                                                 |      |

|---------------------------------------------|-------------------------------------------------|------|

| 4.1                                         | Supply Related Blocks                           | 27   |

| 4.2                                         | Loop Settling Blocks                            | 36   |

| 4.3                                         | Switches                                        | 48   |

| 4.4                                         | Performance Enhancement & Safety Related Blocks | 51   |

| 4.5                                         | Start-up Blocks                                 | 61   |

| 4.6                                         | The Main Control Block                          | 62   |

| 5. Sim                                      | ulation and Results                             | 65   |

| 5.1                                         | Necessary Files and Tools                       | 65   |

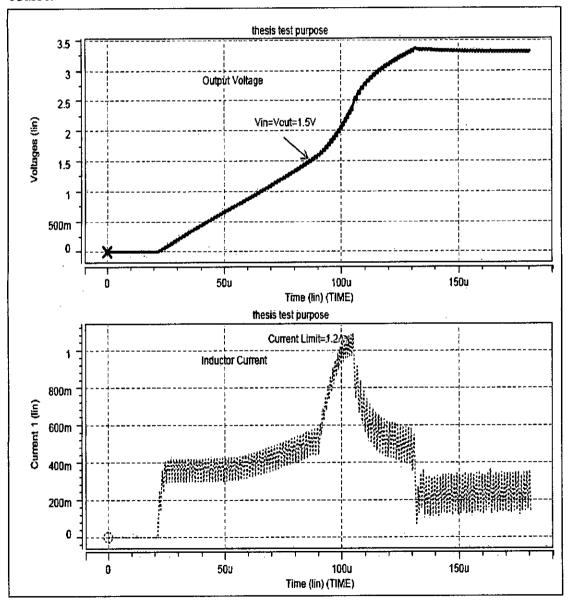

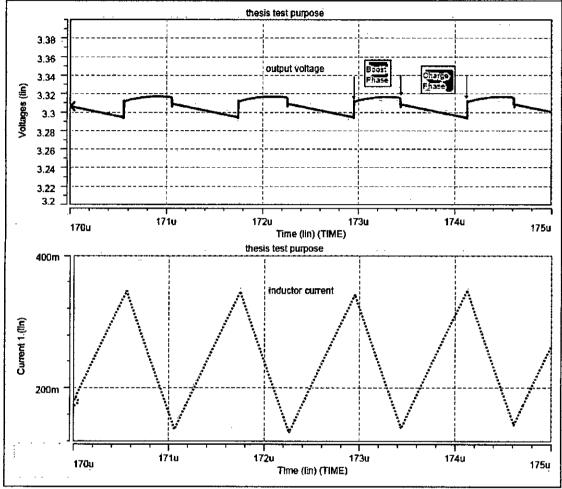

| 5.2                                         | The Start-up Mode                               | . 66 |

| 5.3                                         | The Normal Operating Mode                       | 68   |

| 5.4                                         | Current Limit and Short Circuit Protection      | 68   |

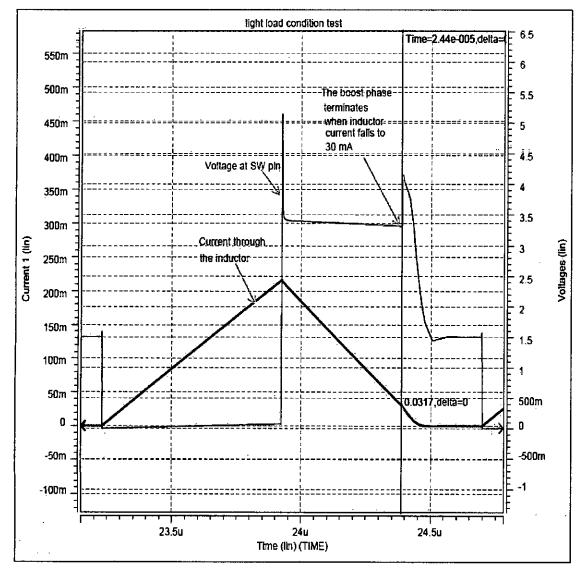

| 5.5                                         | The Light Load Operation                        | 69   |

| 5.6                                         | Output Voltage Selection                        | 70   |

| 5.7                                         | Under Voltage Lockout Condition                 | 70   |

| 5.8                                         | True Shutdown Mode                              | 70   |

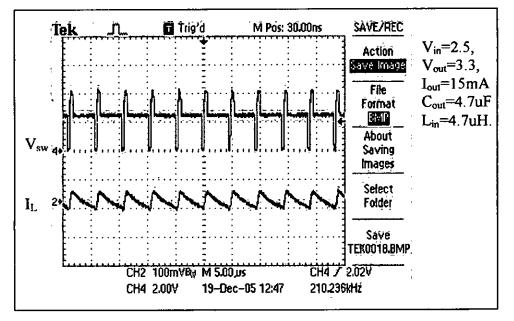

| 6. Mea                                      | asured Data & Real Time Waves                   | 71   |

| 6.1                                         | Measured Data                                   | 71   |

| 6.2                                         | Real Time Waves                                 | 75   |

| 7. Cor                                      | nclusion & Future Work                          | 81   |

| 7.1                                         | Overview of the Whole Thesis                    | 81   |

| 7.2                                         | Future Work on Model Related Issues             | 81   |

| 7.3                                         | Future Work on Implementation Related Issues    | 82   |

## Reference

.

2

..

# **List of Figures**

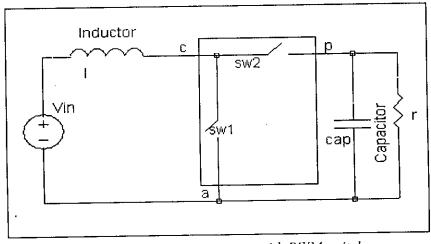

| Fig 2.1: Synchronous boost regulator with modulator                             | 6  |

|---------------------------------------------------------------------------------|----|

| Fig 2.2: Voltage mode control mechanism                                         | 7  |

| Fig 2.3: Current mode control mechanism                                         | 7  |

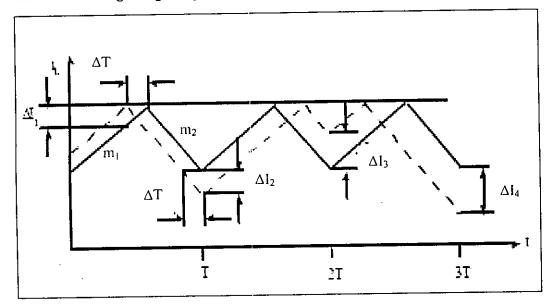

| Fig 2.4: Current loop oscillation for duty cycle greater than 50%               | 8  |

| Fig 2.5: Correction of the oscillation by compensation ramp                     | 9  |

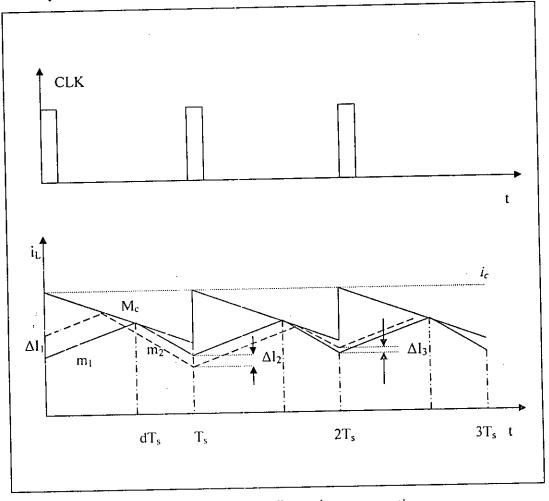

| Fig 2.6: The modulator of the average current-mode control scheme               | 11 |

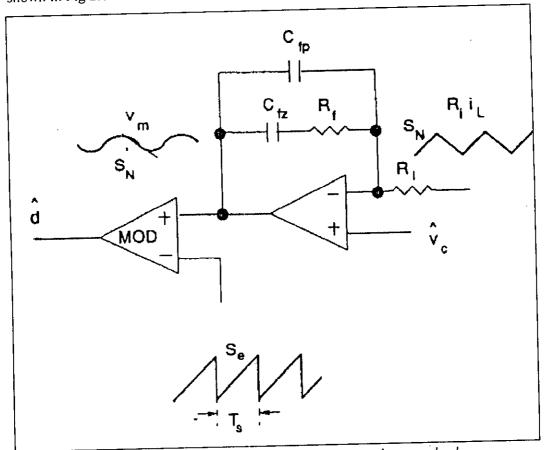

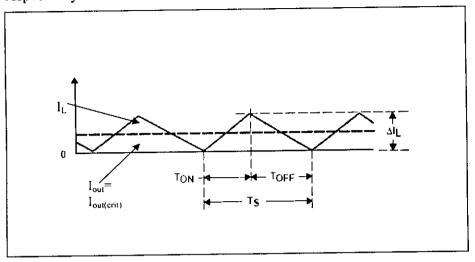

| Fig 2.7: Continuous conduction mode operation                                   | 13 |

| Fig 2.8: The boundary between CCM and DCM                                       | 14 |

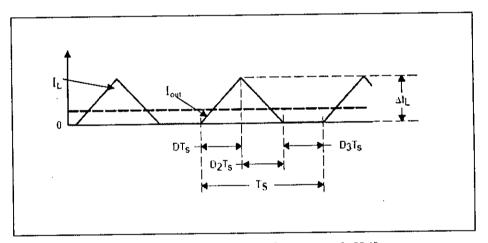

| Fig 2.9: Discontinuous conduction mode                                          | 14 |

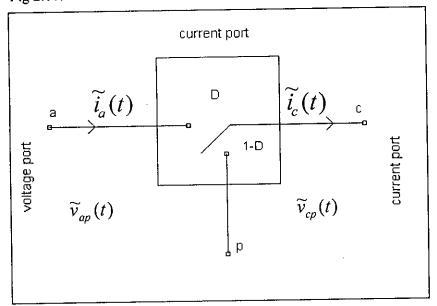

| Fig 2.10: The PWM switch                                                        | 15 |

| Fig 2.11: Boost converter with PWM switch model                                 | 15 |

| Fig 2.12: DC and small signal model of PWM switch.                              | 16 |

| Fig 2.13: DC and small signal model of PWM switch with ESR of the output        | 16 |

| Capacitor.                                                                      |    |

|                                                                                 |    |

| Fig 3.1: The functional block diagram of the converter                          | 18 |

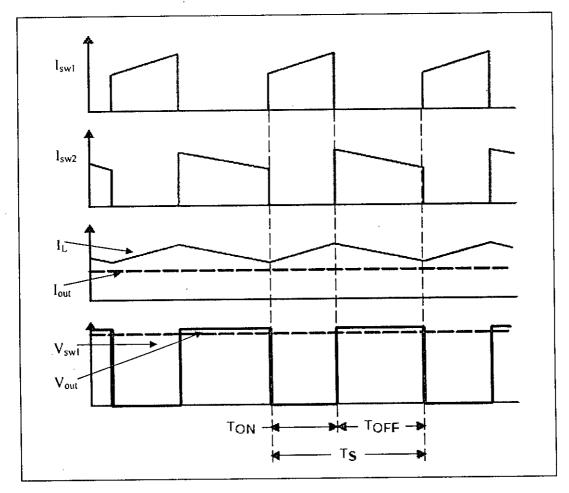

| Fig 3.2: The operational principle of the converter                             | 19 |

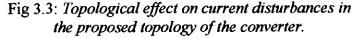

| Fig 3.3: Topological effect on current disturbances in the proposed topology    | 20 |

| of the converter.                                                               |    |

| Fig 3.4: The current loop with compensation in the proposed topology of the     | 21 |

| converter.                                                                      |    |

| Fig 3.5: Geometries of the inductor currents in steady states for obtaining the | 23 |

|                                                                                 |    |

modulator model of the proposed converter.

Fig 3.6: The small signal low frequency model of the proposed converter.25Fig 3.7: The pin configuration & the typical application diagram of the26converter26

| Fig 4.1: The basic Band-gap core used in the converter.              |    |

|----------------------------------------------------------------------|----|

| Fig 4.2: Techniques to avoid unexpected solutions of Band-gap in the | 30 |

| converter                                                            |    |

| Fig 4.3: The variation of reference voltage with temperature         | 31 |

(/

| Fig 4.4: Basic structure of the bias-current generating block of the converter. | 32 |

|---------------------------------------------------------------------------------|----|

| Fig 4.5: Basic structure of the supply selector block of the converter.         | 33 |

| Fig 4.6: The comparator used for the supply selector block of the converter.    | 34 |

| Fig 4.7: The switching portion of the supply selector block of the converter.   | 35 |

| Fig 4.8: The basic structure of the error-amplifier of the converter.           | 36 |

| Fig 4.9: A voltage gain stage used in the error-amplifier of the converter.     | 37 |

| Fig 4.10: Addition of current signals & transformation to a voltage signal in   | 39 |

| the error-amplifier of the converter.                                           |    |

| Fig 4.11: The single stage gain block used in the error-amplifier of the        | 40 |

| converter.                                                                      |    |

| Fig 4.12: The analog part of the time-generator block of the converter.         | 43 |

| Fig 4.13: The overall time-generator block of the converter.                    | 44 |

| Fig 4.14: The ON time to be extracted in time generator block of the            | 44 |

| converter.                                                                      |    |

| Fig 4.15: The output signal, in time unit, for open loop operation of time      | 45 |

| generator block of the converter.                                               |    |

| Fig 4.16: The output signal, in time unit, for normal loop operation of time    | 46 |

| generator block of the converter.                                               |    |

| Fig 4.17: Simulation result of the time generator with the change in input      | 47 |

| voltage                                                                         |    |

| Fig 4.18: A sample segment of a switch used in the converter.                   | 49 |

| Fig 4.19: The NSW, of the converter, for the simulation purpose                 | 50 |

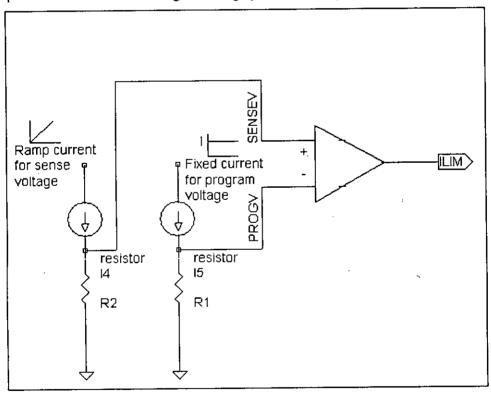

| Fig 4.20: The operational methodology of the current limiter of the             | 51 |

| converter.                                                                      |    |

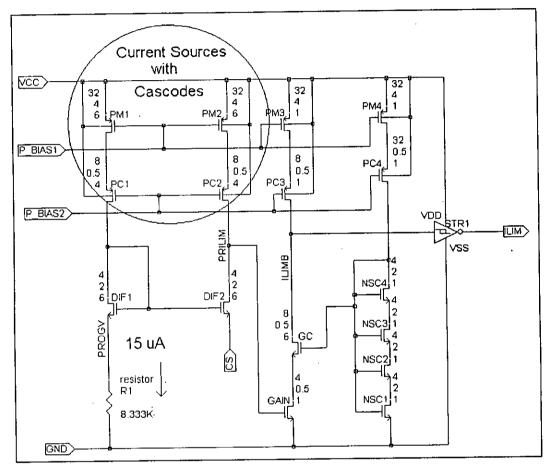

| Fig 4.21: The implementation of the current limiter of the converter.           | 52 |

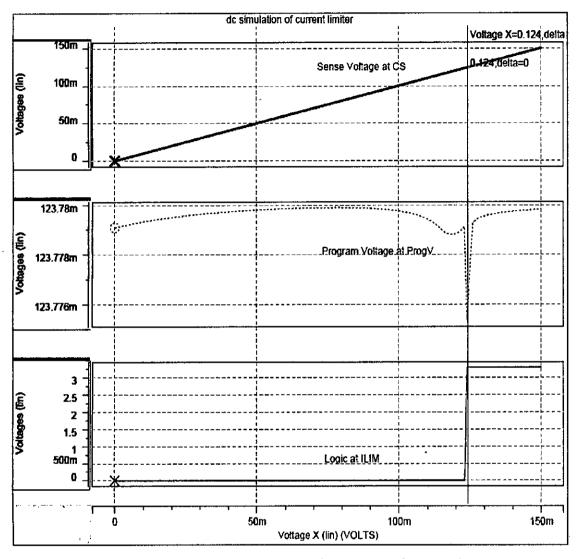

| Fig 4.22: The DC simulation of the current limiter of the converter.            | 53 |

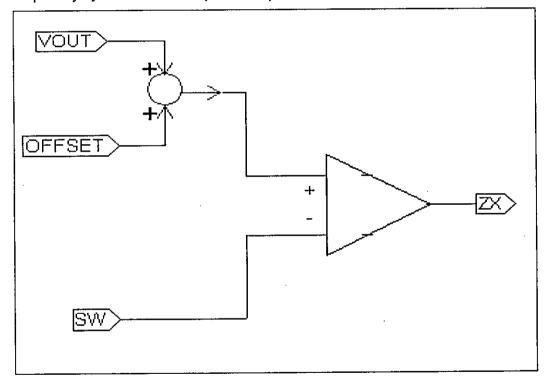

| Fig 4.23: The light load protection scheme of the converter.                    | 54 |

| Fig 4.24: Implementation of the light load protection scheme of the             | 55 |

| converter.                                                                      |    |

| Fig 4.25: Implementation of the thermal sensor of the converter.                | 57 |

| Fig 4.26: The simulation result of the thermal fault condition of the           | 57 |

| converter.                                                                      |    |

| Fig 4.27: Implementation of the switch drivers of the converter.                | 59 |

,

. /

х

Ç.

•••

.

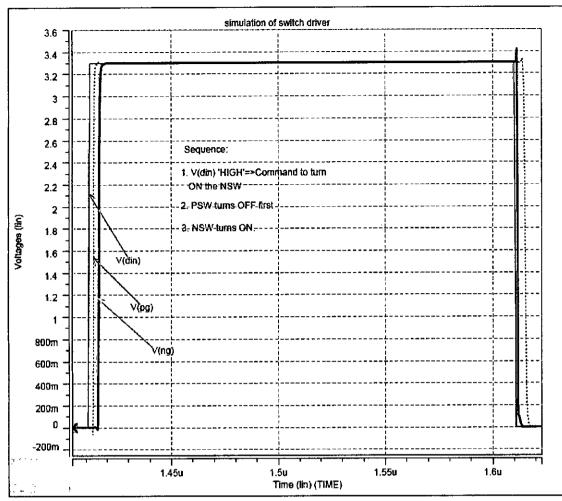

| Fig 4.28: The commutation of the switch driver of the converter.                  | 60 |  |

|-----------------------------------------------------------------------------------|----|--|

| Fig 4.29: Example of the way of staging of the driver of the switch of the        |    |  |

| converter.                                                                        |    |  |

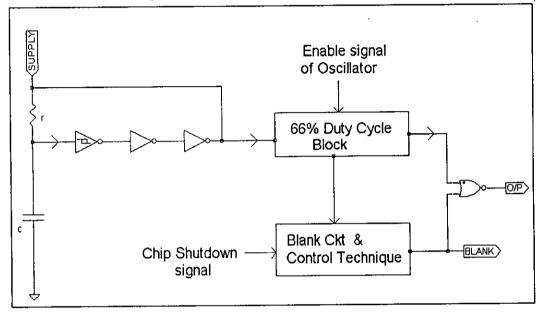

| Fig 4.30: The basic functional structure of the oscillator used the converter.    |    |  |

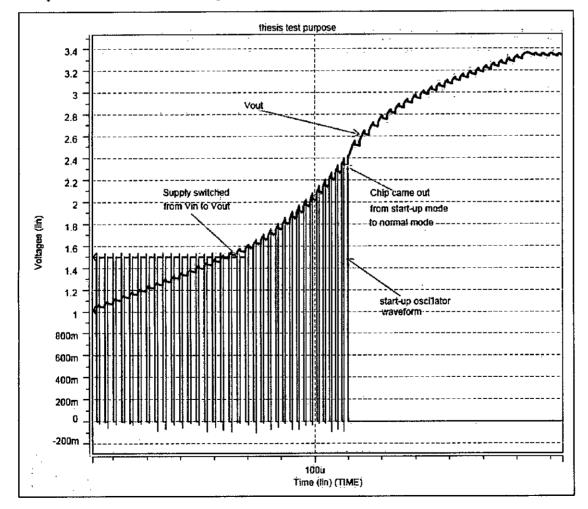

| Fig 5.1: The start-up mode of the converter                                       | 66 |  |

| Fig 5.2: Transition from the start-up mode to the regular mode of the             | 67 |  |

| converter.                                                                        | 68 |  |

| Fig 5.3: Normal PWM operation for 55% duty cycle of the converter.                |    |  |

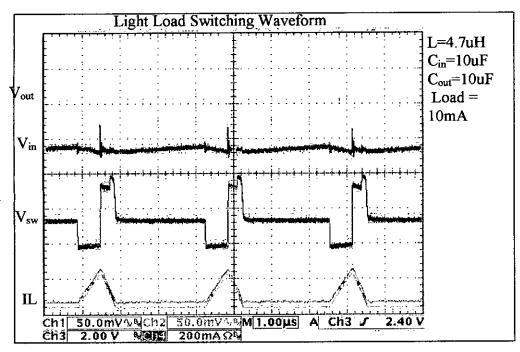

| Fig 5.4: The light load operation of the converter                                | 69 |  |

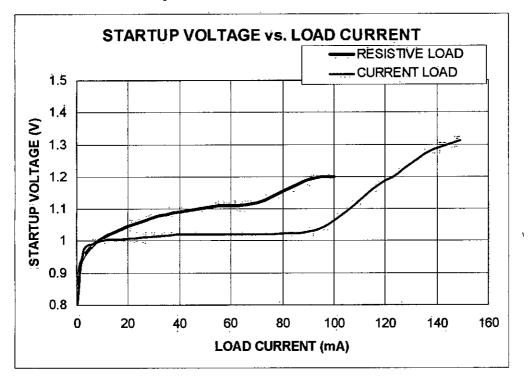

| Fig 6.1: Measured data of start-up load                                           | 72 |  |

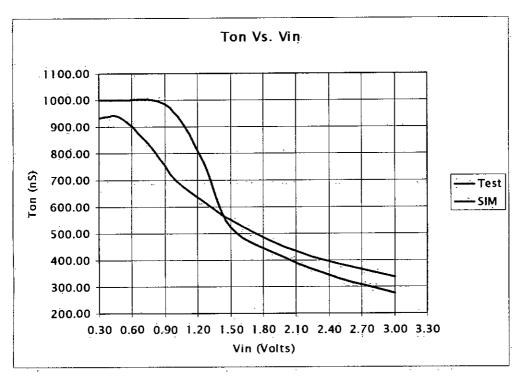

| Fig 6.2: Simulated & measured data of ON time (Ton) of the converter.             | 73 |  |

| Fig 6.3: Measured data of efficiency at different load demand of the              |    |  |

| converter.                                                                        |    |  |

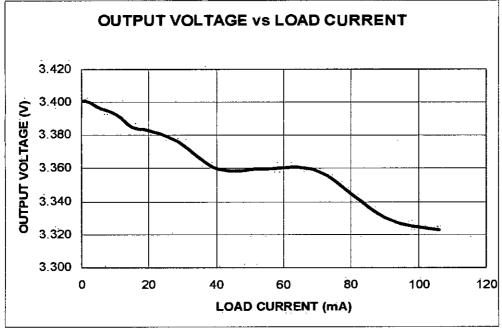

| Fig 6.4: The load regulation characteristics of the converter                     | 74 |  |

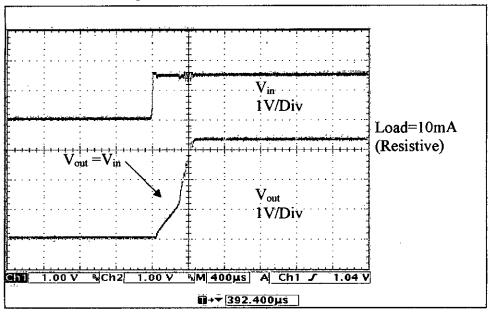

| Fig 6.5: The start-up waveform of the converter for $V_{in}=1.5 \& V_{out}=3.3$ @ | 75 |  |

| 10mA load.                                                                        |    |  |

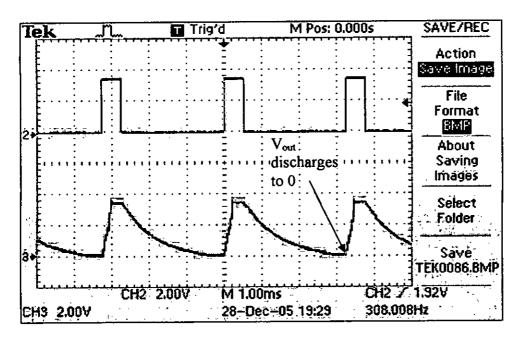

| Fig 6.6: The shut cycle of the converter                                          | 76 |  |

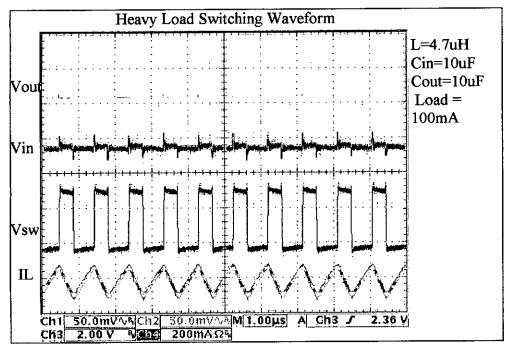

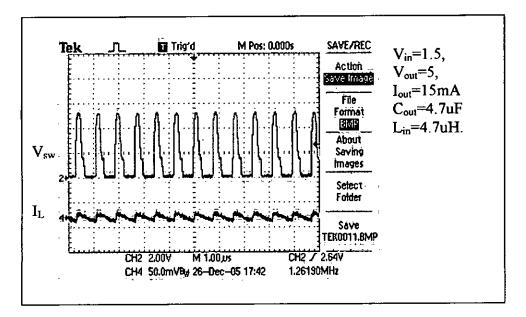

| Fig 6.7: Heavy load switching of the converter at D=55%                           | 77 |  |

| Fig 6.8: The light load operation of the converter                                | 77 |  |

| Fig 6.9: The response of the converter output voltage for a step change in        | 78 |  |

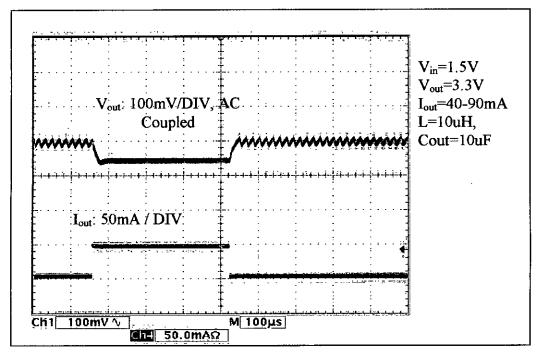

| load.                                                                             |    |  |

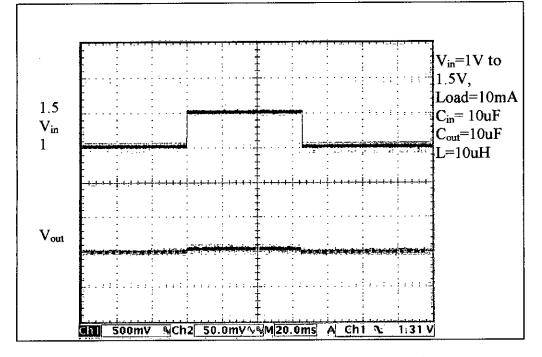

| Fig 6.10: The response of the converter output voltage for a step change in       | 79 |  |

| V <sub>in</sub>                                                                   |    |  |

| Fig 6.11: Operation of the converter at D=70%                                     | 80 |  |

| Fig 6.12. Operation of the converter at $D=24\%$                                  | 80 |  |

# List of Symbols

| Symbols               | Description                                |

|-----------------------|--------------------------------------------|

| mı                    | Positive slope of the inductor current (up |

|                       | slope)                                     |

| <b>m</b> <sub>2</sub> | Negative slope of the inductor current     |

|                       | (down slope)                               |

| Mc                    | Slope of the compensating ramp signal.     |

| D                     | Average duty cycle                         |

| d                     | Small signal duty cycle (generally used as |

|                       | a variable quantity)                       |

| â                     | Perturbed form of duty cycle               |

| Ts                    | Time period                                |

| T <sub>ON</sub>       | Time for the charge phase of the           |

|                       | converter.                                 |

| T <sub>off</sub>      | Time for the boost phase of the converter. |

| $V_{eff}$             | Average effective voltage across the       |

|                       | switches when they remain OFF.             |

| $\hat{v}_{cff}$       | Perturbed form of effective voltage across |

|                       | the switches when they remain OFF.         |

| F <sub>m</sub>        | Gain of the modulator of the converter.    |

| К                     | Boltzmann constant                         |

| Т                     | Absolute temperature.                      |

| q                     | Charge of an electron.                     |

| Is                    | Saturation current.                        |

| А                     | Base-emitter junction area of a bipolar    |

|                       | transistor.                                |

| gm                    | Trans-conductance of a MOS.                |

| $\mu_{\rm p}$         | Mobility of holes                          |

| C <sub>ox</sub>       | Gate capacitance of a MOS.                 |

| V <sub>A</sub>        | Early Voltage.                             |

1

7

ι. Li **Chapter 1**

## Introduction

C

#### 1.1 Background

Among the switching regulators, voltage mode DC-DC conversion was the initial approach, but it required a large number of external components for compensation and the design of the compensation network was too involved. This is due to the fact that the loop gain was sensitive to the load and input supply variation. The above fact made it difficult to use in situations where the supply and load vary widely, since the transfer function (line-to-output) is a strong function of input supply voltage. Because of the complexity of the double pole transfer function in the voltage mode conversion, it was soon felt necessary to simplify the transfer function so that it appears as a single pole. The obvious result was the current-mode control which requires a much simpler compensation scheme compared to its voltage-mode counterpart. The first monolithic current-mode DC-DC converter was introduced in 1985(LTC) and the first on-chip compensated switching regulator was introduced by NSC in 1988 [1]. Current-mode has two feedback loops: an outer one which senses DC output voltage and delivers a DC control voltage to an inner loop which senses power transistor currents and keeps them constant on a pulse-by-pulse basis. Among the several current-mode control techniques, constant-frequency current programmed mode (CPM) control, also known as peak current-mode (PCM) control, is a popular control technique for switch mode power converters. In this control scheme, peak power transistor currents are kept constant on a pulse-by-pulse basis. There are several advantages in this scheme; like built-in over-current protection, robust dynamic responses, simplified voltage-loop compensator design, rejection of input voltage disturbances and relatively simple current sharing for power modules operating in parallel. However, this scheme has also got some disadvantages. The main disadvantage is found during the continuous conduction mode (CCM). This is because of the limited duty cycle that requires compensation to extend the duty-ratio range beyond 50%. Another disadvantage of CPM control is relatively high sensitivity to noise related to sensing the instantaneous current and comparing the sensed signal

to the current command. To enable the converter, operating in CCM, run at higher duty cycle, theoretically above 50%, a compensating ramp is added to current sense signal. Moreover to reduce the sensitivity to noise, the compensation ramp is commonly added in practical CPM designs, even when operating the converter at duty cycles less than 0.5 [2].

#### **1.2 Compensation Issue:**

As mentioned earlier, peak current control mode forces the peak power transistor current to be constant at a level needed to supply the DC load current at the DC output voltage dictated by the voltage error amplifier. The DC load current is the average of the output inductor current, however, and keeping the peak transistor current constant keeps the peak output inductor current constant but does not keep the average inductor current constant. Because of this, in the uncompensated currentmode scheme, changes in the DC input voltage will cause momentary changes in the DC output voltage. The output voltage will be corrected by the voltage error amplifier outer feedback loop. Again, however, the inner- loop, in keeping peak inductor current constant, does not supply the correct average inductor current and output voltage changes again. The effect is then an oscillation in the output voltage. Moreover, for a fixed DC input voltage, there can also be an oscillation. This occurs, when for some reasons an initial current disturbance gets induced in the current loop while the converter is running at duty cycle above 50%. In that case, the current disturbance will grow in pulse by pulse basis first, and then decreases in the next consecutive pulses and afterwards it will grow again. This sort of oscillation is also called as sub-harmonic oscillation, as this occurs at half the switching frequency when the converter runs above the maximum allowable duty cycle, without being compensated [3]-[6].

Another industrially used topology is the Average Current-Mode Control Scheme. In this topology the inductor current is averaged by a current compensator, which is basically an integrator. Integrator adds additional pole to the current loop and this pole needs to be compensated. Hence, external components are needed in the board. This need for the extra components costs severely where space requirements in the board are stringent.

## 1.3 The Recent Research Trend:

Various works have been carried out relevant to the stability of current mode converters operating in CCM. Different topologies have also been introduced along with several analyzing techniques. Middlebrook contributed much to the modeling of PWM converters and analyzing their various features [3]-[5]. A low frequency circuit oriented approach was proposed in [3], though this approach had simplicity and that is why it was widely accepted, it had some issues to be resolved and one of the major insights in [3] was that the crossover frequency of the current loop was considered wideband, implying possible degradation of performance of low frequency model. To cope with potential deficiencies in the earlier approaches, a separate earlier work [7] needed to be used, which could predict the well known subharmonic oscillation, occurring at duty cycle greater than 50% with no compensating ramp. A general expression for the current loop gain is derived, from which it is seen that the crossover frequency of the current loop is limited approximately to one third of the switching frequency. A few authors have contested this result on the ground that Shannon's sampling theorem limits the crossover frequency to half the switching frequency. This apparent contradiction has apparently been resolved in [4]. The most common topology, used in industry nowadays, is fixed frequency Peak Current Mode control. Brayant and Kazimierczuk presented the analysis of open-loop power stage dynamics [8] and the modeling of closed current loop configuration, relevant to current-mode control for a boost pulse width-modulated (PWM) dc-dc converter operating in continuous-conduction mode (CCM) is presented in [9]. In [8], the small signal output current to inductor current transfer function accounting for MOSFET delay and input voltage to inductor current have been derived. In [9] the transfer function from the error voltage to duty cycle has been derived. Another earlier work [10] suggested that the modulator gain factor F<sub>m</sub> can approach to infinity at the limit of stability. In [4], Middlebrook along with Tan developed a unified model for current mode converters where they determined a unified modulator model and current loop gain incorporating sampling effect. Ridley, in [11] and [12] introduced a continuous time model, where sampling gain is incorporated into the current loop. Ridley et. al. proposed another topology other than PCM control in [13], where in stead of peak current, average inductor current is used to control the loop dynamics. Another control technique, valley current mode technique, also known as 'leading edge

modulation' has been introduced in [14], which has some advantages. One of the advantages it offers is the elimination of the positive zero in fixed frequency operation [15].

## 1.4 Review of the Existing Compensation Techniques:

As mentioned above, sub-harmonic oscillation generally occurs for the duty cycle above 50%. This type of oscillation can be stopped by adding a compensation ramp by ensuring that a current perturbation in a switching period diminishes in the next period. For Average Current-Mode Control scheme, some sorts of external compensators are needed. In Average Current-Mode Control, inductor current is averaged by an RC network, which is basically an integrator. Though a huge gain is available in this scheme, the main challenge is to stabilize such loop, as the integrator adds an additional pole to the loop. Hence, to cancel the effect of this additional pole, a zero is needed in the loop, and the addition of this zero is accomplished by the use of external components.

#### **1.5 Objectives of This Thesis:**

The objectives of this thesis are to develop a new topology of synchronous step-up converter, which can run at higher duty cycle without addition of any kind of compensating signal and then to implement the converter paying heed to all the design issues that may have to be encountered in real world. In developing a new topology, the mathematical model for the modulator of the converter will be derived first, considering all the small signal phenomena. This converter will then be implemented using various functional blocks. While designing the functional blocks all the supply, process and temperature dependent parameters will be taken into account. The fabricated chip will then be tested and the test results will be studied in details to evaluate its performance.

## Chapter 2

## **Current Mode Converters in Brief**

#### 2.1 Synchronous Converter in Brief:

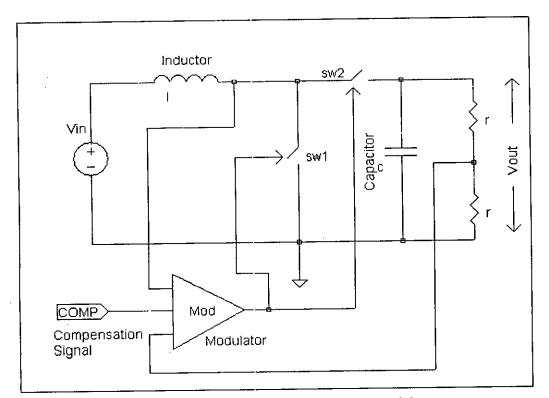

In the synchronous converter, both the switches are controlled unlike the case in its asynchronous counterpart, where only one switch is controlled and in stead of using the other switch, generally a diode is used. However, there is no 100% synchronism in the synchronous converter, i.e. there is no such case where a switch is turned ON at the instant the other is turned OFF or vice versa because of the internal delay in the signal propagation. There are also some design requirements especially for safety purposes and in those cases, one switch is turned OFF first and then the other is turned ON. Fig 2.1 illustrates a synchronous boost converter with a modulator. The two switches SW1 and SW2 are turned ON alternately to have charge and boost phase of the converter. Before one is turned ON, it is ensured that other has been turned OFF. In an open loop boost converter, the input voltage is stepped up to another higher level based on the duty cycle of operation (the clock that is provided externally to the switches). However, to have a regulated output voltage a closed loop control mechanism is needed. The modulator serves that purpose. It senses the parameters like portion of output voltages or the current through the inductor or both and controls the loop operation by converting those signals to time domain signals (i.e. duty cycle). The overall stability of the loop depends; to a great extend, on the stability of the modulator.

#### 2.2 Basic Idea about the Current Mode Converter:

The block diagram shown in Fig 2.2 was the approach used for the first switching regulator designs [16]. This is also known as Voltage Mode Control Topology. The major characteristics of this topology are that there is a single voltage feedback path, with pulse-width modulation performed by comparing the voltage error signal with a constant ramp. Current limiting must be done separately. As a single loop is associated, tasks like designing of that loop and analyzing the loop dynamics are simpler. But there are also some disadvantages of such topology like

slow response (as any change in line or load must first be sensed as an output change and then corrected by the feedback loop.) and relatively more complicated compensation (as the output filters adds two poles to the control loop and the loop gain varies with the input voltage).

To get rid of the voltage mode deficiencies, another control technique called Current Mode Topology has been introduced and it is illustrated in Fig 2.3. As it is evident from Fig 2.3 that, basic current-mode control uses the oscillator only as a fixed-frequency clock and the ramp is replaced with a signal derived from output inductor current. It has got some advantages like fast response with the change in the line voltages (as inductor current rises with a slope determined by  $V_{in}$ - $V_0$ ), simpler loop compensation (Since the Error Amplifier is now used to command an output current rather than voltage, the effect of the output inductor is minimized and the filter now offers only a single pole to the feedback loop.) Moreover, the current mode topology also provides some additional features like: pulse-by-pulse current limiting, and the ease of providing load sharing when multiple power units are paralleled.

Fig 2.1: Synchronous boost regulator with modulator

Fig 2.2: Voltage mode control mechanism [16]

Fig 2.3: Current mode control [16]

# 2.3 Deficiencies in Current Mode Control Mechanism & Their Remedies:

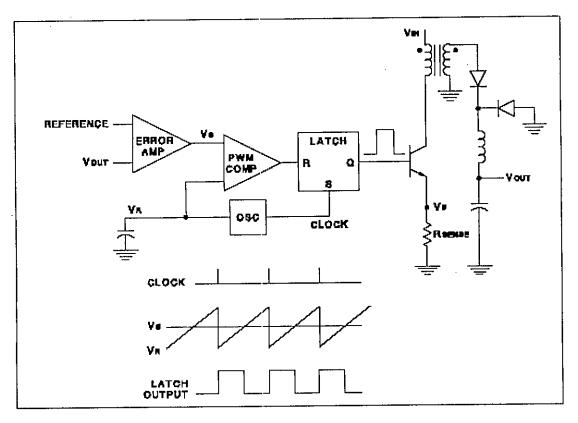

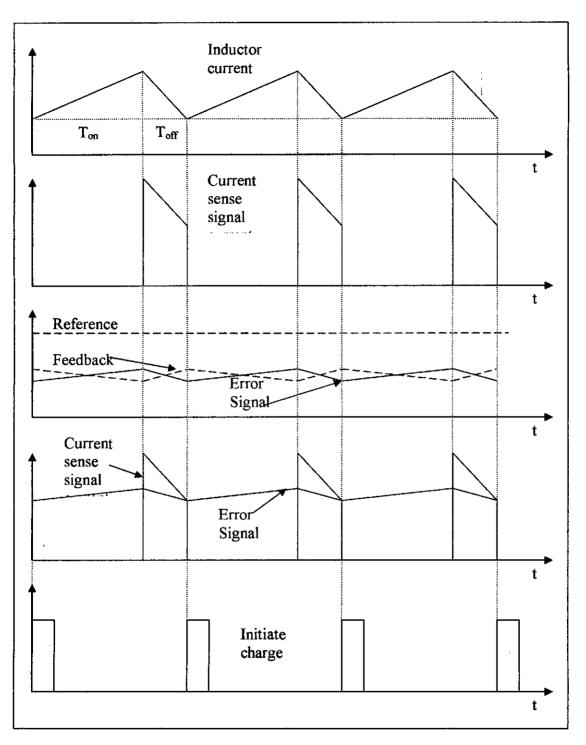

In spite of several advantages, there are also some sorts of deficiencies associated with the current mode control mechanism. A brief idea has been given in previous discussions. In this subsection, those problems have been illustrated more precisely. First, let us have a look at the case of sub-harmonic oscillation. One of the ways such kind of oscillation occurs, when a current disturbance gets induced in a converter running at high duty cycle, for a fixed input. For a fixed DC input voltage,

Fig 2.4: Current loop oscillation for duty cycle greater than 50% [25]

if for some reasons there is an initial current disturbance  $\Delta I_1$ , after a first down-slope the current will be displaced by an amount  $\Delta I_2$ . If the duty cycle is above 50% (m<sub>2</sub>>m<sub>1</sub> in Fig 2.4), the output disturbance after one cycle  $\Delta I_4$  is greater than the input disturbance  $\Delta I_3$ . This can be further explained from Fig 2.4. For a small current displacement  $\Delta I_4$ , the current reaches the original peak value earlier in time by an amount *dt*, where  $dt = \Delta I_1/m_1$ . ON the inductor down-slope, at the end of the ON time, the current is lower than its original value by an amount  $\Delta I_2$  where

$$\Delta I_2 = m_2 dt = \Delta I_1 \frac{m_2}{m_1}$$

Now with  $m_2>m_1$ , the disturbances will continue to grow but eventually decay, giving rise to an oscillation. As mentioned earlier, this sort of

oscillation is also called as sub-harmonic oscillation, when the converter runs above the maximum allowable duty cycle, without being compensated [3],[5],[6]. This PCM (Peak Current Mode, as the peak current is regulated) control, however, is a widely used topology in industrial purposes and the above mentioned type of oscillation is eliminated by the addition of a compensating signal with slope  $M_c > 0$ . The way in which such compensating technique works, has been illustrated in Fig 2.5.

Fig 2.5: Correction of the oscillation by compensation ramp [25]

From a simple geometrical argument, the condition to prevent subharmonic oscillation is:

$$\left|\frac{\Delta I_2}{\Delta I_1}\right| = \left|\frac{m_2 - M_c}{m_1 + M_c}\right| < 1$$

(2.1)

1

where,  $m_1 = V_{m}/L > 0$  is the inductor current slope in the charge phase

$(dT_s)$ , when sw1 in Fig 2.1 is ON, and  $m_2=(V_{out}-V_{in})/L>0$  is the inductor current slope in the boost phase  $[(1-d)T_s]$  when sw2 in Fig 2.1 is ON. From the equation 2.1, it is evident that, by selecting  $M_c > m_2/2$ , stable operation of the current loop under all steady-state conditions is possible to be achieved. Besides, in [3],[17],[18] modulator model for the current programmed converters was derived, experimented and modified. A model for current-mode converter consists of two parts: 1) the model for the power stage, and 2) the model for the modulator [3]. The model of power stage in [19], [20] is now widely accepted, hence the actual task is reduced to the establishment of a modulator model. A modulator is expected to be expressed in terms of the average inductor current  $i_l$ , the average control current  $i_c$  and an effective voltage  $v_{eff}$ , which determines the slopes of the inductor current. Satisfying the conditions, a unified modulator model has been developed in [3] and the modulator gain  $F_m$  is expressed as:

$$F_{m} = \frac{2L}{T_{s}v_{eff} \left[ \left( \frac{2LM_{c}}{D'v_{eff}} + 2 \right) D' - 1 \right]}$$

(2.2)

From the equation (2.2), it is seen that,  $F_m$  approaches infinity for

$$D' = \frac{1}{\left[\frac{2LM_c}{D'v_{eff}} + 2\right]}$$

(2.3)

where, D' = 1 - D

-

Equation (2.3) is the minimum value for D' to maintain a finite positive value for  $F_m$ . Hence, we have:

$$D'_{\min} = \frac{0.5}{\left[1 + \frac{M_c}{D' v_{eff} / L}\right]}$$

$$\Rightarrow D'_{\min} = \frac{0.5}{\left[1 + \frac{M_c}{m_1}\right]}$$

(2.4)

Hence, from equation (2.4), the current loop becomes unstable for  $D'_{min} = 0.5$ , if  $M_c = 0$ , which implies that in the absence of  $M_c$ , the loop oscillates for

æ

$D_{\text{max}}$ =0.5. Addition of slope compensating signal demands extra care and attention. The addition of the slope compensating signal, does not depend on any kind of internal tracking within the chip, it is one sort of asynchronous phenomenon. This compensating signal shows up as a percentage error in the output voltage i.e. it increases the load regulation number of the chip. Moreover, generally this signal is added relative to the ground potential and in doing there also arise some design issues. If this signal is small in magnitude and is fed to the input of a MOS device, the offset of the MOS affects and if this signal is added to the base of a bipolar device, extra input linearity is needed. This is sometimes a design constraint, in case of low voltage application.

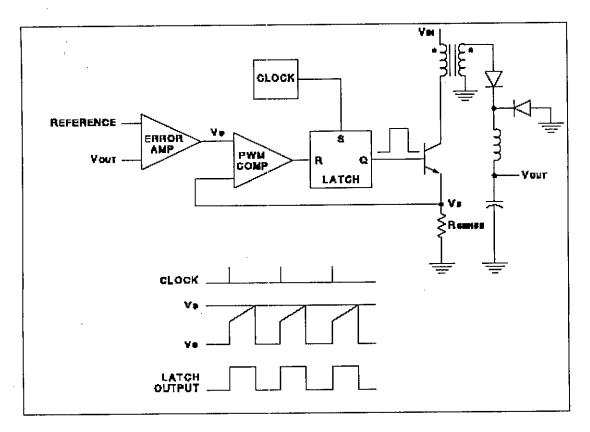

In average current control scheme, the existence of the current compensator makes the modeling of the average current-mode control more complicated [13]. The modulator of the average current control scheme has been shown in Fig 2.6.

Fig 2.6: The modulator of the average current-mode control scheme [13]

As it is evident from Fig 2.6, an integrator (compensator), consisting of R-C network has been used to have the average of the inductor current. This integrator adds a pole at  $\frac{1}{2\pi C_{fc}R_{f}}$  in the current loop, the effect of which has to be cancelled by an external compensator.

## 2.4 Control Topologies & Conduction Modes:

In dc-dc converters current mode Pulse Width Modulation (PWM) and current-limited Pulse Frequency Modulation (PFM) control schemes are widely used in industries due to their fast dynamic response and automatic over-current protection *[21]-[23]*. In PWM control, the inductor current is sensed and is made to modify the pulse-width, whereas, in PFM control inductor current modifies the oscillation frequency for voltage regulation. One of the methods to regulate output voltage, while supplying a specific load demand, in PWM control employs switching at a constant frequency and adjusting the ON duration of the switch. In PFM, however, the switching frequency is varied with the change in load demand while regulating the output voltage. For a certain load, this PFM scheme may turn into a PWM scheme. Usually a converter, though it is not designed to operate in fixed frequency, runs in PWM scheme for a certain load range and then operating frequency becomes constant for that condition. However, when the output load demand becomes very low, numbers of pulses are skipped and hence it seems like it is modulating its operating frequency.

A current mode converter has two types of conduction modes [24];

namely

a). Continuous Conduction Mode (CCM) and

b). Discontinuous Conduction Mode (DCM).

#### a).Continuous Conduction Mode:

In the continuous conduction mode, current flows continuously in the inductor during the entire switching cycle in steady-state operation. In this mode, the boost power stage assumes two states per switching cycle. In the ON state,  $SW_1$  (Fig 2.1) is ON and  $SW_2$  is OFF. The duration of the ON state is  $D \times T_S = T_{ON}$ , where D is the duty cycle set by the control circuit, expressed as a ratio of the switch ON time to

the time of one complete switching cycle,  $T_S$ . The duration of the OFF state is  $T_{OFF}$ . Since there are only two states per switching cycle for continuous conduction mode,  $T_{OFF}$  is equal to  $(1-D) \times T_S$ . The timing waveforms have been illustrated in Fig 2.7. In the CCM, average inductor current tracks the output current, i.e., if the output current decreases, then so does the average inductor current exactly.

Fig 2.7: Continuous conduction mode operation [24]

#### b). Discontinuous Conduction Mode:

In the Discontinuous Conduction Mode, the output load current is reduced below the critical current level so that, the inductor current will be zero for a portion of the switching cycle. The facts are evident in Fig 2.8 and Fig 2.9. There are three unique states that a converter assumes during the DCM. The ON state is when SW<sub>1</sub> is ON and SW<sub>2</sub> is OFF. The OFF state is when SW<sub>1</sub> is OFF and SW<sub>2</sub> is ON. The idle state is when both SW<sub>1</sub> and SW<sub>2</sub> are OFF. Now,  $T_{ON} = D \times T_S$ ,  $T_{OFF} = D_2 \times T_S$ ; and the remainder idle time is given as  $T_S - T_{ON} - T_{OFF} = D_3 \times T_S$ , where  $D_2$  and  $D_3$  are the portions of the total time  $T_S$ , when charge of the inductor is being dumped to the capacitor and the current through the inductor remains at the zero level, respectively.

Fig 2.8: The boundary between CCM and DCM [24]

Fig 2.9: Discontinuous conduction mode [24]

#### 2.5 PWM Switch Model in CCM:

The PWM switch model representing the dc and small-signal characteristics of the nonlinear part of the converter, has been illustrated in [20]. External circuit elements are connected to the switch in such a way as to satisfy the proper port conditions given in Fig 2.10, i.e. it is ensured that in any condition ports a and p do not get shorted and in one cycle a is connected to c and in the other cycle p is connected to c to have continuous current conducting condition in a-c and c-p paths

respectively. The dc and small-signal characteristics of a PWM converter are then obtained by replacing the PWM switch with its equivalent circuit model as shown in Fig 2.11.

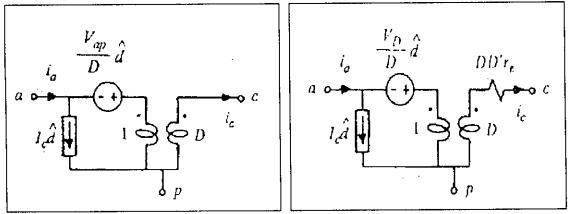

Fig 2.10: The PWM switch

Fig 2.11: Boost converter with PWM switch model.

Now investigating the invariant relationships between the terminal currents and voltages of the PWM switch we have the following for the instantaneous quantities:

$$\widetilde{i}_{\alpha}(t) = \begin{cases} \widetilde{i}_{c}(t), & 0 \le t \le DT_{s} \\ 0, & DT_{s} \le t \le T_{s} \end{cases}$$

$$\widetilde{v}_{cp}(t) = \begin{cases} \widetilde{v}_{op}(t), & 0 \le t \le DT_{s} \\ 0, & DT_{s} \le t \le T_{s} \end{cases}$$

$$(2.5)$$

$$(2.6)$$

However, in dc-dc converters the average quantities are of greater importance and hence, for the average terminal quantities from the equations (2.5) and (2.6) are found as:

$$i_a = di_c \tag{2.7}$$

$$v_{cp} = dv_{op} \tag{2.8}$$

Now, perturbing the equations (2.3) and (2.4) with respect to the variable quantities we have:

$$\hat{i}_{a} = D\tilde{i}_{c} + I_{c}\tilde{d}$$

$$\hat{v}_{cp} = D\hat{v}_{ap} + \hat{d}V_{ap}$$

$$\Rightarrow \hat{v}_{cp} = D(\hat{v}_{ap} + \frac{\hat{d}V_{ap}}{D})$$

(2.10)

The equations (2.9) and (2.10) correspond to the dc and small-signal model of the PWM switch. The perturbed terminal quantities in the equations (2.9) and (2.10) can be arranged to satisfy the circuit configuration, illustrated in Fig 2.12.

Fig 2.12: DC and small signal model of PWM switch [20].

Fig 2.13: DC and small signal model of PWM switch with ESR of the output capacitor [20].

In deriving the equation (2.10), the Equivalent Series Resistance (ESR) of the output capacitor has been neglected; if it is intended to be included, equation (2.10) will be modified as:

$$\hat{v}_{ap} = \frac{\hat{v}_{cp}}{D} + \hat{i}_{c}r_{c}D' - V_{D}\left[\frac{\hat{d}}{D}\right]$$

where,  $V_{D} = V_{ap} + I_{c}(D - D')r_{c}$

(2.11)

The dc and small signal model of the PWM switch will then be represented as in Fig 2.13.

## **Chapter 3**

## The Proposed Converter

#### 3.1 The Architecture of the Proposed Converter:

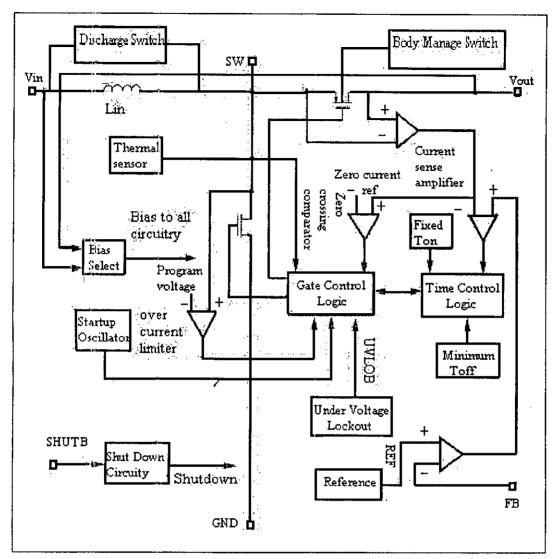

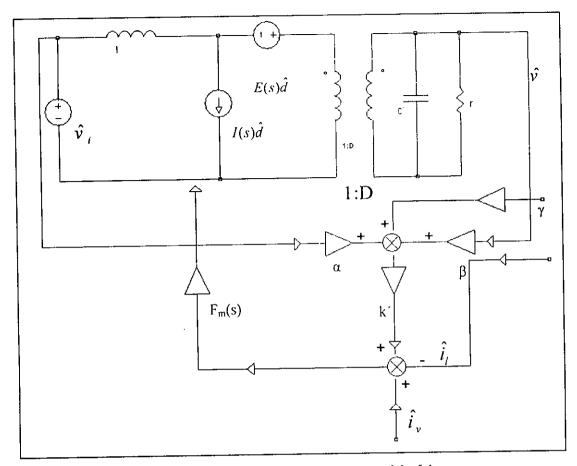

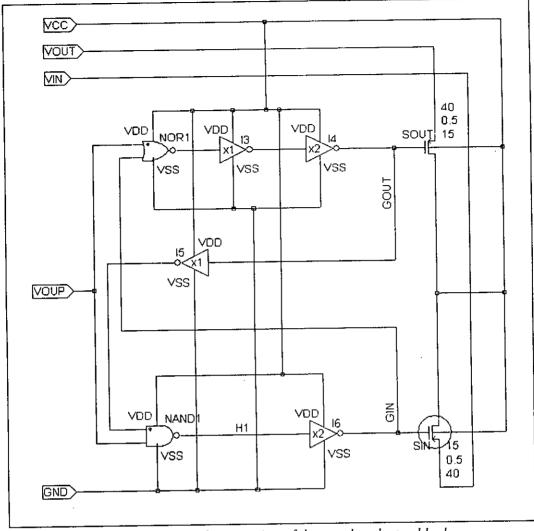

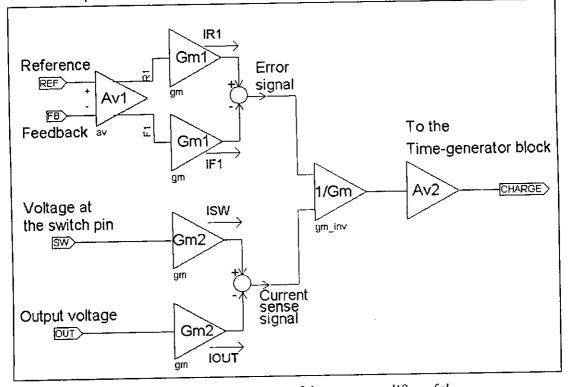

The functional block diagram in Fig 3.1 depicts the basic structure of the converter. The start-up oscillator starts the chip and raises the output voltage from zero to a certain level, where the actual PWM operation is initiated. The PWM operation of the chip is accomplished by two loops: one (current loop) functioning within the other (voltage loop). The current-sense amplifier, which senses the voltage across the PMOS switch, extracts the sensed current signal for the current loop, while the other amplifier taking REF and FB as inputs supplies the sensed voltage signal for the voltage loop. The current loop is embedded in the voltage loop, ensuring that sufficient response speed difference exists between the two loops. However, the loop is completed through a control block namely "Time Control Logic" where a time generator circuit provides a fixed ON time for a certain input voltage and a minimum OFF time. The bias select circuit selects the supply for all the circuitry of the converter either from the input or from the output voltage. The accessories for the proper, safe and efficient operation are thermal sensor, which protects the chip from thermal damage due to excessive rise of temperature within it; over-current limiter that checks the inrush of current from the source, feeding the converter; under voltage lockout block that prevents the logic blocks of the chip from malfunctioning because of low voltage; zero-crossing comparator that hinders the current through the inductor to reverse its polarity and thus back charging of the source from the load side ,when the output load is low, resulting in efficient operation during the light load condition; discharge switch which works to dampen the ringing of the inductor current and the body manage switch that manages the substrate diode of the PMOS switch by selecting the proper substrate bias from input and output voltages depending on the operation conditions. These accessories, however, perform their assigned tasks through a control block called "Gate Control Logic".

¢

Fig 3.1: *The functional block diagram of the converter*

### 3.2 The Basic Operational Principle:

The proposed converter employs OFF time (Boost phase) modulation technique. The timing diagram in Fig 3.2 explains the operation principle of the loop. The ON time (Charge phase) is kept constant for a fixed input voltage  $V_{in}$ , in such a way that this ON time is inversely proportional to  $V_{in}$ . Each charge phase is initiated by an error amplifier which senses the valley current through the inductor as the current sense signal and takes the Band-gap reference and feedback voltage as its input signals.

#### Fig 3.2: The operational principle of the converter

ø

The charge phase, however, will be terminated by a time generator circuit, which generates the required ON time for a fixed input voltage. Referring to Fig 3.2, it is found that the current –sense signal is proportional to the inductor current of the time  $T_{off}$  (i.e. during the boost phase). Besides, the difference between the reference and feedback voltages constitutes the 'error signal'. The 'current sense

signal' and the 'error signal' are compared at their down slopes to yield the logic signal to initiate a charge phase. As the decision of the loop is being taken at the valley of the inductor current, this methodology is also known as 'valley current sense mode'. Here the current loop regulates the valley of the inductor current. The minimum  $T_{off}$  has been provided to have forceful boosting up of the output capacitor, when the loop is broken (e.g. during start-up condition, when a load step is applied etc.).

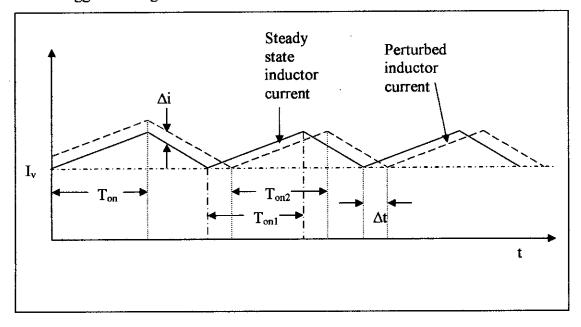

## 3.3 The Topological Impact on the Current Loop Oscillation:

This topology provides some inherent features, so that any sort of the current disturbances may die out within a cycle and does not grow any further. As a result, unlike the case that is in subsection 2.3 of chapter 2 the current disturbances will not aggravate. Fig 3.3 illustrates the fact.

For some reasons, with a fixed input voltage i.e.  $V_{in}$ , a current disturbance  $\Delta i$  occurred (shown by dotted lines in Fig 3.3). As this is a valley current mode topology, the current loop will keep the valley of the inductor current constant (I<sub>v</sub> in Fig 3.3). As a result, the next cycle will be initiated only if the perturbed inductor current reaches the valley at its down-slope. Moreover, ON time is constant for a fixed DC input voltage (T<sub>on</sub>=T<sub>on1</sub>=T<sub>on2</sub>) for this topology and hence the charge phase of the next cycle will terminate that fixed ON time. As a result, the perturbed

inductor current will just be a replica of the steady state inductor current with a  $\Delta t$  shift in time, in the next cycle. Thus the current disturbance that is got induced in the current loop is automatically eliminated by the topological features of the converter.

Following the approaches in [25], let us examine the current loop of the converter in an alternative way to see the issues of current-loop oscillation and the way to compensate the loop to avoid the oscillation.

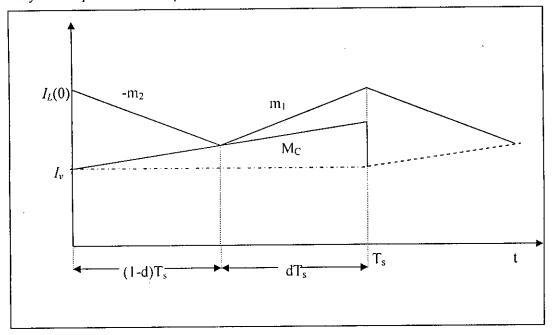

Fig 3.4: The current loop with compensation in the proposed topology of the converter

As mentioned earlier, this converter topology employs the valleycurrent mode technique, when the sensed current reaches the programmed current (illustrated by the dotted line), the boost phase terminates and the charge phase is initiated. Let's introduce a compensation ramp and as a result, the programmed current  $I_y$  will be perturbed with a slope of M<sub>C</sub>. Now from the geometry, we have

$$I_{L}(0) - m_{2}(1-d)T_{s} = I_{v}(T_{s}) + M_{c}(1-d)T_{s}$$

$$\Rightarrow I_{L}(0) - m_{2}T_{s} + m_{2}dT_{s} = I_{v}(T_{s}) + M_{c}T_{s} - M_{c}dT_{s}$$

$$\Rightarrow I_{L}(0) - m_{2}T_{s} + m_{2}T_{out} = I_{v}(T_{s}) + M_{c}T_{s} - M_{c}T_{out}$$

and,

$$I_{v}(T_{s}) + m_{1}dT_{s} - M_{c}dT_{s} = I_{L}(T_{s})$$

$$\Rightarrow I_{v}(T_{s}) + m_{1}T_{out} - M_{c}T_{out} = I_{v}(T_{s})$$

(3.2)

For this topology,  $T_{on}$  is fixed for a particular input voltage  $V_{in}$ . Taking this into consideration and perturbing the equations eq1 & eq2 we have

$$\hat{i}_{L}(0) = \hat{i}_{V}(T_{s})$$

$$\hat{i}_{V}(T_{s}) = \hat{i}_{L}(T_{s})$$

(3.3)

(3.4)

From the equations (3.3) and (3.4), we have  $\hat{i}_L(0) = \hat{i}_L(T_s)$ ; hence

$\Delta \hat{i}_L = 0$ , i.e. any disturbance in the inductor current dies out within a cycle, it is does not aggravate in cycle by cycle basis. Moreover, if the compensating ramp is not used, we have  $\hat{i}_v(T_s) = 0$  and again  $\hat{i}_L(0) = \hat{i}_L(T_s)$  holds, which ensures that even if no compensation scheme is introduced, the current disturbances of the converter are eliminated by the current loop.

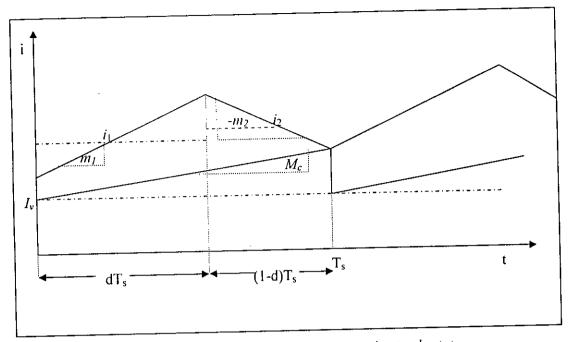

#### 3.4 The Modulator Model:

As mentioned in *subsection 2.3* in the chapter 2, the actual task in modeling a converter has been reduced to the development of the model of the modulator. Following the steps in [4], a unified modulator model has been derived here. Fig 3.5 shows inductor current waveforms in steady state, where  $m_1$  is the upslope,  $-m_2$  is the down-slope and  $M_c$  is the slope of the compensating ramp. The geometries of the waveforms provide fundamental information for derivation of a modulator model.

Finding the values of  $i_1$  and  $i_2$  at the respective middle points of the triangles we have:

$$i_{1} = I_{y} + M_{c}dT_{s} + \frac{1}{2}m_{1}dT_{s}$$

(3.5)

$$i_2 = I_v + M_c dT_s + \frac{1}{2} m_2 d'T_s$$

(3.6)

where,  $d' = (1 - d)$  (3.7)

For a switch-mode converter, the effective voltage  $\hat{v}_{eff}$  across the switches is found in terms of input terminal voltage  $\hat{v}_i$  and the output terminal voltage  $\hat{v}_a$ , by the following expression [4]:

$$\hat{v}_{eff'} = \alpha \, \hat{v}_i + \beta \, \hat{v}_o \qquad (3.8)$$

Where,  $\alpha$ ,  $\beta \in \{0,1\}$ .

For a boost converter,  $\alpha = 0$  and  $\beta = 1$  and hence from (3.8) we have:

$\hat{v}_{eff'} = \hat{v}_o \qquad (3.9)$

S'A

Fig 3.5: Geometries of the inductor currents in steady states for obtaining the modulator model of the proposed converter.

Again, the slope of the inductor current through an inductor of inductance L, during the charge cycle, (3.10)

$$m_1 = \frac{v_i}{L} \tag{3.10}$$

And the input-output relationship of a boost converter operating in Continuous Conduction Mode at the duty cycle d,

$$v_o = \frac{v_i}{1 - d} \tag{3.11}$$

From the equations (3.7), (3.9), (3.10) and (3.11) we have the following relationship:

$$m_1 = \frac{v_{eff}d'}{L} \tag{3.12}$$

Therefore, from (3.5) and (3.12) we have:

$$i_{1} = I_{v} + M_{c}dT_{s} + \frac{1}{2L}(dd'T_{s})v_{eff}$$

$$= I_{v} + KM_{c} + \frac{1}{2L}(Kd')v_{eff}$$

(3.13)

Where K is a constant, as  $dT_s = T_{on}$ , which is a constant number for a fixed input voltage, in this topology.

Equation (3.13) is a unified large-signal expression which describes how a duty cycle d is determined. Small-signal information can be derived by its perturbation. Now differentiating the equation (3.13) partially, with respect to the variables, we have the following relationship:

$$\hat{i}_{1} = \hat{i}_{v} + KM_{c} + \frac{K}{2L} [D'\hat{v}_{eff} - \hat{d}V_{eff}]

\Rightarrow \frac{K}{2L} V_{eff} \hat{d} = (\hat{i}_{v} - \hat{i}_{1}) + \frac{K}{2L} D'\hat{v}_{eff} + KM_{c}

\therefore \hat{d} = \frac{1}{\frac{K}{2L} V_{eff}} [(\hat{i}_{v} - \hat{i}_{1}) + \frac{K}{2L} D'\hat{v}_{eff} + KM_{c}]

= F_{m}[(\hat{i}_{v} - \hat{i}_{t}) + K'\hat{v}_{eff} + K'']

= F_{m}[(\hat{i}_{v} - \hat{i}_{t}) + K'(\hat{v}_{eff} + \frac{K''}{K'})]

= F_{m}[(\hat{i}_{v} - \hat{i}_{t}) + K'(\hat{v}_{eff} + \gamma)]$$

(3.15)

From the Equations (3.14) and (3.15) the following identification can be made in Fig 3.6.

$$F_m = \frac{1}{\frac{K}{2L}V_{egg}}$$

(3.16)

$$K' = \frac{K}{2L}D' \tag{3.17}$$

$$K'' = KM_{c} \tag{3.18}$$

$$\gamma = \frac{K''}{K'} \tag{3.19}$$

Fig 3.6: The small signal low frequency model of the proposed converter.

Hence unlike the modulator model that has been derived in [4], it is found that the gain of the modulator  $F_m$  is duty cycle independent. Again, if the slope signal is eliminated, we will have  $M_c=0$  and hence from equations (3.15), (3.18) and (3.19) the following relationship is derived:

$$\dot{d} = F_m[(\hat{i}_v - \hat{i}_l) + K' \hat{v}_{eff}]$$

(3.20)

Hence, from the equation (3.20), it is evident that the slope compensating signal does not affect the gain of the modulator, which, itself, is duty cycle independent. Moreover, inductor current averaging technique would not be applied here; rather, pulse-by-pulse decision of the current loop will be employed.

All active devices are built on-chip. The device needs only one power inductor and input-output capacitor as the external components.

# 3.5 Other Necessary Information:

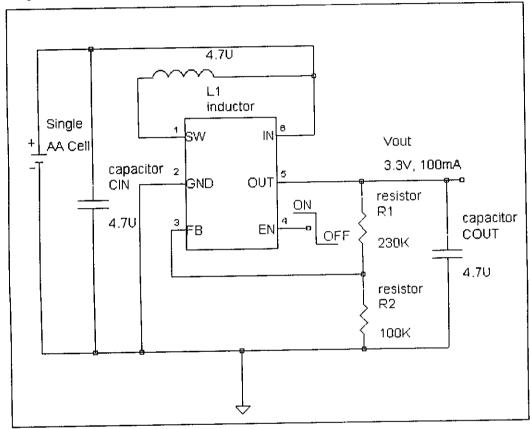

This converter has been practically implemented using 0.5 um single poly double metal processes. The pin configuration and the typical application diagram of the converter have been mentioned in Fig 3.7:

Fig 3.7: The pin configuration & the typical application diagram of the converter

| Name | Pin | Туре              | Function                                                                                                            |

|------|-----|-------------------|---------------------------------------------------------------------------------------------------------------------|

| SW   | 1   | Switch            | Inductor is connected between SW and IN.                                                                            |

| GND  | 2   | Ground            | Ground pin                                                                                                          |

| FB   | 3   | Feedback          | Adjustable feedback input, resistor voltage divider is connected between FB & OUT, to have required output voltage. |

| ĒN   | 4   | Enable            | EN=High: normal operation.                                                                                          |

| OUT  | 5   | Analog<br>output. | Boost regulator output.                                                                                             |

| IN   | 6   | Battery input.    | Boost regulator input.                                                                                              |

# **Chapter 4**

# Implementation of the Proposed Converter

The overall functional blocks can be grouped into the following

categories:

- 1. Supply (bias currents and voltages) related blocks.

- 2. Loop-settling blocks.

- 3. Switches.

- 4. Performance enhancement and safety related blocks.

- 5. Start-up blocks.

- 6. Main Control Block.

Let's have a closer view of the above mentioned categories.

## 4.1Supply related blocks:

These blocks and sub-blocks are responsible for providing necessary bias voltages and currents to all other functional blocks. The supply related blocks are:

#### a) Reference:

Reference block is the heart of all the supply related blocks. This consists of a precise band-gap core. The principle of the band-gap core relies on two groups of transistors running at different emitter current densities. This difference in the current densities cause a difference between the base-emitter voltages, let's call it  $\Delta V_{BE}$ .

From the large signal behavior of the bipolar transistor and neglecting the base current (for high  $\beta_F$ ) of it, we have the following relationship

$$V_{BE1} = \left(\frac{KT}{q}\right) \ln\left(\frac{I_1}{I_{S1}}\right)$$

(4.1)

$$V_{BE2} = \left(\frac{KT}{q}\right) \ln\left(\frac{I_2}{I_{S2}}\right)$$

(4.2)

$$I_{S1} \alpha A_1 \quad \& \quad I_{S2} \alpha A_2$$

(4.3)

and

where,  $I_1 = I_{C1} \cong I_{E1}$ &  $I_2 = I_{C2} \cong I_{E2}$ ,  $I_s \Rightarrow saturation current$ ,  $A \Rightarrow base - emitter junction area of a bipolar transistor.$

$$\therefore \Delta V_{BE} = V_{BE2} - V_{BE1}$$

$$= \left(\frac{KT}{q}\right) \ln\left(\frac{A_1}{A_2}\right)$$

$$= V_T \ln\left(\frac{A_1}{A_2}\right) \qquad (4.4)$$

For  $I_1 = I_2$ , i.e in the balanced condition of the band-gap core.

$$V_T = (\frac{KT}{q})$$

, is called thermal voltage.

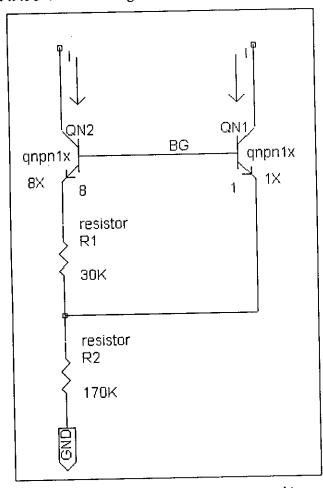

The core, used in the design, has the emitter area ratio of 8:1, i.e.  $A_1:A_2=8:1$  and it is shown in the Fig 4.1.

Fig 4.1: The basic Band-gap core used in the converter.

In the design, the rich transistor will runs at 8 times the density of the lean ones, and a factor of 8 will cause a 54 mv (i.e. 26mv\*ln8) delta between the baseemitter voltages of the two groups. This delta voltage is usually amplified by a factor of about 10 and added to a V<sub>BE</sub> voltage, i.e.

$$I = \frac{\Delta V_{BE}}{R1},$$

$$BG = 2IR2 + V_{BE}$$

$$= 2\Delta V_{BE} \frac{R2}{R1} + V_{BE}$$

$$\therefore BG = 2(54mv) \frac{170K}{30K} + 0.6$$

$$= 1.212V$$

The beauty of the band-gap reference is the weighted summation of the  $V_{BE}$  term, which decreases at the rate of about -2 m.v/°C, and the (delta- $V_{BE}$  term) which grows at about + 2 m.v./°C, to achieve an overall Temperature Coefficient (Tempco) that is substantially zero. As a result, this band-gap voltage remains almost constant with the change in temperature.

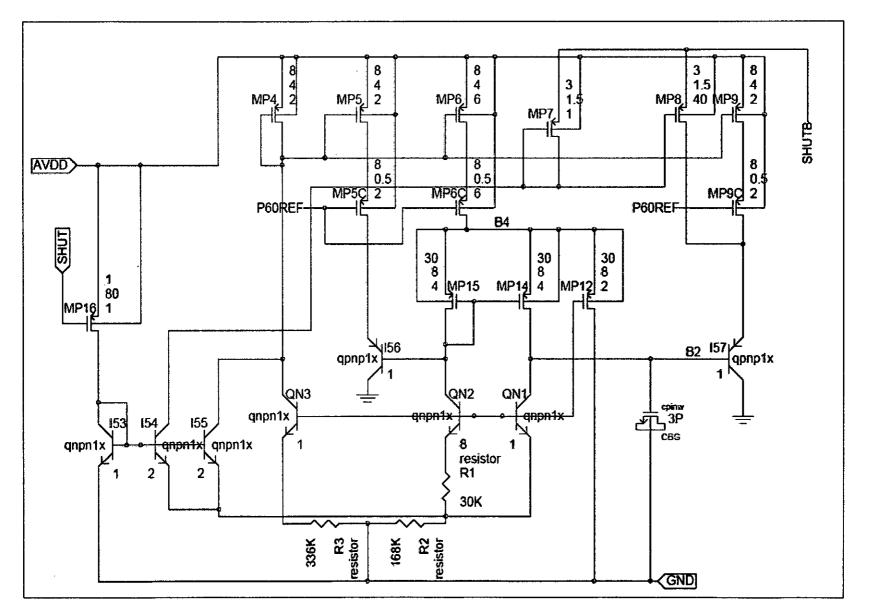

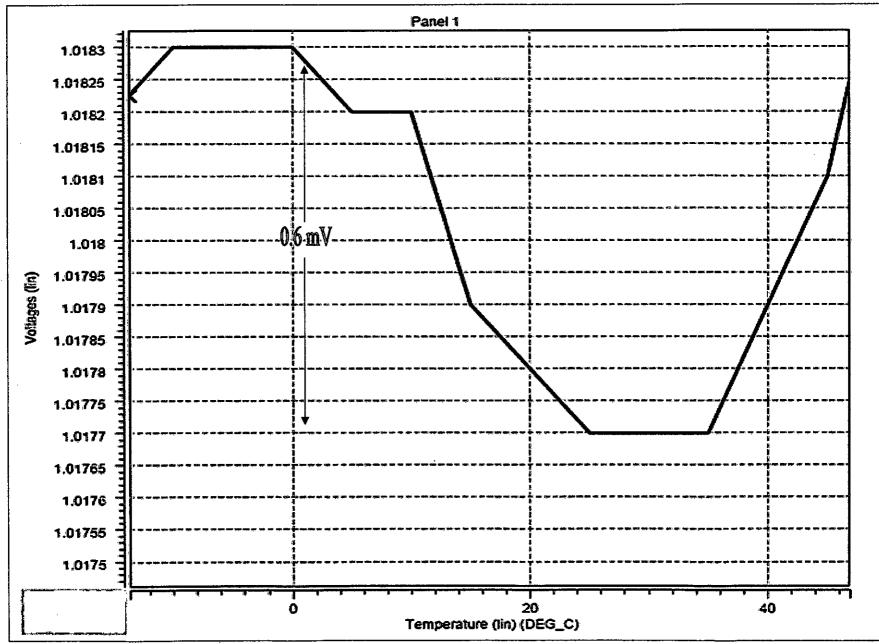

Moreover, this circuit uses a feedback loop to establish an operating point in the circuit such that the output voltage is equal to a  $V_{\text{BE}}$  plus a voltage proportional to the difference between the two base-emitter voltages. If the special measures are not taken, the band-gap circuit halts to other of its two possible solutions i.e. 0 and  $V_{BE}$ . In Fig 4.2, the measures to get rid of those problems have been illustrated. At the beginning of the operation, when the 'SHUT' is released, emitters of 153, 154 and 155 remains at the same potential, as no voltage has been built up. A current (called initial current) set by the ON resistance of MP16, flows from the supply to the base of 153 and its operation is initiated. A 2X current of the initial one is drawn by 154 from the diode connected PMOS MP7. Again, this current of MP7 is amplified 40 times by MP8 and a portion of this huge current is injected to the bandgap core via 157 and thus the core comes out of the zero solution. Similarly, measures have been taken so that the band-gap voltage does not stop at  $V_{BE}$ . The simulation result of the temperature coefficient of the reference voltage has been illustrated in Fig 4.3, it is seen that, the variation of the band-gap voltage is very negligible over room temperature range (Fig 4.3).

Fig 4.2: Techniques to avoid unexpected solutions of Band-gap in the converter

λ.

30

S.

Fig 4.3: The variation of reference voltage with temperature

## b) Bias Current Generating Block:

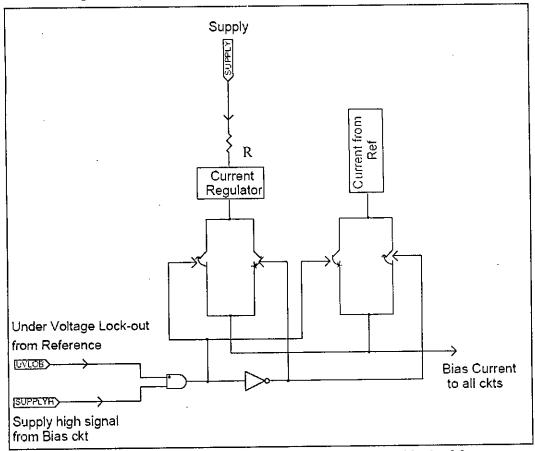

This block provides adjustable bias currents for various functional blocks of the converter based on the operating conditions; i.e. whether the converter is in the start-up mode or in the normal operational mode. The basic structure of the block has been illustrated in Fig 4.4. It also generates signal to indicate if the converter is in the start-up or normal operating-mode. In the start-up mode, a supplybased finely regulated current is provided by this block to have the blocks relevant to this mode to operate smoothly. There are two fail-safe signals available in the converter, one comes from the reference, the under-voltage lock-out signal, that points to the fact that the band-gap voltage is ready and the other comes from this Bias Current Generating Block that indicates if the supply reaches a certain safe limit. When both the conditions are true i.e. the band-gap voltage is ready and the supply has reached a certain safe limit, a logic signal is generated that makes all the operational blocks to take the bias current from the reference block rather than this bias current generating block.

Fig 4.4: Basic structure of the bias-current generating block of the converter.

#### c) Supply Selector:

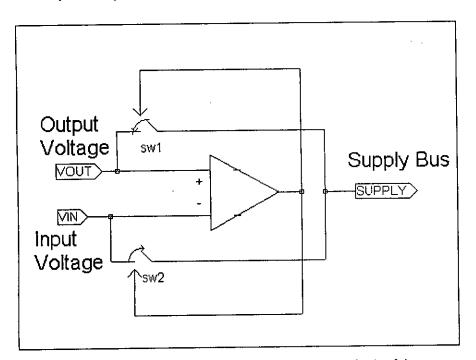

The bias to all the circuitry of the chip is supplied either from the input voltage or from the output voltage depending on the conditions of the two voltages. At the starting, when the output voltage level is building from zero, the bias to the circuitry is provided from the input voltage bus. Once the output voltage builds up enough to exceed the input level, the supply bus is switched to be fed from the output voltage. This facilitates some of the blocks like driver of the switches, error-amplifier etc. to have faster transient response. The aforesaid switching is accomplished by a block called 'Supply Selector'. This circuit is designed to work at the very low voltage level. As shown in Fig 4.5, a comparator checks the two voltage levels. In the beginning of the operation, input voltage is higher. Hence supply bus is fed from the input voltage, the comparator trips causing the switch sw2 to open and sw1 to close. Hence, the supply bus gets connected to the output pin and supply is provided from the output voltage.

Fig 4.5: Basic structure of the supply selector block of the converter.

The comparator used for this purpose has been illustrated in Fig 4.6. A hysteresis has been added to the comparator such that output voltage needs to rise above the input voltage to some extent, to have the 'VOUP' signal of the comparator

'HIGH'. The trans- conductance, gm, of the device POUT is less than that of PIN. Hence the MOS POUT needs more source to gate voltage excursion than that of PIN to have the same  $\Delta i$ , and thus hysteresis is added.

Fig 4.6: The comparator used for the supply selector block of the converter.

Fig 4.7: The switching portion of the supply selector block of the converter.

ļ

The basic switching portion of the block has been illustrated in Fig 4.7. Two MOS switches 'SOUT' and 'SIN' are there to connect VOUT and VIN bus to the VCC bus, based on the condition of the signal ('VOUP') derived from the comparator.

## 4.2 Loop-settling blocks:

The normal loop operation of the step-up regulator is performed by these blocks; an error amplifier and a time generating circuit fall into the category of the loop-settling blocks.

#### a) Error Amplifier:

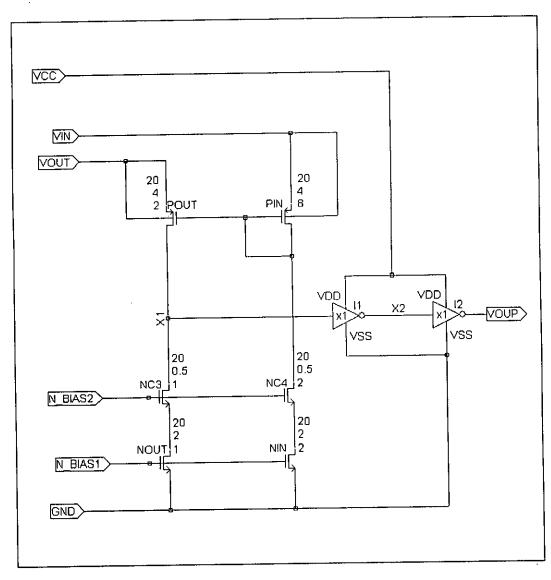

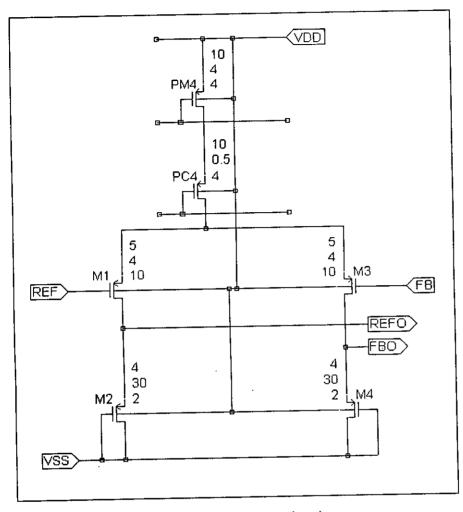

The Error Amplifier block is in fact an open loop uncompensated comparator that takes the band-gap reference voltage, feedback voltage (portion of output voltage taken-off by a suitable resistive divider), the voltage at the switch pin and the output voltage as input signals. This amplifier yields a digital signal called 'charge' that initiates the charging cycle of the boost regulator. The basic structure of the error-amplifier has been illustrated in Fig 4.8. The input differential pair for

Fig 4.8: The basic structure of the error-amplifier of the converter.

REF and FB has been built with MOSFETs and stages of voltage gain have been applied to gain up the differential signal. Differential pairs with gate-drain connected

loads (as shown in Fig 4.9) have been used for the various gain stages in the Avl block in Fig 4.8.

Fig 4.9: A voltage gain stage used in the erroramplifier of the converter.

The differential voltage gain of the pair shown in Fig 4.9 is calculated

as following:

$$A_{v} = g_{m1}R_{out}$$

$$= g_{m1}\left(\frac{1}{g_{m2}}\right)$$

$$= \frac{\sqrt{2I_{12}\beta_{1}}}{\sqrt{2I_{12}\beta_{2}}}$$

Where,  $\beta = \mu_p C_{ox}(W/L)$

$$= \sqrt{\frac{Z_1}{Z_2}}$$

$$= \sqrt{\frac{W_1}{L_1}}$$

$$= \sqrt{\frac{\frac{W_1}{W_2}}{\frac{W_2}{L_2}}}$$

$$= \sqrt{\frac{50}{\frac{4}{15}}}$$

$$= 6.85$$

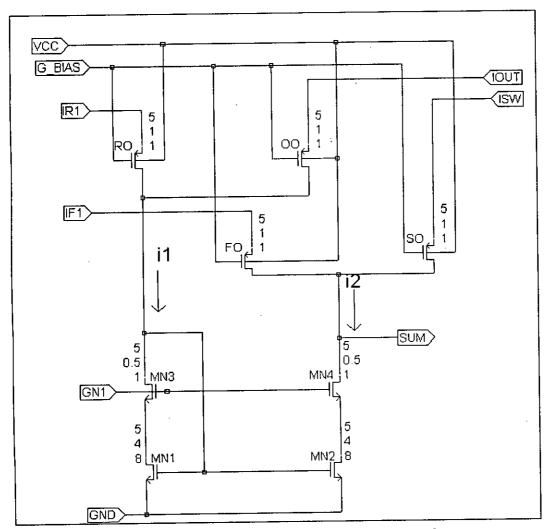

Hence, if the difference between the signal REF and FB is 10mV, the difference between the signal REFO and FBO will be 68.5mV. Another stage cascaded with this stage, will further amplify the difference. In this way, the Avl block will gain up the difference between the input signals. After amplification in the Av1 block, two more signals are found at R1 and F1 nodes and these node voltages are then converted into current signals by trans-conductance blocks, gm1 yielding IR1 and IF1 respectively. The difference between these two signals produces 'Error Signal'. The voltage signals at the SW and OUT pins are directly converted to current signals using similar trans-conductance blocks, without any sort of amplification. The difference between these two current signals will produce 'Current sense signal' (Fig 4.8). Before obtaining 'Error signal' the difference between the reference and feedback voltage has been amplified, whereas, the voltage at SW and OUT pins are directly converted to current signals. Hence, the 'Current sense signal' has more linearity than the 'Error signal'. Moreover, as the number of the stages from reference and feedback nodes to the summing node is larger than that from SW and OUT nodes to the same point, the response of the 'Current sense signal' is faster than that of the 'Error signal', on pulse by pulse basis. This ensures the path of the current signal to be faster than that of the voltage signal. This has been done intentionally, as it is one of the requirements for a loop, having another loop inside it, to be stable. The 'Current sense signal' and the 'Error signal' are then algebraically summed and the resultant signal is converted to a voltage signal by a 1/Gm block (as shown in Fig 4.8). As shown in Fig 4.10, the current signals have been added on the basis of the

O:  $\cdot$

Fig 4.10: Addition of current signals & transformation of current signals to a voltage signal in the error amplifier of the converter.

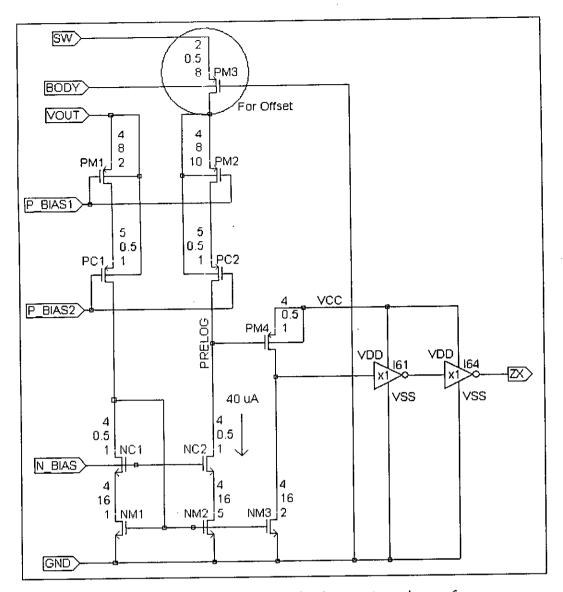

required polarity of the signals corresponding to reference, feedback, switch and output voltages. The node 'SUM' is a high impedance node and therefore, a small difference between i1 and i2 will cause the node to move to a huge quantity, based on the polarity of the difference. And finally, the 'SUM' signal is gained up, using a single stage gain block, Av2, as shown in Fig 4.11. The single stage gain block is, in fact, a basic CMOS inverter, where one device serves as a common-source amplifier (NM2) and the other device acts as an active load (PM1). NC2 and PC1 are NMOS and PMOS cascode devices used to reduce the transient response time of the node 'PRELOGIC' by minimizing the effect of the parasitic gate-source and gate-drain capacitances associated with NM2 and PM1. Among these, the gate-drain capacitance is the most troublesome due to the Miller effect. Since the

Fig 4.11: The single stage gain block used in the error amplifier of the converter.

Miller-effect capacitance reflected to the input depends on the voltage gain at the drain of NM2; it can be kept low by making  $(W/L)_{nm2} \approx (W/L)_{nc2}$ , as it is evident from the equation (4.5). Neglecting the body effect, the voltage gain from the point 'SUM' to the drain of NM2, in Fig 4.10, we have the following relationship:

$$A_{vd} \approx -\frac{gm_{nm2}}{gm_{nc2}} = -\sqrt{\frac{(W/L)_{nm2}}{(W/L)_{nc2}}}$$

(4.5)

Moreover, the cascode connection increases the output impedance by a certain factor. Considering that, both NC2 and NM2 operate in active region, with  $I_D$  = 3uA and  $V_A$  = 50V, we have the output resistance  $r_0$  of each transistor given by,

$$r_{0} = \frac{V_{A}}{I_{D}} = \frac{50}{3 \times 10^{-6}} = 16.67 M\Omega$$

Now, if the resistance looking into the drain of NC2 is  $R_{\theta 2}$ , we have the following relationship:

(4.6)

$$R_{02} = r_{0nc2} (1 + gm_{nc2} r_{0nm2}) + r_{0nm2}$$

Hence, using the values for the parameters, we 've from the equation (4.6),

$$R_{02} = 16.67 \times 10^{6} \times \left(1 + \sqrt{(2 \times 3 \times 10^{-6} \times 60 \times 10^{-6} \times 10)} \times 16.67 \times 10^{6}\right) + 16.67 \times 10^{6}$$

= 16.7 GΩ

Hence voltage gain  $A_v$  from the node 'SUM' to 'PRELOGIC' is given

bу

$$A_{v} = gm_{nm2} \times R_{02}$$

=  $\sqrt{(2 \times 3 \times 10^{-6} \times 60 \times 10^{-6} \times 8)} \times 16.7 \times 10^{\circ}$

= 896.2

Therefore, a small excursion of the 'SUM' signal is gained up to the rail-to-rail excursion using this stage.

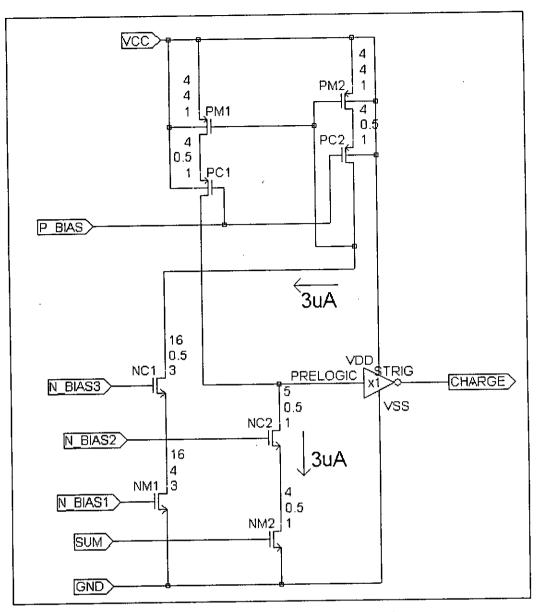

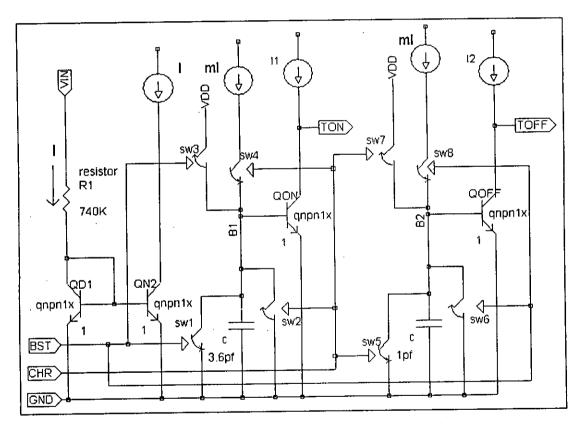

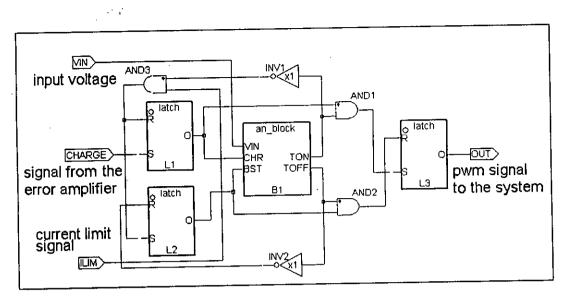

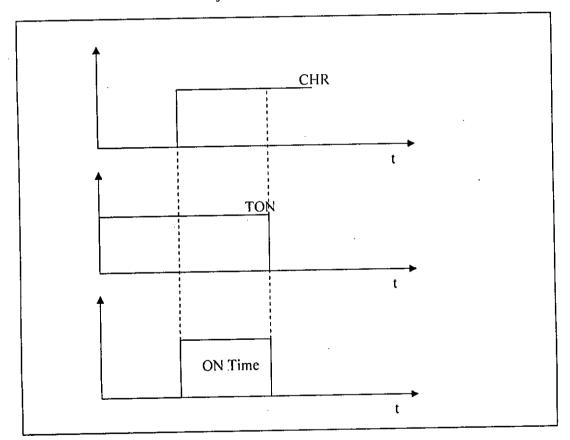

#### b) Time Generator:

Time generator generates the ON time that is inversely proportional to the input voltage and the minimum OFF time. Moreover, it controls the duration of the charge and the boost phases based on different conditions of the overall chip. Time generator can be divided into two parts; 1) Analog Part & 2) Logic Part.

The Analog Part has been shown in Fig 4.12. The basic principle of this time generation process depends on the well known property of a capacitor, being charged by a current source. We know, for a capacitor of capacitance C, being charged by a fixed current I, meets the following condition:

$$\frac{I}{C} = \frac{\Delta V}{\Delta t} \tag{4.7}$$

Considering the generation of ON time, when CHR signal is TRUE (BST signal is FALSE, simultaneously) the switches SW1, SW2 & SW3 will be opened and the switch SW4 will be closed. As a result, the capacitor c(=3.6pf) will be charged by the constant current mI. A ramp, starting from 0, will be generated at the node B1. At that span of time, the node TON will be pulled to a high voltage (supply). When this ramp exceeds the base-emitter voltage of QON, it will turn ON and will pull down the node TON. Now ON time will be the span of time from the instant CHR signal becoming TRUE to the instant QON turning ON (as illustrated in the timing diagram in Fig 4.14). The current I is generated as:

$$I = \frac{V_{IN} - V_{BE}}{R_{I}}$$

$$\Rightarrow I \alpha V_{IN}$$

(4.8)

(4.9)

Again, rewriting equation (4.7), in terms of  $V_{BE}$  and  $T_{on}$ , we

have

$$\frac{I}{C} = \frac{V_{BE}}{T_{on}}$$

$$\Rightarrow T_{on} = \frac{CV_{BE}}{I}$$

$$\Rightarrow T_{on} \alpha \frac{1}{I}$$

(4.10)

Hence, from the equations (4.9) and (4.10) we have the following

(4.11)

relationship:

$T_{on} \alpha \frac{1}{V_{IN}}$

The relationship in equation (4.11) is one of the unique features of the loop in normal operation.

Fig 4.12: The analog part of the time-generator block of the converter.

Fig 4.13: The overall time-generator block of the converter.

Fig 4.14: The ON time to be extracted in time-generator block of the converter.

••••

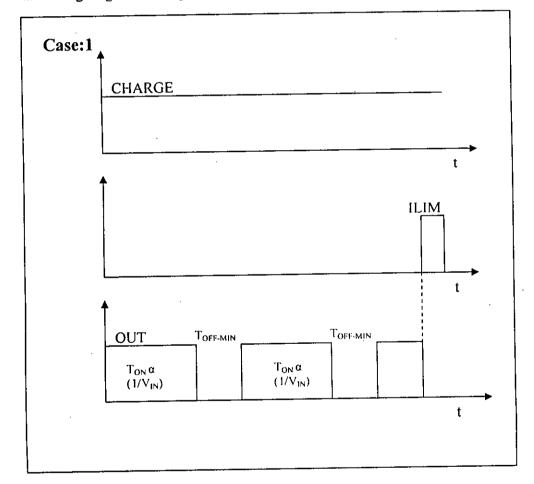

On the other hand, the digital part, consisting of some asynchronous latches and logic gates, converts the signal, generated discretely on TON and TOFF nodes, to the PWM signal as required by the system depending on all the prevailing conditions, e.g. the conditions when the current-loop breaks or when the peak current through the inductor reaches the current limit or when the converter runs at the discontinuous conduction mode etc. The asynchronous latches are actually reset dominant flip-flops.

Depending upon the signal from the error-amplifier i.e. 'charge' in the Fig 4.13, the whole Time Generator block produces necessary signals for the system. Based on some conditions of the 'charge' signal, the results have been illustrated in the timing diagrams on Fig 4.15 & Fig 4.16.

Fig 4.15: The output signal, in time unit, for open loop operation of the time generator block of the converter.

# Fig 4.16: The output signal, in time unit, for normal loop operation of time generator block of the converter.

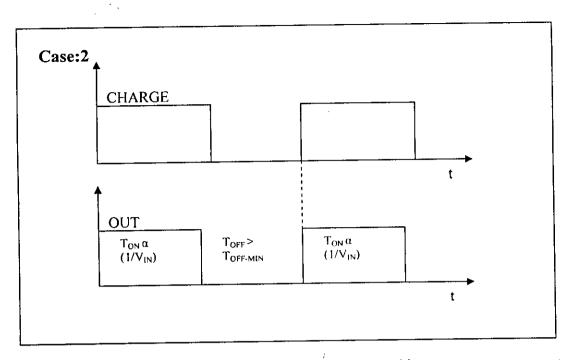

As shown in Fig 4.15, (case:1) the error-amplifier has produced a prolonged 'charge' signal, which takes place at the open-loop condition. As a result, the time-generator block is producing timing signal of ON time inversely proportional to the input voltage and OFF time equal to the minimum off time of the block. As soon as the current limit is hit, ON time terminates. In Fig 4.16 (case:2), the error-amplifier is producing regular signal, which is the case for normal loop operation. Hence, the time-generator block is producing timing signal of ON time inversely proportional to the input voltage but now OFF time is the required OFF time needed to have the expected duty cycle and of course, this OFF time is greater than the minimum OFF time of the block.

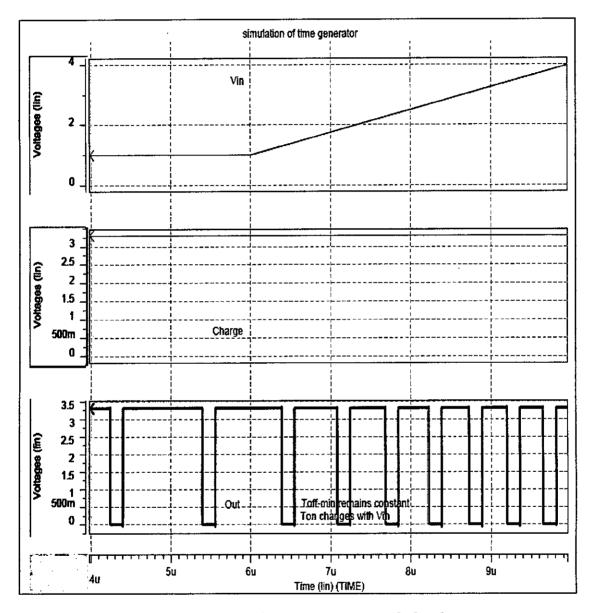

A real time transient simulation result has been shown in Fig 4.17. A prolonged 'Charge' signal has been applied and the input voltage has been swept from IV to 4V. As a result, the Time Generator block will run at the minimum OFF time ( $T_{off-min}$ ), which is invariant of the input voltage, and the ON time ( $T_{on}$ ) will decrease with the increase of the input voltage.

••

Fig 4.17: Simulation result of the time generator with the change in input voltage

From Fig 4.17, it is evident that the minimum OFF time is 150 nS and this time is retaining its value though the ON time is changing with the input voltage.

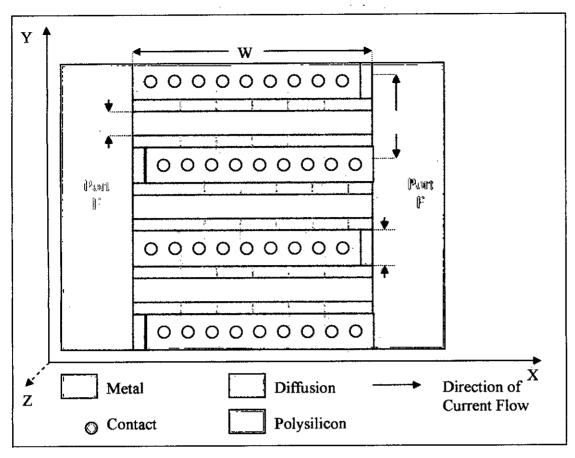

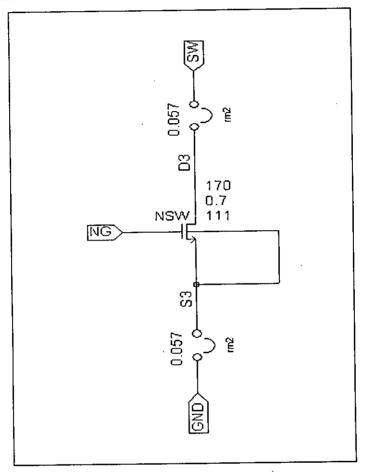

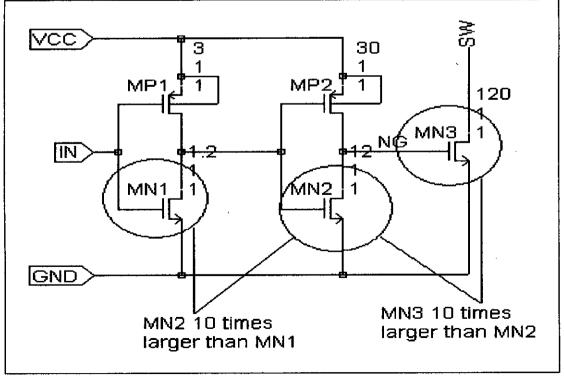

## 4.3 Switches:

This converter is a synchronous boost regulator. Hence two switches, namely NSW (NMOS switch) and PSW (PMOS switch), are switched alternately for the charge and the boost phase, respectively. Since most of the silicon area is used up for the two power devices, it is required to optimize the given silicon area for the efficient operation of the converter. In designing of the switches several factors are taken into account:

a). Total resistance,

b). the percentage of channel resistance in total resistance,

c). the current carrying capability of each segment of the switch.

In order to increase the efficiency of the converter, one of the requirements is to reduce the  $I^2R$  loss of the switches and for that purpose the total resistance of the switch needs to be reduced. Total resistance includes channel resistance, parasitic resistances of metal layers, metal to metal contact, metal to diffusion contact and diffusion resistance. However, this reduction, for a given silicon area, depends on some parameters like the aspect ratio of the switches, orientation of the switches, the pitch of the segments, the number of metal layers, the number of contacts among different metal layers or between metal layer and diffusion etc.

We want to have the total resistance dominated by the channel resistance, as it is the more predictable part than any other sorts of resistance of the switch. The channel resistance, as we know, is derived by the following relationship:

$$R_{ch} = \frac{1}{\beta(V_{gs} - V_{t})}$$