**M. Sc. Engineering Thesis**

## Linear Time Algorithms for Floor-Planning and Routing Problems

by

A. K. M. Azad

#### Submitted to

Department of Computer Science and Engineering in partial fulfillment of the requirements for the degree of M. Sc. Engineering (Computer Science and Engineering)

Department of Computer Science and Engineering (CSE) Bangladesh University of Engineering and Technology (BUET) Dhaka-1000, Bangladesh

August 27, 2005

С

# Linear Time Algorithms for Floor-Planning and Routing Problems

#### A thesis submitted by

### A. K. M. Azad Student No. 9605039P

#### For the partial fulfillment of the degree of M. Sc. Engineering (Computer Science and Engineering) Examination held on August 27, 2005

Approved as to style and contents by:

Dr. Md. Abul Kashem Mia Professor Department of Computer Science and Engineering BUET, Dhaka-1000, Bangladesh

Dr. Md. Shamsul Alam Professor and Head Department of Computer Science and Engineering BUET, Dhaka-1000, Bangladesh

Dr. Md. Saidur Rahman Assistant Professor Department of Computer Science and Engineering BUET, Dhaka-1000, Bangladesh

Md. Elics

Dr. Md. Elias Associate Professor Department of Mathematics BUET, Dhaka-1000, Bangladesh Chairman and Supervisor

Member (Ex-officio)

Member

Member (External)

## Certificate

This is to certify that the work presented in this thesis paper is the outcome of the investigation carried out by the candidate under the supervision of Dr. Md. Abul Kashem Mia in the Department of Computer Science and Engineering, Bangladesh University of Engineering and Technology, Dhaka-1000. It is also declared that neither of this thesis nor any part thereof has been submitted or is being concurrently submitted anywhere else for the award of any degree or diploma.

Signature of the Supervisor

Signature of the Author

# Contents

à,

| Contents                                              | i              |

|-------------------------------------------------------|----------------|

| List of Figures                                       | iv             |

| Acknowledgement                                       | vii            |

| Abstract                                              | 1              |

| 1. Introduction                                       | 2              |

| 1.1 VLSI Design Cycle                                 | 2              |

| 1.2 Physical Design Cycle                             | 4              |

| 1.2.1 Partitioning                                    | 4              |

| 1.2.2 Floorplanning                                   | 5              |

| 1.2.3 Routing                                         | 5              |

| 1.3 Traditional Approach of Floorplanning and Routing | <sup>.</sup> 6 |

| 1.4 Objectives of this thesis                         | 7              |

| 1.5 Organization of this thesis                       | 10             |

| 2. Preliminary                                        | 11             |

| 2.1 Basic Terminology                                 | 11             |

| 2.1.1 Graphs and Multigraphs                          | 11             |

| 2.1.2 Subgraphs                                       |                |

| 2.1.3 Weighted Graphs                                 | 13             |

| 2.1.4 Paths, Distances and Cycles                     | 13             |

| 2.1.5 Connectivity                                    | 14             |

| 2.1.6 Planar Graph                                    | 14             |

| 2.1.7 Trees                                           | 15             |

| 2.2 Graph Drawing Conventions                         | 16             |

.

.

| 2.2.1 Orthogonal Graph Drawing                                         | 16 |

|------------------------------------------------------------------------|----|

| 2.2.2 Box-orthogonal Graph Drawing                                     | 17 |

| 2.2.3 Rectangular Graph Drawing                                        | 18 |

| 2.2.4 Box-rectangular Graph Drawing                                    | 18 |

| 2.2.5 Grid Drawing                                                     | 19 |

| 2.3 Some Known Results on Orthogonal Graph Drawing                     | 20 |

|                                                                        |    |

| 3. Floorplanning and Global Routing                                    | 24 |

| 3.1 Intorduction                                                       | 24 |

| 3.1.1 Traditional Approach of Floorplanning and Routing                | 26 |

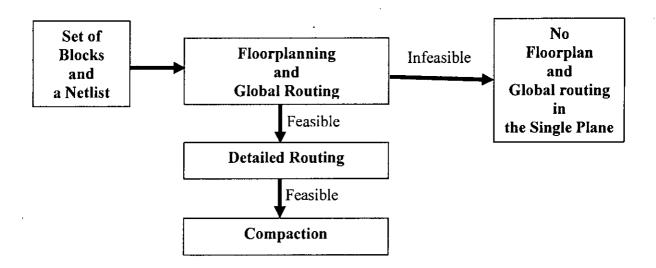

| 3.1.2 Our Integrated Approach of Floorplanning and Routing             | 27 |

| 3.2 Integrated Floorplanning and Global Routing                        | 28 |

| 3.2.1 Representing Circuit using Multi-graph                           | 29 |

| 3.2.2 Converting Multigraph into a 3-graph                             | 30 |

| 3.2.3 Handling Multi-terminal Net                                      | 33 |

| 3.2.4 Handling Multi-headed Pin                                        | 34 |

| 3.2.5 Orthogonal Drawing of plane 3-graph                              | 35 |

| 3.2.6 The Overall Process of Getting Floorplan and Global Routing      | 39 |

| 3.3 Time Complexity of the Integrated Floorplanning and Global Routing | 45 |

|                                                                        |    |

|                                                                        |    |

| 4. Detailed Routing                                                    | 47 |

| 4.1 Introduction                                                       | 47 |

| 4.2 Detailed Routing Algorithm                                         | 47 |

| 4.2.1 Classifying Vertices into Left and Right                         | 49 |

| 4.2.2 Finding Routing Parameters                                       | 53 |

| 4.2.2.1 Finding Routing Parameters for Right Vertices                  | 54 |

| 4.2.2.2 Finding Routing Parameters for Left Vertices                   | 57 |

| 4.2.2.3 Minimizing Routing Parameters                                  | 59 |

| 4.2.3 Bending the Edges                                                | 64 |

.

#### for the second s

| 5. Conclusion   | 71 |

|-----------------|----|

| 6. Bibliography | 74 |

| 7. Index        | 77 |

# **List of Figures**

## Chapter 1

| Figure 1.1: A Simple VLSI Design Cycle                                 | 3 |

|------------------------------------------------------------------------|---|

| Figure 1.2: Partitioning into three blocks                             | 4 |

| Figure 1.3: Circuit blocks and pins after floorplanning                | 5 |

| Figure 1.4: Global routing.                                            | 6 |

| Figure 1.5: Detailed routing.                                          | 6 |

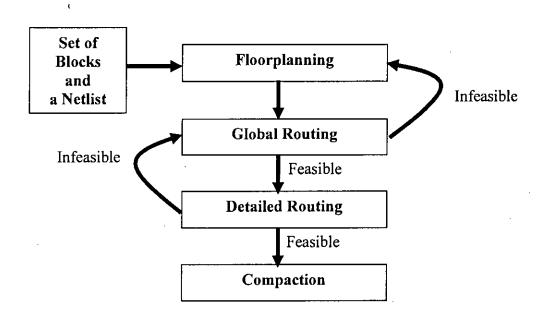

| Figure 1.6: Traditional approach of floorplanning and routing          | 7 |

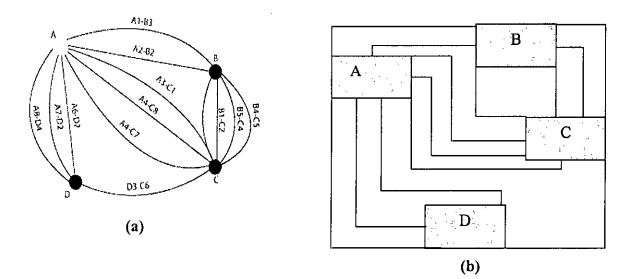

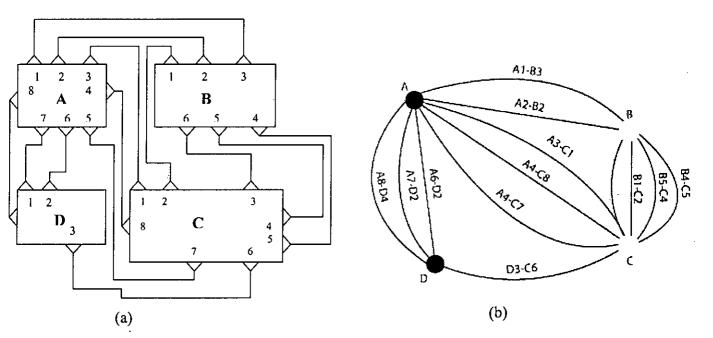

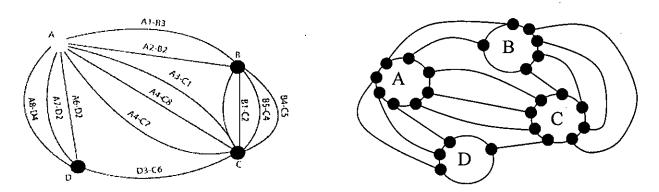

| Figure 1.7: (a) A circuit C (set of blocks and their interconnections) | 8 |

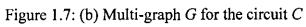

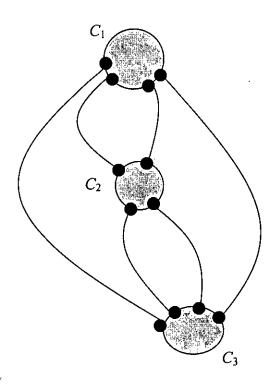

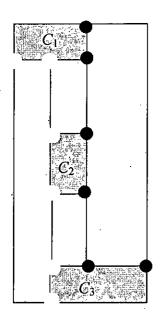

| Figure 1.7: (b) Multi-graph G for the circuit C                        | 8 |

| Figure 1.7: (c) A 3-graph G' equivalent to G                           | 8 |

| Figure 1.7: (d) Floorplanning and global routing for circuit $C$ using |   |

| orthogonal graph drawing                                               | 9 |

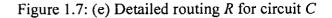

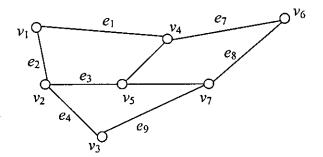

| Figure 1.7: (e) Detailed routing R for circuit C                       | 9 |

|                                                                        |   |

· ·

### Chapter 2

2

| Figure 2.1: A simple graph                                                    | 11 |

|-------------------------------------------------------------------------------|----|

| Figure 2.2: Subgraphs of G in Fig. 2.1: (a) vertex-induced and (b) edge-      |    |

| Induced subgraph.                                                             | 12 |

| Figure 2.3: A weighted graph with five vertices                               | 13 |

| Figure 2.4: $C_1$ and $C_3$ are two 3-legged cycles                           | 14 |

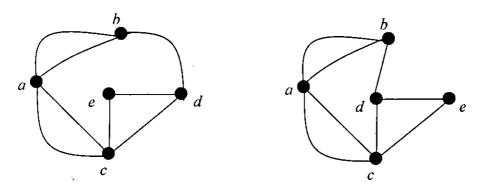

| Figure 2.5: Two plane graph of a same planar graph                            | 14 |

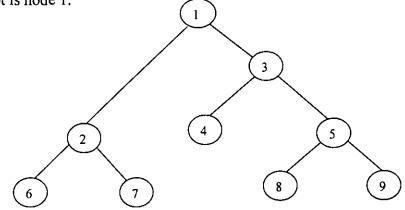

| Figure 2.6: A binary tree with 9 vertices.                                    | 15 |

| Figure 2.7: (a) A plane graph $G$ , (b) an orthogonal drawing of $G$ with 6   |    |

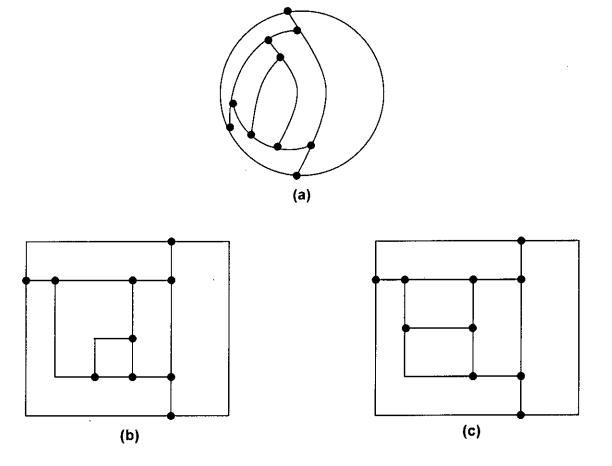

| bends, (c) an orthogonal drawing of G with 5 bends                            | 17 |

| Figure 2.8: (a) A plane multi-graph $G$ , (b) A box-orthogonal drawing of $G$ | 18 |

| Figure 2.9: A rectangular graph drawing                                       | 18 |

| Figure 2.10: A Box-Rectangular Graph Drawing                                  | 19 |

| Figure 2.11: A Grid Drawing                                                   | 19 |

a.

| Figure 2.12: (a) 2-legged cycles                                                 | 20 |

|----------------------------------------------------------------------------------|----|

| Figure 2.12: (b) 3-legged cycles                                                 | 20 |

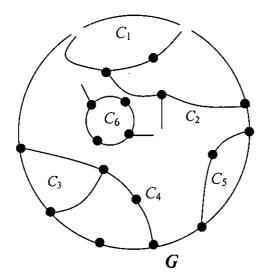

| Figure 2.13: The maximal bad cycles $C_1$ , $C_4$ , $C_5$ and $C_6$ in graph $G$ | 21 |

| Figure 2.14: (a) A plane graph $G$ , (b) Three biconnected components of $G$     | 22 |

| Figure 2.15: BC-tree of the graph G of figure 2.16                               | 23 |

## Chapter 3

| Figure 3.1: Circuit blocks and pins after floorplanning                                | 25 |

|----------------------------------------------------------------------------------------|----|

| Figure 3.2: Global routing                                                             | 26 |

| Figure 3.3: Detailed routing                                                           | 26 |

| Figure 3.4: Traditional approach of floorplanning and routing                          | 27 |

| Figure 3.5: Our integrated approach of floorplanning and routing                       | 28 |

| Figure 3.6: (a) A circuit specification, (b) A multi-graph $G$ for the circuit         | 29 |

| Figure 3.7: Clockwise orientation of pins and vertices                                 | 31 |

| Figure 3.8: (a) Original multi-graph G, (b) 3-graph G'                                 | 31 |

| Figure 3.9: (a) A circuit specification                                                | 32 |

| Figure 3.9: (b) Multi-graph G for the circuit                                          | 32 |

| Figure 3.9: (c) A 3-graph G'                                                           | 33 |

| Figure 3.10: A multi-terminal net                                                      | 33 |

| Figure 3.11:Representing multi-terminal net (a)in multi-graph, (b) in 3-graph          | 34 |

| Figure 3.12: Replacing multi-headed pin by a multi-terminal net                        | 34 |

| Figure 3.13: (a) In-cut vertices v at a concave corner and v'at a non-corner,          |    |

| (b) Out-cut vertices $v$ at a convex corner and $v'$ at a non-                         |    |

| corner                                                                                 | 35 |

| Figure 3.14: Embedding of $v_t$ when $B_x$ is a biconnected component and $B_{t+1}$ is |    |

| a weakly biconnected component.                                                        | 36 |

| Figure 3.15: Embeddings of $v_t$ when both $B_x$ and $B_{i+1}$ are weakly biconnected  |    |

| components                                                                             | 37 |

| Figure 3.16: Embeddings of $v_t$ when $B_x$ is a weakly biconnected component          |    |

| and $B_{i+1}$ is a biconnected component.                                              | 37 |

| Figure 3.17: (a) A plane 3-graph $G$ , (b) Three biconnected components $H_1$ , |    |

|---------------------------------------------------------------------------------|----|

| $H_2$ and $H_3$ , (c) BC-tree for G, (d) Minimum bend orthogonal                |    |

| drawing of $H_1$ , $H_2$ and $H_3$ , (e) Orthogonal drawing of G                | 38 |

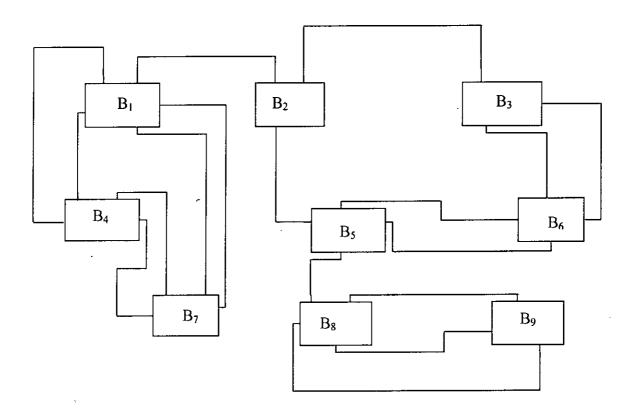

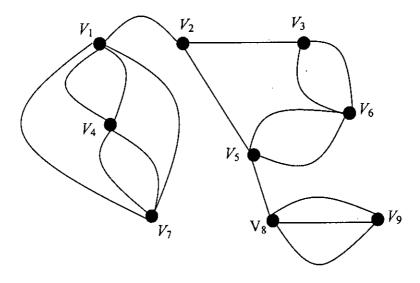

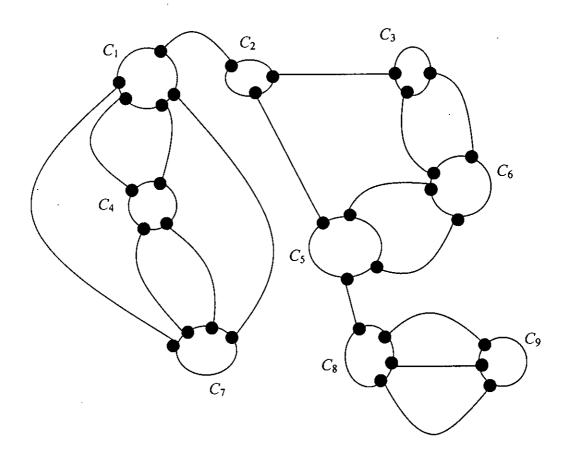

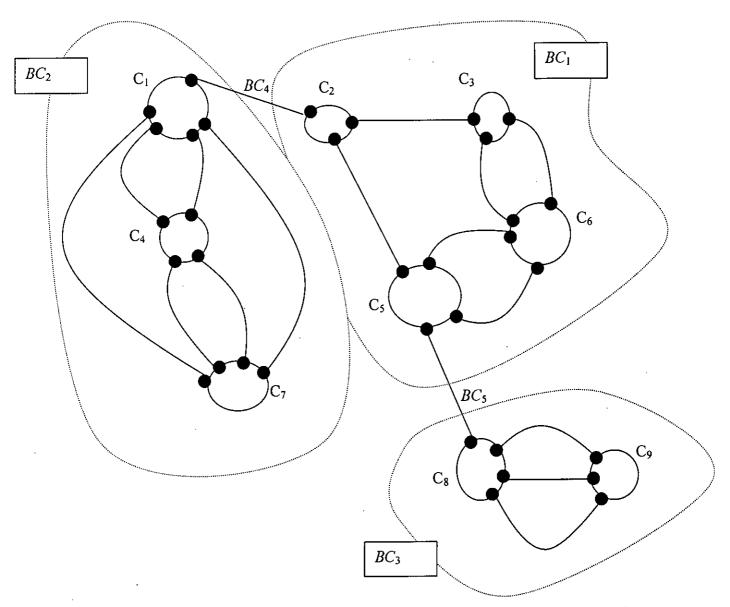

| Figure 3.18: (a) Circuit Specification.                                         | 39 |

| Figure 3.18: (b) Multi-graph G for the circuit.                                 | 40 |

| Figure 3.18: (c) A 3-graph G'                                                   | 40 |

| Figure 3.18: (d) Biconnected components $BC_1$ , $BC_2$ , $BC_3$ and weakly bi- |    |

| connected components $BC_4$ and $BC_5$                                          | 41 |

| Figure 3.18: (e) BC-tree for the 3-graph $G'$ .                                 | 41 |

| Figure 3.18: (f) Orthogonal drawing of biconnected component $BC_1$             | 42 |

| Figure 3.18: (g) Orthogonal drawing of biconnected component $BC_{2}$           | 42 |

| Figure 3.18: (h) Orthogonal drawing of biconnected component $BC_3$             | 43 |

| Figure 3.18: (i) Orthogonal drawing for the 3-graph G'                          | 43 |

## Chapter 4

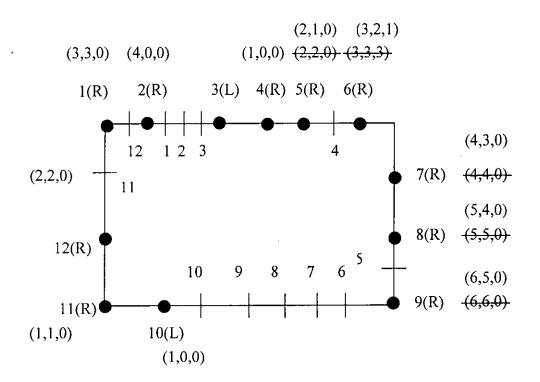

| Figure 4.1: Classification of vertices (Case-1)                        | 50 |

|------------------------------------------------------------------------|----|

| Figure 4.2: Classification of vertices (Case-2)                        | 51 |

| Figure 4.3: Classification of vertices (Case-3)                        | 52 |

| Figure 4.4: Illustration of vertex classification                      | 53 |

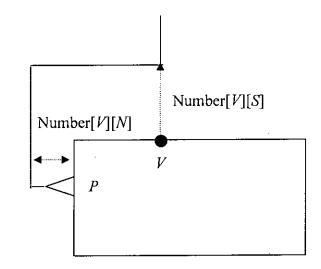

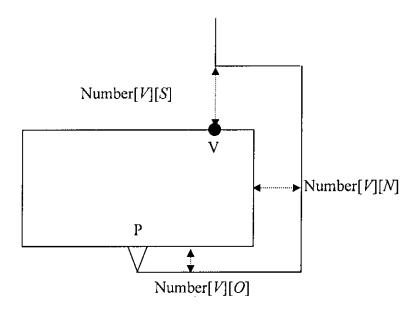

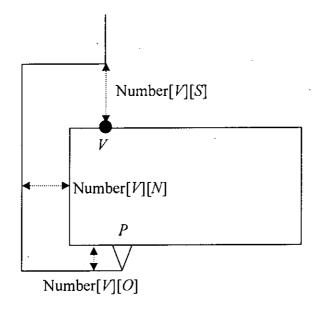

| Figure 4.5: Illustration of (S, N, O) tuple                            | 54 |

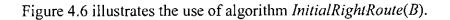

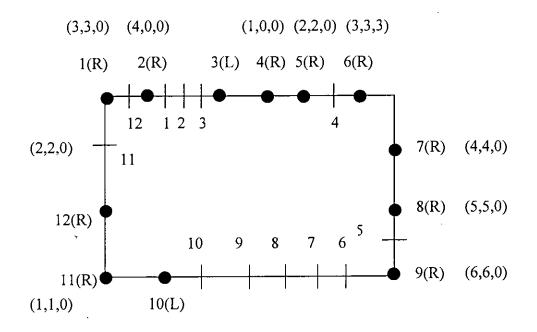

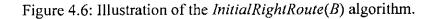

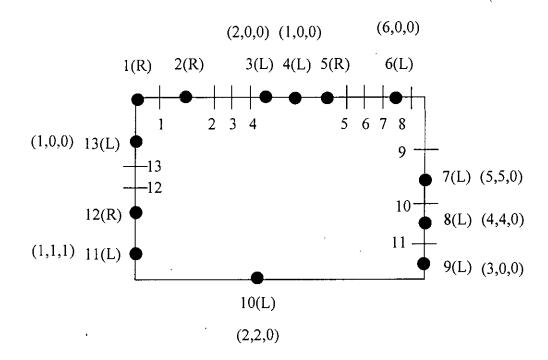

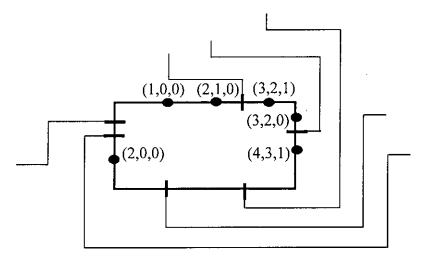

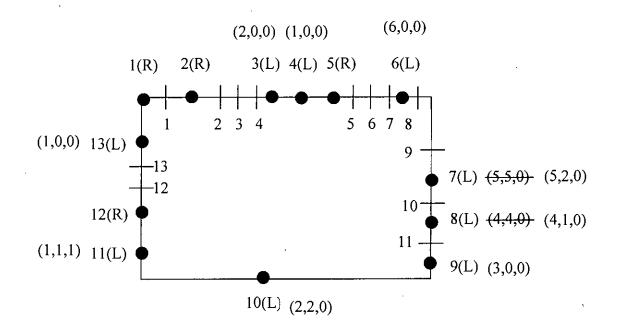

| Figure 4.6: Illustration of the <i>InitialRightRoute</i> (B) algorithm | 56 |

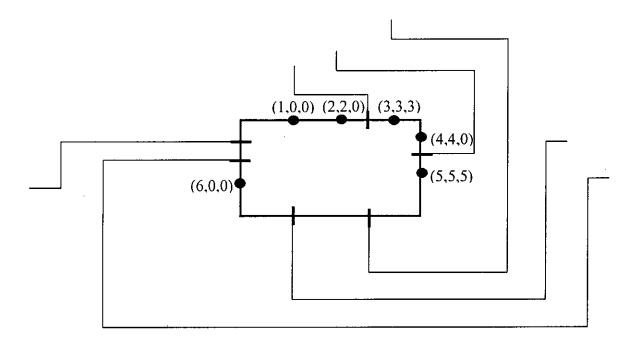

| Figure 4.7 Illustration of the InitialLeftRoute (B) algorithm          | 59 |

| Figure 4.8: (a) Routing parameters before minimization                 | 60 |

| Figure 4.8: (b) Routing parameters after minimization                  | 60 |

| Figure 4.9: Illustration of the <i>MinimizeRightRoute(B)</i> algorithm | 61 |

| Figure 4.10: Illustration of the <i>MinimizeLeftRoute(B)</i> algorithm | 63 |

| Figure 4.11: V and P both are on line $L_1$                            | 65 |

| Figure 4.12: V is on $L_1$ and P is on $L_2$                           | 66 |

| Figure 4.13: V is on $L_1$ and P is on $L_4$                           | 66 |

| Figure 4.14: V is on $L_1$ , P is on $L_3$ and V is a right vertex     | 67 |

| Figure 4.15: V is on $L_1$ and P is on $L_3$ and V is left vertex      | 68 |

|                                                                        |    |

# Acknowledgement

First and foremost, I would like to acknowledge my gratitude to Dr. Md. Abul Kashem Mia, Professor, Department of Computer Science and Engineering, Bangladesh University of Engineering and Technology. His constant supervision, scholarly guidance, valuable advice and encouragement have been a great impetus to this thesis work. I would also like to acknowledge my gratitude to Dr. Md. Saidur Rahman, Associate Professor, Department of Computer Science and Engineering, Bangladesh University of Engineering and Technology. His vast experience and in-depth knowledge in graph theory has helped significantly to achieve a smooth completion of this thesis work. He gives me valuable guide lines through out the thesis work.

I would like to thank the members of the graduate committee, Dr. Md. Shamsul Alam, Head and Professor, Department of Computer Science and Engineering, BUET, and Dr. Md. Elias, Associate Professor, Department of Mathematics, BUET, for their valuable suggestions.

I would like to acknowledge the all-out co-operation and services rendered by the faculty members and staffs of the CSE Department. Finally, I also express my ever gratefulness to all who contributed to this thesis work.

## Abstract

The designer of an integrated circuit (IC) transforms a circuit description to a geometric description, called the VLSI layout. The task of converting the specification of an electrical circuit into a layout is called the physical design. In physical design cycle a circuit specification is converted into a VLSI layout in the four phases: partitioning, floorplanning, routing (global routing and detailed routing) and compaction. A large circuit is divided into a set of smaller blocks and the interconnections (nets) between them in the partitioning phase. Each block is then placed (floorplanning phase) in a plane so that interconnections can be routed (routing phase) through the remaining space. Most of the works that appear in the literature deal floorplanning and global routing in two different phases. Although there are some linear time floorplanning algorithms, but the known best algorithms for global routing and detailed routing run in  $O(N^2)$  time, where N is the number of given nets. In this thesis, we present an integrated algorithm based on orthogonal drawing of plane graph that handle floorplanning and global routing in a single phase. The time complexity of our algorithm is linear. We also develop a linear time detailed routing algorithm.

## **Chapter 1**

## Introduction

Integrated Circuit (IC) has transformed our society into an information society. This revolutionary development and widespread use of ICs has been one of the greatest achievements of mankind. Since its inception in 1960's, IC technology has evolved from integration of a few transistors in *Small Scale Integration (SSI)* to integration of millions of transistors in *Very Larger Scale Integration (VLSI)* chips currently in use. ICs consist of a number of electronic components, built by layering several different materials in a well-defined fashion on a silicon base called *wafer*. The designer of an IC transforms a circuit description into a geometric description, called the *layout*. The process of converting the specification of an electrical circuit into a layout is called the *Physical Design Cycle*. Due to the tight tolerance requirements and the extremely small size of individual components, physical design is an extremely tedious and an error prone process. As a result, almost all phases of physical design extensively use *Computer Aided Design (CAD)* tools and many phases have already been partially or fully automated.

### 1.1 VLSI Design Cycle

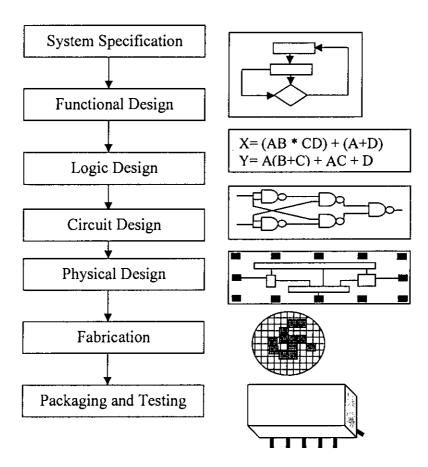

The VLSI design cycle starts with a formal specification of a VLSI chip, follows a series of steps, and eventually produces a packaged chip. A typical design cycle may be represented by the flow chart shown in Figure 1.1.

System specification is a high level representation of the system. The factors to be considered in this process include: performance, functionality and the physical dimensions. It is a compromise between market requirements, technological and economical viability.

Figure 1.1: A Simple VLSI Design Cycle

In functional design step, main functional units and different parameters of the system are identified. This step also identifies the communications between the units.

In logic design, the control flow, word widths, register allocation, arithmetic operation and logic operations of the design that represent the functional design are derived and tested.

The purpose of the circuit design is to develop a circuit specification based on the logic design.

In physical design, the circuit specification is converted into a geometric representation called *layout*:

Layout data is converted into photolithographic *masks* during fabrication. Mask identifies spaces on the wafer, where a certain material needs to be deposited, diffused or even removed.

3

Fabricated chip is then packaged and tested to ensure that it meets all design specifications and that it functions properly.

#### **1.2 Physical Design Cycle**

Physical design is a very complex process and therefore it is usually broken into various sub steps. The input to the physical design cycle is a circuit specification and the output is the layout of the circuit. This is accomplished in several stages such as *Partitioning*, *Floorplanning*, *Routing* and *Compaction*.

#### 1.2.1 Partitioning

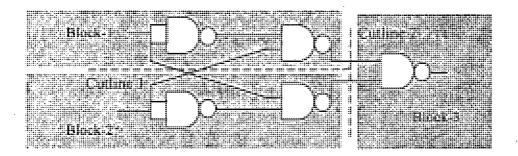

Figure 1.2: Partitioning into three blocks

The input to physical design cycle is a circuit design and output is the layout of the circuit which is later been fabricated, packaged and tested. A chip may contain several millions of transistors. Layout of the entire circuit cannot be handled at once due to the limitation of memory space as well as computation power available. Therefore, it is normally partitioned by grouping the components into *blocks*. The output of partitioning is a set of blocks and the interconnections required between the blocks. Figure 1.2 shows that the input circuit has been partitioned into three blocks. In the large circuit, the partitioning process is hierarchical and at the topmost level a chip may have 5 to 25 blocks [2]. Each block is then partitioned recursively into smaller blocks.

4

#### 1.2.2 Floorplanning

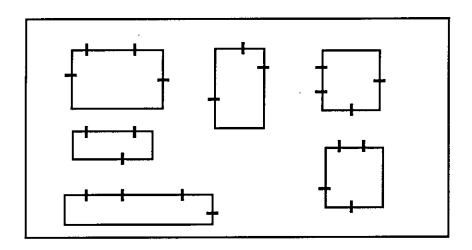

After the circuit partitioning, the area occupied by each block can be calculated and the number of terminals (pins) required by each block is known. Given a set of blocks and the interconnection among them, the floorplanning problem is to assign each block a rectangular area on a plane such that each connection can be routed through the space which is not occupied by any block and no two nets intersect each other. Floorplanning is a key step in physical design cycle. A poor floorplanning consumes larger area and results in performance degradation. It generally leads to a difficult or sometimes impossible routing task.

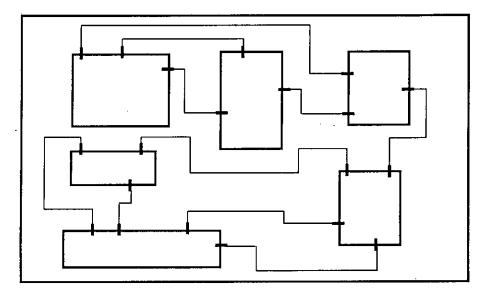

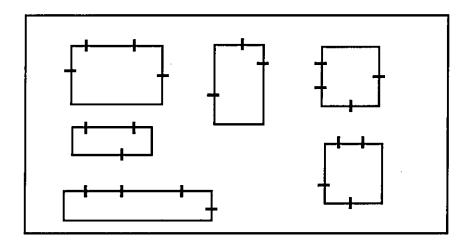

Figure 1.3: Circuit blocks and pins after floorplanning.

#### 1.2.3 Routing

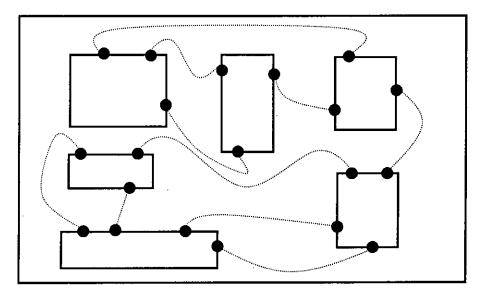

Spaces not occupied by the blocks during floorplanning can be viewed as a collection of regions. These regions are used for routing and is called *routing region*. The process of finding the geometric layout of all the interconnectios among the blocks through the routing region is called *routing*. The entire process of routing is divided into two phases: global routing and detailed routing. If the position of the connection terminals on each block is flexible, that is, actual position of connection could be floated along the side lines of the block, then the routing problem is called *global routing problem*. It generates a loose route for each net.

But if the position of the connection terminals on each block is fixed then the routing problem is called *detailed routing problem*. Detailed routing finds the actual geometric

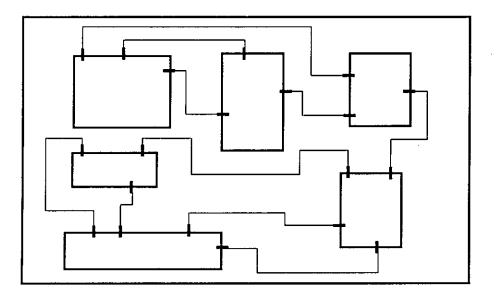

layout of each net within the routing region. The concepts of global and detailed routing are shown in Figures 1.4 and 1.5, respectively.

Figure 1.4: Global routing.

Figure 1.5: Detailed routing.

### 1.3 Traditional Approach of Floorplanning and Routing

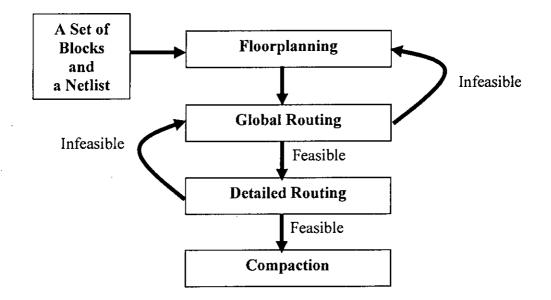

A set of blocks and a netlist (as obtained from partitioning) is the input to the floorplanning problem. A floorplanning algorithm generates a floorplan for the given partitioning of the circuit. Then the global routing of the floorplan is determined if there is any feasible global routing exists; otherwise we backtrack to the floorplanning phase for any other alternative floorplan. A feasible global routing is the base of the detailed routing phase. If no feasible detailed routing is possible for a given global routing we backtrack for alternative global routing. Thus the overall floorplanning and routing process may iterate for several times. The traditional approach of handling floorplanning and routing problems is shown in Figure 1.6.

Figure 1.6: Traditional approach of floorplanning and routing

#### 1.4 Objectives of this Thesis

Since 1960, many researchers have been worked on floorplanning and routing problems. Most of the work had treated floorplanning [1, 10, 14, 15, 16, 18, 19, 20, 21] and routing [3, 29, 31] as two successive phase in the physical design. Here we have presented an integrated approach to solve floorplanning and global routing problems in linear time using orthogonal graph drawing. We also have developed a linear-time algorithm to find the detailed routing from the global routing that we obtained from our integrated floorplanning and global routing algorithm. In Figure 1.7, a brief overview of the overall technique is showh.

7

ζ.

Figure 1.7: (a) A circuit C (set of blocks and their interconnections)

Figure 1.7: (c) A 3-graph G' equivalent to G

Figure 1.7: (d) Floorplanning and global routing for circuit *C* using orthogonal graph drawing

At first, the circuit blocks and the interconnections between them (Figure 1.7a) is represented by an *interconnection graph* G (Figure 1.7b), which may be a multi-graph. Then this multi-graph is converted to a 3-graph G' (Figure 1.7c) for which we can get an orthogonal graph drawing (Figure 1.7d). This orthogonal drawing gives the solution for the floorplanning and global routing problems but the actual pin assignment remain unsolved. Later, our detailed routing algorithm gives solution for the pin assignment and thus gets the detailed routing R (Figure 1.7e) for the circuit C. The details of this approach will be discussed at the later chapters.

9

### **1.5 Organization of the Thesis**

Chapter 1 of this thesis gives a brief introduction of the floorplanning and routing problems and how these problems are handled traditionally. Here we also give a very brief overview of our approach to handle these problems. In Chapter 2 fundamentals of graph theoretic terminologies and some graph drawing techniques have been defined. We also stated some known results on graph drawing there. In Chapter 3 we developed an algorithm that solves floorplanning and global routing in an integrated approach. An algorithm for detailed routing of the global routing obtained in Chapter 3 is developed in Chapter 4. Finally Chapter 5 concludes our works.

### **Preliminary**

In this chapter we present some basic terms and easy observations related to our work. Definitions that are not included in this chapter will be introduced as they are needed. In Section 2.1, we start with some definitions of the standard graph theoretic terminologies used throughout the thesis. In Section 2.2, we define very common graph drawing techniques. Finally, some known results on orthogonal graph drawings are described in Section 2.3.

#### 2.1 Basic Terminology

#### 2.1.1 Graphs and Multigraphs

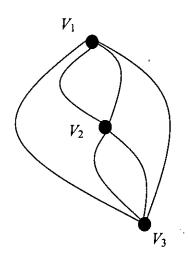

A graph is an ordered pair of (V, E) which consists of a finite set of vertices V and a finite set of edges E; each edge is an unordered pair of distinct vertices. We call V(G) the vertex-set of graph G and E(G) the edge-set of G. If e = (v, w) is an edge, then e is said to join the vertices v and w and these vertices are said to be adjacent. In this case we also say that w is a neighbour of v and that e is incident to v and w. If the graph G has no multiple edge or loop then G is said to be a simple graph. Multiple edges join the same pair of vertices, while a loop joins a vertex to itself. The graph in which loops and multiple edges are allowed is called a multigraph. Sometimes a simple graph is simply called graph, if doing so creates no confusion.

Figure 2.1: A simple graph.

The degree of a vertex v is the number of neighbors of v in G. We denote the maximum degree of graph G by  $\Delta(G)$  or simply by  $\Delta$ . If every vertex of a graph G has degree three or less then G is called a 3-graph. If every vertex of a graph G has degree exactly three then G is called a *cubic graph*.

#### 2.1.2 Subgraphs

A subgraph of a graph G = (V, E) is a graph G' = (V', E') such that  $V' \subseteq V$  and  $E' \subseteq E$ ; we write this as  $G' \subseteq G$ . If G' contains all the edges of G that join two vertices in V' then G' is said to be the subgraph induced by V' and is denoted by G[V']. If V' consists of exactly the vertices on which edges in E' are incident then G' is said to be the subgraph induced by G[E'].

We often construct new graphs from old ones by deleting some vertices or edges. If v is a vertex of a given graph G = (V, E) then G - v is a subgraph of G obtained by deleting the vertex v and all the edges incident to v. More generally, if V is a subset of V then G - V' is subgraph of G obtained by deleting the vertices in V' and the edges incident to them. Then G - V' is a subgraph of G induced by V - V'. Similarly if e is an edge of G then G - e is the subgraph of G obtained by deleting the edge e. More generally, if  $E' \subseteq E$  then G - E' is a subgraph of G obtained by deleting all edges in E'.

Figure 2.2: Subgraphs of G in Fig. 2.1: (a) vertex-induced and (b) edge-induced subgraph.

#### 2.1.3 Weighted Graphs

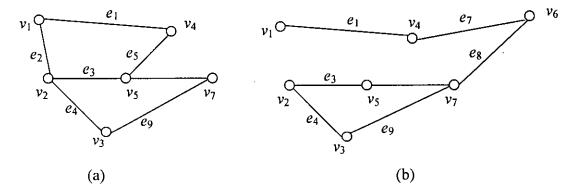

A graph where each of the edges has a positive weight associated with it is called a *weighted graph*. Now if N is the set of all positive integers then we can define the weight function for the edges as  $w: E \rightarrow N$ . Figure 2.3 shows a weighted graph with five vertices and six edges.

Figure 2.3: A weighted graph with five vertices.

#### 2.1.4 Paths, Distances and Cycles

A  $v_0-v_l$  walk in G is an alternating sequence of vertices and edges of G,  $v_0$ ,  $e_1$ ,  $v_1$ , ...,  $v_{l-1}$ ,  $e_b v_l$ , beginning and ending with a vertex, in which each edge is incident to two vertices immediately preceding and following it. If the vertices  $v_0$ ,  $v_1$ ,..., $v_l$  are distinct (except possibly  $v_0$ ,  $v_l$ ), then the walk is called a *path* and is usually denoted by  $v_0 v_1$ ,...,  $v_l$ . The *length* of a path in an unweighted graph is *l*, one less than the number of vertices on the path. In a weighted graph, the length of a path is determined by weights of the edges constituting the path. So the length w(P) of a path *P* is defined as  $w(P)=\sum_{e \in P} w(e)$ . The *distance* between any two vertices in a graph is the length of the shortest path in the graph between the two vertices. We denote the distance from a vertex *u* to another vertex *v* by dist(u, v). Now if the shortest path in G from *u* to *v* is *P*, then dist(u, v) = w(P).

A path or walk is *closed* if  $v_0 = v_l$ . A closed path of length at least one is called a *cycle* where  $v_0 = v_l$  is the only vertex repetition. An edge of G, which is incident to exactly one vertex of a cycle C and located outside of C is called a *leg* of the cycle C. The vertex of C to which a leg is incident is called a *leg-vertex* of C. A cycle in G is called a *k-legged* cycle of G if C has exactly k legs in G.

Figure 2.4:  $C_1$  and  $C_3$  are two 3-legged cycles.

#### 2.1.5 Connectivity

The connectivity  $\kappa(G)$  of a graph G is the minimum number of vertices whose removal results in a disconnected graph or a single vertex graph. We say that G is *k*-connected if  $\kappa(G) > k$ . We call a vertex of G a *cut vertex* if its removal results in a disconnected graph.

#### 2.1.6 Planar Graph

A graph is *planner* if it can be embedded in the plane so that no two edges intersect geometrically except at a vertex to which they both are incident. A *plane* graph is a planar graph with a fixed embedding in the plane. A plane graph G divides the plane into connected regions called *faces*. The unbounded region is called *outer face*. We regard the *contour* of a face as a clockwise cycle formed by the edges on the boundary of the face. We denote the contour of the outer face of the graph G by  $C_0(G)$ .

Figure 2.5: Two plane graphs of a same planar graph.

Let G be a plane connected graph. For a cycle C in G, we denote by G(C) the plane subgraph of G inside C (including C). We say that cycles C and C' in a plane graph G are independent if G(C) and G(C') have no common vertex. A set S of cycles is independent if any pair of cycles in S is independent.

#### 2.1.7 Trees

A *tree* is a connected graph without any cycles. Figure 2.6 is an example of a tree. A *rooted tree* is a tree in which one of the nodes is distinguished from others. This distinguished node is called the *root* of the tree. The root of the tree is generally drawn at the top. A tree is called *binary tree* if each node of the tree has at most two children. In Figure 2.5, the root is node 1.

Figure 2.6: A binary tree with 9 vertices.

Every vertex u other than the root is connected by an edge to some other vertex p called the *parent* of u. We also call u a *child* of p. We draw the parent of a node above that node. For example, in figure 2.5, node 1 is the parent of node 2 and node 3. Alternately, nodes 6 and 7 are children of node 2. A *leaf* is a node of a tree that has no child. Thus every node of a tree is either a leaf or an internal node, but not both. In figure 2.6, the leaves are 4, 6, 7, 8 and 9 and nodes 1, 2, 3 and 5 are internal nodes.

The parent-child relationship can be extended naturally to ancestors and descendants. Suppose,  $u_1, u_2, ..., u_l$  is a sequence of nodes in a tree such that  $u_1$  is the parent of  $u_2$ , which is the parent of  $u_3$  and so on. The node  $u_1$  is called an *ancestor* of  $u_3$  and node  $u_3$  is called a *descendant* of  $u_1$ . The root is the ancestor of every node in a tree and every node is a descendant of the root. In Figure 2.6, all nodes other than node 1 are descendants of node 1 and node 1 is an ancestor of all other nodes.

In a tree T, a node u together with all of its descendants, if any, is called a *subtree* of T. Node u is the root of this subtree. Referring again to Figure 2.5, node 6 by itself is a subtree, since node 6 has no descendant. Again, nodes 2, 6 and 7 form a subtree with root 2. Finally the entire tree of Figure 2.6 is a subtree of itself with root 1. The *height* of a node u in a tree is the length of the longest path from u to a leaf under u. The height of a tree is the height of a root. The *depth* of a node u in the tree is the length of a path from the root to u. In Figure 2.6, for example, node 3 is of height 2 and depth 1. The tree has height 3.

### 2.2 Graph Drawing Conventions

Automatic graph drawings have numerous applications in VLSI layout, networking, computer architecture, circuit schematics, etc [5, 17]. For the last few years many researchers have concentrated their attention on graph drawings and introduced a number of conventions. A drawing convention is some basic rules that the drawing must satisfy. A list of widely used drawing conventions is [17]

- Orthogonal Drawing,

- Box-orthogonal Drawing,

- Rectangular Drawing,

- Box-rectangular Drawing, and

- Grid Drawing

#### 2.2.1 Orthogonal Drawing

An orthogonal drawing of a plane graph G is a drawing of G in which each vertex is drawn as a grid point on an integer grid and each edge is drawn as a sequence of alternate horizontal and vertical line segments along grid lines as illustrated in Figure 2.7(b). Any plane graph with maximum degree at most four has an orthogonal drawing [26], but may need bends. Minimization of number of bends in an orthogonal drawing is a challenging problem. Several works have been done on this issue [7, 8, 23, 25, 30]. In a VLSI floorplanning problem, an input is often a plane graph of maximum degree 3 [12, 24, 25]. Rahman *et al.* gave an algorithm to find an orthogonal drawing of a given plane 3-graph

with minimum number of bends in linear time [27]. However, a plane graph with a vertex of degree 5 of more has no orthogonal drawing. A plane graph G may have an orthogonal drawing without bends [26]. However, not every plane graph has an orthogonal drawing without bends. For example, the cubic plane graph in Figure 2.7(a) has no orthogonal drawing without bends.

Figure 2.7: (a) A plane graph G, (b) an orthogonal drawing of G with 6 bends, (c) an orthogonal drawing of G with 5 bends.

#### 2.2.2 Box-Orthogonal Drawing

A box-orthogonal drawing of a plane graph G is a drawing of G on an integer grid such that every vertex is drawn as a (possibly generated) rectangle, called a box, and each edge is drawn as sequence of alternate horizontal and vertical line segments along grid lines, as illustrated in Figure 2.8. Some of the boxes may be degenerated rectangles, i.e, points. A box-orthogonal drawing is a natural generalization of an ordinary orthogonal drawing.

Moreover, any plane (multi) graph has box-orthogonal drawing even if there is a vertex of degree 5 or more.

Figure 2.8: (a) A plane multi-graph G, (b) A box-orthogonal drawing of G.

#### 2.2.3 Rectangular Drawing

A *rectangular drawing* of a plane graph is an orthogonal drawing in which there is no bend and each face of the graph is drawn as a rectangle. The drawing in Figure 2.9 is an example of a rectangular drawing.

Figure 2.9: A rectangular graph drawing.

#### 2.2.4 Box-Rectangular Drawing

A *box-rectangular drawing* of a graph is a drawing such that each vertex is drawn as a box, and the contour of each face is drawn as a rectangle. The drawing in Figure 2.10 is

an example of a box-rectangular drawing. Unfortunately, not every plane graph has a box- rectangular drawing. Some works on box-rectangular drawing are done in [25].

Figure 2.10: A box-rectangular graph drawing.

#### 2.2.5 Grid Drawing

A drawing of a graph in which vertices and bends are located at grid points of an integer grid is called a *grid drawing*. The drawing in Figure 2.11 is an example of grid drawing. It is a very challenging problem to draw a plane graph on a grid of the minimum size. In recent years, several works have been done in this field [6, 23].

Figure 2.11: A grid drawing.

### 2.3 Some Known Results on Orthogonal Drawing

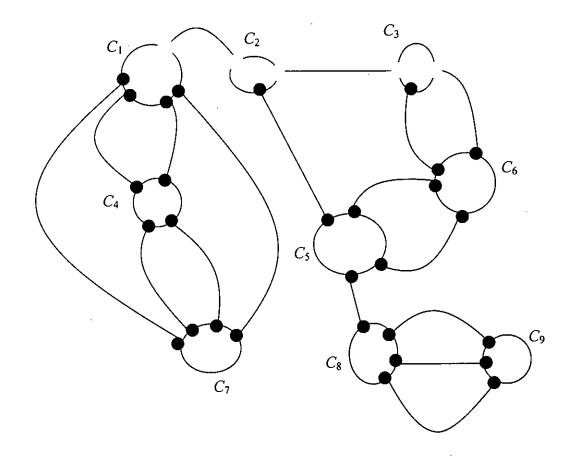

In Chapter 3, we present a floorplanning algorithm using orthogonal drawing of plane graph. Thus it is important to know some definitions and known results regarding orthogonal drawing of plane graphs. We first have the following lemma [30]:

**Lemma 2.1** Let G be a plane biconnected graph with maximum degree  $\Delta \leq 3$ . Assume that, four vertices of degree 2 on  $C_0(G)$  are designated as the four corners of the outer rectangle. Then G has a rectangular drawing if and only if G satisfies the following two conditions:

(r1) every 2-legged cycle contains at least two designated vertices, and

(r2) every 3-legged cycle contains at least one designated vertex.

Furthermore, one can check in linear time whether a graph G satisfies the conditions above, and if G does then one can find a rectangular drawing in linear time [22].

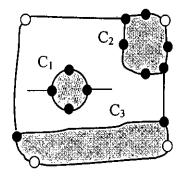

Figure 2.12: (a) 2-legged cycles.

Figure 2.12: (b) 3-legged cycles.

In Figure 2.12, white circles are the four designated corner vertices and the black circles are the non-designated vertices of each graph. Cycles  $C_1$ ,  $C_2$  and  $C_3$  are 2-legged and cycles  $C_4$ ,  $C_5$  and  $C_6$  are 3-legged. Cycles  $C_3$ ,  $C_5$  and  $C_6$  do not violate any of the two conditions in lemma 2.1. On the other hand cycles  $C_1$ ,  $C_2$  and  $C_4$  violate the condition.

A cycle in G violating the condition (r1) or (r2) of Lemma 2.1 is called a *bad cycle*: a 2-legged cycle is bad if it contains at most one designated vertex; a 3-legged cycle is bad if it contains no designated vertex. Thus cycles  $C_1$ ,  $C_2$  and  $C_4$  are bad cycles.

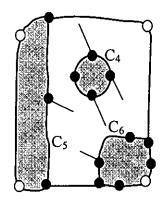

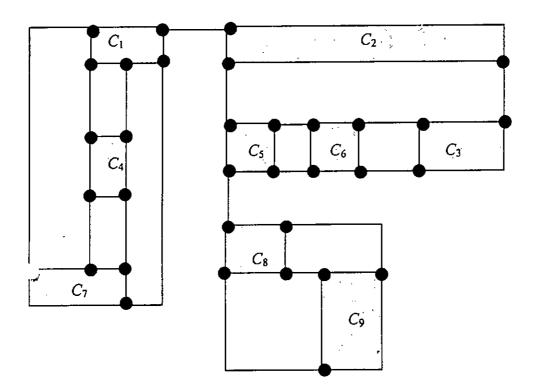

For a cycle C in a plane graph G, we denote by G(C) the plane subgraph of G inside C including C. A bad cycle C in G is called a *maximal bad cycle* if G(C) is not contained in G(C') for any other bad cycle C' of G. In Figure 2.13  $C_1$ ,  $C_2$ ,  $C_4$ ,  $C_5$  and  $C_6$  are bad cycles. Cycles  $C_1$ ,  $C_4$ ,  $C_5$  and  $C_6$  are maximal bad cycles.  $C_3$  is not a maximal bad cycle because subgraph  $G(C_3)$  is contained in a subgraph  $G(C_4)$ .

Figure 2.13: The maximal bad cycles  $C_1$ ,  $C_4$ ,  $C_5$  and  $C_6$  in graph G.

Cycles C and  $C^*$  in a plane graph G are *independent* of each other if G(C) and  $G(C^*)$  have no common vertex. We have the following lemma [26]:

**Lemma 2.2** Let G be a plane biconnected graph with maximum degree  $\Delta \leq 3$ . Assume that four vertices of degree 2 on  $C_0(G)$  are designated as the four corners of the outer rectangle. Then the maximal bad cycles in G are independent of each other.

An orthogonal drawing of a plane graph G is a drawing of G with the given embedding in which each vertex is mapped to a point and each edge is drawn as a sequence of alternate horizontal and vertical line segments and any two edges do not cross except at their common end. A *bend* is a point where an edge changes its direction in the drawing. The following results are known on the orthogonal drawing of a plane graph [26]:

**Lemma 2.3** Let G be a plane bi-connected graph with maximum degree  $\Delta \leq 3$  and four or more vertices on  $C_0$  (G) with degree two. Then G has an orthogonal drawing without bend if and only if every 2-legged cycle in G contains at least two vertices of degree 2 and every 3-legged cycle contains at least one vertex of degree 2.

C

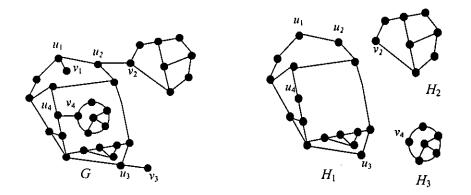

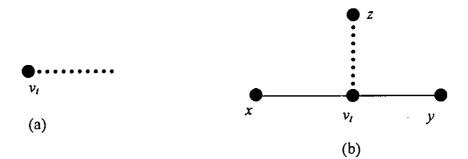

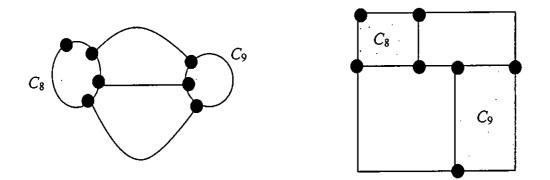

A subgraph H of G is a *biconnected component* of G if H is a biconnected subgraph of G having no cut vertex. A single edge (u, v) of G together with the vertices u and v is a *weakly biconnected component* of G if either both u and v are cut vertex or one of u and v is a cut vertex and the other is a vertex of degree one. The graph G in Figure 2.14(a) has three biconnected components  $H_1$ ,  $H_2$  and  $H_3$  as shown in figure 2.14(b). Edges  $(u_1, v_1)$ ,  $(u_2, v_2)$ ,  $(u_3, v_3)$  and  $(u_4, v_4)$  are weakly biconnected components.

Figure 2.14: (a) A plane graph G, (b) three biconnected components of G.

We call two subgraph  $H_i$  and  $H_j$  of G are *disjoint* with each other if  $H_i$  and  $H_j$  have no common vertex. The following lemma is known [26]:

**Lemma 2.5** Let G be a plane bi-connected graph with maximum degree  $\Delta \leq 3$ . Then the bi-connected components in G are disjoint with each other.

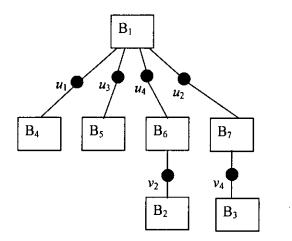

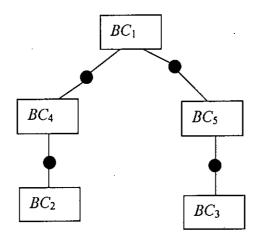

A *block* of a connected graph G is either a bi-connected component or a weakly biconnected component of the graph. A tree called *BC-tree* of G can represent the blocks and cut vertices of the graph. In the BC-tree of G each block is represented by a *B-node* and each cut vertex is represented by a *C-node*. In Figure 2.15 the BC-tree of graph G in Figure 2.14 is shown, where each B-node is represented by a rectangle and a circle represents each C-node.

ć'

Figure 2.15: BC-tree of the graph G of Figure 2.16.

# **Floorplanning and Global Routing**

### **3.1 Introduction**

Floorplanning is one of the very important phases of the physical design cycle in automated VLSI design. The input to physical design cycle is a circuit diagram and the output is the layout of the circuit which is later been fabricated, packaged and tested. A chip may contain several million transistors and is normally partitioned by grouping the components into blocks. The output of partitioning is a set of blocks and the interconnection required between the blocks. After the circuit partitioning phase, the area occupied by each block can be calculated and the number of terminals (pins) required by each block is known. A connection between two terminals of two blocks is called a *net* and the set of all nets among all the blocks is called a *netlist*. Given a set of blocks and a netlist the floorplanning problem is to assign each block a rectangular area on a plane such that each net of the netlist could be routed through the space which is not occupied by any block and no two nets intersect each other. Floorplanning is a key step in physical design cycle. A poor floorplanning consumes larger areas and results in performance degradation. It generally leads to a difficult or sometimes impossible routing task.

The floorplanning of blocks occur at three different levels: *system level, board level* and *chip level* [4]. At system level, the floorplanning problem is to place all the PCBs together so that area occupied is minimized. At board level, all the chips on a board along with other solid-state devices have to be placed with in a fixed area of the PCB. The PCB technology allows mounting of components on both sides. There is essentially no restriction on the number of routing layers in PCB. The objectives of the board level floorplanning algorithm is two fold: minimization of the number of routing layers and satisfaction of the system performance requirements. The key difference between the board level floorplanning problem is the limited number of layers that can be used for routing on a chip. In addition, the circuit is fabricated only on one side of the substrate.

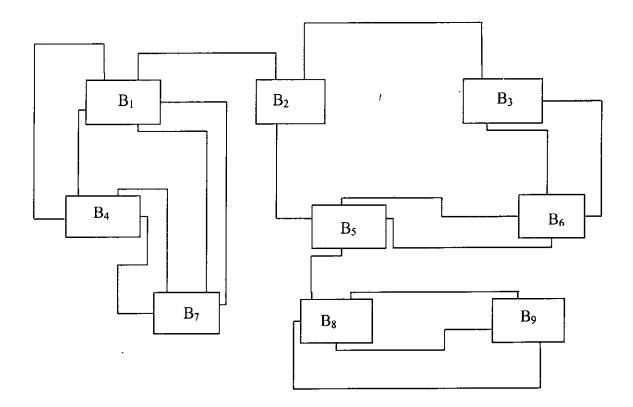

Let us formally state the floorplanning problem. Let  $B_1, B_2, ..., B_n$  be the blocks to be placed on the chip. Let  $N = \{N_1, N_2, ..., N_m\}$  be the set of nets representing the interconnections between different blocks. The floorplanning problem is to find the rectangular region for each block denoted by  $R = \{R_1, R_2, ..., R_n\}$  on the plane such that

- 1. no two rectangles overlap each other, that is,  $R_i \cap R_j = \phi$ ,  $1 \le i, j \le n$ ; and

- floorplanning is routable, that is, Q<sub>i</sub>'s, 1 ≤ i ≤ k, are sufficient to route all the nets, where Q = {Q<sub>1</sub>, Q<sub>2</sub>, ..., Q<sub>k</sub>} represents the empty areas allocated for routing between blocks.

Figure 3.1: Circuit blocks and pins after floorplanning.

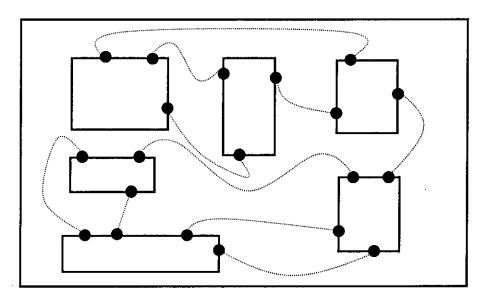

Spaces not occupied by the blocks during floorplanning can be viewed as a collection of regions. These regions are used for routing and is called *routing region*. The process of finding the geometric layout of all the nets through the routing region is called *routing*. Nets must be routed within the routing region and also must not be short circuited, that is, nets must not intersect each other. The entire process of routing is divided into two phases: *global routing* and *detailed routing*. If the position of the connection terminals on each block is flexible that is actual position of connection could be floated along the side lines of the block then the routing problem is called global routing problem. It generates a loose route for each net. But if the position of the connection terminals on each block is fixed then the routing problem is called detailed routing problem. Detailed routing finds the actual geometric layout of each net within the routing region. Figure 3.2 and Figure 3.3 show the global routing and detailed routing respectively.

Figure 3.2: Global routing.

Figure 3.3: Detailed routing.

### **3.1.1 Traditional Approach of Floorplanning and Routing**

A set of blocks and a netlist (as obtained from partitioning) is the input to the floorplanning problem. A floorplanning algorithm generates a floorplan for the given partitioning of the circuit. Then a global routing of the floorplan is determined if there is any feasible global routing exists; otherwise we backtrack for any other alternative floorplan. A feasible global routing is the base of the detailed routing phase. If no feasible detailed routing is possible for a given global routing then we backtrack for alternative global routing. Thus the overall floorplanning and routing process may iterate for several times. The traditional approach of handling floorplanning and routing problems is shown in Figure 3.4.

Figure 3.4: Traditional approach of floorplanning and routing.

### 3.1.2 Our Integrated Approach of Floorplanning and Routing

We handle floorplanning and global routing problems in a single phase. The input to our integrated floorplanning and global routing algorithm is a set of blocks and a netlist and output is the floorplan and the global routing layout (except detail routing) for it. Global routing layout is then used for detailed routing in the next phase. Our integrated algorithm can find floorplan and global routing for a circuit if those exists in a plane. Thus no iteration between floorplanning and routing is required.

In the rest of the chapter, we have presented the integrated approach of solving floorplanning and global routing problems in a single phase. We have used orthogonal graph drawing for this purpose. In Chapter 4, we have developed an algorithm to find detailed routing for the floorplan and we would get global routing from our integrated approach.

27

Our approach of handling floorplanning and routing is shown in Figure 3.5. This is a linear approach, that is, if there exists a feasible floorplan and global routing in a single plane then our approach could find it without any backtracks.

Figure 3.5: Our integrated approach of floorplanning and routing.

# 3.2 Integrated Floorplanning and Global Routing

Unlike traditional approach we have integrated floorplanning and global routing in a single phase. We have used orthogonal graph drawing for this purpose. The outline for our algorithm is as follows:

- Step-1 Represent the circuit C using a multigraph G.

- **Step-2** Get a 3-graph G' from the graph G.

- Step-3 Get an orthogonal drawing D for the 3-graph G'.

- Step-4 Get a floorplan and global routing F for the circuit C from the orthogonal drawing D.

## 3.2.1 Representing a Circuit using Multigraph

We are given a circuit specification consisting of circuit elements (blocks) and the connections between them called netlist. First we represent the circuit using a multigraph G, where each block (circuit element) is represented by a vertex and interconnections between blocks by edges. The resulting graph is a multigraph as there may be more than one connection between two same circuit blocks.

Figure 3.6: (a) A circuit specification, (b) The multigraph G for the circuit.

Assume that the graph G that obtained from the circuit specification as described above is planar and has a fixed planar embedding. For real and complex circuit, where huge number of circuit elements and the interconnection among them are involved, the graph Gmay not be planar. Actually the routing of the nets is done in multiple layers and the nets those reside in a particular layer do not intersect each other. Thus for a single layer the assumption of being the graph plane does match with real circuits. In a VLSI floorplanning problem, an input is often a plane graph of maximum degree 3 [12, 24, 25]. Distributing the nets in different routing layers is beyond the scope of this thesis.

### 3.2.2 Converting Multigraph into a 3-Graph

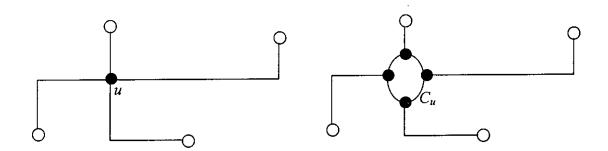

We use orthogonal graph drawing technique to solve the floorplanning and routing problems. Orthogonal drawings have attracted much attention due to their various applications, especially in circuit schematics, entity relationship diagrams, data flow diagrams etc. [5, 28, 30]. If G be a plane graph with maximum degree  $\Delta \leq 3$ , then G has a bend minimum orthogonal drawing [26, 27]. There is a linear-time algorithm to find such orthogonal drawing of G. It is desired to find an orthogonal drawing with a small number of bends, because a bend corresponds to a "via" or "through-hole", and increase the fabrication cost of VLSI circuit [12, 28]. But the graph we obtained from the circuit specification as described in Section 3.2.1 may consist of vertices with degree one, two, three, or more. Thus we need some conversion of the graph so that a bend minimum orthogonal drawing could be obtained by keeping the meaning of the circuit specification. Here we have described the process of getting a 3-graph G' (a graph with maximum degree  $\Delta \leq 3$ ) from the multigraph G.

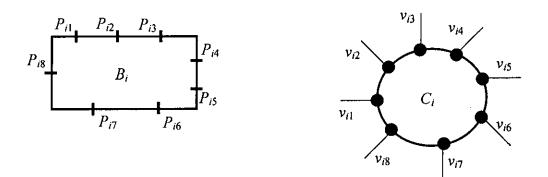

Let G be the graph obtained from the circuit specification as described in Section 3.2.1. Then G may have vertices of varying degrees. We replace each vertex with degree three or more with a cycle containing the number of vertices on the cycle equal to the degree of the original vertex. Let u be a vertex of graph G with degree m and  $m \ge 3$ ; then u should be replace by a cycle  $C_u$  with vertices  $\{u_1, u_2, ..., u_m\}$ , and let v be a vertex with degree n; then v should be replace by a cycle  $C_v$  with vertices  $\{v_1, v_2, ..., v_n\}$ . Now an edge between u and v will be replaced by an edge between  $u_i$  and  $v_j$ , where  $1 \le i \le m$  and  $1 \le j \le n$ . The graph G' that obtained in this way from the original graph G is a 3-graph.

A vertex of graph G represents a circuit element and such vertex with degree three or more is replaced by a cycle in the 3-graph. So each vertex on the replaced cycle in the 3graph G' represents a pin of a circuit element. During this replacement of a vertex with its equivalent cycle, one important feature of circuit specification should be kept: the clockwise orientation of the connecting pins on the circuit element and its equivalent replaced vertices on the corresponding cycle in the 3-graph G' should be the same. Let the clockwise orientation of the connecting pins of the circuit element (block)  $B_i$  is  $\{P_{i1}, P_{i2}, ..., P_{im}\}$  where *m* is the number of connecting pins on block  $B_i$  and  $m \ge 3$  and block  $B_i$  has been replaced by cycle  $C_i$  and vertex  $v_{ij}$  represents pin  $P_{ij}$ , where  $1 \le j \le m$ . Then the clock wise orientation of the vertices on cycle  $C_i$  starting from vertex  $v_{i1}$  should be  $\{v_{i1}, v_{i2}, ..., v_{im}\}$ ; which is same as that of the clockwise orientation of the pins on block  $B_i$ . This relation is shown in Figure 3.7.

Figure 3.7: Clockwise orientation of pins and vertices.

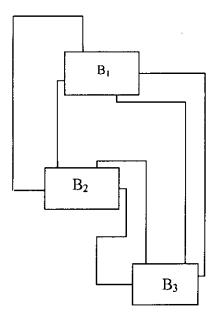

The 3-graph G' obtained in this way may or may not be bi-connected as original graph G may have vertices of degree one or two also. The conversion of the multigraph G of Figure 3.8(a) to a 3-graph G' has been shown in Figure 3.8(b).

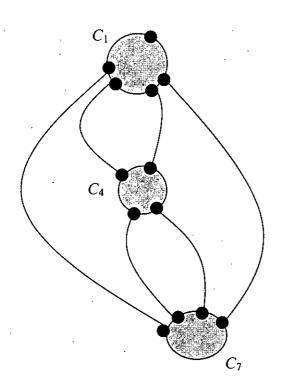

Figure 3.8: (a) Original multi-graph G, (b) 3-graph G'.

The 3-graph G' obtained in Figure 3.8 is bi-connected, but it is not always true. The 3-graph G' obtained in this way may not be bi-connected. Figure 3.9(c) shows such an instance.

Figure 3.9: (a) A circuit specification.

Figure 3.9: (b) Multigraph G for the circuit.

Figure 3.9: (c) A 3-graph *G*'.

# 3.2.3 Handling Multi-Terminal Net

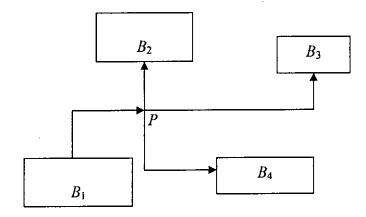

The circuit specifications we have considered so far did not have *multi-terminal net*. A net is called multi-terminal net if it has a single source at one end and more than one destination at the other end. A multi-terminal net is shown in Figure 3.10.

Figure 3.10: A multi-terminal net.

If the circuit containing multi-terminal net is represented by a graph as described in Section 3.2.1, we get a non-planar graph. To avoid this situation we replace the common point P by a vertex u in the multigraph G that represents the circuit. Then u has degree at least 3 and thus later be replaced by a cycle while converting the multi-graph G into a 3-graph. Handling a multi-terminal net is shown in Figure 3.11.

Figure 3.11: Representing multi-terminal net (a) in multigraph, (b) in 3-graph.

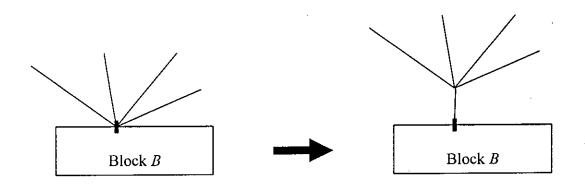

### 3.2.4 Handling Multi-Headed Pin

A *multi-headed pin* is a pin on any circuit block from where more than one connection goes outward. We can replace a multi-headed pin by its equivalent multi-terminal net. Once we get a multi-terminal net, the rest of the process is same as in Section 3.2.3. This process is shown in Figure 3.12.

Figure 3.12: Replacing multi-headed pin by a multi-terminal net.

## 3.2.5 Orthogonal Drawing of a Plane 3-Graph

In this section, we describe how to get an orthogonal drawing for the plane 3-graph as obtained for the circuit specification using the techniques described in Sections 3.2.1, 3.2.2, 3.2.3 and 3.2.4. If G is a plane graph with maximum degree  $\Delta \le 3$ , then there is a linear time algorithm to find bend minimum orthogonal drawing of G [24, 25, 27]. We have the following theorem for the orthogonal graph drawing of a plane 3-graph [27]:

**Theorem 3.1:** Let G be a connected plane 3-graph and let H be a biconnected component of G. Then there is a bend minimum orthogonal drawing D(H) for H. There is a linear time algorithm to find such orthogonal drawing.

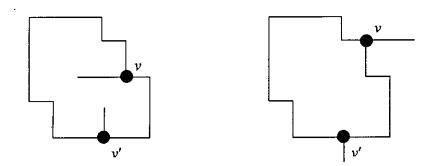

In the rest of this section, we describe some preliminaries and the approach of getting orthogonal drawing for a plane 3-graph using the results described in [26, 27]. Let C be a cycle in G and let v be a cut vertex of G on C. We call v an *out-cut vertex* for C if v is a leg vertex of C in G; otherwise we call v an *in-cut vertex* for C (Figure 3.13). Any in-cut vertex for C is not a convex corner (having interior angle 90°) of the drawing of C in any orthogonal drawing of G. Similarly, any out-cut vertex of C is not a concave corner (having interior angle 270°) [26].

Figure 3.13: (a) In-cut vertices v at a concave corner and v' at a non-corner, (b) Out-cut vertices v at a convex corner and v' at a non-corner.

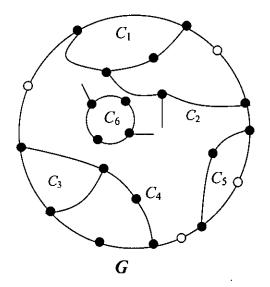

The plane 3-graph G represents the circuit specification is not necessarily biconnected. So it can be decomposed into a set of biconnected and weakly biconnected components. There is a minimum bend orthogonal drawing for each of the biconnected components using the algorithm in [27]. The orthogonal drawing of a weakly biconnected component is either a horizontal line segment or a vertical line segment. In order to get the

orthogonal drawing for the whole plane 3-graph G, we need to merge all the orthogonal drawings of the (weakly) biconnected components.

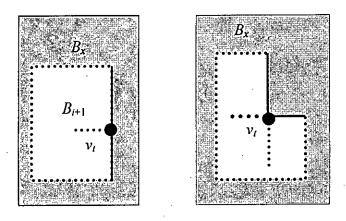

We construct a BC-tree of G to merge the orthogonal drawings of individual biconnected components. Let  $B_0$ ,  $B_1$ , ...,  $B_b$  be the ordering of the blocks following the depth-first search starting from the root  $B_0$  of the BC-tree. Assume that we have already obtained an orthogonal drawing  $D_i$  by merging the orthogonal drawings of the blocks  $B_0$ ,  $B_1$ , ...,  $B_i$ . Now we are going to obtain an orthogonal drawing  $D_{i+1}$ , by merging  $D_i$  with the orthogonal drawing of the block  $B_{i+1}$ . Let  $v_i$  be the cut-vertex corresponding to the C-node which is the parent of  $B_{i+1}$  in the BC-tree of G. Let block  $B_x$  be the parent of  $v_i$  in the BCtree. Then both  $B_x$  and  $B_{i+1}$  contain the vertex  $v_i$  and  $D_i$  contains the drawing of  $B_x$ . We have the following three cases to consider [26]:

**Case A:**  $B_x$  is a bi-connected component and  $B_{i+1}$  is a weakly bi-connected component.

In this case  $v_i$  is either a non-corner or a concave corner.  $B_{i+1}$  is an edge and will be drawn inside an inner face of the drawing  $D_i$  as shown in the Figure 3.14.

Figure 3.14: Embedding of  $v_t$  when  $B_x$  is a biconnected component and  $B_{t+1}$  is a weakly biconnected component.

#### **Case B:** Both $B_x$ and $B_{i+1}$ are weakly bi-connected components.

In this case  $v_t$  is drawn in an inner face of  $D_i$  and has degree 1 or 2 in  $D_i$ . We first consider the case where  $v_t$  has degree one. Then  $v_t$  in  $D_i$  has the embedding in Figure 3.15(a) or a rotated one. We draw  $B_i$  as the dotted line in Figure 3.15(a). We next

consider the case where  $v_i$  has degree two in  $D_i$ . Then  $v_i$  has degree 3 in G and let x, y, and z be the three neighbours of  $v_i$  in G. We may assume without loss of generality that edges  $(v_i, x)$  and  $(v_i, y)$  are already drawn in  $D_i$  and we now merge the drawing of the edge  $(v_i, z) = B_{i+1}$  to  $D_i$ . It is evident from the drawing described above that  $(v_i, x)$ and  $(v_i, y)$  are drawn on a (horizontal or vertical) straight line segment. We draw the edge  $(v_i, z)$  as a dotted line as in Figure 3.15(b).

Figure 3.15: Embeddings of  $v_i$  when both  $B_x$  and  $B_{i+1}$  are weakly biconnected components.

#### **Case C:** $B_x$ is a weakly biconnected component and $B_{i+1}$ is a biconnected component.

In this case  $v_i$  is drawn in  $D_i$  as the end of a horizontal or vertical line segment inside an inner face of  $D_i$ . Vertex  $v_i$  has degree 2 in  $B_{i+1}$  and is an out-cut vertex for  $C_0(B_{i+1})$  and  $v_i$  is either a non-corner or a convex corner in  $D(B_{i+1})$ . Therefore  $D(B_{i+1})$  can be easily merged with  $D_i$  by rotating  $D(B_{i+1})$  by 90° or 180° or 270° and expanding the drawing  $D_i$  if necessary.

Figure 3.16: Embeddings of  $v_i$  when  $B_x$  is a weakly biconnected component and  $B_{i+1}$  is a biconnected component.

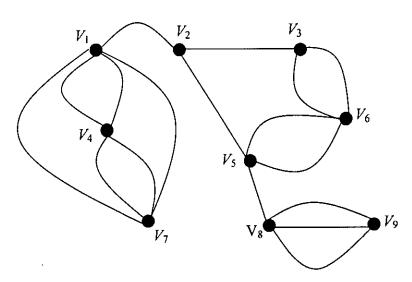

The overall process of getting bend minimum orthogonal drawing of a plane 3-graph is shown in figure 3.17.

Figure 3.17: (a) A plane 3-graph G, (b) Three biconnected components  $H_1$ ,  $H_2$  and  $H_3$ , (c) BC-tree for G, (d) Minimum bend orthogonal drawing of  $H_1$ ,  $H_2$  and  $H_3$ , (e) Orthogonal drawing of G.

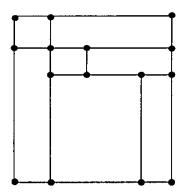

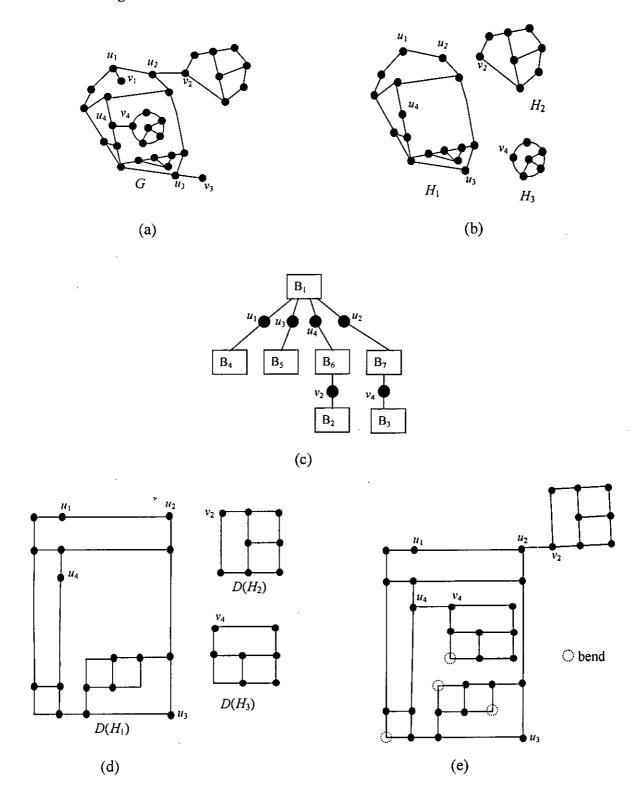

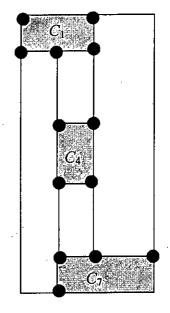

# 3.2.6 The Overall Process of Getting Floorplan and Global Routing

Orthogonal drawing D of plane 3-graph G' almost give the floorplan and global routing of the circuit leaving very little processing undone. Each of the cycle of the plane 3-graph G'that represents each circuit block or a multi-terminal net's common point is drawn as a rectangle in the orthogonal drawing. We replace each rectangular box in orthogonal drawing D that corresponds to the common point of a multi-terminal net by a single point. The overall process of getting floorplan and global routing for a given circuit specification is shown in Figure 3.18.

Figure 3.18: (a) A circuit specification.

Figure 3.18: (b) Multigraph G for the circuit.

Figure 3.18: (c) A 3-graph *G*'.

62

Figure 3.18: (d) Biconnected components  $BC_1$ ,  $BC_2$ ,  $BC_3$  and weakly bi-connected components  $BC_4$  and  $BC_5$ .

Figure 3.18: (e) BC-tree for the 3-graph G'.

Figure 3.18: (f) Orthogonal drawing of biconnected component  $BC_1$ .

Figure 3.18: (g) Orthogonal drawing of biconnected component  $BC_2$ .

Figure 3.18: (h) Orthogonal drawing of biconnected component  $BC_3$ .

Figure 3.18: (i) Orthogonal drawing for the 3-graph G'.

.

So we can describe the floorplanning and global routing process using orthogonal graph drawing for a given circuit specification in the following manner:

\*

#### Algorithm FloorPlanning(Circuit C)

begin

Step 1 Represent the circuit C using a multigraph G.

each block (or multi-terminal net's common point) will be represented by a vertex and interconnections between blocks by edges;

Step 2 Convert G into a 3-graph G'.

replace each vertex with degree three or more with a cycle containing the number of vertices on the cycle equal to the degree of the original vertex;

the clockwise orientation of the connecting pins on the circuit element and its equivalent vertices on the corresponding cycle in the 3-graph G' should be the same;

Step 3 for each biconnected component H (not weakly bi-connected component) of the 3-graph G' do

find a bend minimum orthogonal drawing using algorithm in [27];

**Step 4** Develop a BC-tree T for the 3-graph G'.

- Step 5 Visit BC-tree T in depth-first-search order and combine the orthogonal drawings of the biconnected components obtained in Step3 with the drawing of weakly biconnected components those are either a horizontal or a vertical line segment. Thus get an orthogonal drawing D for the 3-graph G'.

- Step 6 Replace the rectangular areas obtained for each cycle of 3-graph G' with circuit block except rectangular box for those cycles which corresponds to the common point of multi-terminal nets.

end

# 3.3 Time Complexity of the Integrated Floorplanning and Global Routing Algorithm

In this section we find the time complexity of the floorplanning and global routing algorithm.

The input to the floorplanning and global routing algorithm is a circuit specification and output is its floorplan together with global routing. The entire process is accomplished with the following phases one after another:

- i) To represent the circuit specification using a multigraph G.

- ii) To convert the multigraph G into 3-graph G'.

- iii) To get orthogonal drawing for each individual biconnected component.

- iv) To merge the orthogonal drawings of the biconnected components and hence get the floorplan and global routing.

Thus the cost of the algorithm is the summation of the costs of the above mentioned phases. Here we will define the problem size as N, where N is the number of nets (interconnections between the blocks in the circuit specification).

Let,  $B_1, B_2, ..., B_b$  be the blocks after the partitioning of the circuit and  $C(B_i)$  be the number of connections going outward of the block  $B_i$ , where  $1 \le I \le b$ . A net is made up of two terminal connections. Then

$$\sum_{1 \leq i \leq b} C(B_i) = 2N.$$

Let G be the multigraph that represents the circuit and  $V_1, V_2, ..., V_b$  are the set of vertices. Then

$$d(V_i) = C(B_i), \ 1 \le i \le b, \text{ and}$$

$$\Sigma_{1 \le i \le b} d(V_i) = 2N.$$

In the 3-graph G', each vertex  $V_i$  of graph G is replaced by a cycle  $C_i$  with  $d(V_i)$  vertices, where  $d(V_i)$  is the degree of the vertex  $V_i$ . So the number of vertices in the 3-graph G' is

$$\sum_{1 \le i \le b} d(V_i) = 2N.$$

45

14. c

The algorithm in [27] finds orthogonal drawing of a biconnected graph in linear time. So the cost of finding orthogonal drawing of the bi-connected component  $H_i$  with  $O(|V(H_i)|)$ vertices is also  $O(|V(H_i)|)$ . Thus the total cost of getting orthogonal drawing of all the biconnected components is

$$\sum_{1 \le i \le k} O(|V(H_i)|) = O(\sum_{1 \le i \le k} |V(H_i)|) = O(N).$$

Merging of an orthogonal drawing of a biconnected components with the drawing of a weakly biconnected component (a horizontal or vertical line segment) can be done in O(1) time. So merging all the drawings of the biconnected components can be done in O(N) times.

Thus the overall complexity of getting the floorplan and global routing of a circuit with N nets is O(N).

# **Detailed Routing**

In this chapter we present a linear-time algorithm for detailed routing with emphasis on minimizing the routing distance. In Section 1 we discuss on preliminaries for routing algorithm. Then in Section 2 we present the detailed routing algorithm. In Section 3 we find the time complexity of the algorithm.

#### 4.1 Introduction

Given a floorplan of the circuit and a global routing of the nets as obtained in Chapter 3, we are required to bend the nets so that they connect at the actual pin positions of the circuit elements (or blocks). This operation is called *detailed routing* and the drawing thus obtained after detailed routing is called *routed layout* for the input circuit specification that will later be fabricated in the next phase of a VLSI design cycle.

In Chapter 3, we have seen how floor planning of a circuit can be obtained together with the global routing of the nets using the orthogonal graph drawing. If a vertex v has degree d(v) in the multigraph G representing the circuit specification (see Section 3.2.1), then after floorplanning we will get a box corresponding to the vertex v with same number of connections to other circuit elements and each connections on a box is a pin on that circuit element. During graph representation of the circuit, connection on each vertex of graph obtained from circuit specification are considered clock wise. After floorplanning those connections maintain same clockwise ordering, but the exact pin positions on the actual circuit elements (or blocks) and the positions of the corresponding vertices on the floorplan may not be the same. That is why, the edges connected to the boxes need to bend to position exactly on the pin positions of the circuit elements.

### 4.2 Detailed Routing Algorithm

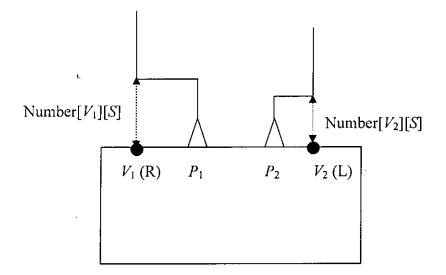

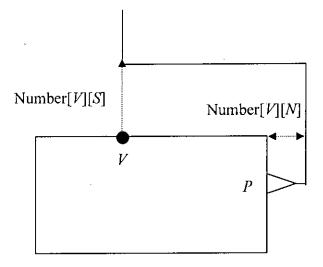

In VLSI design, timing consideration is one of the most critical factors and it is very much related to the length of the nets those connect the circuit elements. So routing algorithm should set its sight on minimizing the net length during bending the nets to fit to the actual pin positions of the circuit elements. A net in orthogonal drawing that subject to route to actual pin position, can either be directed clockwise or anti-clockwise to get there. But we should choose the path that ensures minimum distance of routing. In our algorithm, we classify vertices into two classes: *left vertices* and *right vertices* and has been described in Section 4.2.1.

During detailed routing, there may have a number of nets across a particular position and no two nets should intersect each other. In our algorithm, we associate a tuple of three values with each terminal vertex of the net, one for each side of the block that the net should move around, to ensure that nets are not unnecessarily farther from the side lines of the block. The process of determining the 3-tuple for each vertex has been described in Section 4.2.2.

In Section 4.2.3, the way the nets are to be bended has been described. The outline of the detailed routing algorithm is as follows:

Algorithm DetailedRouting (Floorplan F) begin

Step 1 Classify each vertices into left-vertex or right-vertex;

Step 2 Determine a 3-tuple for each vertex that would later guide the net to move from its vertex position to pin position;

Step 4 Minimize number tuple for each vertex;

Step 3 Bend each net according to its leftness/rightness and tuples associated with its two terminal vertices;

end

### 4.2.1 Classifying vertices into Left and Right

Depending upon the relative position of vertex (on the box of floorplan) and their exact pin position (on the circuit element) each vertex is classified as either left vertex or right vertex.

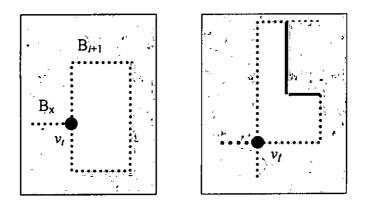

Let, the left-top and bottom-right corner of a box (e.g. each circuit element) in floorplan be  $(x_1, y_1)$  and  $(x_2, y_2)$  respectively. We assume that, X coordinate is increasing horizontally from left to right and Y coordinate is increasing vertically from top to bottom. There are four side lines for each box. Those are top horizontal line  $L_1$ , right vertical line  $L_2$ , bottom horizontal line  $L_3$  and left vertical line  $L_4$ . Let,  $P(x_p, y_p)$  be the exact pin position of the vertex positioned at  $V(x_v, y_v)$  on box of the floorplan. Then there are following three cases:

**Case 1** If  $P(x_p, y_p)$  and  $V(x_v, y_v)$  are on the same line  $(L_1 \text{ or } L_2 \text{ or } L_3 \text{ or } L_4)$  then vertices can be classified into left and right vertex in the following manner:

On  $L_1$ : When pin position  $P(x_p, y_p)$  and its corresponding vertex position  $V(x_v, y_v)$  both are on line  $L_1$  then:

if  $x_p \ge x_v$  then vertex  $V(x_v, y_v)$  is a right vertex;

else

vertex  $V(x_v, y_v)$  is a left vertex;

**On**  $L_2$ : When pin position  $P(x_p, y_p)$  and vertex position  $V(x_v, y_v)$  both are on line  $L_2$  then:

if  $y_p \ge y_v$  then

vertex  $V(x_v, y_v)$  is a right vertex;

else

vertex  $V(x_v, y_v)$  is a left vertex;

**On**  $L_3$ : When pin position  $P(x_p, y_p)$  and vertex position  $V(x_v, y_v)$  both are on line  $L_3$  then:

if  $x_p \ge x_v$  then vertex  $V(x_v, y_v)$  is a left vertex; else

vertex  $V(x_v, y_v)$  is a right vertex;

**On**  $L_4$ : When pin position  $P(x_p, y_p)$  and vertex position  $V(x_v, y_v)$  both are on line  $L_2$  then:

```

if y_p \ge y_v then

vertex V(x_v, y_v) is a left vertex;

else

vertex V(x_v, y_v) is a right vertex;

```

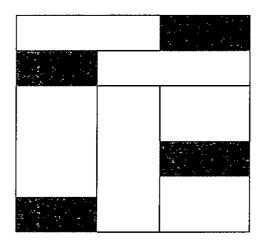

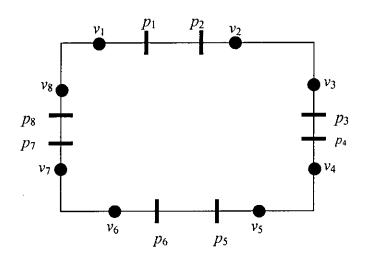

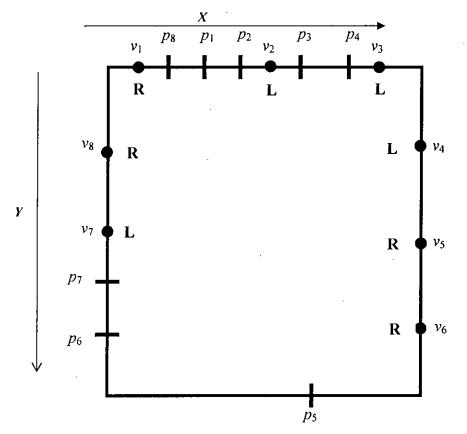

Case-1 classification is shown in Figure 4.1. Here a small bold circle on the side line represents a vertex position and a small horizontal or vertical line is a pin position on the box. In Figure 4.1,  $v_1$ ,  $v_3$ ,  $v_5$  and  $v_7$  are right vertices and  $v_2$ ,  $v_4$ ,  $v_6$  and  $v_8$  are left vertices

Figure 4.1: Classification of vertices (Case-1).

**Case 2** If pin position  $P(x_p, y_p)$  and vertex position  $V(x_v, y_v)$  are on two neighboring side lines then vertices can be classified into left and right vertex in the following manner:

```

if V is on L<sub>1</sub> and P is on L<sub>2</sub> then

V is a right vertex;

elseif V is on L<sub>1</sub> and P is on L<sub>4</sub> then

V is a left vertex;

elseif V is on L<sub>2</sub> and P is on L<sub>3</sub> then

V is a right vertex;

```

- elseif V is on L<sub>2</sub> and P is on L<sub>1</sub> then V is a left vertex;

elseif V is on L<sub>3</sub> and P is on L<sub>4</sub> then V is a right vertex;

- elscif V is on  $L_3$  and P is on  $L_2$  then V is a left vertex;

- elseif V is on  $L_4$  and P is on  $L_1$  then V is a right vertex;

- elseif V is on  $L_4$  and P is on  $L_3$  then

*V* is a left vertex;

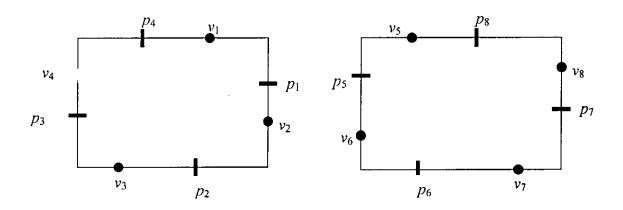

Case-2 classification is shown in Figure 4.2. Here,  $v_1$ ,  $v_2$ ,  $v_3$  and  $v_4$  are right vertices and  $v_5$ ,  $v_6$ ,  $v_7$  and  $v_8$  are left vertices.

Figure 4.2: Classification of vertices (Case-2).

**Case 3** If pin position  $P(x_p, y_p)$  and vertex position  $V(x_v, y_v)$  are on two opposite side lines then vertices can be classified into left and right vertex in the following manner:

(A) if V is on L1 and P is on  $L_3$  then

if  $x_p - x_1 + x_v - x_1 > x_2 - x_1$  i.e.  $x_p + x_v > x_1 + x_2$  then

V is right vertex;

else

*V* is left vertex;

(B) if V is on  $L_3$  and P is on  $L_1$  then

```

if x_p - x_1 + x_v - x_1 > x_2 - x_1 i.e. x_p + x_v > x_1 + x_2 then

```

```

V is left vertex;

```

else

*V* is right vertex;

```

(C) if V is on L_2 and P is on L_4 then

```

```

if y_p - y_1 + y_v - y_1 > y_2 - y_1 i.e. y_p + y_v > y_1 + y_2 then

```

V is right vertex;

else

*V* is left vertex;

```

(D) if V is on L_4 and P is on L_2 then

```

```

if y_p - y_1 + y_v - y_1 > y_2 - y_1 i.e. y_p + y_v > y_1 + y_2 then

```

*V* is left vertex;

else

V is right vertex;

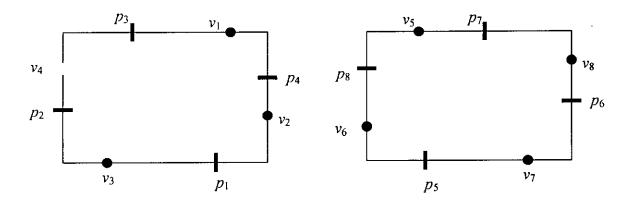

Case-3 classification is shown in Figure 4.3. Here,  $v_1$ ,  $v_2$ ,  $v_3$  and  $v_4$  are right vertices and  $v_5$ ,  $v_6$ ,  $v_7$  and  $v_8$  are left vertices

Figure 4.3: Classification of vertices (Case-3).

All three cases of vertex classification are illustrated in Figure 4.4. Here L or R in the parenthesis with each vertex indicates whether the vertex is left or right vertex.

Figure 4.4: Illustration of vertex classification.

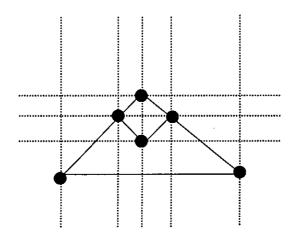

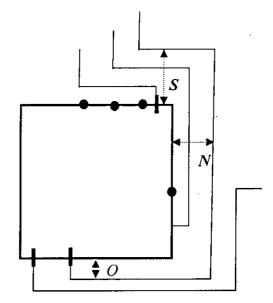

#### **4.2.2 Finding Routing Parameters**

After classifying the vertices into left and right kinds, we are left with the task of determining the number of grids a net to be away from the side lines of the block to reach from the vertex position to the corresponding actual pin position of the block. We have seen in Section 4.2.1 that a vertex and its corresponding pin may be situated on the same line or on two neighboring lines or on two opposite lines. If a vertex and its actual pin are on the same line then during detailed routing the net needs to move along only one side line of the block to reach from the vertex position to the pin position. A net needs to move along two neighboring side lines of the block. In the worst case, net needs to move along three neighboring side lines if vertex and its corresponding pin are on two opposite side lines of the block. So we are required to determine a tuple of three values namely (*S*, *N*, *O*); where *S* represents the number

of grids the net need to be away from the line on which the vertex is situated during moving towards the actual pin. N and O are both zero if the vertex and its actual pin are on the same line of the block. N is the number of grid lines the net to be away from the

neighboring side line during its move from the vertex to actual pin; if vertex and actual pin is either on neighboring side lines or on opposite side lines of the block. The value of O is nonzero only if vertex and actual pin are on two opposite side lines of the block and then it represents the number of grids the net should be away from the opposite side lines during its move from the vertex to actual pin. Figure 4.5 illustrates the (*S*, *N*, *O*) tuple.

٤

Figure 4.5: Illustration of (*S*, *N*, *O*) tuple.

The determination of the routing parameter (S, N, O) for each vertex of each block of the floorplan is done with emphasis on minimizing the total route. In order to determine the tuples for all vertices of a block or circuit element, we need to move twice around the block. First move is clock wise and it determines tuples for the right vertices only and it is accomplished by the algorithm *InitialRightRoute(B)* for block *B*. Next move is anti-clock wise to determine number tuples for the left vertices and is done by the algorithm *InitialRightRoute(B)*.

#### 4.2.2.1 Finding Routing Parameters for Right Vertices

The clockwise ordering of vertices obtained in the floorplan is same as the clockwise ordering of the pins of the actual circuit block. Thus during clockwise move around the block, the order of occurrence of the right vertices and its correspondence pin will be the same. That is, it is never be the case that a late coming right vertex reaches its pin earlier than an early coming right vertex during the move. We keep the right vertices in a

¢