# Design of a High Speed Crypto-Processor ASIC for Next Generation IT Security

by Niranjan Roy

MASTER OF SCIENCE

IN

INFORMATION AND COMMUNICATION TECHNOLOGY

Institute of Information and Communication Technology

BANGLADESH UNIVERSITY OF ENGINEERING AND TECHNOLOGY

2007

This thesis titled, "Design of a High Speed Crypto-Processor ASIC for Next Generation IT Security" submitted by Niranjan Roy, Roll No: MP0331026, Session 2003-2004 has been accepted as satisfactory in partial fulfillment of the requirement for the degree of Master of Science in Information and Communication Technology on the 07<sup>th</sup> October 2007.

#### **BOARD OF EXAMINERS**

|                                                                              | Chairmar    |

|------------------------------------------------------------------------------|-------------|

| Dr. Md. Liakot Ali<br>Assistant Professor, IICT<br>BUET, Dhaka - 1000        | Gildinia    |

| Q. w.                                                                        |             |

| - M                                                                          | Member      |

| Dr. S. M. Lutful Kabir<br>Professor and Director, IICT<br>BUET, Dhaka - 1000 | (Ex-officio |

| At Down                                                                      | Member      |

| Dr. Md. Abul Kashem Mia<br>Professor, IICT<br>BUET, Dhaka - 1000             | Welliber    |

| Forashir 10/10/07                                                            | Member      |

| Dr. A. B. M. Harun Ur-Rashid                                                 | (External)  |

| Professor Department of EEE                                                  | (=          |

BUET, Dhaka - 1000

# CANDIDATE'S DECLARATION

This is hereby declared that this thesis or any part of it has not been submitted elsewhere for the award of any degree or diploma.

Niranjan Roy

To my parents and my wife for their love and support

# **TABLE OF CONTENTS**

| List of Fig | ures | 5        |                                  | viii |

|-------------|------|----------|----------------------------------|------|

| List of Tal | oles |          |                                  | ix   |

| List of Abl | brev | iations  | of Technical Symbols and Terms   | x    |

| Acknowle    | dgei | nents    |                                  | xii  |

| Abstract    |      |          |                                  | xiii |

| Chapter 1:  | In   | troducti | ion                              | 1    |

|             | 1.   | 1 Introd | luction                          | 1    |

|             | 1.:  | 2 Scope  | e and Motivation                 | 3    |

|             | 1.3  | 3 Objec  | etives                           | 4    |

|             | 1.4  | 4 Frame  | ework                            | 5    |

| Chapter 2:  | Th   | eoretica | al Background                    | 6    |

|             | 2.1  | Introd   | uction                           | 6    |

|             | 2.2  | 2 IT Sec | curity Needs                     | 6    |

|             | 2.3  | 3 Overv  | iew of Cryptography              | 7    |

|             |      | 2.3.1    | Basic Terminology and Concepts   | 7    |

|             |      | 2.3.2    | Ciphering Techniques             | 8    |

|             |      | 2.3.3    | Cryptanalysis                    | 9    |

|             | 2.4  | The O    | rigins of AES                    | 10   |

|             | 2.5  | AES P    | erformance on Different Platform | 11   |

| Chapter 3:  | The  | AES A    | Algorithm                        | 13   |

|             | 3.1  | Introdu  | uction                           | 13   |

|             | 3.2  | The St   | rate                             | 13   |

|             | 3.3  | The AE   | ES Structure                     | 14   |

|             | 3.4  | Encryp   | otion                            | 16   |

|             |      | 3.4.1    | SubBytes() Transformation        | 17   |

|             |      | 3.4.2    | ShiftRows() Transformation       | 18   |

|             |      | 3.4.3    | MixColumns() Transformation      | 19   |

|             |      | 3.4.4    | AddRoundKey() Transformation     | 19   |

|             | 3.5  |          | pansion                          | 19   |

|             | 3.6  | Decryp   | tion                             | 20   |

|             |      | 3.6.1    | InvShiftRows() Transformation    | 21   |

|            |      | 3.6.2   | InvSubBytes() Transformation             | 21 |

|------------|------|---------|------------------------------------------|----|

|            |      | 3.6.3   | Inverse AddRoundKey() Transformation     | 22 |

|            |      | 3.6.4   | InvMixColumns() Transformation           | 22 |

| Chapter 4: | Hig  | gh Spee | ed Design Considerations                 | 23 |

|            | 4.1  | Introd  | uction                                   | 23 |

|            | 4.2  | Algori  | thm Optimization                         | 23 |

|            | 4.3  | Benef   | its of Optimized Algorithm               | 25 |

|            | 4.4  | Offline | e Key Expansion                          | 25 |

|            | 4.5  | Desig   | n Architecture                           | 26 |

|            |      | 4.5.1   | Loop Unrolling                           | 27 |

|            |      | 4.5.2   | Pipelining                               | 27 |

|            |      | 4.5.3   | Outer Round Pipelining                   | 27 |

|            |      | 4.5.4   | Inner round Pipelining                   | 27 |

| Chapter 5: | AS   | IC Mod  | ules and Verilog Design Entries          | 29 |

|            | 5.1  | Introdu | uction                                   | 29 |

|            | 5.2  | Compo   | onents                                   | 29 |

|            | 5.3  | Memor   | ry Unit                                  | 30 |

|            |      | 5.3.1   | S-box Memory                             | 30 |

|            |      | 5.3.2   | Key Memory                               | 30 |

|            |      | 5.3.3   | Column Vector Memory                     | 30 |

|            |      | 5.3.4   | Total Memory Requirements                | 31 |

|            | 5.4  | Encryp  | otion Unit                               | 31 |

|            | 5.5  | Decryp  | otion Unit                               | 32 |

|            | 5.6  | Key Ex  | pansion Unit                             | 33 |

|            | 5.7  | Verilog | Design Entries for "Encryption" Module   | 33 |

|            |      | 5.7.1   | "MixColumnProcessor" Module              | 34 |

|            |      | 5.7.2   | "Round10" Module                         | 34 |

|            | 5.8  | Verilog | Design Entries for "KeyExpansion" Module | 34 |

|            |      | 5.8.1   | "S_box" Module                           | 34 |

|            |      | 5.8.2   | "KeyProcessor" Module                    | 34 |

|            |      | 5.8.3   | "KeyRegister" Module                     | 35 |

|            | 5.9  | Verilog | Design Entries for "Decryption" Module   | 35 |

|            | 5.10 | Tools   | Used                                     | 35 |

| Chapter 6:  | Results and Performance Analysis                   | 36 |

|-------------|----------------------------------------------------|----|

|             | 6.1 Introduction                                   | 36 |

|             | 6.2 Resources Used                                 | 36 |

|             | 6.3 The Simulation Result                          | 36 |

|             | 6.4 Timing Analysis and Speed Measurement          | 38 |

|             | 6.5 Comparison with Other Related Works            | 39 |

|             | 6.5.1 FPGA Implementation                          | 39 |

|             | 6.5.2 ASIC Implementation: Prediction and Analysis | 40 |

|             | 6.4 I/O Signals and Data Buses                     | 42 |

| Chapter 7:  | Conclusion                                         | 44 |

|             | 7.1 Conclusion                                     | 44 |

|             | 7.2 Further Studies                                | 44 |

| References  |                                                    | 46 |

| Appendix A  | A Column Vectors                                   | 48 |

| Appendix E  | Rey Expansion Module                               | 49 |

| Appendix C  | Encryption Module                                  | 55 |

| Appendix D  | S_box Memory (ROM)                                 | 60 |

| Appendix E  | Inverse S_box (ROM)                                | 62 |

| Appendix F  | Decryption Module                                  | 64 |

| List of Pub | lications                                          | 69 |

# LIST OF FIGURES

| Figure 3.1: | Mapping of input bytes, state array and output bytes               | 13 |

|-------------|--------------------------------------------------------------------|----|

| Figure 3.2: | AES encryption and decryption                                      | 14 |

| Figure 3.3: | Key and expanded key                                               | 15 |

| Figure 3.4: | A full encryption round                                            | 15 |

| Figure 3.5: | Pseudo code for the encryption                                     | 17 |

| Figure 3.6: | Shift row transformation                                           | 18 |

| Figure 3.7: | Add round key transformation                                       | 19 |

| Figure 3.8: | Pseudo code for key expansion                                      | 20 |

| Figure 4.1: | Standard round of optimized algorithm                              | 25 |

| Figure 4.2: | Offline RoundKey addition                                          | 26 |

| Figure 5.1: | AES crypto-processor components                                    | 29 |

| Figure 5.2: | The encryption unit of the crypto-processor                        | 31 |

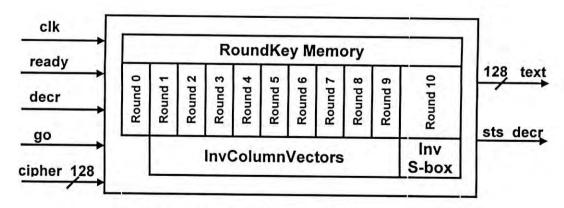

| Figure 5.3: | The decryption unit of the crypto-processor                        | 32 |

| Figure 5.4: | Key expansion unit                                                 | 33 |

| Figure 5.5: | Verilog design hierarchy of "Encryption" module                    | 33 |

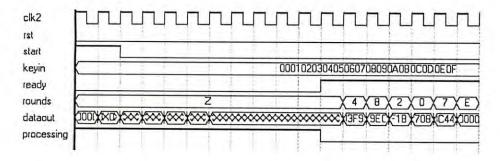

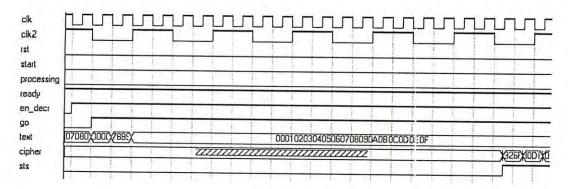

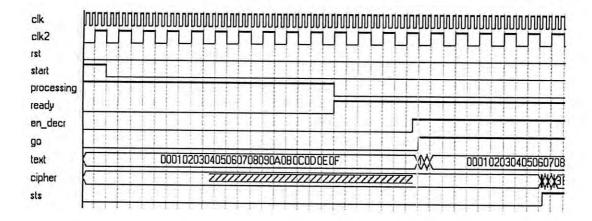

| Figure 6.1: | Simulation result of "KeyExpansion" module                         | 37 |

| Figure 6.2: | Simulation result of a full "Encryption" module                    | 37 |

| Figure 6.3: | Simulation result from start to cipher                             | 38 |

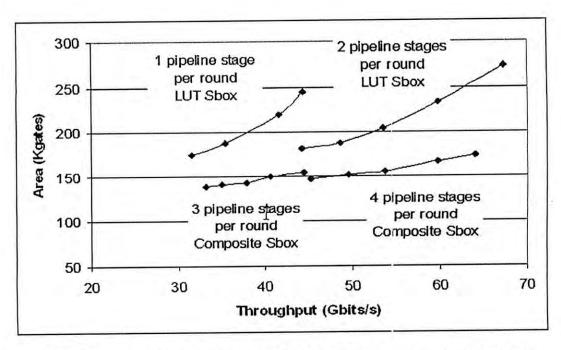

| Figure 6.4: | The throughput-area trade-off of the AES processor with online key | 40 |

|             | scheduling                                                         |    |

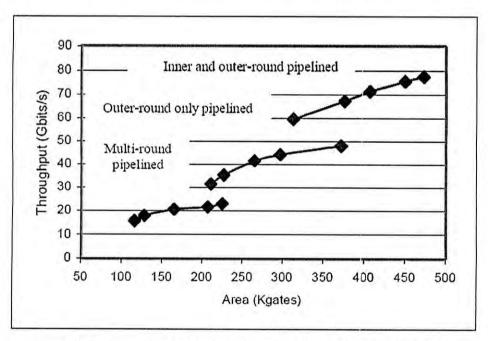

| Figure 6.5: | Area-throughput trade-off for the high speed pipelined AES         | 41 |

|             | implementations                                                    |    |

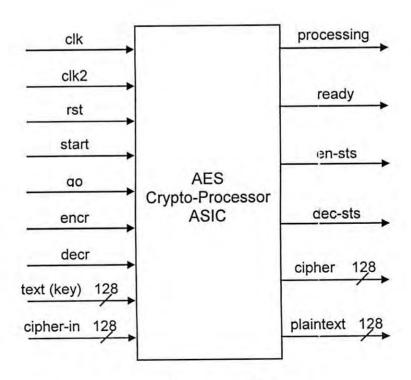

| Figure 6.6: | I/O Signals and Data Buses                                         | 42 |

# LIST OF TABLES

| Table 3.1: | S-box                                                    | 18 |

|------------|----------------------------------------------------------|----|

| Table 3.2: | Inverse S-box                                            | 21 |

| Table 4.1: | Transformations of a round                               | 23 |

| Table 6.1: | Timing analysis summary                                  | 39 |

| Table 6.2: | Comparison of this design with other FPGA implementation | 39 |

| Table 6.3: | Performance of AES ASIC on different pipeline stages     | 41 |

| Table 6.4: | Functions of I/O signals and data buses                  | 43 |

| Table A.1: | Column vectors                                           | 48 |

## LIST OF ABBREVIATIONS OF TECHNICAL SYMBOLS AND TERMS

3DES Triple-DES (Data Encryption Standard)

ACM Association for Computing Machinery

AES Advanced Encryption Standard

ALM Adaptive Logic Module – basic building block of Stratix family

ALUT Adaptive Look-Up Table

ASIC Application Specific Integrated Circuit

CBC Cipher Block Chaining

CFB Cipher Feedback

CHES Cryptographic Hardware and Embedded System

CLB Configurable Logic Block

DES Data Encryption Standard

DPA Differential Power Analysis

DSA Digital Signature Algorithm

DSP Digital Signal Processor

e.g. For example

EDA Electronic Design Automation

Eq. Equation

FIPS Federal Information Processing Standards

FIPS PUB Federal Information Processing Standards Publications

f<sub>MAX</sub> Maximum Clock Frequency

FPGA Field Programmable Gate Array

FPL Field Programmable Logic

Gbps Giga bits per second

GF Galois Field

GX Gigabit Transceiver

HDL Hardware Description Language

InvMixColumns() Inverse Mix Columns operation

InvSubBytes() Inverse Substitute Bytes operation

ISCAS International Symposium of Circuits And Systems

K Cipher Key

LAB Logic Array Block – a physically grouped set of logic cells

LC Logic Cell

LNCS Lecture Notes in Computer Science

LPM Library of Parameterized Module

LUT Look-Up Table

M4K Memory block of 4096 bits

M512 Memory block of 512 bits

MixColumns() Forward Mix Columns operation

M-RAM Mega RAM

NIST National Institute of Standards and Technology

PDA Personal Digital Assistant

PLD Programmable Logic Device

RAM Random Access Memory

Rcon[] The Round Constant word array

ROM Read Only memory

RotWord() A Function that performs a cyclic permutation

RSA Rivest-Shamir-Adelman

S-box A lookup table that holds non-linear substitute byte values

SubBytes() Forward Substitute Bytes operation

tco Clock-to-Output Time

th Hold Time

tpd Point-to-Point Delay

tsu Setup Time

VHDL Very High Speed Integrated Circuit Hardware Description

Language

Word A group of 32 bits

xor Exclusive-OR

Exclusive-OR operationSignal name or port name

" " Module name or citation

Matrix Multiplication

#### **ACKNOWLEDGEMENTS**

During the time I was performing my masters thesis, I came across many people who have supported and assisted me. First, I want to express my heartiest thanks to my supervisor, Dr. Md. Liakot Ali, for giving me the opportunity to do my masters thesis under his supervision. He encouraged me to involve in this promising and sophisticated field of advanced digital design. Without his continuous support, even in my personal matters, this thesis could not have been completed.

I gratefully acknowledge the valued advice and support from Professor Dr. M. A. Kashem Mia, and Professor Dr. S. M. Lutful Kabir, Director, IICT.

I also express my gratitude to the management of Biman Bangladesh Airlines Limited, where I have been doing my job, for giving me the permission for higher studies.

My special thanks go to all the authorities and staff of IICT, BUET.

I thank my beloved wife, Nilima Biswas Lata, for her boundless support in all respects, which helped me devote to the work.

Finally, I want to thank all my friends and family who helped me, making this work a nice experience.

#### **ABSTRACT**

Since demand for privacy and security of information are gradually emerging due to the rapid growth of information and communication technology, the research in protecting information for coming generation is getting enormous importance. Cryptographic algorithms form the fundamental aspect within this research field. The Advanced Encryption Standard (AES), the latest security algorithm, has added new dimension to cryptography with its potentiality of safeguarding the IT systems. Since the National Institute of Standards and Technology (NIST) accepted the AES to be the next generation IT security algorithm, a lot of research is going on to harness the power of AES in different security applications. For applications requiring high speed, hardware based implementation is the only choice. Since Application Specific Integrated Circuit (ASIC) is inherently ornamented with better performance than any other discrete system, ASIC based AES crypto-processor is anticipated to be the best solution for high-speed security mechanism.

This thesis presents the design of a crypto-processor ASIC to generate cryptographically secured information at a rate of multi-ten Gbps. The proposed novel crypto-processor addresses the next generation IT security requirements: the resistance against all attacks and high speed with low latency. This thesis uses AES algorithm as AES meets the first requirement, i.e. it is immune to all known attacks. Achieving high speed with AES algorithm is the main goal of this thesis. This work optimizes AES algorithm to eliminate algebraic operations from the datapath, which contributes to increase the processing speed and reduce the latency. By using loop unrolling, inner-round and outer-round pipelining techniques and offline key scheduling, this design can deliver secured data at ultra high speed. Thus, it becomes available for encryption on an optical link. The proposed crypto-processor is designed with Verilog HDL using Quartus II EDA software. The design is then simulated on a Stratix II GX FPGA device to test and verify the functional behavior and performance of the crypto-processor. The speed achieved on the FPGA is 36.16 Gbps. This design can be used to process data at a throughput of about 100 Gbps on ASIC technology.

# CHAPTER 1 INTRODUCTION

#### 1.1 Introduction:

This is the age of information and communication technology. The rapid growth in computer systems and their interconnections via networks has increased the dependence of both organizations and individuals on the information stored and communicated using these systems. This has increased the awareness of the need to protect data from disclosure, to guarantee data integrity and to protect systems from network-based attacks. To enforce security and privacy of information that is sent over the electronic communication media, a wide variety of security systems have been proposed and materialized. Keeping pace with the maturity of security technology, the hackers, the viruses, the electronic eavesdroppers and the electronic frauds have been coming into the field with new and sophisticated techniques of attacking existing security mechanisms. So, to breach and to supersede the technology of attacks, there must have a continual effort of developing new technologies for IT security. These phenomena show that IT security is an ever-ending research field for the researchers. This thesis is targeted to take the research on IT security one step ahead to next generation.

In today's information age, communications play an important role in e-commerce to satisfy the customers and business needs of this fast and high-tech global marketplace. In coming generation, the whole real world will be considered to be replicated in 'Cyber World'. To achieve this, high-speed communication infrastructure is being evolved to fulfill the requirements of transferring huge amount of data in minimum time. So, to avoid creating bottleneck in the high speed communication system, the IT security systems should equally have high speed. In summary, the security mechanisms for next generation IT security should address the challenging aspects like, (i) resistance against all attacks and (ii) high speed with low latency. These aspects of next generation IT security system are focused in this thesis to design the proposed security system. The first challenge is overcome by choosing the best available algorithm for IT security. Achieving high speed, the second challenge for next generation IT security, is the main focus of this thesis. The problem of latency, is also given importance so that it is kept minimum while gaining speed.

The cryptographic algorithm, also known as cipher, forms the fundamental aspect within the research field on IT security. On November 26, 2001, Advanced Encryption Standard (AES) was chosen by the National Institute of Standards and Technology (NIST) to be the replacement for Data Encryption Standard (DES) [1], the most used and analyzed cryptographic algorithm for last 25 years. The AES algorithm satisfies the following NIST statement: "Assuming that one could build a machine that could recover a DES key in a second, then it would take that machine approximately 149 trillion years to crack a 128-bit AES key [2]." Due to this outstanding feature of AES, the AES meets one of the two prominent requirements for next generation IT security system; i.e. the AES is resistant to all known attacks. So this thesis work uses the AES as security algorithm.

The AES algorithm is a safeguard against all sorts of attack. But as AES has eleven rounds of complex algebraic and matrix operation which create hinders against high speed operation. This thesis provides solution to achieving high speed by the combination of the following algorithm optimization and design techniques:

- i. ASIC Technology;

- ii. Removal of all algebraic operations from its datapath;

- iii. Offline key scheduling;

- iv. Loop unrolling;

- v. Outer and inner loop pipelining;

- vi. Use of memory blocks (ROM and RAM);

- vii. Reduction of stages per round.

Though pipelining is used here, the latency of the datapath is kept reasonably lower.

There are two ways to implement any algorithm, i.e. hardware or software. A software implementation offers only limited physical security. But hardware implementation, by nature, is more physically secure, as they cannot easily be read or modified by an outside attacker. The most significant disadvantage of software based solutions is that the speed performance is significantly lower than that based on hardware. This thesis addresses the hardware-based design for the applications requiring high speed security infrastructure. For implementing cryptographic applications in hardware, there are two ways: FPGA (Field Programmable Gate Arrays) technology and ASIC (Application Specific Integrated Circuit) technology.

FPGAs are flexible, because FPGAs contain programmable logic blocks that allow the same FPGA to be used in many different applications. For comparable performance, cost of FPGA devices is still a bottleneck in the case of mass production. For the FPGA based implementations, extra delays are introduced by the routing process. As a result of this speed penalty, the AES implemented in FPGA is typically slower than the same circuit implemented in an ASIC, assuming that both integrated circuits are fabricated using the same semiconductor technology (in particular, using the same transistor size). Furthermore, FPGA based devices consume more power than ASIC devices do. Hence this thesis is targeted to design of an ASIC.

# 1.2 Scope and Motivation

U.S. unveils AES as a new U.S. encryption standard for the federal government in hopes that industry will also embrace it. "AES will help the nation protect its critical information infrastructures and ensure privacy for personal information about individual Americans," Commerce Secretary Don Evans told an industry group [2]. The Commerce Department also said that the algorithm could be used without paying royalty fees [2]. It is estimated that AES has the potential to remain secure from key exhaustion attacks. These phenomena imply that AES will occupy the encryption market worldwide and will monopoly for many years. Therefore, a huge volume of AES products is necessary to meet the global market of security mechanism. Due to these attractive and motivational phenomena, this thesis targets to design IT security mechanism employing AES algorithm.

The Advanced Encryption Standard was accepted as a FIPS standard in November 2001 [1]. Since then, there have been different hardware realizations using ASIC and FPGA technology. References [3], [4], [5], [6], and [7] present the fastest FPGA realization of the AES algorithm. All of the architectures used in those works can achieve the throughput rate of several Gbits/s. The maximum throughput achieved is 21.54 Gbits/s on FPGA shown by [3].

References [8], [9], and [10] presents ASIC designs employing AES algorithm. The work [9] presented the possibilities of achieving a throughput of over 30 Gbits/s encryption, using a 0.18µm CMOS technology. The work [10] presented an AES processor that runs between 30 to 70 Gbits/s with minimum area cost. References

[11], [12], [13], and [14] present the implementation of other aspects (like low power, Differential Power Attack (DPA), Side channel analysis, etc.) of AES algorithm. This thesis work presents the techniques and the architectures as stated in section 1.1, which can achieve the throughput above 100 Gbps.

This crypto-processor will be designed using Verilog HDL with Quartus II development software. The Quartus II design environment ensures easy design entry and is a fully integrated, architecture-independent package for designing logic with Altera Programmable Logic Device (PLD). Quartus II supports several LPM functions and other mega-functions that allow implementing RAM and ROM. The generic, scalable nature of each of these functions ensures implementation of any supported type of RAM (synchronous or asynchronous). Then the design will be simulated and verified. Finally, after simulation and verification, this will be synthesized into ASIC.

Since the design of the proposed ASIC is in Verilog HDL, which is technology independent, the soft core can be reused in any new fabrication technology of this ever-changing technology environment. ASIC designs usually consume less power, show better performance and reliability and require smaller system size and shorter time to market. Therefore, the design of the crypto-processor in this thesis is ornamented with all the above advantages of the ASIC.

# 1.3 Objectives

The goal of this thesis is to design a high speed crypto-processor ASIC using AES algorithm. To meet the goal, the following objectives have been identified:

- Algorithm optimization;

- Design of a crypto-processor ASIC using Verilog HDL (Hardware Description Language);

- Design simulation using Quartus II development software;

- Analysis of throughput of the proposed design.

#### 1.4 Framework

The organization of this thesis is as follows. Chapter 2 provides the thesis background information. In this chapter the foundations and principles of cryptography and the AES architecture are overviewed. Furthermore, an overview of related work on the AES cipher is given. Chapter 3 discusses the AES algorithm in general. Chapter 4 provides the design issues and design architecture used for achieving high speed. The design hierarchy and design modules are described in chapter 5. Chapter 6 presents the results and performance of the design. Chapter 7 concludes the thesis and gives some suggestions for future work. References and appendices are provided following chapter 7.

# CHAPTER 2 THEORETICAL BACKGROUND

#### 2.1 Introduction:

This chapter describes foundations and principles of cryptography and different IT security needs. Furthermore, it also overviews related works on the AES cipher.

# 2.2 IT Security Needs

The importance of transmitting messages securely is not new. For millenniums, people have had a need to keep their communications private and secured [15]. Thousands of years ago, the Egyptian rulers, diplomats and defense personnel had been using different techniques of communicating messages among them so that the messengers or other people can not interpret the messages. In today's information age, communications play an important role which contributes to the growth of technology. Internet commerce, mobile commerce, electronic marketplace, electronic auction electronic payment system, e-governess, etc. are playing important role in e-commerce to satisfy the customers and business needs of this fast and high-tech global marketplace. Electronic security is increasingly involved in making communications more prevalent. Therefore, a mechanism is needed to assure the security and privacy of information that is sent over the electronic communications media. Information should be protected from unauthorized reception or interception at any cost no matter whether the communication media is wired or wireless. The Cryptography has been playing an important role in providing security mechanisms for information communication. History says that more than two thousand years back, Julius Caesar, the great, first used cipher (cryptography) technique as a security mechanism [16].

Until the last two decades, cryptography was the domain of the diplomatic and military world. But now the cryptography has been growing outside of military and diplomatic circles, and into public domain. Often there has been a need to protect information from 'prying eyes'. In this electronic age, information that could otherwise benefit or educate a group or individual can also be used against such groups or individuals. Industrial espionage among highly competitive businesses often requires that extensive security measures be put into place. And, those who wish to exercise their personal freedom, outside of the oppressive nature of

governments, may also wish to encrypt certain information to avoid suffering from the penalties of going against the wishes of those who attempt to control.

## 2.3 Overview of Cryptography

In this section ciphering definitions, methods and techniques are overviewed. This section is included as background information, since this thesis is about designing a high speed IT security mechanism with a cipher algorithm.

#### 2.3.1 Basic terminology and concepts

The term cryptography is derived from the Greek word "Kryptos". Kryptos is used to describe anything that is hidden, obscured, veiled, secret or mysterious. Cryptography, over the ages, has been an art. However over the past twenty years, cryptography has moved from an art perspective to a science perspective. Cryptography is the study of mathematical techniques related to aspects of information security such as privacy, data integrity, entity authentication, and data origin authentication.

The fundamental goal of cryptography is to prevent and detect cheating and other malicious activities. This goal is achieved by adequately addressing four frameworks. These four frameworks, which are commonly applied in network services, are described as follows:

- a. Confidentiality is a service used to keep the content of information away from all but those authorized to see it. Secrecy is a term synonymous with confidentiality and privacy. There are numerous approaches to provide confidentiality, ranging from physical protection to mathematical algorithms which render data unintelligible.

- b. Data integrity is a service which addresses the unauthorized alteration of data. To assure data integrity, one must have the ability to prevent data manipulation by unauthorized parties. Data manipulation includes such actions as insertion, deletion, substitution and multiplication.

- c. Authentication is a service related to identification. This service applies to both the sender and the receiver entity. To clarify, two parties initiated into a secure communication should first identify each other.

- d. Non-repudiation is a service which prevents a person/entity from denying previous commitments or actions. This service is desired in situations where, for example, one entity can authorize the purchase of property to another entity and later denies such authorization was granted. In practice the involvement of a trusted third party is necessary to resolve such disputes.

The cryptographic algorithms are the fundamental building blocks for the four frameworks that are described above. Each cryptographic algorithm is classified according to its characteristic features. The next section will overview these classifications and will describe the ciphering principles of each classification.

### 2.3.2 Ciphering techniques

There are three groups in which cryptographic algorithms can be classified, these are:

- symmetric cryptographic or secret-key algorithms;

- (ii) asymmetric cryptographic or public-key algorithms; and

- (iii) hash functions.

Algorithms of the first two classifications are key based techniques in which plain-text is transformed into cipher-text or vice versa. Plain-text is a state of data in which information is easily accessible. While, cipher-text is a state of data in which information is hard to reveal. The process of transforming plain-text into cipher-text is called encryption, while the process of transforming cipher-text into plain-text is called decryption. The cipher-text can be transformed back into the plain-text only by using a valid key.

The algorithms of the last classification, hash functions, are mathematical techniques, which map data of arbitrary length to certain unique value. Hash functions are commonly used in network services involving data integrity.

The characteristic feature of symmetric cryptographic algorithms is that both the encryption and decryption processes are accomplished by using the same key. On the other hand, in public-key algorithm, the encryption and decryption processes are accomplished by using different keys. More precisely, the encryption process is based on using a key that is easily available, while the decryption process is based on another key, which is only accessible to a specific person or entity. The key that is used for the encryption process is known as the public key, while the key that is used for the decryption process is known as the secret key. The strength of public-key algorithms is based on the fact that factorizing the product of both keys is a hard mathematical problem.

Data Encryption Standard (DES), Triple Data Encryption Standard (3DES) and Advanced Encryption Standard (AES) are secret-key algorithms; whereas Rivest-Shamir-Adleman (RSA) and Elliptic Curve Cryptosystem (ECC) are public-key algorithms. Public-key algorithms are commonly used in network services involving non-repudiation. The disadvantage of public-key algorithms is that considerable amount of computation capacity is needed for encrypting or decrypting large amounts of data. For high-speed considerations, the symmetric key cryptography is more suitable to encrypt a large amount of data. On the contrary, the asymmetric key cryptography is suitable for digital signature or computation of small and fixed data length. Symmetric key based algorithms are also classified into two enciphering techniques, namely: stream ciphers and block ciphers. The characteristic of stream ciphers is that the algorithm operates on smaller units of plain-text, usually bits. While block ciphers take a number of bits (known as blocks) and encrypt them as a single unit. The AES uses the block cipher technique.

# 2.3.3 Cryptanalysis

Cryptanalysis is the study of retrieving the plain-text without any knowledge of the valid key. A cipher is said to be breakable if a third party, without prior knowledge of the key, can systematically recover plain-text from the corresponding cipher-text. With the exhaustive search method, known as brute force attack, all possible keys are tried in order to reveal the plain-text.

There are three types of cryptanalysis techniques: (i) linear technique, (II) differential technique and (iii) side-channel technique.

- (i) Linear technique: The linear cryptanalysis takes advantage of input-output correlations over a few rounds of the cipher. This technique uses a linear approximation to describe the behavior of the block cipher. Given sufficient pairs of known plain-text and corresponding cipher-text, bits of information about the key can be obtained.

- (ii) Differential technique: The differential cryptanalysis is a type of cryptanalytic technique that appears to be most effective on block ciphers. This technique is based on the evolution of the differences made in two related plain-texts encrypted with the same key.

- (iii) Side-channel technique: The side-channel cryptanalysis techniques are based on timing, fault and power analysis of systems. For example, the power consumption of the electrical components is logged to deduce secret information like the encrypting key. In practice, sometimes devices are tampered in order to have it perform some erroneous operations. All these techniques are used within the framework of revealing the secret key or the secret information.

## 2.4 The Origins of AES

The most used and analyzed cryptographic algorithm is the Data Encryption Standard (DES). Introduced in the early 70s, DES became the encryption standard in 1977. In 1983 it was shown that DES cipher is vulnerable due to its short key length (64-bit). Therefore, an enhanced version of the cipher was introduced. This enhanced version, known as Triple-DES (3DES), performs DES three times sequentially and therefore it is more secure than DES. However, the speed performance of 3DES was not interesting for practical applications. Therefore in 1997, the National Institute of Standards and Technology (NIST) organized a contest in order to develop a new cryptographic algorithm standard which would replace both DES and Triple-DES [16]. On November 26, 2001, the algorithm known as Rijndael (pronounced Rhine-dall) was chosen to be the replacement for DES and since then it is known as the Advanced Encryption Standard (AES) [17].

#### 2.5 AES Performance on Different Platform

Various aspects of the AES algorithm have been investigated. One is the performance of the algorithm. Several organizations have implemented the AES algorithm on several platforms. Most of the results are published and are available on Internet [16]. Depending on the platform, the AES speed performance varies from several Mbit to a few Gbit per second. Another AES research aspect is the methodology of breaking the cipher. Nowadays, new cryptanalysis techniques and algorithms are being developed in order to break the AES cipher.

All the AES implementations can be classified into two groups: software based implementations and hardware based implementations. The software based implementations are designed and coded in programming languages, such as C, C++, Java, and assembly. These implementations are executed, e.g. on general-purpose microprocessors, Digital Signal Processors (DSP), and micro-controllers (such as smart cards). The hardware based implementations are designed and coded in hardware description languages, such as VHDL and Verilog HDL, and finally synthesized into Application Specific Integrated Circuits (ASICs) or Field Programmable Gate Arrays (FPGA).

The efficiency of cryptographical implementations in both software and hardware is generally characterized by several parameters. One of these parameters is speed performance and it is expressed by the throughput. Throughput is defined as the number of bits that are processed in a second. For the encryption process, the throughput is defined as the number of bits encrypted in a second. Similarly, for the decryption process, the throughput is defined as the number of bits decrypted in a second. Since throughput depends on the platform environment and therefore it does not always characterize the efficiency of an implementation, it is often accompanied by the parameter latency. Latency is defined as the time that is required to complete the processing of one data block and is usually expressed in number of clock cycles.

Another parameter that characterizes the implementation efficiency is size. In software based designs this parameter is related to the size of the binary code that is compiled for a certain machine. In systems with memory shortage, such as wireless systems and smart cards, this parameter becomes often the most important

design criterion. For example, developers who secures systems like wireless phones and personal digital assistants (PDAs), often make trade-offs between code size and throughput. For hardware based designs, the parameter, size, is related to the silicon area of the synthesized circuit. Dependent on what technology is used, there are various ways for expressing the size of a synthesized circuit. In the ASIC technology, the occupied area, or in short area, is expressed in the terms of equivalent transistors or logic gates. In the FPGA based solutions, area is expressed in the terms of basic building blocks. Dependent on the FPGA vendor, a basic building block is either expressed in Configurable Logic Block (CLB) or in Logic Cells (LC). Various FPGA vendors also give an equivalent logic gate number of the FPGA device. Another parameter, which is used to characterize the efficiency, is the power consumption. This parameter represents the energy that the design consumes and it is usually expressed in Watts or Milli Watts. For low power systems, this is the most critical parameter. Since the system environment sets the critical parameter for a design, it is often impossible to compare various designs in an efficient way.

#### **CHAPTER 3**

#### THE AES ALGORITHM

#### 3.1 Introduction

The Rijndael algorithm, referred to as the AES Algorithm, is a symmetric key block cipher that can process data blocks of 128 bits, using cipher keys with lengths of 128, 192, and 256 bits. For high speed design, this thesis uses the AES algorithm with key lengths of 128 bits. So this chapter describes the algorithm using 128 bits cipher key.

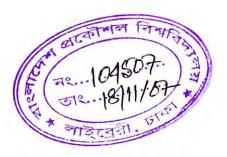

#### 3.2 The State

The AES algorithm's internal operations are performed on a two dimensional array of bytes called state. The state consists of 4 rows of bytes and each row has 4 bytes. Each byte is denoted by  $S_{i,\,j}$  ( $0 \le i < 4,\,0 \le j < 4$ ). The four bytes in each column of the state array form a 32-bit word, with the row number as the index for the four bytes in each word. At the beginning of encryption or decryption, the array of input bytes is mapped to the state array as illustrated in Fig. 3.1, assuming a 128-bit block can be expressed as 16 bytes:  $in_0$ ,  $in_1$ ,  $in_2$  ...  $in_{15}$ . The encryption/decryption are performed on the state, at the end of which the final value is mapped to the output bytes array  $out_0$ ,  $out_1$ ,  $out_2$  ...  $out_{15}$ .

Figure 3.1: Mapping of input bytes, state array and output bytes

Hence, the relation of the input array, state array and output array follows the following scheme:

$$S[i,j] = in[I,4j] \qquad \text{and} \quad out[I,4j] = s[i,j] \qquad \text{for } 0 \le i < 4 \text{ and } 0 \le j < 4,$$

#### 3.3 The AES Structure

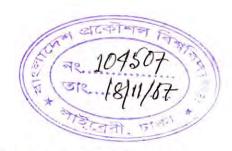

Figure 3.2 depicts the overall structure of AES. The input to the encryption and decryption process is a single 128-bit block. This block is copied into the state, as mentioned in section 3.2, which is modified at each stage of encryption or decryption. After the final stage, the state is copied to an output matrix.

Figure 3.2: AES encryption and decryption

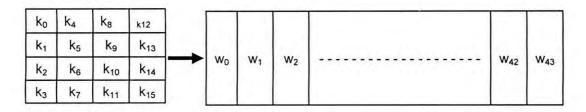

Similarly, the 128-bit key is depicted as a square matrix of bytes. This matrix is by column, i.e. the first four bytes occupy the first column and so on. This key is then expanded into an array of 44 words, said to be 'w' matrix, as illustrated in figure 3.3. Each word is 4-byte (32-bit) long. Four consecutive words serve as a round key for each round. The key expansion algorithm is described in section 3.5.

Figure 3.3: Key and expanded key

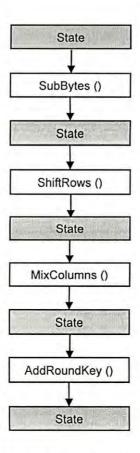

Four different stages are used, one for permutation and three for substitutions. Figure 3.4 depicts the structure of a full encryption round. The stages are as follows:

Figure 3.4: A full encryption round

- Substitute bytes: This function uses an S-box to perform a byte-by-byte substitution of the block. For encryption and decryption, this function is indicated by SubBytes () and InvSubBytes () respectively.

- Shift rows: This is a simple permutation. For encryption and decryption, this function is indicated by ShiftRows () and InvShiftRows () respectively.

- Mix Columns: This is a substitution that makes use of arithmetic over GF(2<sup>8</sup>), with the irreducible polynomial m(x) = x<sup>8</sup> + x<sup>4</sup> + x<sup>3</sup> + x +1. For encryption and decryption, this function is indicated by MixColumns () and InvMixColumns () respectively.

- Add round key: This function does a bitwise XOR operation of the current block with a portion of the expanded key. For both encryption and decryption this function is indicated by AddRoundKey ().

For both encryption and decryption, the algorithm starts with an add round key stage, followed by nine rounds, each of which contains all four stages; and then followed by a tenth round containing three stages, excluding Mix columns stage.

Each stage is reversible. For SubBytes (), ShiftRows () and MixColumns () stages, there are corresponding inverse function - InvSubBytes (), InvShiftRows () and InvMixColumns (). For the AddRoundKey () stage, the inverse is achieved by XORing the same round key to the block, using the result:  $A \oplus A \oplus B = B$ . The decryption process makes use of the expanded key in reverse order. The decryption process is not identical to the encryption algorithm. This is a consequence of the particular structure of AES.

# 3.4 Encryption

At the beginning of encryption, the input is copied to the state array as described in section 3.2. After an initial round key addition, the state array is transformed into

final state by implementing a round function 10 times. The final state is then copied to the output. The pseudo code for the encryption process is shown in Figure 3.5.

```

Encryption(byte in[16], byte out[16], word w[44])

begin

byte state[16]

state = in

AddRoundKey(state, w[0, 3])

// Section, 3.4.4

for round = 1 step 1 to 9

SubBytes(state)

// Section 3.4.1

ShiftRows(state)

// Section 3.4.2

MixColumns(state)

// Section 3.4.3

AddRoundKey(state, w[round*4, (round+1)*3]) // Section 3.4.4

end for

SubBytes(state)

ShiftRows(state)

AddRoundKey(state, w[40, 43])

out = state

end

```

Figure 3.5: Pseudo code for the encryption

The individual transformations - SubBytes(), ShiftRows(), MixColumns(), and AddRoundKey() - process the states and are described in the following subsections. The array w[] contains the key schedule, which is described in section 3.5.

## 3.4.1 SubBytes() transformation

The **SubBytes()** is a simple lookup table. This transformation is a non-linear byte substitution that operates independently on each byte of the state using a  $16\times16$  matrix of byte values, called 'S-box'. This S-box is constructed by first computing the multiplicative inverse of each element in  $GF(2^8)$  with irreducible polynomial  $m(x) = x^8 + x^4 + x^3 + x + 1$ , the element  $\{00\}$  is mapped to itself. Then an affine transformation is applied which can be expressed in matrix form as:

$$\begin{bmatrix} b'_0 \\ b'_1 \\ b'_2 \\ b'_3 \\ b'_4 \\ b'_5 \\ b'_6 \\ b'_7 \end{bmatrix} = \begin{bmatrix} 1 & 0 & 0 & 0 & 1 & 1 & 1 & 1 \\ 1 & 1 & 0 & 0 & 0 & 1 & 1 & 1 \\ 1 & 1 & 1 & 0 & 0 & 0 & 1 & 1 \\ 1 & 1 & 1 & 1 & 0 & 0 & 0 & 1 \\ 1 & 1 & 1 & 1 & 1 & 0 & 0 & 0 \\ 0 & 1 & 1 & 1 & 1 & 1 & 0 & 0 \\ 0 & 0 & 1 & 1 & 1 & 1 & 1 & 0 \\ 0 & 0 & 0 & 1 & 1 & 1 & 1 & 1 \end{bmatrix} \begin{bmatrix} b_0 \\ b_1 \\ b_2 \\ b_3 \\ b_4 \\ b_5 \\ b_6 \\ b_7 \end{bmatrix} + \begin{bmatrix} 1 \\ 1 \\ 0 \\ 0 \\ 0 \\ 1 \\ 1 \\ 0 \end{bmatrix}$$

where b<sub>i</sub> is the i<sup>th</sup> bit of a byte. Here and elsewhere, a prime on a variable (e.g., b'<sub>i</sub>) indicates that the variable is to be updated with the value on the right.

The Table 3.1 shows the substitution byte values of S-box.

Table 3.1: S-box

|   |   | -  |    |    |    |    |    |    |    |    |    |    |    |    |    |    |     |

|---|---|----|----|----|----|----|----|----|----|----|----|----|----|----|----|----|-----|

|   |   |    |    |    |    |    |    |    |    | /  |    |    |    |    |    |    |     |

|   |   | 0  | 1  | 2  | 3  | 4  | 5  | 6  | 7  | 8  | 9  | Α  | В  | С  | D  | E  | F   |

|   | 0 | 63 | 7C | 77 | 7B | F2 | 6B | 6F | C5 | 30 | 01 | 67 | 2B | FE | D7 | AB | 76  |

|   | 1 | CA | 82 | C9 | 7D | FA | 59 | 47 | F0 | AD | D4 | A2 | AF | 9C | A4 | 72 | CO  |

|   | 2 | B7 | FD | 93 | 26 | 36 | 3F | F7 | CC | 34 | A5 | E5 | F1 | 71 | D8 | 31 | 15  |

|   | 3 | 04 | C7 | 23 | C3 | 18 | 96 | 05 | 9A | 07 | 12 | 80 | E2 | EB | 27 | B2 | 75. |

|   | 4 | 09 | 83 | 2C | 1A | 1B | 6E | 5A | A0 | 52 | 3B | D6 | В3 | 29 | E3 | 2F | 84  |

|   | 5 | 53 | D1 | 00 | ED | 20 | FC | B1 | 5B | 6A | СВ | BE | 39 | 4A | 4C | 58 | CF  |

|   | 6 | D0 | EF | AA | FB | 43 | 4D | 33 | 85 | 45 | F9 | 02 | 7F | 50 | 3C | 9F | A8  |

|   | 7 | 51 | A3 | 40 | 8F | 92 | 9D | 38 | F5 | ВС | B6 | DA | 21 | 10 | FF | F3 | D2  |

| X | 8 | CD | 0C | 13 | EC | 5F | 97 | 44 | 17 | C4 | A7 | 7E | 3D | 64 | 5D | 19 | 73  |

|   | 9 | 60 | 81 | 4F | DC | 22 | 2A | 90 | 88 | 46 | EE | B8 | 14 | DE | 5E | 0B | DB  |

|   | Α | E0 | 32 | 3A | 0A | 49 | 06 | 24 | 5C | C2 | D3 | AC | 62 | 91 | 95 | E4 | 79  |

|   | В | E7 | C8 | 37 | 6D | 8D | D5 | 4E | A9 | 6C | 56 | F4 | EA | 65 | 7A | AE | 08  |

|   | С | BA | 78 | 25 | 2E | 1C | A6 | B4 | C6 | E8 | DD | 74 | 1F | 4B | BD | 8B | 8A  |

|   | D | 70 | 3E | B5 | 66 | 48 | 03 | F6 | 0E | 61 | 35 | 57 | B9 | 86 | C1 | 1D | 9E  |

|   | Е | E1 | F8 | 98 | 11 | 69 | D9 | 8E | 94 | 9B | 1E | 87 | E9 | CE | 55 | 28 | DF  |

|   | F | 8C | A1 | 89 | 0D | BF | E6 | 42 | 68 | 41 | 99 | 2D | 0F | B0 | 54 | BB | 16  |

The substitution strategy is that the four most significant bits of each state element are used for the row index, while the rest are used for the column index.

## 3.4.2 ShiftRows() transformation

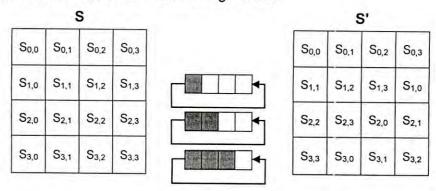

In this transformation, the bytes in the first row of the State do not change. The second, third, and fourth rows shift cyclically to the left one byte, two bytes, and three bytes, respectively, as illustrated in Figure 3.6.

Figure 3.6: Shift row transformation

## 3.4.3 MixColumns() transformation

The MixColumns transformation operates on each column of the state matrix individually. Each byte of a column is mapped into a new value that is a function of all four bytes in the column. The transformation can be defined by the following matrix multiplication on state:

$$\begin{bmatrix} 02 & 03 & 01 & 01 \\ 01 & 02 & 03 & 01 \\ 01 & 01 & 02 & 03 \\ 03 & 01 & 01 & 02 \end{bmatrix} \begin{bmatrix} S_{0,0} & S_{0,1} & S_{0,2} & S_{0,3} \\ S_{1,0} & S_{1,1} & S_{1,2} & S_{1,3} \\ S_{2,0} & S_{2,1} & S_{2,2} & S_{2,3} \\ S_{3,0} & S_{3,1} & S_{3,2} & S_{3,3} \end{bmatrix} = \begin{bmatrix} S'_{0,0} & S'_{0,1} & S'_{0,2} & S'_{0,3} \\ S_{1,0} & S'_{1,1} & S'_{1,2} & S'_{1,3} \\ S'_{2,0} & S'_{2,1} & S'_{2,2} & S'_{2,3} \\ S_{3,0} & S'_{3,1} & S'_{3,2} & S'_{3,3} \end{bmatrix}$$

# 3.4.4 AddRoundKey() transformation

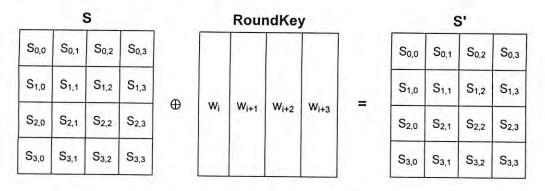

In AddRoundKey transformation, a RoundKey is added to the state by bitwise Exclusive-OR (XOR) operation. Each RoundKey consists of 4 words (128 bits) generated from Key Expansion described in section 3.5. As shown in Figure 3.7, the XOR operation is viewed as a column-wise operation between the 4 bytes of a state column and one word of the round key.

Figure 3.7: Add round key transformation

# 3.5 Key Expansion

In the AES algorithm, Key Expansion generates a total of 44 words. The key, K, is used as the initial set of 4 words, and the rest of the words are generated from the key iteratively. The output of Key Expansion is an array of 4-byte words denoted by  $w_i$ , where  $0 \le i < 44$ . Each RoundKey is a concatenation of 4 words from the output of Key Expansion, RoundKey(i) =  $(w_{4i}, w_{4i+1}, w_{4i+2}, w_{4i+3})$ . The Key Expansion scheme can be expressed by the pseudo code shown in Figure 3.8.

```

KeyExpansion (byte key[16], word w[44])

begin

word temp

i = 0

while (i < 4)

w[i] = (key[4*i], key[4*i+1], key[4*i+2], key[4*i+3])

end while

i = 4

while (i < 44)

temp = w[i-1]

if (i mod 4 = 0)

temp = SubWord(RotWord(temp)) xor Rcon[i/4]

end if

w[i] = w[i-4] xor temp

i = i + 1

end while

end

```

Figure 3.8: Pseudo code for key expansion

SubWord in Figure 3.8 performs a byte substitution on each byte of its input word using the S-box (Table 3.1). The function RotWord rotates each byte in a word one position to the left. Rcon(j) is the round constant word array and is defined as Rcon(j) = [RC(j),  $\{00\}$ ,  $\{00\}$ ,  $\{00\}$ ]. Where, RC[j] =  $x^{j-1}$ , with  $x^{j-1}$  being powers of x (x is denoted as  $\{02\}$ ) in the field GF( $2^8$ ). The values of RC(j) in hexadecimal are as follows:

| J     | 1  | 2  | 3  | 4  | 5  | 6  | 7  | 8  | 9  | 10 |

|-------|----|----|----|----|----|----|----|----|----|----|

| RC[j] | 01 | 02 | 04 | 08 | 10 | 20 | 40 | 80 | 1R | 36 |

# 3.6 Decryption

The encryption process as described in section 3.4 can be inverted and then implemented in reverse order to produce straightforward decryption cipher. The sequence of transformations for decryption differs from that for encryption. But the form of the key schedule for encryption and decryption are the same. An encryption

round has the structure of SubBytes(), ShiftRows(), MixColumns() and AddRoundKey(). Whereas the standard decryption round has the structure InvShiftRows(), InvSubBytes(), AddRoundKey() and InvMixColumns(). This has the disadvantage that two separate modules are needed for applications that require both encryption and decryption.

### 3.6.1 InvShiftRows() transformation

InvShiftRows() is the inverse of the ShiftRows() transformation. This performs the circular shifts in the opposite direction for each of the last three rows with one-byte circular right shift for the second row, two-byte circular right shift for the third row and three-byte circular right shift for the fourth row.

#### 3.6.2 InvSubBytes() transformation

The transformation uses the inverse S-box as shown in Table 3.4.

y 0 2 1 3 4 5 8 В C F D 52 09 6A D5 30 36 A5 38 BF 40 A3 9E 81 F3 D7 FB 7C E3 39 82 1 9B 2F FF 87 34 8E 43 44 C4 DE E9 CB 2 54 **7B** 32 94 A6 C2 23 3D EE 4C 95 0B 42 FA 4E 08 2E A1 66 28 D9 24 **B2** 76 5B A2 49 6D 8B D1 25 4 72 F8 F6 64 86 68 98 16 D4 A4 5C CC 5D 65 92 6C 5 70 48 50 FD ED **B9** DA 5E 15 46 57 A7 8D 9D 84 6 90 D8 AB 00 8C BC D3 0A F7 E4 58 05 **B8 B3** 45 06 7 D0 2C 8F 1E CA 3F OF 02 C1 AF BD 03 01 13 8A 6B X 8 3A 91 11 41 4F 67 DC EA 97 F2 CF CE F0 **B4** E6 73 96 AC 9 74 22 E7 AD 35 85 E2 F9 37 **E8** 1C 75 DF 6E 47 F1 71 A 1A 1D 29 C5 89 6F **B7** 0E 62 AA BE 18 1B B FC 56 3E **4B** C6 D2 79 20 DB 9A CO FE 78 F4 CD 5A C 1F DD A8 33 88 07 C7 31 **B1** 12 59 10 27 80 EC 5F 60 51 7F A9 19 D **B5** 4A 0D 2D E5 **7A** 9F 93 C9 9C EF A0 E0 **3B** 4D AE 2A F5 BO C8 EB BB 3C 83 53 99 61 17 2B 04 7E BA 77 D<sub>6</sub> 26 E1 69 14 63 55 21 OC 7D

Table 3.2: Inverse S-box

This is obtained by applying the inverse of the affine transformation (section 3.4) followed by taking the multiplicative inverse in GF(2<sup>8</sup>). This transformation is depicted in matrix form as follows:

$$\begin{bmatrix} b'_0 \\ b'_1 \\ b'_2 \\ b'_3 \\ b'_4 \\ b'_5 \\ b'_6 \\ b'_7 \end{bmatrix} = \begin{bmatrix} 0 & 0 & 1 & 0 & 0 & 1 & 0 & 1 \\ 1 & 0 & 0 & 1 & 0 & 0 & 1 & 0 \\ 0 & 1 & 0 & 0 & 1 & 0 & 0 & 1 \\ 1 & 0 & 1 & 0 & 0 & 1 & 0 & 0 \\ 0 & 1 & 0 & 1 & 0 & 0 & 1 & 0 \\ 0 & 0 & 1 & 0 & 1 & 0 & 0 & 1 \\ 1 & 0 & 0 & 1 & 0 & 1 & 0 & 0 \\ 0 & 1 & 0 & 0 & 1 & 0 & 1 & 0 \\ 0 & 1 & 0 & 0 & 1 & 0 & 1 & 0 \\ 0 & 0 & 0 & 0 & 1 & 0 & 1 & 0 \end{bmatrix} \begin{bmatrix} b_0 \\ b_1 \\ b_2 \\ b_3 \\ b_4 \\ b_5 \\ b_6 \\ b_7 \end{bmatrix} + \begin{bmatrix} 1 \\ 0 \\ 1 \\ 0 \\ 0 \\ 0 \\ 0 \\ 0 \end{bmatrix}$$

## 3.6.3 Inverse AddRoundKey() transformation

The inverse AddRoundKey() transformation is identical to the AddRoundKey() transformation used in encryption, since the XOR operation is its own inverse.

#### 3.6.4 InvMixColumns() transformation

The InvMixColumns() transformation operates on each column of the state matrix individually. Each byte of a column is mapped into a new value that is a function of all four bytes in the column. The transformation can be defined by the following matrix multiplication on state:

$$\begin{bmatrix} 0\mathsf{E} & 0\mathsf{B} & 0\mathsf{D} & 0\mathsf{9} \\ 0\mathsf{9} & 0\mathsf{E} & 0\mathsf{B} & 0\mathsf{D} \\ 0\mathsf{D} & 0\mathsf{9} & 0\mathsf{E} & 0\mathsf{B} \\ 0\mathsf{B} & 0\mathsf{D} & 0\mathsf{9} & 0\mathsf{E} \end{bmatrix} \begin{bmatrix} \mathsf{S}_{0,0} & \mathsf{S}_{0,1} & \mathsf{S}_{0,2} & \mathsf{S}_{0,3} \\ \mathsf{S}_{1,0} & \mathsf{S}_{1,1} & \mathsf{S}_{1,2} & \mathsf{S}_{1,3} \\ \mathsf{S}_{2,0} & \mathsf{S}_{2,1} & \mathsf{S}_{2,2} & \mathsf{S}_{2,3} \\ \mathsf{S}_{3,0} & \mathsf{S}_{3,1} & \mathsf{S}_{3,2} & \mathsf{S}_{3,3} \end{bmatrix} = \begin{bmatrix} \mathsf{S}'_{0,0} & \mathsf{S}'_{0,1} & \mathsf{S}'_{0,2} & \mathsf{S}'_{0,3} \\ \mathsf{S}_{1,0} & \mathsf{S}'_{1,1} & \mathsf{S}'_{1,2} & \mathsf{S}'_{1,3} \\ \mathsf{S}'_{2,0} & \mathsf{S}'_{2,1} & \mathsf{S}'_{2,2} & \mathsf{S}'_{2,3} \\ \mathsf{S}_{3,0} & \mathsf{S}'_{3,1} & \mathsf{S}'_{3,2} & \mathsf{S}'_{3,3} \end{bmatrix}$$

#### **CHAPTER 4**

# HIGH SPEED DESIGN CONSIDERATIONS

## 4.1 Introduction

This chapter provides the aspects of the AES algorithm optimization which contribute to gain high processing speed of the crypto-processor. Though getting high speed is the main objective, the other such as the silicon area and the power consumption of the ASIC are also given importance to make the design altogether a competitive product.

# 4.2 Algorithm Optimization

Table 4.1 shows four transformations expressed in algebraic and matrix form.

Table 4.1: Transformations of a round

| Functions                       | Expressions                                                                                                                                                                                                                                                      |

|---------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| SubBytes() Transformation       | $b_{i,j} = S[a_{i,j}]$ , where $S[a_{i,j}]$ input matrix                                                                                                                                                                                                         |

| ShiftRows()Transformation       | $\begin{bmatrix} c_{0,j} \\ c_{1,j} \\ c_{2,j} \\ c_{3,j} \end{bmatrix} = \begin{bmatrix} b_{0,j} \\ b_{1,j-1} \\ b_{2,j-2} \\ b_{3,j-3} \end{bmatrix}$                                                                                                          |

| MixColumns()Transformation      | $\begin{bmatrix} d_{0,j} \\ d_{1,j} \\ d_{2,j} \\ d_{3,j} \end{bmatrix} = \begin{bmatrix} 02 & 03 & 01 & 01 \\ 01 & 02 & 03 & 01 \\ 01 & 01 & 02 & 03 \\ 03 & 01 & 01 & 02 \end{bmatrix} \begin{bmatrix} c_{0,j} \\ c_{1,j} \\ c_{2,j} \\ c_{3,j} \end{bmatrix}$ |

| AddRoundKey()<br>Transformation | $\begin{bmatrix} e_{0,j} \\ e_{1,j} \\ e_{2,j} \\ e_{3,j} \end{bmatrix} = \begin{bmatrix} d_{0,j} \\ d_{1,j} \\ d_{2,j} \\ d_{3,j} \end{bmatrix} \oplus \begin{bmatrix} k_{0,j} \\ k_{1,j} \\ k_{2,j} \\ k_{3,j} \end{bmatrix}$                                  |

In the ShiftRows equation, the column indices are taken mod 4. All of these expressions of the four transformations can be combined into a single equation:

$$\begin{bmatrix} c_{0,j} \\ c_{1,j} \\ c_{2,j} \\ e_{3,j} \end{bmatrix} = \begin{bmatrix} 02 & 03 & 01 & 01 \\ 01 & 02 & 03 & 01 \\ 01 & 01 & 02 & 03 \\ 03 & 01 & 01 & 02 \end{bmatrix} \begin{bmatrix} S[a_{0,j}] \\ S[a_{2,j-2}] \\ S[a_{3,j-3}] \end{bmatrix} \oplus \begin{bmatrix} k_{0,j} \\ k_{1,j} \\ k_{2,j} \\ k_{3,j} \end{bmatrix} = \begin{bmatrix} 02 \\ 01 \\ 01 \\ 03 \end{bmatrix} \bullet S[a_{0,j}] \\ \oplus \begin{bmatrix} 03 \\ 02 \\ 01 \\ 01 \end{bmatrix} \bullet S[a_{0,j-1}] \\ \oplus \begin{bmatrix} 01 \\ 03 \\ 02 \\ 01 \end{bmatrix} \bullet S[a_{0,j-2}] \\ \oplus \begin{bmatrix} 01 \\ 01 \\ 03 \\ 02 \\ 01 \end{bmatrix} \bullet S[a_{0,j-2}] \\ \oplus \begin{bmatrix} 01 \\ 01 \\ 03 \\ 02 \\ 01 \end{bmatrix} \bullet S[a_{0,j-2}] \\ \oplus \begin{bmatrix} k_{0,j} \\ k_{1,j} \\ k_{2,j} \\ k_{3,j} \end{bmatrix}$$

... ... [Eq. 1]

This shows that matrix multiplication can be expressed as a linear combination of vectors. As a result, an implementation based on the equation 1 requires only four table lookups per column per round. These tables can be pre-calculated and stored in memories. Each table takes as input a byte value of the input state matrix and provides a 32-bit wide column vector. This column vectors are shown in Table A.1 of Appendix A.

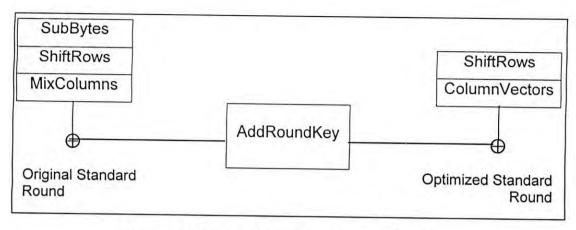

The nine rounds, starting from second round to tenth round, are identical and are said to be standard round, since they have all four stages in original AES algorithm. A standard round of original algorithm has four stages whereas the standard round of the optimized algorithm has only three stages as in Figure 4.1.

Figure 4.1: Standard round of optimized algorithm

# 4.3 Benefits of Optimized Algorithm

This algorithm optimization eliminates the need for using S-box for the standard rounds. This also eliminates the most speed expensive algebraic operation, i.e. the matrix multiplication of the MixColumns transformation. So, a standard round will have only table lookups for column vectors and XOR operations with round key and column vectors. This is the most important and unique consideration for the proposed design of this thesis work. As the column vectors of 16 elements (Byte value) can be fetched in one cycle rather than calculated sequentially, we can say this parallel processing. The algebraic operations are vulnerable to cryptanalysis and require more power. So the proposed design will consume relatively less power and will be secured against algebraic attack.

# 4.4 Offline Key Expansion

The key expansion process can be accomplished in one of two ways: using hardware or using software. In later case, the round keys would be generated using software and be stored in memory for subsequent use. This can save a significant number of gates and reduce the total power consumption, but needs external support. As this thesis is to provide a standalone system, the first way of key scheduling is used.

The key expansion process in standalone crypto-processor can be on-line or offline. The key expansion algorithm inherently expands the AES key in the order that the encryption process requires the round-keys. In this way, a round key generation block can provide encryption round-keys as they are required, in the correct order in real-time; no buffering of these round keys is necessary. As this work uses the optimized algorithm reducing the number of stages per round, this on-line key scheduling is not feasible. Moreover, for decryption, where round-keys are required in reverse order, there is no way of algorithmically producing the inverse round-keys in the correct order directly from the supplied AES encryption key.

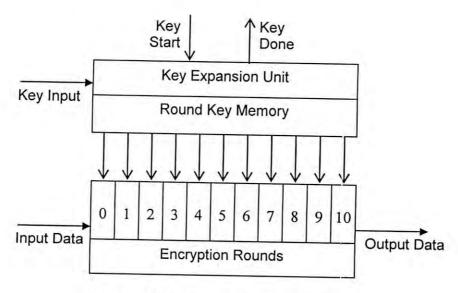

In on-line key expansion process, the round keys are calculated for each session that remains constant during the whole session. In this approach, for a particular session, first the offline key expansion unit calculates all the required round keys for each round and stores them in memories. Then the encryption data-path performs the AES algorithm on the input data samples and uses the stored round key values for the key addition stage of a round. The off-line key scheduling is shown in Figure 4.2.

Figure 4.2: Offline RoundKey addition

# 4.5 Design Architecture

To generate high throughputs, this work uses the loop unrolling and pipelined architecture and incorporates parallel processing for encryption and decryption.

# 4.5.1 Loop unrolling

The AES algorithm has round loops. For high speed design the AES iteration loop has to be unrolled. If the datapath is shared in different iteration, the datapath can not be pipelined and the throughput significantly decreases. As the key scheduling used in this design is off-line, this does not have influence on the throughput of the encryption and decryption datapath. So key scheduling is not unrolled.

#### 4.5.2 Pipelining

The AES encryption and decryption processes have 11 rounds. If all the rounds are calculated in one clock cycle, the clock signal requires high time period which eventually decreases throughput. The time period of the clock can be reduced if the whole datapath is calculated in several clock cycles. But this does not increase the throughput rather further decreases in throughput occurs. The highest possible throughput can be achieved when each output sample is generated in every clock. This is possible when pipelining architecture is used.

# 4.5.3 Outer round pipelining

Encryption and decryption datapath of AES comprise 11 rounds. For pipelining purpose, each round is calculated every cycle; in other words, in each cycle all the rounds are calculated. In a particular cycle, each round gets input from the output generated by the preceding round in the previous cycle and generates output for the use as input to the following round in the next cycle. Thus the first round takes input samples every cycle and the last round generates output sample every cycle. The throughput can be calculated by dividing the number of bits in output samples by the time period of the clock cycle. So by using pipelining, throughput is increased, since output is generated every cycle. If there is one pipeline stage for each round, it is referred to as outer round pipelining. So there are 11 outer-round pipelining stages for encryption and decryption datapath.

# 4.5.4 Inner round pipelining

In the optimized AES algorithm, each standard round has three operations: table lookup for column vectors, shifting and XORing. The shifting operation can be done by simple interconnection which produces negligible amount of delay. Three operations of a round are further pipelined. In one pipeline stage, fetching of data from the memory for column vectors and shifting operation is performed

concurrently. In another pipeline stage, the key addition (XOR) operation is done. So each standard round is performed in two pipeline stages. Further pipelining is also possible but it increases the throughput a bit with exponentially increasing area which is not a cost effective solution. As this pipelining is done within a round it is termed as inner round pipelining.

The first round of the encryption and decryption datapath has only one operation - the key addition (XORing). This round is performed in one clock cycle. The eleventh round of the original AES algorithm has three operations: byte substitution, byte shifting and key addition. This round does not have the MixColumns operation. So it is not optimized as the standard rounds. The byte substitution operation is done by simply table lookup of S-box. It is identical with the optimized standard rounds. So this round is also pipelined with the same number of pipeline stages that a standard round has; and these pipeline stages are compatible with those of a standard round.

In this thesis work, the proposed design has 21 pipeline stages for encryption/decryption datapath: one stage for the first round and two stages for each of the other 10 rounds.

#### **CHAPTER 5:**

## ASIC MODULES AND VERILOG DESIGN ENTRIES

#### 5.1 Introduction

In the previous chapter, the design considerations and the design architecture have been described. The proposed crypto-processor design is partitioned functionally into deferent modules of several levels. The textual designs of these modules are coded with verilog HDL. The textual design module is called verilog design entry. These entries are then compiled, synthesized, placed and routed, and then time-analyzed and simulated. This chapter describes the design hierarchy, verilog design entries and operation of the crypto-processor.

#### 5.2 Components

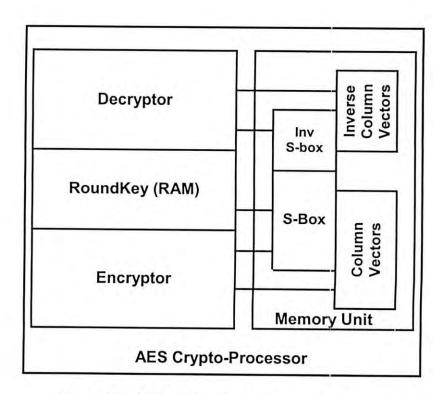

The crypto-processor is a standalone system. Figure 5.1 shows the main modules and their interconnection and relation.

Figure 5.1: AES crypto-processor components

It consists of an encryptor and a decryptor. The encryption and the decryption operations can not be done with the same circuitry. So there are two separate

encryptor and decryptor modules. There is another module for key expansion function. These are the top-level modules. The following sections describe these modules and their sub-modules.

#### 5.3 Memory Unit

The crypto-processor ASIC has three memories: S-box Memory, Column Vector Memory and Key Memory.

#### 5.3.1 S-box memory

The S-box memory unit holds constant byte values. These constant byte values are stored in ROM. The S-box values are used by the off-line key scheduling operation at the starting of a session to expand the session key. These are also used by the last round of the encryption and decryption operation throughout the whole session. The address and data bus of this memory are of 8-bits wide. Each S-box memory has  $2048 \ (2^8 \times 8)$  bits. For parallel operation, 16 identical S-box memory segments are used by the last round. So, the total size of the S-box memory unit becomes  $2048 \times 16 = 32,768$  bits.

As the key scheduling is done off-line there is no need for separate S-box memory block; the memory unit as described above for last round of the encryption can be used in key expansion operation.

#### 5.3.2 Key memory

The key scheduling process generates 11 roundkeys off-line. These roundkeys are made available to the on-line encryption and decryption operation. The size of each roundkey is 128 bits. To address 11 roundkeys at least 4-bit address bus is necessary which necessitates 2048 (128×16) bits of memory. As the values of the round key change with the change in session key, these are stored in RAM. These values are used by both the encryption and decryption operation. The width of the data path is 128 bits and that of the address bus is 4 bits.

## 5.3.3 Column vector memory

The column vectors used by the standard rounds are stored in ROM. The value of column vector is of 32 bits. As the values are pre-calculated and constant, these are stored in ROM. The width of the address bus and the data bus are of 8 bits and 32

bits respectively. Each column vector memory requires 8192 (32×2<sup>8</sup>) bits. For parallel operation, 16 identical memory segments are used by each of nine standard rounds. For pipelining operation, 144 (16×9) identical memory segments for column vectors are required by encryption process. So, for parallel operation and pipelining purposes, the requirement of memory for column vectors is 1,179,648 (8192×144) bits.

#### 5.3.4 Total memory requirements

The total memory requirements for the encryption is the summation of S-box memory, key memory and column vector memory which amounts (32,768+2,048+1,179,648) bits =1,214,464 bits.

The decryption algorithm uses Inverse S-box and different column vectors but the same roundkeys, so it requires (32,768+1,179,648) bits =1,212,416 bits.

Therefore, the total amount of memory requires for the crypto-processor is (1,214,464+1,212,416) bits = 2,426,880 bits

# 5.4 Encryption Unit

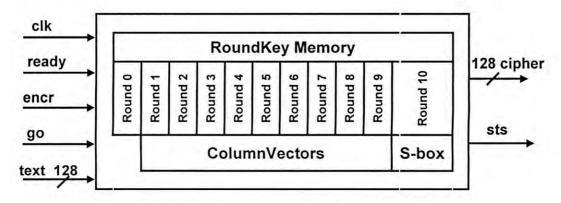

Figure 5.2 shows the encryption module with its constituent modules and input/output signals.

Figure 5.2: The encryption unit of the crypto-processor

The encryption module starts and continues to function as long as 'encr' (encryption) and 'go' signal is asserted when the 'ready' signal is high after the key expansion

operation is completed. It takes the input samples from the 'text' input data bus in first cycle and performs XOR operation with the 'text' and roundkey0.

In next 9 rounds, it takes 2 cycles for each round. In first cycle it fetches column vectors from column vector memory (module "ColumnVector") and performs necessary shifting operation. The shifting operation requires only interconnection which does not make delay. It performs XOR operation with corresponding roundkey in the next cycle.

The operation of the final round also takes two cycles. The first cycle reads substitute byte from S-box memory; and the 2nd cycle performs XOR operation with the roundkey. Finally, cipher output is generated at 'cipher' data bus.

The encryption datapath is 21 cycles long, which means, output is generated after 21 cycles from the first cycle that takes input samples. So the latency of the encryption process is 21 cycles. At 21st cycle, the 'sts' (status signal) is made high and remains high until the encryption session is stopped by either de-asserting 'go' or 'encr' signal .

# 5.5 Decryption Unit

The operation of decryption process is the inverse of encryption process. Figure 5.3 shows the decryption module. It takes cipher as its input and generates text as output. The starting of the module is triggered by the assertion of 'decr' signal when 'ready' signal is high.

Figure 5.3: The decryption unit of the crypto-processor

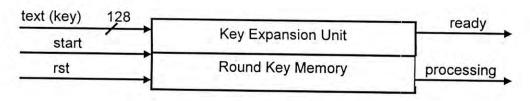

### 5.6 Key Expansion Unit

The key expansion unit is shown in Figure 5.4. When 'start' signal is asserted with 'rst' low, the key expansion process starts functioning taking the sample from 'text' bus as its session key; and the 'processing' signal becomes high. After all the roundkeys have generated and stored in the round key memory, the process forces the 'ready' signal to go high. For the rest of the session this process remains standby, but provides the corresponding round key as asked by the encryption and decryption unit.

Figure 5.4: Key expansion Unit

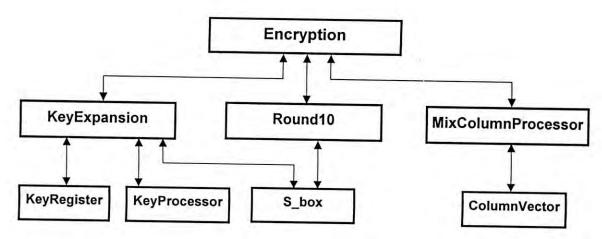

# 5.7 Verilog Design Entries for "Encryption" Module

The encryption module has the hierarchy of design entries as shown in Figure 5.5. The top level module, "Encryption", contains both design information and instantiations of the modules: "KeyExpansion", "MixColumnProcessor" and "Round10". The "KeyExpansion" module provides the "Encryption" module the roundkeys for all pipeline stages and all eleven rounds. The "Encryption" module does the XORing operation with appropriate roundkeys provided by "KeyExpansion" module and the data provided by "MixColumnProcessor" or "Round10" module. Section 5.8 describes the "KeyExpansion" module. The verilog HDL coding of the "Encryption" module is given in Appendix C.

Figure 5.5: Verilog design hierarchy of "Encryption" module

#### 5.7.1 "MixColumnProcessor" module

Though the complex algebraic operation of the MixColumns transformation has been eliminated, and only the column vector memory is used, to have flavor of original algorithm, this name is given to this module. This module instantiates "ColumnVector" module. The "ColumnVector" module infers a ROM that holds the column vector values. For the nine standard rounds, the "MixColumnProcessor" module reads column vectors from the memory and does the necessary 'shifting' operations. The Verilog code for "MixColumnProcessor" and "ColumnVector" are given in Appendix C.

#### 5.7.2 "Round10" module

The "Encryption" module instantiates this module for the last round of the encryption process. The "Round10" module again instantiates "S\_box" module. The "S\_box" module infers a ROM that stores substitute byte values. The "S\_box" module is instantiated both in "Round10" and "KeyExpansion" module. The "Round10" module fetches S-box values from memory and does the necessary 'shifting' operations. The Verilog code of "Round10" is also given in Appendix C.

# 5.8 Verilog Design Entries for "KeyExpansion" Module

The Verilog HDL code of "KeyExpansion" module is given in Appendix B. This module is instantiated both in "Encryption" and "Decryption" modules. This module again instantiates "S\_box", "KeyProcessor" and "KeyRegister" modules. The hierarchy of this module is shown in Figure 5.5.

# 5.8.1 "S\_box" module

This module infers a ROM that stores the substitute byte values. These values are used by the "KeyExpansion" module and the "Round10" module of the encryption unit. The Verilog code of this module is given in Appendix D.

# 5.8.2 "KeyProcessor" module

This module calculates the round keys. This is the most delay inducing module because this involves in operation of computing the most complex algebraic jargons. The Verilog code of this module is given in Appendix B.

#### 5.8.3 "KeyRegister" module

This module stores the round key generated by KeyProcessor module in memory (RAM) and fetch from memory whenever needed by the encryption process. The Verilog HDL textual design is given in Appendix B.

### 5.9 Verilog Design Entries for "Decryption" Module

The "Decryption" module has the similar hierarchy of modules as the "Encryption" module shown in Figure 5.5. It instantiates "KeyExpansion", "InvRound10" and "InvMixColumnProcessor" modules. The corresponding sub-modules are "InvS\_box" and "InvColumnVetor". The functional description of these modules are the same as described in section 5.7.1 and section 5.7.2. The Verilog HDL code given in Appendix F corresponds to the original algorithm and without pipelining. This is because of distinguishing the performance of original and optimized algorithms. Appendix E provides the coding for "InvS\_box" module, which infers a ROM that stores the inverse substitute byte values for decryption process only. The "InvS\_box" module is only instantiated in "Decryption" module not in "KeyExpansion" module.

#### 5.10 Tools Used