# DESIGN OF A CMOS RF WIDE BAND FREQUENCY SYNTHESIZER

A Thesis Submitted to the

Department of Electrical and Electronic Engineering

of

Bangladesh University of Engineering and Technology

In Partial Fulfillment of the Requirement

For the Degree of

#### MASTER OF SCIENCE IN ELECTRICAL AND ELECTRONIC ENGINEERING

by

#### **Abdullah Ibn Abbas**

Student ID: 0413062287

DEPARTMENT OF ELECTRICAL AND ELECTRONIC ENGINEERING

BANGLADESH UNIVERSITY OF ENGINEERING AND TECHNOLOGY (BUET)

NOVEMBER, 2014

The thesis titled "DESIGN OF A CMOS RF WIDE BAND FREQUENCY SYNTHESIZER" submitted by Abdullah Ibn Abbas, Student ID.: 0413062287 F, Session: April 2013 has been accepted as satisfactory in partial fulfillment of the requirement for the degree of MASTER OF SCIENCE IN ELECTRICAL AND ELECTRONIC ENGINEERING on November 29, 2014.

# **BOARD OF EXAMINERS**

| Dr. A. B. M. Harun-Ur-Rashid<br>Professor<br>Department of Electrical and Electronic Engineering<br>BUET, Dhaka-1000, Bangladesh | Chairman<br>(Supervisor)      |

|----------------------------------------------------------------------------------------------------------------------------------|-------------------------------|

| Dr. Taifur Ahmed Chowdhury Professor and Head Department of Electrical and Electronic Engineering BUET, Dhaka-1000, Bangladesh   | <b>Member</b><br>(Ex-Officio) |

| Dr. Md. Ziaur Rahman Khan Professor Department of Electrical and Electronic Engineering BUET, Dhaka-1000, Bangladesh             | Member                        |

| Dr. Md. Anwarul Abedin Professor and Head Department of EEE Dhaka University of Engineering and Technology Gazipur, Bangladesh   | <b>Member</b><br>(External)   |

STATEMENT OF ORIGINALITY

I, Abdullah Ibn Abbas, hereby declare that the thesis entitled "DESIGN OF A CMOS

RF WIDE BAND FREQUENCY SYNTHESIZER" and the work presented in the thesis

are both my own, and have been generated by me as the result of my own original

research and has not been submitted for higher degree to any other university or

institution. I confirm that:

• This work was done in candidature for a master degree at this university;

• Where any part of this thesis has previously been submitted for a degree or any

other qualification at this university or any other institution, this has been clearly

stated;

• Where I have consulted the published work of others, this is clearly attributed;

• I have acknowledged all main sources of help.

| (Abdullah Ibn Abbas) | Date |

|----------------------|------|

Student ID.: 0413062287 F

iii

# **Dedication**

To my Parents and Teachers

# **CONTENTS**

| TITLE                                         | Page no. |

|-----------------------------------------------|----------|

| Approval Certificate                          | ii       |

| Declaration                                   | iii      |

| Dedication                                    | iv       |

| List of Figures                               | viii     |

| List of Tables                                | xii      |

| Acknowledgement                               | xiii     |

| Abstract                                      | xiv      |

|                                               |          |

| CHAPTER 1: INTRODUCTION                       | 1        |

| 1.1 Motivation                                | 1        |

| 1.2 Literature Review                         | 2        |

| 1.3 Outline of the Thesis                     | 3        |

| CHAPTER 2: PHASE LOCKED LOOP FREQUENCY SYNTES | IZERS 4  |

| 2.1 Basics of phase-locked loops (PLL)        | 4        |

| 2.1.1 Operation of phase-locked loop          | 5        |

| 2.1.2 Terminology of PLL                      | 5        |

| 2.1.3 Dynamics of PLL                         | 7        |

| 2.2 Types of PLL                              | 14       |

| 2.3 Types of Frequency Synthesizers           | 15       |

| 2.3.1 Integer-N Frequency Synthesizer         | 15       |

| 2.  | 2 Fractional-N Frequency Synthesizer             | 16 |

|-----|--------------------------------------------------|----|

| 2.  | 3 Direct Digital Synthesizer                     | 17 |

| 2.4 | Non Ideal Effects in PLL                         | 17 |

| 2.  | 1 Jitter in PLL                                  | 18 |

| 2.  | 2 Phase Noise                                    | 19 |

| 2.  | 3 Reference Spur                                 | 23 |

| 2.5 | Applications of PLL                              | 24 |

| 2.  | 1 Frequency multiplication and synthesis         | 24 |

| 2.  | 2 Skew reduction                                 | 25 |

| СНА | PTER 3: FREQUENCY SYNTHESIZER BUILDING BLOCKS    | 26 |

| 3.1 | Phase detector/Phase Frequency Detector (PD/PFD) | 26 |

| 3.2 | Charge Pump                                      | 30 |

| 3.3 | Voltage Controlled Oscillator (VCO)              | 32 |

| 3.4 | Divider                                          | 33 |

| СНА | PTER 4: CMOS RF WIDE BAND FREQUENCY SYNTHESIZE   | ER |

|     | DESIGN                                           | 35 |

| 4.1 | Phase Frequency Detector Design                  | 35 |

| 4.2 | Charge pump and Loop filter Design               | 41 |

| 4.3 | Voltage Controlled Oscillator Design             | 56 |

| 4.4 | Programmable Divider Design                      | 76 |

| 4.  | 1 Prescaler (N)                                  | 76 |

| 4   | .2 2/3/4/5 Divider                               | 77 |

| 4.  | 3 P-Counter                                      | 77 |

| 4.  | 4 Multiplexer                                    | 79 |

| 4.5 | RF Frequency Synthesizer                         | 80 |

| CH         | APTER 5: CONCLUSIONS AND FUTURE WORK | 90 |

|------------|--------------------------------------|----|

| 5.1        | Conclusions                          | 90 |

| 5.2        | Future work                          | 90 |

| References |                                      | 92 |

# List of Figures

| Figure no.   |                                                                                                               | Page |

|--------------|---------------------------------------------------------------------------------------------------------------|------|

| Figure 2.1:  | Basic structure of a phase-locked loop                                                                        | 5    |

| Figure 2.2:  | Illustration of Terminologies of PLL                                                                          | 6    |

| Figure 2.3:  | Linear model of a type-I PLL                                                                                  | 7    |

| Figure 2.4:  | Type-II charge pump PLL                                                                                       | 10   |

| Figure 2.5:  | Linear model of a type-II PLL                                                                                 | 11   |

| Figure 2.6:  | Pulse-swallow frequency divider                                                                               | 15   |

| Figure 2.7:  | A fractional frequency divider                                                                                | 16   |

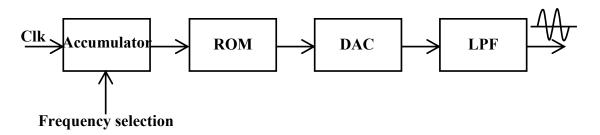

| Figure 2.8:  | A direct digital synthesizer                                                                                  | 17   |

| Figure 2.9:  | Ideal and Jittery Waveforms                                                                                   | 19   |

| Figure 2.10: | Phase noise and spur                                                                                          | 21   |

| Figure 2.11: | Phase noise of VCO and PLL                                                                                    | 22   |

| Figure 2.12: | Frequency Multiplication                                                                                      | 24   |

| Figure 2.13: | Use of PLL to Eliminate Skew                                                                                  | 25   |

| Figure 3.1:  | Phase detector characteristics                                                                                | 26   |

| Figure 3.2:  | XOR phase detector and phase characteristics                                                                  | 27   |

| Figure 3.3:  | Tri-state PFD implementation                                                                                  | 28   |

| Figure 3.4:  | Transfer characteristics of a tri-state PFD                                                                   | 29   |

| Figure 3.5:  | Dead zone in tri-state PFD                                                                                    | 29   |

| Figure 3.6:  | Dead zone free PFD                                                                                            | 30   |

| Figure 3.7:  | Charge pump with loop filter                                                                                  | 30   |

| Figure 3.8:  | Charge pump transient analysis                                                                                | 31   |

| Figure 3.9:  | Feedback oscillatory system                                                                                   | 32   |

| Figure 3.10: | Programmable divider                                                                                          | 33   |

| Figure 4.1:  | Transistor Level PFD Circuit Diagram [24]                                                                     | 36   |

| Figure 4.2:  | Waveforms of PFD [24]                                                                                         | 37   |

| Figure 4.3:  | Waveforms showing the UP, DN, and Charge Pump output signal                                                   | 38   |

| Figure 4.4:  | where frequency of A is greater than that of B<br>Waveforms showing the UP, DN, and Charge Pump output signal | 39   |

| Figure 4.5:  | where frequency of B is greater than that of A IBM 90nm CMOS Process PFD Auxiliary Circuit Implementation     | 40   |

| Figure 4.6:  | Waveforms after addition of auxiliary circuit showing the UP, DN                                                                       | 40 |

|--------------|----------------------------------------------------------------------------------------------------------------------------------------|----|

|              | and Charge Pump output signal where frequency of A is greater than                                                                     |    |

| Figure 4.7:  | that of B Waveforms after addition of auxiliary circuit showing the UP, DN,                                                            | 41 |

|              | and Charge Pump output signal where frequency of B is greater than                                                                     |    |

| Figure 4.8:  | that of A<br>Charge Pump Block Diagram                                                                                                 | 42 |

| Figure 4.9:  | Proposed Charge Pump Circuit (CP-1)                                                                                                    | 43 |

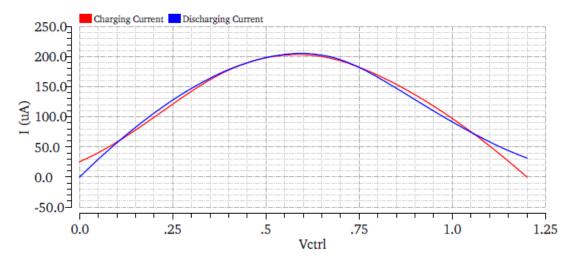

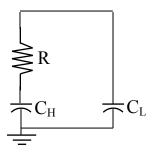

| Figure 4.10: | Charge pump current matching characteristic                                                                                            | 44 |

| Figure 4.11: | Low Pass Filter (Loop Filter)                                                                                                          | 44 |

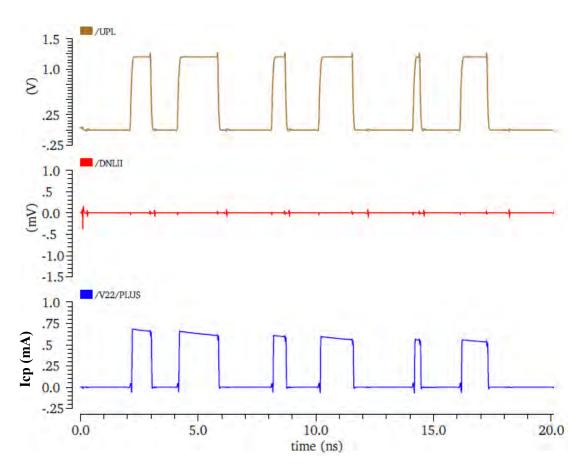

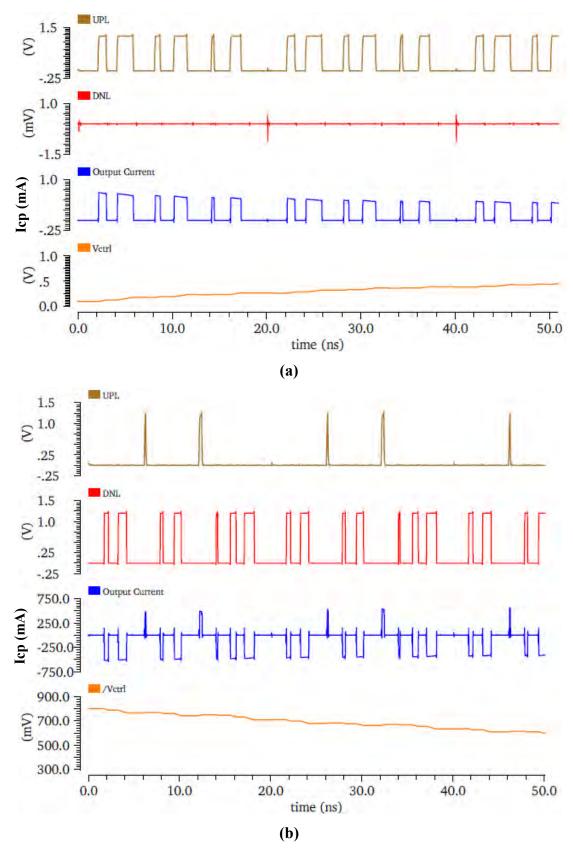

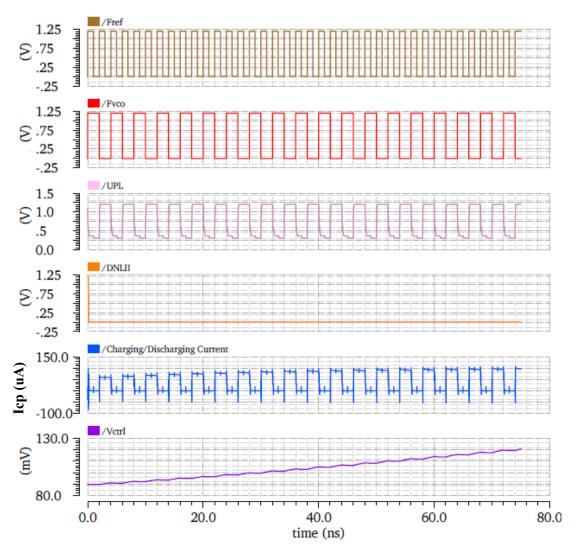

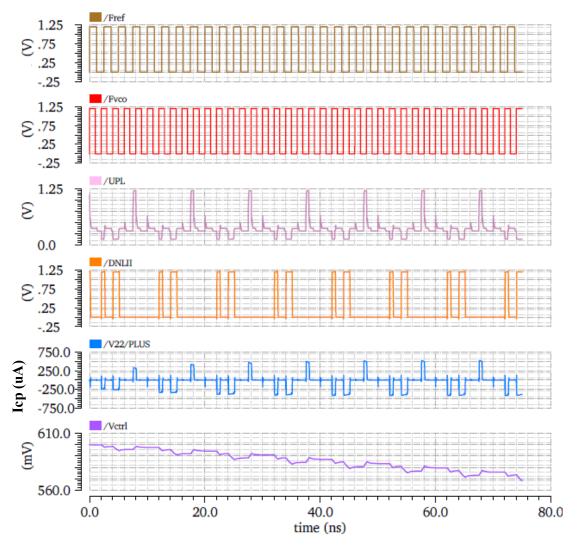

| Figure 4.12: | Waveform for CP-1 ( $F_{ref} > F_{div}$ )                                                                                              | 46 |

| Figure 4.13: | Modified Proposed Charge Pump Circuit (CP-2)                                                                                           | 47 |

| Figure 4.14: | Waveform showing no glitches in the output current for CP-2 (F <sub>ref</sub> >                                                        | 48 |

|              | $F_{div}$ )                                                                                                                            |    |

| Figure 4.15: | Waveform for CP-2                                                                                                                      | 49 |

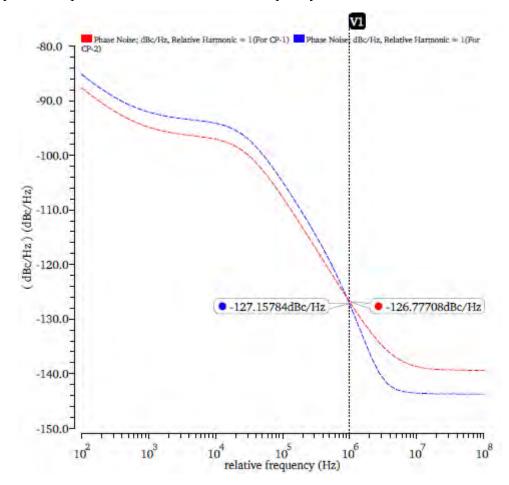

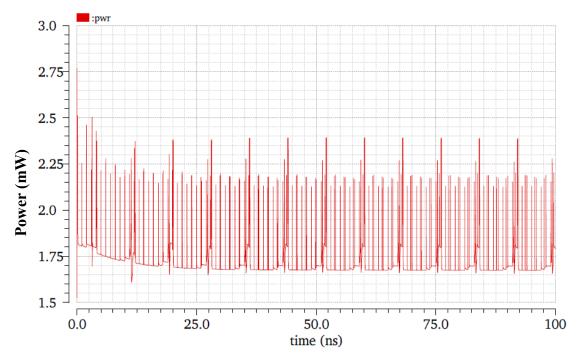

| Figure 4.16: | Phase noise plot for PFD-CP-1 and PFD-CP-2                                                                                             | 50 |

| Figure 4.17: | Power Dissipation plot of the PFD-CP circuit                                                                                           | 51 |

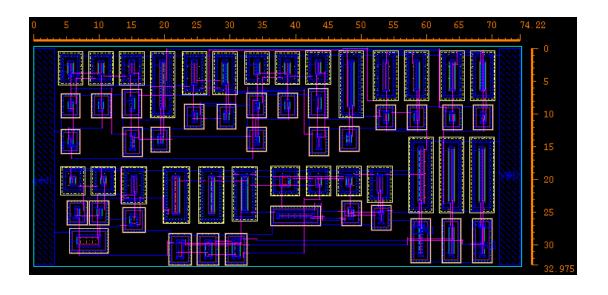

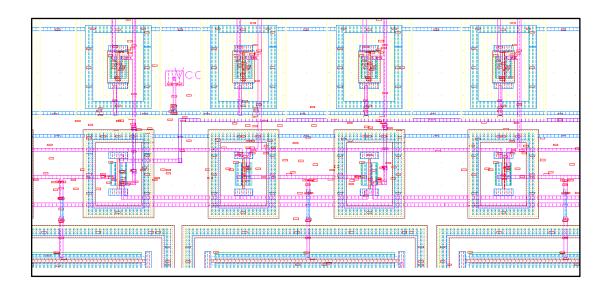

| Figure 4.18: | PFD and CP Layout                                                                                                                      | 51 |

| Figure 4.19: | PFD, CP and Loop Filter Layout                                                                                                         | 52 |

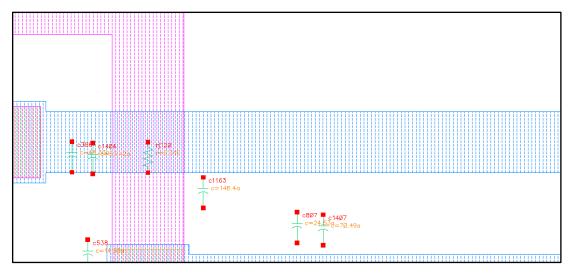

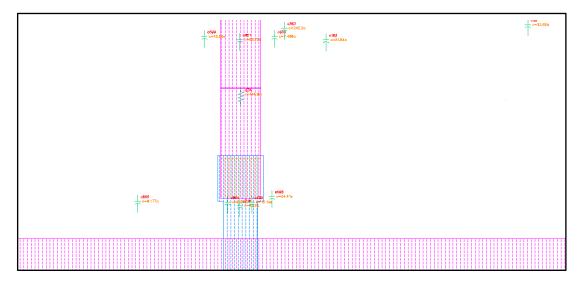

| Figure 4.20: | PFD, CP and Loop Filter Layout showing Parasitic                                                                                       | 52 |

| Figure 4.21: | Closer view of Fig. 4.20                                                                                                               | 53 |

| Figure 4.22: | Post Layout Waveforms showing the UP, DN, and Charge Pump                                                                              | 54 |

| Figure 4.23: | output signal where frequency of $F_{ref}$ is greater than that of $F_{div}$ Post Layout Waveforms showing the UP, DN, and Charge Pump | 55 |

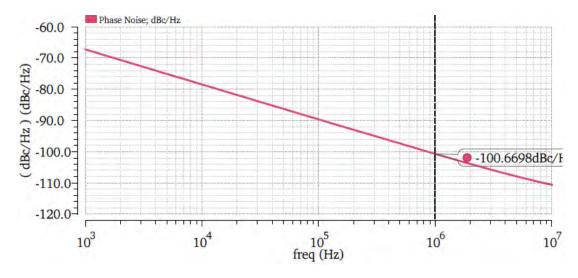

| Figure 4.24: | output signal where frequency of $F_{\text{div}}$ is greater than that of $F_{\text{ref}}$ Post-layout Phase noise plot for PFD-CP-2   | 56 |

| Figure 4.25: | Delay cell for the proposed ring oscillator with a source-coupled                                                                      | 57 |

|              | pair and symmetric loads                                                                                                               |    |

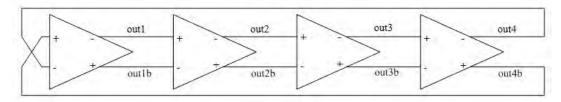

| Figure 4.26: | Four-Stage Differential Ring VCO                                                                                                       | 57 |

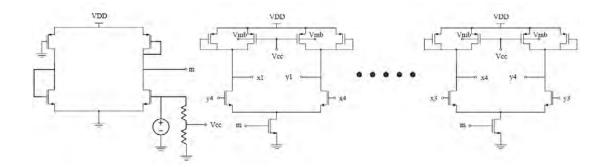

| Figure 4.27: | Schematic of the proposed VCO                                                                                                          | 58 |

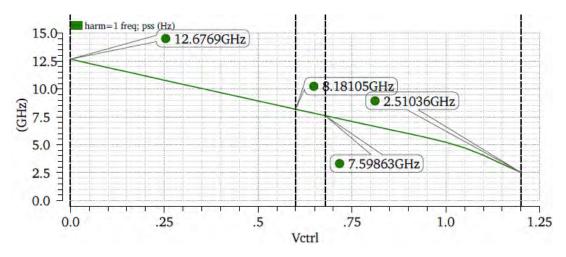

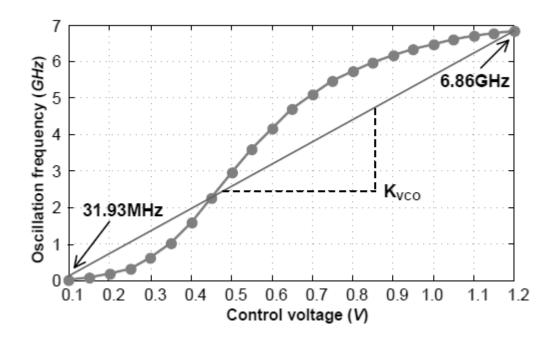

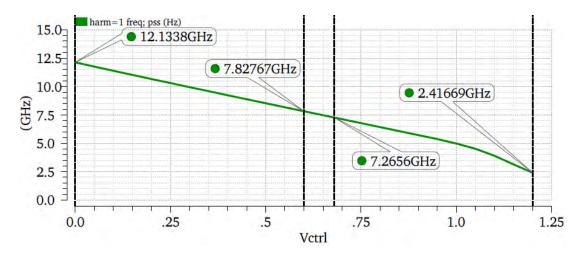

| Figure 4.28: | Tuning range characteristic of the proposed VCO                                                                                        | 58 |

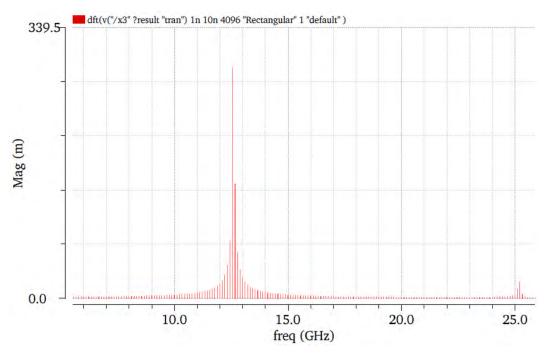

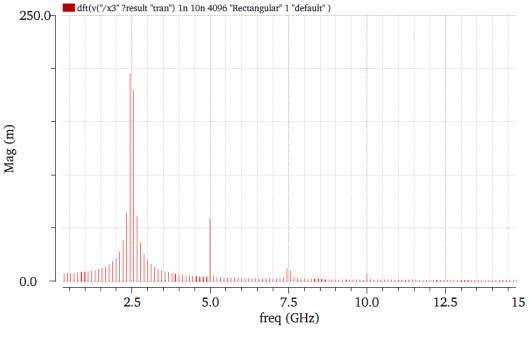

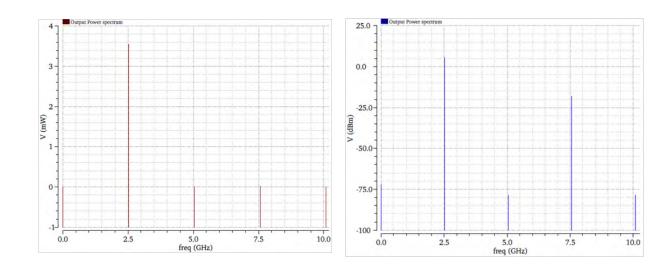

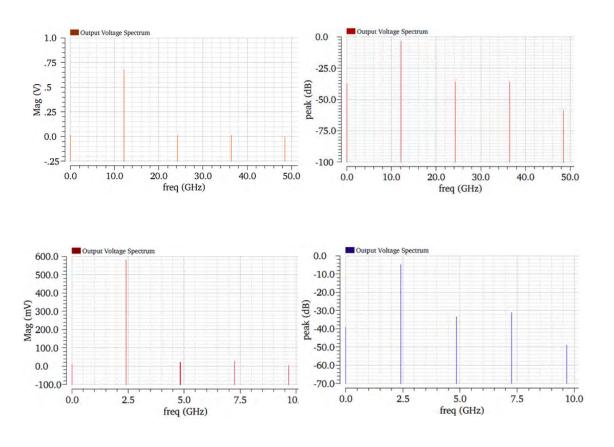

| Figure 4.29: | Frequency Spectrum plot for Vctrl=0 V                                                                                                  | 59 |

| Figure 4.30: | Frequency Spectrum plot for Vctrl=1.2 V                                                                                                | 59 |

| Figure 4.31: | Frequency of oscillation Vs Vctrl for non-linear tuning range                                                                          | 60 |

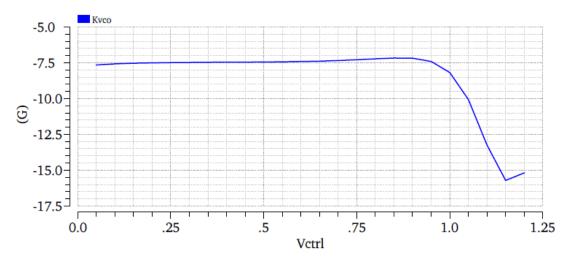

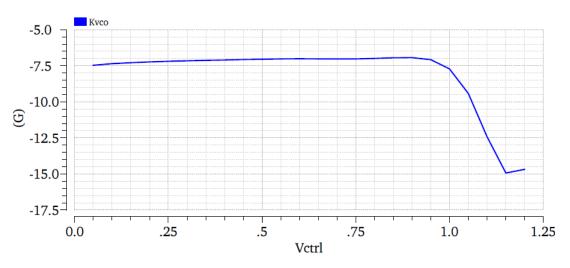

| Figure 4.32: | Gain of the VCO (K <sub>VCO</sub> ) Vs Vctrl                                                                                           | 61 |

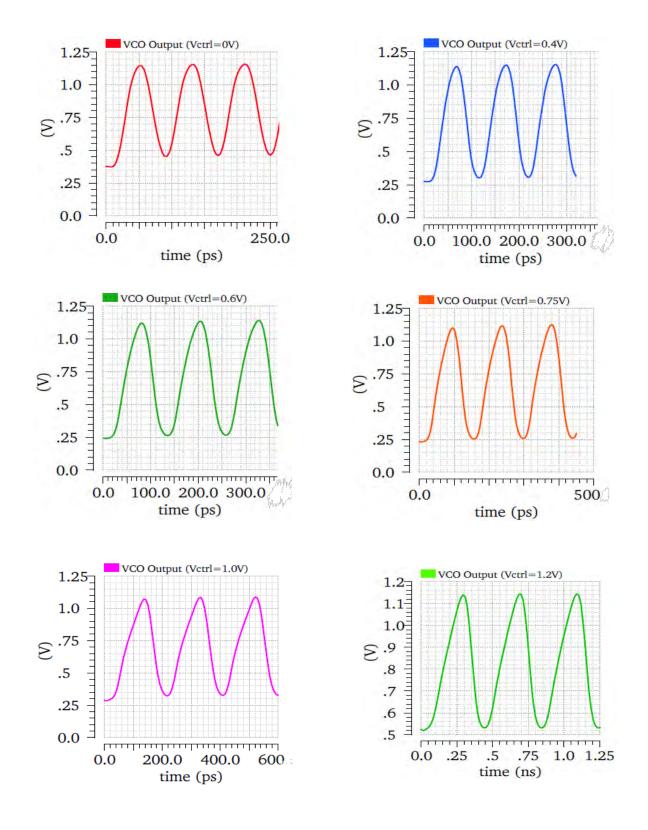

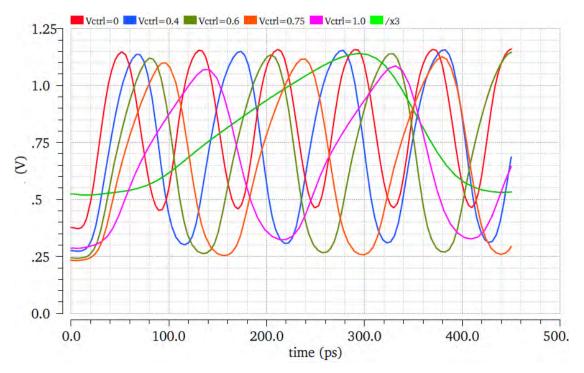

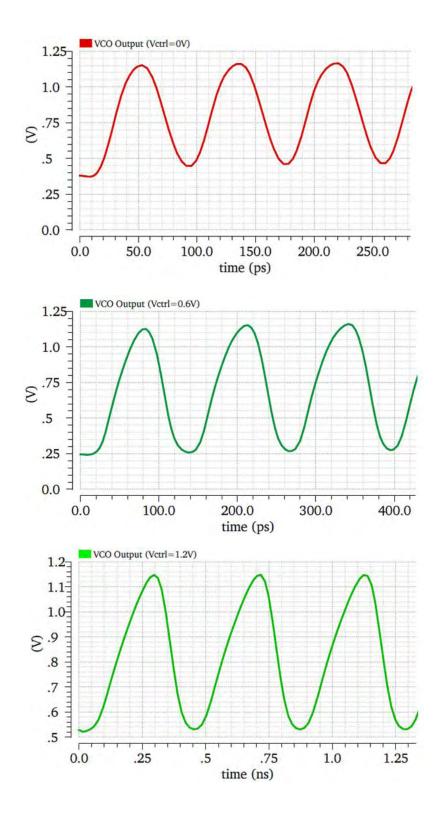

| Figure 4.33: | Output Waveform of the proposed VCO for different values of Vctrl   | 62 |

|--------------|---------------------------------------------------------------------|----|

| Figure 4.34: | Comparison of Output Waveforms of the proposed VCO for              | 63 |

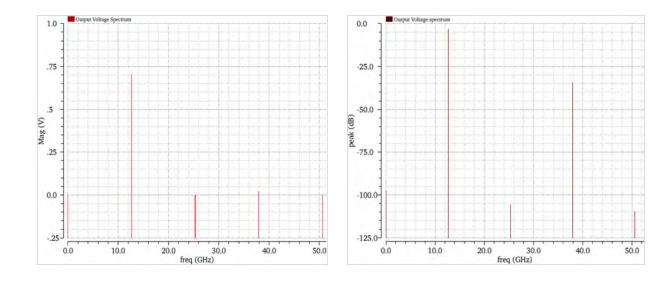

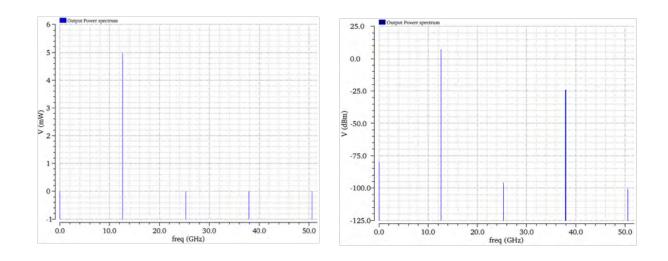

| Figure 4.35: | VCO Output Voltage and Power Spectrum at 12.68 GHz                  | 64 |

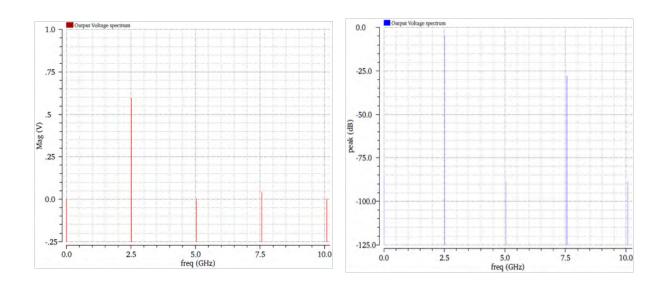

| Figure 4.36: | VCO Output Voltage and Power Spectrum at 2.51 GHz                   | 65 |

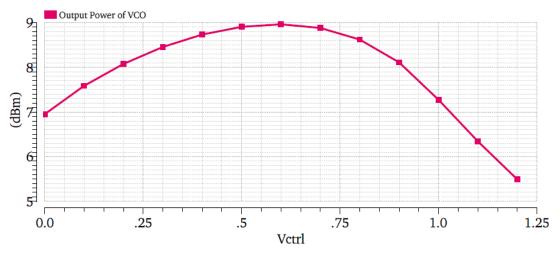

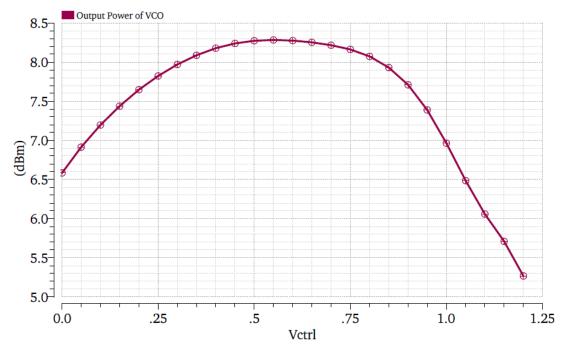

| Figure 4.37: | Output power of the VCO                                             | 66 |

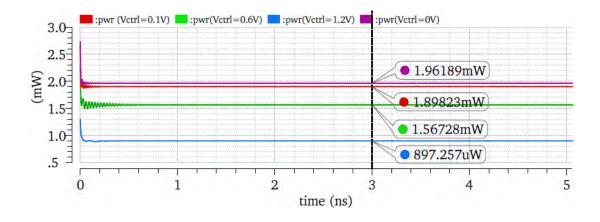

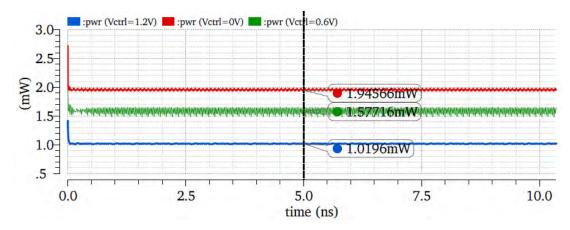

| Figure 4.38: | Total power consumption of the VCO for different output             | 66 |

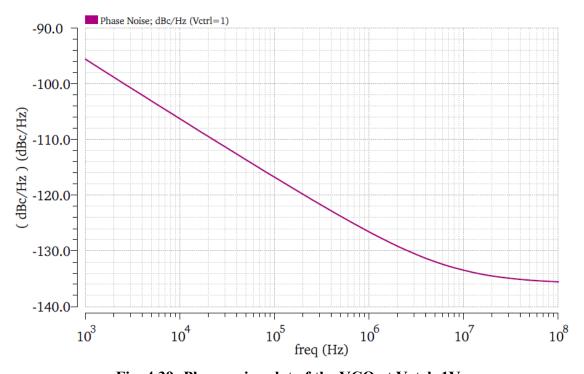

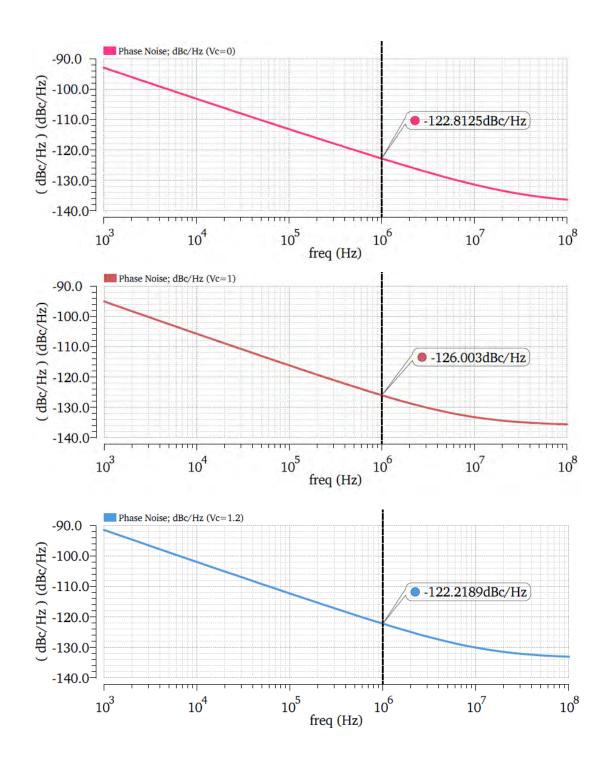

| Figure 4.39: | Phase noise plot of the VCO at Vctrl=1V                             | 67 |

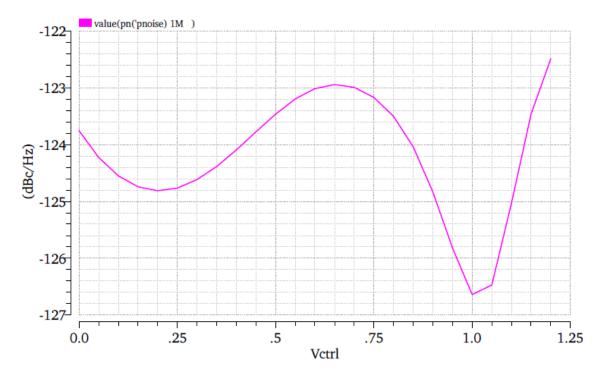

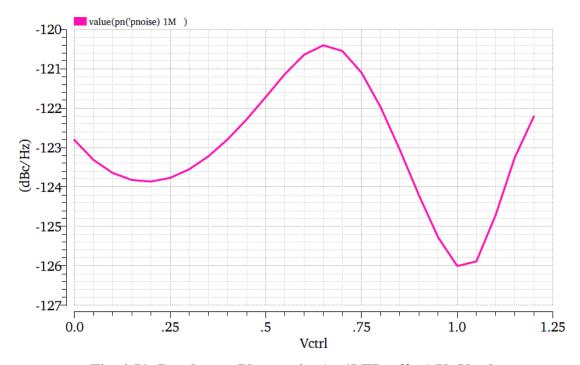

| Figure 4.40: | Phase noise (at 1MHz offset) Vs Vctrl                               | 68 |

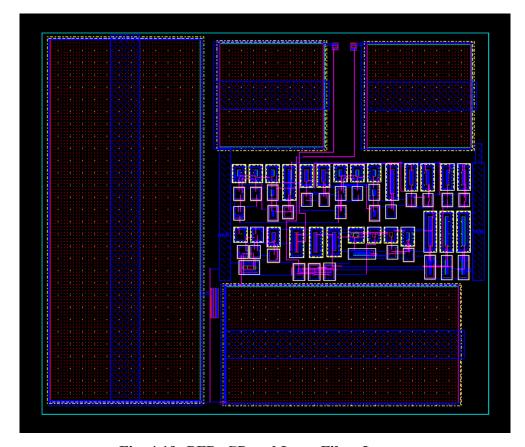

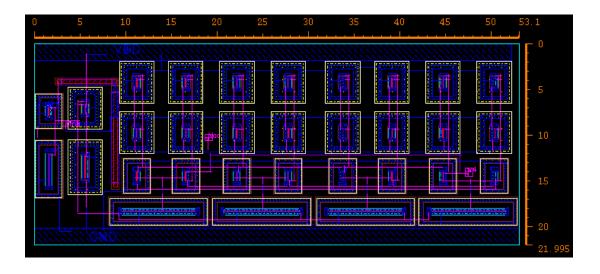

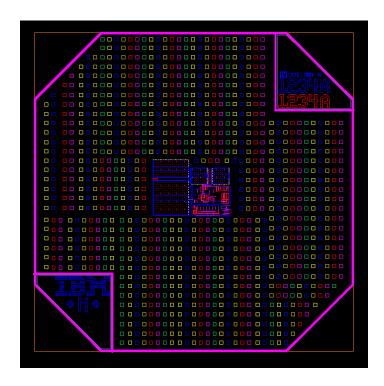

| Figure 4.41: | Layout of the VCO                                                   | 68 |

| Figure 4.42: | VCO Layout showing Parasitic capacitors and resistors               | 70 |

| Figure 4.43: | Closer view of Fig. 4.42                                            | 70 |

| Figure 4.44: | Post-layout tuning range characteristic of the proposed VCO         | 71 |

| Figure 4.45: | Post-layout gain of the VCO (K <sub>VCO</sub> ) Vs Vctrl            | 71 |

| Figure 4.46: | Output Waveform of the proposed VCO for different values of Vctrl   | 72 |

| Figure 4.47: | Post layout VCO Output Voltage Spectrum (magnitude and dB) at       | 73 |

|              | Vctrl=0 V and 1.2 V                                                 |    |

| Figure 4.48: | Post layout output power of the VCO                                 | 73 |

| Figure 4.49: | Post layout total power consumption of the VCO for different output | 74 |

|              | frequencies                                                         |    |

| Figure 4.50: | Post layout phase noise plot of the VCO at Vctrl=0 V, 1 V, and 1.2  | 75 |

| Figure 4.51: | Post layout Phase noise (at 1MHz offset) Vs Vctrl                   | 76 |

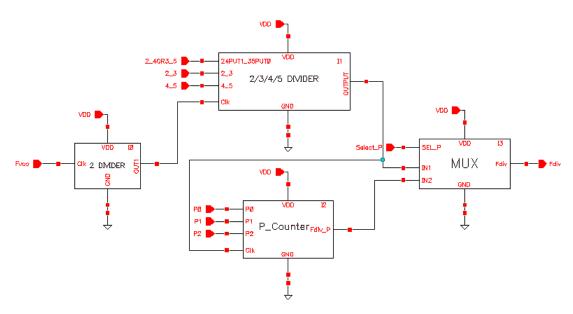

| Figure 4.52: | Block Diagram of the programmable divider                           | 77 |

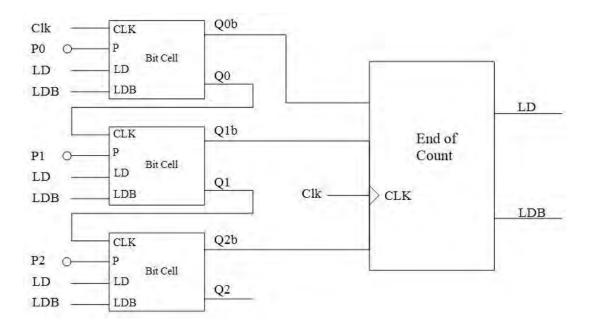

| Figure 4.53: | Block diagram of the Programmable P-Counter                         | 78 |

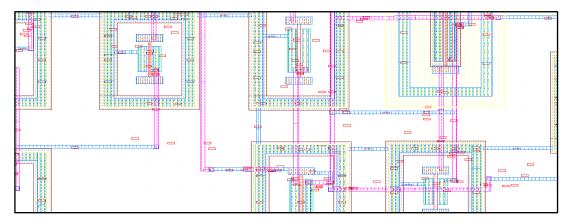

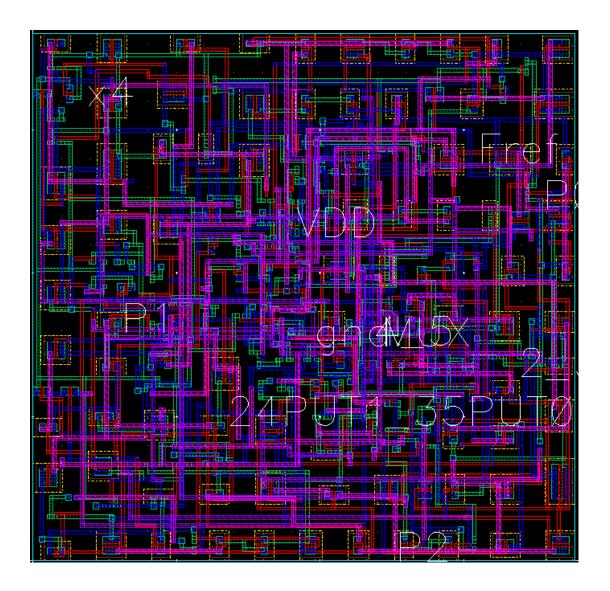

| Figure 4.54: | Layout of the complete Divider Circuit                              | 80 |

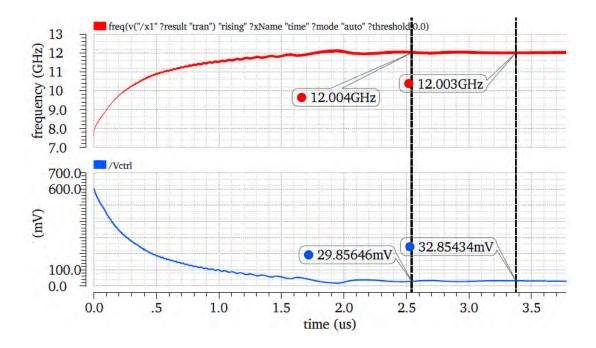

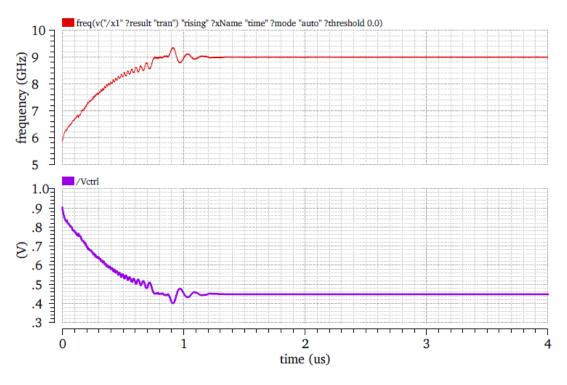

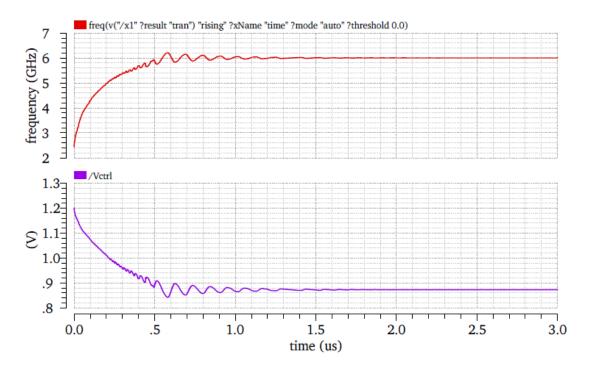

| Figure 4.55: | Frequency and control voltage variation plot over time and lock-    | 81 |

|              | time required to achieve 12 GHz output frequency                    |    |

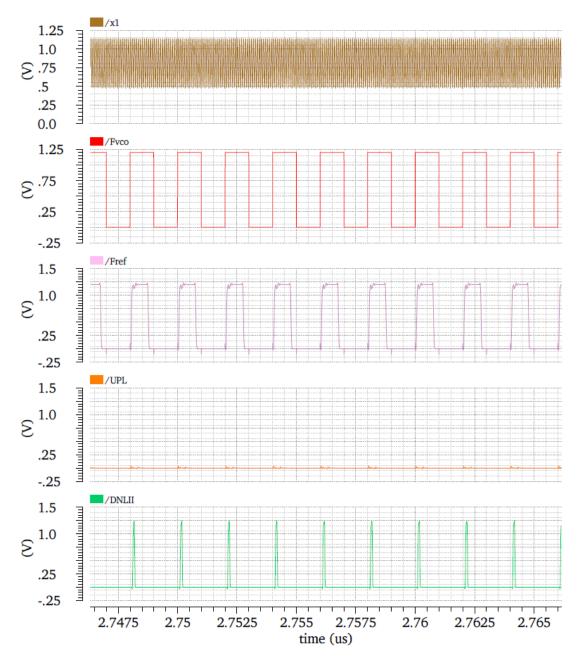

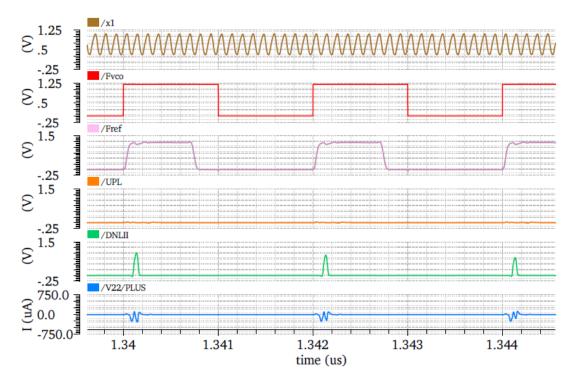

| Figure 4.56: | Different signals of the frequency synthesizer in lock state at a   | 82 |

|              | frequency of 12 GHz                                                 |    |

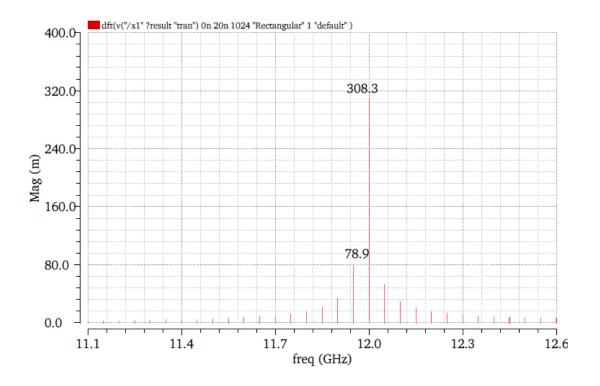

| Figure 4.57: | Frequency Spectrum at an output frequency of 12 GHz                 | 83 |

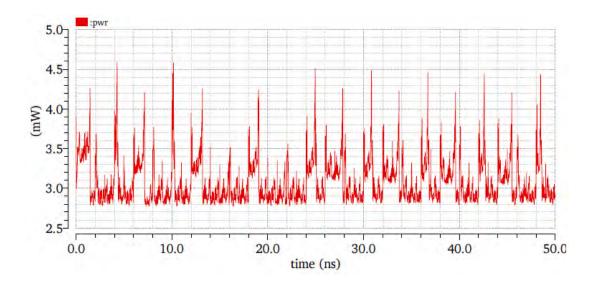

| Figure 4.58: | Plot of power dissipation (at 12 GHz) over time                     | 83 |

| Figure 4.59: | Frequency and control voltage variation plot over time and lock-    | 84 |

|              | time required to achieve 9 GHz output frequency                     |    |

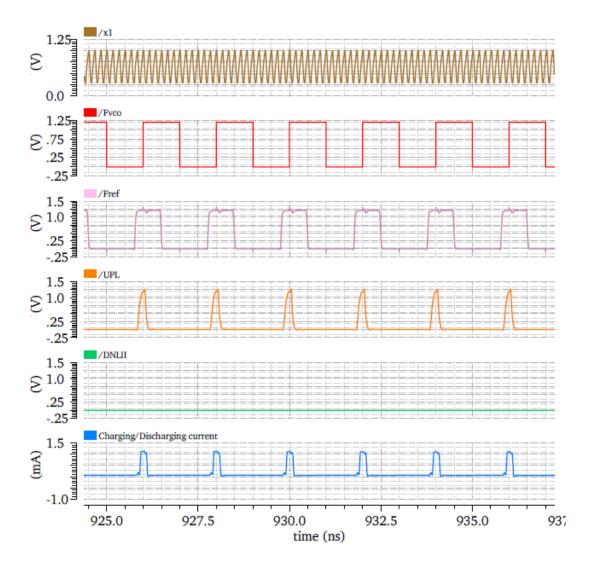

| Figure 4.60: | Different signals of the frequency synthesizer in lock state at a   | 84 |

|              | frequency of 9 GHz                                                  |    |

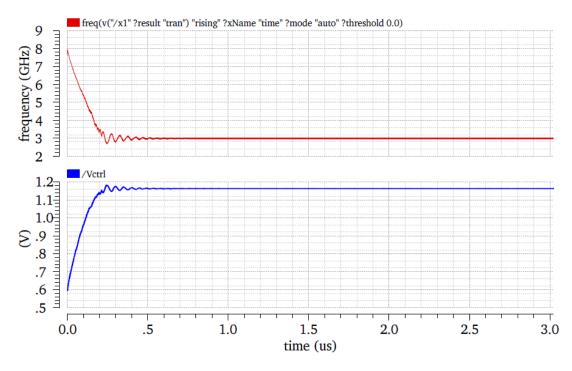

| Figure 4.61: | Frequency and control voltage variation plot over time and lock-                                                       | 85 |

|--------------|------------------------------------------------------------------------------------------------------------------------|----|

| Figure 4.62: | time required to achieve 6 GHz output frequency<br>Different signals of the frequency synthesizer in lock state at a   | 86 |

| Figure 4.63: | frequency of 6 GHz Frequency and control voltage variation plot over time and lock-                                    | 87 |

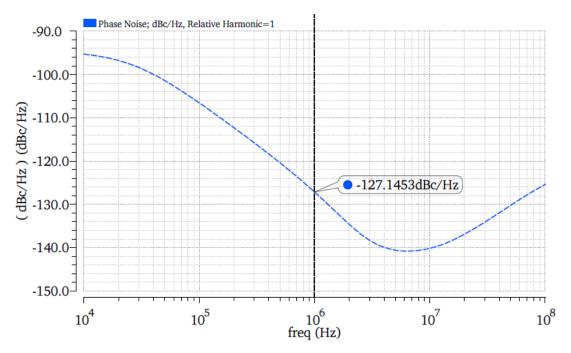

| Figure 4.64: | time required to achieve 3 GHz output frequency<br>Phase noise plot of the proposed frequency synthesizer operating at | 87 |

|              | 12 GHz                                                                                                                 |    |

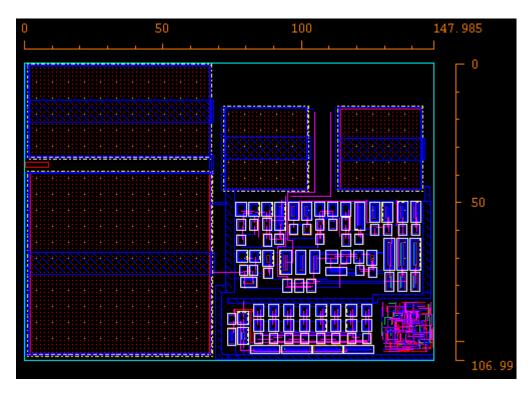

| Figure 4.65: | Complete layout of the frequency synthesizer                                                                           | 88 |

| Figure 4.66: | Layout of the frequency synthesizer inside the chip-edge                                                               | 88 |

# List of Tables

| Table no.  |                                                              | Page |

|------------|--------------------------------------------------------------|------|

| Table 4.1: | Operating principle of Phase Frequency Detector              | 37   |

| Table 4.2: | Summary of VCO Performances                                  | 69   |

| Table 4.3: | Performance Summary and Comparison of VCOs                   | 69   |

| Table 4.4: | Programmable Values of the Divider                           | 79   |

| Table 4.5: | Performance Summary and Comparison of Frequency Synthesizers | 89   |

# Acknowledgment

All praises, prayers, glory, and gratitude belong to almighty Allah who is the gracious and the ever merciful.

This thesis is the outcome of the support from my beloved parents and teachers who encouraged me to carry out this work.

The person who deserves the salutation and respect from the core of my heart is no one but my supervisor, Dr. A. B. M. Harun-Ur-Rashid for his multidimensional support and parental care. I am deeply grateful to him for giving me the opportunity to carry out my research under his supervision. His guidance and encouragement made me to complete my thesis work successfully. He not only helped me with research material but also trusted me and provided me the Cadence Electronic Design Automation tools in VLSI laboratory which was badly needed for simulation and physical verification of the designed circuit.

I want to extend special thanks to Dr. Mohammad Ali Choudhury, Dr. Md. Saifur Rahman, and Dr. Satya Prasad Majumder for their generous help and support during my thesis work and stay.

I greatly appreciate the help and support from Mr. Md. Anwar Hossain, senior laboratory instructor cum store keeper of VLSI Lab.

I am thankful to my parents and sisters who are the ultimate source of my strength and the reason of my endeavor and without them I would not have achieved whatever I possess.

# **Abstract**

The focus of this thesis is to design a silicon based RF frequency synthesizer in CMOS process that will generate frequency from the S band up to the X band (2 GHz -12 GHz). To achieve this target, an improved CMOS ring oscillator topology is proposed and is implemented in IBM 90nm RF CMOS process technology. The other building blocks of a frequency synthesizer, namely phase frequency detector (PFD), charge pump (CP), and divider circuits were also designed and implemented successfully to achieve the target. The proposed VCO can generate frequency from 2.51 GHz to 12.68 GHz with almost constant gain (Kvco) and low phase noise within the operating range. The performance of PFD has been boost up with proposed technique and an innovative idea in the design of CP has reduced the glitches in the charging and discharging current of the loop filter.

Each block of the proposed Phase-Locked Loop based Frequency Synthesizer is designed using Cadence Electronic Design Automation tools in IBM 90nm CMOS process technology. Virtuoso Schematic Editor tool is used for schematic design and all the simulation results are plotted in Cadence Spectre. Virtuoso Layout Editor (XL) tool is used for physical layout design whereas Assura DRC, LVS, and QRC tools are used for physical verification.

Simulation results are provided for the performance of VCO, PFD, CP and the PLL. Post-layout simulation including the parasitic is also provided to verify the functionality of the proposed circuit. Pre and post layout simulation results are compared and it is found that they meet our target and specification.

Finally, the results obtained for the designed circuits are compared with the literature works and is found that our proposed circuits are better in most of the performance parameters than those reported in literature works.

# CHAPTER 1

# INTRODUCTION

#### 1.1 Motivation

Over the last two decades, the continuous shrinking in the feature of MOSFETs has increasingly attracted the research and development of low-power radio frequency CMOS integrated circuits [1],[2]. For the modern transceiver architecture, a fully integrated frequency synthesizer with high frequency and low power voltage controlled oscillator (VCO) is always a topic of interest in research.

Phase-locked loops (PLLs) are widely used in radio frequency synthesis. The PLL based frequency synthesizer is one of the key building blocks of an RF frontend transceiver.

Fundamentally, no matter whether designed for digital or analog applications, a frequency synthesizer must ensure the devices are working at their designed operational speed. Furthermore, the frequency synthesizer requires their frequency to be tunable over a range of frequency bands. This requires the use of a voltage controlled oscillator (VCO) and the controllability requirement demands the utilization of the PLL. VCO is an integrated part of a frequency synthesizer. Recently, several CMOS voltage-controlled oscillators operating above 50 GHz have been demonstrated [3]-[5]. The existing phase-locked loops operating at frequencies above 50 GHz are usually based on III-V [6],[7] or SiGe HBT technologies [8]. Operating frequency around 12 GHz in silicon based CMOS process has not been reported till the present work.

Ring oscillator based voltage-controlled oscillators are attractive in terms of small area and frequency tuning range. Furthermore, they have the particularly desirable property that inductors can be dispensed with altogether, which makes ring-VCOs highly scalable. Unfortunately, their phase-noise performance is inferior to that of LC-VCOs with comparable power consumption. Nevertheless, a low-phase-noise ring VCO can be obtained if a noise-suppression mechanism can be included in the VCO.

Since its invention, the design of PLL has remained challenging because of the requirement of fast, low power consuming and less noisy electronic equipment. "Charge Pump" is an essential part of a PLL. Charge pump (CP) converts the phase or frequency difference information of two input signal into a voltage which is used to tune a VCO towards reference input frequency. Other elements of PLL are "Phase Frequency Detector (PFD)", "Low Pass Filter (LPF)" and "VCO". Implementation of LPF is very easy while PFD and VCO can be implemented in static CMOS logic. But being a current driven system, charge pump is found to be more challenging for implementation, since performance of CP directly affects the speed, power consumption and noise behaviour of PLL. Clock feed through, charge sharing, current mismatch are some of the challenges in design of CP.

#### 1.2 Literature Review

The recent trend in the design of high frequency PLL based frequency synthesizer is to use LC oscillators [9] because of its low phase noise characteristics. These LC oscillator based frequency synthesizers on the other hand have narrow tuning range as compared to those frequency synthesizers which uses ring oscillators. Ring oscillators can be built in any standard CMOS process and may require less die area than LC designs. The design is straightforward, and ring architectures can be used to provide multiple output phases and wide tuning ranges. The literature works that uses sub-micron process technology fails to present ring oscillators that operate above 8 GHz and with a wide tuning range. Some literature works show that up to 6 GHz [10],[11] operating frequency have been achieved in recent technology process (0.18µm, 90nm etc.) but these technology are based on GaAs or SiGe HBT etc. but not silicon based CMOS process technology. A constant gain voltage-controlled oscillator within the full range of operating frequency has not been reported till date. Therefore, it is needed to design a wide tuning range ring oscillator that can operate at very high frequency for gigahertz application is needed to design in cheap silicon technology and which can have constant gain within the operating range. To design a frequency synthesizer which can operate at such a high frequency requires a phase frequency detector [12]-[14] which can stand this high frequency operation. The design of frequency synthesizer presented in this work can be successfully implemented in the area where on-chip high frequency and wide tuning range is desired.

#### 1.3 Outline of the Thesis

This thesis consists of five chapters. Chapter 1 introduces the topic and the present state of the work.

Chapter 2 briefly describes the basics of PLL.

Chapter 3 builds the concepts of charge pump PLL and in the subsequent sections the building blocks of a PLL are discussed in brief.

The designed RF wide band frequency synthesizer is proposed in chapter 4. The proposed modified fast operating PFD with glitch suppressed and current matched CP is presented in section 4.1 and section 4.2. These sections also contain the simulation and verification results in addition to the layout drawn to estimate the area budget. The post simulation results are also provided to estimate the real performance of the circuit. The proposed VCO with improved topology is presented in section 4.3. Different properties of the VCO simulated are also shown along with the layout of the design and post layout simulated results. Finally, in section 4.4, the divider circuit designed to show the desired operation of the proposed RF frequency synthesizer is presented.

Chapter 5 concludes the thesis work highlighting the outcome of the proposed design and the future work on this topic to make the work more concrete.

# CHAPTER 2

# PHASE LOCKED LOOP FREQUENCY SYNTHESIZERS

In this Chapter, the fundamentals of frequency synthesizers are discussed. First we define the PLL frequency synthesizer. We then discuss the theory behind the phase locked loops (PLL) and the integer-N charge pump frequency synthesizer based PLL. Subsequently, all the building blocks of the frequency synthesizer such as phase frequency detector (PFD), charge pump (CP), Voltage controlled oscillator (VCO), divider and loop filter (LF) are discussed.

# 2.1 Basics of phase-locked loops (PLL)

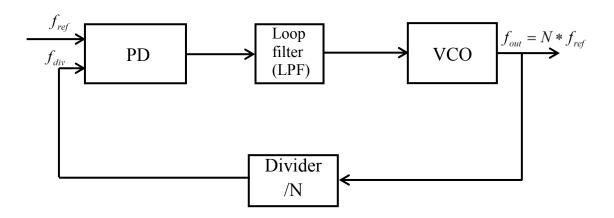

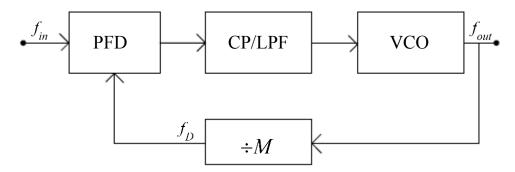

A simple Phase Locked Loop (PLL) is a feedback system [15],[16] that compares the frequency and phase of the reference signal with that of the feedback signal coming from its output. The comparison is performed by a Phase Frequency Detector (PFD) which produces a voltage proportional to the phase difference. The output frequency of the PLL is in turn proportional to the voltage generated by the PFD. The earliest description of a PLL was provided by H. de Bellescize in 1932 and from then onwards the basic PLL has remained nearly the same but its implementation in different technologies and for different applications continues to challenge designers. Fig. 2.1 shows the basic block diagram of a PLL. Phase-locked loops are widely used in the design of frequency synthesizers of RF transceivers.

Before going into the detailed discussion of PLL, we first discuss the concept of phase locking. Phase locking means the phase difference between the two signals is constant with time and almost negligible. This means that once the loop achieves the locking, there is no frequency difference between the two signals which are compared. By using a feedback loop, a constant phase difference of two periodic signals is ensured when the loop reaches its steady state.

#### 2.1.1 Operation of phase-locked loop

Fig. 2.1 shows the basic block diagram of a simple phase-locked loop. A PLL is a feedback system which minimizes the phase difference between the reference input  $f_{ref}$  and the feedback signal  $f_{div}$ . Here, a phase detector (PD) generates a phase error whose DC value is proportional to the difference between the phases of the reference and feedback signals. The

Fig. 2.1: Basic structure of a phase-locked loop

low pass filter (LPF) extracts the DC value and applies it to the voltage controlled oscillator (VCO), which changes the output frequency  $f_{out}$ . Since frequency synthesizer is required to produce a programmable output frequency, a frequency divider (FD) of programmable division ratio N is employed in the feedback path to divide down the VCO output frequency to the one comparable to the input reference frequency [17]-[19]. When the loop reaches steady state, the phase difference between the reference input  $f_{ref}$  and feedback signal  $f_{div}$  is constant over time and the relation  $f_{out} = Nf_{ref}$  holds true. By changing the value of N, the VCO output frequency can be changed.

# 2.1.2 Terminology of PLL

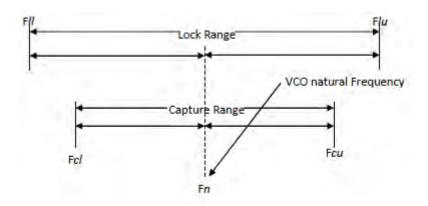

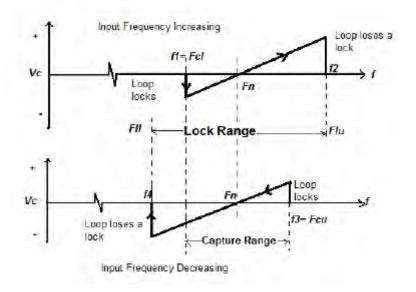

## 1. Lock range:

The range of input signal frequencies over which the loop can maintain the lock is called as Lock Range or Tracking Range of PLL.

#### 2. Capture range:

The range of input signal frequencies over which PLL can acquire a lock is called as Capture Range or Acquisition Range of PLL.

Capture range depends on the amount of the gain in a loop itself and the loop filter bandwidth. Reducing the loop filter bandwidth thus improves the rejection of the out of band signals, but at the same time the capture range decreases, pull in time becomes larger and phase margin becomes poor.

Fig. 2.2: Illustration of Terminologies of PLL

#### 3. Pull in time:

The total time taken by the PLL to capture the signal (or to establish the lock) is called as Pull in Time of PLL. It is also called as Acquisition Time of PLL.

#### 4. Band width of PLL

Bandwidth is the frequency at which the PLL begins to lose the lock with reference.

#### 2.1.3 Dynamics of PLL

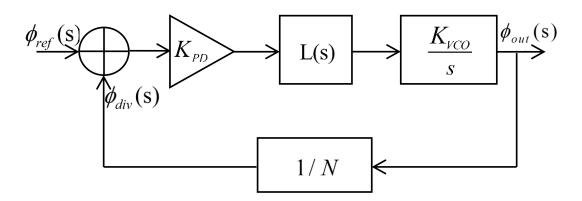

PLLs are classified according to the type of loop filter used in architecture. The order of loop filter is the type of PLL. For example, if  $1^{st}$  order loop filter is used, then it is called as type I PLL. If  $2^{nd}$  order filter is used, it is called as type II PLL and so on.

If PLL uses simple "Phase detector" in its architecture, it is called as simple PLL. But if PLL uses "Phase Frequency Detector" accompanied with "Charge Pump", it is called as "Charge Pump PLL".

#### 2.1.3.a Dynamics of Type-I PLL

Fig. 2.3: Linear model of a type-I PLL

A simple PLL is analyzed by the phase transfer function as the PD compares the phase difference between the input  $\phi_{ref}(s)$  and feedback signal  $\phi_{div}(s)$ . Fig.2.3 shows the linear model of a type-I PLL with the respective transfer functions of the building blocks. If the loop filter is a simple first order low pass filter (LPF), the transfer function is given by [19]

$$L(s) = \frac{1}{1 + s / \omega_{LPF}} \tag{2.1}$$

where  $\omega_{LPF}$  denotes the -3 dB bandwidth. The open-loop transfer function is given by

$$H_o(s) = \frac{\phi_{out}}{\phi_{ref}}(s) = \frac{K_{PD}K_{VCO}}{N} \frac{1}{s(1+s/\omega_{LPF})}$$

(2.2)

Since open-loop transfer function contains only one pole at origin, this type of PLL is called type-I PLL. If the input phase varies slowly, owing to the pole at origin, the loop gain goes to infinity as s approaches zero. Thus, the PLL under locked condition ensures that the change in  $\phi_{out}$  is exactly equal to the change in  $\phi_{ret}$  as s goes to zero.

The closed-loop transfer function is written as

$$H_C(s) = \frac{\phi_{out}}{\phi_{ref}}(s) = \frac{K_{PD}K_{VCO}}{s^2 / \omega_{LPF} + s + K_{PD}K_{VCO} / N}$$

(2.3)

The second order closed-loop transfer function suggests the system can be overdamped, under-damped or critically damped. If we compare (2.3) with standard second order equation from control theory which is given by

$$H(s) = \frac{\omega_n^2}{s^2 + 2\xi\omega_n s + \omega_n^2}$$

(2.4)

$$\omega_n = \sqrt{\omega_{LPF} K_{PD} K_{VCO}} \tag{2.5}$$

$$\xi = \frac{1}{2} \sqrt{\frac{\omega_{LPF}}{K_{PD} K_{VCO}}} \tag{2.6}$$

where  $\xi$  is the damping ratio and  $\omega_n$  is the natural frequency. The two poles of the closed-loop system are given by

$$S_{1,2} = \frac{1}{2} \left( \omega_{LPF} \pm \sqrt{\omega_{LPF}^2 - \frac{4K_{PD}K_{VCO}}{N}} \right)$$

(2.7)

$$\xi \omega_n = \frac{1}{2} \omega_{LPF} \tag{2.8}$$

If  $\omega_{LPF}^2 - 4K_{PD}K_{VCO}/N > 0$ , the two poles are real and the transient step response is given by

$$\omega_{out}(t) = \begin{bmatrix} \frac{2K_{PD}K_{VCO}}{\sqrt{\omega_{LPF}^{2} - \frac{4K_{PD}K_{VCO}}{N}}} \times \frac{1}{\omega_{LPF} - \sqrt{\omega_{LPF}^{2} - \frac{4K_{PD}K_{VCO}}{N}}} \begin{bmatrix} 1 - e^{-\frac{1}{2}(\omega_{LPF} - \sqrt{\omega_{LPF}^{2} - \frac{4K_{PD}K_{VCO}}{N}})t} \\ -\frac{1}{\omega_{LPF} + \sqrt{\omega_{LPF}^{2} - \frac{4K_{PD}K_{VCO}}{N}}} \begin{bmatrix} 1 - e^{-\frac{1}{2}(\omega_{LPF} + \sqrt{\omega_{LPF}^{2} - \frac{4K_{PD}K_{VCO}}{N}})t} \\ 1 - e^{-\frac{1}{2}(\omega_{LPF} + \sqrt{\omega_{LPF}^{2} - \frac{4K_{PD}K_{VCO}}{N}})t} \end{bmatrix} \end{bmatrix} u(t)\Delta\omega$$

(2.9)

(2.8) shows that the step response includes two exponential terms decaying with time constants  $\tau_1$  and  $\tau_2$  as

$$\tau_{1} = \left[\frac{1}{2}(\omega_{LPF} - \sqrt{\omega_{LPF}^{2} - \frac{4K_{PD}K_{VCO}}{N}})\right]^{-1}$$

(2.10)

$$\tau_2 = \left[\frac{1}{2}(\omega_{LPF} + \sqrt{\omega_{LPF}^2 - \frac{4K_{PD}K_{VCO}}{N}})\right]^{-1}$$

(2.11)

Since  $au_1 > au_2$ , the settling time is determined by  $au_1$ , which decreases with the increase in  $K_{PD}K_{VCO}/N$ . But, having larger gain degrades the stability. Thus there is a trade-off between the settling time and stability for the type-I PLL. If  $\omega_{LPF}^2 - 4K_{PD}K_{VCO}/N < 0$ , the two poles are complex and the transient step response is given by

$$\omega_{out}(t) = \begin{bmatrix} 1 - e^{\frac{1}{2}\omega_{LPF}t} \cos(\sqrt{\frac{4K_{PD}K_{VCO}}{N}} - \omega_{LPF}^2 t) + \\ \frac{\omega_{LPF}}{\sqrt{\frac{4K_{PD}K_{VCO}}{N}} - \omega_{LPF}^2 t} \sin(\sqrt{\frac{4K_{PD}K_{VCO}}{N}} - \omega_{LPF}^2 t) \end{bmatrix} Nu(t)\Delta\omega \quad (2.12)$$

If the damping factor is greater than one ( $\xi > 1$ ), the system is over-damped and from (2.12), the step response contains only one exponential term with the time constant equal to  $2/\omega_{LPF}$ , which is less than the time constant for real pole case. The larger is the bandwidth, the faster the settling time. In addition to the trade-off between settling time, phase error and bandwidth, type-I PLL suffers from the acquisition range. These problems are addressed by type-II PLL which is called charge pump PLL [20].

## 2.1.3.b Dynamics of Type-II PLL

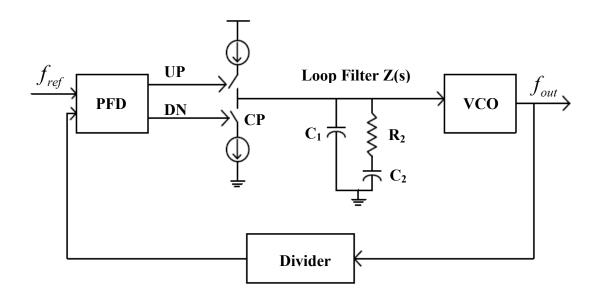

Fig. 2.4: Type-II charge pump PLL

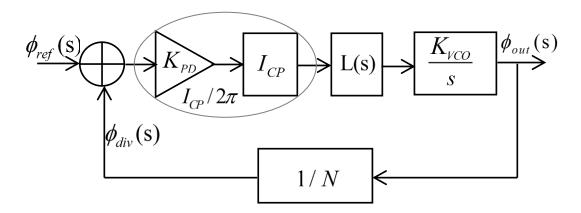

Fig. 2.4 shows the typical type-II charge pump PLL with a 2nd order loop filter. In this architecture the charge pump is used to either sink or source a current with the help of the switches driven by the phase frequency detector (PFD). As a result, the PLL becomes a discrete system rather than a continuous system and strictly, the analysis cannot be performed in s-domain. However, Gardner [20] has proposed a limit that states, as long as the loop bandwidth is less than one-tenth of the reference frequency, the s-domain analysis holds true. Since the PD is replaced by the PFD, the locking range increases. Since the VCO acts as an integrator and the

combination of PFD with the charge pump and the LPF results in another integrator in the loop. Thus there exists two poles at the origin and this type of PLL is called as type-II PLL. Fig. 2.5 shows the linearized model of type-II PLL with their respective transfer functions.

Fig. 2.5: Linear model of a type-II PLL

The open-loop transfer function is given by

$$H_O(s) = \frac{I_{CP} K_{VCO}}{2\pi N} \frac{L(s)}{s}$$

(2.13)

Where the transfer function of the 2<sup>nd</sup> order loop filter is given by

$$L(s) = \frac{1 + sR_2C_2}{s^2R_2C_1C_2 + s(C_1 + C_2)}$$

(2.14)

Here,  $C_2$  together with charge pump generates a pole at the zero frequency while  $R_2$  and  $C_2$  generates a zero at the left half plane to stabilize the system. The location of the zero has to be less than the unity-gain frequency. The additional capacitor  $C_1$  is introduced to generate a pole with  $R_2$  to suppress high frequency components at the VCO control line. For stability, this pole has to be much larger than unity-gain frequency  $\omega_c$ . The zero and pole frequencies are given by

$$\omega_{z1} = \frac{1}{R_2 C_2} = \frac{1}{T_2} \tag{2.15}$$

$$\omega_{p1} = \frac{C_2 + C_1}{R_2 C_2 C_1} = \frac{1}{T_1} \tag{2.16}$$

The closed-loop transfer function is given by

$$H(s) = \frac{I_{CP}K_{VCO}}{2\pi N(C_2 + C_1)} \frac{1 + sRC}{s^3 \frac{R_2C_2C_1}{C_2 + C_1} + s^2 + s \frac{I_{CP}K_{VCO}R_2C_2}{2\pi N(C_2 + C_1)} + \frac{I_{CP}K_{VCO}}{2\pi N(C_2 + C_1)}} \frac{1}{2}$$

(2.17)

Since the pole  $\omega_{p1}$  is far behind the unity gain frequency and  $C_1 > C_2$ , the closed loop transfer function can be re-written as

$$H_C(s) = \frac{I_{CP}K_{VCO}}{2\pi NC_2} \frac{1 + sR_2C_2}{s^2 + s\frac{I_{CP}K_{VCO}R_2}{2\pi N} + \frac{I_{CP}K_{VCO}}{2\pi NC_2}}$$

(2.18)

This can be compared with the standard 2<sup>nd</sup> order negative feedback system from the control theory given by (2.4) and the critical loop parameters are obtained as,

$$\omega_n = \sqrt{\frac{I_{CP} K_{VCO}}{2\pi N C_2}} \tag{2.19}$$

$$\xi = \frac{R_2}{2} \sqrt{\frac{K_{VCO}I_{CP}C}{2\pi N}} \tag{2.20}$$

$$\phi_m = \tan^{-1}\left(\frac{\omega_C}{\omega_{z1}}\right) - \tan^{-1}\left(\frac{\omega_C}{\omega_{p1}}\right)$$

(2.21)

Here,  $\omega_n$  is natural frequency,  $\omega_c$  is loop bandwidth (unity-gain cross over frequency),  $\xi$  is the damping factor and  $\phi_m$  is the phase margin. The poles of the closed-loop system are given by

$$S_{1,2} = \frac{1}{2} \left( -\frac{I_{CP} K_{VCO} R_2}{2\pi N} \pm \sqrt{\left(\frac{I_{CP} K_{VCO} R_2}{2\pi N}\right)^2 - \frac{4I_{CP} K_{VCO}}{2\pi N C_2}} \right)$$

(2.22)

Similar to type-I PLL, the system will have a higher settling time when the two poles are complex, which means

$$\left(\frac{I_{CP}K_{VCO}R_2}{2\pi N}\right)^2 - \frac{4I_{CP}K_{VCO}}{2\pi NC_2} < 0 \Rightarrow \frac{I_{CP}K_{VCO}}{2\pi N} < \frac{4}{R_2^2C_2} \tag{2.23}$$

Based on this, the transient response for the system with complex poles is given by

$$\omega_{out}(t) = \left[1 - e^{\frac{1}{2}(\frac{I_{CP}K_{VCO}R_{2}}{2\pi N})t}\right] \left[\frac{\cos(\sqrt{\frac{4I_{CP}K_{VCO}}{2\pi NC_{2}}} - \left(\frac{I_{CP}K_{VCO}R_{2}}{2\pi NC_{2}}\right)^{2}t) + \frac{R_{2}C_{2}}{2\sqrt{\frac{4I_{CP}K_{VCO}}{2\pi NC_{2}}} - \left(\frac{I_{CP}K_{VCO}R_{2}}{2\pi NC_{2}}\right)^{2}}\sin(\sqrt{\frac{4I_{CP}K_{VCO}}{2\pi NC_{2}}} - \left(\frac{I_{CP}K_{VCO}R_{2}}{2\pi N}\right)^{2}t)\right]Nu(t)\Delta\omega$$

(2.24)

The step response contains only one exponential term with the time constant  $\tau$  expressed as,

$$\tau = \left(\frac{1}{2} \frac{I_{CP} K_{VCO} R_2}{2\pi N}\right)^{-1} \tag{2.25}$$

From the above study, the settling time is minimized by increasing  $I_{CP}K_{VCO}$ , thus there is no trade-off between critical specifications in the selection of  $I_{CP}K_{VCO}$ .

However, the increase of  $I_{CP}K_{VCO}$  is bounded by the unity gain frequency, which is no more than one-tenth of the reference frequency as stated by the Gardner [20].

## 2.2 Types of PLL

Several types of PLL [21] architectures are available in market. The architectures broadly range according to the application. These different architectures of PLL can be considered as different types of PLL. Following types of PLL are classified according to their application.

- 1. Programmable PLL: This type of PLL can be programmed for wide range of signals.

- 2. Single and multi-phase PLL: These can control a single or many phases. They are used in digital clock networks.

- 3. Digital Phase Locked Loop: They are used digital input signals for application like Manchester coding.

- 4. PLL with lock detector: It uses a lock on one of the pins and is used in frequency modulation.

- 5. PLL frequency synthesizer: These are used to synthesize the frequency of different range and band.

- 6. PLL FM/AM demodulator: The FM/AM radio frequencies are modulated and demodulated using this type of PLL.

- 7. Single RF/ Multi RF PLL: It is used for controlling single or multiple radio frequencies.

- 8. Super PLL: It is used for frequency synthesizing of radios, networks of GSM, cordless phones, etc.

PLLs are also classified according to the type of loop filter used in architecture. The order of loop filter is the type of PLL. For example, if 1st order loop filter is used, then it is called as type I PLL. If 2nd order filter is used, it is called as type II PLL and so on.

If PLL uses simple "Phase detector" in its architecture, it is called as simple PLL. But if PLL uses "Phase Frequency Detector" accompanied with "Charge Pump", it is called as "Charge Pump PLL".

# 2.3 Types of Frequency Synthesizers

From the above study and analysis, the PLL output frequency could be programmed by setting frequency division ratio to different values. Indeed, the PLL based frequency synthesizer is the most widely used frequency synthesizer approach in modern wireless communications systems.

## 2.3.1 Integer-N Frequency Synthesizer

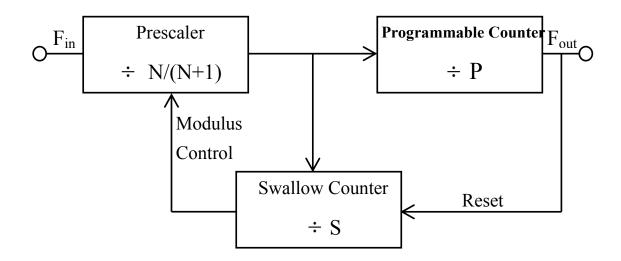

An integer-N frequency synthesizer consists of integer-N divider with integer division ratios. The advantage of this type of synthesizer is the robust design of the frequency dividers. The most commonly used integer-N divider is pulse-swallow divider as shown in Fig. 2.6.

Fig. 2.6: Pulse-swallow frequency divider

Here, the PLL output is the integer multiple of the reference frequency and the finest PLL output frequency change equals to the reference frequency. Therefore, the required frequency spacing sets the upper-limit of the reference frequency. This results in the limited bandwidth, larger settling time and high close-in output phase noise.

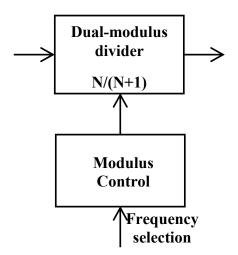

## 2.3.2 Fractional-N Frequency Synthesizer

In a fractional-N frequency synthesizer [18], the smallest frequency step can be a fraction of the reference frequency. A simple fractional divider is shown in Fig. 2.7 which consists of a N/(N+1) dual-modulus divider and a modulus control unit. The modulus control unit sets the instantaneous division ratio to either N or N+ 1 ratio so that the division ratio is a fractional number between N and N+1. If the division ratio is N for P cycles of the output and N+1 for Q cycles of the output, the equivalent division ratio is equal to (PN+Q(N+1))/(P+Q).

Fig. 2.7: A fractional frequency divider

Since the output is obtained by averaging instant ratios over time, the spectrum of divider output contains spurious tones called fractional spurs at the output of the PLL. The problem is severe when P and Q are constant over time. To address this issue, a delta-sigma modulator has introduced in place of modulus control unit which

transforms the fractional spurs to random noise. However, this approach increases the complexity and power consumption.

## 2.3.3 Direct Digital Synthesizer

A direct digital synthesizer (DDS) generates carrier frequency very fast by removing the feedback as shown in Fig.2.8. A DDS generates the signal in the digital domain through an accumulator and a read-only memory (ROM), which is converted to analog waveform by digital-to-analog converter (DAC). Spurious harmonics at the output of DAC are filtered out by low pass filter (LPF). Since this architecture employs no feedback, settling time is very fast. The main advantages of DDS are low phase noise, fine frequency steps and no stability issues.

Fig. 2.8: A direct digital synthesizer

The main drawback of DDS is its low output frequency due to the practical speed limit of the DAC. To reconstruct the analog waveform correctly, the clock frequency has to be no less than twice of the output frequency (Nyquist"s theorem). In RF applications, to have all the digital blocks of DDS work at least twice the carrier frequency is very difficult to achieve. The non-idealities of DAC are also major concerns.

#### 2.4 Non Ideal Effects in PLL

So many imperfections always remain in practical PLL circuit. Ideally, the synthesized signal is a pure sinusoidal waveform. But in reality, its power spectrum features a peak at the desired frequency and tails on both sides. The uncertainty of a synthesizer's output is characterized by its phase noise (or spur level) at a certain frequency offset from the desired carrier frequency in unit of dBc/Hz (or dBc). The

unit of dBc/Hz measures the ratio (in dB) of the phase noise power in 1Hz bandwidth at a certain frequency offset to the carrier power. Similarly, the unit of dBc measures the ratio (in dB) of the spur (also known as tone) power at a certain frequency offset to the carrier power. These lead to high ripple on the control voltage even when the loop is locked. These ripples modulate the VCO frequency, which results in non-periodic waveform. This section considers these non-ideal effects in PLL [16],[22], [23].

#### 2.4.1 Jitter in PLL

Timing jitter is the time domain characterization of the uncertainty of a synthesizer or oscillator's output. A jitter is the short-term variations of a signal with respect to its ideal position in time. This problem negatively impacts the data transmission quality. Deviation from the ideal position can occur on either leading edge or trailing edge of signal. Jitter may be induced and coupled onto a clock signal from several different sources and is not uniform over all frequencies. Denoting the period of the nth cycle of an oscillator's output as  $T_n$  and its average period is T, there are basically three-types of jitters:

(1) The cycle jitter, or cycle-to-average jitter, is defined as:

$$\Delta T_{cn} = T_n - \overline{T} \tag{2.26}$$

(2) The cycle-to-cycle jitter is expressed as:

$$\Delta T_{ccn} = T_{n+1} - T_n \tag{2.27}$$

(3) The absolute jitter, also known as long-term jitter or accumulated jitter, of the  $N_{th}$  cycle can be described as:

$$\Delta T_{abs}(N) = \sum_{n=1}^{N} (T_n - \overline{T}) = \sum_{n=1}^{N} (\Delta T_{cn})$$

(2.28)

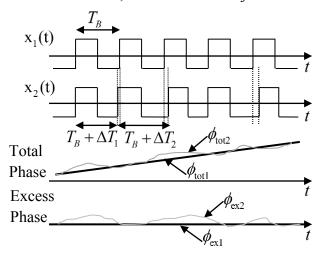

The response of PLL to jitter is very important in most applications. Fig. 2.9 explains the jitter in PLL.

As shown in Fig. 2.9, a strictly periodic waveform, x1(t), contains zero crossings that are evenly spaced in time. Now consider nearly periodic signal x2(t),

whose period experiences a small changes, deviating the zero crossing from their ideal points. Hence we can say that x2(t) suffers from jitter. If the instantaneous frequency of signal varies slowly from one period to next period, then it is called as "slow jitter", and if the variation is fast, it is called as fast jitter.

Fig. 2.9: Ideal and Jittery Waveforms

#### 2.4.2 Phase Noise

Phase noise is random variation of phase of the signal. It is the frequency domain representation of rapid, short term fluctuations in the phase of the wave, caused by time domain instabilities ("jitter"). Generally the phase noise and jitter are closely related. Or more specifically, radio engineer call it as phase noise, but digital system engineer call it as jitter of the clock.

The ideal synthesizer produces a pure sinusoidal waveform

$$V(t) = V_0 \sin(2\pi f_0 t)$$

((2.29)

When amplitude and phase fluctuations are accounted, the waveform becomes

$$V(t) = (V_0 + v(t))\sin(2\pi f_0 t + \phi(t))$$

(2.30)

where V(t) and  $\phi(t)$  represent amplitude and phase fluctuations, respectively. Here two types of phase fluctuations are considered, the periodic variation and the random variation [17]. In mathematical form,  $\phi(t)$  can be written as:

$$\phi(t) = \Delta\phi \sin(2\pi f_{\perp}t) + \phi(t) \tag{2.31}$$

The first term represents the periodic phase variation and it produces a spurious tone at an offset frequency of  $f_m$  from the carrier frequency  $f_0$ . The magnitude of the spurious tone can be derived as follows:

$$V(t) = V \sin(2\pi f t + \Delta \phi \sin(2\pi f t))$$

(2.32)

$$= V_0 \left[ \sin(2\pi f_0 t) \cos(\Delta \phi \sin(2\pi f_m t)) + \cos(2\pi f_0 t) \sin(\Delta \phi \sin(2\pi f_m t)) \right]$$

For very small phase modulation, i.e.,  $\Delta \phi << \pi / 2$

$$\cos(\Delta\phi\sin(2\pi f\,t)) \approx 1\tag{2.33}$$

$$\sin(\Delta\phi\sin(2\pi f_{\perp}t)) \approx \Delta\phi\sin(2\pi f_{\perp}t) \tag{2.34}$$

Then (2.4) yields:

$$V(t) = V \left[ \sin(2\pi f_0 t) + \Delta \phi \cos(2\pi f_0 t) \sin(2\pi f_m t) \right]$$

$$=V_{0}\left[\sin(2\pi f_{0}t)-\frac{\Delta\phi}{2}\sin(2\pi(f_{0}-f_{m}))+\frac{\Delta\phi}{2}\sin(2\pi(f_{0}+f_{m}))\right] \quad (2.35)$$

From (2.35) we observe that the two spurious tones at  $f_0 + f_m$  and  $f_0 - f_m$  are both  $-20\log(\Delta\phi/2)dB$  below the carrier. The second term of  $\phi(t)$  in (2.31) represents the random phase variation and it produces phase noise. The spectral density of phase variation is

$$S_{\varphi}(f) = \int_{\varphi}^{+\infty} R_{\varphi}(\tau) e^{-j2\pi f \tau} d\tau \qquad (2.36)$$

where  $R_{arphi}( au)$  is the auto-correlation of the random phase variation arphi(t) :

$$R_{\sigma}(\tau) = E[\varphi(t)\varphi(t-\tau)] \tag{2.37}$$

When the root-mean-square (rms) value of  $\varphi(t)$  is much smaller than 1 radian, the power spectrum density of V(t) can be approximated as

$$S_{V}(f) = \frac{V_{0}^{2}}{2} \left[ \delta(f - f_{0}) + S_{\varphi}(f - f_{0}) \right]$$

(2.38)

It consists of the carrier power at  $f_0$  and the phase noise power at frequency offsets from  $f_0$ . The single-sideband (SSB) phase noise is defined as the ratio of noise power in 1Hz bandwidth at a certain frequency offset  $\Delta f = f - f_0$  from the carrier to the carrier power. The unit is dBc/Hz.

$$N(\Delta f) = 10 \log \frac{(\text{noise\_in\_}1Hz \ at \ f)}{P_{carrier}} = 10 \log \frac{S_{\varphi}(\Delta f)}{2} \frac{1}{2} \qquad dBc/Hz$$

(2.39)

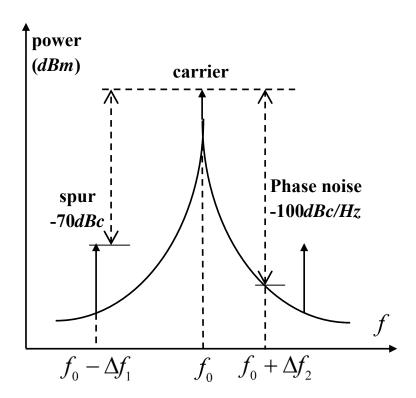

Fig. 2.10: Phase noise and spur

Therefore, the phase noise dBc/Hz value observed on the spectrum analyzer is numerically equivalent to  $10\log[S_{\varphi}(\Delta f)]-3$ . Fig. 2.10 illustrates the phase noise and spurs of a synthesized signal of frequency  $f_0$ . The spur level at an offset frequency of  $-\Delta f_1$  is -70dBc, and the phase noise at an offset frequency of  $\Delta f_2$  is -100dBc/Hz.

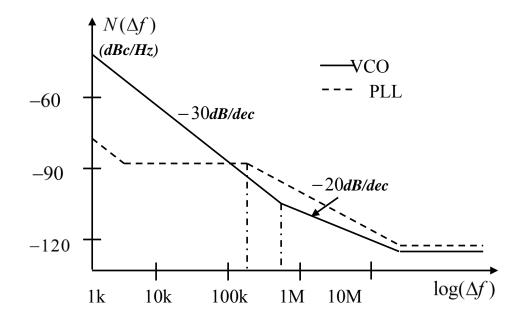

Fig. 2.11: Phase noise of VCO and PLL

Fig. 2.11 conceptually shows the phase noise of a voltage-controlled oscillator (VCO) and a phase-locked loop (PLL). The phase noise of a VCO demonstrates regions with slopes of -30dBc/dec and -20dBc/dec, and a flat region. A PLL"s inband phase noise is usually as flat as its reference input, while its out-band phase noise follows that of the VCO.

Phase noise is of very much concern in PLL, since it directly affects the entire performance of the system. Following are the common sources of phase noise in PLL.

i) **Oscillator noise**: There are two oscillators that contribute to the phase noise of the PLL. One is the reference oscillator and other is the VCO. Although both oscillators can be modeled similarly, their effects on the output noise are distinct just due to their position in the loop. Suppose a noiseless VCO is added with AWGN with DSPSD of No/2. Then the output power spectrum is given by  $2KVCO((No/2)\omega 2)$ . Though it is very simplified equation, it clearly gives the idea of output noise of PLL in the presence of VCO noise. The reference oscillator is also assumed to have sufficient behavior with different constant of proportionality.

- ii) **Frequency Divider noise**: The excess noise of a digital divider can be modeled as additive noise source at its output. In a PLL, this noise directly appears at the input of phase detector and experiences the same transfer function as the noise on the input terminal.

- iii) **Phase detector noise**: Usually phase detectors are not major sources of noise in PLLs. As the work of PD is to detect the phase difference, any random variation in the phase of input signal makes the phase detector to produce wrong output, which is get transferred through filter and tunes the VCO wrongly.

### 2.4.3 Reference spur

Reference spurs are spurious emissions that occur from the carrier frequency at an offset equal to the channel spacing. These are usually caused by leakage and mismatch in charge pump of PLL. Though they occur outside the band of interest, they can enter the mixers and be translated back onto band of interest.

Reference spur mainly occurs in Charge Pump PLL. Though there is no phase difference between reference and feedback signal, in the locked state, the phase detector (or phase frequency detector) produces very narrow pulse width error voltage which drives the charge pump. Although these pulses have a very narrow width, the fact that they exist means that the dc voltage driving the VCO is modulated by a signal of frequency equal to input reference frequency. This produces reference spurs in the RF output occurring at offset frequencies that are integer multiples of input reference frequency. A spectrum analyzer can be used to detect reference spurs. Simply increase the span to greater than twice the reference frequency.

Let  $I_{cp}$  is charge pump current,  $I_{leak}$  is leakage current in CP then the phase offset is given by:

$$\Phi_{\in} = 2\pi \cdot \frac{I_{\text{leak}}}{I_{\text{cp}}} [rad]$$

(2.40)

Now if  $f_{ref}$  is the input reference frequency,  $f_{BW}$  is loop bandwidth,  $f_{pl}$  is the frequency of pole in loop filter and N is the division value then the amount of reference spur in 3rd order PLL is given by:

$$P_{r} = 20 \log \left( \frac{1}{\sqrt{2}} \cdot \frac{f_{ref}}{f_{BW}} \cdot N \cdot \Phi_{\epsilon} \right) - 20 \log \left( \frac{f_{ref}}{f_{pl}} \right) [dBc]$$

(2.41)

If reference spur is not enough to meet the requirement, the loop bandwidth should be further narrowed or charge pump current should be increased. It is also helpful to reduce the division value to relax the charge pump design.

### 2.5 Applications of PLL

Since its invention, PLL continues to find new applications in electronics, communication and instrumentation. Examples include memories, microprocessors, hard disk drive electronics, RF and wireless transceivers, clock recovery circuits on microcontroller boards and optical fiber receivers. Some of the applications are as follows [16].

### 2.5.1 Frequency multiplication and synthesis

A PLL can be modified such that it multiplies its input frequency by factor of M. Fig. 2.12 shows basic frequency multiplication concept.

Fig. 2.12: Frequency Multiplication

Just like a voltage divider is used in feedback in voltage amplifier, as shown in Fig. 2.5, output frequency of PLL is divided by M and applied to the phase detector, we

get,  $f_{out} = M.f_{in}$ . Also, since fin and  $f_D$  must be equal, PLL multiplies  $f_{in}$  by M. Some systems require a periodic waveform whose frequency (a) must be very accurate and (b) can be varied in very fine stapes. Hence to synthesize a required frequency, a channel control word (digital) is applied to divider block in feedback that varies the value of M. Since  $f_{out} = M.f_{in}$ , the relative accuracy of  $f_{out}$  is equal to that of  $f_{ref}$ . It is also notable that  $f_{out}$  varies in stapes equal to  $f_{ref}$  if M changes by one each time.

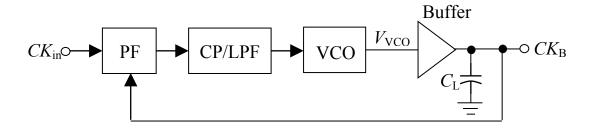

#### 2.5.2 Skew reduction

This is one of the very popular and earliest uses of PLL. Suppose synchronous pair of data and clock lines enter a large digital chip. Since clock typically drives a large number of transistors and logic interconnects, it is first applied to large buffer. Thus, the clock distributed on chip may suffer from substantial skew (delay due to buffer insertion) with respect to data. This is an undesirable effect which reduces the timing budget for on-chip operations.

Now consider the circuit as shown in Fig 2.13. Here input clock  $CK_{in}$  is applied to on chip PLL and buffer is placed inside the loop. Since PLL guarantees a nominally zero phase difference between  $CK_{in}$  and  $CK_{B}$ , the skew is eliminated. That is, the constant phase shift introduced by the buffer is divided by infinite loop gain of the feedback system. Alignment of  $V_{VCO}$  with  $CK_{in}$  is not important since  $V_{VCO}$  is not used.

Fig. 2.13: Use of PLL to Eliminate Skew

# CHAPTER 3

# Frequency Synthesizer Building Blocks

## 3.1 Phase detector/Phase Frequency Detector (PD/PFD)

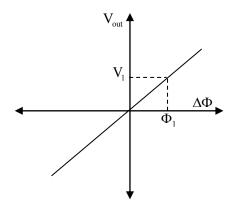

A phase detector (PD) [24]-[26] is a circuit whose average output voltage ( $\overline{V_{out}}$ ) is linearly proportional to the phase difference ( $\Delta\phi$ ) between its two inputs. In an ideal case, the relationship between  $\overline{V_{out}}$  and  $\Delta\phi$  is linear, crossing the origin for  $\Delta\phi$ =0 as shown in Fig. 3.1. The gain of the PD is K<sub>PD</sub> expressed in V/rad.

Fig. 3.1: Phase detector characteristics

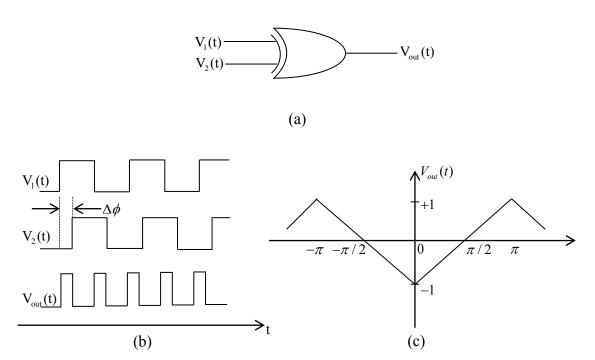

#### A. XOR Based PD

A familiar example of phase detector is the exclusive OR (XOR) gate [19] as shown in Fig.3.2. As the phase difference between the inputs varies, so does the width of the output pulses, thereby providing a dc level proportional to  $\Delta \phi$ . The XOR PD produces error pulses on both rising and falling edges. Fig.3.2c shows the transfer characteristics of the XOR PD.

Fig. 3.2: XOR phase detector and phase characteristics

The major drawback of XOR PD is its inability to detect frequency difference. As any frequency difference exists, the phase difference would be accumulated either in a positive direction (reference frequency slower than divider frequency) or in a negative direction (reference frequency faster than divided frequency). As shown in Fig. 3.2c, the transfer function of PD is symmetrical over y-axis due to which it fails to differentiate the polarity of phase difference, and thus the frequency difference. The second issue is that, when the PLL is locked, the average of XOR PD output is zero. This zero voltage is averaged from a square wave of twice the reference frequency. Therefore, the pole of LPF has to be low enough to attenuate this reference spur. The XOR PD is sensitive to the duty cycle of the input signals.

### B. D flip-flop Based PD

A simple D flip-flop (DFF) could also be used as a phase detector [27]. Here, the reference signal serves as a clock to sample the divided VCO signal. When reference leads the feedback divider signal, the output remains at logic "1" and if

the reference lags the feedback divider signal, the output switches to logic "0". Therefore, the DFF based PD operation is highly nonlinear and leads to the stability issue and phase error. This PD also fails to detect any frequency difference.

## C. Tri-State Phase Frequency Detector (PFD)

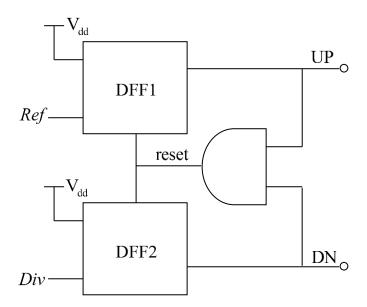

The XOR and DFF based PD's fail to detect the frequency difference and are not suitable for PLL applications where initial VCO oscillation frequencies are far away from reference. A tri-state PFD [28] detects both phase and frequency difference. Fig.3.3 shows the implementation of the PFD.

Fig. 3.3: Tri-state PFD implementation

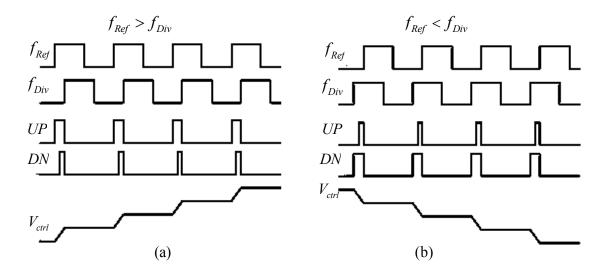

Let *Ref* be the reference signal, and *Div* the divider output signal. If *Ref* leads *Div*, the rising edge of *Ref* triggers DFF1 and the UP signal is switched from 0 to 1 and DN signal remains at 0. The UP signal remains at 1 until the occurrence of rising edge of *Div* which triggers DFF2 and the UP signal is reset to 0 by the AND gate. A similar behavior happens when *Ref* lags *Div*. The phase difference between *Ref* and *Div* is indicated by the difference between UP and DN signals.

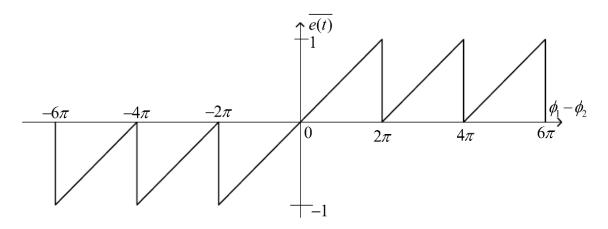

Fig. 3.4: Transfer characteristics of a tri-state PFD

Fig.3.4 shows the transfer characteristics of a tri-state PFD which is unsymmetrical over y-axis and the output has the same sign as that of the phase difference. Therefore, the output would be in opposite polarities between positive and negative frequency difference. When Ref leads Div ( $f_{Ref} > f_{Div}$ ), the resulting positive pulses appear at UP while DN stays at 0. When Ref lags Div ( $f_{Ref} < f_{Div}$ ), the resulting positive pulses appear at DN while UP stays at 0. Thus, the average of UP-DN suggests the frequency difference.

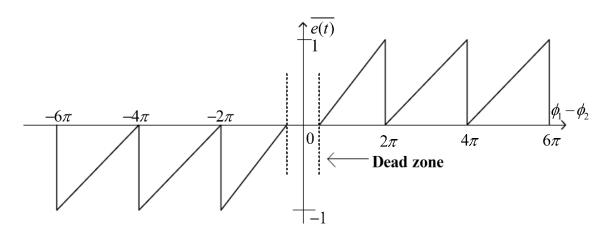

Fig. 3.5: Dead zone in tri-state PFD

However, tri-state PFD suffers from the "dead zone" problem [29]. The transfer function curve under the dead zone is given in Fig.3.5. When the phase difference between *Ref* and *Div* is close to zero, the width of the UP and DN pulses would approach to a minimal, which is set by the delay of the AND gate in the feedback path. However, the charge pump may not be to detect such narrow pulses, resulting

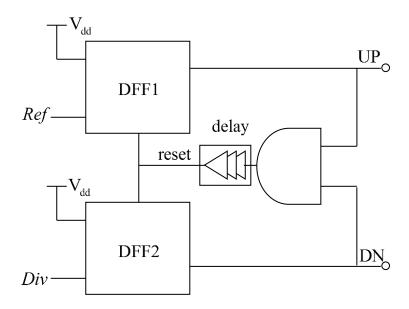

to no current injecting to the LPF, which is almost similar to the case of zero phase difference. As a result, the PFD gain is down to zero and the PLL loop would not function and there would be an unpredictable phase error between the two inputs so the jitter at output of the PLL accumulates. The dead zone in the PFD is avoided by introducing delay after the AND gate in the feedback path to increase the propagation delay as shown in Fig.3.6. However, this technique increase the charge pump mismatch current causing reference spurs.

Fig. 3.6: Dead zone free PFD

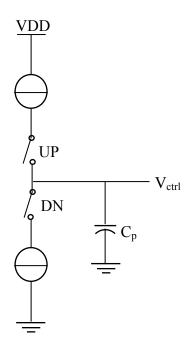

### 3.2 Charge Pump

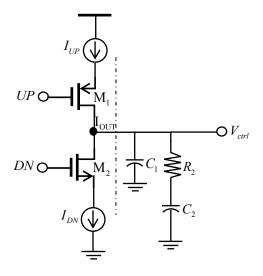

Fig. 3.7: Charge pump with loop filter

A charge pump [31] generally consists of two current sources that are switched on and off at the proper instance of time. When Ref leads Div (  $f_{Ref} > f_{Div}$ ), the resulting positive pulses appear at UP while DN stays at 0. Under this condition, M1 is turned-on and M2 is turned-off such that the current  $I_{UP}$  charges the loop filter to pull-up the VCO frequency as shown in Fig.3.8a. When Ref lags Div (  $f_{Ref} < f_{Div}$ ), the resulting positive pulses appear at DN while UP stays at 0. Under this condition, M1 is turned-off and M2 is turned-on such that the current  $I_{DN}$  discharges the loop filter to pull-down the VCO frequency as shown in Fig.3.8b. Under locked condition when Ref is equal to Div (  $f_{Ref} = f_{Div}$ ), both switches M1 and M2 are on for a short period equal to the dead zone pulse width and net current flowing into the loop filter is negligible.

Fig. 3.8: Charge pump transient analysis a) Ref leads Div b) Ref lags Div

Charge pump suffers from non-ideal effects. Switches are constructed using PMOS and NMOS. The inherent mismatches between these two switches results in mismatch in charging and discharging current in addition to timing mismatch. Hence there is variation in control voltage at the output. In fact the W/L ratios are adjusted so as to have equal UP and DOWN currents. That means, since two current sources are themselves mismatched, the control voltage experiences the random changes in it. There is also problem of charge sharing between output node of charge pump (in

fact between filter capacitor) and the parasitic capacitances between drain and source of switch transistors. This results in sudden change in control voltage which may disturb the VCO. Another effect is clock feed through. The high frequency signal provided at the gate of switch transistor passes to the output node via gate to drain parasitic capacitor Cgd. This also results in jumps in control voltage. Since the VCO sensitivity is high, even a small jump in control voltage results a large jump in output frequency. Later on in chapter 4 we will use some techniques to overcome these non-idealities.

### 3.3 Voltage Controlled Oscillator (VCO)

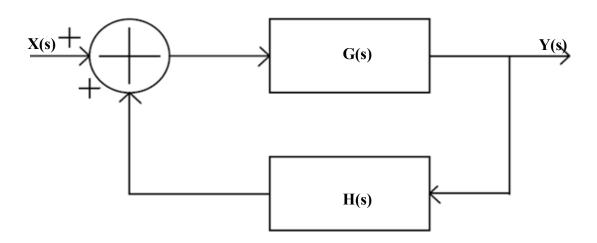

Fig. 3.9: Feedback oscillatory system

The voltage controlled oscillator (VCO) is an important building block of a PLL synthesizer which generates periodic signals. Consider a linear feedback system shown in Fig.3.9 and its transfer function is given by [19],

$$\frac{Y(s)}{X(s)} = \frac{G(s)}{1 - G(s)H(s)}$$

(2.48)

Oscillation happens if a stable periodic signal is produced and in the steady state, Barkhausen's criteria must be satisfied at  $\omega_0$  [19]:

(1) The loop gain

$$|G(s)H(s)| \ge 1$$

# (2) The total phase shift around the loop, $\angle G(s) + H(s) = 0^{\circ}$ or $360^{\circ}$

While Barkhausen's criteria explain the steady state of the VCO, it does not give hints on how the VCO converts its own noise in to periodic signal with certain amplitude. Actually, during oscillation start-up, the loop gain |G(s)H(s)| must be larger than unity to amplify noise at  $\omega_0$ . The nonlinearity of VCO would eventually limit the amplitude of the signal to a certain level, arriving at the steady state when the average loop gain is unity. Commonly, both ring oscillators and LC oscillators are used in GHz range applications [32],[33]. However, ring oscillators suffer from poor phase noise compared to that of LC oscillators [34],[35]. Ring oscillators are more attractive due to their smaller area compared to that of LC oscillators and are suitable for applications where such level of phase noise is acceptable.

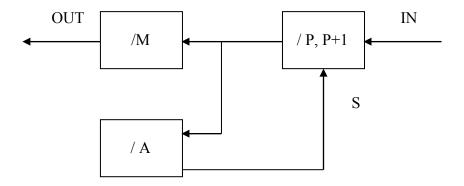

#### 3.4 Divider

The divider in the feedback path of the PLL determines the output frequency of the VCO in locked state. Typically the divider sees the full range of frequencies in the loop (from several hundred kHz to several GHz). The divider must be programmable to select different channels for the desired application. Due to different speed requirement, the divider is usually implemented by a combination of different logic family circuits. In the low speed part, the full swing conventional CMOS logic is used for its low static power consumption.

Fig. 3.10: Programmable divider

A programmable divider usually consists of a prescaler and two counters in a pulse swallow architecture [36], Fig. 3.10. The dual modulus prescaler divides the input frequency by either P or P+1 depending on the setting signal S. But in our design, we have purposely used static N divider which is explained in chapter 4. The output of the prescaler serves as the input of counter A and counter M. In our design we have omitted the A (swallow) counter. At the beginning, the prescaler is in the divide by P+1 mode. When counter A reaches zero, the setting signal S sets the prescaler in the divide by P mode. This mode continues until counter M reaches zero. For a complete cycle, it takes MP+A edges of the input to generate one edge at the divider output. This means that the divider divides the input by MP+A.

# CHAPTER 4

# **CMOS RF Wide Band Frequency Synthesizer Design**

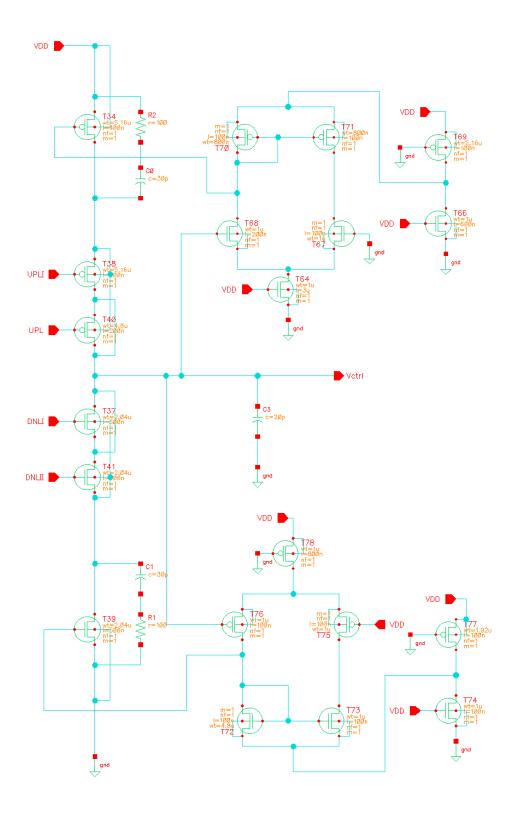

### 4.1 Phase Frequency Detector Design

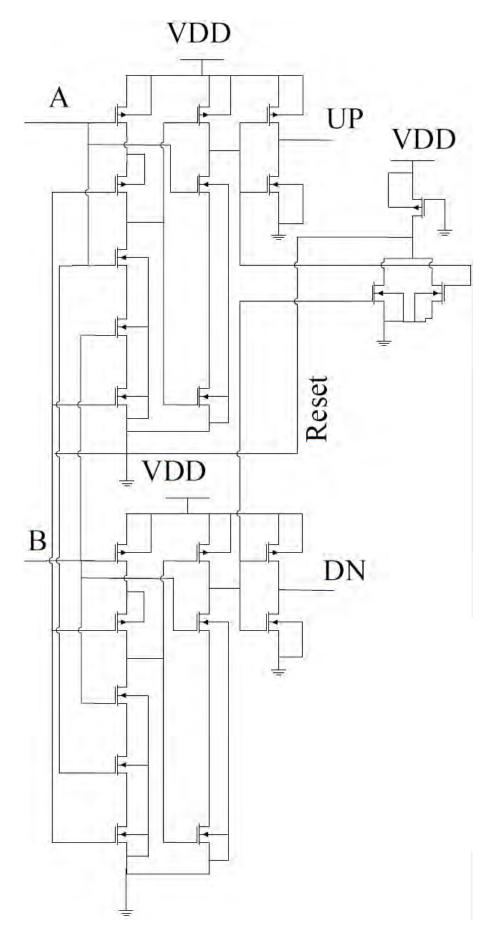

A Phase Frequency Detector (PFD) consists of two positive edge triggered D flip flop [37], which compares the reference and feedback clock continuously. The not gate and a delay buffer is used to reset the PFD when both the pulses go high, a state which we avoid to achieve. Since, when both the signals go high we don"t want the PFD to keep working so we add a delay and then reset the D flip flops. To take a further look into what makes this D flip flop achieve its intended operation we will take a look at transistor level circuit diagram of the PFD.

The Phase Frequency Detector used in this design of PLL is similar to [38] with certain modification to achieve fast operation. According to [38], the Phase Frequency Detector consists of two D flip flops. Each D flip flop has 8 transistors and one extra CMOS inverter to get the positive output. The number of transistors has been reduced compared to [39] to further increase the operating frequency of the PFD. The two PMOS is connected to the VDD, the clocks and the reset pulse. When the Clock and Reset are both low then the PMOS turns "ON" and latches with the VDD and holds its value till the positive edge of the clocks. This is the basic idea of this flip flop. When the RESET turns high the PMOS is switched off and the node below PMOS is latched to ground via the 3 NMOS transistors. The transistor level circuit diagram of PFD in [38] is shown in Fig. 4.1. The UP and DN signals are obvious reference to slowing and speeding of the VCO.

Fig. 4.1: Transistor Level PFD Circuit Diagram [38]

The following table and waveform in Fig. 4.2 explains the operating principle of Phase Frequency Detector.

TABLE 4.1

Operating principle of Phase Frequency Detector

| UP | DN | Effect:         |

|----|----|-----------------|

| 0  | 0  | No Change       |

| 0  | 1  | Slow Down       |

| 1  | 0  | Speed Up        |

| 1  | 1  | Avoid Dead-Zone |

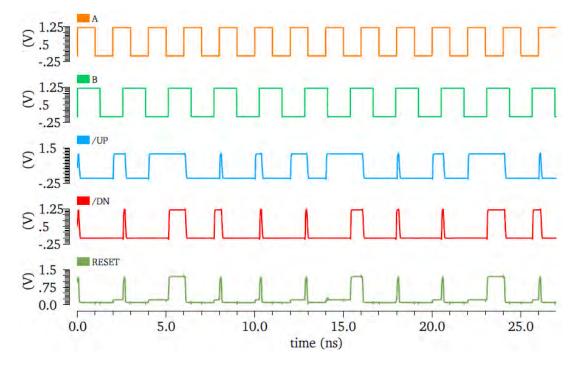

As it can be seen from the simulation in Fig. 4.2, when the rising edge of the clock A leads that of the clock B, UP goes high while the DN remain in the low position causing the DN to speed up. When B leads A, UP remains low while the DN goes high, causing the UP to speed up. The reset is activated when both the UP and DN line (outputs of the D flip flop) are both high.

Fig. 4.2: Waveforms of PFD [38]

The UP and DN signals drive the charge pump which in turn charges and discharges the loop filter depending on the values of UP and DN signals. In the Fig. 4.2, the frequency of A is higher than that of B. Hence the charge pump must charge the loop filter to speed up the frequency of the oscillator. As it can be seen from the above figure that both UP and DN signals may simultaneously be high for a longer period of time irrespective of the frequencies of A and B and this increases the charging and discharging time of the loop filter by the charge pump. Ideally, if the frequency of A is higher than that of B, then DN signal must remain low or if the frequency of B is higher than that of A, then UP signal must remain low, otherwise it will take longer to charge and discharge as the case may be.

Fig. 4.3: Waveforms showing the UP, DN, and Charge Pump output signal where frequency of A is greater than that of B

In Fig. 4.3, A and B are the input signals of the two D flip flops used in the PFD and the frequency of A is higher than that of B. The UP signal remains high for longer period of time compared to the DN signal. The last waveform is of charge pump output which we will discuss in the next section in detail. It is clearly seen that the output of the charge pump is charged with the passage of time to boost up the

oscillator frequency. Fig. 4.4 explains the discharging phenomenon when the frequency of B is greater than that of A.

Fig. 4.4: Waveforms showing the UP, DN, and Charge Pump output signal where frequency of B is greater than that of A

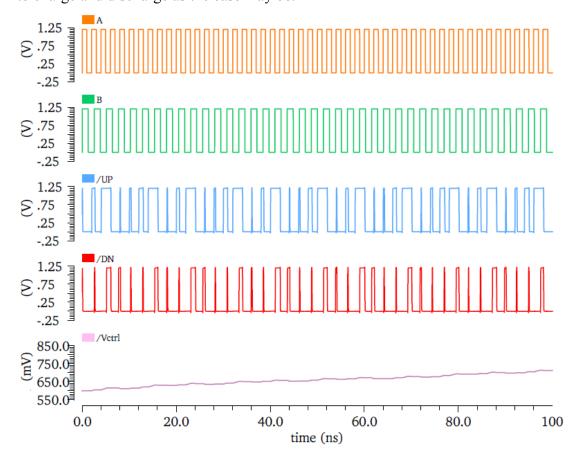

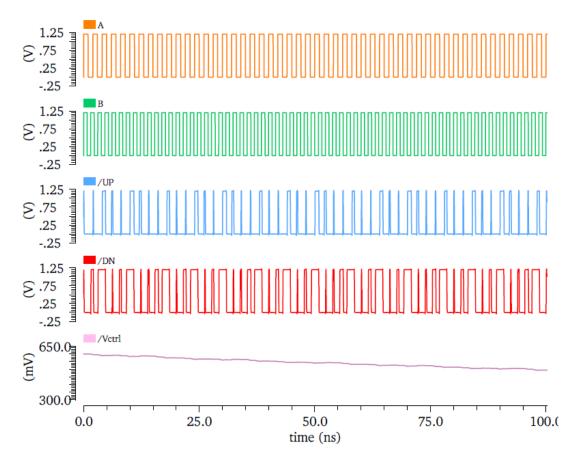

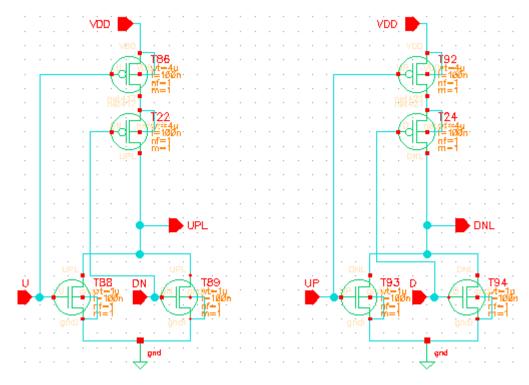

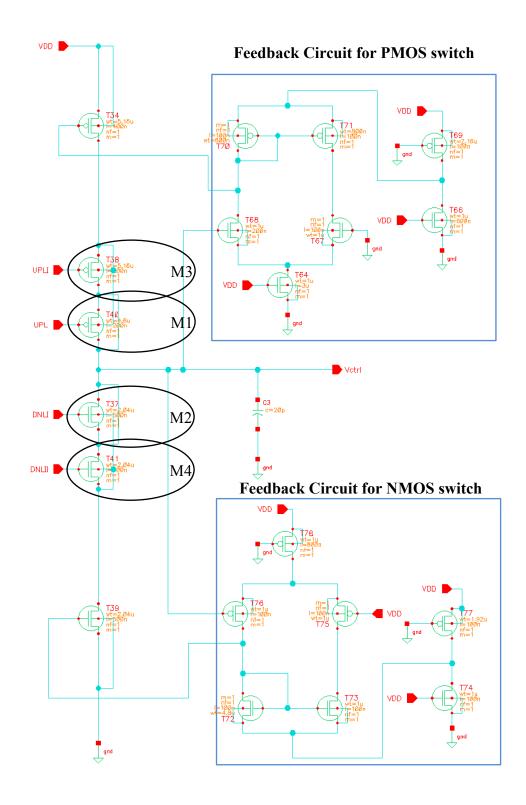

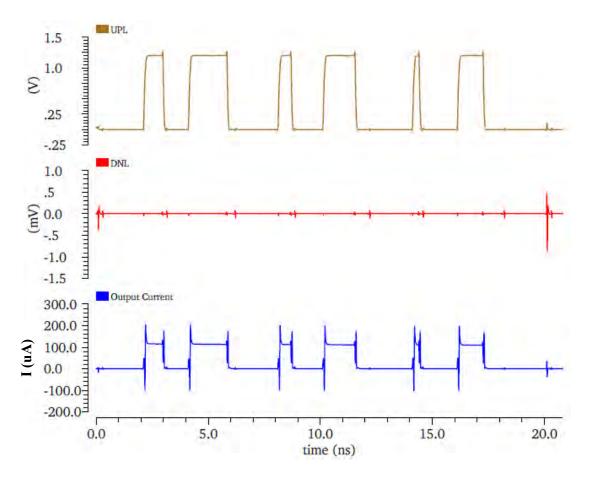

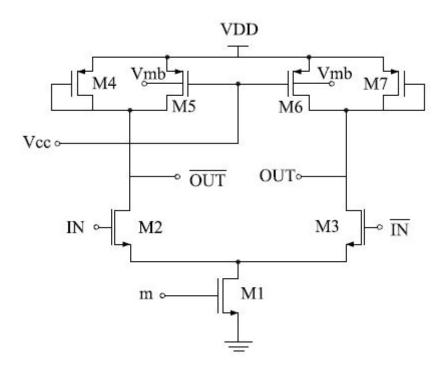

To minimize the chances of UP and DN signal to be high simultaneously, the circuit which we name as "auxiliary circuit" in Fig. 4.5 is added to that in Fig. 4.1 and in the auxiliary circuit  $\overline{U}$  =UP and  $\overline{D}$  =DN. This auxiliary circuit speeds up the charging and discharging of the loop filter. The auxiliary circuit takes UP and DN as its inputs. Now the output of PFD is UPL and DNL instead of UP and DN. If we compare Fig. 4.3 with that of Fig. 4.6 and Fig. 4.4 with that of Fig. 4.7, it is clearly seen that in a given period of time, the loop filter charges and discharges fast with the addition of the auxiliary circuit. In figure 4.6 and figure 4.7, UPL and DNL are the up and down signals at the output of the auxiliary circuit.

Fig. 4.5: IBM 90nm CMOS Process PFD Auxiliary Circuit Implementation

Fig. 4.6: Waveforms after addition of auxiliary circuit showing the UP, DN, and Charge Pump output signal where frequency of A is greater than that of B

Fig. 4.7: Waveforms after addition of auxiliary circuit showing the UP, DN, and Charge Pump output signal where frequency of B is greater than that of A

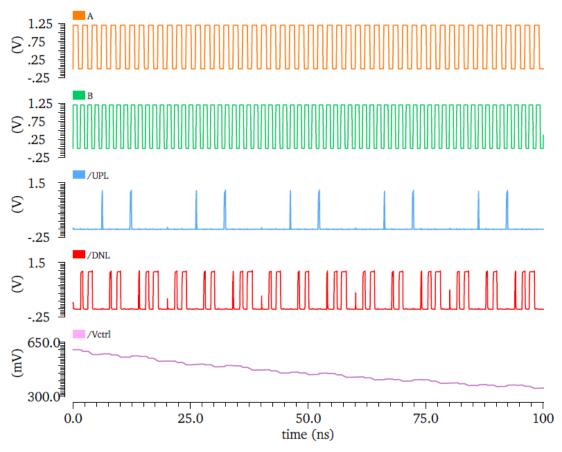

### 4.2 Charge pump and Loop filter Design

The Charge Pump and Low Pass Filter govern the stability and smoothness of the PLL system. Generally the design of these block are overlooked but should be given considerable amount of time doing so. The Charge Pump (CP) takes the output of the PFD's UP and DOWN pulses as its input. The Charge Pump then produces a single output depending on charging and discharging state of the Charge Capacitor (Cp). The Low Pass Filter takes the Charge Pump output, it integrates its output and low pass filters the ripples to bring it down to close to DC level. The more the ripple on the LPF output the more unstable will be the VCO. Therefore, we need to determine optimum LPF component parameter to meet both the criteria, i.e. low ripple on the V control and also close to DC level to stability purpose. We will

discuss the Charge Pump and Low Pass Filter now individually and in detail. The following diagram describes the basic block diagram of a Charge Pump.

Fig. 4.8: Charge Pump Block Diagram

In the above diagram the output pulses of PFD charges or discharges the Cp capacitor via VDD and Ground. When the UP pulse is prominent the PMOS switch connected with VDD turns on and charges the Cp. The PMOS switch has an inverter connected to its input, so that to turn it "ON" when the UP is high, as PMOS turns on for logic 0. Similarly, the NMOS switch is turned "ON" when DN signal is prominent and discharges the Cp capacitor to ground. There are many non-idealities of conventional CP [40], such as current mismatch, charge share and charge injection, etc. Charge pump current mismatch due to finite output resistance of the MOS current sources is addressed in [41]. Any mismatch between the charging and discharging current can cause steady-state offset as well as dynamic jitter, known as reference spur in a PLL. Glitches [40] in the output current will increase the level of reference spurs in a PLL. It will also increase the level of jitter generation in clock and data recovery systems.

Various circuit techniques to reduce current mismatch have been reported in the literature [42]. A wide dynamic range of the charge pump is desired for the wide

Fig. 4.9: Proposed Charge Pump Circuit (CP-1)

operating range of the PLL. To reduce the overall mismatch and the output current glitches significantly, different charge pump has been reported in [43].