## DEVELOPMENT OF A LOW COST 16-BIT MICROPROCESSOR TRAINER

BY GOLAM MOSTAFA

SUPERVISED BY DR. CHOWDHURY MOFIZUR RAHMAN

#92772#

A THESIS

SUBMITTED TO THE DEPARTMENT OF COMPUTER SCIENCE AND ENGINEERING IN PARTIAL FULFILLMENT OF THE REQUIREMENTS FOR THE DEGREE OF MASTER OF SCIENCE IN ENGINEERING (COMPUTER SCIENCE AND ENGINEERING)

### DEPARTMENT OF COMPUTER SCIENCE AND ENGINEERING BANGLADESH UNIVERSITY OF ENGINEERING AND TECHNOLOGY DHAKA, BNAGLADESH OCTOBER, 1998

## DEVELOPMENT OF A LOW COST 16-BIT MICROPROCESSOR TRAINER

A thesis submitted by

**GOLAM MOSTAFA**

Roll No: 901807P, Session 1988-89, Registration No: 72343, to the Department of Computer Science and Engineering in Partial Fulfillment of the Requirements for the Degree of Master of Science in Engineering (Computer Science & Engineering). Examination held on : 4/10/98

Approved as to the style and content by :-

10/98

(DR. CHOWDHURY MOFIZUR RAHMAN) Asst. Professor, CSE Department, BUET

MARIAND 10198

(PROF. Dr. M. KAYKOBAD) Head, CSE Department, BUET

-YEJYR

(MD: ABDUS SATTAR) Asst. Professor, CSE Department, BUET

(PROF. DR. MD. SAIFUR RAHMAN) EEE Department, BUET

Chairman and Supervisor

Member

#### Member

·

#### Member (External)

## DECLARATION

- 10

This is to declare that the work presented in this thesis is the result of my extensive study and experiments on 'The Development of a Low Cost 16-Bit Microprocessor Trainer' under the supervision of Dr Chowdhury Mofizur Rahman of the Department of Computer Science and Engineering of the Bangladesh University of Engineering and Technology, Dhaka. It is further declared that neither this thesis nor any part thereof has been submitted elsewhere for the award of any degree or diploma.

Signature of the Author

## ACKNOWLEDGMENT

The author wishes to make due acknowledgments to the following organizations and persons for their generous support, participation and encouragement for the successful realization of a working 8086-based trainer.

To the Department of Computer Science and Engineering of the Bangladesh University of Engineering and Technology for its support in conducting higher studies in the field of computer science and technology. This favorable atmosphere has led to the materialization of an 8086-based trainer.

To Dr. Syed Mahbubur Rahman, ex-Head of the Department of Computer Science and Engineering of BUET, for his keen interest in this project. In fact, the project was initiated during his time.

To Dr. M. Kaykobad, Professor and Head, Department of Computer Science and Engineering, BUET for his active effort in finding a professor to supervise the project works.

To Dr. Mohammed Ali Chowdhury, Professor, Department of Electrical and Electronic Engineering, BUET, for his continuous encouragement.

To Dr. Chowdhury Mofizur Rahman, Assistant Professor, Department of Computer Science and Engineering, BUET - who is the supervisor of the present work. Special thanks and regards are due to him for his pleasant personality and technical expertise that has supplied most of the fuel necessary for successful completion of the present work.

To Mr. Abdus Satter, Assistant Professor, Department of Computer Science and Engineering, BUET, for his dedication in sparing time to discuss many microprocessor related issues.

To the staff of the department of CSE, DAERS and ADMIN. of BUET who helped me in many ways.

To Engr. Akbar-e-Sarwar, Director of Design Group Limited, Dhaka for his untiring efforts for making the double-layer PCB for the trainer. Without this PCB, the trainer would never be transformed from the engineering prototype to the professional version.

To members of the family, friends and others who shared directly or indirectly the sorrow and happiness that the author was experiencing during the development phase of the trainer.

Golam Mostafa October, 1998

dedicated to..... Late Moni Singh

-. .

v

.

#### Abstract

This thesis contains the technical details of the design, development and construction of an 8086-based 16-bit microprocessor trainer. The trainer has been built using local technology and at lesser cost compared to the foreign made trainers. The hardware and software design are simple and logical to allow others become acquainted with the design rules. The trainer has been built with the features of a 'Learning and Development System.' The features are (a) edge connectors for developing interfacing circuits, (b) integrated peripheral module containing all the common peripheral controllers (c) the IBM-PC to trainer down loading software and (e) many useful routines and subroutines in the EPROMs.

The trainer has been constructed successfully. All the objectives quoted above have also been achieved.

The trainer has the following hardware features : (a) 8086 CPU, (b) 64Kbytes EPROM, (c) 64 Kbytes RAM, (d) Bus Lines at Edge Connectors for Interfacing Experiments, (e) 5.5''x2.5'' Bread Board for Prototyping Circuits, (f) Well-documented User's Manual, (g) 18-Key Hex-key pad for Machine Codes Programming, (h) 9 - Digits 7-Segment Display Window, (i) Memory and Port Decoded Lines Available at Edge Connectors, (j) +5V Power Supply Adapter.

The trainer has also software features like (a) Powerful and Comprehensive Resident Monitor Program, (b) Auto/Manual Data Entry for both Bytes/Word Operations, (c) Program Execution Capability, (d) Forward/Backward/Change/Backspace Facilities, (e) Bytes/Word Examine/Edit Capability, (f) Single Instruction Execution Capability for Program Debugging, (g) Basic Initialization Routines for Many Peripheral ICs like ADC, DAC,8251,8259, (h) Register's Contents can be Examined and Changed, (i) Flag Register's Contents can be Examined in Bit-form and Hex-form, (j) Many Stand-Ione Useful Routines and Subroutines to facilitate microprocessor based system design.

This thesis contains detailed description of the procedures and techniques employed for the design, development and construction of the trainer. It is a comprehensive reference containing experimented steps that the designers and academicians may consult to solve microprocessor related problems. This thesis has also documented the description of the new ideas conceived to solve varieties of hardware and software problems. The examples are -- the design of composite memory/port decoder and single stepping routine.

The thesis contains 10 chapters, 6 appendices and a reference caption. Attempt has been made to document the work in the form of descriptive language, schematic diagram, flow chart, assembly and C codes.

돣

## CONTENTS

| List | of Figure | 25                | ••      | ••          | ••       | ••         | ••     |       | ••            | x  |

|------|-----------|-------------------|---------|-------------|----------|------------|--------|-------|---------------|----|

|      |           |                   |         |             |          |            |        |       |               |    |

| 1    | INTRO     | ODUCTION          |         |             |          |            |        |       |               | 1  |

| 2    | 8086 N    | <b>IICROPROCE</b> | ssoi    | R FUNDA     | MENT     | TALS       |        |       |               |    |

|      | 2.1       | Pin Diagram a     | nd Fu   | nctions     |          |            |        |       |               | 5  |

|      | 2.2       | Internal Archit   | ecture  | e           |          |            |        |       |               | 14 |

|      | 2.3       | Instructions      |         |             |          |            |        |       |               | 17 |

| 3    | OPER      | ATING PROC        | EDUI    | RES         |          |            |        |       |               |    |

|      | 3.1       | Trainer Board     | Layou   | it .        |          |            |        |       |               | 21 |

|      | 3.2       | Components D      | escrip  | otion       |          |            |        |       | <del></del> - | 22 |

|      | 3.3       | Signal Signatu    | res     |             |          |            |        |       |               | 23 |

|      | 3.4       | Keyboard Mne      | monie   | s and Me    | aning    |            |        |       |               | 25 |

|      | 3.5       | Program Code:     |         |             | -        |            |        |       |               | 27 |

|      | 3.6       | Program Execu     | ition   | -           |          |            |        |       |               | 28 |

|      | 3.7       | Program Debu      | gging/  | Register (  | Check    |            |        |       |               | 28 |

|      | 3.8       | Example Progr     | ams     |             |          |            |        |       |               | 30 |

| 4    | HARD      | WARE DESIG        | N       |             |          |            |        |       |               |    |

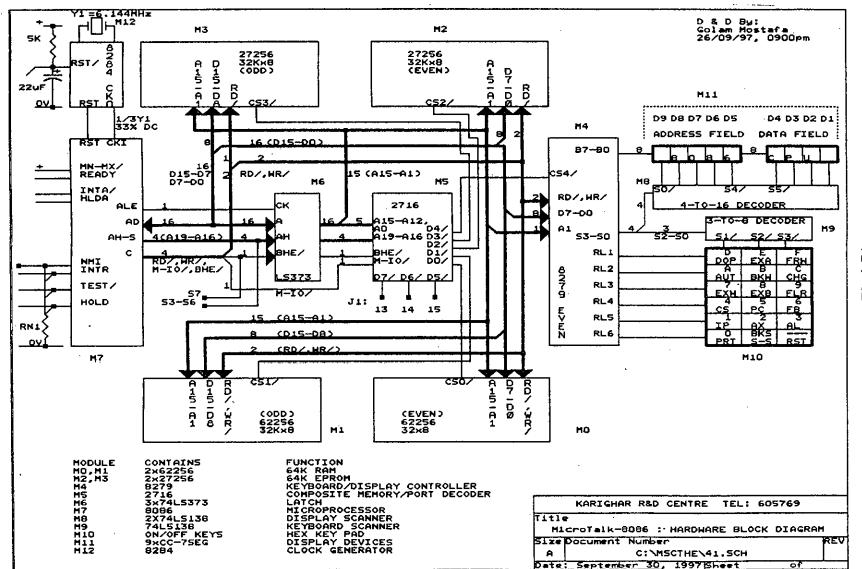

|      | 4.1       | Block Diagram     | L       |             |          |            |        |       |               | 32 |

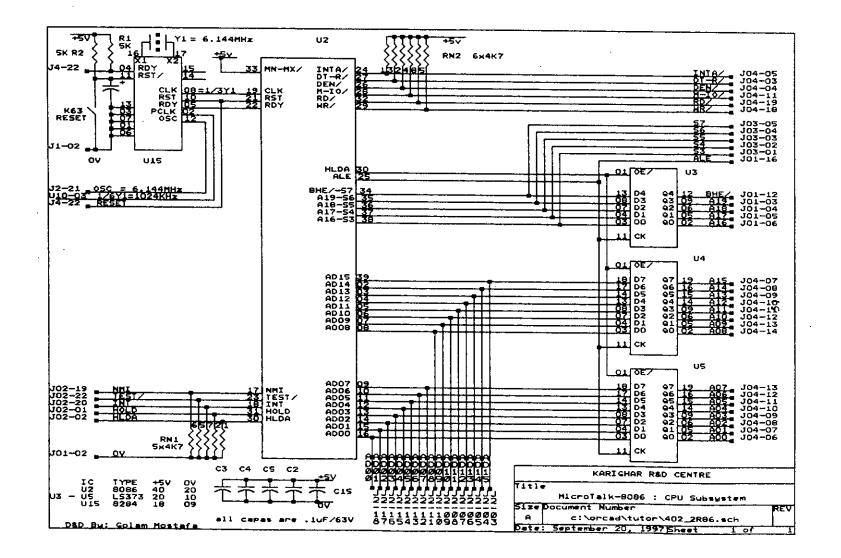

|      | 4.2       | CPU Subsyster     | n       |             |          |            |        |       |               | 34 |

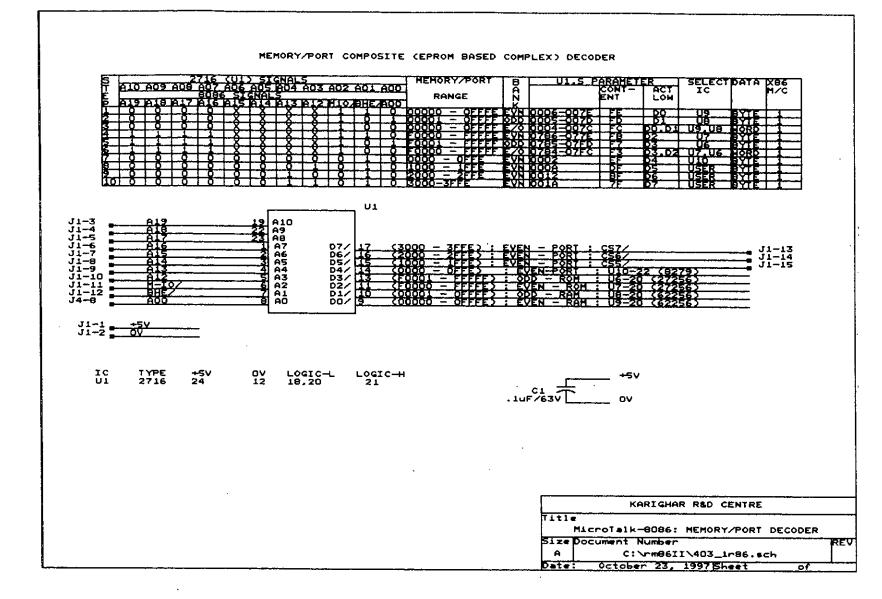

|      | 4.3       | Memory/Port I     | Decod   | ing Subsys  | stem     |            |        |       |               | 36 |

|      | 4.4       | Memory Subsy      |         | '           |          |            |        |       |               | 38 |

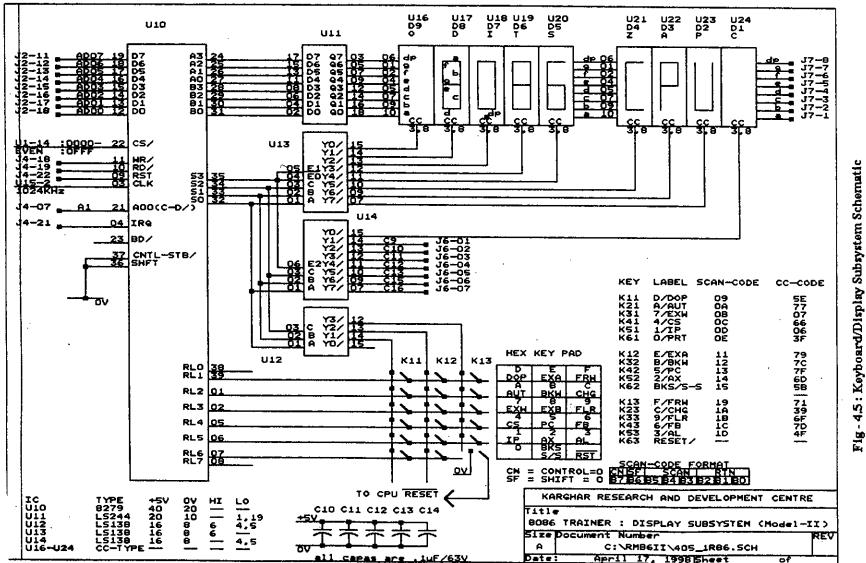

|      | 4.5       | Keyboard/Disp     | lay Su  | ıbsystem    |          |            |        |       |               | 40 |

| 5    | MONI      | TOR PROGRA        | M D     | ESIGN       |          |            |        |       | -             |    |

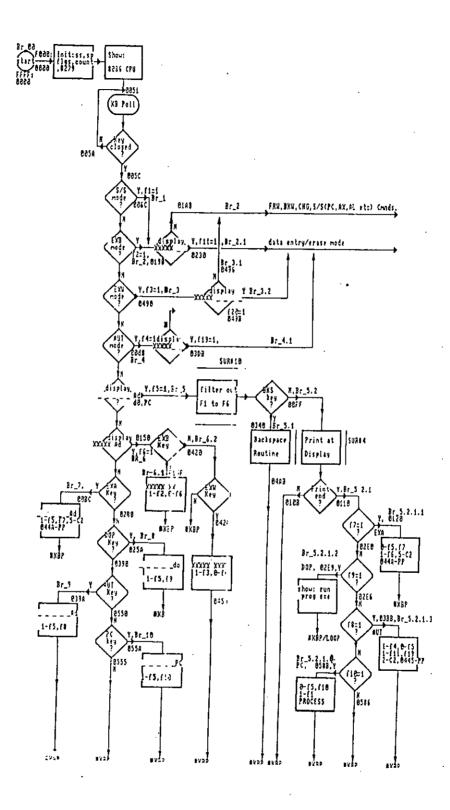

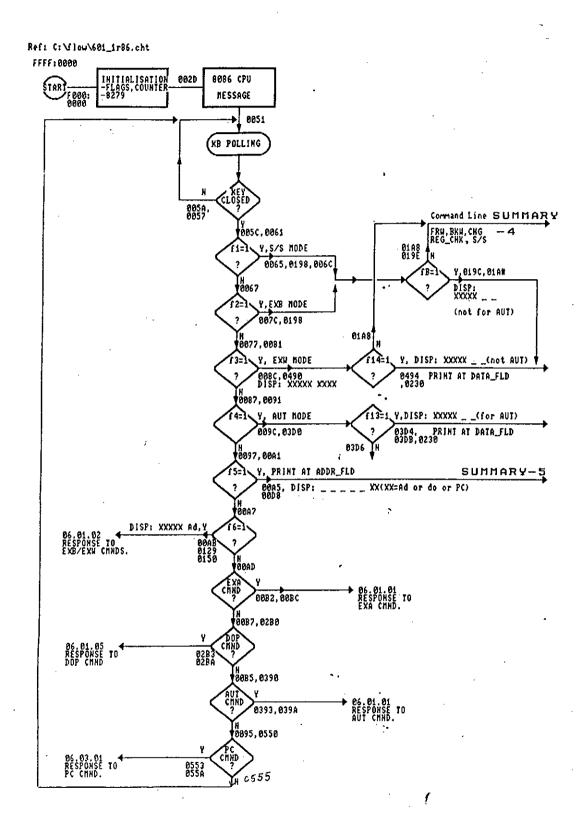

|      | 5.1       | What is a Moni    | tor Pr  | ogram?      |          |            |        |       |               | 42 |

|      | 5.2       | Implementing I    |         |             | V. AUT   | E. BKS at  | nd DOP | Comm  | ands          | .2 |

|      |           | 5.2.1 Respon      | d/Actio | on for EXA  | Ćomm     | and        |        |       |               | 52 |

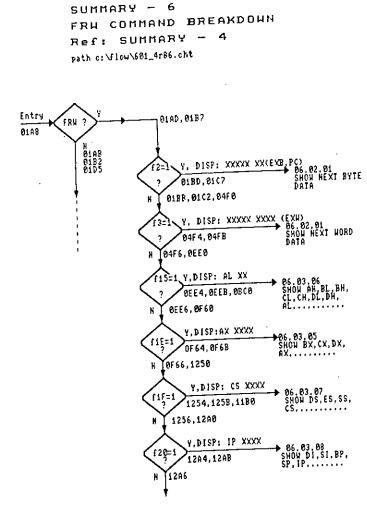

|      |           |                   |         | on to EXB/i |          |            |        |       |               | 53 |

|      |           |                   |         | on to AUT   | Comma    | nd         |        |       |               | 54 |

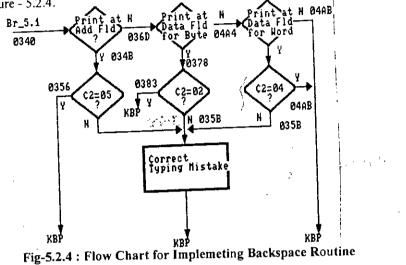

|      |           | 5.2.4 Backspa     |         |             |          |            |        |       |               | 55 |

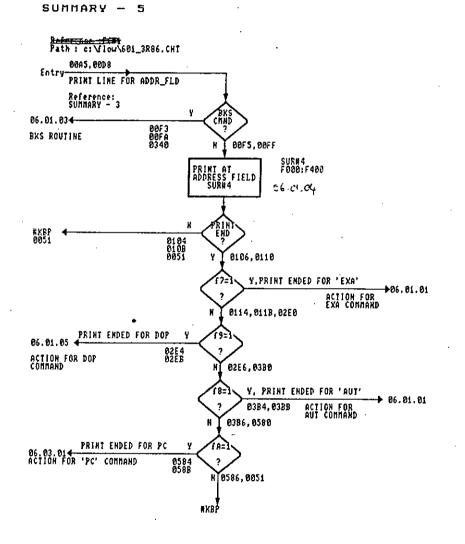

|      |           |                   |         | play Windo  |          |            |        |       |               | 56 |

|      | 6.2       |                   |         | on to DOP ( |          |            |        | tion) |               | 57 |

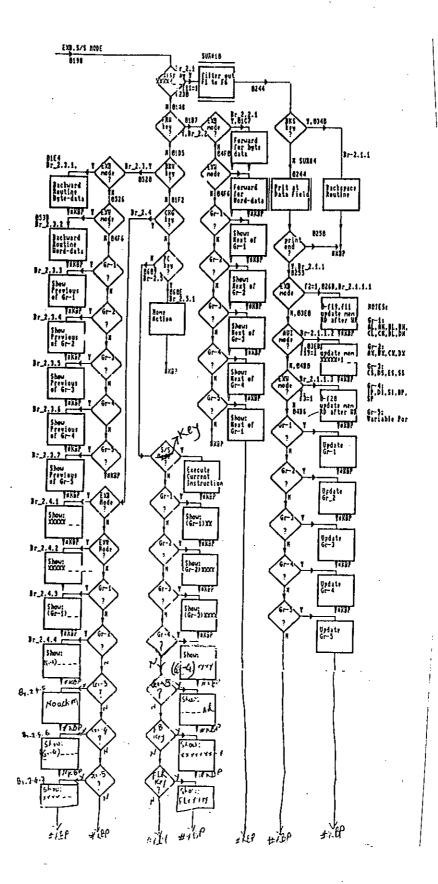

|      | 5.3       | Implementing I    |         |             | non) ت   | S/S) Con   | nmands |       |               | 58 |

|      |           | 5.3.1 Forward     |         |             |          |            |        |       |               | 59 |

|      |           | 5.3.2 Backwa      |         |             |          |            |        |       |               | 60 |

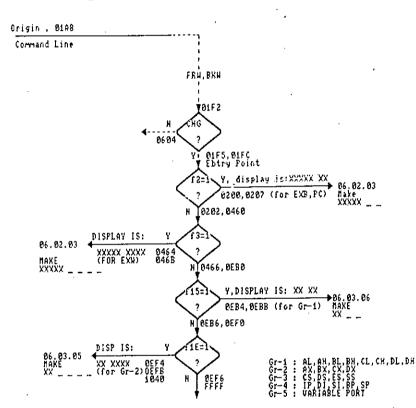

|      |           |                   |         | nd and Byte |          |            |        |       |               | 61 |

|      |           | J.J.4 UHUU        | лппаг   | nd and Wor  | u-data l | update for | Memory | /     |               | 62 |

÷,

|   | 5.4   | Theory of Single Stepping (Program Debugging Routine)                                                                   |     |     |

|---|-------|-------------------------------------------------------------------------------------------------------------------------|-----|-----|

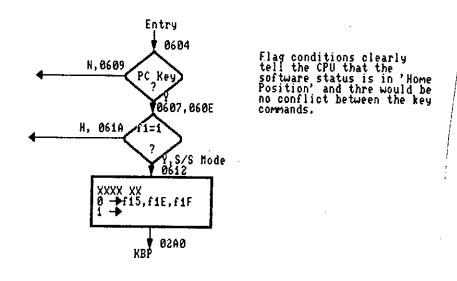

|   |       | 5.4.1 Respond/Action to PC Command                                                                                      |     | 63  |

|   |       | 5.4.2 Home Key Routine (PC command in S/S Mode)                                                                         |     | 64  |

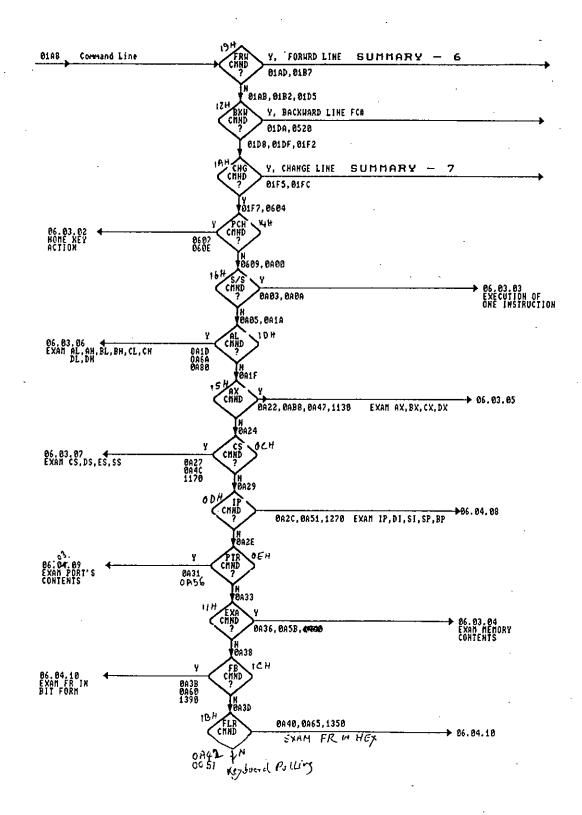

|   |       | 5.4.3 Execution of One Instruction (Single Stepping)                                                                    |     | 65  |

|   |       | 5.4.4 Exam/Edit AX, BX, CX, DX Registers                                                                                |     | 70  |

| • |       | 5.4.5 Exam/Edit Al, AH, BL, BH, CL, CH, DL, DH Registers                                                                |     | 71  |

|   |       | 5.4.6 Exam/Edit IP,SI,DI,SP,BP Registers                                                                                |     | 72  |

|   |       | 5.4.7 Exam/Edit CS,DS,SS,ES Registers                                                                                   |     | 73  |

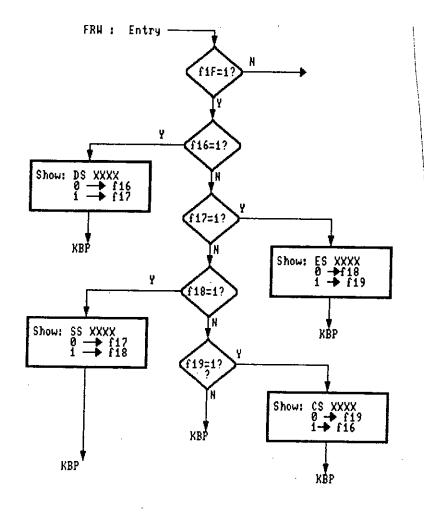

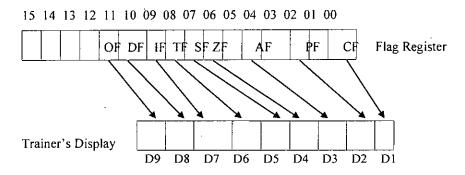

|   |       | 5.4.8 Exam/Edit Flag Register                                                                                           |     | 74  |

|   |       | 5.4.9 Exam/Edit Memory Contents (Memory as a simple Register                                                            | )   | 75  |

|   |       | 5.4.10 Exam/Edit Port Contents                                                                                          |     | 76  |

|   | 5.5   | Subroutines                                                                                                             |     | 77  |

|   | 5.6   | Stand-alone Routines                                                                                                    |     | 83  |

|   | 5.7   | Data Tables                                                                                                             |     | 86  |

|   | 5.8   | Interrupt Vector Table                                                                                                  | ••• | 88  |

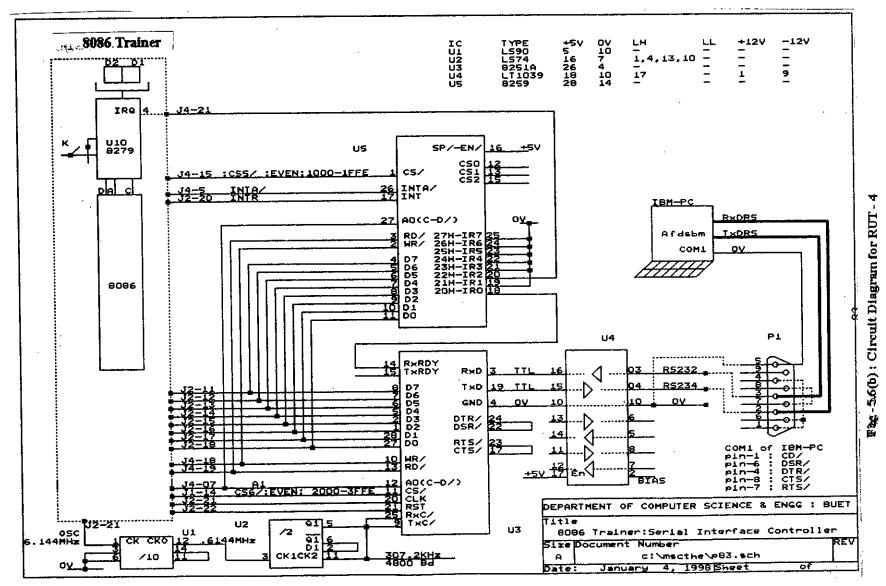

|   | 5.9   | Memory Space Map                                                                                                        |     | 90  |

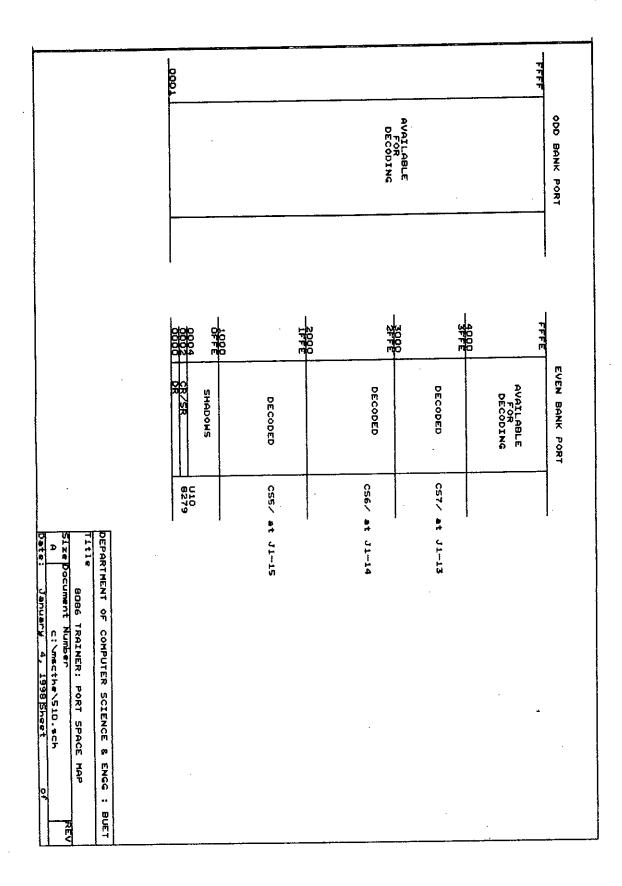

|   | 5.10  | Port Space Map                                                                                                          |     | 92  |

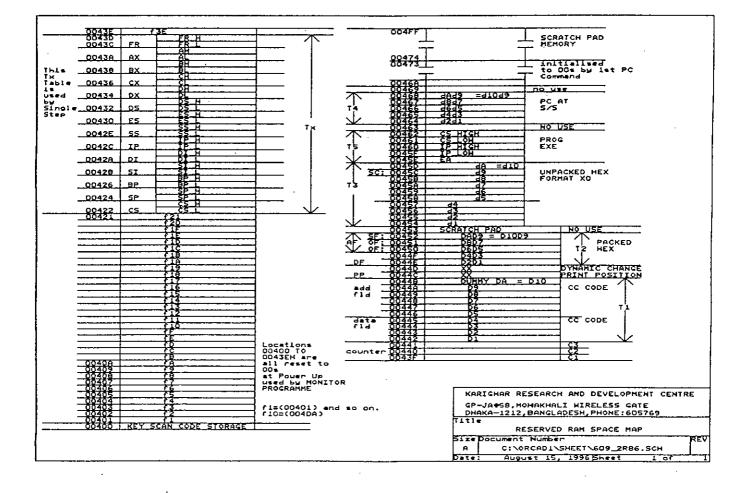

|   | 5.11  | Reserved RAM Space Map                                                                                                  |     | 94  |

| _ |       |                                                                                                                         |     |     |

| 6 |       | EGRATED PERIPHERAL MODULE                                                                                               |     |     |

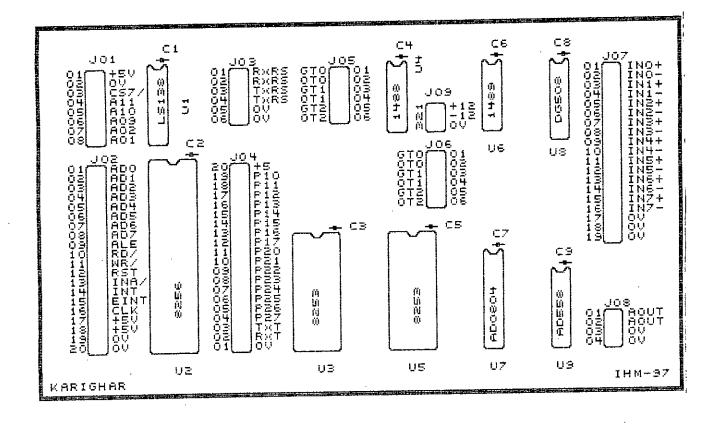

|   | 6.1   | Introduction and Board Components Layout                                                                                |     | 96  |

|   | 6.2   | Components Description                                                                                                  |     | 97  |

|   | 6.3   | Signal Signatures                                                                                                       |     | 98  |

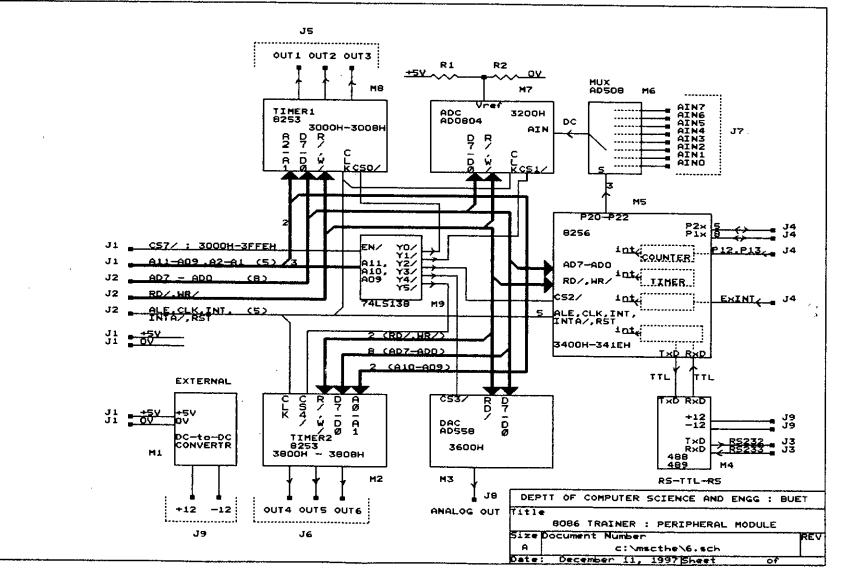

|   | 6.4   | Block Diagram                                                                                                           |     | 100 |

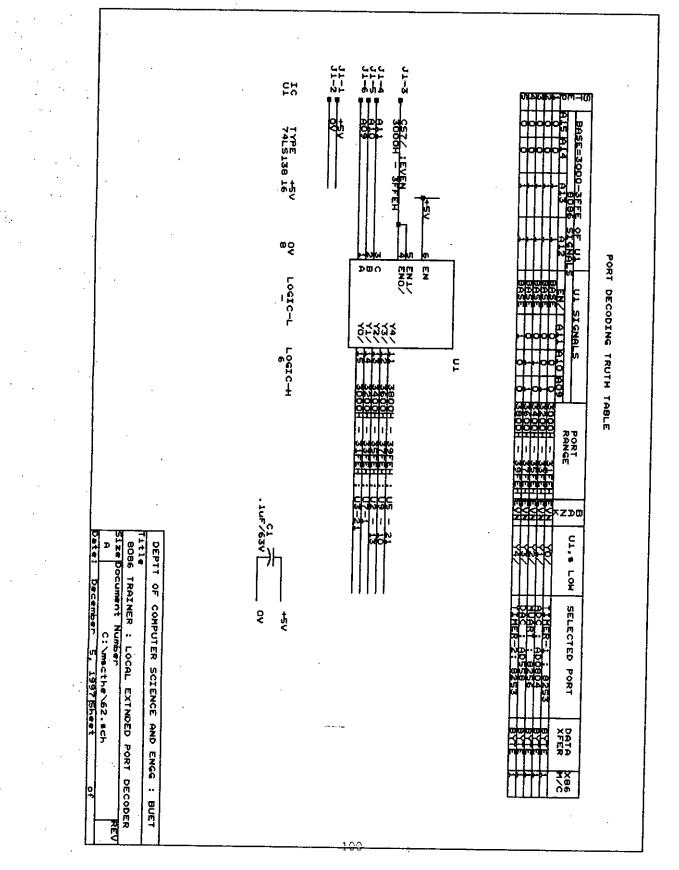

|   | 6.5   | Local Extended Port Decoder                                                                                             |     | 102 |

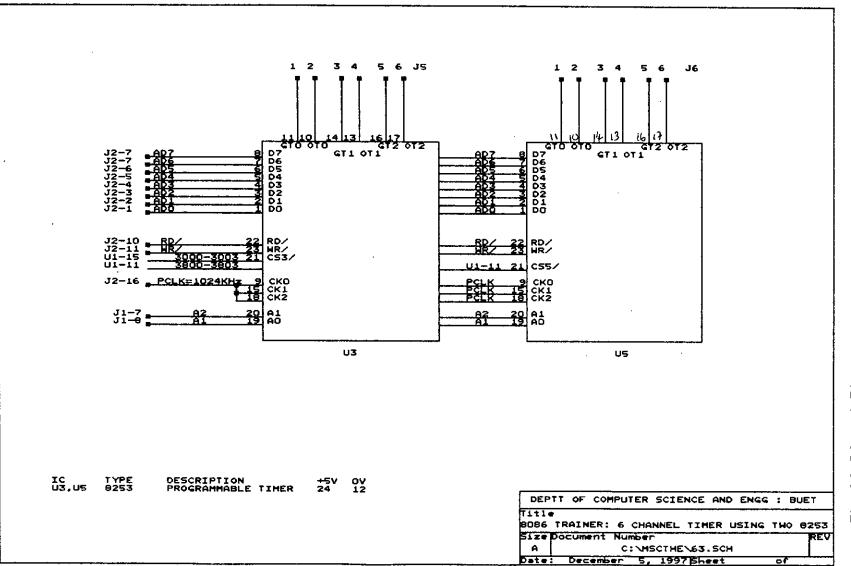

|   | 6.6   | 6 Channel Programmable Interval Timer using two 8253s                                                                   |     | 104 |

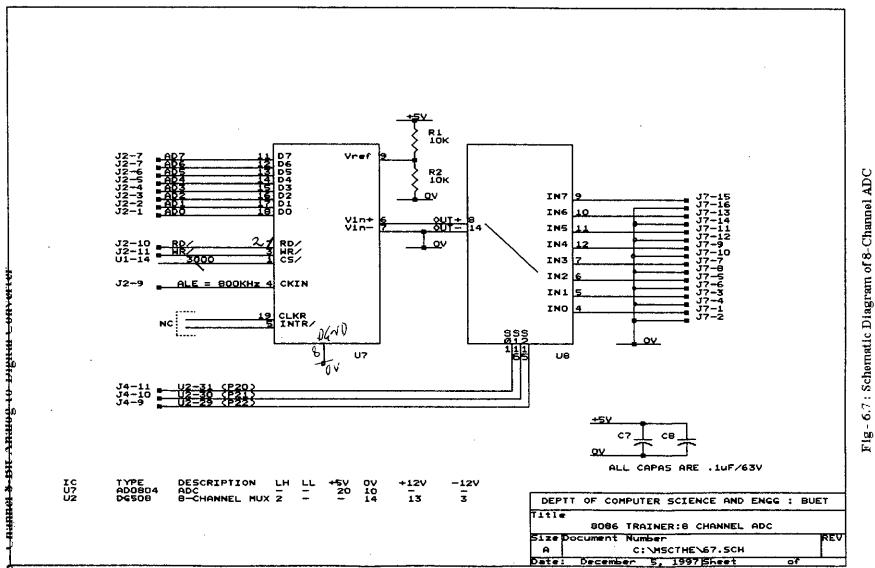

|   | 6.7   | 8 Channel 8-Bit ADC using AD0804 + Multiplexer DG508                                                                    |     | 106 |

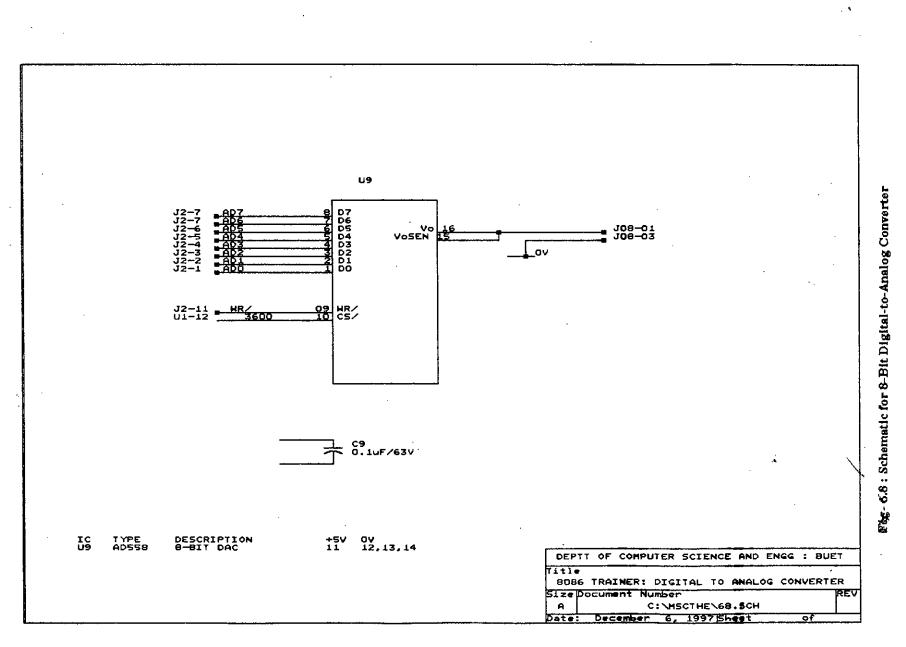

|   | 6.8   | 8-Bit Digital-to-Analog Converter using AD558                                                                           |     | 108 |

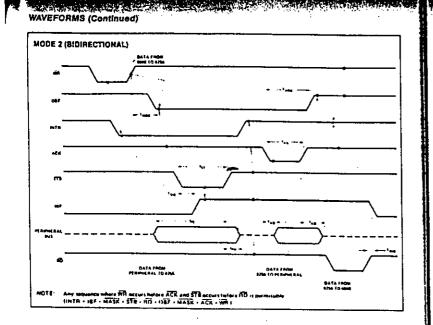

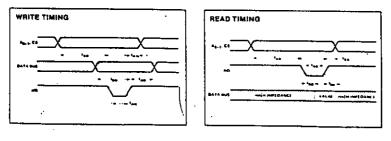

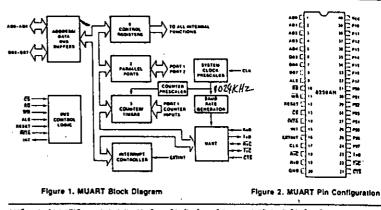

|   | 6.9   | Multifunction Asynchronous Receiver/Transmitter using 8256                                                              |     |     |

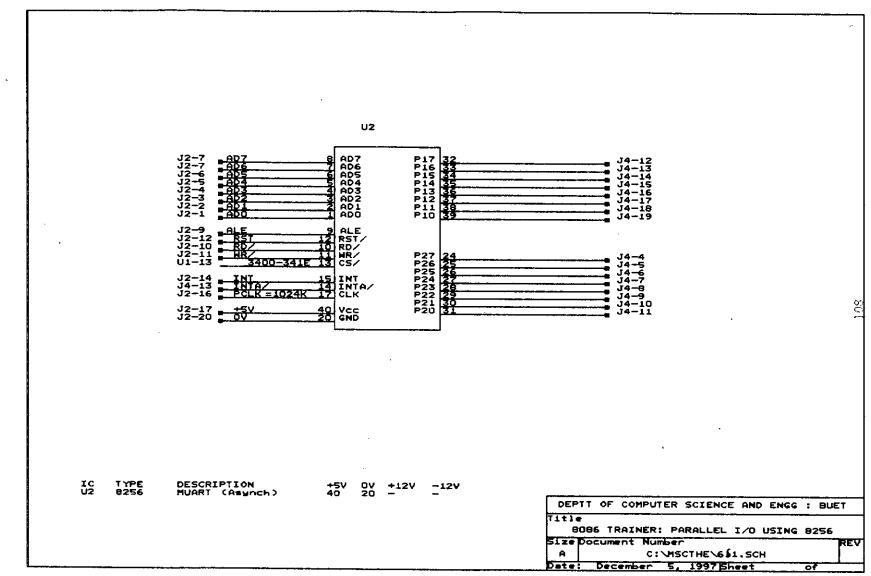

|   |       | 6.9.1 Parallel I/O using 8256                                                                                           |     | 110 |

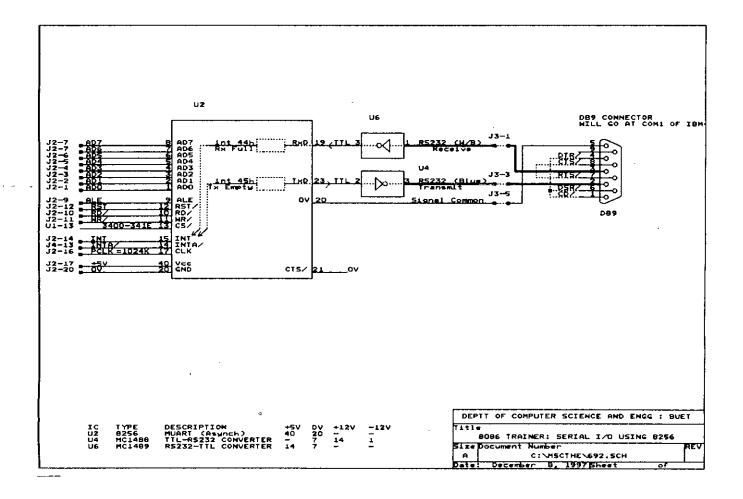

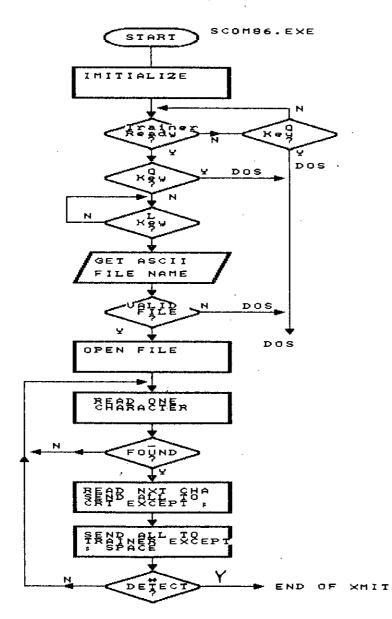

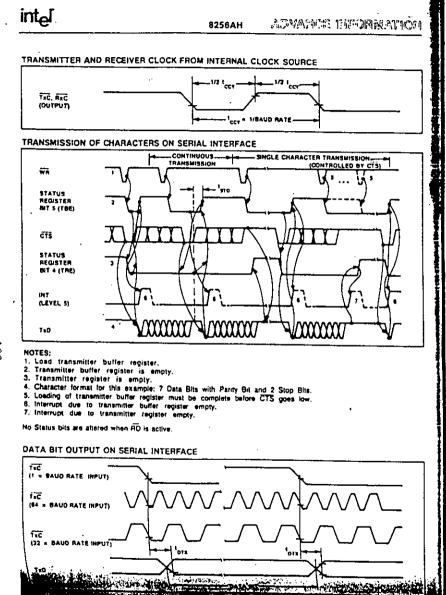

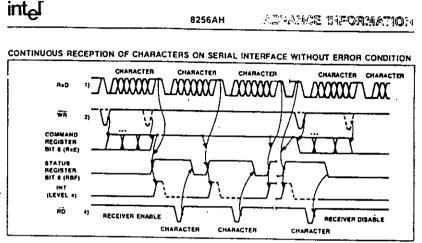

|   |       | 6.9.2 Serial I/O using 8256                                                                                             |     | 112 |

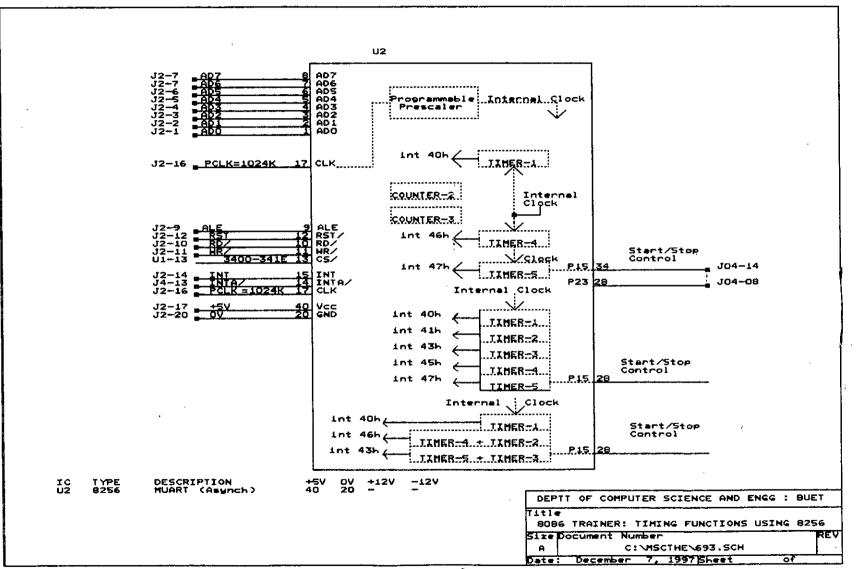

|   |       | 6.9.3 Timing Functions using 8256                                                                                       |     | 114 |

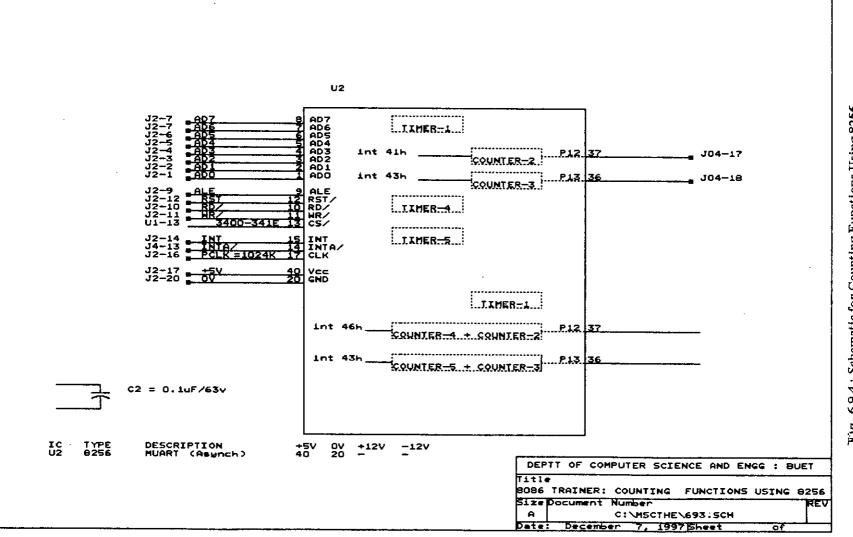

|   |       | 6.9.4 Counting Functions using 8256                                                                                     |     | 116 |

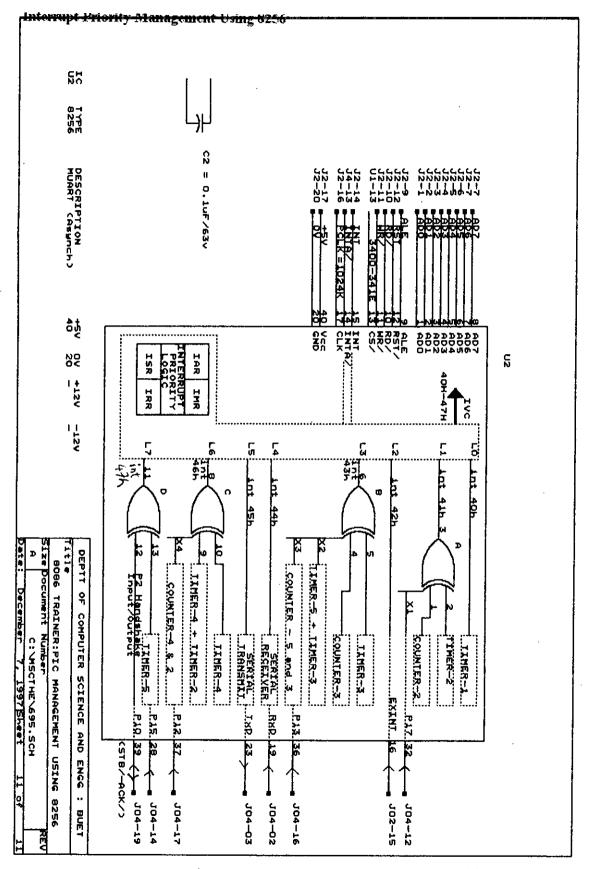

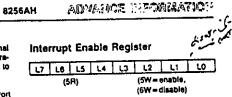

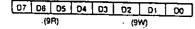

|   |       | 6.9.5 Interrupt Priority Management using 8256                                                                          |     | 118 |

| ~ |       |                                                                                                                         |     |     |

| 7 | -     | LICATIONS                                                                                                               |     |     |

|   | 7.1   | As a Microprocessor Learning System                                                                                     |     |     |

|   |       | 7.1.1 Developing and Running Program for Hardware Project<br>7.1.2 Developing and Running Program for Software Projects |     | 120 |

|   | 7.2   | 7.1.2 Developing and Running Program for Software Projects<br>As a Microprocessor Based System Design Kit               |     | 122 |

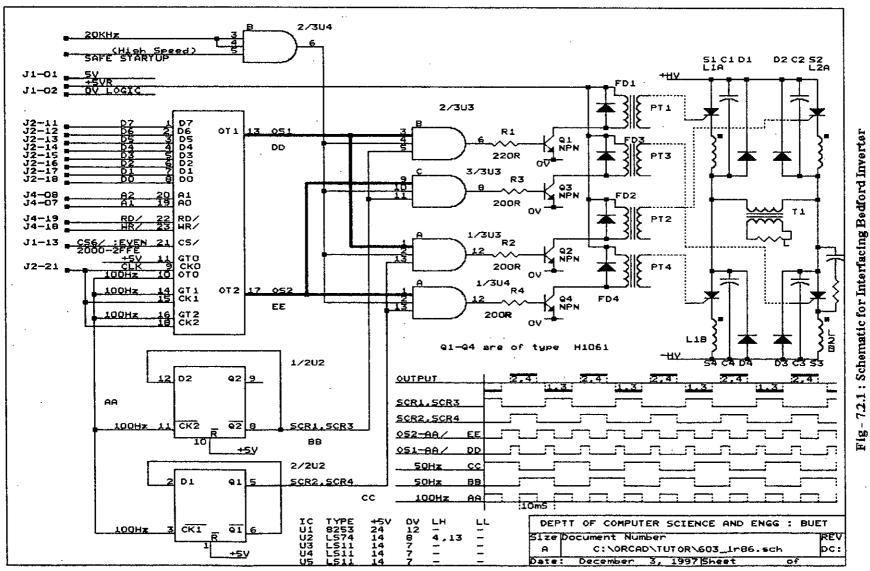

|   | 1.2   | 7.2.1 Generating Timing Functions for Firing the Bedford Inverter                                                       |     | 104 |

|   |       | 7.2.1 Overlaining runchons for Firing the Bedford Inverter<br>7.2.2 Developing an EPROM Programmer                      |     | 124 |

|   |       | 7.2.2 Developing an Er KOW Programmer                                                                                   |     | 126 |

| 8 | IBM-I | PC to TRAINER DOWN LOADING SOFTWARE                                                                                     |     |     |

| - | 8.1   | Introduction                                                                                                            |     | 141 |

|   | 8.2   | Assembly Source Code Listing for IBM-PC's EXE Prog                                                                      |     | 141 |

|   | 8.3   | C Source Code Listing for IBM-PC's EXE Prog                                                                             |     |     |

|   | 8.4   | Assembly Source Code Listing for Trainer's EXE Prog                                                                     |     | 151 |

|   | 0.7   |                                                                                                                         |     | 153 |

.

8

. م

| 9 RESULTS A  | ND DISC     | USSION         |            |               |            |          |                | 15/         |

|--------------|-------------|----------------|------------|---------------|------------|----------|----------------|-------------|

| 10 CONCLUSIO | ON AND      | FUTURE SCO     | OPE OF     | WORK          | 5          |          |                | 159         |

| APPENDIX - A | MAXIN       | IUM MODE (     | OPERAT     | ION OF        | F 8086 w   | ith 8087 | 7 FPU          |             |

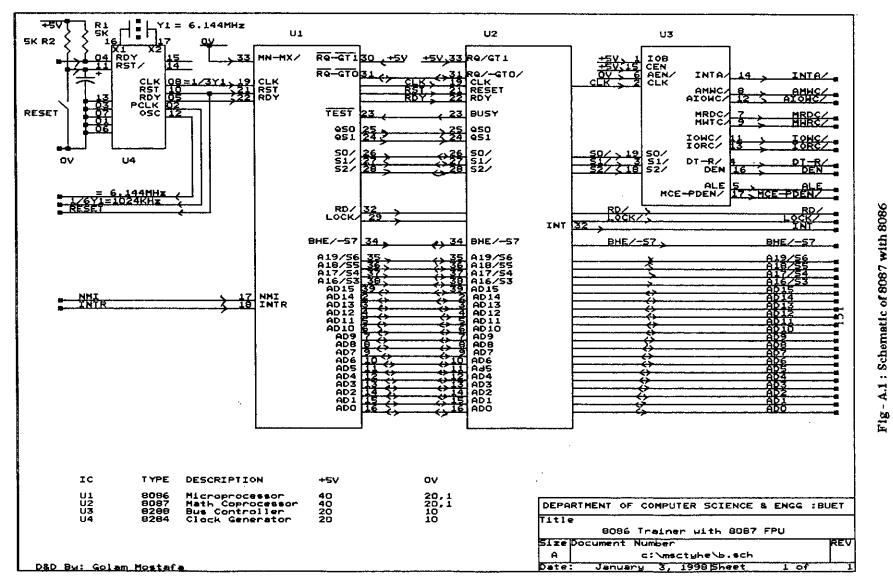

|              | A.1         | Circuit Diagra | am Descr   | iption        | <b>-</b> - |          | <del>-</del> - | <b>16</b> 1 |

|              | A.2         | Demonstratio   | n Exampl   | e             |            |          | <b>-</b> -     | 163         |

| APPENDIX - B | 8086 TR     | AINER WIT      | H BUILT    | -IN ASS       | SEMBL      | ER       |                |             |

| •            | B.1         | Introduction   |            |               |            |          |                | 164         |

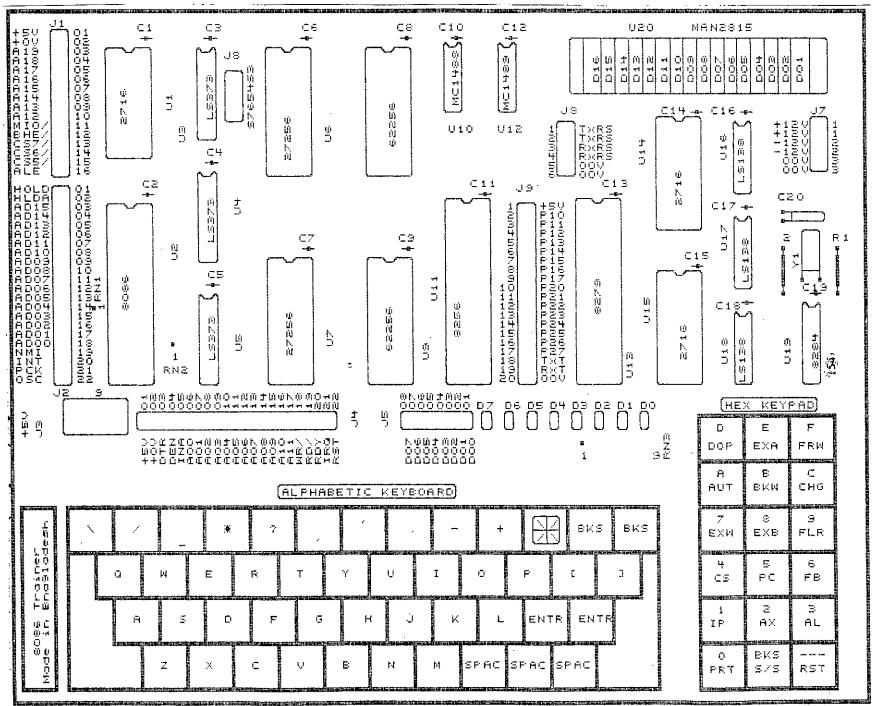

|              | B.2         | Alphanumeri    | c Display  | /Keyboa       | rd Circu   | it       |                | 166         |

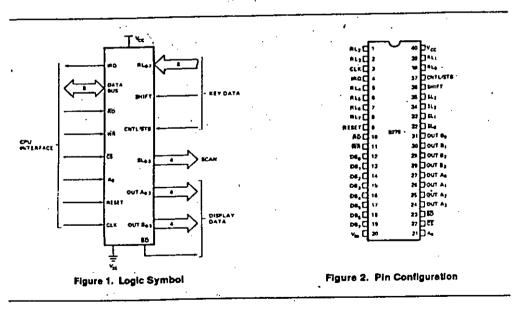

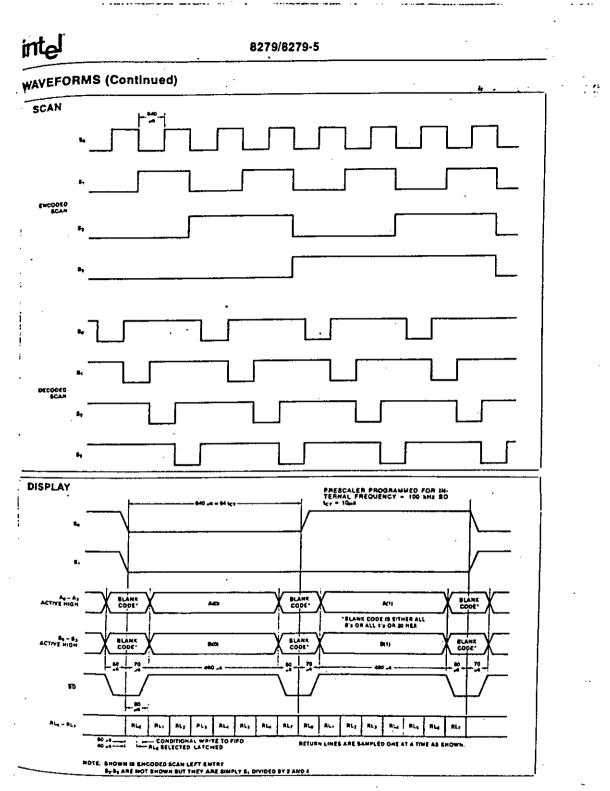

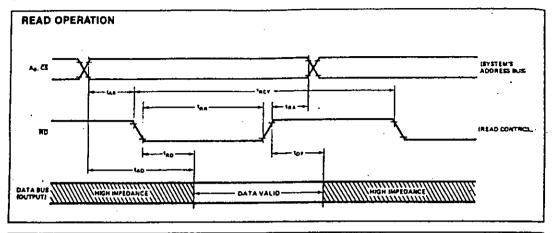

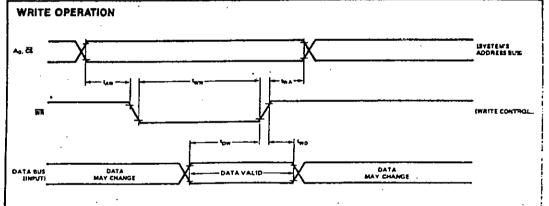

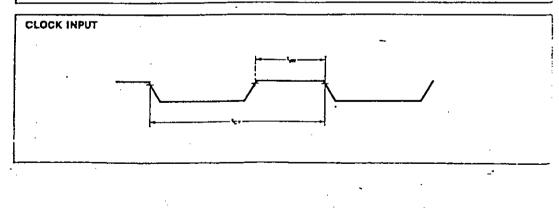

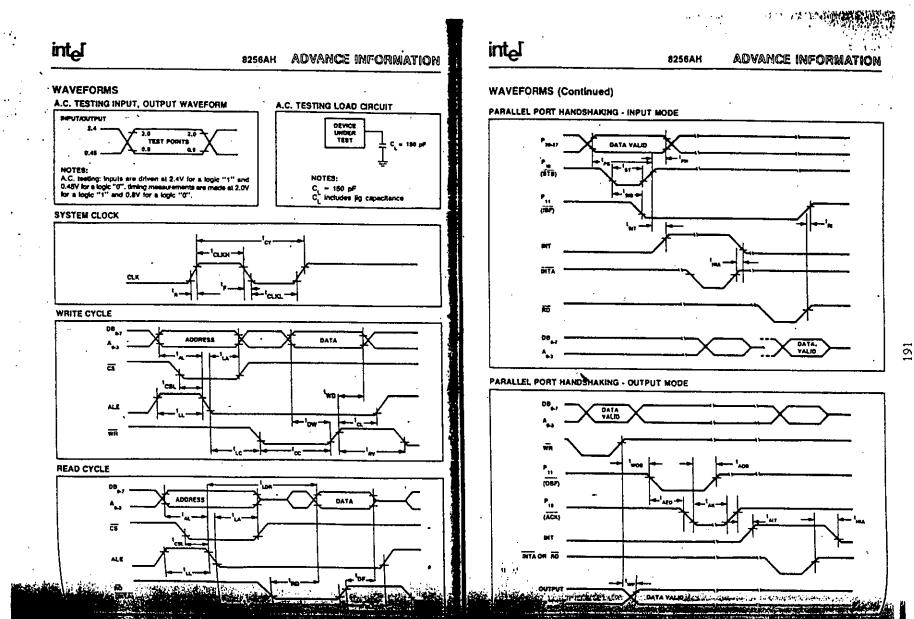

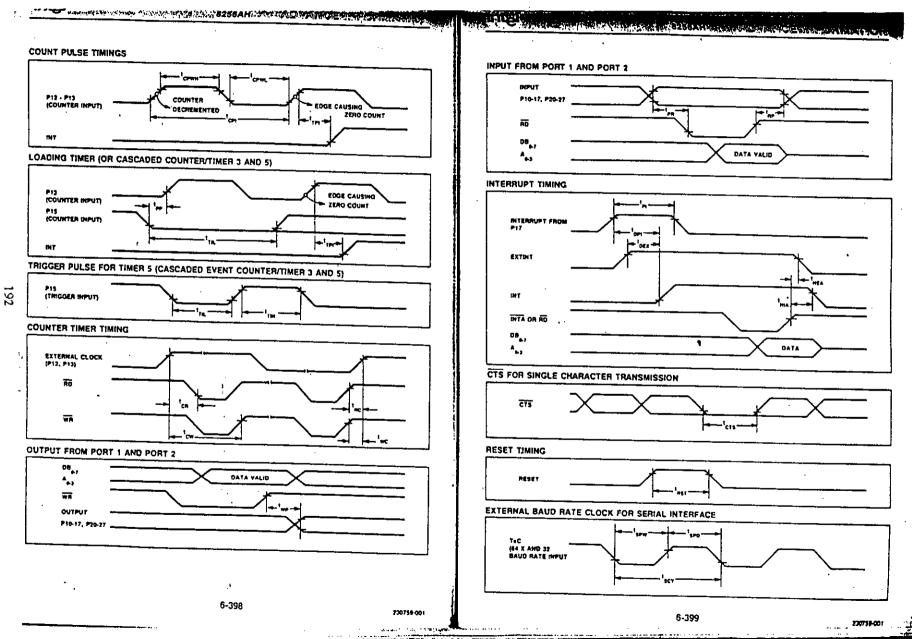

| APPENDIX - C | SELEC       | TED DATA S     | HEETS (    | (8279, 82     | 256)       |          |                | 170         |

| APPENDIX - D | HARD        | WARE DEVE      | LOPME      | NT TEC        | HNOLO      | OGY      |                |             |

|              | <b>D</b> .1 | Introduction ( | to Proced  | ure/Meth      | odology    |          |                | 194         |

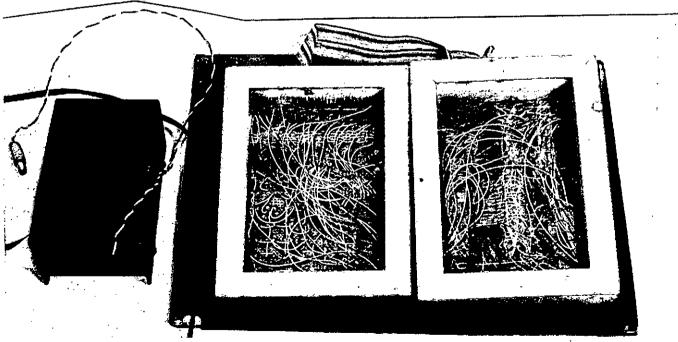

|              | D.2         | Wire-wrappir   |            |               |            |          |                | 195         |

|              | D.3         | Printed Circu  | it Board I | Manufac       | turing     |          |                | 196         |

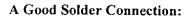

|              | D.4         | Soldering Tee  |            |               |            |          |                | 197         |

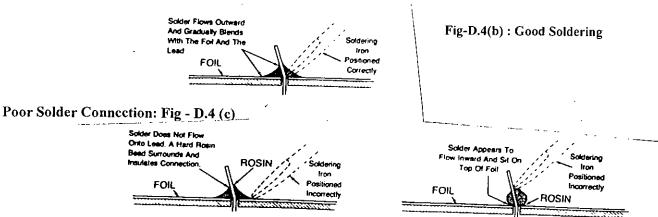

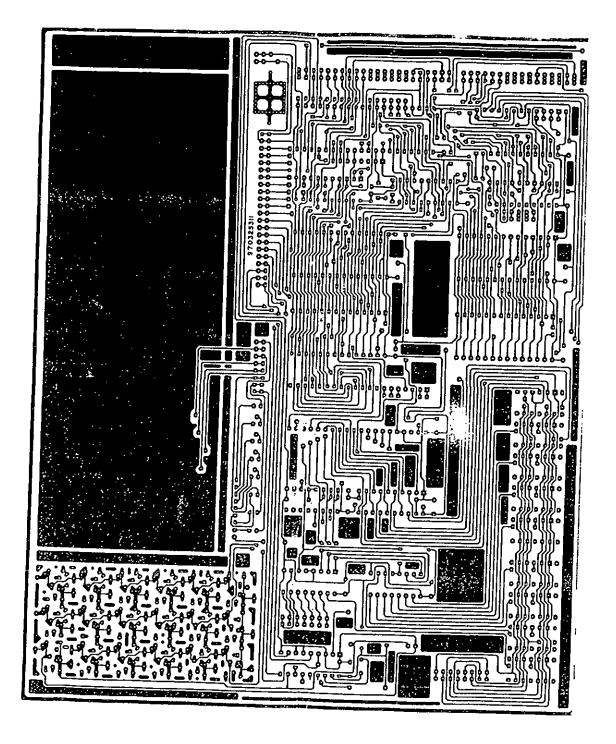

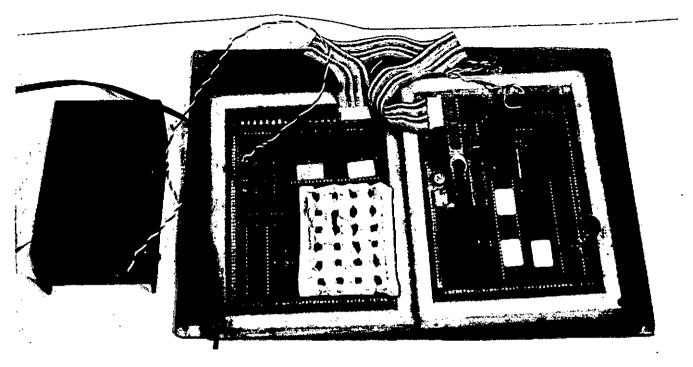

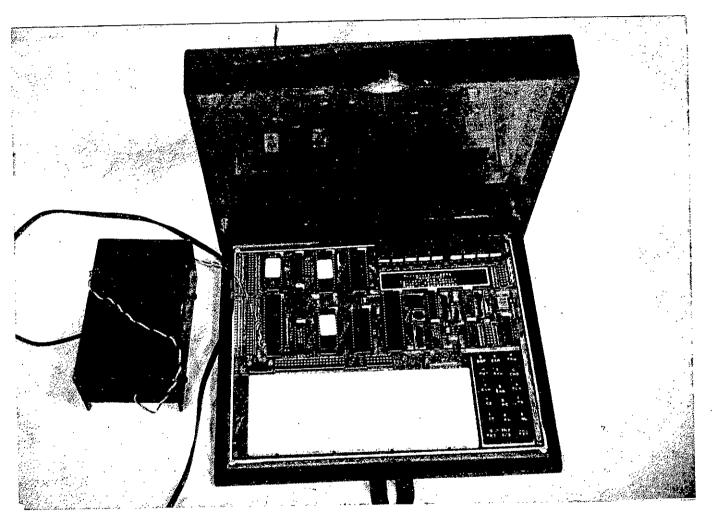

|              | D.5         | View of the 1  |            |               |            |          |                | 198         |

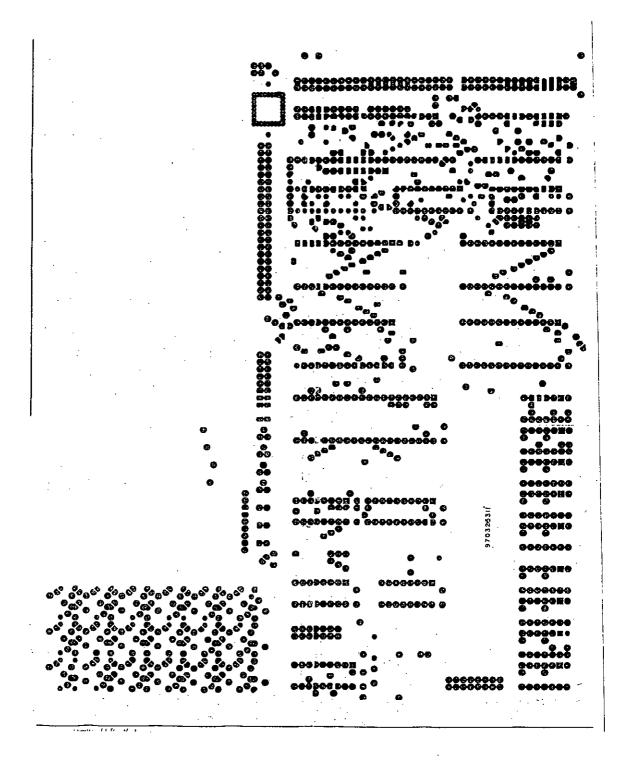

|              | D.6         | Solder side P  | CB Artwo   | ork Look      | ing from   | Bottom   | ) <del></del>  | 199         |

|              | D.7         | Component-s    | ide PCB    | Artwork       | Looking    | , from T | OP             | 200         |

|              | D.8         | Solder Mask    | (includin) | g PTH) A      | Artwork    |          |                | 201         |

| APPENDIX - E | MONIT       | OR PROGRA      | AM DEV     | ELOPM         | IENT TJ    | ECHNC    | DLOGY          | 202         |

| APPENDIX - F | COLOF       | R PLATES       |            |               |            |          |                |             |

|              | <b>F</b> .1 | Component S    |            |               |            |          |                | 206         |

|              | F.2         | Wire-wrap Si   |            |               |            |          |                | 206         |

|              | F.3         | Component S    |            |               |            |          |                | 207         |

|              | F.4         | Solder Side o  |            |               |            |          |                | 207         |

|              | F.5         | Pictorial View | w of the F | inal Cor      | nmercial   | Trainer  | ·              | 208         |

| REFERENCES   |             |                |            | 、 <del></del> |            |          |                | 209         |

ix

$\mathfrak{O}$

## List of Figures

|                   |                                                               |         | 1        |

|-------------------|---------------------------------------------------------------|---------|----------|

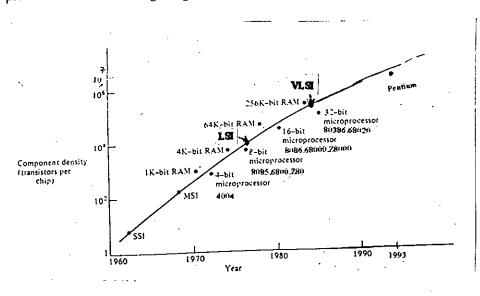

| Figure - 1        | : Growth of Maximum Achievable IC Components Density          |         | 5        |

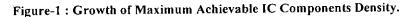

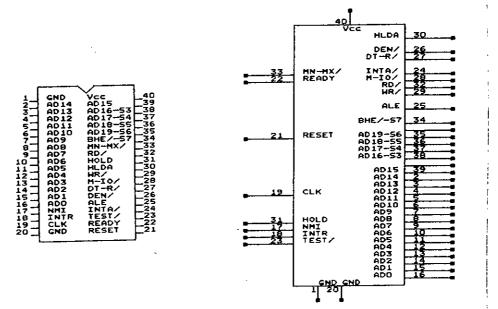

| Eigure $-21(a)$   | · Pin Assignment of the 8086 CPU (Min Mode)                   |         |          |

| Figure - $2.1(b)$ | : Bus Structured Pin Assignment of 8086 CPU (Min Mode)        | ••      | 5        |

| Figure - $2.1(c)$ | : Implementing the DEN/ and DT-R/ Signals                     | ••      | 10       |

| Figure - $2.1(d)$ | · Basic 8086 Timings in Minimum Mode                          |         | 12       |

| Figure - $2.1(e)$ | : Schematic to Allocate 1mbyte per Segment of 8086 CPU        |         | 13       |

| Figure - $2.2(a)$ | : Functional Block Diagram of 8086 CPU                        |         | 14       |

| Figure - $2.2(b)$ | : Address Computing Chart of 8086 CPU                         | ••      | 15       |

| Figure - $2.2(c)$ | : Internal Register Layout of the 8086                        |         | 16       |

| Figure - $2.3(a)$ | : Instructions Mnemonics Summary of 8086 CPU                  |         | 17       |

| •                 | : Coding Template of 8086 Instruction                         | ••      | 18       |

| Figure - $2.3(b)$ | : Coding Template of 8086 Instruction (continued)             |         | 19       |

| Figure - $2.3(c)$ | : Coding Template of 8086 Instruction (continued)             |         | 20       |

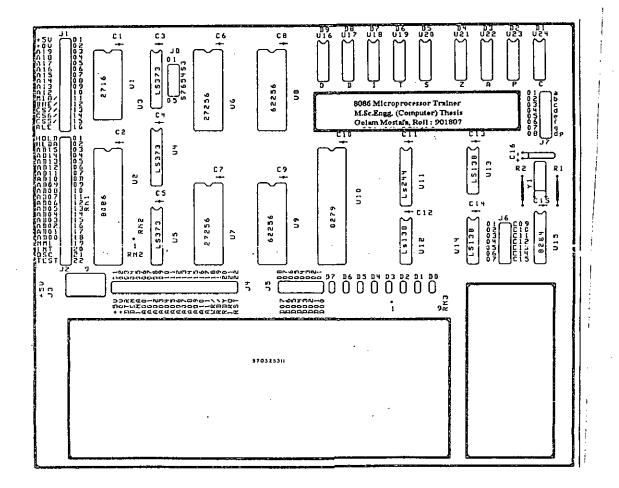

| Figure - 2.3(d)   | : The Component Layout of the 8086 Trainer                    |         | 21       |

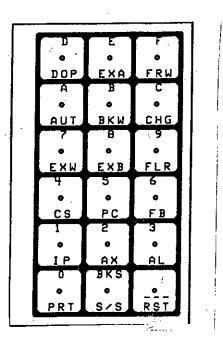

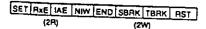

| Figure - 3.1      | Keyboard Template of the 8086 Trainer                         |         | 25       |

| Figure - 3.4      | . Keyboard Template of the occor frame                        |         | 30       |

| Figure - 3.8      | : Installing Additional 7-Segment Digit with 8086 Trainer     |         | 33       |

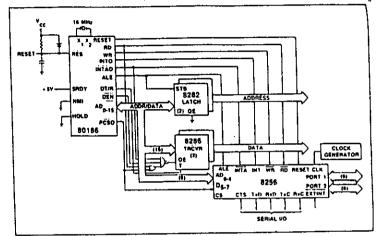

| Figure - 4.1      | : Hardware Block Diagram of 8086 Trainer                      | ••      | 35       |

| Figure - 4.2      | : CPU Subsystem Schematic Diagram                             |         | 37       |

| Figure - 4.3      | : Memory/Port Decoding Subsystem                              | ••      | 39       |

| Figure - 4.4      | : Memory Subsystem Schematic Diagram                          | ••      |          |

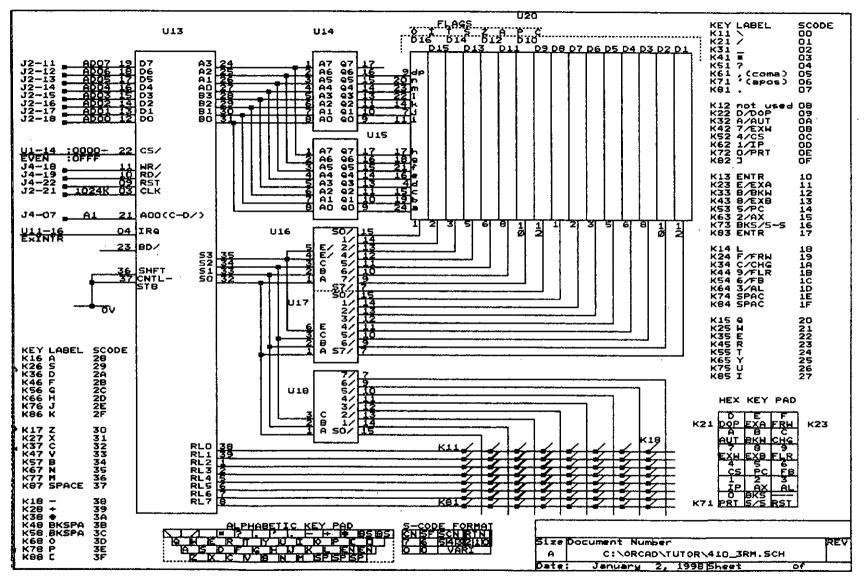

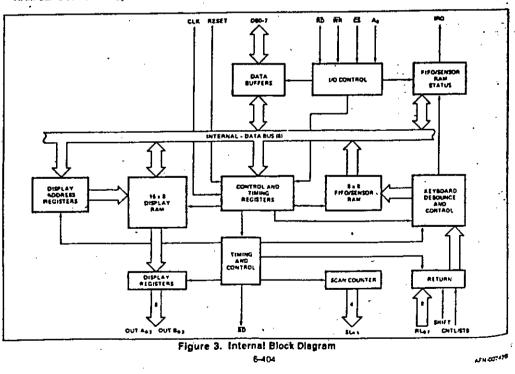

| Figure - 4.5      | : Keyboard/Display Subsystem Schematic Diagram                |         | 41       |

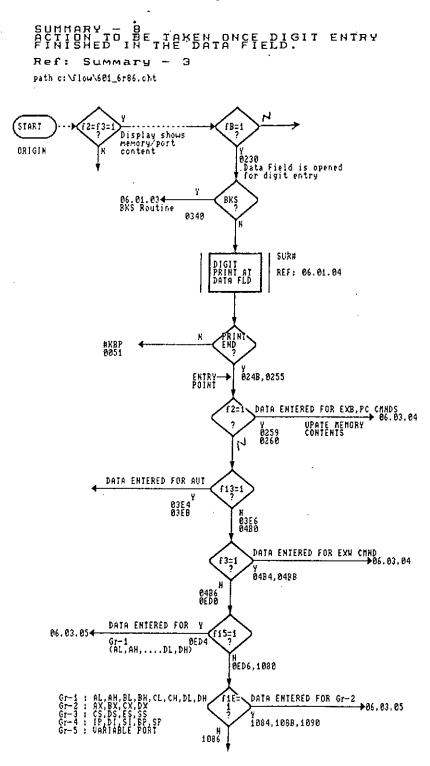

| Figure - 5.1(a)   | : Monitor Program Flow Chart Summary - 1                      |         | 44       |

| Figure - 5.1(b)   | : Monitor Program Flow Chart Summary - 2                      | ••      | 45       |

| Figure - 5.1(c)   | : Monitor Program Flow Chart Summary - 3                      |         | 46       |

| Figure - 5.1(d)   | : Monitor Program Flow Chart Summary - 4                      | ••      | 47       |

| Figure - 5.1(e)   | : Monitor Program Flow Chart Summary - 5                      | ••      | 48       |

| Figure - 5.1(f)   | : Monitor Program Flow Chart Summary - 6                      |         | 49       |

| Figure - 5.1(g)   | : Monitor Program Flow Chart Summary - 7                      |         | 50       |

| Figure - 5.1(h)   | : Monitor Program Flow Chart Summary - 8                      |         | 51       |

| Figure - 5.2.4    | : Flow Chart for Implementing Backspace Routine               |         | 55       |

| Figure - 5.2.5    | : Flow Chart to Implement Digit Printing in the Display Windo | w       | 56       |

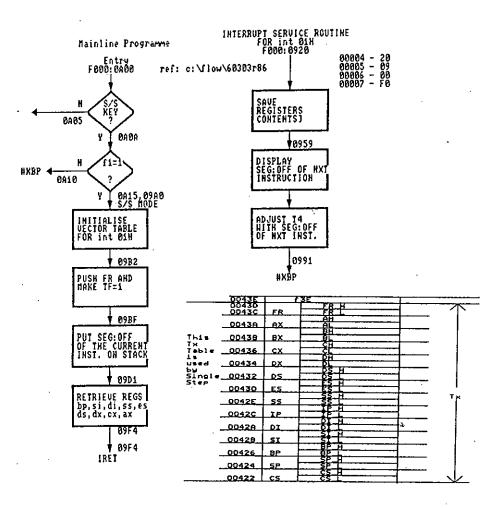

| Figure - 5.4.3    | : Flow Chart and Data Structure to Implement Single Step Rou  |         | 65       |

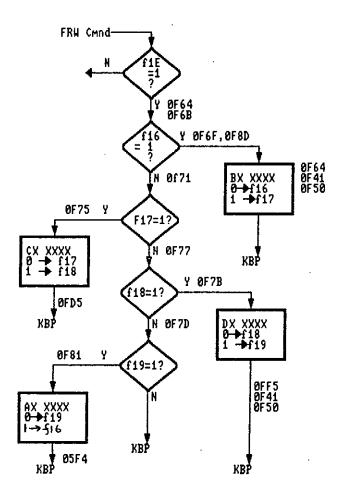

| Figure - 5.4.4    | : Flow Chart to Implement AX, BX, CX and DX Content Exam      | ination | 70       |

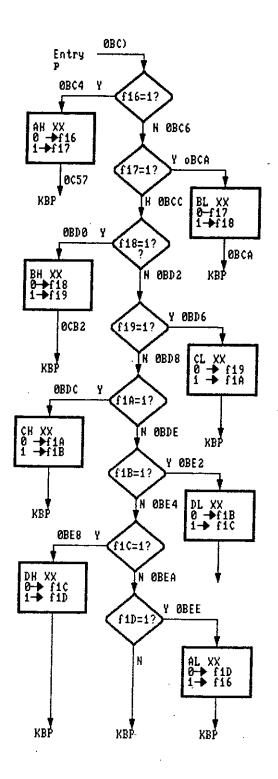

| Figure - 5.4.5    | Flow Chart to Examine AL, AH, BL, BH, CL, CH, DL, DH Conte    | ents    | 71       |

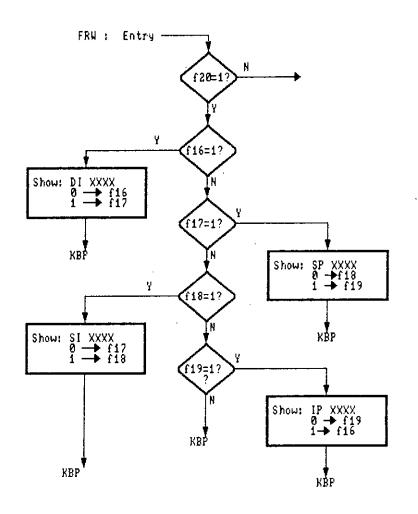

| Figure - 5.4.6    | : Flow Chart to Examine IP,SI,SP,DI,BP Contents               |         | 72       |

| Figure - 5.4.7    | : Flow Chart to Examine CS, DS, SS, ES Contents               |         | 73       |

| Figure - 5.4.8    | : Diagram Showing the Mapping of Flag Register's Content to   | Display | 74       |

| Figure - 5.4.9    | : Flow Chart to Examine Memory Content in S/S without Exit    |         |          |

| Figure - 5.4.10   | : Flow Chart to Examine Port Contents                         |         | 76       |

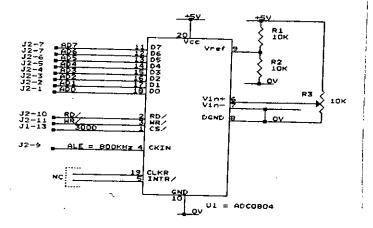

| U U               | : Circuit for Prototyping Analog-to-Digital Conversion        |         | 83       |

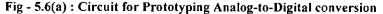

| Figure - $5.6(a)$ | : Circuit Diagram for Stand-alone Routine No. 4 )RUT - 4)     | ••      | 85       |

| Figure - 5.6(b)   |                                                               | ••      | 89       |

| Figure - 5.8      | : Data Structure for Interrupt Vector Table                   | ••      | 91       |

| Figure - 5.9      | : Memory Map Table                                            |         | 91<br>93 |

| Figure - 5.10     | : Port Space Map Table                                        | ••      | 95<br>95 |

| Figure - 5.11     | : Memory Map Table for Reserved RAM Space                     | ••      | 93<br>96 |

| Figure - 6.1      | : Broad Layout for the Integrated Peripheral Module           | ••      | 70       |

|                   |                                                               |         |          |

| a transferration of the second Medule                                            | 1 | 01         |

|----------------------------------------------------------------------------------|---|------------|

| Figure - 6.4 : Block Diagram for the Integrated Peripheral Module                |   | .03        |

| Figure - 6.5 : Schematic Diagram for the Extended Port Decoder of IPM            | 1 | 05         |

| Figure - 6.6 : Schematic Diagram for 6-Channel Programmable Timer                | 1 | .07        |

| Figure - 6.7 : Schematic Diagram of the 8-Channel AC                             | 1 | 09         |

| Figure - 6.8 : Schematic for 8-Bit Digital-to-Analog Converter                   | 1 | 11         |

| Figure - 6.9.1 : Schematic for Parallel I/O using 8256                           | 1 | 13         |

| Figure - 6.9.2 : Schematic Diagram for Serial I/O Using 8256                     | 1 | 15         |

| Figure - 6.9.3 : Schematic Diagram for the Timing Functions Using 8256           |   | 117        |

| Figure - 6.9.4 : Schematic Diagram for the Counting functions Using 8256         |   | 119        |

| Figure - 6.9.5 : Schematic Diagram for Interrupt Priority Management Usi         | 0 | 121        |

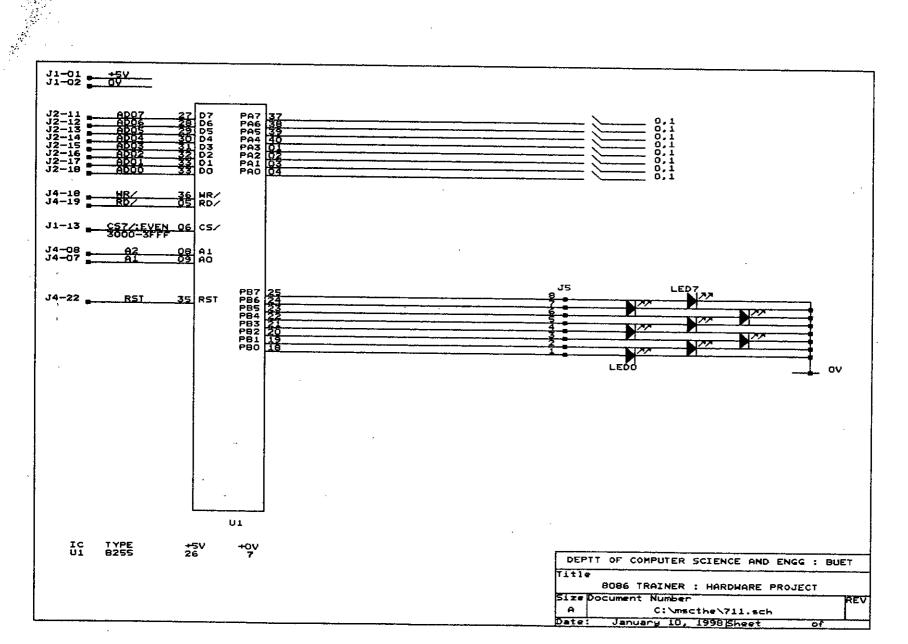

| Figure - 7.1.1 : Schematic for Driving LED Arrays Using 8255 and 8086            |   | 121        |

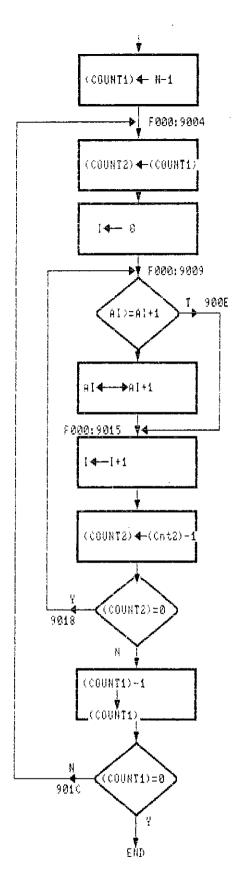

| Figure - 7.1.2 : Flow Chart to Implement Bubble Sort Algorithm                   | 1 | 125        |

| Figure - 7.2.1 : Schematic for Interfacing Bedford Inverter                      |   | 125        |

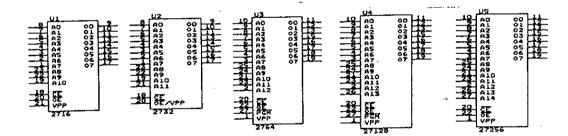

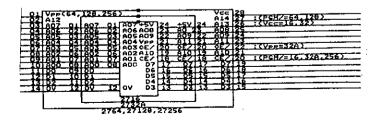

| Figure - 7.2.2(a) : EPROM Programming Chart using 28-PIN ZIF Sc                  |   | 126        |

| Figure - 7.2.2(b): 28-Pin ZIF Socket Pin Diagram                                 |   |            |

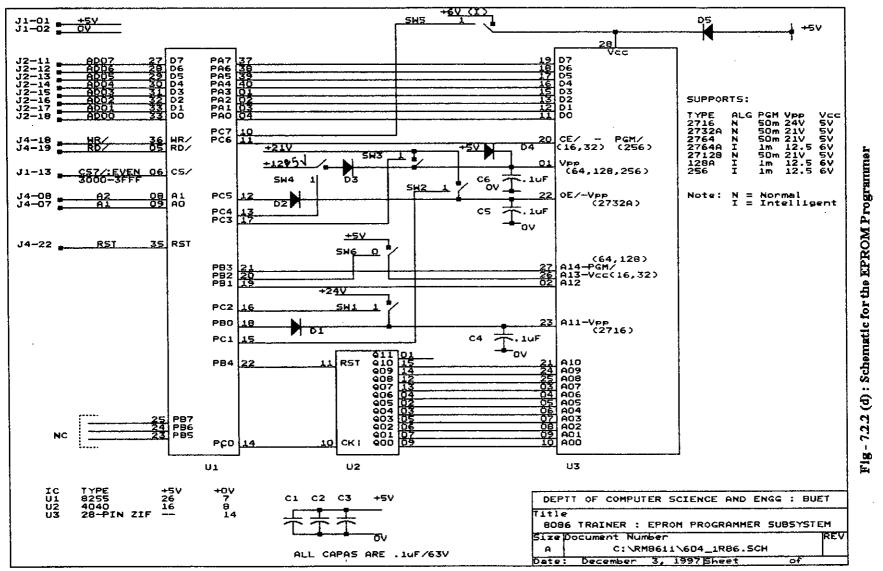

| Figure - 7.2.2(d): Schematic for the EPROM Programmer                            |   | 128        |

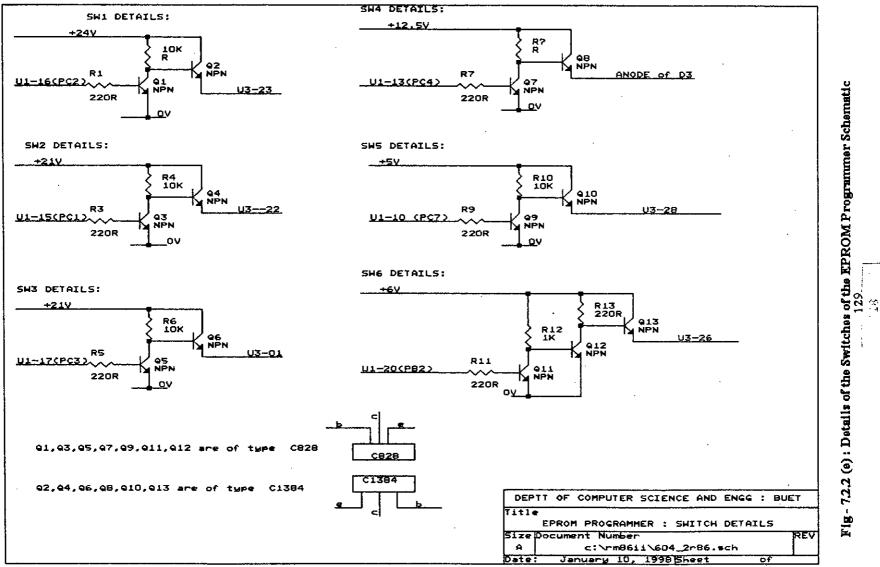

| Figure - 7.2.2(e): Details of the Switches of the EPROM programmer               |   | 129        |

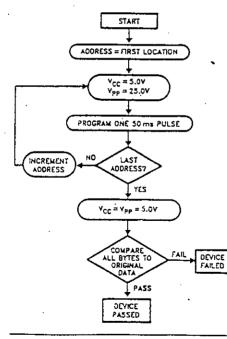

| Figure - 7.2.2(f): Programming Algorithm for 2716                                |   | 130        |

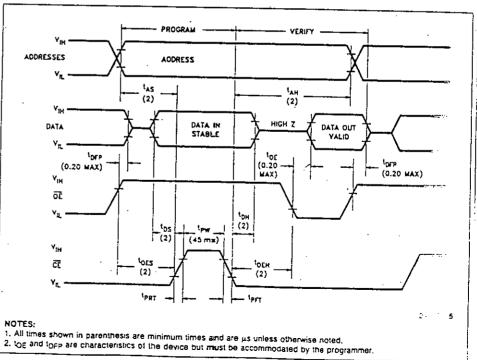

| Figure - 7.2.2(g): Timing Parameters for 2716 EPROM                              |   | 131        |

| Figure - 7.2.2(h): Programming Algorithm for 2732A                               |   | 132        |

| Figure - 7.2.2(i): Timing Parameters for 2732A EPROM                             |   | 133        |

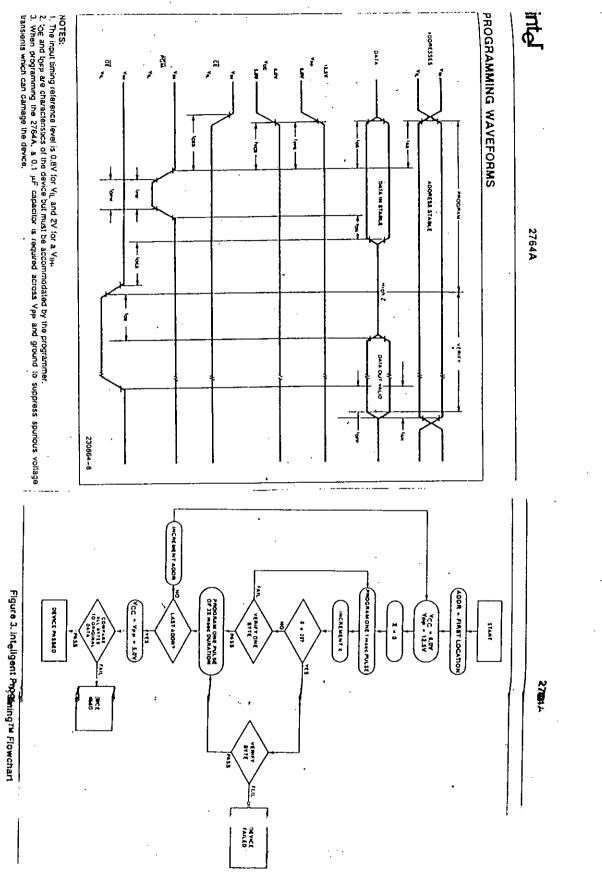

| Figure - 7.2.2(j): Programming Algorithm for 2764A                               |   | 134        |

| Figure - 7.2.2(k): Timing Parameters for 2764A EPROM                             |   | 135        |

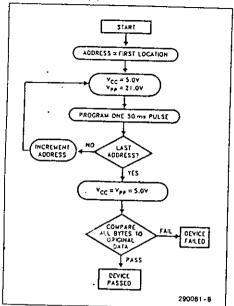

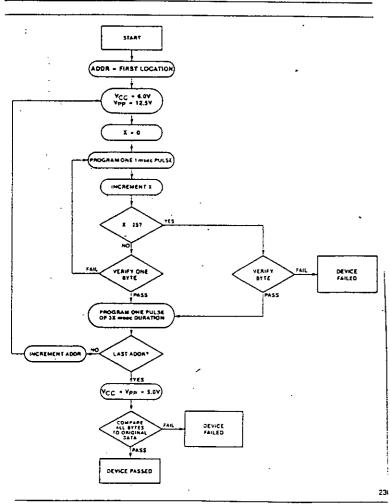

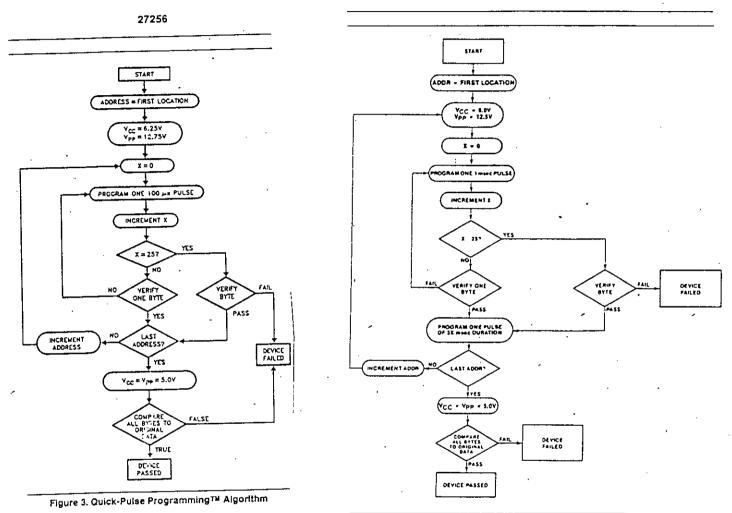

| Figure - 7.2.2(I): Programming Algorithm for 27128A EPROM                        |   | 136        |

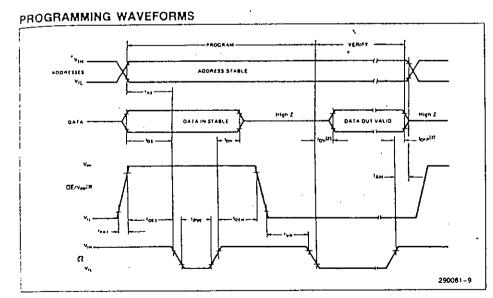

| Figure - 7.2.2(m): Timing Parameters for 27128A EPROM                            |   | 137        |

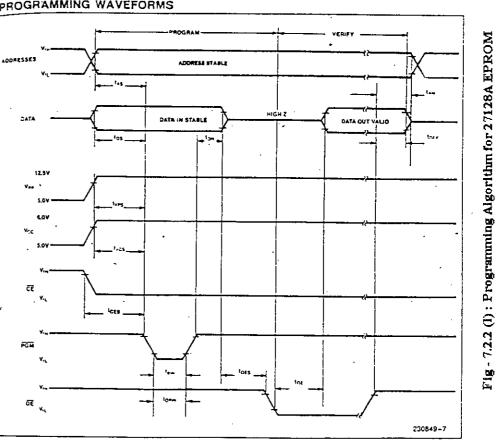

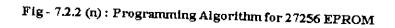

| Figure - 7.2.2(n): Programming Algorithm for 27256 EPROM                         |   | 138        |

| Figure - 7.2.2(o): Timing Parameters for 27256 EPROM                             |   | 139        |

| Figure - 7.2.2(p): Timing Parameters for 27256 EPROM (continued)                 |   | 140        |

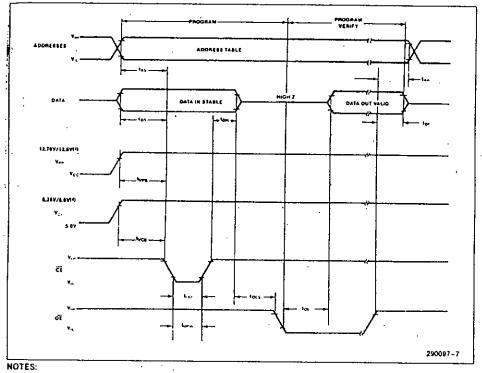

| Figure - 8.1(a) : Hardware Interface Circuit Bet <sup>n</sup> Trainer and IBM-PC |   | 142        |

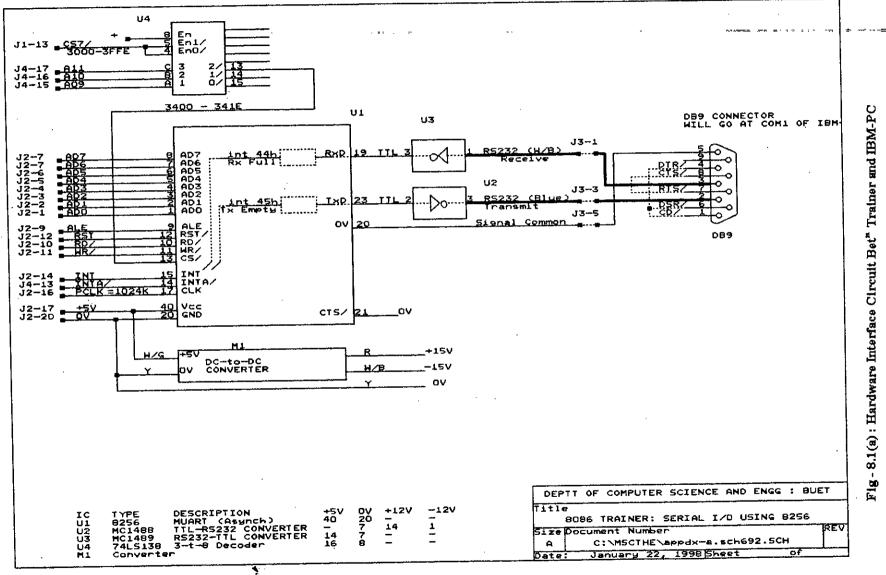

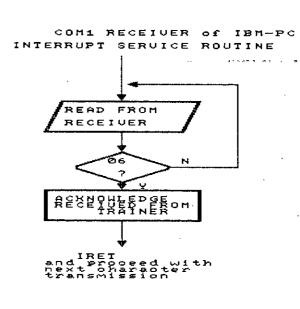

| Figure - 8.1(b) : Software Flow Chart for IBM-PC's Serial Transmission P         | 0 | 143        |

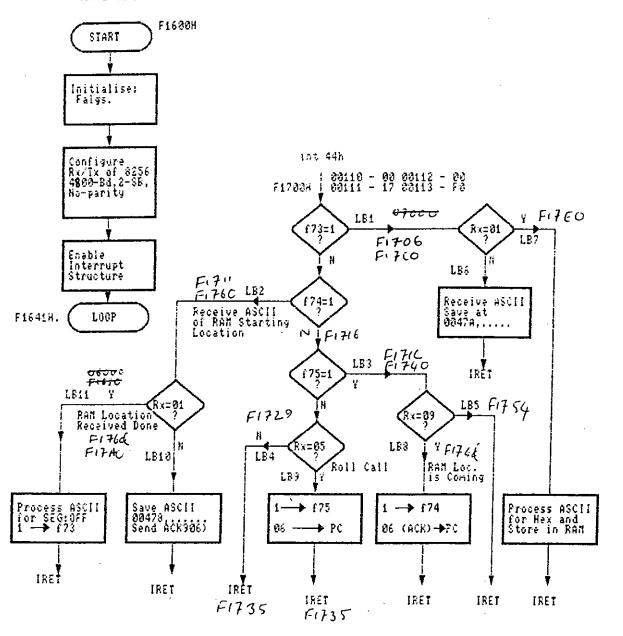

| Figure - 8.4 : Software Flow Chart for Trainer's Firmware                        |   | 156        |

| Figure - A.1 : Schematic Diagram of 8087 with 8086                               |   | 162        |

| Figure - B.1 : Component Layout of the ROM-BASED Assembler's 808                 |   | 165<br>167 |

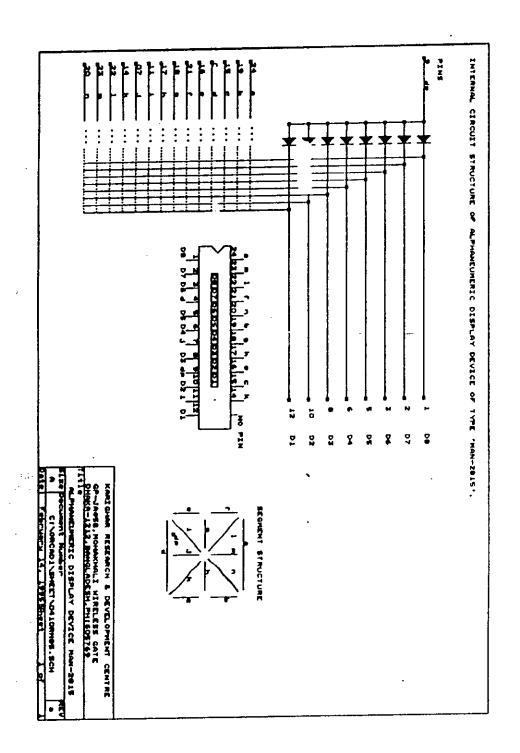

| Figure - B.2(a) : Schematic of the Alphanumeric Display/Keyboard                 |   |            |

| Figure - B.2(b) : Internal Circuitry of MAN2815 Display Device                   |   | 168        |

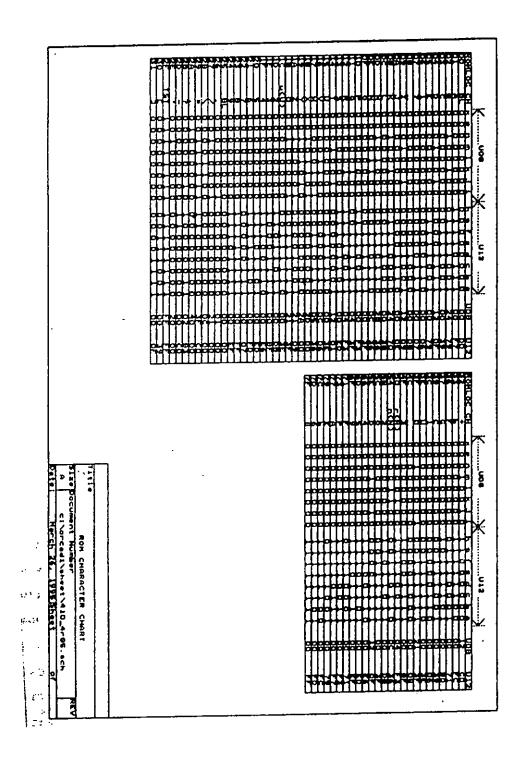

| Figure - B.2(c) : Character ROM Data Table                                       |   | 169        |

| Figure - D,2 : Wire Wrap Tools and Accessories                                   |   | 195        |

| Figure - D.4(a) : Soldering Techniques                                           |   | 197        |

| Figure - D.4(b) : Good Soldering                                                 |   | 197        |

| Figure - D.4(c) : Poor Soldering                                                 |   | 197        |

| Figure - D.5 : View of the Trainer Board as seen from TOP                        |   | 198        |

| Figure - D.6 : Solder Side PCB Artwork Looking from Bottom                       |   | 199        |

| Figure - D.7 : Component Side PCB Artwork Looking from TOP                       |   | 200        |

| Figure - D.8 : Solder mask including PTH of the PCB Artwork                      |   | 201        |

| Figure - F.1 : Color Plate of Component Side of the Prototype 8086 Tra           |   | 206        |

| Figure - F.2 : Color Plate of Wire Wrap Side of the 8086 Trainer                 |   | 206        |

| Figure - F.3 : Color Plate of Component Side of the PCB of 8086 Trainer          |   | 207        |

| Figure - F.4 : Color plate of Solder Side of the PCB of the 8086 Trainer         |   | 207        |

| Figure - F.5 : Color plate of the pictorial View of the final 8086 Trainer       |   | 208        |

# 1

# INTRODUCTION

This chapter gives a brief introduction to the Evolution of Microprocessor, Motivation for the Thesis Work, Detailed Content Outline and the Main Features of the developed Trainer.

### **Evolution of Microprocessor**

A microprocessor is a programmable device. Within it, there are thousands of transistors forming large number of floating type basic logic gates and memory cells. The interconnections between these circuits are established and broken asserting software commands from outside. This way, a single microprocessor chip is used to impleir ent numerous types of work. The credit for the idea of a general purpose microprocessor goes to one of the Intel engineers who was working on the Japanese camera Co. - Busicom around 1970. The microprocessor can take data from different users and can modify the data exactly the way a user wants. The CPU can give back the modified data to the user.

The arrival of microprocessor has brought revolutionary change in the field of 'Information Technology' and 'Industrial Instrumentation and Control.' Without today's high speed microprocessor, it would be simply impossible to build low cost desktop computers that are processing and presenting 'Information' worth million of dollars.

Early microprocessors, during 1974 - 1976, were mainly developed for making business calculators and controlling simple industrial processes. With the passage of time, peoples' mentality evolved and started thinking of 'Time Saving.' They made the personal computers using the early 8-bit microprocessor (8085, 6502,...) to do their word processing and simple spread sheet works at home without going to the mainframe station located somewhere down town.

The first 16-bit microprocessor, called 8086 appeared in 1978. Enhanced version of 8086, called 80186, appeared in the same year with integrated peripherals. In 1983, the 80286 microprocessor appeared with 'Protected Virtual Mode Addressing' capability and 'Multitasking' support. As application begun to demand more speed, the 80386 (32-bit) appeared in 1986. In 1989, Intel released 80486 (32-bit) with built-in math coprocessor and cache. The Pentium (64-bit) appeared in 1993.

Figure - 1 presents a curve showing the growth of component density per chip versus time.

1

#### Motivation for the Present Work

"Microprocessor Fundamentals" is a basic subject offered to computer, electrical and electronic engineering and many other applied disciplines. Because of the enormous popularity of Intel microprocessors, it has become a *de facto* standard of including Intel's 8085 (8-Bit) and 8086 (16-Bit) microprocessors in the curriculum. The study and the understanding of the features of these microprocessors require relevant CPU based trainers. The prescribed text books usually make frequent references to the microprocessor trainers for the clarification of many concepts and the experimentation of new ideas. These trainers are also needed by the professionals engaged in designing and developing microprocessor based industrial control systems and consumer products.

These trainers are non-consumer items and are usually made by the rich companies in the developed countries as a side product in their factories, where the main product is an electronic/electrical consumer product. They have the manpower, machinery, sophisticated development tools etc., worth millions of dollars. Setting up such a million dollar factory to produce these educational trainers, woould merely mean to be a dream - at least, in Bangladesh!

The educational institutions of Bangladesh are in a crying need of these trainers. They could not get them in time due to price hulk and import formalities. As a result, the microprocessor courses are being conducted mainly on paper and black board. Some of the institutions might have their trainers but the numbers are certainly very low compared to the number of students.

#### Outline of this Thesis

**Chapter - 1** is the introduction. It makes a brief survey of the evolution of various microprocessors. A curve is shown to indicate the trend of evolution of microprocessor with time. This chapter has included the motivation behind the development of the 8086 trainer presented in this thesis.

**Chapter - 2** has documented the operating procedures of the trainer. The meanings for the labels of the Keys of the 'Keyboard Template' are also given. A component layout of the trainer is provided. The commercial type numbers of the components are also provided. The names of the signals at various pins of the edge connectors are also given. This chapter also contains some example programs for exercising how to enter a program code into the trainer for execution.

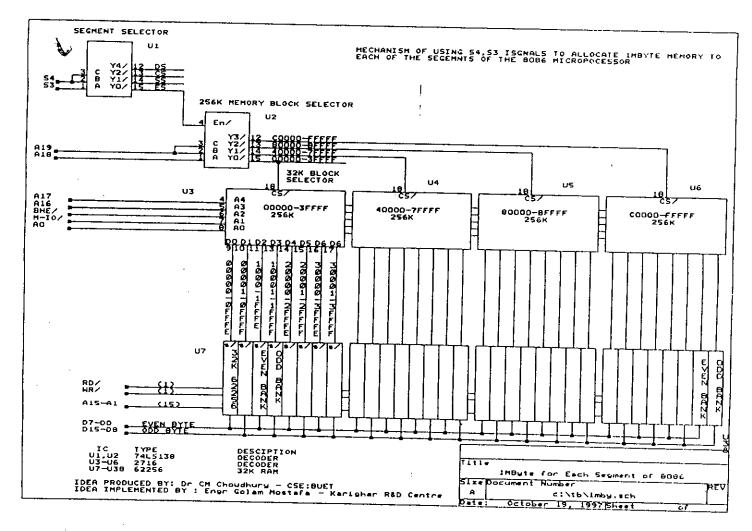

**Chapter - 3** describes the fundamental features of the 8086 microprocessor. The functional description of the pins are presented along with diagrams. The use of DT-R/ and DEN/ signals are illustrated showing their connection with 74LS245 data buffer. The definitions of the processor status signals are given. Special attention is given as to the application of the S4,S3 signals in connection with their possible use for accessing 1Mbyte of memory per segment. A circuit diagram is added showing how these status bits could be decoded to allow the 8086 CPU for accessing 4 Mbytes of memory [1].

The chapter also includes the register architecture of the 8086 processor. An address computation chart is provided along with examples. This chapter also contains a summary of the instruction set.

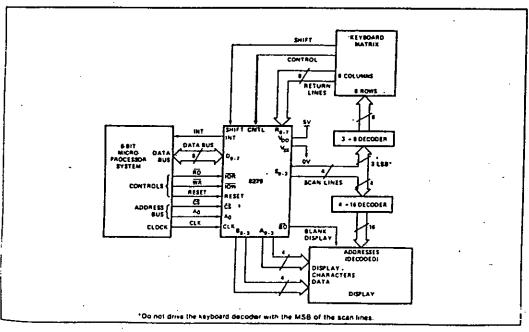

Chapter - 4 includes the complete schematics of the hardware of the trainer. The total circuit is divided into four subsystems viz., (1) CPU Subsystem, (2) Memory/Port Decoding Subsystem, (3) Memory Subsystem, and (5) Keyboard/Display Subsystem. There is a block diagram showing the overall hardware structure of the trainer. Every subsystem is followed by detailed description of the working principles of the circuit of that subsystem.

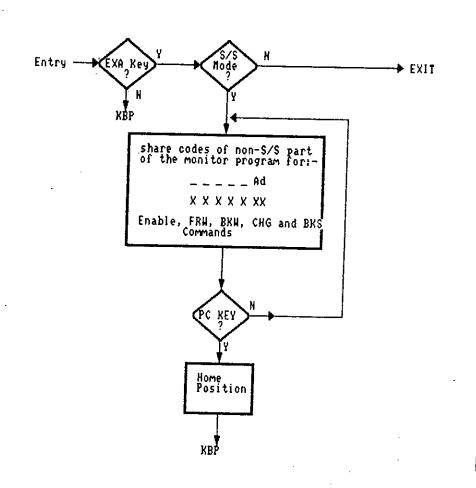

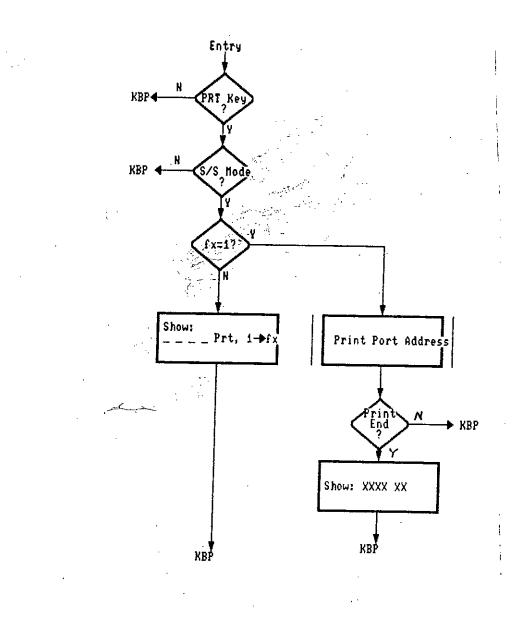

**Chapter - 5** is the full documentation of the monitor program of the 8086 trainer. The logic of the entire monitor program is summarized into eight flow charts. These flow charts will be fe\requently referred during the study and analyze of the working principles of the monitor program.

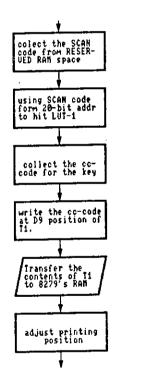

There is also description corresponding to each key command. For example, how does the trainer response when EXA key is pressed. Or, how does the CPU response when BKS key is pressed. The description has also been augmented by flow charts and program listing.

The chapter contains the source code listing of all the subroutines and the stand-alone routines which are provided as firmware in the EPROMs of the trainer. The various data and lookup tables are also given.

The memory/port and the reserved RAM space maps are provided. The interrupt vector table is also given.

**Chapter - 6** contains full technical documentation of an Integrated Peripheral Module containing 2 -Programmable Interval Timers of the type 8253, 1- Analog-to-Digital Converter of type AD08084, 1-Digital-to-Analog Converter of the type AD558, 1- Eight Channel Analog Multiplexer of the type DG508, RS232-TTL-RS232 Converting Chips of the type 489, 488 and a versatile Controller Chip of the type 8256. The 8256 chip contains all the commonly used five functions viz., Parallel I/O, Serial I/O, Timing, Counting and Interrupt Priority Management. This separate board is provided to help convenient implementation of interfacing experiments. Basic initialization routines of all the peripherals are also given.

**Chapter - 7** has indicated the realistic application of the 8086 trainer. The applications are (1) display of the binary data using an 8255 controller (2) coding and running a Bubble Sort Program (3) Complex timing function generation for the Bedford Inverter and (4) the construction of an EPROM programmer. The chapter also contains full data sheet of the commonly used EPROMs of the type 2716, 2732, 2764, 27128 and 27256. The data sheets include the flow charts of numerous programming algorithms. An example program has been included in this chapter to program an EPROM of the type 2716.

**Chapter - 8** documents the serial communication software to download program codes from IBM-PC to the 8086 trainer. The schematic of the hardware interfacing between the trainer and the IBM-PC is given. The transmitter software is developed using assembly/C language and the complete source code listing is provided. The resulting exe file is named scom86.EXE and is provided in a 3.5" disk with the trainer. The trainer's firmware listing is also given.

**Chapter - 9** shows a study of the results expected from the trainer and the actual results achieved. The reasons for the discrepancies are described in the discussion caption.

**Chapter - 10** makes hints as to possible future good technical works that could be done based on this trainer. The possible areas are 80286 trainer to study PVAM features, ROM-Based Assembler, On-board 8087 math coprocessor and improving the existing monitor program.

Appendix - A includes the schematic diagram of the 8086 system in its maximum mode while operated with an 8087 math coprocessor.

**Appendix - B** documents the preliminary experimental works for the development of a ROM based Assembler 8086 Trainer. The component lay out is given along with an alphanumeric keyboard. The original Hex keyboard is retained to operate the trainer for learning purposes. The appendix contains the full schematic of the 15-segment alphanumeric display system. The ROM character table is also presented. The internal circuitry of the 15-segment display is also provided.

Appendix - C contains data sheets for the 8279 and 8256 programmable controllers. This is provided to make this thesis complete.

**Appendix - D** describes the manual procedures of making the PCB for the trainer. The PTH (printed through holes) have been made by hand. The procedures of good soldering is also presented in the form of pictorial illustration. This appendix also contains the pictorial view of the PCB artwork.

Appendix - E describes the manual procedures/methodology of fusing the program/data codes of the monitor program into EPROM. This job is usually done by an automatic development system where the program codes are developed in the IBM-PC and then down loaded into the prototype trainer..

**Appendix - F** includes the color plates of the various board of the trainer. These are the component/wire wrapping sides, the component/solder sides of the final PCB and the solder mask.

#### Features Summary

| HARDWARE and SOFTWARE FEATURES SUMMARY                                              |

|-------------------------------------------------------------------------------------|

|                                                                                     |

| lardware Features:                                                                  |

| 1. 8086 CPU                                                                         |

| 2. 64Kbytes EPROM                                                                   |

| 3. 64 Kbytes RAM                                                                    |

| 4. Bus Lines at Edge Connectors for Interfacing Experiments                         |

| 5. 5. 5''x2.5'' Bread Board for Prototyping Circuits                                |

| 6. Well Documented User's Manual                                                    |

| 7. 18-Key Hex-key pad allows Machine Codes Programming                              |

| 8. 9 - Digits 7-Segment Display Window                                              |

| 9. Memory and Port Decoded Lines are Available at Edge Connectors                   |

| 0. +5V Power Supply Adapter.                                                        |

| oftware Feature:                                                                    |

| 1. Powerful and Comprehensive Resident Monitor Program                              |

| 2. Auto/Manual Data Entry for both Bytes/Word Operations                            |

| 3. Program Execution Capability                                                     |

| 4. Forward/Backward/Change/Backspace Facilities, Bytes/Word Examine/Edit Capability |

| 5. IBM-PC to Trainer Down Loading Software                                          |

| 6. Single Instruction Execution Capability for Program Debugging                    |

| 7. Basic Initialization Routines for Many Peripheral ICs like ADC, DAC,8251,8259    |

| 18. Register's Contents can be Examined and Changed                                 |

## 2

# 8086 MICROPROCESSOR FUNDAMENTALS

This chapter is an introduction to the fundamental of 8086 microprocessor. Included are, the detailed description of the various pin functions, the basic timing diagram, internal architecture, register layout, address computing chart and the instruction set summary.

#### 2.1 Pin Diagram and Functions

The 16-bit 8086 microprocessor is packaged in a 40-pin CERDIP (CERamic Dual In Package) or plastic DIP package [Figure - 2.1(a), 2.1(b)]. It is 0.3-inch wide and 2-inch long. The pins are separated from each other by 0.1-inch. The CPU design has been implemented using HMOS technology to achieve high performance. The 8086 operates at 5MHz, 8086-2 at 8MHz and the 8086-1 at 10 MHz with maximum power dissipation of 2.5W. There are corresponding CMOS versions (80C86,80C86-2,80C86-1) which operate at the same frequencies as for the HMOS 8086 but with maximum power dissipation of 1W. The 8086 has two modes of operation viz., Minimum Mode which does not permit connecting a 2nd processor/co-processor in the system and Maximum Mode which allows connecting a second processor/co-processor. Throughout this thesis, we will be studying the 8086 CPU in a minimum mode for better understanding the underlying concepts. Appendix-A includes the maximum mode operation of the 8086 CPU.

#### Address Bus - 20 Lines

There are 20 address lines and are designated by A19 - A15 and A15 - A00 (embedded in AD15 - AD00) which are shown in Fig-2.1(a) and Fig-2.1(b). Address lines are used by the processor to select a particular memory location of a standard memory or an interface memory for data read/write operation. Since these lines are always originating from the processor and terminating to the memory devices, they are unidirectional output lines. The possible combinations of these lines range from 0000 0000 0000 0000 0000 0000 (binary) to 1111 1111 1111 1111 (binary).

In hex notation the range is from 00000H to FFFFFH. In decimal, the range is from 0 to 1,048,575 which equals to 1,048,576 combinations. This figure indicates that the 8086 CPU can individually select up to 1,048,576 memory locations. Taking 1024 as 1K and 8-bit size (1 byte) for each memory location as is the normal practice in computer literature, then the total addressable memory becomes 1 mega bytes or 1Mbyte. The address number for the data location of a standard memory or port memory is always treated as an unsigned binary number.

The lower 16 address lines (A15-A00) are used to assert the address of a memory location when that location is considered as a port space and is enabled by the LOW level of the M-IO/ line. During port read/write operations, the upper four address lines viz., A19-A16 remain zeros. Thus the 8086 CPU can address up to 65,536 locations of port.

In 8086 CPU, the lower 16 address lines viz., AD15 - AD00 share common lines with the 16 data signals D15 - D00. This is possible due to the fact that a memory location is selected first and then the data read/write operation takes place. Stating another way, the address assertion and the data dump events never occur at the same time. Therefore, these two distinct information can be multiplexed over the same physical wires in time axis. And the composite signals being carried by these lines may be shown as AD15 - AD00.

#### Data Bus - 16 Lines multiplexed with A15-A00 Lines

There are 16 data lines D15-D00 (embedded in AD15-AD00) for the 8086 CPU and are time multiplexed with the lower 16 address lines A16-A00. The default read/write operation of the CPU is byte oriented. That is, while the CPU is reading data from memory on its own (while booting up after power up reset), it reads data byte by byte. Then what is the benefit of having 16 data lines? The answer is given saying that the CPU has got powerful instruction by virtue of which the programmer can instruct the CPU to do a word operation. This increases the speed of the system almost by twice. The lower data bye D7-D0 is called EVEN data while the upper data byte D15-D8 is called ODD data. The Data lines are bi-directional.

#### Read/Write Control Bus - 2 Lines

Fundamentally, only one line should be enough to complete read and write operation on memory chip. Single line can carry either HIGH or LOW logic value and this feature can be utilized to distinguish between read and write operations. In fact Motorola 6802 and 68000 microprocessors use only one line for both read/write operation. Whereas, Intel 8085,8086 use two lines for read/write operations. The choice of 1 or 2 lines is a matter of design convention and convenience.

To differentiate read/write with standard memory or port memory, use of a separate line makes sense. And it is M-IO/ line.

#### Read Control Line: RD/ - 1 line

This is a single line originating from the CPU and going to the memory (both the standard and the port memory) devices. It carries active low signal to indicate the selected memory chip that the address information asserted to its inputs are now stable and it should now dump the desired data byte on the data bus. Figure -2.1(d) is referred for the timing relationship of this signal with other bus signals.

#### Write Control Line : WR/ - 1 line

This is also a single output line. This line is connected to both the standard memory and port memory. It carries active low signal to trigger the selected memory chip that the address and data asserted to its

٤.

inputs are now stable and it should absorb the data byte from the data bus. Figure - 2.1(d) shows the timing relationship of this signal with other bus signals.

#### Memory/Port Control Line: M-IO/ - 1 line

A microcomputer system can have many memory chips. Some of them are RAM and ROM and the rest are certainly port memories being connected with the users devices. By standard convention and practices, the RAM and ROMs are assigned 20-bit unsigned number for the addresses of their internal memory locations. And the input/output controllers (port memories or simply port) are assigned 16-bit/8-bit numbers for the internal memory locations. A single line designated as M-IO/ is used to distinguish between memory or port selection. A high signal on M-IO/ line will enable the memories and a low signal on M-IO/ line will enable the ports.

#### Memory Bank Control Lines

#### BHE/ (Byte High Enable) Signal

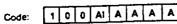

This signal is multiplexed with S7 signal on pin-34 of the CPU. This is a memory related signal and hence needs to be sampled by an optional latch (refet to section-4.2 schematic). The CPU asserts low level signal over this line when a user instruction requests a WORD oriented or ODD byte data read/write operation. The BHE/ signal has a close association with A00 address line as shown below:-

| BHE/ | A00 | Meaning                                                     |

|------|-----|-------------------------------------------------------------|

| 0    | 0   | : one word operation in one machine cycle when aligned with |

|      |     | even address                                                |

| 0    | 1   | : D15-D8 (upper byte = ODD byte) operation                  |

| 1    | 0   | : D7-D0 (lower byte = EVEN byte) operation                  |

#### **Multiplexed Bus Control Line**

#### ALE Line (Address Latch Enable)

The 16-bit address information from the composite AD15 - AD00 signals is to be sampled and kept to the input address lines of the intended memory location until the data read/write operation is finished. To accomplish this, it is necessary to know the 'Time Point' at which the address signal is being asserted on the composite AD15 - AD00 lines. The 8086 CPU does indicate this 'Time Point' by generating a single pulse called ALE over pin-25. This ALE signal could be used to trigger optional D-type flip-flops (for example 74LS373 in section - 4.2) to latch the address information from their inputs to the output. Since ALE signal is generated only once during a read or write operation (refer to page-22), the output of the D-FFs which is in fact address information will remain constant at the input of the memory chip until the data movement operation is completed.

The above reasoning may also be applied for the upper 4 address lines viz., A19 - A16. The physical wires assigned to carry these signals might in fact carry composite signals like A19/S6 - A16/S3. S6 - S3 stand for Status signals. An optional latch (section - 4.2) can be triggered to sample the A19- A16 information from the composite signal and hold them at the output. Now the lines are free and they may be used to carry the processor Status signals S6-S3.

#### **Processor Control Lines**

#### RST (ReSeT) Line

It is an input line and carries a positive pulse to start the processor from the cold state. The minimum requirement for the width of this pulse is at least four clock periods. The reset pulse is usually supplied by an auxiliary clock chip of type 8284 (Sec-4.2) and is synchronized with processor clock. At the rising edge of the reset pulse, the CPU will terminate all operations if it was doing something. The CPU will

remain 'Idle' for the duration of the pulse. During the falling edge of the reset pulse, the CPU will undergo an internal reset sequence and will last for about 10 clock periods. During the reset sequence, the following events occur within the CPU:-

| Data Segment register is initialized to 0000H         | DS = 0000H |

|-------------------------------------------------------|------------|

| Stack Segment register is initialized to 0000H        | SS = 0000H |

| Extra Segment register is initialized to 0000H        | ES = 0000H |

| Code Segment register is initialized to FFFFH         | ĊS = FFFFH |

| Instruction Pointer register is initialized to 00000H | IP = 0000H |

| Flag Register is initialized to 0000H                 | FR = 0000H |

At the end of the reset sequence, the processor starts booting up from the absolute memory location CS:IP = FFFF:0000H

#### MN-MIX/ (MiNimum mode or MaXimum mode)

The meaning of the pin signals of the 8086 CPU are sufficiently different when it operates in minimum maximum and modes (Appendix B). Maximum mode allows connecting additional processors/coprocessors to realize multiprocessing environment. Whereas, minimum mode does not permit so. An IC having only 40 pins is not capable of furnishing all the functions required by min and max mode operations. To keep the number of pins at minimum while achieving the multiprocessing performance, a jumper pin (pin-33) has been added to the CPU. When MN-MX/ pin is strapped to +5V, the 8086 asserts signals at its various pins as required by the minimum mode operation (Section - 3.1). When the jumper pin is connected to ground potential, the CPU asserts maximum mode signals at its various pins.

#### RDY (ReaDY)

This is an input logic to the processor. The CPU functions normally as long as the logic level at this pin remains high. When the logic level of this pin goes low, the CPU starts inserting 'WAIT States' in its operating clock (page-22). It means that the clock period begins stretching and all bus activities gets frozen. Activities resume when the pin restores high logic level.

The addition of the RDY pin in the CPU allows the utilization of slow memory in the system design. Slow memories are cheap in price but the access time is greater than 200nS. There are in fact some commercial systems requiring huge on-board memories with moderate importance in speed. The RDY line is connected with the controller of the slow memory module. After the reception of the address, data and read signal from the buses, the controller pulls down the RDY line. After the known delay, the slow memory dumps the data on the bus. The controller also receives this information and it immediately releases the RDY line.

The RDY signal is usually provided by the clock chip generator (8284). The output of the slow memory controller is connected to the input of the clock chip (Section - 4.2). This is to allow synchronous operation of the RDY signal with the processor clock.

#### CLK

The CLK signal is the prime mover to the CPU for the generation of all the timing functions. The clock signal is usually provided by an auxiliary clock generator chip viz., 8284. The clock has a duty cycle of 33% for optimum operation. For details of the clock circuitry, refer see section - 4.2.

#### +5V Supply

To supply the power for the operation of the internal electronics. The tolerance of the voltage is  $5V\pm10\%$  for the 8086 and 5% tolerance for the 8086-1 and 8086-2. The maximum current that may be drawn from the power supply is 340 mA at room temperature.

#### 0V Supply

To sink the +5V supply current. Two pins have been used to provide parallel paths for minimizing the noise.

#### Interrupt Control Lines

#### NMI (Non-Maskable Interrupt)

It is an asynchronous external input signal for interrupting the CPU. The active signal is rising edge which is sampled by the processor during the last clock cycle of the instruction being executed. The CPU is directed to an interrupt service routine (abbreviated as ISR) for interrupt 'type 2'. The starting address of the ISR is found by consulting a lookup table called Interrupt Vector Table (IVT) located at space 00000H - 003FFH of the main memory. This interrupt can not be disabled by setting the IF-bit of the flag register. This type of interrupt is designated as externally triggered internally vectored hardware interrupt. This input is usually terminated by a pull down resistor of 5Kohm.

#### INTR (INTeRrupt)

This is also an asynchronous external input to interrupt the CPU. It is level sensitive and is sampled by the CPU during the last clock cycle of the instruction being executed. This interrupt is usually funneled by an Interrupt Priority Controller chip like 8259. The type code for the interrupt is supplied by the interrupting device via 8259. The CPU is directed to an ISR consulting the IVT. This interrupt can be disabled by setting the IF-bit of the flag register. This type of interrupt is designated as externally triggered externally vectored hardware interrupt.

#### INTA/ (INTerrupt Acknowledge)

This is an active low signal, generated by the CPU in response to INTR signal. It is asserted to inform the interrupting device to dump the 8-bit interrupt type code on the data bus. There are two such pulses that are generated. This output is terminated by a pull up resistor of 5Kohm.

#### DMA Control Lines

#### HOLD

An asynchronous input signal asserted by DMA device. The signal must remain high until the DMA service is completed. The CPU samples this input during every machine cycle of an instruction. The input is terminated by a pull down resistor of 5Kohm.

#### HLDA (HoLD Acknowledge)

The CPU generates an active high signal at this pin in response to the HOLD input. This signal is propagated to the DMA device to indicate that the local bus has been isolated from the system bus (Section - 4.2). Now the system bus mastership may be owned by the DMA device for direct data transfer to the RAM bypassing the CPU. At the end of DMA action the HOLD line goes low and the CPU also pulls down the HLDA line. The local bus becomes associated with system bus and the CPU regains the bus mastership.

## Interprocessor Communication Line *TEST Line*

The CPU samples this input during every clock cycle and keeps working if logic low is detected. This line is usually connected with a math coprocessor called 'Floating Point Unit = FPU' in maximum mode operation (8087). The FPU asserts this pin high to inform the 8086 to stop executing its instructions and wait for some computational result to be supplied by the FPU. Refer to Figure- A.2 at page-162.

#### **Utility Lines**

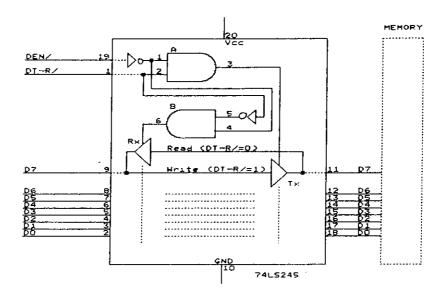

#### DEN/ (Data buffer Enable)

The local bus of the CPU has a very limited current driving capability and is just good to drive one TTL load. If a user wishes to connect more loads, suitable data buffer (like 74LS245) are to be installed to protect the local bus from being damaged due to overloading. The asynchronous DEN/ (active low) signal is generated by the CPU may be used to enable such data buffers. For minimum systems, this line usually remains open. Refer Fig-2.1(c) for the application of this signal.

#### DT-R/

This alternate signal is generated by the CPU asynchronously to change the direction of the data buffer being enabled by DEN/ signal. The signal level becomes high if the instruction being executed refers to a write operation on external memory. The signal becomes active low if the instruction is involved in data read operation from the external memory. Please see Fig-2.1(c) below for the implementation of this line.

Fig - 2.1(c) : Implementing the DEN/ and DT-R/ Signals

#### Processor Status Lines

#### S3,S4,S5,S6 and S7 Lines

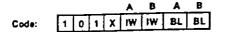

Signals S3,S4,S5,S6 and S7 appearing at the indicated pins of the Fig-2.1(b) are termed as Status lines. These signals become available just after the assertion of the A19-A16 address information. To grasp these status information, suitable electronic circuitry are to be employed. The meaning of these signals are as follows:

| Status<br>S4               | Signals<br>S3 | Meaning                                                                                                                                            |

|----------------------------|---------------|----------------------------------------------------------------------------------------------------------------------------------------------------|

| 1                          | 1             | : The memory reference instructions are using Data Segment for read/<br>write operations during the execution of the current instruction           |

| 1                          | 0             | : The memory reference instructions are using Code Segment for read/<br>write operations during the execution of the current instruction.<br>or    |

|                            |               | : The CPU is accessing the Interrupt Vector Table for jumping to Interrupt Service Routine in response to an Interrupt.                            |

| 0                          | 1             | : The memory reference instructions are using Stack Segment for data accessing.                                                                    |

| 0                          | 0             | : The memory reference instructions are using Extra (Alternate) Segment for read/write operations during the execution of the current instruction. |

| S5 = 1<br>S6 = 0<br>S7 = ? |               | : The IF-bit of the flag register is set.<br>: always<br>: Spare                                                                                   |

S3 and S4 - these two lines indicate the status of the segment being used by the processor for accessing the data/code at the current instruction. These two lines can be used to access up to 4 Mbytes of memory (1 Mbyte per Segment) [1]. Refert to Fig - 2.1(e) for the hardware circuit to realize this concept.

#### **Pin Loading Considerations**

#### Sourcing

Every pin can source maximum  $400\mu$ A current at minimum 2.4V. if the load increases, the logic level may decrease and the behavior of the CPU will become unpredictable.

#### Sinking

Every pin can sink about 2.5mA current at maximum 0.45V.

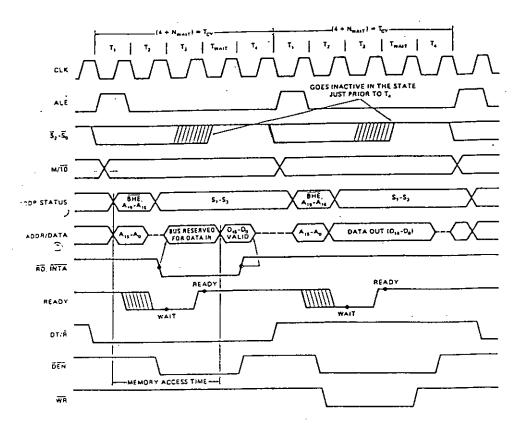

Figure-2.1(d) shows the activities on the 8086 bus during simple read/write operations. The first line show the clock waveform. One cycle of this clock is referred to as 'State' and is designated by the symbol 'T'. The group of states required for the completion of one read or write operation is called a 'Machine Cycle'. The total time needed by the CPU to complete the activities of one instruction is called an 'Instruction Cycle'.

To read data from a memory location, the CPU asserts the 20-bit address information on the bus. The ALE signal is generated to demultiplex the address information from the composite AD15 - AD0 signals. M-IO/ signal is made 'High' to select memory device. After some delay, the RD/ signal is asserted to bring the data from the bus into the accumulator of the CPU. DT-R/ and DEN/ signals are generated to enable the data buffers if there is any.

Fig - 2.1(e) : Schematic Diagram to Allocate 1MByte per Segment for 8086 using S3,S4 Signals

### 2.2 Internal Architecture

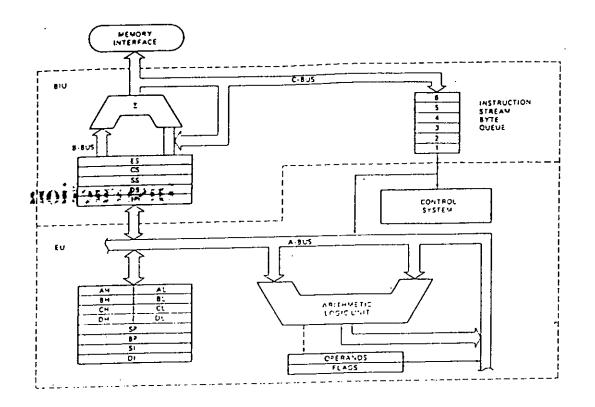

Figure - 2.2(a) is the block diagram of the internal architecture of 8086 microprocessor. The machine is primarily composed of two functional units viz., 'Bus Interface Unit (BIU)' and 'Execution Unit (EU).' Each functional unit is also composed of many subunits.

Fig - 2.2(a) : Functional Blook Diagram

#### **BIU : Bus Interface Unit**

This unit is composed of the following subunits:-

#### Memory Interface Unit

This unit asserts the 20-bit physical address on the external bus to read/write data/code out of memory.

#### Instruction Stream Byte Queue

The instruction codes (program codes) goes to the 'Instruction Stream Byte Queue (ISBQ)' over the C-Bus. When the CPU is busy for calculating the address or internal processing, the bus is free and is used to read the instruction codes from the external memory and are stored in the ISBQ. Thus the CPU always gets the instruction bytes from inside except during branch and jump. This increases the throughput of the system.

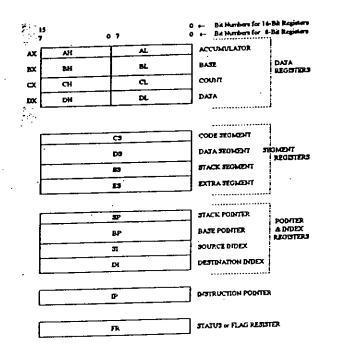

#### Segment and Instruction Pointer Registers

There are five registers. Thease are:-

ES : Extra Segment Register. It holds the upper 16-bit of the 20-bit base address of the extra segment.

CS : Code Segment Register. It holds the upper 16-bit of the 20-bit base address of the code segment.

SS: Stack Segment Register. It holds the upper 16-bit of the 20-bit base address of the stack segment

DS : Data Segment Register. It holds the upper 16-bit of the 20-bit base address of the data segment.

IP : Instruction Pointer Register. Its 16-bit content is added with the CS-base address to read code byte.

#### Address Computing Subunit

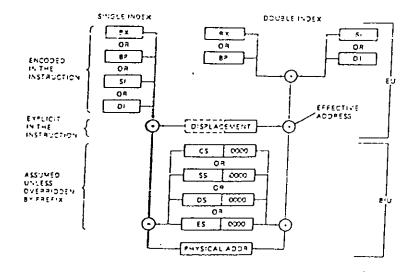

Figure - 2.2(b) is the expnaded view of the address computing unit of the BIU unit. The chart shows all possible modes for calculating the 20-bit physical address of a memory operand. Examples :-

| Single Index: | mov a<br>mov a | x,[bx]<br>x,[bx+d8]<br>x, [bx+d16]<br>x, cs: [bx + d8] | : default segment is DS<br>: default segment is DS<br>: default segment is DS<br>: default segment is overridden CS |

|---------------|----------------|--------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------|

| Double Index: | mov            | ax,[bx+si]                                             | : default segment is DS                                                                                             |

|               | mov            | ax,[bx+si+d8]                                          | ; default segment is DS                                                                                             |

|               | mov            | ax,[bx+si+d16]                                         | ; default segment is DS                                                                                             |

|               | mov            | ax, cs:[bx+si+d8]                                      | ; default segment is overridden by CS                                                                               |

Fig - 2.2(b) : Address Computing Unit

#### EU = Execution Unit

This is composed of the following subunits:-

#### Working Register Bank

Figure - 2.2(c) shows the layout of the internal registers of the 8086 microprocessor. The programmer can access these registers except the CS and IP registers.

Fig - 2.2(c) : Internal Register Layout

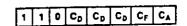

#### Status/Flag Register

There is a 16-bit status register of which only 9 bits are active. This register reflects the operational status after the execution of each instruction. The flag bits are :-

| B0 - CF  | : Carry Flag - when a carry is generated after the addition of two operands           |

|----------|---------------------------------------------------------------------------------------|

| B2 - PF  | : Parity Flag - number of 1s becomes even after operation                             |

| B4 - AF  | : Auxiliary Flag - a carry is generated out of 4th bit during BCD operation.          |

| B6 - ZF  | : Zero Flag - the result due to operation is zero                                     |

| B7 - SF  | : Sign Flag - the MSB of the data is 1 due to the execution of an instruction.        |

| B8 - TF  | : Trap Flag - to allow the CPU to execute one instruction at a time.                  |

| B9 - IF  | : Interrupt Flag - to enable/disable hardware interrupts viz., INTR.                  |

| B10 - DF | : Direction Flag - used to control the direction of string transfer.                  |

| B11 - OF | : Overflow Flag - when the result of an operation exceeds the capacity of the destin. |

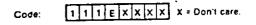

### 2.3 Instructions

The instructions of 8086 microprocessor are broadly classified into 6 groups. The mnemonics summary is given in Figure-2.3(a). Coding templates are given in Figures-2.3(b), 2.3(c) and 2.3(d).

| DATA TRANSFER INSTRUCTIONS                                                                                                                            |                                                                                                                                                                                      | PROCESSOR CONTROL                                                                                                                                      |

|-------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------|

| General Purpose                                                                                                                                       | Addition                                                                                                                                                                             | Flag Operations                                                                                                                                        |

| mov                                                                                                                                                   | add                                                                                                                                                                                  | clc                                                                                                                                                    |

|                                                                                                                                                       | adc                                                                                                                                                                                  | cmc                                                                                                                                                    |

| push                                                                                                                                                  | inc                                                                                                                                                                                  | stc                                                                                                                                                    |

| pop                                                                                                                                                   |                                                                                                                                                                                      | cld                                                                                                                                                    |

| xchg                                                                                                                                                  | aaa                                                                                                                                                                                  |                                                                                                                                                        |

| xlat                                                                                                                                                  | daa                                                                                                                                                                                  | std                                                                                                                                                    |

|                                                                                                                                                       |                                                                                                                                                                                      | cli                                                                                                                                                    |

| Input/Output                                                                                                                                          | Subtraction                                                                                                                                                                          | sti                                                                                                                                                    |

| in                                                                                                                                                    | sub                                                                                                                                                                                  |                                                                                                                                                        |

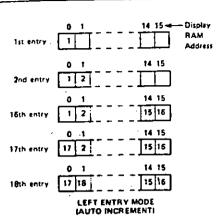

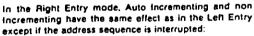

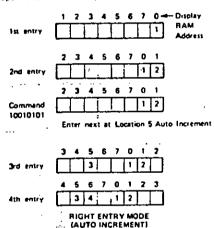

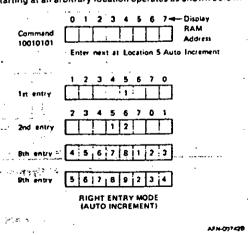

| out                                                                                                                                                   | sbb                                                                                                                                                                                  | External Synchrpnizn.                                                                                                                                  |