# SYMBOLIC SUBSTITUTION BASED APPROACH FOR THE DESIGN OF CARRY-FREE BINARY ARITHMETIC UNIT

by

TASADDUQ IMAM

A THESIS SUBMITTED TO THE DEPARTMENT OF COMPUTER SCIENCE AND ENGINEERING IN PARTIAL FULFILLMENT OF THE REQUIREMENTS FOR THE DEGREE OF MASTER OF SCIENCE IN ENGINEERING (COMPUTER SCIENCE AND ENGINEERING)

DEPARTMENT OF COMPUTER SCIENCE AND ENGINEERING BANGLADESH UNIVERSITY OF ENGINEERING AND TECHNOLOGY DHAKA, BANGLADESH

**JUNE 2004**

The thesis "SYMBOLIC SUBSTITUTION BASED APPROACH FOR THE DESIGN OF CARRY-FREE BINARY ARITHMETIC UNIT" submitted by Tasadduq Imam, Roll No. 040205033P, Registration No. 95401, Session April 2002, to the Department of Computer Science and Engineering, BUET, has been accepted as satisfactory for partial fulfillment of the requirements for the degree of Master of Science in Engineering (Computer Science and Engineering) and approved as to its style and contents.

| $\mathbf{v}$ | ARD OF EXAMINERS                                |                   |

|--------------|-------------------------------------------------|-------------------|

| 1.           | 2028Y1467964Dly 12-06.2004                      |                   |

|              | (Dr. M. Kaykobad)                               | Chairman          |

|              | Professor,                                      | (Supervisor)      |

|              | Department of CSE, BUET, Dhaka.                 |                   |

| 2.           | 2/6/04                                          |                   |

|              | (Dr. Md. Shamsul Alam)                          | $\mathbf{Member}$ |

|              | Professor and Head,                             | (Ex-officio)      |

|              | Department of CSE, BUET, Dhaka.                 | •                 |

| 3.           | (Dr. A. S. M. Latiful Haque)                    | Member            |

|              | Assstant Professor,                             |                   |

|              | Department of CSE, BUET, Dhaka.                 |                   |

| 4.           | Thakkon<br>12.06.2004                           |                   |

|              | (Dr. Md. Mozammel Haque Azad Khan)              | Member            |

|              | Professor,                                      | (External)        |

|              | Department of CSE, East West University, Dhaka. |                   |

# **DECLARATION**

t.

I, hereby, declare that the work presented in this thesis is the outcome of the investigation performed by me under the supervision of Dr. M. Kaykobad, Professor, Department of Computer Science and Engineering, Bangladesh University of Engineering and Technology, Dhaka. I also declare that no part of this thesis and thereof has been or is being submitted elsewhere for the award of any degree or diploma.

Countersigned

(Dr. M. Kaykobad)

Supervisor

Tasaddia Imem 12/06/04

(Tasadduq Imam)

# ACKNOWLEDGEMENT

Here I would like to take the opportunity to express my greatest gratitude to the patrons of this thesis work, without whom I could never have completed this arduous task.

First and Foremost, I express my sincere gratitude and profound respect to my supervisor **Dr. M. Kaykobad**, Professor, Dept. of Computer Science and Engineering, Bangladesh University of Engineering and Technology. It would be injustice to say only that the thesis was just completed under his kind supervision. His keen interest, deep insight and ideas and above all his time to time scholarly guidance and suggestions have made it possible to complete this thesis work.

I would also like to thank Dr. M. A. Karim, Professor, Dept. of Electrical and Electronic Engineering, City College of NewYork, US for guiding me to some reading materials and giving valuable suggestions.

I would also like to express my heartiest gratitude to **Dr. M. Z. Iqbal**, Professor, Dept. of Electrical and Electronic Engineering, Shahjalal University of Science and Technology, Sylhet, Bangladesh for sending me a copy of a presentation of Professor Karim, very much related to my thesis topic.

I would also like to thank the anonymous reviewers of the *International Journal of Computers and Mathematics with Applications* for their suggestions that have been helpful in providing some new insight.

I must acknowledge with due respect the constant support and patience of my parents for completing the thesis.

And I must thank the members of the board, Prof. Dr. Md. Shamsul Alam, Dr. A. S. M. Latiful Haque and Prof. Dr. M. H. A. Khan, for their comments and suggestions.

# ABSTRACT

Symbolic Substitution has been proposed in optical computing literature as a parallel processing technique to perform arithmetic computation. Employing a conversion table as a reference, the process iteratively substitutes a set of input patterns by pre-defined output patterns. Along with the development of this parallel processing technique, researchers have also come up with a number of non-binary representations that allow fast carry-free addition. Modified Signed Digit(MSD) and Canonical Modified Signed Digit(CMSD) number systems have been extremely popular in this regard. In contrast with the binary system, these number systems use three types of symbols: 0, 1 and -1. Redundancy due to the extra digit make these systems suitable for symbolic substitution based parallel addition process.

However, traditional computing is based on binary system and corresponding binary logic. But generation of carry in binary arithmetic is the main hindrance to employing the symbolic substitution process and making the computation fast.

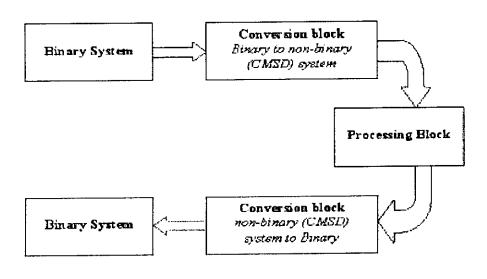

The focus of this study has, therefore, been the development of a symbolic substitution based process for fast arithmetic computation of binary numbers. The idea has been the design of a fast addition unit that accepts at its interface numbers represented in binary form. then converts these numbers to some intermediate non-binary representation for processing, and then converts the result back to the binary form. The focus has been the development of symbolic substitution processes for all the intermediate phases involved like the conversion of binary to the non-binary representation, processing of the numbers and finally the conversion of the non-binary representation to binary representation. Due to its capability of unique representation of numbers and sparseness of the non-zero digits in the representation, Canonical Modified Signed Digit (CMSD) representation has been chosen as the non-intermediate representation for the arithmetic unit proposed in the study.

An important factor in the context of symbolic substitution is the required number of

substitution steps. The thesis presents a set of symbolic substitution tables and algorithms that require much less substitution steps to complete the conversion and addition operations than any other corresponding earlier schemes. Also, the addition algorithm presented in the study derives the addition result in CMSD notation and thus it could be employed to perform symbolic substitution based associative addition of a set of CMSD numbers.

An important contribution of this thesis is the development of a symbolic substitution based unit that can perform the associative addition of a set of binary numbers in computationally more efficient way than using any of the earlier proposed schemes. Such an algorithm can lead to the way of employing symbolic substitution in other arithmetic operations, like multiplication, where associative addition of a set of numbers is an integral process.

# CONTENTS

| A            | CKN                    | OWL    | EDGEMENT                                                    | i    |

|--------------|------------------------|--------|-------------------------------------------------------------|------|

| A            | BST                    | RACT   |                                                             | ii   |

| $\mathbf{L}$ | IST (                  | OF FI  | GURES                                                       | vii  |

| $\mathbf{L}$ | IST (                  | OF TA  | ABLES                                                       | viii |

| L            | IST (                  | OF AL  | GORITHMS                                                    | ix   |

| <u>C</u>     | hap                    | ters   |                                                             |      |

| 1            | INT                    | rrod'  | UCTION                                                      | 1    |

|              | 1.1                    | Fast ( | Computation and Bottlenecks of Traditional Computing System | 1    |

|              | 1.2                    |        | oaches to Fast Computation                                  |      |

|              | 1.3                    | Optic  | al Computing and Symbolic Substitution                      | 2    |

|              | 1.4                    | Non-b  | oinary Number Systems                                       | 2    |

|              | 1.5                    | Objec  | tive and Scope of the Thesis                                | 3    |

|              | 1.6                    | Organ  | nization of the Thesis                                      | 4    |

| 2            | $\mathbf{C}\mathbf{A}$ |        | FREE ARITHMETIC: A LITERATURE SURVEY                        | 5    |

|              | 2.1                    |        | -free Arithmetic                                            |      |

|              | 2.2                    | Carry  | Lookahead Adder(CLA)                                        |      |

| !            | 2.3                    | Introd | luction of Redundancy in Number Systems                     |      |

|              | 2.4                    | Differ | ent Number Systems                                          |      |

|              |                        | 2.4.1  | Redundant Number System                                     |      |

|              |                        | 2.4.2  | Modified Signed Digit Number System                         |      |

|              |                        | 2.4.3  | Canonical Modified Signed Digit Number System               |      |

|              |                        | 2.4.4  | Residue Number System                                       |      |

|              |                        | 2.4.5  | Other Variations of Redundant Number System                 |      |

|              |                        | 2.4.6  | Double Base Number System                                   |      |

|              | 0 5                    | Corne  | from Addition Schames                                       | 13   |

|   | 2.6               | Choic                                                                              | e of Number System in Carry-free Addition Scheme                                                                                                                                                                                                                                                                                                                                                  | 13                                                                 |

|---|-------------------|------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------|

| 3 | SY                | MBOL                                                                               | IC SUBSTITUTION AND ARITHMETIC COMPUTATION                                                                                                                                                                                                                                                                                                                                                        | 15                                                                 |

|   | 3.1               | Optic                                                                              | s as a Backbone of Fast Computation                                                                                                                                                                                                                                                                                                                                                               | 15                                                                 |

|   | 3.2               |                                                                                    | olic Substitution                                                                                                                                                                                                                                                                                                                                                                                 |                                                                    |

|   | 3.3               | Differ                                                                             | ent Symbolic Substitution Methods                                                                                                                                                                                                                                                                                                                                                                 | 16                                                                 |

|   | 3.4               | Intens                                                                             | sity Coded Symbolic Substitution                                                                                                                                                                                                                                                                                                                                                                  | 17                                                                 |

|   |                   | 3.4.1                                                                              | Dual-rail Encoding                                                                                                                                                                                                                                                                                                                                                                                | 17                                                                 |

|   |                   | 3.4.2                                                                              | Symbolic Substitution Process                                                                                                                                                                                                                                                                                                                                                                     | 18                                                                 |

|   |                   | 3.4.3                                                                              | Multiple-rules Symbolic Substitution Process                                                                                                                                                                                                                                                                                                                                                      | 21                                                                 |

|   | 3.5               | Polari                                                                             | zation Coded Symbolic Substitution                                                                                                                                                                                                                                                                                                                                                                | 21                                                                 |

|   | 3.6               | Basic                                                                              | Symbolic Substitution Unit                                                                                                                                                                                                                                                                                                                                                                        | 22                                                                 |

|   | 3.7               | Symbo                                                                              | olic Substitution and Arithmetic Computation                                                                                                                                                                                                                                                                                                                                                      | 23                                                                 |

|   | 3.8               |                                                                                    | olic Substitution Based Computation Algorithms                                                                                                                                                                                                                                                                                                                                                    |                                                                    |

|   |                   | 3.8.1                                                                              | Three-step MSD Addition                                                                                                                                                                                                                                                                                                                                                                           | 24                                                                 |

|   |                   | 3.8.2                                                                              | Two-step MSD Addition                                                                                                                                                                                                                                                                                                                                                                             | 26                                                                 |

|   |                   | 3.8.3                                                                              | One-step CMSD Addition                                                                                                                                                                                                                                                                                                                                                                            | 27                                                                 |

|   |                   | 3.8.4                                                                              | Conversion to CMSD                                                                                                                                                                                                                                                                                                                                                                                | 28                                                                 |

|   | 3.9               | Concl                                                                              | uding Remarks                                                                                                                                                                                                                                                                                                                                                                                     | 28                                                                 |

|   | Y 17/             | TONI A                                                                             |                                                                                                                                                                                                                                                                                                                                                                                                   | _T                                                                 |

| 4 |                   | SIGN (<br>TIC U                                                                    | OF A SYMBOLIC SUBSTITUTION BASED BINARY ARITH                                                                                                                                                                                                                                                                                                                                                     | .1-<br>30                                                          |

|   | 4.1               |                                                                                    | lying Motivation                                                                                                                                                                                                                                                                                                                                                                                  |                                                                    |

|   | 4.1               |                                                                                    | sed Arithmetic Unit                                                                                                                                                                                                                                                                                                                                                                               |                                                                    |

|   | 4.3               |                                                                                    | ent Phases of the Proposed Arithmetic Unit                                                                                                                                                                                                                                                                                                                                                        |                                                                    |

|   | 4.0               |                                                                                    |                                                                                                                                                                                                                                                                                                                                                                                                   | - 3                                                                |

|   |                   | 121                                                                                |                                                                                                                                                                                                                                                                                                                                                                                                   |                                                                    |

|   |                   | 4.3.1                                                                              | Conversion of MSD and Binary to CMSD                                                                                                                                                                                                                                                                                                                                                              | 32                                                                 |

|   |                   | 4.3.2                                                                              | Conversion of MSD and Binary to CMSD                                                                                                                                                                                                                                                                                                                                                              | 32<br>34                                                           |

|   |                   | 4.3.2<br>4.3.3                                                                     | Conversion of MSD and Binary to CMSD                                                                                                                                                                                                                                                                                                                                                              | 32<br>34<br>38                                                     |

|   |                   | 4.3.2<br>4.3.3<br>4.3.4                                                            | Conversion of MSD and Binary to CMSD                                                                                                                                                                                                                                                                                                                                                              | 32<br>34<br>38<br>40                                               |

|   |                   | 4.3.2<br>4.3.3<br>4.3.4<br>4.3.5                                                   | Conversion of MSD and Binary to CMSD                                                                                                                                                                                                                                                                                                                                                              | 32<br>34<br>38<br>40<br>43                                         |

|   | :                 | 4.3.2<br>4.3.3<br>4.3.4<br>4.3.5<br>4.3.6                                          | Conversion of MSD and Binary to CMSD                                                                                                                                                                                                                                                                                                                                                              | 32<br>34<br>38<br>40<br>43<br>44                                   |

|   | 4.4               | 4.3.2<br>4.3.3<br>4.3.4<br>4.3.5<br>4.3.6<br>Compa                                 | Conversion of MSD and Binary to CMSD                                                                                                                                                                                                                                                                                                                                                              | 32<br>34<br>38<br>40<br>43<br>44<br>45                             |

| 5 |                   | 4.3.2<br>4.3.3<br>4.3.4<br>4.3.5<br>4.3.6<br>Compa                                 | Conversion of MSD and Binary to CMSD  Conversion of Binary to CMSD: One-step Algorithm  Addition of CMSD numbers  Addition of CMSD numbers in 1 step  Conversion of MSD to Binary  Conversion of CMSD to Binary  arison of the Proposed Schemes with Earlier Ones  EDUCTION AND EXPERIMENTAL ANALYSIS                                                                                             | 32<br>34<br>38<br>40<br>43<br>44<br>45                             |

| 5 | <b>ST</b> 5.1     | 4.3.2<br>4.3.3<br>4.3.4<br>4.3.5<br>4.3.6<br>Compa                                 | Conversion of MSD and Binary to CMSD  Conversion of Binary to CMSD: One-step Algorithm  Addition of CMSD numbers  Addition of CMSD numbers in 1 step  Conversion of MSD to Binary  Conversion of CMSD to Binary  arison of the Proposed Schemes with Earlier Ones  EDUCTION AND EXPERIMENTAL ANALYSIS  Attion of Symbolic Substitution Steps                                                      | 32<br>34<br>38<br>40<br>43<br>44<br>45<br><b>47</b>                |

| 5 | <b>ST</b> 5.1 5.2 | 4.3.2<br>4.3.3<br>4.3.4<br>4.3.5<br>4.3.6<br>Compa                                 | Conversion of MSD and Binary to CMSD  Conversion of Binary to CMSD: One-step Algorithm  Addition of CMSD numbers  Addition of CMSD numbers in 1 step  Conversion of MSD to Binary  Conversion of CMSD to Binary  arison of the Proposed Schemes with Earlier Ones  EDUCTION AND EXPERIMENTAL ANALYSIS  tion of Symbolic Substitution Steps  rsion of MSD and Binary to CMSD                       | 32<br>34<br>38<br>40<br>43<br>44<br>45<br>47<br>47                 |

| 5 | <b>ST</b> 5.1     | 4.3.2<br>4.3.3<br>4.3.4<br>4.3.5<br>4.3.6<br>Compa<br>EP RE<br>Reduce<br>Converted | Conversion of MSD and Binary to CMSD  Conversion of Binary to CMSD: One-step Algorithm  Addition of CMSD numbers  Addition of CMSD numbers in 1 step  Conversion of MSD to Binary  Conversion of CMSD to Binary  arison of the Proposed Schemes with Earlier Ones  EDUCTION AND EXPERIMENTAL ANALYSIS  Ition of Symbolic Substitution Steps  rsion of MSD and Binary to CMSD  ion of CMSD numbers | 323<br>344<br>388<br>400<br>433<br>444<br>455<br>477<br>479<br>500 |

| 5 | <b>ST</b> 5.1 5.2 | 4.3.2<br>4.3.3<br>4.3.4<br>4.3.5<br>4.3.6<br>Compa<br>EP RE<br>Reduce<br>Converted | Conversion of MSD and Binary to CMSD  Conversion of Binary to CMSD: One-step Algorithm  Addition of CMSD numbers  Addition of CMSD numbers in 1 step  Conversion of MSD to Binary  Conversion of CMSD to Binary  arison of the Proposed Schemes with Earlier Ones  EDUCTION AND EXPERIMENTAL ANALYSIS  tion of Symbolic Substitution Steps  rsion of MSD and Binary to CMSD                       | 32<br>34<br>38<br>40<br>43<br>44<br>45<br>47<br>47                 |

| 3.7 | ٠ |

|-----|---|

| v   | 4 |

#### CONTENTS

| 6  | SYI  | MBOLIC SUBSTITUTION BASED ASSOCIATIVE ADDITION | 55 |

|----|------|------------------------------------------------|----|

|    | 6.1  | Introduction to the Topic                      | 55 |

|    | 6.2  | Associative Addition of Binary Numbers         |    |

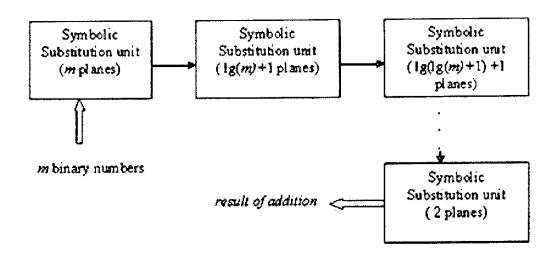

|    | 6.3  | Block Level Architecture of the Unit           |    |

|    | 6.4  | Required Steps to Complete Addition            | 57 |

|    | 6.5  | Concluding Remarks                             |    |

| 7  | CO   | NCLUSION AND RECOMMENDATIONS                   | 60 |

|    | 7.1  | Concluding Words                               | 60 |

|    | 7.2  | Recommendations for Future Work                | 62 |

|    |      |                                                |    |

| Βl | BLI  | OGRAPHY                                        | 64 |

|    |      |                                                |    |

| ΡŪ | JBLI | CATIONS OF THE CANDIDATE RELATED TO THE THESIS | 68 |

| IN | DEX  |                                                | 69 |

|    |      |                                                |    |

# LIST OF FIGURES

| 2.1 | Carry-free addition                                                       | 6  |

|-----|---------------------------------------------------------------------------|----|

| 3.1 | Dual-rail encoding                                                        | 17 |

| 3.2 | Substitution rule                                                         | 18 |

| 3.3 | Symbolic substitution: Recognition phase (step 1)                         |    |

| 3.4 | Symbolic substitution: Recognition phase (step 2)                         |    |

| 3.5 | Symbolic substitution: Recognition phase (step 3)                         |    |

| 3.6 | Symbolic substitution: Substitution phase                                 |    |

| 3.7 | Multiple substitution rules                                               |    |

| 3.8 | Block architecture of a symbolic substitution unit                        |    |

| 3.9 | Symbolic substitution based arithmetic computation                        |    |

| 4.1 | Logical diagram of the proposed fast addition unit                        | 31 |

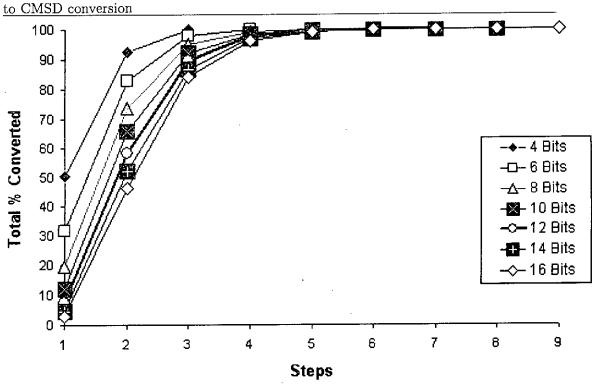

| 5.1 | Graph of total of the percentage converted vs. required no. of steps for  |    |

|     | MSD to CMSD conversion                                                    | 51 |

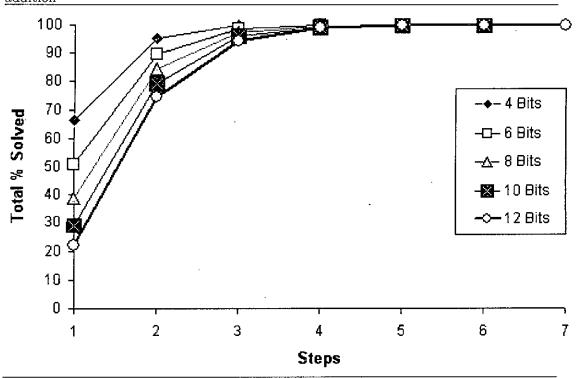

| 5.2 | Graph of total of the percentage added vs. required no. of steps for CMSD |    |

|     | addition                                                                  | 52 |

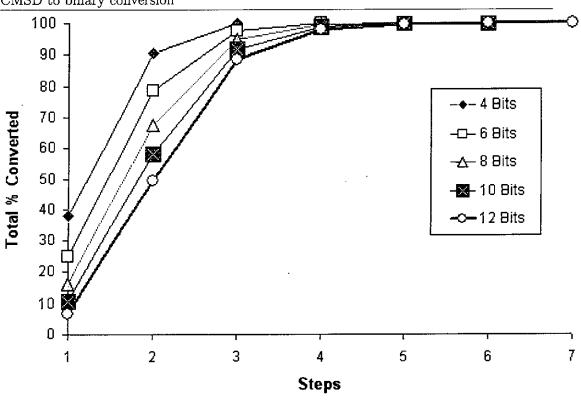

| 5.3 | Graph of total of the percentage converted vs. required no. of steps for  |    |

| 5.0 | CMSD to binary conversion                                                 | 54 |

| 6.1 | Symbolic substitution architecture for associative addition               | 58 |

# LIST OF TABLES

| $3.1_{\sim}$ | Symbolic substitution tables for MSD addition: Three-steps                                         | 24         |

|--------------|----------------------------------------------------------------------------------------------------|------------|

| 3.3          | Symbolic substitution tables for MSD addition: Two-steps                                           | 26         |

| 3.4          | Symbolic substitution tables for CMSD addition: One-step                                           | 28         |

| 3.5          | Reitwiesner's conversion table and corresponding complementary conver-                             |            |

|              | sion table                                                                                         | 28         |

| 4.1          | Symbolic substitution table to convert MSD and binary number to CMSD                               |            |

|              | in $\left(\left\lfloor \frac{n}{2} \right\rfloor + 1\right)$ steps                                 | 33         |

| 4.2          | CheckCond.1 for Table 4.1                                                                          | 33         |

| 4.3          | CheckCond.2 for Table 4.1                                                                          | 33         |

| 4.4          | Symbolic substitution table for converting 4-bit binary number to CMSD                             |            |

|              | representation in 1 step                                                                           | 37         |

| 4.5          | Symbolic substitution table for performing addition of CMSD numbers in                             |            |

|              | $(\lfloor \frac{n}{2} \rfloor + 1)$ steps and preserving CMSD property                             | 39         |

| 4.6          | $CheckCond.1 \ for \ Table \ 4.5 \ \dots \dots \dots \dots \dots \dots \dots \dots \dots \dots$    | 40         |

| 4.7          | CheckCond.2 for Table 4.5                                                                          | 40         |

| 4.8          | Symbolic substitution table for performing addition of CMSD numbers in                             |            |

|              | one step $\dots$                                                                                   | <b>4</b> 1 |

| 4.9          | Symbolic substitution table for converting MSD number to 2's complement                            |            |

|              | binary number in $n$ steps                                                                         | 43         |

| 4.10         | Symbolic substitution table to convert CMSD to binary in $(\lfloor \frac{n}{2} \rfloor + 1)$ steps | <b>4</b> 5 |

| 5.1          | Result of analysis for MSD to CMSD conversion                                                      | 49         |

| 5.2          | Result of analysis for CMSD addition                                                               | 51         |

| 5.3          | Result of analysis for CMSD to binary conversion                                                   | 53         |

| 6.1          | Demonstration of associative addition                                                              | 56         |

| 6.1          | $(Contd.) \ \ldots \ $     | 57         |

| 6.2          | Values of $m$ and $F(m)$                                                                           | 58         |

# LIST OF ALGORITHMS

|     | Conversion to CMSD (Reitwiener's algorithm)                                                                                      | 28   |

|-----|----------------------------------------------------------------------------------------------------------------------------------|------|

| 3.1 | Conversion to CMSD (Retwicted 5 algorithm) conversion to CMSD in $(\lfloor \frac{n}{2} \rfloor + 1)$ steps                       | 32   |

| 4.1 | Algorithm to convert MSD and binary number to CMSD in $(\lfloor \frac{n}{2} \rfloor + 1)$ steps                                  | 34   |

| 4.2 | Search for a pattern like (10)*11. used in Algorithm 4.3                                                                         | 25   |

| 4.9 | Binary to CMSD Conversion Algorithm: 1 Step                                                                                      | . 00 |

| 4.0 | Algorithm for performing addition of CMSD numbers in $(\lfloor \frac{n}{2} \rfloor + 1)$ steps                                   | 38   |

| 4.4 | CMSD addition in 1 step                                                                                                          | 41   |

| 4.5 | CMSD addition in 1 step                                                                                                          |      |

| 4.6 | Algorithm for converting MSD number to 2's complement binary number                                                              | 43   |

|     | in $n$ steps $\dots \dots \dots$ | 4.4  |

| 4.7 | Algorithm to convert CMSD to binary in $( \begin{bmatrix} \frac{1}{2} \end{bmatrix} + 1 )$ steps                                 |      |

| 4.1 | Associative addition algorithm                                                                                                   | 56   |

| 6.1 | Associative addition agorism.                                                                                                    |      |

Chapter

# INTRODUCTION

# 1.1 Fast Computation and Bottlenecks of Traditional Computing System

With the advance of science and technology, the need for processing of large amount of data at high-speed has gradually increased. Data-intensive applications like signal and image processing, weather forecasting and modelling, remote sensing require computational rates equivalent to trillions of operations per second. This high speed-up can only be achieved through parallel processing of information.

Traditional computing system is based on electronic devices and binary number system. One of the main obstacles to the increase of speed in the traditional binary computing system is the generation of carry during arithmetic operation. Any generated carry during binary arithmetic ripples through all the cascaded stages and affects the overall computation. Thus binary computing system implies sequential processing of data and results in a bottleneck in the context of fast computation. Also, high speed computing in the traditional electronic computing system is constrained by the interconnection bottleneck that results in sequential processing of digital information.

There have been efforts to improve the performance of a conventional computer system by reducing the basic cycle time through employing different fast circuits and packaging technique. However, to reach the rate of one trillion operations per second, the system requires a cycle time of less than a picosecond. This cannot be expected from the advances in electronic technology alone, because of the inherent physical limitations. Further speedup, therefore, will have to come through parallelism.

# 1.2 Approaches to Fast Computation

Researchers have made numerous efforts to develop computing systems that can perform fast parallel arithmetic computation. These studies have been carried out mainly in two perspectives. One is the development of computing systems that can process information in parallel [1–7]. The other is the design of number systems that allow limited carry-propagation or completely carry-free arithmetic [2,7–13].

# 1.3 Optical Computing and Symbolic Substitution

Optical signals propagate in parallel, cross each other without interference, have lowest propagation delay of all signals, and can provide a million channel free-space interconnections with primitive lenses. Whereas communication bottleneck forces electronic computers to update the computation state space sequentially, optics allows the whole state to be changed in parallel [14]. This inherent parallelism has led to the development of parallel arithmetic processing techniques in the field of optical computing, that allow higher throughput and faster processing rate than conventional computing system.

Symbolic substitution [2,15,16] is an optical processing technique that has been widely proposed for applications like image processing and arithmetic computation. Basically it is a parallel pattern replacement process through which a set of given input patterns are substituted by a set of output patterns. A symbolic substitution table is used as reference during the substitution process. Considering the representation of operands as input patterns, researchers have proposed the symbolic substitution process for arithmetic processing of numbers [14]. The main advantage of the process is the absence of carry. As a result all output bits are derived in parallel, resulting in the speed up of the computation.

# 1.4 Non-binary Number Systems

Along with the development of parallel processing techniques, researchers have also come up with different non-binary representation of numbers that exploit the parallelism through limited carry-propagation or carry-free arithmetic [8,9,12,14,17,18]. Among these number systems, the Modified Signed Digit(MSD) number system and its variation, the Canonical

Modified Signed Digit(CMSD) number system, have found its wide application in optical computing in the context of symbolic substitution process [2,14]. Both of these systems are weighted radix 2-based number systems, comprising three types of symbols: 0,1&-1. The redundancy in the systems allows carry-free operation and therefore the systems have been most suitable for application in symbolic substitution process.

### 1.5 Objective and Scope of the Thesis

The earlier proposed symbolic substitution processes have concentrated on employing non-binary systems for arithmetic computing. This study, however, concentrates on the design of an arithmetic unit that combines the parallelism of the symbolic substitution process with the flexibility of binary system for data-intensive computing. Addition is the basic operation involved in any arithmetic computation and speeding up addition will result in speeding up the whole arithmetic process. So the focus has been mainly on the development of an adder that operates with binary numbers at its interface; however, employs the symbolic substitution technique for its processing. The idea was to convert the given binary operands to a non-binary representation, apply symbolic substitution technique for their processing, and finally convert the result to binary notation. For the **CMSD** its capability of unique the system, due to study, representation of numbers and carry-free parallel arithmetic, has been chosen as the intermediate non-binary representation. The focus has been the development of symbolic substitution tables and algorithms for all the phases involved like: conversion of binary to the non-binary representation, processing of the numbers and finally conversion of the non-binary representation to binary representation.

In any symbolic substitution process, there are two basic operations involved: the recognition of input patterns and the substitution of these patterns. A number of optical hardware systems for these operations have already been proposed [3,6,7,19]. We have used in this study a simplified version of such a system as presented by Louri [6,19]. This study, however, mainly concentrates on developing the symbolic substitution tables and algorithms involved in the proposed addition unit, rather than on designing the corresponding hardware.

An important factor in the context of symbolic substitution is the required number of substitution steps. The thesis presents a set of symbolic substitution tables and algorithms that require much less substitution steps than any earlier corresponding schemes. Another issue the study concentrates on is the development of a symbolic substitution based

approach for associative addition of binary numbers. Such an algorithm can be employed in arithmetic computation, like multiplication, where associative addition of a set of numbers is an integral process.

# 1.6 Organization of the Thesis

The thesis has been organized in different chapters, with each chapter discussing different aspects of the study. The areas covered by different chapters are briefly as follows:

| Chapter 2 | Provides a literature review of the different methods and number<br>systems that have been proposed in the context of carry-free addition |

|-----------|-------------------------------------------------------------------------------------------------------------------------------------------|

| Chapter 3 | The concept of optical computing, symbolic substitution and related algorithms for arithmetic computation                                 |

| Chapter 4 | A detailed discussion of the outcome of the study; introducing the different symbolic substitution based algorithms and tables            |

| Chapter 5 | A computer analysis of reduction of steps introduced in the algorithms presented in chapter 4                                             |

| Chapter 6 | A novel approach for symbolic substitution based associative addition                                                                     |

| Chapter 7 | The concluding chapter giving some recommendations                                                                                        |

# Chapter 2

# CARRY-FREE ARITHMETIC: A LITERATURE SURVEY

# 2.1 Carry-free Arithmetic

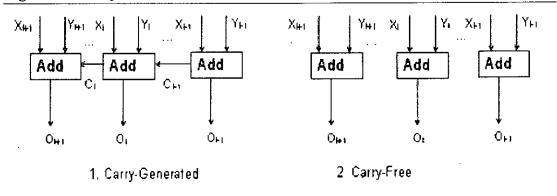

Different researchers have developed a number of methodologies and number systems for the design of parallel carry-free arithmetic unit. Figure 2.1 illustrates what is meant by the term 'carry-free computation'. The left side of the figure depicts an arithmetic unit in which each output bit depends not only on the input bits, but also on the previous stage carries. The right side of the figure illustrates another arithmetic unit where each output bit depends on input bits only, but not on any processing result of previous stages. Thus while the left sided unit implies sequential processing, the right sided unit can derive all the resultant bits in parallel and independent of each other. The development goal of a carry-free addition unit is, hence, the design of a system, similar to the right sided unit of Figure 2.1, that can derive its operational result based on its operands only and not on any previous stage computations.

The efforts made in the context of the implementation of carry-free computation have been mainly in two perspectives. One is the design of computational system that process the digits in the computer representation of the operands in parallel. The other has been the design of number representation that allows the parallel arithmetic computing technique to be applied for carry-free computation. This chapter takes a look at these different techniques and number representation systems that have been proposed in computing literature.

Figure 2.1 Carry-free addition

# 2.2 Carry Lookahead Adder(CLA)

Carry Lookahead Adder(CLA) is an implementation proposed [20] to speed up the addition of two binary numbers. Let  $A_i$  &  $B_i$  be the addend and augend respectively in the ith bit position of a binary full adder. Also let two functions: the carry propagate,  $P_i$  and the carry generate,  $G_i$  be defined as follows:

$$P_i = A_i \oplus B_i$$

$$G_i = A_i \cdot B_i$$

Then the full adder equations can be written as follows:

$$S_i = P_i \oplus C_i$$

$$C_{i+1} = G_i + P_i \cdot C_i$$

Here the '+' symbol denotes logical 'or'.

Using this scheme, the addition of two binary numbers can be performed in parallel. However, the implementation is expensive, since it requires a lot of internal circuitry. For example, for a four-bit adder, the carries for various bit positions are calculated as follows:

$$C_1 = G_1 + P_1C_0$$

$$C_2 = G_2 + P_2G_1 + P_2P_1C_0$$

$$C_3 = G_3 + P_3G_2 + P_3P_2G_1 + P_3P_2P_1C_0$$

$$C_4 = G_4 + P_4G_3 + P_4P_3G_2 + P_4P_3P_2G_1 + P_4P_3P_2P_1C_0$$

while the sum bits can be calculated as follows:

$S_1 = P_1 \oplus C_0$

$S_2 = P_2 \oplus C_1$

$S_3 = P_3 \oplus C_2$

$S_4 = P_4 \oplus C_3$

As can be seen, with the increasing no. of bits, the circuit complexity and the required no. of gates increases. For large no. of input bits, this implementation becomes too expensive. Also, the inherent delay in the internal circuitry affects the computation speed and the circuit virtually becomes a sequential carry-affected adder.

## 2.3 Introduction of Redundancy in Number Systems

The alternative schemes to CLA, that have been proposed, involve the use of number systems with some kind of redundancy in the representation [8,9,11,21]. The redundancy allows multiple encoding for the same number and thus can be utilized for the development of carry-free or limited carry-propagation addition scheme. The next section focuses on some of these number systems, while the subsequent section discusses about the use of these number systems in the context of parallel carry-free addition.

# 2.4 Different Number Systems

Different number systems have been proposed for the computation of arithmetic operations by computers. These number systems may be categorized into two classes:

1. Weighted, where every integer X can be represented as in equation 2.1. Here  $\tau$  is the corresponding base and  $x_i \in \{0, 1, \dots, r-1\}$

$$X = \sum_{i=0}^{n} x_i r^i \tag{2.1}$$

2. Non-weighted, where digits are not assigned any specific weight and the ordering of the digits does not affect the representation.

The most common number systems like binary number system, hexadecimal number system are examples of the weighted number system. The Residue Number system (RNS) is an example of non-weighted number system.

In this section, we focus on the different number systems that have been proposed in computing literature in the context of carry-free parallel arithmetic. An outline of their relative advantages and disadvantages in this respect is also provided.

#### 2.4.1 Redundant Number System

Avizienis [8] introduced the Redundant Number system. Formally, Redundant Number System is a redundant representation of a number that operates as follows [8, 22]:

For any radix,  $r \geq 2$ , a signed digit integer number,  $X = (x_{n-1}, \ldots, x_1, x_0)$ , represented with n digits, has the algebraic value,  $X = \sum_{i=0}^{n-1} x_i r^i$ .

Here each digit  $x_i$  assumes its value in the digit set,

$$S = \{-\alpha, -\alpha + 1, \dots, -1, 0, 1, \dots, \alpha - 1, \alpha\}$$

The cardinality of the set S is  $2\alpha + 1$  and maximum digit magnitude,  $\alpha$  must satisfy,

$$\operatorname{ceil}\left(\frac{r-1}{2}\right) \le \alpha \le r-1$$

here ceil(x) denotes [x]

The redundant number system is also known as signed-digit number system in computing literature [8,23].

A significant property of the redundant representation is that it allows limited carry-propagation or carry-free addition. This capability arises due to the redundancy of extra digits and the capability of representing number in more than one way.

Different variations of the redundant number system have been proposed in literature [2,9, 10, 12, 18, 21]. However, the Modified Signed Digit and Canonical Modified Signed Digit number systems have found the most popularity among the researchers in the context of carry-free addition [1, 2, 14, 24–26].

## 2.4.2 Modified Signed Digit Number System

The Modified Signed Digit(MSD) number system is a redundant number system with  $\alpha = 1$ . An *n*-digit Modified Signed Digit (MSD) number can be represented as:

$$X = \sum_{i=0}^{n-1} x_i 2^i \tag{2.2}$$

where each digit  $x_i \in \{0, 1, \underline{1}\}$ . Here  $\underline{1}$  denotes -1.

MSD number system is thus a redundant binary number system employing the symbols  ${}^{'}0', {}^{'}1'$  and  ${}^{'}-1'$ . The MSD number system allows carry-free and borrow-free arithmetic operations. It is essentially a superset of the binary number system. The inclusion of the extra symbol  $\underline{1}$  [denoting  ${}^{'}-1'$ ] makes the provision for parallel arithmetic operations.

A number in MSD number system is represented as a string of symbols, members of which are from the set  $\{0,1,\underline{1}\}$ . For example,

$$5 = 1 \quad 0 \quad 1 = 4 \quad + \quad 0 \quad + \quad 1$$

$-5 = \underline{1} \quad 0 \quad \underline{1} = -4 \quad + \quad 0 \quad + \quad -1$

However, representation of a number in MSD system is not unique. For example the number 11 [using 6 bits] can be represented as any of the following ways:

$\begin{array}{rcl}

11 & = & 0 \ 0 \ 1 \ 0 \ 1 \ 1 \\

11 & = & 0 \ 1 \ 0 \ \underline{1} \ 0 \ \underline{1}

\end{array}$

$11 = 1 \underline{1} \underline{1} 0 1 1$

This non-uniqueness of MSD number system is one of its disadvantages. However, a specialization of this number system, known as Canonical Modified Signed Digit (CMSD) number system, has been proposed [2, 26] that gives unique representation for each number.

# 2.4.3 Canonical Modified Signed Digit Number System

Canonical Modified Signed Digit (CMSD) number system is essentially a variant i.e. a recoding of the general Signed Digit number system. The property that is maintained in the representation is that no two consecutive digits are non-zero.

Formally, an n-digit Canonical Modified Signed Digit number can be represented as:

$$X = \sum_{i=0}^{n-1} x_i 2^i \tag{2.3}$$

where each digit  $x_i \in \{0, 1, \underline{1}\}$  and  $x_i \cdot x_{i-1} = 0; \forall i = 1 \dots n-1$

The representation of number 11 [using 6 bits], for example, in CMSD is as follows:

$$11 = 0 1 0 1 0 1$$

The advantage of this number system is that representation is unique. Also, the sparseness of non-zero digits in the representation minimizes the number of addition and subtraction operations required in arithmetic computation. Canonic Modified Signed Digit (CMSD) is thus a good candidate for appliance in parallel computing architecture and fast processing.

#### 2.4.4 Residue Number System

Residue Number System(RNS) [27,28] is a non-weighted number system that allows carry-free addition and borrow-free subtraction. It uses positional bases that are relatively prime to each other. For example, using 2, 3 and 7 as the prime modula, we can represent the following numbers as shown:

| Number | Bases: | 2, | 3, | 7 |

|--------|--------|----|----|---|

| 0      |        | 0, | 0, | 0 |

| 7      |        | 1, | 1, | 0 |

| 11     |        | 1, | 2, | 4 |

Here the digit for each position is obtained by the modulus of the number to be represented divided by the prime factor for that position. The representation of '11' is thus obtained as:

$$11 = 1 (11 \mod 2), 2 (11 \mod 3), 4 (11 \mod 7)$$

The dynamic range, DR, of the number system is the product of the prime moduli. The dynamic range for the example is thus 0 to 41. Negative numbers can also be accommodated by designating DR/2 numbers as positive and the rest as negative. For example, using 2,3,7 as the prime moduli and employing Signed RNS, the following numbers may be represented as follows:

$$\begin{array}{rcl} \mathbf{11} & = & 1, & 2, & 4 \\ \mathbf{\cdot 11} & = & 1, & 1, & 3 \end{array}$$

The addition and subtraction are performed in digit by digit basis. The result of operation in each position is then represented as the modulus of the resultant divided by the prime factor at that position. The following examples (using 3,5,7 as the prime moduli) illustrate the operation:

| 21 + 13 | 17 - 38 |

|---------|---------|

| 0, 1, 0 | 2, 2, 3 |

| +       | +       |

| 1, 3, 6 | 1, 2, 4 |

| 1, 4, 6 | 0, 4, 0 |

| =34     | =-21    |

Residue Number system thus allows carry-free arithmetic. However, it is more difficult to implement due to the fact that the system computation elements require a different set of prime-moduli-based logic elements for each arithmetic operation. It is thus a rather complex system.

#### 2.4.5 Other Variations of Redundant Number System

The redundant signed-digit number representations is of symmetrical type in the sense that the allowed digit range is from  $-\alpha$  to  $\alpha$ , for some value of  $\alpha$  satisfying equation 2.4.1. It is now referred to as the Ordinary Signed Digit (OSD) number system in contemporary literature [12].

An extension of this system was later proposed and is known as the Generalized Signed Digit (GSD) number system [9,21]. The GSD number system for radix  $\tau > 1$  has the digit set  $-\alpha, ..., -1, 0, 1, ..., \beta$ , where  $\alpha \geq 0$  and  $\beta \geq 0$ . The system has been proposed for use in schemes like carry-save adders and carry-skip adders [17].

Another variation of signed digit number system, that has been recently proposed, is the Asymmetric High-radix Signed Digit (AHSD) number system [12]. The radix-r asymmetric high-radix signed-digit (AHSD) number system, denoted AHSD(r), is a positional weighted number system with the digit set S = -1, 0, ..., r - 1, where r > 1. The AHSD number

system is a minimally redundant system with only one redundant digit in the digit set. An n-digit number X in AHSD(r) is represented as

$$X = (x_{n-1}, x_{n-2}, ..., x_0)$$

(2.4)

where  $x_i \in S$  for i = 0, 1, ..., n - 1, and S = -1, 0, 1, ..., r - 1 is the digit set of AHSD(r). The value of X can be represented as,  $X = \sum_{i=0}^{n-1} x_i r^i$ .

#### 2.4.6 Double Base Number System

The Double Base Number System (DBNS) [11] is a 2-D representation of numbers with 2 and 3 used as bases and using 0 and 1 as the only allowable digits. The representation of a given number x is of the form:

$$X = \sum_{i,j} x_{i,j} 2^{i} 3^{j}; x_{i,j} \epsilon \{0, 1\}$$

(2.5)

A simple geometric interpretation of the system may be denoted as in the following table:

|       | 20          | <b>2</b> ¹ | 2 <sup>2</sup> | 23        |

|-------|-------------|------------|----------------|-----------|

| 30    | $x_{0,0}$   | $x_{0,1}$  | $x_{0,2}$      | $x_{0,3}$ |

| $3^1$ | $x_{1,0}$   | $x_{1,1}$  | $x_{1,2}$      | $x_{1,3}$ |

| $3^2$ | $x_{2,0}$   | $x_{2,1}$  | $x_{2,2}$      | $x_{2,3}$ |

| $3^3$ | $ x_{3,0} $ | $x_{3,1}$  | $x_{3,2}$      | $x_{3,3}$ |

For example, one representation of the number '11' is as follows:

|                | 20 | 21 | 2 <sup>2</sup> | 23 |

|----------------|----|----|----------------|----|

| 3 <sup>0</sup> | 0  | 0  | 0              | 1  |

| $3^1$          | 1  | 0  | 0              | 0  |

| 3 <sup>2</sup> | 0  | 0  | 0              | 0  |

| 33             | 0  | 0  | 0              | 0  |

The DBNS system have a sparseness in its representation and is thus a suitable number system for application in parallel computing architecture. However, we require much

more storage for the representation of a DBNS number than its binary notation. Also, the representation of a number is not unique.

# 2.5 Carry-free Addition Schemes

A number of schemes, based on the aforementioned number systems, have been designed. These schemes, described under different titles in computing literatures like carry-skip (single- or multilevel) adder, carry-select adder, carry-save adder and hybrid adder [5,9, 17,18,29], deal with the generation of carry by limiting carry propagation to within a small number of bits or detecting the end of propagation; or speeding up propagation via some lookahead scheme or eliminating carry propagation altogether. Several digital and VLSI systems have been proposed on the basis of these schemes [9,17,29,30].

Another arena, where these non-binary number systems have found their application in the context of carry-free arithmetic, is the symbolic substitution process in optical computing. Detailed description of the process has been presented in the next chapter.

# 2.6 Choice of Number System in Carry-free Addition Scheme

Each number system has its advantages and disadvantages in the context of a carry-free arithmetic scheme. Usually the questions that are asked while selecting a number system are as follows:

- 1. Does the number system represent every number? (completeness)

- 2. Are the representation of the numbers unique for every number? (non-ambignous)

- 3. Does the number system give any advantage in employing arithmetic operations and other operations like sign detection and comparison?

Not all advantages can be gained from employing a single number system. Binary system, for example, is the simplest to implement. But it does not allow carry free operation. Redundant number system, on the other hand allows carry free arithmetic. But it is harder to implement and the representation is not unique. The same problem holds for other variants of redundant number system, residue number system and double base

number system as well. Hence no single number system is the best choice and the choice solely depends on the application and algorithm to be implemented.

The MSD number system (which is a subset of the redundant number system) and its variant the CMSD number system, though having an extra digit than binary, allow carry-free arithmetic and thus are suitable for parallel computing architecture. It is used specially in optical computing where polarization and other properties of light may be utilized to denote the three different states as required in the representation [14]. Thus the symbolic substitution based architectures have always concentrated on using these trinary systems [2,16,19,31] and in this thesis also, focus will be made on the utilization of these trinary number systems.

# Chapter 3

# SYMBOLIC SUBSTITUTION AND ARITHMETIC COMPUTATION

# 3.1 Optics as a Backbone of Fast Computation

The speed of conventional computers is mainly constrained by the interconnection bottleneck and inherent delay within the electronic devices. So efforts have been made to achieve speedup by miniaturizing electronic components to a very small micron-size scale so that those electrons need to travel only very short distances within a very short time. This goal of improving computer speed has thus resulted in the development of the Very Large Scale Integration (VLSI) technology with smaller device dimensions and greater complexity. However the VLSI technology is approaching its fundamental limits in the sub-micron miniaturization process. To meet the demand of high speed processing, we therefore need to find alternative fast computing system.

Optical interconnections and optical integrated circuits may provide a way out of the limitations to computational speed and complexity inherent in conventional electronics. They are immune to electromagnetic interference and free from electrical short circuits. They have low-loss transmission and provide large bandwidth; i.e. multiplexing capability, capable of communicating several channels in parallel without interference. They are capable of propagating signals within the same or adjacent fibers with essentially no interference or cross-talk.

Another advantage of optical methods over electronic ones for computing is that optical data processing can be done much easier in parallel than can be done in electronics. Parallelism is the capability of the system to execute more than one operation

simultaneously. Electronic computer architecture is, in general, sequential, where the instructions are implemented in sequence. This implies that parallelism with electronics is difficult to construct. Parallelism in conventional electronic computing system has focussed mainly on the use of multiple processors in conjunction with the computer memory to enhance the speed. However, the effect of using a large number of processors are not necessarily an increase of computational speed, but could be in fact detrimental. This is because as more processors are used, there is more time lost in communication. On the other hand, using a simple optical design, an array of pixels can be transferred simultaneously in parallel from one point to another. Thus optical system that works simultaneously with an array of numbers, represented using some kind of spatial arrangement of pixels, and derive the arithmetic computation in parallel has been developed based on this inherent parallelism of optics [14, 19].

### 3.2 Symbolic Substitution

Symbolic substitution [14, 19, 31–35] technique was developed as an optical computing method to take advantage of the optical parallelism for 2-D image processing and arithmetic computation. At the heart of the process is a pattern replacement operation, defined by a symbolic substitution rule, that converts some given patterns to some desired patterns. The substitution process, therefore, comprises two basic phases. In the first phase, the recognition phase, the inputs are scanned for the location of desired input patterns. In the second phase, the substitution phase, the desired output pattern is written into all the locations determined by the previous phase.

# 3.3 Different Symbolic Substitution Methods

In order to process an information by a device, the data has to be encoded with a physical quantity that the device can process. While in electronic computers information is encoded with an electrical quantity (electrical voltage or current), in optics the information is encoded with an optical quantity (optical intensity, polarization, amplitude or phase). Optical intensity and the optical polarization are the two optical quantities that have been used extensively in optical computing in the context of symbolic substitution process. And according to the type of encoding, the symbolic substitution methods have been classified into two categories: intensity coded symbolic substitution (ICSS) [14, 33, 34] and polarization coded symbolic substitution (PCSS) [36]. Another method, symbolic

substitution using shadow-casting, employs both ICSS and PCSS [1,35].

### 3.4 Intensity Coded Symbolic Substitution

Intensity coded symbolic substitution (ICSS) uses the information coded with the optical intensity. The basic units in this coding are pixels which can be either transparent or opaque. A pixel or certain spatial combination of pixels represents a certain value of the encoded information.

#### 3.4.1 Dual-rail Encoding

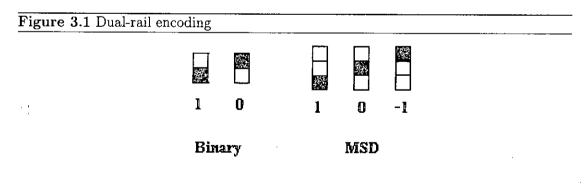

The simplest way of encoding an information in binary form is to attach the logical one to the transparent pixel and the logical zero to the opaque pixel. However, optical computing uses a scheme termed as Dual-rail Encoding [2,14] that uses more than one pixel to represent information. In dual-rail encoding a spatial arrangement of the transparent and opaque pixels is treated as a logical one and another arrangement is treated as logical zero as shown in figure 3.1. The dark and white pixels, in this figure, indicate the opaque and the transparent pixels respectively. As has been illustrated, in dual-rail encoding, pixels are arranged into a two-pixel vertical bar, where the logical one is represented by the transparent pixel in the upper position and by the opaque pixel in the lower position and logical zero is represented vice versa. Similar spatial arrangement of the transparent and opaque pixels are also used to represent 1, 0 and -1 in the MSD representation.

#### 3.4.2 Symbolic Substitution Process

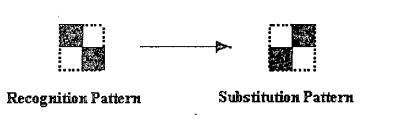

Symbolic substitution operation is characterized by the substitution rule. Figure 3.2 shows an example substitution rule that will be used to explain the method. The pattern at the left is the recognition pattern that has to be located in the input array. The pattern at the right is the substitution pattern, which has to replace the located pattern.

Figure 3.2 Substitution rule

#### Recognition Phase

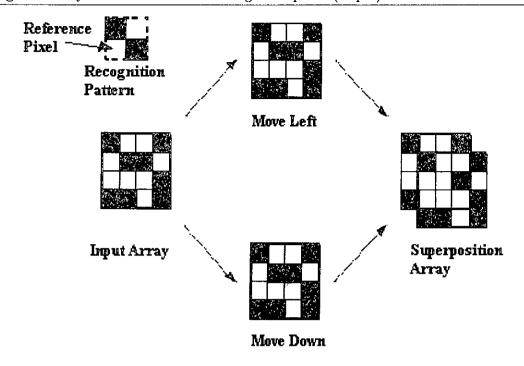

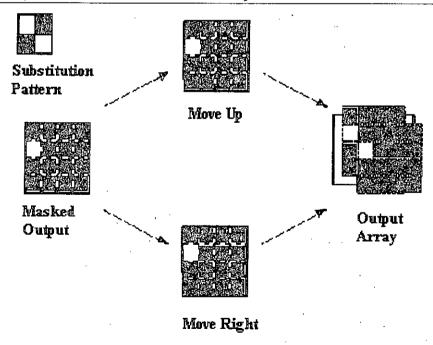

In the recognition phase all occurrences of a recognition pattern are located. First a pixel of the recognition pattern is defined as a reference pixel. This reference pixel will determine the position of the recognition pattern in a masked array, which is a recognition phase output array. Figure 3.3 shows the recognition pattern and the reference pixel, which is the lower left pixel of the 2 X 2 square surrounding the pattern. Naturally, any other choice is also possible. The pixels in the input or output patterns are also referred to as 'pels' and we will use this term for the subsequent discussion. The first step in the recognition phase is to produce as many replicas of the input array as there are significant(opaque) pels in the left hand side (LHS) of the rule. For the demonstrated example, the number is two. One replica is associated with the upper left pixel and the other replica with the lower right pixel. The significant pels are then shifted onto the reference pixel. For the example, the replica associated with the upper left pel is shifted one pixel down and the replica associated with the lower right pel is shifted one pixel to the left. These two replicas are then superimposed to produce the superposition array.

The second step is an operation of inversion (Figure: 3.4). All dark pixels are inverted onto bright pixels and vice versa.

Figure 3.3 Symbolic substitution: Recognition phase (step 1)

Figure 3.4 Symbolic substitution: Recognition phase (step 2)

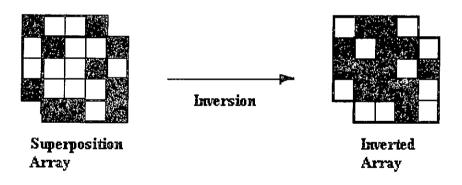

The final step in the recognition phase (Figure: 3.5) is an operation of masking. The mask selects only the pels whose positions in the inverted array coincide with positions of holes in the mask. The output of this operation is an array with the bright pels determining the occurrences of the recognition pattern. The remaining pels are dark.

Figure 3.5 Symbolic substitution: Recognition phase (step 3)

#### Substitution Phase

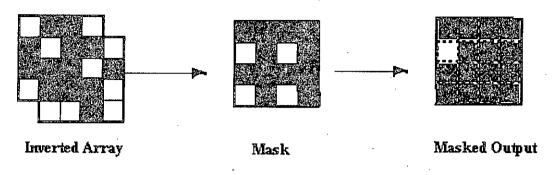

The first step in the substitution phase is to create as many copies of the masked output as there are bright pels in the substitution pattern. As shown in Figure 3.6, the substitution pattern, for the example, contains two bright pels and therefore two copies are made. To scribe the substitution pattern, one copy is shifted to the top and the other copy to the right. The copies are then superimposed to obtain an output array.

Figure 3.6 Symbolic substitution: Substitution phase

#### 3.4.3 Multiple-rules Symbolic Substitution Process

In a typical symbolic substitution process, a set of symbolic substitution rules, stored in the storage element of the unit, are applied to detect a set of input patterns and scribe a set of output patterns. The unit consists of pattern recognizer and pattern substituter for each set of rules (Figure: 3.7). The pattern splitter splits the input for the recognition phase, while the pattern combiner combines the substituted patterns at the output.

MINIMUM TO THE REAL PROPERTY OF THE PERSON O Pattern Rule 1 Pattern Recognizer 1 Substitutor 1 Pattern Rule 2 Pattern Substitutor 2 Recognizer 2 Pattern. Pattern Splitter Combiner Pattern Pattern Rule 3 Recognizer 3 Substitutor 3 Pattern Rulen Pattern Recognizer n Substitutor n Input Output

Figure 3.7 Multiple substitution rules

# 3.5 Polarization Coded Symbolic Substitution

Polarized coded symbolic substitution (PCSS) is another implementation of symbolic substitution logic. The basic feature of this method is that an information is coded in terms of polarization. The input data array in PCSS looks like in ICSS, but with one exception. Instead of bright and dark pels the input array consists of pels containing horizontally or vertically polarized light. In essence, the basic principle of PCSS is the same as in ICSS and consists of replication, shifting, superimposing, inverting and masking operations as in the ICSS. However, PCSS offers four logic values as compared to two logic

Figure 3.8 Block architecture of a symbolic substitution unit

values in ICSS. The states 'zero' and 'one' have the same meaning as in ICSS. In addition PCSS appears allows two new logic states, that after Brenner [36], are referred to as the 'never match' and 'always match' states. The state 'never match' can be used to inhibit the recognition, whereas the state 'always match' can serve as a wild card or don't care condition. Thus PCSS allows the implementation of complex symbolic substitution rules.

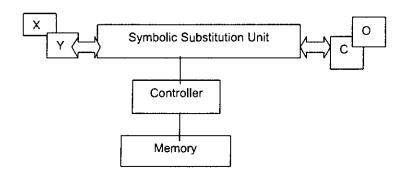

# 3.6 Basic Symbolic Substitution Unit

Figure 3.8 depicts the basic block architecture of a symbolic substitution unit. The inputs to the system are the variables X & Y. C is an auxiliary variable and O is the output variable. The symbolic substitution rules are stored in memory, while the controller controls the recognition and substitution phase. Inputs, X & Y are scanned for recognition patterns during the recognition phases. During the substitution phase, the controller substitutes these patterns with the substitution patterns, defined by the symbolic substitution rules, at the output O. Some applications require multiple substitution steps. In these cases, the auxiliary variable C is used as another output during the substitution phase. For the subsequent iteration, the values of O and C are copied back to X and Y and the symbolic substitution process is repeated with the new values of X and Y.

# 3.7 Symbolic Substitution and Arithmetic Computation

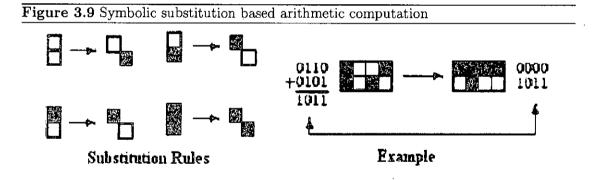

Symbolic substitution can be used for implementing arithmetic operations [2,6,14,31,33,36]. The idea is to consider the representation of the operands as input patterns and the resultant as the output patterns. The symbolic substitution rules define the corresponding arithmetic operation. As an example, figure 3.9 illustrates an addition following the rules: 1+1=10, 1+0=0+1=1, 0+0=0. ICSS process has been used for the illustration and a bright pixel, in the figure, represents the logical one, while a dark pixel represents the logical zero. The symbolic substitution rules corresponding to the addition operation have been shown at the left side of the figure. The right side shows the addition of two numbers (0110) and (0101), the addition of which equals (1011). As has been shown, the symbolic substitution process simply detects the desired input patterns in the operands and substitutes these patterns with the substitution rule-defined patterns at the output. There are four substitution rules and are applied as many times as there are bits in the numbers (in this example four times). Obviously, this addition can also be implemented with dual-rail coded or polarization coded numbers provided they use the corresponding substitution rules.

# 3.8 Symbolic Substitution Based Computation Algorithms