# DESIGN AND ANALYSIS OF INTEGRATED ANTENNA ON SI FOR ON-CHIP WIRELESS INTERCONNECT

A Dissertation submitted to the Department of Electrical and Electronic Engineering of Bangladesh University of Engineering and Technology

> in partial fulfillment of the Requirement for the Degree of

MASTER OF SCIENCE IN ELECTRICAL AND ELECTRONIC ENGINEERING

By

DEPARTMENT OF ELECTRICAL AND ELECTRONIC ENGINEERING BANGLADESH UNIVERSITY OF ENGINEERING AND TECHNOLOGY 2006 The thesis titled "Design and Analysis of Integrated Antenna on Si for On-chip Wireless Interconnect" submitted by Nasrin Sultana, Roll No.: 040406219P, Session: April 2004 has been accepted as satisfactory in partial fulfillment of the requirement for the degree of MASTER OF SCIENCE IN ELECTRICAL AND ELECTRONIC ENGINEERING on 17.10.2006

#### **BOARD OF EXAMINERS**

1.1 Krow

Dr. A.B.M. Harun Ur-Rashid

Professor

Department of Electrical and Electronic Engineering BUET, Dhaka-1000, Bangladesh.

2.1

Dr. Satya Prasad Majumder Professor and Head Department of Electrical and Electronic Engineering BUET, Dhaka-1000, Bangladesh.

RL 3.1

Dr. Pran Kanai Saha

Professor

Department of Electrical and Electronic Engineering BUET, Dhaka-1000, Bangladesh.

odder 4.1

Dr. Jiban Podder

Professor Department of Physics BUET, Dhaka-1000, Bangladesh. Chairman (Supervisor)

Member (Ex-officio)

Member

Member

(External)

# **DECLARATION**

It is hereby declared that this thesis or any part of it has not been submitted elsewhere for the award of any degree or diploma.

Signature of the student

Novin Sub

(Nasrin Sultana)

# **DEDICATION**

To my parents.

iii

# **CONTENTS**

| Сна  | APTER 1 INTRODUCTION1                                     |

|------|-----------------------------------------------------------|

| 1.1  | Background1                                               |

| 1.2  | Interconnect Problem1                                     |

| 1.3  | Impact of Interconnect Problem2                           |

| 1.4  | Evolution of Interconnect technologies4                   |

| 1.5  | Different Solution of Interconnection Problems-The wiring |

|      | bottleneck                                                |

| 1.   | 5.1 Multi layer Interconnects                             |

| 1.   | 5.2 Cu Interconnect                                       |

| 1.6  |                                                           |

|      | Interconnect                                              |

| 1.6. | 1 3-D integration10                                       |

|      | 2 Optical interconnects                                   |

|      | 3 RF/wireless interconnect                                |

| 1.0. |                                                           |

| 1./  | Advantages of Wireless Interconnect over Optical          |

|      | Interconnect                                              |

| 1.8  | Research Outline                                          |

| 1.9  | Thesis Layout19                                           |

30

| <b>A</b> N'                                                        | ΓΕΝΝΑ21                                                                                                                                                                                                                                                                                                                                                                                                                 |

|--------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 2.1                                                                | Basic Antenna Theory2                                                                                                                                                                                                                                                                                                                                                                                                   |

|                                                                    | .1.1 Dipole Antenna                                                                                                                                                                                                                                                                                                                                                                                                     |

|                                                                    | .1.2 Monopole Antenna                                                                                                                                                                                                                                                                                                                                                                                                   |

| 2                                                                  | .1.3 Radiation patterns                                                                                                                                                                                                                                                                                                                                                                                                 |

| 2.2                                                                | The Scattering Matrix                                                                                                                                                                                                                                                                                                                                                                                                   |

| 2.3                                                                | Friis Transmission Formula                                                                                                                                                                                                                                                                                                                                                                                              |

|                                                                    |                                                                                                                                                                                                                                                                                                                                                                                                                         |

| Сн                                                                 | APTER 3 THEORETICAL ANALYSIS OF THE                                                                                                                                                                                                                                                                                                                                                                                     |

| wo                                                                 | RK                                                                                                                                                                                                                                                                                                                                                                                                                      |

|                                                                    |                                                                                                                                                                                                                                                                                                                                                                                                                         |

|                                                                    |                                                                                                                                                                                                                                                                                                                                                                                                                         |

| 3.1                                                                | Work outline                                                                                                                                                                                                                                                                                                                                                                                                            |

|                                                                    | Work outline    31      Theoretical gain of a Dipole Antenna    32                                                                                                                                                                                                                                                                                                                                                      |

| 3.2                                                                | Theoretical gain of a Dipole Antenna                                                                                                                                                                                                                                                                                                                                                                                    |

| 3.2                                                                | Theoretical gain of a Dipole Antenna                                                                                                                                                                                                                                                                                                                                                                                    |

| 3.2<br>3.3                                                         | Theoretical gain of a Dipole Antenna                                                                                                                                                                                                                                                                                                                                                                                    |

| 3.2<br>3.3<br>3.4                                                  | Theoretical gain of a Dipole Antenna.       .32         Effect of variation of Resistivity and antenna distance on the analytical gain of the antenna.       .34         Description of the Analytical Model       .34                                                                                                                                                                                                  |

| 3.2<br>3.3<br>3.4                                                  | Theoretical gain of a Dipole Antenna                                                                                                                                                                                                                                                                                                                                                                                    |

| <b>3.2</b><br><b>3.3</b><br><b>3.4</b><br>3.3                      | Theoretical gain of a Dipole Antenna.       .32         Effect of variation of Resistivity and antenna distance on the analytical gain of the antenna.       .34         Description of the Analytical Model       .35         .4.1 Estimation of the entire system as T-model.       .35         .4.2 Antenna Modeling.       .36                                                                                      |

| <b>3.2</b><br><b>3.3</b><br><b>3.4</b><br>3.<br>3.<br>3.           | Theoretical gain of a Dipole Antenna.32Effect of variation of Resistivity and antenna distance on the<br>analytical gain of the antenna.34Description of the Analytical Model.35.4.1 Estimation of the entire system as T-model.35.4.2 Antenna Modeling.36.4.3 Transmission Medium Modeling.38                                                                                                                          |

| <b>3.2</b><br><b>3.3</b><br><b>3.4</b><br>3.3<br>3.3<br><b>3.5</b> | Theoretical gain of a Dipole Antenna.32Effect of variation of Resistivity and antenna distance on the<br>analytical gain of the antenna.34Description of the Analytical Model35.4.1 Estimation of the entire system as T-model.35.4.2 Antenna Modeling.36.4.3 Transmission Medium Modeling.38The problem in using Dipole Antenna with Upper Metal Layer.38                                                              |

| 3.2<br>3.3<br>3.4<br>3.3<br>3.5<br>3.6                             | Theoretical gain of a Dipole Antenna.32Effect of variation of Resistivity and antenna distance on the<br>analytical gain of the antenna.34Description of the Analytical Model35.4.1 Estimation of the entire system as T-model.35.4.2 Antenna Modeling.36.4.3 Transmission Medium Modeling.38The problem in using Dipole Antenna with Upper Metal Layer.38The improved Integrated Antenna39                             |

| 3.2<br>3.3<br>3.4<br>3.<br>3.3<br>3.5<br>3.6<br>3.7                | Work outline31Theoretical gain of a Dipole Antenna32Effect of variation of Resistivity and antenna distance on the<br>analytical gain of the antenna34Description of the Analytical Model354.1 Estimation of the entire system as T-model354.2 Antenna Modeling364.3 Transmission Medium Modeling38The problem in using Dipole Antenna with Upper Metal Layer39Analytical gain of Monopole antenna40Discussion41        |

| 3.                                                                 | Theoretical gain of a Dipole Antenna32Effect of variation of Resistivity and antenna distance on the<br>analytical gain of the antenna34Description of the Analytical Model354.1 Estimation of the entire system as T-model354.2 Antenna Modeling364.3 Transmission Medium Modeling38The problem in using Dipole Antenna with Upper Metal Layer38The improved Integrated Antenna39Analytical gain of Monopole antenna40 |

| 3.2<br>3.3<br>3.4<br>3.<br>3.3<br>3.5<br>3.6<br>3.7                | Theoretical gain of a Dipole Antenna.32Effect of variation of Resistivity and antenna distance on the<br>analytical gain of the antenna.33Description of the Analytical Model .33.4.1 Estimation of the entire system as T-model.33.4.2 Antenna Modeling.34.4.3 Transmission Medium Modeling.34The problem in using Dipole Antenna with Upper Metal Layer.35Analytical gain of Monopole antenna.40                      |

| CHAPTER 4 | <b>RESULTS AND</b> | DISCUSSIONS | 42 |

|-----------|--------------------|-------------|----|

|-----------|--------------------|-------------|----|

:

ł

| 4.1   | Work summary42                                                                   |

|-------|----------------------------------------------------------------------------------|

| 4.2   | Simulated Device structure43                                                     |

| 4.2   | 2.1 Dipole antenna— s-matrix data extraction44                                   |

| 4.2   | 2.2 Dipole antenna— z-matrix data extraction45                                   |

| . 4.2 | 2.3 Monopole antenna— s-matrix data extraction45                                 |

| 4.3   | Simulation Method46                                                              |

| 4.4   | Comparison between the Simulation results and analytical data of                 |

|       | $S_{21}$ – with and without upper metal layer in case of Dipole                  |

|       | antenna47                                                                        |

| 4.5   | The effect of variation in Resistivity on S <sub>21</sub> of the dipole antennas |

|       | comparison between simulated and analytical data49                               |

| 4.6   | The effect of variation in distance between the dipole antennas on               |

|       | $S_{21}$ — comparison between simulated and analytical                           |

|       | data51                                                                           |

| 4.7   | Comparison between the simulated circuit parameters and the                      |

|       | Analytical parameters of the Antenna model                                       |

| 4.8   | Dipole Antenna Model at different distance                                       |

| 4.9   | Transmission line model at different distance                                    |

| 4.10  | Comparison between the Simulation s-matrix and s-matrix of the                   |

| Ì     | proposed model                                                                   |

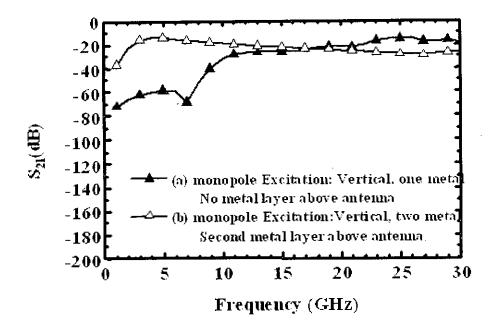

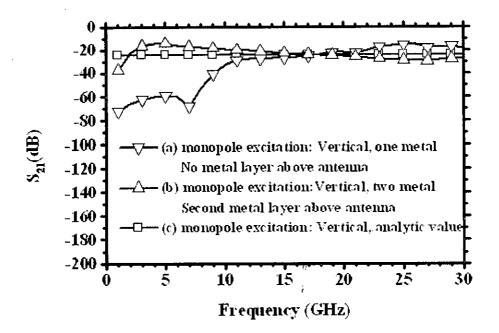

| 4.11  | Comparison between simulated results and analytical data of $S_{\rm 21}$ –       |

|       | with and without upper metal layer in case of Monopole                           |

| •     | Antenna                                                                          |

| 4.12  | Conclusion61                                                                     |

vi

¢.;

| Сн   | APTER 5 CONCLUSION | 63 |

|------|--------------------|----|

|      | Review of the work | 63 |

| 5.2  | Future work        | 64 |

| Refe | erence             | 65 |

# LIST OF FIGURES

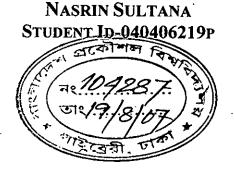

| 1.1                                                                                                                | Projected Clock Frequency4                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

|--------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

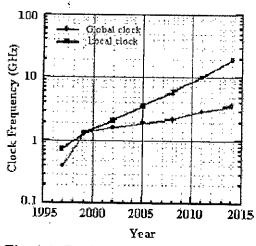

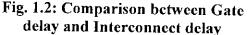

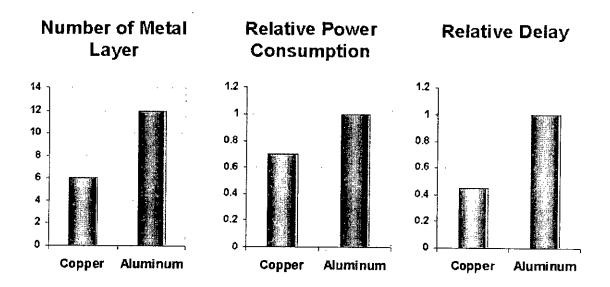

| 1.2                                                                                                                | Comparison between Gate delay and Interconnect delay4                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| 1.3                                                                                                                | Superiority of Cu/low-k interconnection over Al/ SiO <sub>2</sub> interconnection8                                                                                                                                                                                                                                                                                                                                                                                                      |

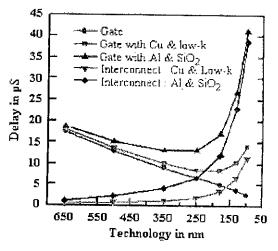

| 1.4                                                                                                                | Typical gate and interconnect delays as a function of feature sizes. The                                                                                                                                                                                                                                                                                                                                                                                                                |

|                                                                                                                    | interconnect delay assumes an optimally repeated line and includes the delay due                                                                                                                                                                                                                                                                                                                                                                                                        |

|                                                                                                                    | to the repeaters                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

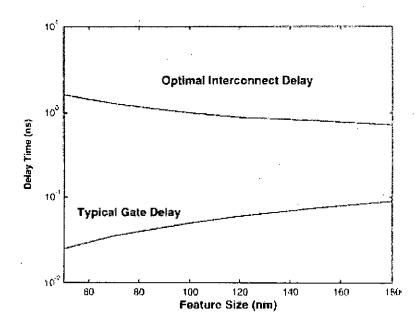

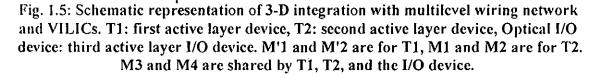

| 1.5                                                                                                                | Schematic representation of 3-D integration with multilevel wiring network and                                                                                                                                                                                                                                                                                                                                                                                                          |

|                                                                                                                    | VILICs. T1: first active layer device, T2: second active layer device, Optical I/O                                                                                                                                                                                                                                                                                                                                                                                                      |

|                                                                                                                    | device: third active layer I/O device. M'1 and M'2 are for T1, M1 and M2 are for                                                                                                                                                                                                                                                                                                                                                                                                        |

|                                                                                                                    | T2. M3 and M4 are shared by T1, T2, and the I/O device10                                                                                                                                                                                                                                                                                                                                                                                                                                |

| 1.6                                                                                                                | Optical Interconnect Technology on Si                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| 1.7                                                                                                                | Proposed two groups of Optical Interconnect13                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| 1.8                                                                                                                | Integrated RF interconnect channel concept16                                                                                                                                                                                                                                                                                                                                                                                                                                            |

|                                                                                                                    |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

|                                                                                                                    |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

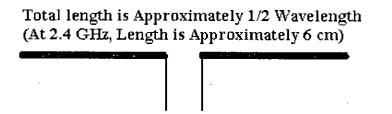

| 2.1                                                                                                                | Basic Dipole                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| 2.1<br>2.2                                                                                                         | Basic Dipole                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

|                                                                                                                    |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

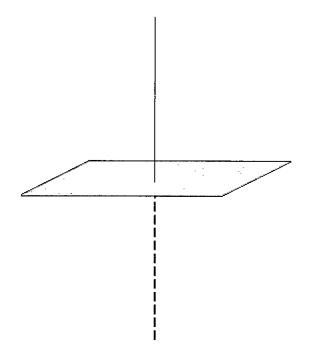

| 2.2                                                                                                                | Monopole above a ground plane, showing the "Mirror" Antenna                                                                                                                                                                                                                                                                                                                                                                                                                             |

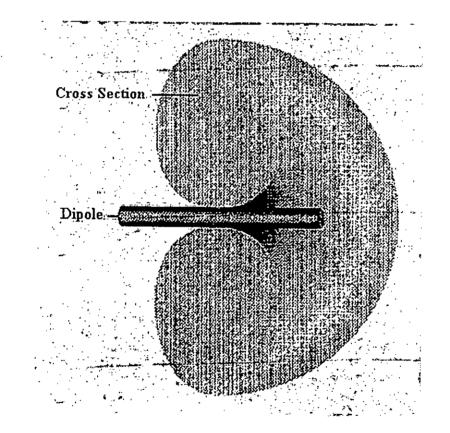

| 2.2<br>2.3                                                                                                         | Monopole above a ground plane, showing the "Mirror" Antenna                                                                                                                                                                                                                                                                                                                                                                                                                             |

| 2.2<br>2.3<br>2.4                                                                                                  | Monopole above a ground plane, showing the "Mirror" Antenna                                                                                                                                                                                                                                                                                                                                                                                                                             |

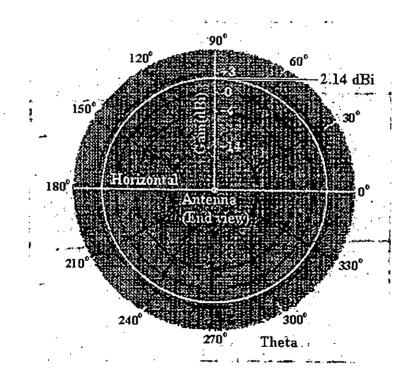

| 2.2<br>2.3<br>2.4<br>2.5                                                                                           | Monopole above a ground plane, showing the "Mirror" Antenna                                                                                                                                                                                                                                                                                                                                                                                                                             |

| 2.2<br>2.3<br>2.4<br>2.5<br>2.6                                                                                    | Monopole above a ground plane, showing the "Mirror" Antenna.23Radiation Pattern of Horizontal Half-Wave Dipole (3 dimensional sketch).24Three dimensional Co-ordinate System.25Radiation Pattern of Horizontal Half-Wave Dipole (Vertical Plane).25Radiation Pattern of Horizontal Half-Wave Dipole (Horizontal Plane).26Radiation Pattern of Vertical Monopole Antenna.26                                                                                                              |

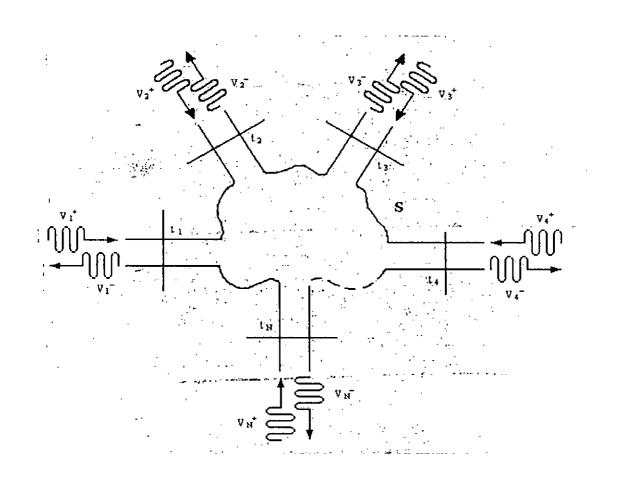

| <ol> <li>2.2</li> <li>2.3</li> <li>2.4</li> <li>2.5</li> <li>2.6</li> <li>2.7</li> </ol>                           | Monopole above a ground plane, showing the "Mirror" Antenna.23Radiation Pattern of Horizontal Half-Wave Dipole (3 dimensional sketch).24Three dimensional Co-ordinate System.25Radiation Pattern of Horizontal Half-Wave Dipole (Vertical Plane).25Radiation Pattern of Horizontal Half-Wave Dipole (Horizontal Plane).26Radiation Pattern of Vertical Monopole Antenna.26An arbitrary N-port microwave network.28                                                                      |

| <ol> <li>2.2</li> <li>2.3</li> <li>2.4</li> <li>2.5</li> <li>2.6</li> <li>2.7</li> <li>2.8</li> </ol>              | Monopole above a ground plane, showing the "Mirror" Antenna.23Radiation Pattern of Horizontal Half-Wave Dipole (3 dimensional sketch).24Three dimensional Co-ordinate System.25Radiation Pattern of Horizontal Half-Wave Dipole (Vertical Plane).25Radiation Pattern of Horizontal Half-Wave Dipole (Horizontal Plane).26Radiation Pattern of Vertical Monopole Antenna.26                                                                                                              |

| <ol> <li>2.2</li> <li>2.3</li> <li>2.4</li> <li>2.5</li> <li>2.6</li> <li>2.7</li> <li>2.8</li> </ol>              | Monopole above a ground plane, showing the "Mirror" Antenna.23Radiation Pattern of Horizontal Half-Wave Dipole (3 dimensional sketch).24Three dimensional Co-ordinate System.25Radiation Pattern of Horizontal Half-Wave Dipole (Vertical Plane).25Radiation Pattern of Horizontal Half-Wave Dipole (Horizontal Plane).26Radiation Pattern of Vertical Monopole Antenna.26An arbitrary N-port microwave network.28                                                                      |

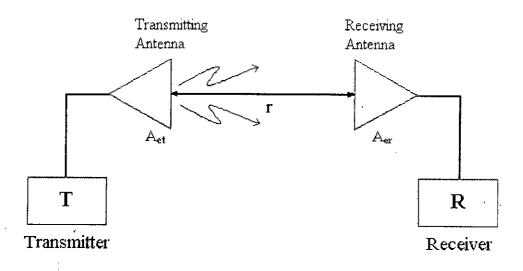

| <ol> <li>2.2</li> <li>2.3</li> <li>2.4</li> <li>2.5</li> <li>2.6</li> <li>2.7</li> <li>2.8</li> <li>2.9</li> </ol> | Monopole above a ground plane, showing the "Mirror" Antenna.23Radiation Pattern of Horizontal Half-Wave Dipole (3 dimensional sketch).24Three dimensional Co-ordinate System.25Radiation Pattern of Horizontal Half-Wave Dipole (Vertical Plane).25Radiation Pattern of Horizontal Half-Wave Dipole (Horizontal Plane).26Radiation Pattern of Vertical Monopole Antenna.26An arbitrary N-port microwave network.28The Radio Communication Link describing Friis Transmission Formula.29 |

÷

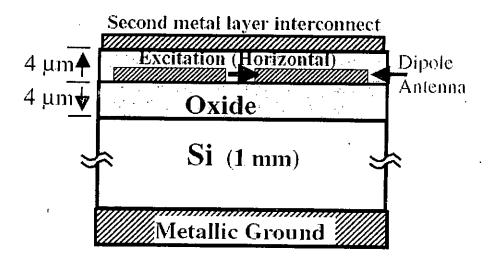

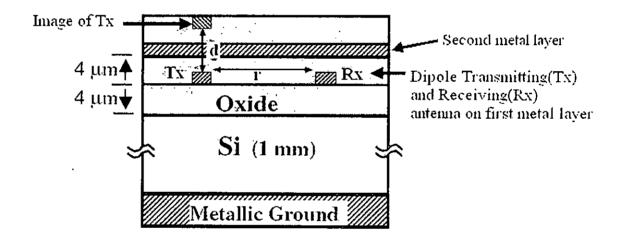

| 3.2         | Conceptual Diagram of the structure explaining the image theory when the                    |

|-------------|---------------------------------------------------------------------------------------------|

|             | antenna is excited horizontally                                                             |

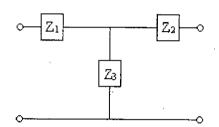

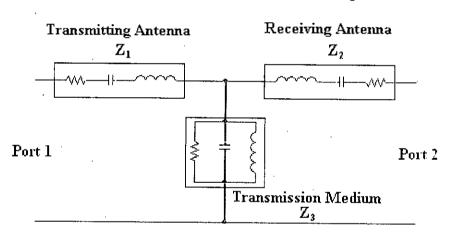

| 3.3         | The estimated T-model of the Antenna structure                                              |

| 3.4         | The estimated T-modeled circuit in detail                                                   |

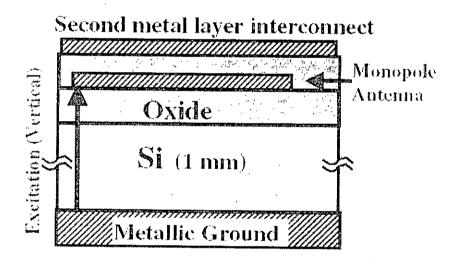

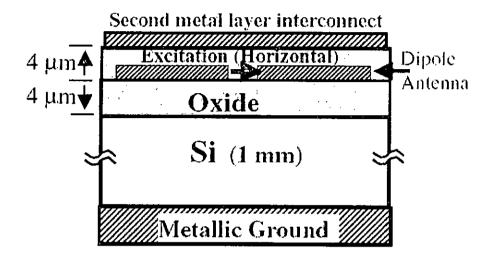

| 3.5         | Cross-sectional diagram of a monopole antenna excited vertically through the Si             |

|             | layer                                                                                       |

|             |                                                                                             |

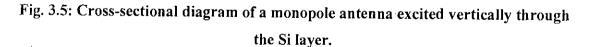

| 4.1         | The structure used in the simulation43                                                      |

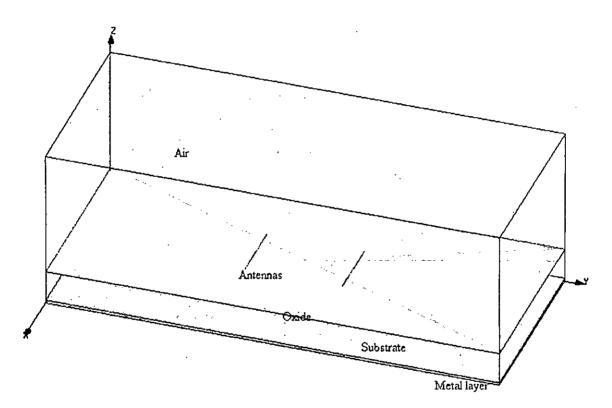

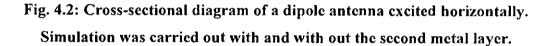

| 4.2         | Cross-sectional diagram of a dipole antenna excited horizontally. Simulation was            |

|             | carried out with and with out the second metal layer44                                      |

| 4.3         | Cross-sectional diagram of a monopole antenna excited vertically through the Si             |

|             | layer. Simulation was carried out with and with out the second metal layer46                |

| 4.4         | Three Dimensional finite element (Tetrahedron)47                                            |

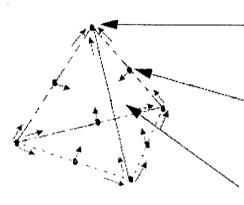

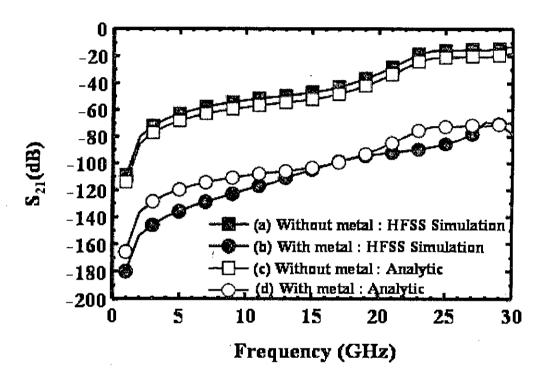

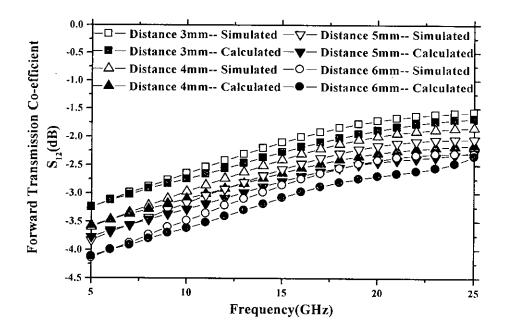

| 4.5         | Simulation result: Variation of the Forward transmission coefficient $(S_{21})$ with        |

|             | frequency for a horizontally excited Dipole antenna                                         |

| 4.6         | Comparison of antenna transmission gain of dipole antenna between simulated                 |

|             | data and analytically calculated values using HFSS49                                        |

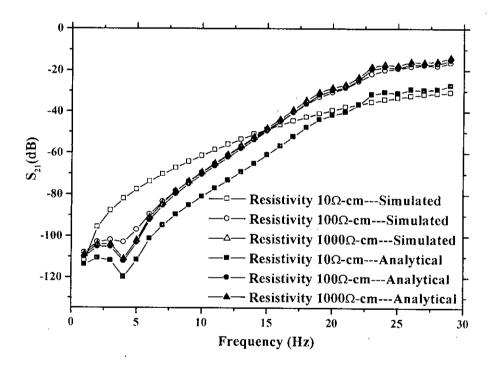

| <b>4.</b> 7 | Comparison between the simulated and analytical Forward Transmission Co-                    |

|             | efficient $(S_{21})$ of the structure under study at different resistivity. The plot is a   |

|             | semi log one, i.e., S <sub>21</sub> values are in dB50                                      |

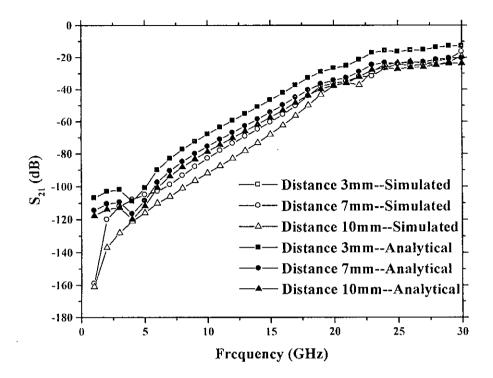

| 4.8         | Comparison between the simulated and analytical Forward Transmission Co-                    |

|             | efficient $(S_{21})$ of the structure under study at different inter antenna distances. The |

|             | plot is a semi log one, i.e., S <sub>21</sub> values are in dB52                            |

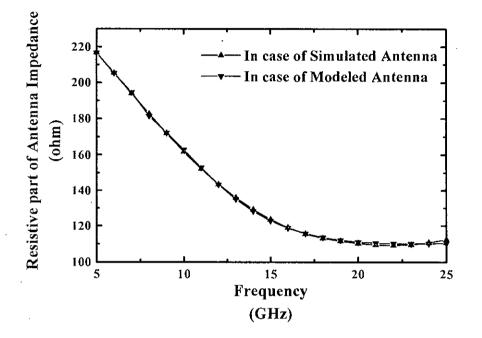

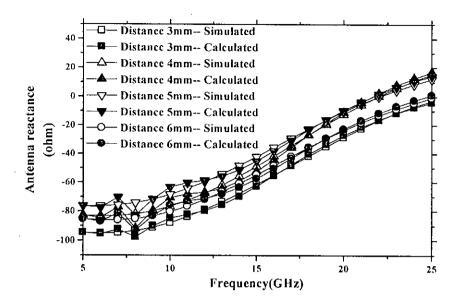

| 4.9         | (a) The comparison of the Transmitting or Receiving Antenna resistance between              |

|             | simulated data and analytically calculated values of the estimated model53                  |

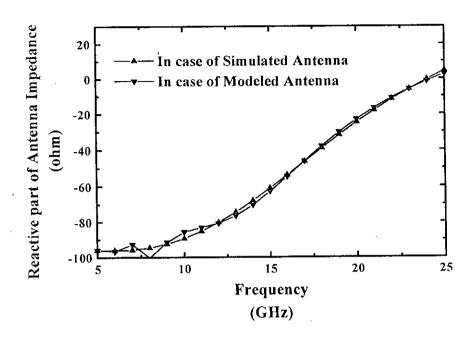

|             | (b) The comparison of the Antenna Reactance between simulated data and                      |

|             | analytically calculated values of the estimated model54                                     |

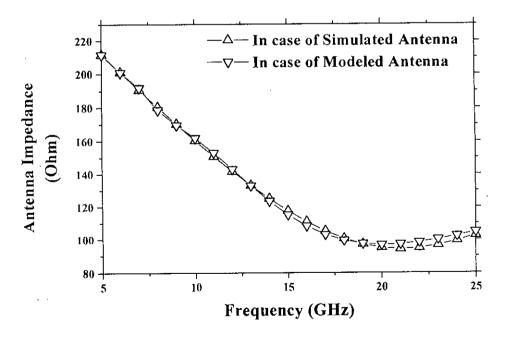

|             | (c) The comparison of the Antenna Impedance between simulated data and                      |

|             | analytically calculated values of the estimated model54                                     |

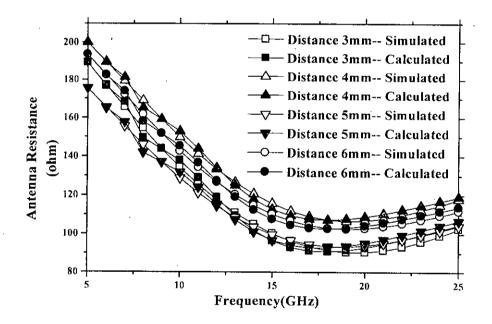

| 4.10        | (a) Antenna Resistances at different inter antenna distances— the simulated data            |

|             | and calculated values from the estimated model and comparisons among them55                 |

Ö

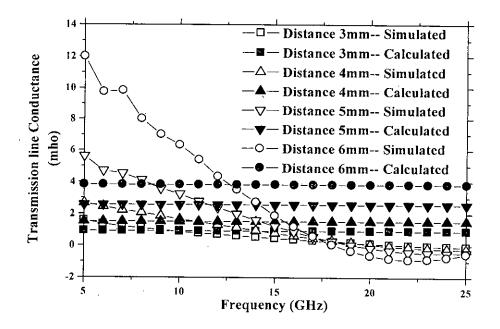

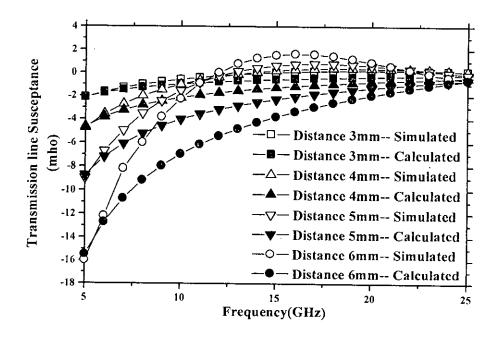

| 4.11 | (a) Comparison among the calculated and the estimated Transmission Line                                            |

|------|--------------------------------------------------------------------------------------------------------------------|

|      | Conductances at different frequencies                                                                              |

|      | (b) Comparison among the calculated and the estimated Transmission Line                                            |

|      | Susceptances at different frequencies                                                                              |

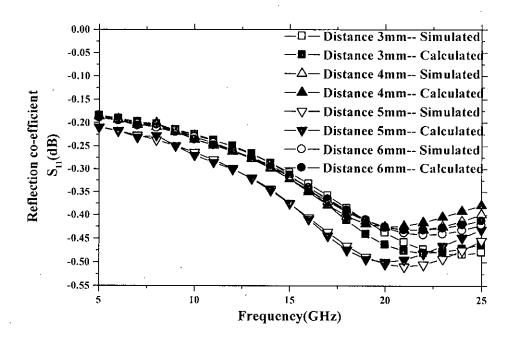

| 4.12 | (a) Comparison among the calculated and the estimated Reflection Co-efficient                                      |

|      | (S <sub>11</sub> ) at different frequencies                                                                        |

|      | (b) Comparison among the calculated and the estimated Forward Transmission                                         |

|      | Co-efficient (S <sub>12</sub> ) at different frequencies                                                           |

| 4.13 | Simulation result: Variation of the Forward transmission coefficient (S <sub>21</sub> ) with $\dot{\vec{h_{\mu}}}$ |

|      | frequency for a vertically excited Monopole antenna60                                                              |

| 4.14 | Comparison of antenna transmission gain of monopole antenna between                                                |

|      | simulated data and analytically calculated values using HFSS                                                       |

|      | \$                                                                                                                 |

|      |                                                                                                                    |

.

.

.

. X

.

.

.

.

·:----

### **ACKNOWLEDGEMENT**

At first, all thanks goes to almighty Allah to make me capable both physically and mentally to finish my thesis work.

I would like to express my sincere gratitude and heartiest respect to my supervisor. Dr. A. B. M. Harun Ur-Rashid. He supported me all through my work and tried to make me self motivated. I have been strongly impressed by his passion to academic professionalism and integrity, and those virtues will be one of important goal I hope to pursue in my career. Also I really appreciate his dedication to my research to the end of my study, not withstanding his tight schedule.

I am thankful to Dr. Rezwan Khan, Professor and Vice-chancellor, United-International University and former Professor of dept. of EEE, BUET for his time, kind attention, fruitful discussion and collaborations. The interaction with him was one of the most valuable experiences of my life.

I would like to express my deepest gratitude to my parents for their unconditional love and devoted support. Their endless encouragement is unforgettable.

Č.

# **ABSTRACT**

Dipole antenna is commonly used for Wireless Interconnect on chip. In this thesis, the characteristics of Integrated Dipole Antenna in Si substrate have been investigated by simulation and this simulation has been explained by theoretical derivation. The effect of upper metal layer above the antenna in a multilayer metal process has been simulated using ANSOFT HFSS and explained analytically for the first time in this work. It has been seen that the second metal layer effects significantly on the Forward Transmission Co- efficient- presence of the upper metal layer reduces the gain of the antenna structure. Also, the effect of changing resistivity of the Si substrate, i.e., the transmitting medium and effect of changing the inter antenna distance on the forward transmission Co-efficient has been simulated and explained by theoretical analysis. The comparison between the simulated data and analytical values shows good agreement in each case. At last, Monopole Antenna has been introduced to improve the performance of the antenna in case of the presence of upper metal layer. Monopole antenna preserves the gain of the antenna both in presence of upper metal layer and also without this layer. The analytical explanation of this observation has also been provided here. Monopole antenna with vertical excitation has been proved itself as more efficient than dipole antenna in multilayer metal processes. But the recent works has proposed to use dipole antenna for on-chip wireless interconnect.

# CHAPTER 1

## INTRODUCTION

6

#### **1.1 BACKGROUND:**

The electronics industry has achieved a phenomenal growth over the last 50 years, mainly due to the invention of Integrated Circuit (IC) in early 1960. Improvement in the processing technique in subsequent years has resulted in a steady increasing chip area and a progressively reducing feature size. This has allowed a complexity increase of approximately one hundred every ten years [1]. Technically speaking, the history of Very Large Scale Integration (VLSI) is a history of miniaturization. This miniaturization is backed by the scaling theory, which states that a MOSFET operates at higher speed without any degradation of reliability when the device size is scaled by a factor of k and at the same time, the operating voltage is scaled by a factor of k. The circuit cost per function is also decreased by miniaturization. Thus, the cost-performance is rapidly improved as devices are scaled down. That is why miniaturization has been pursued so persistently for the last thirty years and will continue to be pursued in the future. Recently, however, undesirable side effects of scaling have become noticeable. These unwanted effects have arrived as challenges to the researchers. To enhance the circuit and system performance, recent studies are focusing on and trying to mitigate these problems [2].

#### **<u>1.2 INTERCONNECT PROBLEM:</u>**

Despite remarkable experimental results for transistor scaling well below 100nm design rule, there are growing challenges to our ability to effectively stay on the technology roadmap [3]. One such prime challenge is "Interconnect Problem".

In microelectronic circuits, the transistors and other devices are often connected by the metallic interconnects. Formation of digital nanocomputers that promise

.1

dramatically increased computational speed and density requires the successful formation of molecular-scale devices. Even after the challenges of fabricating the molecular devices are successfully overcome, the problem of connecting these devices in a circuit to carry the information from the output of one device to the input of the next device sustains. This problem is usually referred to as the "Interconnect Problem" [4].

The quintessential purpose of an interconnect is to communicate. To give a more complete definition, it is communication between distant points with small latency. Reducing the distributed resistance– capacitance product provides smaller latency for a given interconnect length [5]. However, during the past four decades interconnect scaling has increased the distributed resistance– capacitance product, demanding larger latency for a given interconnect length. In stark contrast, scaling of transistors reduces the power–delay product or switching energy of a binary transition, to reduce simultaneously both average power transfer and delay.

Scaling of transistors reduces their cost, intrinsic switching delay, and energy dissipation per binary transition. Scaling of interconnects serves to reduce cost but increases latency or time delay and energy dissipation relative to that of transistors. These increase result from relatively larger average interconnect lengths and larger die sizes for successive generations. Therefore, interconnects have become the primary limit on both the performance and the energy dissipation of future Ultra Large Scale Integration (ULSI).

#### **1.3 IMPACT OF INTERCONNECT PROBLEM:**

According to the simple scaling rule, when the devices and interconnects are scaled down in all three dimensions by a factor of S, the intrinsic gate delay is reduced by a factor of S, the delay of local interconnects (such as connections between adjacent gates) remains the same, but the delay of global interconnects increases by a factor of S<sup>2</sup> [5-9]. As a result, the interconnect delay has become the dominating factor in determining system performance. Interconnect problem is the most prevailing one. In many systems designed today, as much as 50% to 70% of clock cycle is consumed by

2

interconnect delays. This percentage will continue to rise as the feature size decreases further.

1

Repeater insertion is generally used to reduce the delay of long global interconnects [10]. The delay can be reduced up to a certain extent by this technique, but the power consumption increases by about 70% due to the inserted buffers, which will be described in more detail below. Another way to decrease the interconnect delay without increasing the power is to use a thicker and wider metal layer. However, with consistent scaling of global interconnect dimensions to meet the increased connectivity demands in a high performance system-on-a-chip (SoC), the interconnect delay per unit length of optimally buffered minimum sized global wires is also increasing with technology scaling [11]. Therefore, global interconnects tend to limit the performance of highperformance SoCs. In order to achieve improvement in performance, designers tend to use wires, which are wider than minimum-sized global interconnects prescribed by the technology. Increasing the width of the interconnect proportionally reduces its resistance per unit length and also increases the line capacitance per unit length. However, for global interconnects in nanometer technologies, where the aspect ratio of wires is approximately 2-2.5, the increase in width results in a reduction in the resistancecapacitance (RC) time constant of the line and therefore improves delay per unit length [12]. However, these "fat" wires take up a lot of routing resources and using fat wires can adversely affect the wireability of the chip, like signal integrity problems such as high crosstalk noise and large delay fluctuation due to capacitive coupling among adjacent lines. The higher speed causes inductance-related issues and electromagnetic interference problems. For further improvement in performance, the spacing of global interconnects can also be increased which, to some extent, offsets the increase in line capacitance due to increasing line width. On the other hand, this increase in spacing will further degrade the wireability of the chip. Therefore, in determining the wire width at the global tier, the number of interconnects per unit chip edge should also be taken into account along with the delay per unit length.

t

#### **1.4 EVOLUTION OF INTERCONNECT TECHNOLOGIES:**

The semiconductor technology is moving quickly towards applications requiring operating frequencies of the order of tens and hundreds of GHz, as have been predicted in fig.1.1. Also, this is fuelling the demand for scaling the VLSI integration down to the deep sub-micron level with an astonishing pace, i.e., toward ULSI. Along with the transistor scaling, wire width and wire spaces have been scaled down together. Metal routing pitches have also been scaled down and the number of metal layers has been increased. This increasing level of integration is the main route to achieve ever-higher computing speed. But, the main concern toward high-speed operation of ULSIs is the interconnect delay due to the parasitic resistance and capacitance [13]. The scaled chip interconnects suffer from increased resistance due to a decrease in conductor cross-sectional area and increased capacitance for reduced spacing and an increase in conductor height. Thus, Interconnect delay exceeds the gate delay at present technology, as shown in fig. 1.2 [14]. Therefore, the parasitic R and C will remain the primary obstacle to increase clock frequency in future ULSI. Therefore, now-a-days, one of the most urgent needs concerns the development of new interconnect technologies for systems on chip.

Fig. 1.1: Projected Clock Frequency

# **<u>1.5 DIFFERENT SOLUTIONS OF INTERCONNECTION PROBLEMS</u> THE WIRING <b>BOTTLENECK:**

Due to continually shrinking feature sizes, higher clock frequencies, and the simultaneous growth in complexity, the role of interconnect as a dominant factor in determining circuit performance is growing in importance. For the past few decades, a great deal of work has been focused on improving the conventional interconnect technology. If all these solutions are enlisted chronologically, then we get the following approaches —

#### 1.5.1 Multi layer Interconnects:

In the 80's, advances in VLSI and electronic product performance were driven by silicon technologies. The main driver was transistor scaling which was propelled by advances in lithography and gate dielectrics. Thus, the smaller the feature size is, the faster the transistors become. In the '90s, multilayer interconnection on VLSI became a common technology driven by advances in metallization. An extremely large number of interconnects are needed not just for connecting the devices in a circuit but also for connecting the circuits together. The results show that multilayer interconnects show similar capacitance behavior as do the corresponding single path interconnects. However, the current carrying capability of a multilayer interconnection is expected to be much higher. Therefore it could be beneficial to use multilayer interconnects since more current could be carried by the interconnect in relation to the amount of additional capacitance that the interconnect adds to the circuit [15]. Thus, this advance, in turn, hastened VLSI integration. While this advance is impressive, it is increasingly apparent that such high levels of integration and performance place significant demands on VLSI interconnections. It is evident that VLSI circuit speed is now dominated by the interconnection. In order to mitigate this limitation, modern VLSI interconnection strategies were driven mostly by adding more metal layers. However, due to the increase of interconnect resistance and intra-layer capacitance, multilayer capacitance failed to meet the speed demand of new generation chip.

5

#### **<u>1.5.2 Cu Interconnect:</u>**

The introduction of copper metallization, along with the imminent introduction of low-dielectric-constant insulating materials, indicates an accelerating pace of innovation.

Cu has been seriously evaluated as an interconnection material due to its high electrical conductivity and relatively high melting temperature. Al, on the other hand, had been the interconnection material for about 30 years. The restriction was due to two limiting behaviors of Al.

The first one is related to interconnection failures associated with electromigration [16]. The phenomenon of electromigration occurs when the conductor is subjected to high current density at operating conditions where atomic drifting is severe, leading to mass transports associated with atomic flux divergence. The enhanced and directional mobility of atoms are caused by the direct influence of the electric field on the ionized atoms and the collision of electrons with atoms, leading to momentum transfers and atomic movements. Table 1.1 compares the electromigration parameters of Al and Cu as calculated for the bulk large-grained metals, where  $Z^*$  is effective valence,  $\rho$  is the electrical resistivity, Q is the activation energy of diffusivity, and Do is the pre-exponential constant. Cu is the more resistant against electromigration.

|       |          |          | Diffusion parameters |                       |                             |

|-------|----------|----------|----------------------|-----------------------|-----------------------------|

| Metal | -Z*      | ρ(μΩ-cm) | Q(eV)                | $D_0 (cm^2/s)$        | Z <sup>*</sup> ρD at 100°C  |

| Al    | 6.5-16.4 | 2.65     | 1.71                 | 2.1x10 <sup>-20</sup> | 3.62-9.12x10 <sup>-19</sup> |

| Cu    | 3.7-4.3  | 1.67     | 0.78                 | 2.1x10 <sup>-30</sup> | 1.3-1.5x10 <sup>-29</sup>   |

#### Table 1.1: Comparison of electromigration parameters for bulk materials.

The second limiting property of Al is its resistivity. For pure Al, the resistivity is 2.7  $\mu\Omega$ -cm, which is considerably higher than that of pure Cu (1.7  $\mu\Omega$ -cm). Making the situation worse, pure Al is not used as the interconnection metal. To bolster its electromigration resistance and minimize its reactivity with silicon substrate, actual Al

interconnections are alloys containing Cu and Si, which increase the resistivity to 3 to 3.5 mW-cm or higher.

As the channel length of a MOS transistor decreases, the carrier transit time across the length of the channel also decreases, making the transistor a faster device. However, the signal propagation in between the devices must occur through interconnections. The interconnection is surrounded by insulating dielectrics. One can approximate the RC delay by multiplying R with a simple plate capacitance C, leading to an expression—

$$RC = \frac{\rho}{t_M} \frac{L^2 \varepsilon_{IJD}}{t_{IJD}}$$

(1.1)

where  $\rho$ ,  $t_M$  and L are the resistivity, thickness, and length of the interconnection respectively.  $\epsilon_{ILD}$  and  $t_{ILD}$  are interlayer dielectric (ILD) permittivity and thickness of the dielectric respectively. One can substitute  $\rho/t_M$  with the sheet resistance  $R_s$  given in units of ohms per square. A reduction in  $t_M$  or  $t_{ILD}$  will increase the RC. For a given  $t_M$  and  $t_{ILD}$ , however, RC delay depends only on  $R_s$ , L, and  $\epsilon_{ILD}$  and is independent of the width of the interconnection. This dependency implies that, to the first order, reducing the line width does not affect the RC. Indirectly, this is a disadvantage because the RC time constant can offset the speed advantage of device miniaturization.

More rigorous calculations of the RC time constant that includes the effect of fringing capacitances will show that at smaller dimensions, the total circuit delay is a composite of the intrinsic device delay associated with the transistor and the interconnection delay [17]. Therefore, by changing the interconnection material from Al to Cu, number of metal layer, power consumption, and RC delay can be significantly improved as shown in Fig. 1.3.

1

Fig. 1.3: Superiority of Cu/low-k interconnection over Al/ SiO<sub>2</sub> interconnection.

# <u>**1.6 REVOLUTIONARY TECHNIQUES-PREDICTED "END OF THE ROAD" FOR**</u> <u>**METALLIC INTERCONNECT:**</u>

At 250-nm technology node, copper (Cu) with low- dielectric was introduced to alleviate the adverse effect of increasing interconnect delay [18]. However, as shown in Fig. 1.4, below 130-nm technology node, substantial interconnect delays will result in spite of introducing these new materials, which in turn will severely limit the chip performance. Further reduction in interconnect delay cannot be achieved by introducing any new materials.

÷

### Fig. 1.4: Typical gate and interconnect delays as a function of feature sizes. The interconnect delay assumes an optimally repeated line and includes the delay due to the repeaters.

Again, the global clock skew can limit the high-speed operation of microprocessors, even when using the state-of-the-art copper and low- $\kappa$  interconnect technology [19]. Worse than this, typical systemic clock skew solutions involve use of H-tree circuitry, taking up a large area and requiring symmetry [20]. What this means in terms of clock delivery is that as the chip size and clock frequency are increased each passing year, the clock skew becomes harder to equalize across the chip, and the total area used in clock delivery increases. This problem is one of the grand challenges facing the semiconductor industry, which could place serious limitations on the growth of the industry.

The problem facing us then is that evolutionary solutions will not be sufficient to meet the performance roadmap. To tackle the issues developed above, radically different interconnect approaches displaying a highly improved data-rate to power ratio must be developed. At present, the most prominent ideas are

- 3D (non-planar) integration [21],

- Optical interconnects [22] and

5

Integrated radio frequency or microwave interconnects [23].

9

#### **1.6.1 3-D integration:**

乀

Three-dimensional integration (schematically illustrated in Fig. 1.5) to create multilayer Si ICs is a concept that can significantly improve deep-submicrometer interconnect performance, increase transistor packing density, and reduce chip area and power dissipation [24]. In the 3-D design architecture, an entire (2-D) chip is divided into a number of blocks, and each block is placed on a separate layer of Si that is stacked on top of each other. Each Si layer in the 3-D structure can have multiple layers of interconnect. These layers are connected together by vertical interlayer interconnects (VILICs) and common global interconnects as shown in Fig. 1.5 [21].

3-D integration offers some attractive <u>advantages</u> related to system performance and enabling of new system architectures.

Ś

<u>First</u>, the 3-D architecture offers extra flexibility in system design, placement, and routing. For instance, logie gates on a critical path can be placed very close to each other using multiple active layers. This would result in a significant reduction in RC delay and ean greatly enhance the performance of logic circuits.

Second, the negative impact of deep-submicrometer interconnects on VLSI design can be reduced significantly by eliminating the long *global wires* that realize the interblock communications by vertical placement of logic blocks connected by short vertical interlayer interconnects.

<u>Third</u>, the 3-D chip design technology can be exploited to build SoCs by placing circuits with different voltage and performance requirements in different layers.

<u>Fourth</u>, three-dimensional integration can reduce the wiring, thereby reducing the capacitance, power dissipation, and chip area and therefore improve chip performance.

<u>Fifth</u>, the digital and analog components in the mixed-signal systems can be placed on different Si layers thereby achieving better noise performance due to lower electromagnetic interference between such circuit blocks.

However, there are several critical challenges on the way to use this technique.

- Difficult technological barriers are opposed to the use of this technique. Heterogeneous integration is still a long way from reaching the status of mature technology.

- It also appears rather clear that physical problems must be solved, such as the evacuation of thermal energy and the necessarily higher reliability of the components, which must survive the longer and more intricate fabrication process.

- Even if these issues are resolved, it is also necessary to question the long-term validity of the approach. Indeed, when communication frequency increases, the communication distance decreases at constant power budget. The surface of each layer must thus decrease, which results in a quadratic increase in the number of layers and in the vertical communication distance.

• Thus it is not obvious that all technological problems will be solved before this technique becomes obsolete compared to bandwidth requirements.

The active interconnect layer is a variant on the general vertical integration technique, specific to the interconnect problem. This solution will not solve the problems inherent to metallic interconnect, but it offsets them for a while. The idea is to graft a layer of active buffers above the last metal layer and use these buffers (which can be arranged in a matrix formation or as a "sea" of buffers) solely as repeaters for long interconnect. This approach frees up active silicon area for computing functions rather than for interconnects. It also reduces congestion by replacing the via stacks (necessary between the last metal layer and the active silicon layer), by single vias going vertically upwards from the last metal layer to the vertically adjacent buffer layer. Power may be marginally reduced (as the via stack contribution to line load is removed). Crosstalk or any disturbance on victim lines should be reduced. As with 3D, doubts can be expressed as to how long this approach could be viable.

#### **1.6.2 Optical interconnects:**

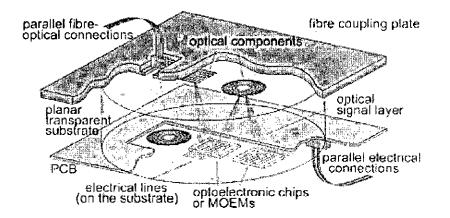

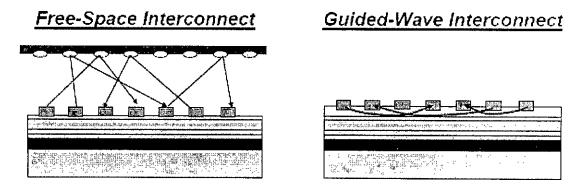

Optics is arguably a very interesting and different physical approach to interconnection that can in principle address most, if not all, of the problems encountered in electrical interconnections. [22]. Fig. 1.6 shows a typical view of an optical interconnect system. Proposed optical approaches can be grouped into guided wave and free space [25], as shown in fig. 1.7. Guided wave optics involves the use of waveguides to contain the optical signals within a board, package, or on a chip. Free-space optics utilizes diffractive optics and conventional lenses or microlens arrays to guide single or multiple parallel optical beams in free space.

Fig. 1.6: Optical Interconnect Technology on Si

Fig. 1.7: Proposed two groups of Optical Interconnect.

Compared to electrical wires, optical technology offers fundamental advantages to global interconnects, given that the technology can be realized in a simple, cost effective implementation.

- The bandwidth of electrical interconnects is  $\sim A/l^2$ , where A is the cross section area of the Interconnect and l is the length. Optical interconnects, however, are not bandwidth limited in this way, although they are limited by the propagation delays of optoelectronic components such as transmitters, modulators, and receivers.

- The signal propagation velocity of electrical interconnects tends to be 10%-30% of the speed of light, c, whereas the optical propagation velocity for guided waves tends to be ~ (l/3)c.

Optical interconnects used for off-chip and on-chip clock and signal distribution have similar bandwidths and latency, and they, therefore, eliminate the hierarchical constraints imposed by off-chip electrical interconnects, i.e., the lower bandwidth and longer delay times.

Optical interconnects must overcome some rather difficult fundamental and technological challenges before they will find application even in off-chip applications. The technical challenges this interconnect is facing includes

- The decisions on which signals to include in optical communications and which remain in conventional metal dielectric, and the choice of on-chip optical emitters, are significant. In the case of optical interconnects, it is easy to assume that this solution will meet speed requirements because the signal travels at "the speed of light." However, to define the total interconnect system for this approach it is necessary to consider the delays associated with rise and fall times of optical emitters and detectors, the speed of light in the transmitting medium, losses in the optical waveguides (if used), the signal noise due to coupling between waveguides, and a myriad of other details.

- Guided wave optical interconnects may require separate active layers in the vertical dimension with via interconnect to the functional blocks to support the required optoelectronic components.

- An on-chip optical interconnect technology may require either impractical high levels of optical signal power or area intensive error correction circuits. The latter, again, can be achieved perhaps in a separate set of active interconnect layers.

- The additional disadvantages include Power dissipation for receivers, and, to a lesser extent, transmitters can be prohibitively large.

- Other issues with optical interconnects are the technologies for fabricating III–V devices on silicon. Heteroepitaxial growth of III–V vertical-cavity surfaceemitting lasers (VCSELs) on silicon CMOS circuits is a very difficult technology limited by reliability concerns.

Much sophisticated optical and optoelectronic technology has been developed for long-distance communications, but the requirements of dense interconnects are substantially different. Low power dissipation, small latency, small physical size, and the ability to integrate with mainstream silicon electronics in large numbers are all required for dense interconnects at the chip-to-chip or on-chip level. Existing optical telecommunications applications do not require any of these constraints, and the technologies developed do not satisfy them. Additionally, the discrete approaches used for long distances are likely not to be viable for dense interconnects. However, other opportunities in optical and optoelectronic technology have been researched over the last several years that are apparently capable of operating at the densities needed, though the technologies are often quite different from those of long-distance communications and are much less mature.

#### **1.6.3 RF/Wireless Interconnect:**

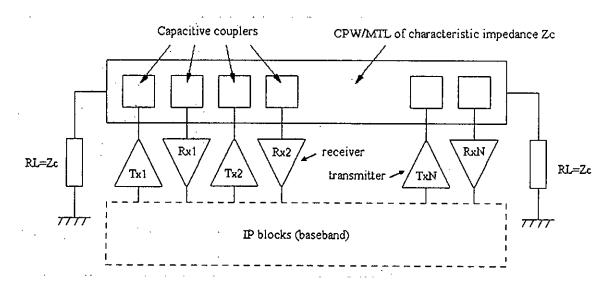

A relatively radical alternative to the usual metal/dielectric interconnects is to use transmission of signals from one part of a chip to another via RF or microwaves. Recently, this technology has been considered as a viable candidate to replace metal/dielectric global wires. In general, RF signals can be transmitted through free space or waveguide mediums. At chip scale, the free space transmission is not possible. On the other hand, guided transmission (by MTL (Microstrip transmission line) or CPW (Coplanar waveguide)) can be carried out with attenuation lower than 2dB/cm up to 200GHz. A wireless LAN type interconnect architecture (Fig. 1.8) can exploit this high bandwidth by associating IP blocks, RF transceivers, capacitive couplers as near-field antennas and MTL/CPW as shared RF communication channel [23].

ε

Fig. 1.8 Integrated RF interconnect channel concept

RF interconnects are a very new approach for intrachip and interchip interconnects. This approach has become possible because of the confluence of wireless technologies for communications applications with high-frequency silicon technologies. This approach can be used for both clock and data signals. They have been demonstrated recently for clock distribution at 7.4 GHz and 15 GHz in 0.25-µm and 0.18-µm technologies respectively. They have also received attention for data communication [26].

The use of code division multiple access (CDMA) and frequency division multiple access (FDMA) to obtain up to 100 channels in a 100-GHz carrier connecting multiple transmitting and receiving nodes is the special and novel feature of this wireless approach. Using local area network (LAN) communication techniques applied to microsystems applications, this micro-LAN (M-LAN) approach will provide high-speed, low-loss intrachip clock/signal distribution among multiple block functions on a chip, or, more likely, among multiple chips in a package.

Compared to global electrical wires, RF interconnects potentially offer several advantages.

Circuits can be synchronized over much larger areas because wireless approach transmit signals three to ten compared to global wires.

- In addition, the bandwidth of the RF approaches is only limited by the bandwidths

of the transmitting and receiving components, and not by the transmission

medium, as is the case for global wires.

- The crosstalk between channels should be much improved, particularly for the approach using FDMA and CDMA communication techniques.

- The signal multiplexing capability of the M-LAN approach should reduce the actual number of I/O ports going off-chip and the M-LAN communications techniques can provide new flexibility to reconfigure the interconnect system simply by changing the CDMA codes.

- RF interconnects are a very new approach for intrachip and interchip interconnects, although the techniques proposed are well developed for wireless communications applications.

RF interconnect has to overcome some difficult challenges before becoming a viable candidate to replace global wires. First, for package applications, the RF implementation must be cost competitive with conventional interconnect systems. Further, the power dissipated by RF interconnect support circuits must be equal to or less than the power dissipated by the global interconnect wires, and the silicon area consumed by these RF circuits must only be a small fraction of the chip size. Also, the RF power dissipation cannot add a significant amount of heat to an already heavy thermal load. Finally, similar to optical interconnects, RF interconnect systems will likely require adaptation of new system architectures to fully exploit the capabilities of RF interconnects.

### **1.7 ADVANTAGES OF WIRELESS INTERCONNECT OVER OPTICAL** INTERCONNECT:

Though both optical and wireless interconnect schemes are simultaneously evaluated as a new technology solution for the future ULSI, the later shows a number of promising advantages.

> The advantage of RF technique lies primarily in the possibility of offering several IP blocks access to a broadband communication channel through a single physical channel, without major process modifications. Whereas

optical interconnect, traditionally considered as a specialized technique, raises design questions that industrial IC designers are not equipped to answer. Difficulties expected are obtaining a large enough opticalelectrical conversion efficiency.

- Optical devices are fabricated using III-V group which are not compatible with existing Si technology and hence costly to implement. On the other hand, wireless interconnects provide completely CMOS compatible architecture.

- The relative size of optical components (particularly waveguides and photo-receiver circuits) compared to chip circuitry is a critical design constraint. That is why, optical interconnects may require separate active layers in the vertical dimension with via interconnect to the functional blocks to support the required optoelectronic components. To the contrary, no special guided wave mechanism is required for on-chip wireless interconnect hence it reduces the electronic overhead on the existing circuit components.

- WDM (Wavelength Division Multiplexing) is the only technique that makes possible to increase the aggregate data rate of the optical link. RF interconnect exploits CDMA (Code Division Multiple access) or FDMA (Frequency Division Multiple access) encoding techniques, managed by the transceivers, which are not only the most common and easy techniques, but also increase data rate and reduce any interchannel interference. CDMA and FDMA are compatible to other communication systems also.

#### **<u>1.8 RESEARCH OUTLINE:</u>**

The ultimate goal of this work is to develop an efficient system of On-chip integrated antenna on Si for Wireless Interconnect. A model of on chip integrated antenna on Si substrate will also be developed. The outcomes while delving through the work are asserted below—

- The effect of multi layer interconnect scheme on forward transmission coefficient of dipole antenna.

- Analytical explanation of the simulation of dipole antenna excited horizontally.

- The effect of Si resistivity on transmission co-efficient of dipole antenna at different frequencies.

- The effect of distance between the antennas on transmission co-efficient of dipole antenna at different frequencies.

- The efficient way of providing excitation to the antenna in integrated circuit fabricated with planar IC technology.

- Analytical explanation of the simulation of antenna excited in vertical direction.

The complete system was simulated in ANSOFT and the calculation was done by MATLAB. Optimistic results from these simulations and theoretical studies took us a way forward to achieve the overall goal of finding the circuit parameters of the transmitting and receiver antenna and also the transmission medium.

#### **<u>1.9 THESIS LAYOUT:</u>**

This thesis comprises of seven chapters.

In chapter 1, we first highlighted the interconnect problem of today's small scale ICs as a prime challenge to meet the projected overall technology requirements. There are several new techniques to overcome this interconnect problem. Different types of Interconnect schemes have been delineated in details starting with the definition of interconnect. The problem of using metallic interconnect irrespective of the material has been also depicted in this chapter. Consequently, the importance of revolutionary interconnect schemes has aroused and all this new techniques has been sketched. It has been shown that the wireless interconnect scheme using Si integrated antenna has some superfluous advantages above the others. At last, a detailed outline of the research has been sketched. In chapter 2, the definitions and theories that have been used in this work has been described elaborately. At first the characteristics of dipole and monopole antennas has been recited with the help of electromagnetic theory. Then the definition of scattering matrix of a microwave network has been depicted and at last the Friis transmission formula, which is the backbone of the work, has been derived.

In **chapter 3**, the detail of the analytical part of the research has been enumerated. At first an analytical model of dipole antenna under study has been formed on the basis of Friis transmission formula. The Forward transmission Co-efficient ( $S_{21}$ ) of a dipole has been developed from this Formula. Then equation of  $S_{21}$  at different conditions, like without any metal layer on the top of the dipole antenna, with metal layer on the top has been derived and the explanation is given for the first time in this work. The effect of change in resistivity of Si substrate and variation in distance between the transmitting and receiving antenna on  $S_{21}$  has been also incorporated in case of dipole antenna without any metal layer. Dipole antenna without any metal layer on the top has been analyzed as it is the most conventional and efficient way of using integrated antenna in VLSI. In this same chapter, the same antenna structure has been modeled as a two port microwave T network. The circuit parameters of each of the T model element have been further derived. Then the problem in using the dipole antenna in presence of upper metal layer has been described and a novel approach of applying vertical excitation to the antenna has been proposed here.

In chapter 4, the simulation procedure has been described and comparison between the theoretical data and simulation results has been also shown. The simulation, result has been extracted in the form of Forward Transmission Co-efficient ( $S_{21}$ ) and Z-matrix of the antennas. All the theoretical data that have been acquired from the theory described in chapter3, has been juxtaposed with the simulated one at different situations and cases. The comparison showed good agreement between the simulated and modeled data.

In chapter 5, the thesis has come to its end with the summary of the research and with some suggestions to move toward the future of this work.

20

CHAPTER 2