# INVESTIGATION INTO THE PERFORMANCE AND TESTABILITY OF BICMOS LOGIC CIRCUITS

A thesis submitted to the Department of Electrical and Electronic Engineering Bangladesh University of Engineering & technology Dhaka-1000 in partial fulfillment of the requirements for the degree of Master of Science in Engineering (Electrical and Electronic)

### ZAHEEDUL MURSHALIN

ROLL NO: 930655P SESSION: 1992-93-94

**DECEMBER 1996**

#91170#

The thesis titled "Investigation into the Performance and Testability of BiCMOS Logic Circuits" submitted by Zaheedul Murshalin, Roll No. 930655P to the Department of Electrical and Electronic Engineering, BUET has been accepted as satisfactory for partial fulfillment of the requirements for the degree of Master of Science in Engineering (Electrical and Electronic).

### **BOARD OF EXAMINERS**

1.

(Dr. Syed Mahfuzul Aziz) Associate Professor Department of Electrical and Electronic Engineering BUET, Dhaka

2.

(Dr. Md. Quamrul Ahsan) Professor and Head Department of Electrical and Electronic Engineering BUET, Dhaka

m- a. Mati 3.

ц. У

> (Dr. Md. Abdul Matin) Pprofessor Department of Electrical and Electronic Engineering BUET, Dhaka

4.

29.12.96

(Dr. Md. Abdul Mottalib) Associate Professor and Chairman Department of Computer Science Dhaka University, Dhaka Chairman (Supervisor)

Member (Ex-officio)

Member (Internal)

Member (External)

## **DECLARATION**

3

I hereby declare that this work has been done by me and it has not been submitted elsewhere for the award of any other degree or diploma.

Countersigned

~

(Dr. Syed Mahfuzul Aziz) Supervisor

(Zaheedul Murshalin)

### ACKNOWLEDGMENT

It is a matter of great pleasure on the part of the author to acknowledge his heartiest gratitude and profound obligation to his supervisor Dr. Syed Mahfuzul aziz, Associate professor of the Department of Electrical and Electronic Engineering, Bangladesh University of Engineering and Technology for his excellent supervision, continuous guidance and valuable suggestion throughout the progress of the work.

The author also wishes to express his special thanks and gratitude to Dr. Md. Quamrul Ahsan, Professor and Head of the Department of Electrical and Electronic Engineering, BUET for his all-out support. The author is also grateful to Dr. A. B. M. Siddique Hossain, Professor and former Head of the Department of Electrical and Electronic Engineering, BUET for his help and cooperation.

Finally the author would like to express thanks to all his friends and colleagues and stuff of the Department of Electrical and Electronic Engineering, BUET for their constant support and assistance.

### Abstract

CMOS logic is now being extensively used for VLSI circuits because of its extremely low static power dissipation, high noise immunity and high packing density. However, standard CMOS circuits are still slower than its bipolar counterpart. BiCMOS logic circuits have been introduced to increase the output drive capability and speed of CMOS circuits. In order to justify the additional complexity of fabricating both MOS and bipolar devices in BiCMOS logic circuits, it is necessary to ascertain their relative advantages and disadvantages compared to standard CMOS. This thesis examines the performance and testability of two classes of BiCMOS circuits, namely, basic BiCMOS and full-swing BiCMOS circuits. Although some work has been carried out on basic BiCMOS circuits, to the best of our knowledge none has been reported so far on full-swing BiCMOS circuits.

Investigation is carried out on the speed, static power dissipation and noise immunity of the BiCMOS circuits. The results indicate that the two types of BiCMOS circuits are much faster than standard CMOS. The noise immunity of basic BiCMOS circuits is lower than standard CMOS while that of full-swing BiCMOS circuits is the same as that of standard CMOS. The static power dissipation of both classes of BiCMOS circuits are higher than that of standard CMOS.

Some new interesting results have been obtained from the investigations on the behavior of BiCMOS circuits under various single faults. Unlike standard CMOS circuits, the stuck open faults in the pull-down bipolar drivers of the full-swing BiCMOS circuits have been found to be undetectable. The behavior of both types of BiCMOS circuits under other stuck open faults are the same as that of standard CMOS circuits. All stuck on faults in both classes of BiCMOS circuits can be detected by current monitoring. The order of increment in power supply current when these faults are sensitized is almost the same as that in standard CMOS circuits. The results presented in this thesis would provide useful guidelines for designing testable BiCMOS logic circuits.

V

### TABLE OF CONTENTS

٠

| Acknowledgment                    | iv  |   |

|-----------------------------------|-----|---|

| Abstract                          | v   |   |

| List of Figures                   | ix  |   |

| List of Tables                    | xi  |   |

| List of Abbreviations and Symbols | xii | i |

| CHAPTER I | Intro | oduction                                                  |     |

|-----------|-------|-----------------------------------------------------------|-----|

|           | 1.1   | Aims                                                      | . 1 |

|           | 1.2   | Literature Review                                         | 2   |

|           | 1.3   | Organization of the Thesis                                | 4   |

| CHAPTER 2 | CM    | <b>OS/BiCMOS Logic Families and Faults</b>                |     |

|           | 2.1   | Introduction                                              | 5   |

| ٢         | 2.2   | Various CMOS circuit Techniques                           | 5   |

|           |       | 2.2.1 Conventional Static CMOS Logic                      | 6   |

|           |       | 2.2.2 Differential Cascode Voltage<br>Switch (DCVS) Logic | 6   |

|           |       | 2.2.3 Differential Split Level (DSL)<br>CMOS Logic        | 7   |

|           | 2.3   | BiCMOS Logic Circuits                                     | 8   |

|           |       | 2.3.1 Conventional BiCMOS Logic                           | 11  |

vi

|           |         | 2.3.2   | Full Swing                    | BiCMOS Logi                | с                                 | 12 |

|-----------|---------|---------|-------------------------------|----------------------------|-----------------------------------|----|

| · .       |         |         | 2.3.2.1                       | Full-swing F<br>Using Clam | BiCMOC Logic<br>ping Diode        | 12 |

|           |         |         | 2.3.2.2                       | Low-capacit<br>Full-swing  | ance variation of<br>BiCMOS logic | 14 |

| 2.4       | 4 Physi | cal Fai | lures in ICs                  |                            |                                   | 19 |

|           | 2.4.1   | Stuck   | at Fault mo                   | del                        |                                   | 20 |

|           | 2.4.2   | Stuck   | -on Fault me                  | odel                       |                                   | 20 |

|           | 2.4.3   | Stuck   | -open Fault                   | model                      |                                   | 20 |

| CHAPTER 3 | Perfo   | orman   | ce of BiCM(                   | OS Logic Circ              | uits                              |    |

|           | 3.1     | Introd  | luction                       |                            |                                   | 21 |

|           | 3.2     | Test A  | Arrangement                   |                            | <i></i>                           | 21 |

|           | 3.3     | SPIC    | E Simulation                  | n Results                  |                                   | 22 |

|           | 3.4     | Com     | oarison                       |                            |                                   | 25 |

| CHAPTER 4 | Fault   | : Chara | acterization                  | of BICMOS I                | ogic Circuits                     |    |

|           | 4.1     | Introd  | luction                       |                            |                                   | 30 |

|           | 4.2     | Fault   | Modeling                      |                            |                                   | 31 |

|           | 4.3     |         | vior of BiCM<br>r Single Stuc | IOS Circuits<br>k Faults   |                                   | 32 |

|           |         | 4.3.1   | Stuck-on F                    | aults                      |                                   | 32 |

|     | 4.3.2 | SPICE Simulation Results for<br>Stuck-on Faults   | 39 |

|-----|-------|---------------------------------------------------|----|

|     | 4.3.3 | Effects of Device Geometry                        | 44 |

|     | 4.3.4 | Comparison with Standard CMOS                     | 52 |

| 4.4 | Stuck | -open Faults                                      | 52 |

|     | 4.4.1 | SPICE Simulation Results<br>for Stuck-open Faults | 57 |

|     | 4.4.2 | Effects of Device Geometry                        | 60 |

|     | 4.4.3 | Comparison with Standard CMOS                     | 60 |

CHAPTER 5

ł

## **Conclusions and Recommendations**

| Refe | rences                          | 64 |

|------|---------------------------------|----|

|      | Ø.                              |    |

| 5.2  | Recommendations for Future Work | 63 |

| 5.1  | Conclusions                     | 61 |

# List of Figures

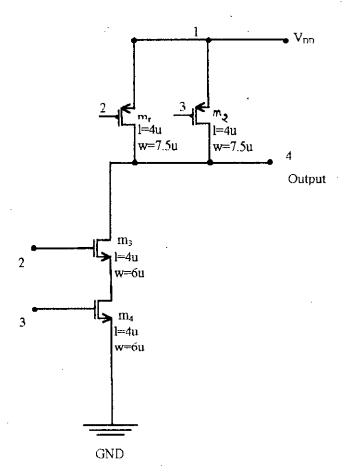

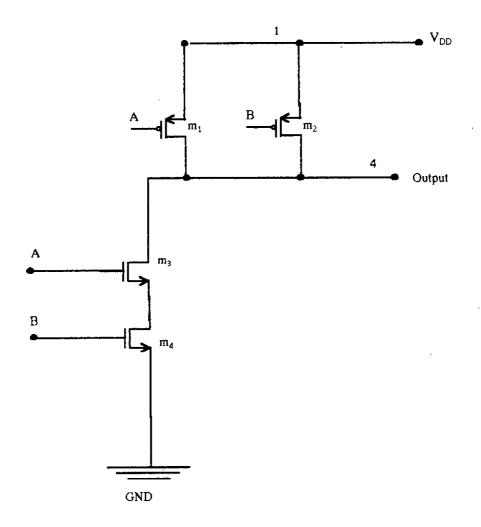

| Fig.2.1    | CMOS NAND gate                                    | 9    |

|------------|---------------------------------------------------|------|

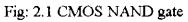

| Fig.2.2    | Basic logic gate in DCVS                          | 9    |

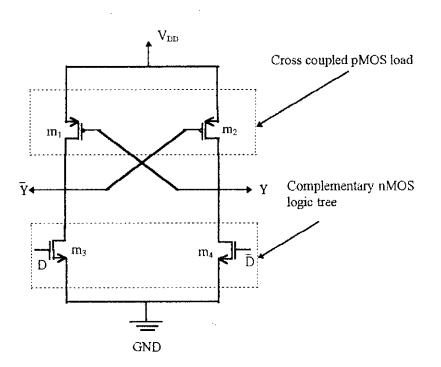

| Fig.2.3    | DSL CMOS logic principle                          | 10   |

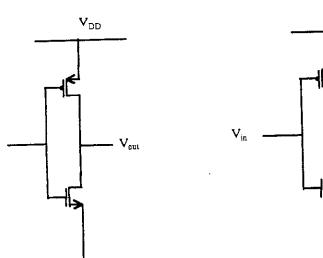

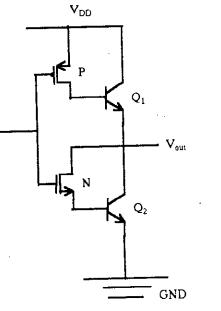

| Fig.2.4(a) | CMOS inverter                                     | - 15 |

| Fig.2.4(b) | BiCMOS inverter                                   | 15   |

| Fig.2.5    | Conventional BiCMOS inverter                      | 15   |

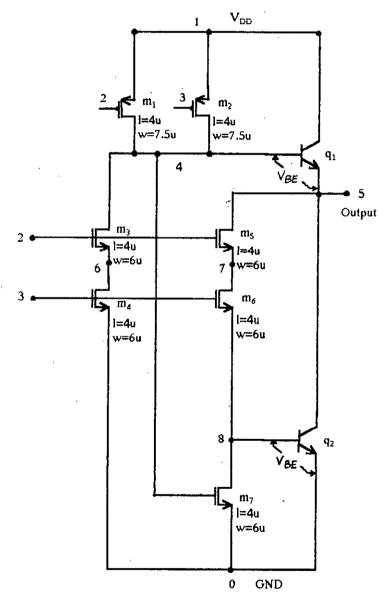

| Fig.2.6    | Basic BiCMOS NAND gate                            | 16   |

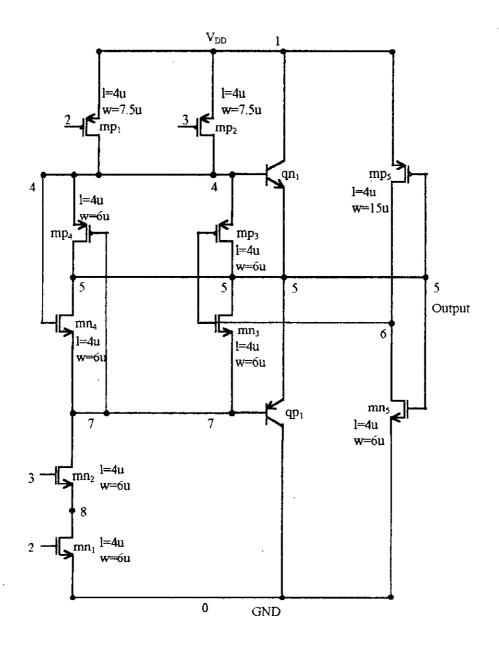

| Fig.2.7    | Basic Full-Swing BiCMOS NAND gate                 | 17   |

| Fig.2.8    | Low-capacitance Basic Full-Swing BiCMOS NAND gate | 18   |

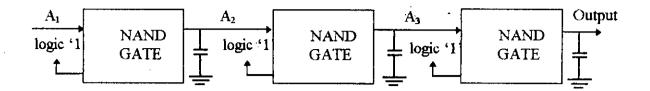

| Fig.3.1    | Cascaded chain of three two-input NAND gate       | 26   |

|            | د<br>-                                            |      |

| Fig.3.2    | Basic BiCMOS NAND gate                            | 26   |

| Fig.3.3    | Full-Swing BiCMOS NAND gate                       | 27   |

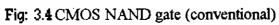

| Fig.3.4    | CMOS NAND gate                                    | 28   |

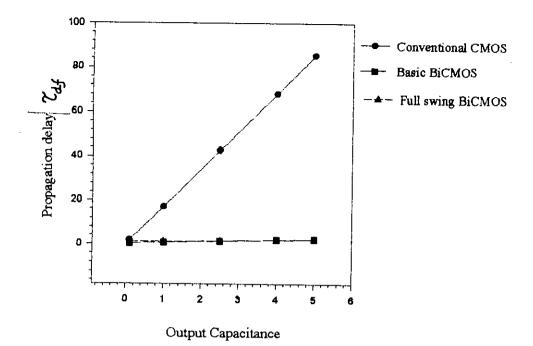

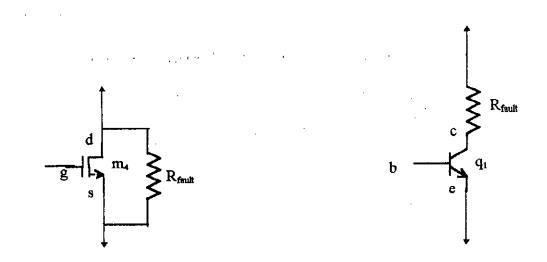

| Fig.3.5    | Propagation delay vs. output capacitance          | 29   |

| Fig.3.6  | Propagation delay vs. output capacitance for BiCMOS circuits                                        | 29 |

|----------|-----------------------------------------------------------------------------------------------------|----|

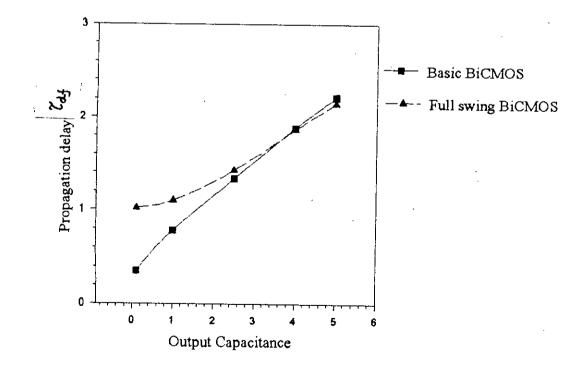

| Fig.4.1  | Stuck-on fault model for MOS m <sub>4</sub>                                                         | 32 |

| Fig.4.2  | Stuck-on fault model for bipolar $q_1$                                                              | 32 |

| Fig.4.3  | Basic BiCMOS NAND gate                                                                              | 35 |

| Fig.4.4  | Full-Swing BiCMOS NAND gate                                                                         | 36 |

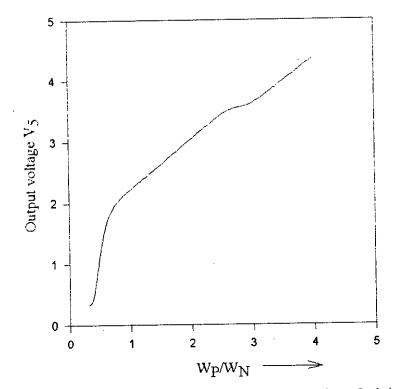

| Fig.4.5  | Variation of output with device parameter for dsm <sub>4</sub> fault in Fig.4.3                     | 46 |

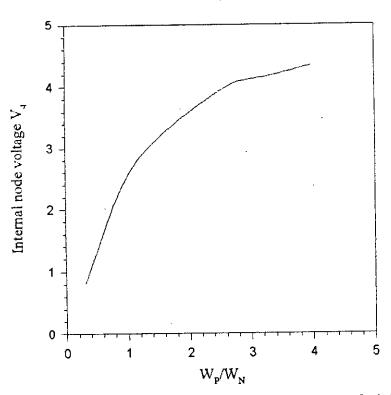

| Fig.4.6  | Variation of $V_4$ with device parameter for dsm <sub>4</sub> fault in Fig.4.3                      | 46 |

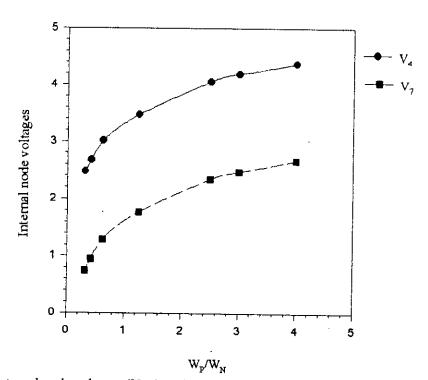

| Fig.4.7  | Internal node voltages ( $V_4 \& V_7$ ) vs. device parameter for dsmn <sub>1</sub> fault in Fig.4.4 | 47 |

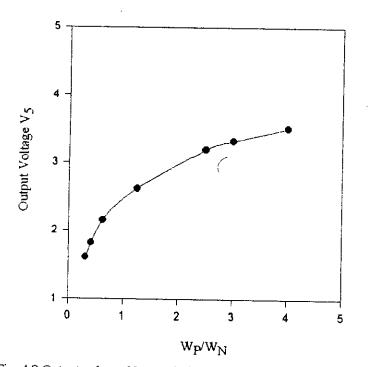

| Fig.4.8  | Output voltage $V_5$ vs. width ratio( $W_p / W_n$ )for dsmn <sub>1</sub> fault in Fig.4.4           | 47 |

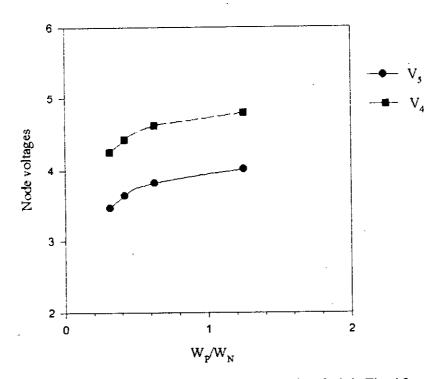

| Fig.4.9  | Node voltages vs. device geometry for dsm <sub>1</sub> fault in Fig.4.3                             | 48 |

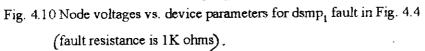

| Fig.4.10 | Node voltages vs. device parameters for dsmp1 fault in Fig.4.4                                      | 48 |

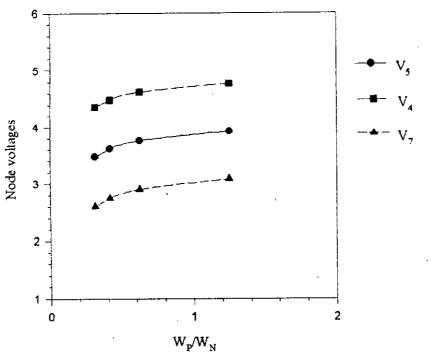

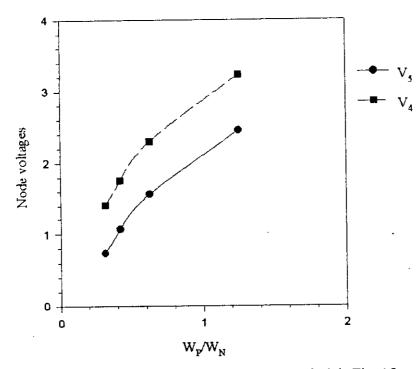

| Fig.4.11 | Node voltages vs. device geometry for dsm <sub>1</sub> fault in Fig.4.4                             | 49 |

| Fig.4.12 | Node voltages vs. device parameters for dsmp1 fault in Fig.4.4                                      | 49 |

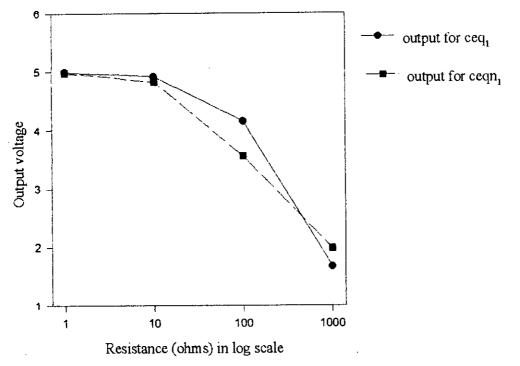

| Fig.4.13 | Output voltage level vs. fault resistance for $ceq_1$ and $ceqn_1$ fault in Figures 4.3 and 4.4     | 50 |

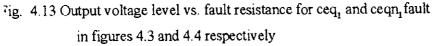

| Fig.4.14 | Node voltage vs. fault resistance for $ceq_2$ fault in Fig.4.3                                      | 50 |

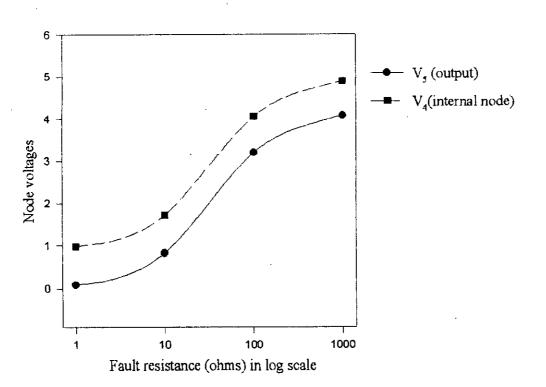

| Fig.4.15 | Node voltage vs. fault resistance for ceqp1 fault in Fig.4.4                                        | 51 |

|          |                                                                                                     |    |

|          |                                                                                                     |    |

. .

**X** .

# List of Tables

| Table 3.1 | SPICE simulation results showing output Logic levels and Power dissipation                                            | 22 |

|-----------|-----------------------------------------------------------------------------------------------------------------------|----|

| Table 3.2 | SPICE simulation results showing Propagation delay                                                                    | 23 |

| Table 4.1 | SPICE simulation results for stuck-on fault in nMOS $m_4$ in the basic BiCMOS NAND gate of Fig. 4.3                   | 40 |

| Table 4.2 | SPICE simulation results for stuck-on fault in nMOS mn <sub>1</sub> in the full-swing BiCMOS NAND gate of Fig. 4.4    | 40 |

| Table 4.3 | SPICE simulation results for stuck-on fault in pMOS $m_1$ in the basic BiCMOS NAND gate of Fig 4.3                    | 41 |

| Table 4.4 | SPICE simulation results for stuck-on fault in pMOS $m_1$ in the full-swing BiCMOS NAND gate of Fig 4.4               | 41 |

| Table 4.5 | SPICE simulation results for stuck-on fault in bipolar driver $q_1$ in the basic BiCMOS NAND gate of Fig 4.3          | 42 |

| Table 4.6 | SPICE simulation results for stuck-on fault in bipolar driver $qn_1$ in the full-swing BiCMOS NAND gate of Fig 4.4    | 42 |

| Table 4.7 | SPICE simulation results for stuck-on fault in bipolar driver q <sub>2</sub> in the basic BiCMOS NAND gate of Fig 4.3 | 43 |

| Table 4.8 | SPICE simulation results for stuck-on fault in bipolar driver $qp_2$ in the full-swing BiCMOS NAND gate of Fig 4.4    | 43 |

xi

•

# List of Abbreviations and Symbols

| cq1:                 | Collector of bipolar transistor q1 open (transistor q1 stuck-open fault) |

|----------------------|--------------------------------------------------------------------------|

| DCVS:                | Differential Cascode Voltage Switch (logic)                              |

| DSL:                 | Differential Split-Level (logic)                                         |

| dsm4:                | Drain and Source of MOSFET $m_4$ shorted (MOSFET $m_4$ stuck- on fault)  |

| V <sub>be</sub> :    | Base-Emitter junction voltage of a bipolar transistor                    |

| V <sub>be,on</sub> : | Base-Emitter voltage when a (bipolar) transistor is turned ON            |

| V <sub>CE,ON</sub> : | Collector-Emitter voltage when a (bipolar) transistor is turned ON       |

| V <sub>DD</sub> :    | Power supply voltage                                                     |

| V <sub>REF</sub> :   | Reference voltage                                                        |

| V <sub>tpo</sub> :   | Zero bias threshold voltage of p-transistor                              |

| τ <sub>df</sub> :    | Propagation delay through a gate when output falls                       |

| τ <sub>œ</sub> :     | Propagation delay through a gate when output rises                       |

| V <sub>TN</sub> :    | Threshold voltage of n transistor                                        |

xii

## Chapter 1

## Introduction

1.1 Aims:

Recently CMOS is considered the mainstream technology for VLSI applications because of its low static power dissipation and high packing density [1]. But it demonstrates lower speed than other technologies such as Silicon Bipolar technology or Gallium-Arsenide technology [2]. The demand for superior performance, which has motivated the relentless search and development of new technologies, eventually lead the way towards the emergence of BiCMOS technology. It is the technology which merges old rivals, namely, CMOS and bipolar to complement each other, so that the strength of one covers the weakness of other. Today BiCMOS technology is one of the leading candidate technologies for future generations of high speed VLSI circuits. However the cost of BiCMOS processes, due to added complexity of merging CMOS and bipolar devices together, prevents this technology from being widely used in place of existing CMOS together, prevents this technology from being widely used in place of existing CMOS processes. Moreover the complex failure modes of various BiCMOS circuits speaks against it. Thus it is of great importance to study the effect of physical failures on BiCMOS logic circuits and the effect of these failures on the testing techniques currently employed for MOS and bipolar technologies. The objective of this research is to observe the behavior of different BiCMOS circuits under various faults. The impact of each possible single defect on the behavior of the circuits is analyzed by simulation. The research provides the results of a simulation based fault characterization study of BiCMOS logic circuits. Based on these results this research also aims at a comparative study of BiCMOS circuits with conventional CMOS logic circuits subjected to same faults, with a view to determine the suitability of these circuits for VLSI design. The performance of BiCMOS logic circuits in terms of speed, static power dissipation and propagation delay are also compared with the conventional CMOS logic circuits.

2

#### 1.2 Literature Review:

The main advantages of BiCMOS technology over CMOS technology are its high current driving capability and high speed [3],[4]. There are two main BiCMOS logic families. The first one is the conventional (Pull-up/Pull-down) family which uses a CMOS structure to implement the logic, followed by a bipolar output stage for high driving capability [4]. The second family uses a differential-mode logic whose operation is based on switching a fixed bias current between two branches [5], [6]. Introduction of bipolar drivers at the output stages of conventional CMOS logic gates significantly increases the gates' speed [3], [4]. However, to overcome the long turn-off time of bipolar transistors bleeding elements are added to speed the discharging of base charge [4], [7]. But conventional BiCMOS logic gates do not exhibit full logic swing. As a result they loose the performance leverage over CMOS circuits in the reduced voltage environment [8]. The emergence of emitter follower driver configuration with full swing techniques overcomes this problem. Full swing is achieved by shunting base and emitter of the complementary emitter follower driver with MOS diodes [4], [9], [10]. BiCMOS logic family using differential mode logic operates at high a speed in reduced supply voltage environment. High transconductance of bipolar devices is used in the evolution of BiCMOS DCVSL gates. It consists of a bipolar differential pair combined with the existing differential nchannel MOSFET logic tree of CMOS DCVSL technique [5]. Merged CMOS/Bipolar current switch logic is another structure of differential BiCMOS logic family which have several potential application in high speed VLSI circuits to shorten delay times through critical paths of complex circuits [6].

ł

Most of the work reported in the literature to-date on the testability of BiCMOS circuits has concentrated on fault characterization of the conventional family [11]-[15]. Different testing methods are also presented on the conventional BiCMOS gates [5], [6], [11], [16]. A design for testability (DFT) technique for detecting short and bridging fault in CMOS/BiCMOS logic circuits has been presented in [17]. The DFT technique applies for detecting the defects which causes an excessive increase in power supply current ( $I_{DDQ}$  fault). It has been claimed that about 67% of all possible shorts and bridging faults are detectable with this technique. However conventional BiCMOS circuits under stuck-open fault demand further investigation. A few work has also been done on the fault characterization and testing methods of differential BiCMOS logic circuits [12], [16], [18].

3

The topic of studying the effect of physical failures on basic BiCMOS circuits and the effect of these failures on the testing techniques currently employed for MOS and bipolar technologies is also attended in [11]. But the behavior of full swing BiCMOS circuits under various physical failures is the least attended topic.

#### 1.3 Organization of the thesis:

Chapter two introduces the various BiCMOS logic families. Also a brief introduction to CMOS logic circuits are presented in that chapter. In chapter three the performance of various BiCMOS circuits are investigated and compared to that of standard CMOS circuits. A detailed investigation into the behavior of various BiCMOS circuits under different single faults is carried out in chapter four. The results presented in this chapter are then compared with those of standard CMOS to asses their testability. Chapter five concludes this thesis with some recommendations for future work.

### Chapter 2

## CMOS/BiCMOS Logic Families and Faults

#### 2.1 Introduction :

This chapter introduces various CMOS/BiCMOS logic circuits. The principles of operation of conventional static CMOS, Differential CMOS, conventional BiCMOS and full swing BiCMOS circuits are described in detail. The chapter also focuses on the various faults that occur in integrated circuits and the fault models used to analyze the behavior of the faultv circuits.

#### 2.2 Various CMOS Circuit Techniques :

Recently CMOS has been accepted as the most widely used technology in VLSI applications. In this section conventional static CMOS and two different types of differential CMOS circuits: Differential Cascode Voltage Switch (DCVS) logic and Differential Split Level (DSL) CMOS logic are described.

#### 2.2.1 Conventional Static CMOS :

The structure of a conventional static CMOS logic gate consists of a driver network comprising only nMOS transistors and a load network comprising only pMOS transistors, where all MOSFETs are of enhancement mode [1]. The load network is connected between power supply  $V_{DD}$  and the output node. The driver network is connected between the output node and ground. The load and driver networks are never ON simultaneously rather they operate in antiphase. As a result, the output logic levels are independent of the sizes of load and driver networks. This is why CMOS circuits are referred to as "ratioless" circuits. When no input changes, then ideally there should be no current through the load and driver network.

Fig. 2.1 depicts the circuit diagram of a conventional CMOS NAND gate. It consists of enhancement mode nMOS transistors  $n_1$  and  $n_2$  as the driver network and enhancement pMOS transistors  $p_1$  and  $p_2$  as the load network. When both the inputs are raised to logic high level of 5 volts (which is much greater than the threshold voltage [1] of nMOS transistors), both nMOS transistors conduct and output node  $V_{our}$  is pulled down to ground (logic 0). For any other input vector either one or both the transistors in the load network conduct and output is pulled up to  $V_{DD}$  (logic 1). With such inputs no conducting path exists between  $V_{OUT}$  and ground due to OFF state of one or both the pMOS transistors [1].

#### 2.2.2 Differential Cascode Voltage Switch (DCVS) Logic :

Differential CMOS logic was introduced for speed improvement in CMOS logic circuits while maintaining the low quiescent power characteristics of CMOS circuitry [19],

6

[20]. Fig. 2.2 shows the basic logic gate using DCVS logic. In larger gates, the transistors  $m_3$  and  $m_4$  represent complimentary nMOS combinational logic trees for intended functions. Depending on the differential inputs D and  $\overline{D}$ , either the node Y or the node  $\overline{Y}$  is pulled down. Regenerative action sets the cross-coupled pMOS latch to static outputs Y and  $\overline{Y}$  having full differential high and ground logic levels. The logic trees do not draw direct current from the power supply after the circuit latches. Since the inputs drive only the nMOS devices, input gate capacitance loading is typically three times smaller than fully complementary CMOS circuits that require complementary nMOS and pMOS transistors to be driven[19]. Performance of the circuit is limited by the set time of the pMOS latch [19]. However "Clocked DCVS logic" overcomes the problems of long output settling time of pMOS latch of static DCVS logic [19].

#### 2.2.3 Differential Split-Level CMOS Logic :

The load and tree arrangement of DSL CMOS logic circuit is shown in Fig. 2.3. Here the load circuit consists of cross coupled current controlled cascode n and p transistors. This load is similar to that of DCVS circuit in Fig. 2.2. except two extra nMOS transistors  $m_3$  and  $m_6$  driven by a reference voltage  $V_{REF}$  have been introduced in the load. Let  $V_{REF}$  is set to  $(V_{DD}/2 + V_{TN})$ . If D is high (5v) and  $\overline{D}$  is low (0v), then  $m_3$  is ON and  $m_4$  is OFF. Then node  $\overline{A}$  has logic low level and node A has logic high level of  $V_{DD}$ . Node  $\overline{Y}$  is also pulled down to logic 0 through  $m_3$ . This turns  $m_2$  hard ON. The reference voltage determines the logic high level at node Y to be  $V_{DD}/2$ . For  $V_{DD} = 5v$  and  $V_{TN} = 1v$ , the voltage at Y is approximately 2.5 volts. Therefore,  $m_1$  is moderately conducting. This

7

causes a large leakage current and a voltage drop between nodes  $\overline{Y}$  and ground. The magnitude of this drop depends upon the number of n-transistors in series in the pull down path as well as their aspect ratios (W/L) [23]. If the inputs D and  $\overline{D}$  are now switched then m<sub>3</sub> turns ON and m<sub>4</sub> turns ON. The half  $V_{DD}$  level at Y discharges immediately and m<sub>1</sub> turns more ON to its high drive state. At the same time node  $\overline{A}$  and  $\overline{Y}$  start rising because m<sub>1</sub> was already partly ON, causing m<sub>2</sub> to switch faster to its low drive state than in the DCVS gate of Fig. 2.2. Because of the reduced voltage swing at the nodes  $\overline{Y}$  and Y, the delay due to wiring capacitance can be reduced by using them as the I/O nodes. The speed of operation of DSL circuit is maximum when the reference voltage is close to (V<sub>DD</sub>/2 + V<sub>TN</sub>) [23]. If V<sub>REF</sub> is increased further, the logic high level at Y (when D=5v and  $\overline{D} = 0v$ ) increases. As a result m<sub>1</sub> becomes less conducting, reducing the amount of leakage current which in turn reduces the voltage drop between  $\overline{Y}$  and ground. The leakage current at V<sub>REF</sub>=V<sub>DD</sub> is negligible. However, as V<sub>REF</sub> is increased from the optimum value, the speed of operation reduces.

#### 2.3 BiCMOS Logic Circuits :

CMOS and bipolar technologies have their weak and strong points. CMOS has qualified to be the most appropriate choice for VLSI applications because of its low DC power dissipation and its high packing density, yet its speed is limited by the capacitive loading. On the other hand, bipolar digital circuits outperforms CMOS in terms of speed, but are power consuming. Thus a performance gap exists between CMOS and bipolar and neither of them have the flexibility required to cover the gap. This can only be achieved by

Fig: 2.2 Basic logic gate in DCVS logic

Ŷ

a technology such as BiCMOS. Introducing bipolar drivers at the output stage of CMOS gate, significantly increases the gate's driving capability and hence its speed [3]. The objective of the synergy of bipolar and CMOS is to exploit the advantages of both at the circuit and system levels. In this section various BiCMOS circuits are introduced. The principles of operation of conventional BiCMOS logic gate as well as different full-swing BiCMOS gates are described.

#### 2.3.1 Conventional BiCMOS Logic :

• • •

Fig. 2.4(b) shows the early version of a BiCMOS inverter deduced from a basic CMOS inverter of Fig.2.4(a). Here the transconductance of both the p and n transistors of Fig. 2.4(a) are increased by adding a bipolar transistor at the output stage of each MOS device. The operation of BiCMOS inverter is similar to CMOS inverter. When the input is low (0v), pMOS is ON and its drain current turns the transistor  $Q_1$  ON. The collector current of  $Q_1$  charges the output load capacitance. As the output reaches  $V_{DD} - V_{BEON}$ ,  $Q_1$  gradually turns OFF. The HIGH DC level output is hence  $V_{DD} - V_{BEON}$ . If the input is high, transistor N is turned ON causing  $Q_2$  to turn ON to discharge the output node. As the output voltage reaches  $V_{BEON}$ , transistor  $Q_2$  turns OFF and the DC LOW level stays at  $V_{BEON}$ . The speed of this circuit is limited because of the long turn OFF time of the bipolar transistors. Therefore bleeding elements are added to speed the discharging of the base charge when the BJTs are turning OFF [4]. Fig. 2.5 shows a conventional BiCMOS inverter with  $N_{d1}$  and  $N_{d2}$  as the bleeder. The path between base of the bipolar and ground is created only when the bipolar transistor is to be turned OFF. Fig. 2.6 shows a basic

11

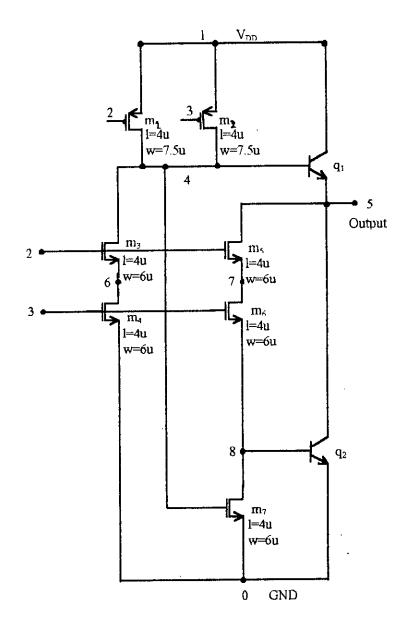

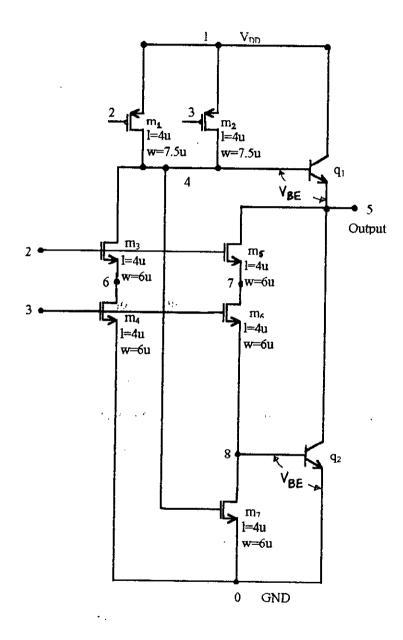

BiCMOS NAND gate. Transistors  $m_1$ ,  $m_2$ ,  $m_3$  and  $m_4$  implements the logic.  $m_7$  is ON during the pull-up stage and bleeds the base charge of  $Q_2$ .

#### 2.3.2 Full Swing BiCMOS Logic:

Recently, comparison of generic BiCMOS drivers have shown that the emitter follower driver configuration with full-swing techniques may extend the leverage of BiCMOS for scaled technologies [8]. Various full-swing BiCMOS logic circuits with the complementary emitter-follower driver configuration have been fabricated in a fully complementary BiCMOS technology [9], [10].

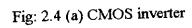

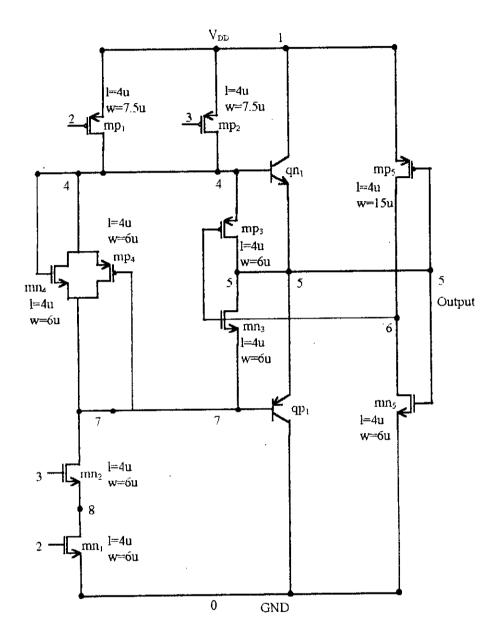

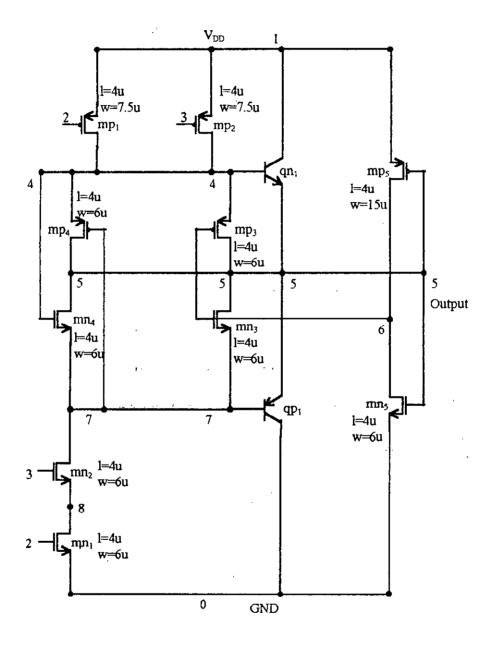

#### 2.3.2.1 Full-swing BiCMOS Logic using clamping diode :

Fig. 2.7 shows the basic full-swing complementary MOS/bipolar logic circuit realizing a two-input NAND function [10]. Logic is implemented in the CMOS stage ( $mn_1$ ,  $mn_2$ ,  $mp_1$  and  $mp_2$ ) and output is driven by the push pull complementary emitter follower ( $qn_1$  and  $qp_1$ ). Two base nodes (4 and 7) of the emitter follower are clamped to ensure that  $qn_1$  and  $qp_1$  are never turned ON simultaneously but biased near the edge of turn off in steady states. The clamping device is a CMOS diode which is a parallel pair of nMOS diode  $mn_4$  and pMOS diode  $mp_4$ . Full swing is achieved by the CMOS positive feedback network that shunts the base and emitter of  $qn_1$  and  $qp_1$  in a controlled manner. Gate terminals of the shunting devices ( $mp_3$  and  $mn_3$ ) are driven by the CMOS inverter ( $mn_5$ ,  $mp_5$  pair)that inverts the output signal and delays turn-on of  $mp_3$  (or  $mn_3$ ) during pull-up (or pull-down) until the output changes its logical state.

Initially when both the inputs are high (5v), node 7 is fully discharged to ground and, if mn<sub>3</sub> were OFF, output node 5 would stay at  $V_{BEp,on}$  which is the turn-on voltage of qp<sub>1</sub>. This low voltage is inverted by the output inverter and node 6 becomes high. This turns mn<sub>3</sub> fully ON, shorting output to GND and turning qp<sub>1</sub> OFF. In this state qp<sub>1</sub> is clamped off because mn<sub>4</sub> holds node 4 at  $V_{uno}$ , which is the zero bias threshold voltage of mn<sub>4</sub> assumed to be smaller than  $V_{BEn,on}$  of qn<sub>1</sub>. mp<sub>4</sub> is OFF due to the body effect and mp<sub>3</sub> is OFF. When input A falls to zero, mp<sub>2</sub> turns ON and its drain current charges up node 4 as well as node 7 through mn<sub>4</sub>. Because mp<sub>3</sub> remains OFF until the output crosses inverter logic threshold voltage, most of the current flows into the base of qn<sub>1</sub>, turning it ON. The output is then pulled up by a large emitter current of qn<sub>1</sub>. Since mn<sub>3</sub> is ON and mn<sub>4</sub> clamps the voltage between base nodes 4 and 7, qp<sub>1</sub> is held OFF and there is no crossover current through qp<sub>1</sub>.

When output (node 5) rises above the logic threshold voltage, voltage at node 6 falls falls to GND and mn<sub>3</sub> will be OFF immediately. At this point, since  $V_4$  (= $V_5 + V_{BEn,on}$ ) will be greater than  $|V_{\psi}|$ , mp<sub>3</sub> turns ON bypassing a fraction of the qn<sub>1</sub> base current to the output. Although this causes the final output transient to be slower, because the output has already changed its logical state, the circuit speed will not be degraded. Finally when  $V_4$ = $V_7$  the threshold voltages of mp<sub>3</sub> and mp<sub>4</sub> return to  $V_{\mu\rho}$ . Then mp<sub>3</sub> strongly discharges the base-emitter junction of qn<sub>1</sub>, pulling up the output to  $V_{DD}$  and turning qn<sub>1</sub> OFF. The diode mp<sub>4</sub> clamps  $V_7$  at  $V_{DD} - |V_{\mu\rho}|$  preventing qp<sub>1</sub> from turning ON. If the input A is changed back to logic high, the circuit operates in a complementary way. Because the output level of this circuit reaches the full supply rails after the feedback inverter changes its logical state minimum operation voltage of this circuit is the larger of  $V_{BEn,on} + V_{LT}$  or

and the action of the state of the state of the

services and the service of the service of the

••, •

13

$(V_{BEp,on} + V_{DD} - V_{LT})$  where  $V_{LT}$  is the logic threshold voltage of the feedback inverter. For a symmetric case minimum  $V_{DD}$  is  $2V_{BE,on}$ .

Performance of this type of circuit mainly depend on parasitic capacitances at nodes 4 and 7, current voltage characteristics of the clamping diode and details of the full swing circuitry. Reduction of parasitic capacitances (by reducing W/Ls of  $mn_3$  and  $mp_3$ ) at these prevent excessive base current bypassing and premature cutoff of  $qn_1$  and  $qp_1$  during active periods and essentially improve the speed.

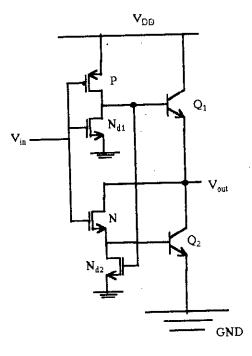

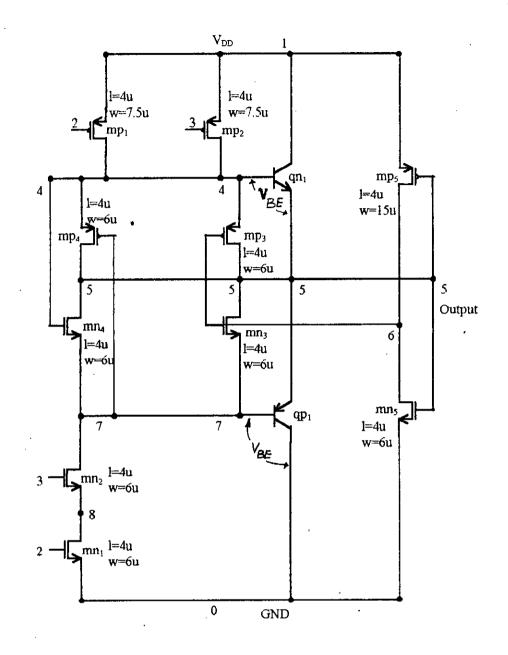

#### 2.3.2.2 Low capacitance variation of Full-swing BiCMOS Logic :

The parasitic capacitances at nodes 4 and 7 of Fig. 2.7 can be reduced by modifying the CMOS diode as in Fig. 2.8. Comparing the two the drain terminals of  $mn_4$ and  $mp_4$  are connected to the output node in this circuit, instead of nodes 4 and 7 respectively. So this circuit has less parasitic at nodes 4 and 7 by as much as the drain junction capacitances of  $mn_4$  and  $mp_4$  [9]. However this CMOS diode operates differently and has a higher clamping voltage because of the body effect. When both inputs are ONE base node 7 and output node 5 are shorted to GND. Thus  $mp_4$  functions as a MOSFET diode biasing node 4 at  $|V_{tp}|$  [9]. For  $qn_1$  to be clamped OFF, this bias voltage  $|V_{tp}|$ must be smaller than  $V_{BEn,en}$ . Therefore a zero bias threshold voltage much smaller than the BJT turn-on voltage is required for  $mp_4$ . This requirement also applies to  $mn_4$  due to complementary nature if so  $mn_4$  is ON providing an additional shunt path between node 7 and output node 5 because its gate-source bias is larger than its threshold voltage. During pull-up transient, node 7 is clamped by  $mn_4$  operating in source follower mode. Since the voltage between nodes 4 and 7 is close to  $V_{BEn,om}$  a small fraction of base current for  $qn_1$

GND

$V_{\rm in}$

Fig: 2.4 (b) BiCMOS inverter

Ţ

Fig: 2.5 Conventional BiCMOS inverter

Fig. 2.6 Basic BiCMOS NAND gate

-

ſ

Fig: 2.7 Basic Full-Swing BiCMOS NAND gate

٦<u>(</u>

leaks through mp<sub>4</sub> to the output. As the output is pilled up, mn<sub>4</sub> gets weaker but mp<sub>4</sub> becomes stronger because of the body effect. When the output is high, mn<sub>4</sub> clamps node 7 at  $V_{DD}$  -  $V_{tn}$  and prevents qp<sub>1</sub> from turning ON as long as  $V_{tn}$  is smaller than  $V_{BEp.on}$  of qp<sub>1</sub>. Similarly during pull down, node 4 is clamped by mp<sub>4</sub> operating in a source follower mode [9], [10].

#### 2.4 Physical failures in ICs :

Various physical failures can occur in ICs [11], [22]. Physical defects can occur during the fabrication of an IC or during its use. A defect that causes a change of the logical function of the circuit can be represented by a logical abstraction known as logical fault. Similarly a defect that causes a change in a continuous parameter of the circuit can be represented by an abstraction called a parametric fault.

BiCMOS devices are subjected to most of the defects which occurs in each of the CMOS and bipolar technologies. The most prevalent failures in bipolar technology are [11]: (1) open connections, (2) shorts between connections, (3) "piped" transistors with excessive emitter to collector leakage current. Similarly the defects which can be found in MOS ICs are: (1) shorts (e.g., gate oxide shorts), (2) opens (e.g., intragate breaks), and (3) circuit degradation (e.g., threshold voltage variations).

When a vector is applied to a faulty device which produces an incorrect response, an error is said to have occurred. However, if we try to derive test vectors for every possible physical failure in a VLSI chip, the problem would soon become unmanageable. In order to successfully tackle the problem, physical failures in a chip are represented with the help of a fault model.

#### 2.4.1 Stuck-at Fault Model :

In stuck-at fault model it is assumed that the fault causes a line in the circuit to behave as if it is permanently at logic 0 or logic 1 [22]. If the line is permanently at logic 0 it is said to stuck-at 0, otherwise if the line is permanently at logic 1 it is said to be stuck-at 1.

#### 2.4.2 Stuck-on Fault Model :

If a fault causes a transistor to conduct continuously, the transistor is said to be stuck-on [11], [22]. When a defect causes a bipolar to become permanently ON it is assumed in this model that the bipolar's collector and emitter terminals are shorted through a fault resistance whose value depends upon the fault strength. Similarly, stuck-on fault in MOS devices are modeled by shorting its source and drain nodes through the fault resistance.

#### 2.4.3 Stuck-open Fault Model :

When a transistor is rendered non-conducting by a faulty it is said to be stuck-open. A stuck-open fault may force a combinational CMOS circuit to behave in a sequential fashion. Thus in order to detect a stuck-open fault, a sequence of vectors is required. To model an open fault of a device terminal, a large resistance is inserted between the device terminal and the circuit node to which the terminal would otherwise be connected.

### Chapter 3

# Performance of BiCMOS Logic Circuits

#### 3.1 Introduction:

BiCMOS as an emerging technology has faced fierce opposition due to the increased cost of adding BJTs to a conventional CMOS process. Nevertheless BiCMOS has been widely accepted due to their high performance and high speed. This chapter aims at a detailed analysis of the performance of BiCMOS circuits. Basic BiCMOS as well as full swing BiCMOS circuits are analyzed. These circuits are simulated to determine the propagation delay, static power dissipation and output logic low and high voltage level. Propagation delays are measured with additional loading. Their performances are then compared with the performance of conventional static CMOS circuits.

#### 3.2 Test Arrangement:

To analyze and compare the performance of various BiCMOS circuits, a cascaded chain of three two-input NAND gates are used as shown in Fig. 3.1. One of the inputs of each NAND gate is tied internally to a logic high level of 5 volts. The other input is connected to the output of the preceding gate. Additional capacitive load is placed at the output of each gate.

A structured approach is adopted for simulation of the cascaded chain of Fig. 3.1. Description of only one NAND gate of Fig. 3.1 is written using the subcircuit function of SPICE [25]. Then the whole cascaded chain is modeled in a main SPICE program by making three references to the subcircuit. Propagation delay between the input and output of the second stage is measured. Static power dissipation is measured for all the three gates.

#### 3.3 Spice Simulation Results:

As mentioned earlier cascaded chain of Fig. 3.1 has been simulated using three types of NAND gates: (i) Basic BiCMOS, (ii) Full-Swing BICMOS and (iii) Conventional CMOS. The circuit diagrams of these NAND gates are shown in Figures 3.2, 3.3 and 3.4 respectively. Width and length of the MOS devices shown in the figures are used for simulating the circuits. Table 3.1 presents the SPICE simulation results on cascaded chain of NAND gates.

| Circuit                     | Logic Level (volts) |                   | Static Power Dissipation<br>(nw) |

|-----------------------------|---------------------|-------------------|----------------------------------|

|                             | VLOW                | V <sub>HIGH</sub> |                                  |

| Conventional CMOS NAND gate | 0                   | 5                 | $2.42 \times 10^{-1}$            |

| Basic BiCMOS gate           | 0.263               | 4.675             | $7.18 \times 10^{44}$            |

| Full swing BiCMOS gate      | 0                   | 5                 | $3.51 \times 10^{+1}$            |

Table 3.1: SPICE simulation results showing output Logic levels and Power dissipation

Regarding output logic level, the full swing BiCMOS circuit of Fig. 3.3 achieves the same rail to rail swing as the conventional CMOS circuit of Fig. 3.4. Depending on the inputs, in a conventional CMOS gate, either the driver or the load network are active and thereby connects output to either ground or  $V_{DD}$  respectively. Thus, the circuit achieves full voltage swing (refer to section 2.2.1). As for the full swing BiCMOS gate (Fig. 3.3), after initial pull up through the bipolar qn<sub>1</sub> to ( $V_{DD} - V_{BE,on}$ ), rail to rail swing is achieved by the shunting MOS device mp<sub>3</sub>. During pull down, mn<sub>3</sub> operates to achieve logic low level of 0 volt. This phenomenon was described in section 2.3.2.2.

For the basic BiCMOS gate of Fig. 3.2, output achieves partial swing. Bipolar drivers prevents the output from attaining full  $V_{DD}$  swing since they remain at the edge of turning ON after the output is pulled up or pulled down to a certain extent. The behavior of this circuit was described in section 2.3.1.

It is found in Table 3.1 that the static power dissipation in basic BiCMOS circuit is approximately 10<sup>5</sup> orders of magnitude higher than that in conventional CMOS circuit. However, the power dissipation in full-swing BiCMOS circuit is about 10<sup>2</sup> order of magnitude higher than conventional CMOS circuits. Thus, full-swing BiCMOS is advantageous compared to basic BiCMOS in terms of static power dissipation.

| Output<br>Capacitance | Conventional CMOS gate |                  |                 |                  | Full Swing BiCMOS gate |                  |

|-----------------------|------------------------|------------------|-----------------|------------------|------------------------|------------------|

| (pF)                  | $\tau_{\rm df}$ (ns)   | $\tau_{dr}$ (ns) | $\tau_{df}(ns)$ | $\tau_{dr}$ (ns) | $\tau_{df}(ns)$        | $\tau_{dr}$ (ns) |

| 0.1                   | 1.66                   | 1.23             | 0.35            | 00.17            | 1.02                   | 0.26             |

| 1                     | 17.05                  | 12.25            | 0.78            | 0.33             | 1.1                    | 0.46             |

| 2.5                   | 42.75                  | 30.78            | 1.33            | 0.60             | 1.42                   | 0.37             |

| 4                     | 68.18                  | 49.2             | 1.88            | 0.90             | 1.86                   | 0.61             |

| 5                     | 85.29                  | 61.03            | 2.21            | 1.05             | 2.14                   | 0.78             |

Table 3.2: SPICE simulation results showing propagation delay

Table 3.2 presents the propagation delays of the NAND gates obtained from SPICE simulation on the three types of logic circuits under consideration. The results confirm the advantage of BiCMOS circuits over conventional CMOS circuits with speed as the criterion of comparison. The propagation delays of various gates are plotted as a function of load capacitance in Fig. 3.5. The figure shows that the delays for basic BiCMOS and full-swing BiCMOS gates are very close for various loading conditions. However, when the propagation delays of the BiCMOS gates are plotted on an expanded time scale as in Fig. 3.6, the full-swing BiCMOS is found to be slightly faster than basic BiCMOS at small load. With increased capacitive loading, the delays of two types of BiCMOS gates are found to be almost the same. Delays in BiCMOS circuits are considerably small as compared to the delays in conventional CMOS circuits due to the high current driving capability of bipolar drivers at the output stages of BiCMOS gates. However, as can be seen from Table 3.2, the propagation delay when the output rises ( $\tau_{dr}$ ) is much lower than the delay when the output falls  $(\tau_{df})$  for both types of BiCMOS gates. Since the sources of the load network ( $m_1$  and  $m_2$ ) are connected to the power supply voltage  $V_{DD}$ , body effect cannot adversely affect the operation of these transistors. As a result, when input to m1 or m2 falls to  $(V_{DD} - |V_{tro}|)$  the respective transistor turns fully ON and connects base of  $q_1$  to  $V_{DD}$ . The large emitter current of q1 then charges the output towards high logic level. During the falling transition, body effect adversely affects the turning ON of the n-MOS transistors m<sub>3</sub>, m<sub>5</sub> and m<sub>6</sub> since their source nodes are not grounded. Also, m7 remains ON until node 4 is pulled down below  $V_m$  and bypasses a fraction of base current for  $q_2$  from the output. Consequently its emitter current is not as large as the current during pull up transient. This causes output transition from logic high to logic low level slower than the transition from low to high level.

3.4 Comparison:

The SPICE simulation results presented in the last section have been analyzed. A comparison of these results for the various types of circuits leads to the following conclusions:

- BiCMOS circuits are much faster than conventional CMOS circuits at nominal loading conditions. The speed advantage of BiCMOS circuits become more and more prominent with increasing capacitive load.

- The speed of basic and full-swing BiCMOS circuits are very close for various capacitive loads except at small load when the later shows slight speed advantage over the former.

- While conventional CMOS and full-swing BiCMOS circuits have full output logic swing, the basic BiCMOS circuit has a reduced output swing. Thus, basic BiCMOS circuits have a lower noise immunity compared to other two classes of circuits under consideration.

- Power dissipation in BiCMOS circuits are higher than that in conventional CMOS circuits. Full-swing BiCMOS circuits have much lower static power dissipation than basic BiCMOS circuits.

Fig: 3.1 Cascaded chain of three two-input NAND gates

Fig: 3.3 Full-Swing BiCMOS NAND gate

Fig: 3.5 Propagation delay vs. output capacitance

Fig: 3.6 Propagation delay vs. output capacitance for BiCMOS circuits

## Chapter 4

# Fault Characterization of BiCMOS

Logic Circuits

#### 4.1 Introduction:

The behavior of different BiCMOS logic circuits under various faults are investigated in this chapter. Various modes of failure can occur in VLSI circuits resulting in stuck-at, stuck-on, stuck-open, bridging faults etc. To avoid the complexity of dealing with multiple defect case, it is assumed in this chapter that not more than one defect can occur at a time. Single stuck-on and single stuck-open faults in MOS logic transistors and bipolar transistors are considered. Multiple faults are clearly possible but it seems reasonable to suppose that a circuit with two faults will still fail test programs. Of course there may be fault masking but very few researchers believe that this is a significant problem in practice [22]. Another reason to support single stuck fault model is that due to exponential rise of multiple fault conditions with the number of nodes, it may not be feasible to consider all the possibilities [22]. The results of extensive SPICE simulation using various fault models are presented in this chapter.

#### 4.2 Fault Modeling:

Physical defects in VLSI circuits can be modeled as opens or shorts in switch level representation [11], [22]. For a more realistic modeling the possibility of a short between two terminals (collector-emitter for bipolar and drain-source for MOS) of a transistor as well as an open in one transistor node (collector or emitter for bipolar and drain or source for MOS) are considered. Shorts are modeled as a small resistor between two nodes. Open circuits are modeled as a large resistor inserted between the affected node and the node to which it would normally have been connected. The values of the resistors, modeling shorts and opens, are varied in a wide range to take into account faults of various strengths.

The following nomenclatures are used to represent various faults in a circuit:

If a fault is caused by a short between two nodes of a transistor, it is referred to by the first letters of those nodes, followed by the name of the transistor; e.g., a fault caused by a short between drain and source of MOS  $m_2$  will be referred to as  $dsm_2$ . This fault is also referred to as a transistor stuck-on fault. Stuck-on fault in an active device means that the device is permanently ON even in the absence of an input excitation. An open fault at a transistor node will be referred to by the first letter of that node, followed by the name of the transistor; e.g., an open in the collector of  $q_1$  will be denoted by  $cq_1$ . This fault can also be defined as transistor stuck-open fault. With this fault an active device remains permanently OFF even in the absence of any input excitation.

Figures 4.1 and 4.2 shows how these two types of faults are modeled.

Fig. 4.1 Stuck-on fault model for MOS m<sub>4</sub>

Fig. 4.2 Stuck-open fault model for bipolar q1

#### 4.3 Behavior Of BiCMOS Circuits Under Single Stuck Faults:

The behavior of BiCMOS circuits under single stuck-on and single stuck-open fault in MOS and bipolar parts are analyzed in this section. Both the basic BiCMOS and full-swing low-capacitance BiCMOS circuits are considered. The two input NAND gates shown in Figures 4.3 and 4.4 for the basic and full-swing BiCMOS case are used in this analysis.

4.3.1 Stuck-on Faults:

$dsm_4$ : (Stuck-on fault in  $m_4$  of Fig. 4.3)

Referred to Fig. 4.3 physical defects may cause  $m_4$  to be permanently ON, thus causing a stuck-on fault. The fault is sensitized when  $V_2 = 5v$  and  $V_3 = 0v$  are applied. In a fault free circuit these vectors would have pulled the output node 5 to a high level of  $(V_{DD} - V_{BE})$ . The input vectors causes  $m_3$  and  $m_2$  to turn on. With dsm<sub>4</sub>,  $m_4$  is also ON and a low resistance path is thus

established from  $V_{DD}$  to ground. This causes supply current to increase. The amount of current depends on the resistances of the ON transistors (m<sub>2</sub> and m<sub>3</sub>) and the fault strength at m<sub>4</sub>. The voltage at the internal node 4 also depends on the ON resistances of m<sub>2</sub> and m<sub>3</sub>, and on the fault strength. Since the ON resistance of a transistor depends on its geometry, therefore for a particular value of fault resistance, the voltage V<sub>4</sub> is independent of the sizes of transistors m<sub>2</sub> and m<sub>3</sub>. That is when the circuit is sensitized for dsm<sub>4</sub> then the voltage V<sub>4</sub> varies with device geometry and fault strength. Therefore V<sub>4</sub> can have any value between 0 and 5v depending on device geometry and fault strength. Consequently the output voltage at node 5 may have any value between logic low to logic high level with it's value less than V<sub>4</sub> by V<sub>BE</sub>. Under the fault sensitized condition m<sub>6</sub> remains OFF thus no base current for q<sub>2</sub> and it remains OFF. Thus, the fault dsm<sub>4</sub> is not detectable by logic monitoring. However, it may be detected by the increase in power supply current.

#### dsmn<sub>1</sub>: (Stuck-on fault in mn<sub>1</sub> of Fig. 4.4)

For a stuck-on fault in the full swing BiCMOS NAND gate (referred to Fig. 4.4), behavior is almost the same as that of the basic BiCMOS gate described above. This fault is sensitized when  $V_2 = 0v$  and  $V_3 = 5v$  are applied. Therefore mp<sub>1</sub> is turned ON thus pulling  $V_4$  to a high value, turning qn<sub>1</sub> ON, and consequently charging the output node 5. However, as mn<sub>2</sub> is ON ( $V_3 = 5v$ ) and mn<sub>1</sub> is also ON due to fault, node 7 has a low resistance path to ground. Then due to high output node,  $|V_{BE}| > |V_{BEon}|$  for qp<sub>1</sub>. The output discharges through qp<sub>1</sub> and at the same time it is charged up through qn<sub>1</sub>, thereby causing large supply current. Again due to lower  $V_7$ ,  $V_{GS}$  for mn<sub>4</sub> is greater than  $V_{tn}$  and  $|V_{GS}|$  for mp<sub>4</sub> is greater than  $|V_{tp}|$ , so these transistors are also ON, providing another current path from  $V_{DD}$  to ground. The current is constant for a particular device geometry. The node voltage  $V_4$  depends on the ON resistances and thus on the device geometry of mp<sub>1</sub>, mp<sub>4</sub>, mn<sub>4</sub>, mn<sub>2</sub>, as well as on the fault strength at mn<sub>1</sub>. Therefore,  $V_4$  may have any value between 0v and  $V_{DD}$ . As a result output at node 5 under fault is indeterminate. Hence, in similarity with dsm<sub>4</sub>, this fault cannot be detected by logic monitoring. However, it may be detected by current monitoring.

#### $dsm_1$ : (Stuck-on fault in $m_1$ of Fig. 4.3)

When  $m_1$  is permanently ON, the fault is sensitized by applying  $V_2=V_3=5v$ . Thus  $m_3$  and  $m_4$  are ON. Due to faulty  $m_1$  a low resistance path is established between  $V_{DD}$  and ground. Consequently there is a large power supply current when the fault is sensitized. The voltage at node 4 then depends on the resistances (thus on device geometry) of  $m_3$  and  $m_4$  and on the fault strength at  $m_1$ . If  $m_1$  is very strongly ON then the voltage drop across  $m_1$  may be so small that  $V_4$  may have a high logic level. This causes  $q_1$  to turn ON thereby charging output node #5. High  $V_4$  also causes  $m_7$  to turn ON. As  $m_5$  and  $m_6$  are ON due to the input vectors,  $q_2$  turns on. The output tends to discharge through  $q_2$  and at the same time it is charged up by  $q_1$ . Therefore, there would be large increment in supply current when the fault dsm<sub>1</sub> is sensitized. However, the output logic level is unpredictable.

If  $m_1$  is very poorly ON,  $V_4$  may have a much lower voltage level turning  $q_1$  either very weakly ON or OFF. Consequently  $V_5$  will have a much lower voltage level than for the case discussed above (when  $m_1$  was assumed strongly ON).

Fig: 4.3 Basic BiCMOS NAND gate

Fig: 4.4 Full-Swing BiCMOS NAND gate

ł

36

f

.

### dsmp<sub>1</sub>: (Stuck-on fault in mp<sub>1</sub> of Fig. 4.3)

Fault sensitizing vector is the same as  $dsm_1$ , i.e.,  $V_2=V_3=5v$ . Faulty mp<sub>1</sub> causes node 4 to be charged up. If  $V_4$  is a reasonably high voltage then qn<sub>1</sub> turns on and output node 5 charges up towards ( $V_4 - V_{BE}$ ). High inputs connect node 7 to ground. As a result qp<sub>1</sub> turns on and large power supply current flows as in the case of dsm<sub>1</sub>. Output logic is unpredictable as well. Low  $V_7$ also causes mp<sub>4</sub> to turn ON and high  $V_4$  causes mn<sub>4</sub> to turn ON. Thus another conducting path is established from  $V_{DD}$  to ground through faulty mp<sub>1</sub>, and mp<sub>4</sub>, mn<sub>4</sub>, mn<sub>2</sub> and mn<sub>1</sub>. If mp<sub>1</sub> is weakly ON due to the fault then the voltages at node 4 and node 5 may be much lower than the case when mp<sub>1</sub> is strongly ON.

ceq<sub>1</sub>: (Stuck-on fault in q<sub>1</sub> of Fig. 4.3)

The fault is sensitized by applying  $V_2 = V_3 = 5v$ . In a fault free circuit the output would have been pulled down to logic low level. However, due to the fault the output node 5 is always connected to  $V_{DD}$  through  $q_1$ . Due to the input vectors  $m_5$  and  $m_6$  are ON and connect the base of  $q_2$  to the output node 5 thus turning it ON. This causes a large increment in power supply current when the fault is sensitized. This current depends on the fault strength. Also, the output voltage level at node 5 is unpredictable and depends on how hard  $q_1$  is ON. Therefore, the stuckon fault in  $q_1$  can not be detected by logic monitoring. However, it may be detected by current monitoring

## ceqn<sub>1</sub>: (Stuck-on fault in qn<sub>1</sub> of Fig. 4.4)

The behavior of the circuit under  $ceqn_1$  fault is little more complicated than the corresponding fault in the basic BiCMOS gate. The fault  $ceqn_1$  in Fig. 4.4 is sensitized by the

• 4.7 // // application of  $V_2 = V_3 = 5v$ . For these inputs, the output  $V_3$  in a fault free gate would be low. However, due to the fault output node 5 is always connected to  $V_{DD}$  through the permanently ON transistor qn<sub>1</sub>. Thus, output node 5 may attain a high voltage level. High output causes  $V_6$  to become low. Depending on the previous states of the inputs, low  $V_6$  may cause mp<sub>3</sub> to turn ON. Also, due to ON states of mn<sub>1</sub> and mn<sub>2</sub>, node 7 is connected to ground and mp<sub>4</sub> will be ON. Thus node 4 is charged by the output current through mp<sub>4</sub> and mp<sub>3</sub> and  $V_4$  becomes equal to the output voltage. The rise in  $V_4$  causes mn<sub>4</sub> to turn ON and offers output current a parallel path through mn<sub>4</sub>, mn<sub>2</sub> and mn<sub>1</sub>. Thus voltage at node 7 is clamped by mn<sub>4</sub> at ( $V_4 - V_m$ ).

For a poorly ON transistor  $(qn_1)$  output may assume low state (1v to 2v). Depending on the aspect ratio (W/L) of output inverter, V<sub>6</sub> may be high enough so that mp<sub>3</sub> remains in the OFF state. This high V<sub>6</sub> will then cause mn<sub>3</sub> to turn ON and provide an additional path for the output current to pass through mn<sub>1</sub> and mn<sub>2</sub>. However, mp<sub>4</sub> will still be ON due to ON states of mn<sub>1</sub> and mn<sub>2</sub> causing node 4 to charge up until V<sub>4</sub> equals V<sub>5</sub>. Then mn<sub>4</sub> turns ON and clamps V<sub>7</sub> at (V<sub>4</sub> -V<sub>in</sub>). It is clear that there will be a significant increment in power current when the fault ceqn<sub>1</sub> is sensitized. However, the output logic level is unpredictable.

ceq<sub>2</sub>: (Stuck-on fault in q<sub>2</sub> of Fig. 4.3)

The fault is sensitized when one (or both) of the input line is grounded. Thus node 4 is pulled up to logic high state and  $q_1$  turns ON. Due to faulty  $q_2$  a low resistance path is established between  $V_{DD}$  and ground. The voltage  $V_{DD}$  is divided between the transistors  $q_1$  and  $q_2$  according to the ratio of their ON resistances. As  $q_1$  operates in the linear region, a constant current flows through  $q_1$  and  $q_2$  depending on the fault strength at  $q_2$ . When fault resistance is low the current is

high and the output node 5 may remain at a logic low level. However, for a very large fault resistance at  $q_2$ , the output may attain a logic high level.

ceqp<sub>1</sub>: (Stuck-on fault in qp<sub>1</sub> of Fig. 4.4)

The behavior of the full swing BiCMOS circuit under this fault is similar to the fault ceq<sub>1</sub> in the basic BiCMOS NAND gate. Depending on the fault strength output logic level may be at any state between 0v to 5v. Fault sensitizing pattern (one or both of the input grounded) turns  $qn_1$  ON. Thus  $V_{DD}$  is connected to ground through  $qn_1$  and the faulty  $qp_1$ . As a result, power supply current increases. Low fault resistance causes output to remain at logic low level. Then  $V_6$  is high which causes  $mn_3$  to turn ON and pulling node 7 to output voltage level. As a result |  $V_{BE}$  | for  $qp_1$  is zero and it is clamped OFF. With increasing fault resistance output increases to logic high level.  $V_4$  is always greater than output level by  $V_{BE}$ . High  $V_4$  causes  $mn_4$  to turn ON and node 7 is pulled to the output level.

#### 4. 3. 2 Spice Simulation Results For Stuck-On Faults:

This section summarizes the SPICE simulation results for a single stuck-on fault in both the MOS and bipolar sections of the basic BiCMOS NAND gate as well as the full swing BiCMOS NAND gate. Length of all the MOS devices are taken as  $4\mu m$  and SPICE Level-2 mode parameters are used for simulating the circuits.

| Fault | Fault      | Transistor    | Input | Logic |       | Output V <sub>5</sub> | Power Supply            |

|-------|------------|---------------|-------|-------|-------|-----------------------|-------------------------|

|       | Resistance | Size          |       |       | Volts | Volts                 | Current                 |

|       | Ohms       | $W_{P}/W_{N}$ | $V_1$ | $V_2$ |       |                       | $I(V_{DD}) * 10^{-4} A$ |

| dsm₄  | 1          | 7.5/24        | 5     | 0     | 0.828 | 0.335                 | 4.55                    |

| dsm₄  | 10         | 7.5/24        | 5     | 0     | 0.833 | 0.340                 | 4.55                    |

| dsm₄  | 100        | 7.5/24        | 5     | 0     | 0.879 | 0.385                 | 4.54                    |

| dsm₄  | 1K         | 7.5/24        | .5    | 0     | 1.317 | 0.823                 | 4.36                    |

| dsm₄  | 1          | 7.5/6         | 5     | 0     | 2.913 | 2.418                 | 3.09                    |

| dsm₄  | 10         | 7.5/6         | 5     | 0     | 2.915 | 2.420                 | 3.09                    |

| dsm₄  | 100        | 7.5/6         | 5     | 0     | 2.940 | 2.444                 | 3.06                    |

| dsm₄  | 1K         | 7.5/6         | 5     | 0     | 3.151 | 2.813                 | 2.82                    |

| dsm₄  | 1          | 24/6          | 5     | 0     | 4.342 | 4.369                 | 3.68                    |

| dsm4  | 10         | 24/6          | 5     | 0     | 4.343 | 4.371                 | 3.67                    |

| dsm₄  | 100        | 24/6          | 5     | 0     | 4.352 | 4.570                 | 3.63                    |

| dsm₄  | 1K         | 24/6          | 5     | 0     | 4.428 | 3.934                 | 3.23                    |

Table 4.1: SPICE simulation results for stuck-on fault in nMOS transistor m₄ in the basicBiCMOS NAND gate of Fig 4.3

Table 4.2: SPICE simulation results for stuck-on fault in nMOS transistor mn1 in the full-swingBiCMOS NAND gate of Fig 4.4

|                   | Fault      | Transistor | Input          | Logic | V <sub>7</sub> | V <sub>4</sub> | Output V <sub>5</sub> | Power Supply            |

|-------------------|------------|------------|----------------|-------|----------------|----------------|-----------------------|-------------------------|

| Fault             | Resistance | Size       | V <sub>2</sub> | $V_3$ | Volts          | Volts          | Volts                 | Current                 |

|                   | Ohms       | $W_P/W_N$  |                |       |                |                |                       | $I(V_{DD}) * 10^{-2} A$ |

| dsmn <sub>1</sub> | 1          | 7.5/24     | 5              | 0     | 0.743          | 2.472          | 1.608                 | 3.35                    |

| dsmn <sub>1</sub> | 10         | 7.5/24     | 5              | 0     | 0.746          | 2.476          | 1.611                 | 3.351                   |

| dsmn1             | 100        | 7.5/24     | 5              | 0     | 0.781          | 2.510          | 1.646                 | 3.319                   |

| dsmn <sub>1</sub> | 1K         | 7.5/24     | 5              | 0     | 0.8            | 2.54           | 1.66                  | 3.25                    |

| dsmn <sub>1</sub> | 1          | 7.5/6      | 5              | 0     | 1.764          | 3.467          | 2.616                 | 1.99                    |

| dsmn <sub>1</sub> | 10         | 7.5/6      | 5              | 0     | 1.765          | 3.468          | 2.617                 | 1.98                    |

| dsmn1             | 100        | 7.5/6      | 5              | 0     | 1.775          | 3.477          | 2.626                 | 1.96                    |

| dsmn <sub>1</sub> | 1K         | 7.5/6      | 5              | 0     | 1.867          | 3.564          | 2.716                 | 1.79                    |

| dsmn <sub>1</sub> | 1          | 24/6       | 5              | 0     | 2.652          | 4.370          | 3.511                 | 2.73                    |

| dsmn <sub>1</sub> | 10         | 24/6       | 5              | 0     | 2.654          | 4.372          | 3.513                 | 2.72                    |

| dsmn1             | 100        | 24/6       | 5              | 0     | 2.656          | 4.374          | 3.516                 | 2.72                    |

| dsmn <sub>1</sub> | 1K         | 24/6       | 5              | 0     | 2.66           | 4.377          | 3.518                 | 2.69                    |

| Fault            | Fault<br>Resistance<br>Ohms | Transistor<br>Size<br>W <sub>P</sub> /W <sub>N</sub> | Input<br>V <sub>1</sub> | Logic<br>V <sub>2</sub> | V₄<br>Volts | Output V <sub>3</sub><br>Volts | Power Supply<br>Current<br>I (V <sub>DD</sub> ) *10 <sup>-3</sup> A |

|------------------|-----------------------------|------------------------------------------------------|-------------------------|-------------------------|-------------|--------------------------------|---------------------------------------------------------------------|

| dsm <sub>1</sub> | 1                           | 7.5/24                                               | 5                       | 5                       | 4.999       | 4.215                          | 2.21                                                                |

| dsm <sub>1</sub> | 10                          | 7.5/24                                               | 5                       | 5                       | 4.992       | 4.208                          | 2.21                                                                |

| dsm <sub>1</sub> | 100                         | 7.5/24                                               | 5                       | 5                       | 4.923       | 4.138                          | 2.25                                                                |

| dsm <sub>1</sub> | 1K                          | 7.5/24                                               | 5                       | 5                       | 4.25        | 3.462                          | 2.43                                                                |

| dsm <sub>1</sub> | 10K                         | 7.5/24                                               | 5                       | 5                       | 1.395       | 0.738                          | 0.37                                                                |

| dsm <sub>1</sub> | 1                           | 7.5/6                                                | 5                       | 5                       | 4.999       | 4.216                          | 1.64                                                                |

| dsm <sub>1</sub> | 10                          | 7.5/6                                                | 5                       | 5                       | 4.997       | 4.214                          | 1.65                                                                |

| dsm <sub>1</sub> | 100                         | 7.5/6                                                | 5                       | 5                       | 4.979       | 4.195                          | 1.66                                                                |

| dsm <sub>1</sub> | 1K                          | 7.5/6                                                | 5                       | 5                       | 4.797       | 4.011                          | 1.75                                                                |

| dsm <sub>1</sub> | 10K                         | 7.5/6                                                | 5                       | 5                       | 3.232       | 2.451                          | 1.44                                                                |

Table 4.3: SPICE simulation results for stuck-on fault in pMOS transistor m1 in the basicBiCMOS NAND gate of Fig 4.3

Table 4.4: SPICE simulation results for stuck-on fault in pMOS transistor mp1 in the full-swingBiCMOS NAND gate of Fig 4.4

| Fault             | Fault              | Transistor                             | Input          | Logic | V <sub>7</sub> | V4    | Output V <sub>5</sub> | Power Supply                               |

|-------------------|--------------------|----------------------------------------|----------------|-------|----------------|-------|-----------------------|--------------------------------------------|

|                   | Resistance<br>Ohms | Size<br>W <sub>P</sub> /W <sub>N</sub> | V <sub>2</sub> | Ū3    | Volts          | Volts | Volts                 | Current I ( $V_{DD}$ ) *10 <sup>-2</sup> A |

| dsmp <sub>1</sub> | 1                  | 7.5/6                                  | 5              | 5     | 3.313          | 4.999 | 4.156                 | 1.46                                       |

| dsmp <sub>1</sub> | 10                 | 7.5/6                                  | 5              | 5     | 3.311          | 4.997 | 4.154                 | 1.46                                       |

| dsmp <sub>1</sub> | 100                | 7.5/6                                  | 5              | 5     | 3.289          | 4.975 | 4.132                 | 1.45                                       |

| dsmp <sub>1</sub> | 1K                 | 7.5/6                                  | 5              | 5     | 3.085          | 4.769 | 3.927                 | 1.40                                       |

| dsmp <sub>1</sub> | 10K                | 7.5/6                                  | 5              | 5     | 2.192          | 3.855 | 3.023                 | 0.95                                       |

| dsmp <sub>1</sub> | 1                  | 7.5/24                                 | 5              | 5     | 3.236          | 4.999 | 4.117                 | 6.4                                        |

| dsmp <sub>1</sub> | 100                | 7.5/24                                 | 5              | 5     | 3.165          | 4.927 | 4.046                 | 6.32                                       |

| dsmpi             | 1K                 | 7.5/24                                 | 5              | 5     | 2.603          | 4.360 | 3.482                 | 5.60                                       |

| dsmp1             | 10K                | 7.5/24                                 | 5              | 5     | 1.044          | 2.748 | 1.896                 | 2.06                                       |

| Fault            | Fault<br>Resistance<br>Ohms | Transistor<br>Size<br>W <sub>P</sub> /W <sub>N</sub> | Input<br>V. | Logic<br>V2 | V <sub>4</sub><br>Volts*10 <sup>-7</sup> | Output V <sub>5</sub><br>Volts | Power Supply<br>Current<br>I (V <sub>DD</sub> ) *10 <sup>-3</sup> A |

|------------------|-----------------------------|------------------------------------------------------|-------------|-------------|------------------------------------------|--------------------------------|---------------------------------------------------------------------|

|                  |                             | 7.5/6                                                | 5           | 5           | 2.52                                     | 4.991                          | 8.78                                                                |

| ceq_1            | 10                          | 7.5/6                                                | 5           | 5           | 2.52                                     | 4.912                          | 8.77                                                                |

| ceq <sub>1</sub> | 100                         | 7.5/6                                                | 5           | 5           | 2.52                                     | 4.157                          | 8.42                                                                |

| ceq <sub>1</sub> | 100                         | 7.5/6                                                | 5           | 5           | 2.51                                     | 1.679                          | 3.32                                                                |

Table 4.5: SPICE simulation results for stuck-on fault in bipolar driver  $qn_1$  in the basic BiCMOS NAND gate of Fig 4.3

Table 4.6: SPICE simulation results for stuck-on fault in bipolar driver qn1 in the full-swingBiCMOS NAND gate of Fig 4.4

| Fault             | Fault<br>Resistance<br>Ohms | Transistor<br>Size<br>W <sub>P</sub> /W <sub>N</sub> | Input<br>V2 | Logic<br>V <sub>3</sub> | V <sub>7</sub><br>Volts | V <sub>4</sub><br>Volts | Output V <sub>5</sub><br>Volts | Power Supply<br>Current<br>I (V <sub>DD</sub> ) *10 <sup>-2</sup> A |

|-------------------|-----------------------------|------------------------------------------------------|-------------|-------------------------|-------------------------|-------------------------|--------------------------------|---------------------------------------------------------------------|

| cean.             | 1                           | 7.5/6                                                | 5           | 5                       | 4.134                   | 4.982                   | 4.982                          | 1.76                                                                |

| ceqn <sub>i</sub> | 10                          | 7.5/6                                                | 5           | 5                       | 3.977                   | 4.825                   | 4.825                          | 1.74                                                                |

| ceqn <sub>1</sub> | 100                         | 7.5/6                                                | 5           | 5                       | 2.726                   | 3.568                   | 3.568                          | 1.43                                                                |

| ceqn <sub>1</sub> | 100<br>1K                   | 7.5/6                                                | 5           | 5                       | 1.186                   | 1.988                   | 1.988                          | 0.30                                                                |

| ceqni             |                             | 7.5/24                                               | 5           | 5                       | 4.043                   | 4.927                   | 4.927                          | 7.21                                                                |

| ceqn <sub>1</sub> |                             | 7.5/24                                               | 5           | 5                       | 3.441                   | 4.323                   | 4.323                          | 6.76                                                                |

| ceqn <sub>1</sub> | 10                          | ·                                                    | 5           | 5                       | 1.266                   | 2.127                   | 2.127                          | 2.87                                                                |

| ceqn <sub>1</sub> | 100                         | 7.5/24                                               |             | 5                       | 0.376                   | 1.184                   | 1.184                          | 0.38                                                                |