# EFFECTS OF DYNAMIC STRESS INDUCED CHARGE TRAPPING IN STACK GATE DIELECTRICS OF SCALED MOS DEVICES

#### Sonia Ahsan

A thesis submitted to

The Department of Electrical and Electronic Engineering

Bangladesh University of Engineering and Technology, Dhaka, Bangladesh

in partial fulfillment of the requirements for the degree of

MASTER OF SCIENCE IN ELECTRICAL AND ELECTRONIC ENGINEERING

DEPT. OF ELECTRICAL AND ELECTRONIC ENGINEERING (EEE)

BANGLADESH UNIVERSITY OF ENGINEERING AND TECHNOLOGY

(BUET)

August, 2009

The thesis titled "EFFECTS OF DYNAMIC STRESS INDUCED CHARGE TRAPPING IN STACK GATE DIELECTRICS OF SCALED MOS DEVICES.", submitted by Sonia Ahsan, Roll No: 100606230P, Session: October 2006 has been accepted as satisfactory in partial fulfillment of the requirement for the degree of Master of Science in Electrical and Electronic Engineering on August 11, 2009.

#### **BOARD OF EXAMINERS:**

| Dr. Quazi Deen Mohd Khosru                                                       | Chairman    |

|----------------------------------------------------------------------------------|-------------|

| Professor                                                                        | (Supervisor |

| Department of Electrical and Electronic Engineering BUET, Dhaka 1000, Bangladesh |             |

| Cioum It Jul 11/8/09                                                             |             |

| Dr. Aminul Hoque                                                                 | Member      |

| Professor and Head                                                               | (Ex-officio |

| Department of Electrical and Electronic Engineering                              |             |

| BUET, Dhaka 1000, Bangladesh                                                     |             |

| - 25 Jaylor 11/08/2009                                                           |             |

| Dr. Md. Shafiqul İslam                                                           | Member      |

| Professor                                                                        |             |

| Department of Electrical and Electronic Engineering                              |             |

| BUET, Dhaka 1000, Bangladesh                                                     |             |

| 12009 War 11/8/2009                                                              | ٠           |

| Dr. Khairul Alam                                                                 | Member      |

| Assistant Professor                                                              | (External)  |

| Department of Electrical and Electronic Engineering                              |             |

| East west university, Dhaka 1212, Bangladesh                                     |             |

#### **DECLARATION**

It is hereby declared that this thesis or any part of it has not been submitted elsewhere for the award of any degree or diploma.

Signature of the Candidate

Sonia Ahsan

#### **ACKNOWLEDGMENT**

First of all, the author would like to pay her gratitude to Almighty Allah for the successful completion of the work. The author expresses sincere gratitude and respect to her supervisor Dr. Quazi Deen Mohd Khosru, Professor, Department of EEE, BUET for his sincere guidance and supervision throughout the work. She is also thankful to Dr. Aminul Haque, Professor, Head, Dept. of EEE, BUET for his support and kind co-operation.

The author likes to express her gratitude to her siblings and parents for their selfless inspiration and encouragement throughout the progress of the work. She would like to express her profound gratitude to her husband, Farhan Shahil for his guidance and inspiration. The author likes to pay her gratitude to her in-laws and Athena who were also her source of inspiration.

Finally, the author reminds with gratitude the names of all those who were directly or indirectly involved with this work.

# DEDICATION

To my Family

## TABLE OF CONTENTS

| Declaration Acknowledgements  |                                                  | iii                  |          |

|-------------------------------|--------------------------------------------------|----------------------|----------|

|                               |                                                  | iv<br>v<br>ix<br>xii |          |

| Dedication                    |                                                  |                      |          |

| List of Figures Abbreviations |                                                  |                      |          |

|                               |                                                  |                      | Abstract |

| СНАРТЕ                        | R 1 INTRODUCTION                                 |                      |          |

| 1.1                           | General Overview                                 | 2                    |          |

| 1.2                           | Literature Review                                | 3                    |          |

| 1.3                           | Scope of the Work                                | 5                    |          |

| 1.4                           | Thesis Layout                                    | 6                    |          |

| СНАРТЕГ                       | R 2 HIGH-K GATE STACKS AND ITS IN                | MPLICATION           |          |

|                               | ON DEVICE CHARACTERISTICS                        |                      |          |

| 2.1                           | Introduction and Motivation                      | 7                    |          |

| 2.2                           | Background of MOSFETT                            | 7                    |          |

| 2.3                           | MOS Structure and Operation                      | 8                    |          |

| 2.4                           | MOSFET Scaling and Recent Trends                 | 10                   |          |

| 2.5                           | Quantum Confinement in MOS Structures            | 12                   |          |

| 2.6                           | The Gate and Gate Dielectrics                    | 14                   |          |

| 2.7                           | Choice Of Hfo <sub>2</sub> as Gate Dielectrics   | 15                   |          |

| 2.8                           | Electrical Characteristics of High-K Dielectrics | 18                   |          |

| 2.9                           | New Challenges for Hafnium Based Dielectrics     | 20                   |          |

| 2.                            | .9.1 Mobility degradation                        | 20                   |          |

| 2.                                      | 9.2 Chare tr                  | apping/detrapping ph                   | enomena in    | gate         |            |            |

|-----------------------------------------|-------------------------------|----------------------------------------|---------------|--------------|------------|------------|

|                                         | dielectri                     | cs                                     |               |              | 23         |            |

| 2.9                                     | 9.3 Threshol                  | ld Voltage (Vth) insta                 | bility and re | liability    | 24         |            |

| 2.10                                    | Conclusion                    |                                        |               |              | 24         |            |

| СНА                                     | PTER 3                        | CALCULATIO<br>LEAKAGE CU<br>DISSIPATED | RRENT D       | ENSITY       | ,          | TED<br>AND |

|                                         |                               | CHANNEL MO                             | BILITY        | DEGRAD       | ATION      | ſ          |

| 3.1                                     | Introduction                  | ı                                      |               |              | 26         |            |

| 3.2                                     | Self-Consist                  | tent Model                             |               |              | 27         |            |

| 3.3                                     | Charge Trap                   | Model                                  |               |              | <b>2</b> 9 |            |

| 3.4                                     | Trap Assiste                  | ed Leakage Current D                   | ensity and I  | Dissipated   | Power      |            |

|                                         | Density                       |                                        |               |              | 30         |            |

| 3.5                                     | Mobility Ca                   | lculation                              |               |              | 32         |            |

| 3.6                                     | Conclusion                    |                                        |               |              | 37         |            |

| CHAPTER                                 | 4 RES                         | SULTS                                  |               |              |            |            |

| 4.1 Int                                 | roduction                     |                                        |               |              | 38         |            |

| 4.2 Potential Profile of NMOS Structure |                               | 39                                     |               |              |            |            |

| 4.3 Th                                  | reshold Volta                 | ge Shift                               |               |              | 40         |            |

| 4.3.                                    |                               | Voltage Shift vs Gate :<br>et level    | voltage as a  | function o   | of         |            |

| 4.3.                                    | 2 Polaron ef                  | Tect .                                 |               |              |            |            |

| 4.3.                                    | 3 Threshold 1 Voltage         | Voltage Shift vs stress                | time as a fi  | inction of   | gate       |            |

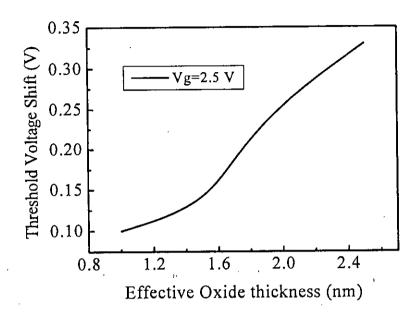

| 4.3.4                                   | 4 Threshold V                 | oltage Shift vs Effecti                | ive Oxide Th  | nickness (I  | EOT)       |            |

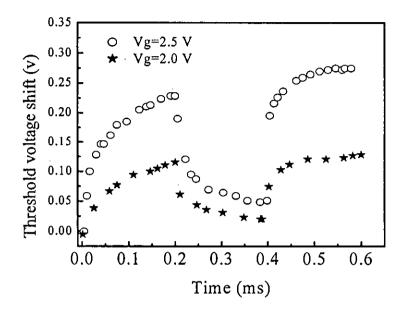

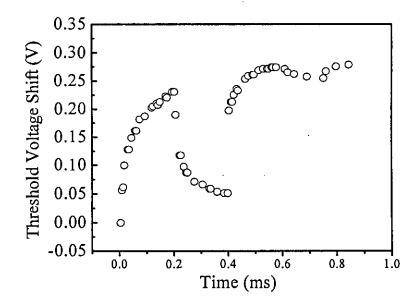

| 4.3.2                                   | 5 Threshold V<br>Gate voltage | Toltage Shift under dy<br>e            | namic stress  | s at differe | nt         |            |

|                                         |                               |                                        |               |              |            |            |

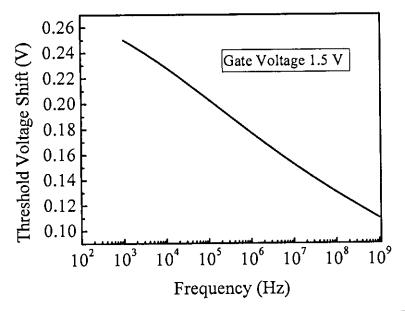

# 4.3.6 Threshold Voltage Shift vs frequency

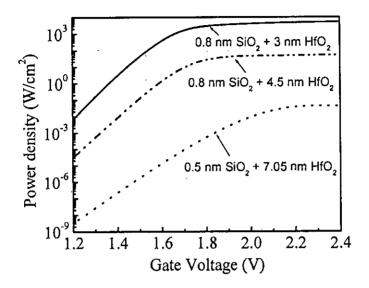

| 4.4 Trap Assisted Leakage Current Density (TALC) vs Gate Voltage                                                                                                                                                   | 47 |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

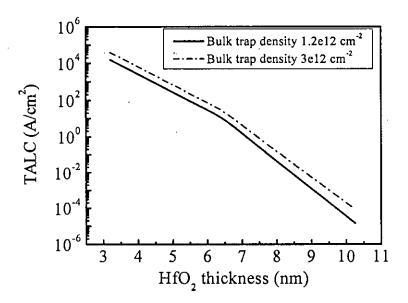

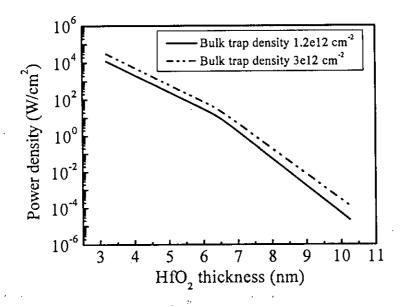

| 4.5 TALC vs HfO <sub>2</sub> Thickness At Different Bulk Trap Density                                                                                                                                              | 48 |

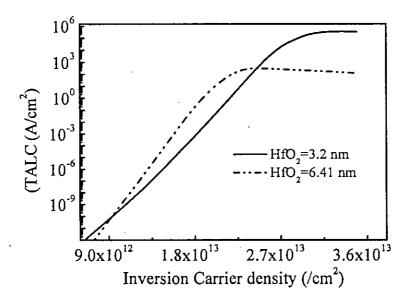

| 4.6 TALC vs Inversion Carrier Density                                                                                                                                                                              | 49 |

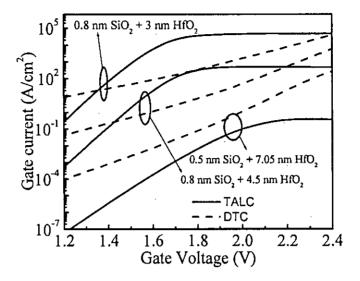

| 4.7 Comparison of TALC With Direct Tunneling Current (DTC)                                                                                                                                                         | 50 |

| 4.8 Power Calculation                                                                                                                                                                                              | 51 |

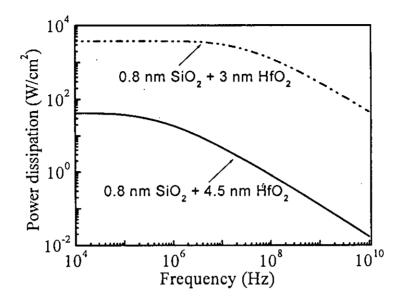

| 4.8.1 Dissipated Power density vs Gate voltage as a function of oxide thickness 4.8.2 Power density vs HfO₂ thickness at different bulk trap density 4.8.3 Power density vs Frequency at different oxide thickness |    |

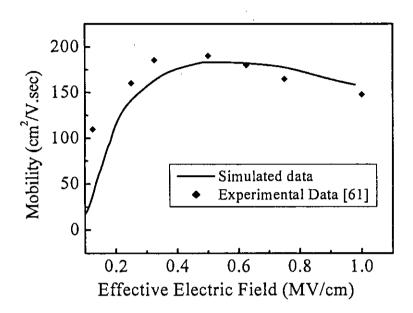

| 4.9 Mobility Calculation                                                                                                                                                                                           | 55 |

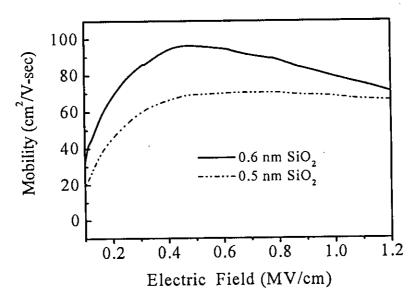

| 4.9.1 Mobility vs Electric field 4.9.2 Mobility vs Electric field varying interfacial oxide thickness                                                                                                              |    |

| 4.10 Conclusion                                                                                                                                                                                                    | 56 |

| CHAPTER 5 CONCLUSION                                                                                                                                                                                               |    |

| 5.1 Summary                                                                                                                                                                                                        | 57 |

| 5.2 Suggestion for future work                                                                                                                                                                                     | 58 |

|                                                                                                                                                                                                                    |    |

| References                                                                                                                                                                                                         | 59 |

# LIST OF FIGURES

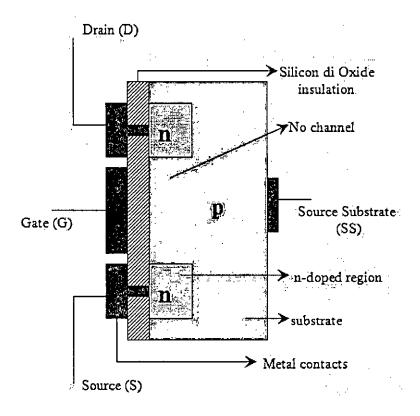

| Figure 2.1 | N-channel_enhancement-type_MOSFET.                                                                | 9     |

|------------|---------------------------------------------------------------------------------------------------|-------|

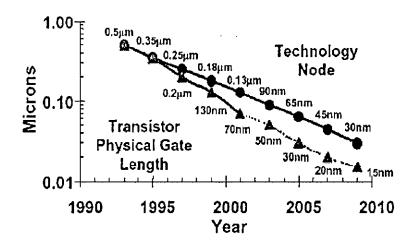

| Figure 2.2 | Technology node and transistor physical gate length in Intel processors                           | ,     |

|            |                                                                                                   | 11    |

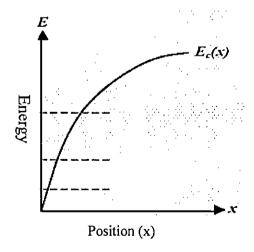

| Figure 2.3 | Potential well formed at oxide semiconductor interface.                                           | 12    |

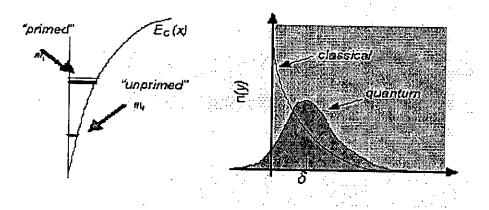

| Figure 2.4 | Potential well formed at the oxide semiconductor interface. Horizontal                            | lines |

|            | represent the subbands.                                                                           | 13    |

| Figure 2.5 | Classical and quantum mechanical charge distribution inside                                       |       |

|            | semiconductor.                                                                                    | 13    |

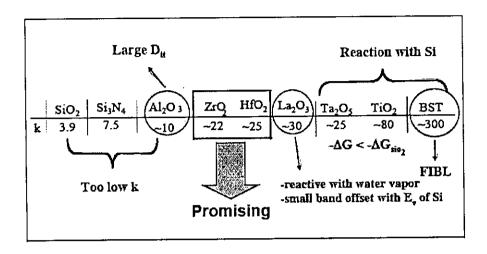

| Figure 2.6 | Various gate dielectrics and their dielectric constants, and concerns for                         | the   |

|            | application into gate dielectrics.                                                                | 16    |

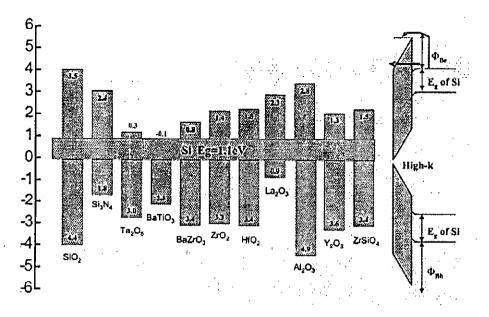

| Figure 2.7 | Band offset of gate dielectric candidates with conduction band edge and                           | i     |

|            | valence band edge of Si substrate.                                                                | 17    |

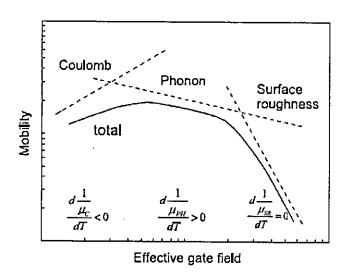

| Figure 2.8 | Schematic carrier mobility vs. vertical field in FETs in the universal                            |       |

|            | mobility model, showing the mechanisms which limit the mobility, and                              |       |

|            | their temperature dependences.                                                                    | 21    |

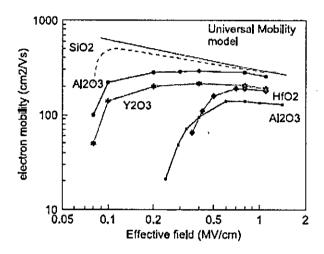

| Figure 2.9 | Carrier mobility of n-type Si, for various gate oxides, after Gusev et al.                        |       |

|            |                                                                                                   | 22    |

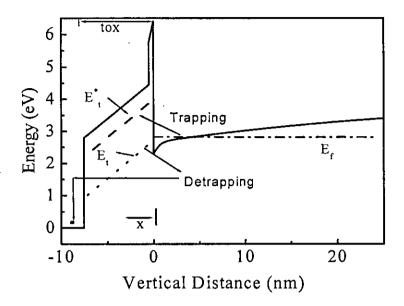

| Figure 4.1 | Potential profile of a multi-stack (Si/SiO <sub>2</sub> /HfO <sub>2</sub> /poly-Si) containing em | pty   |

|            | defect level and occupied defect level in the HfO2 layer at positive gate                         | bias. |

|            |                                                                                                   | 39    |

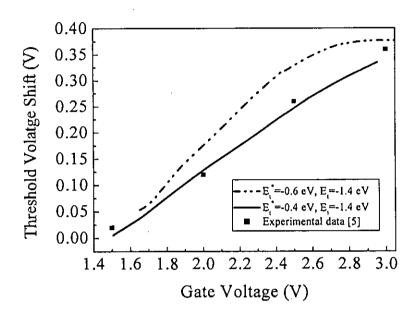

| Figure 4.2 | Threshold-voltage shift as a function of gate voltage taking two empty                            |       |

|            | defect levels and same occupied defect level.                                                     | 40    |

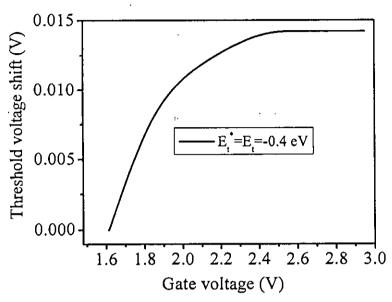

| Figure 4.3 | Polaron effect is shown by taking $E_t = E_t^* = -0.4$ eV in the simulation.                      | 41    |

|            |                                                                                                   | √ . { |

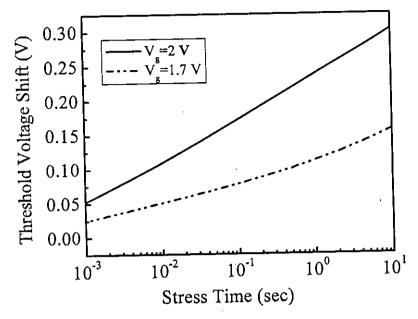

| Figure 4.4  | Threshold-voltage shift versus stress time for HfO <sub>2</sub> / poly-SiO <sub>2</sub> gate constant voltage stress.    | under<br>42        |

|-------------|--------------------------------------------------------------------------------------------------------------------------|--------------------|

| Figure 4.5  | Threshold-voltage shift versus varying effective oxide thickness at a ga voltage of 2.5V.                                | te<br>43           |

| Figure 4.6  | Simulated threshold-voltage shift as a function of time during on an stress at $V = 2.0 \text{ V}$ and $2.5 \text{ V}$ . | d off<br>44        |

| Figure 4.7  | Simulated threshold-voltage shift as a function of time during on an stress at $V = 2.5 \text{ V}$ and five pulses.      | d off<br>45        |

| Figure 4.8  | Simulated threshold-voltage shift as a function of frequency at $V = 1.5V$                                               | <i>7</i> .         |

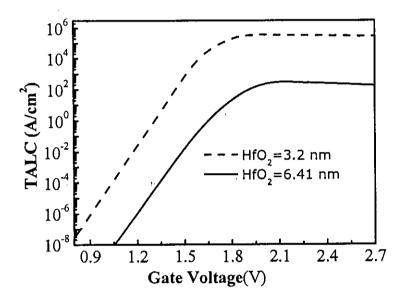

| Figure 4.9  | TALC versus gate voltage at different oxide thickness. Here substanting density.                                         | 46<br>strate<br>47 |

| Figure 4.10 | TALC versus gate voltage at different oxide thickness.                                                                   | 48                 |

| Figure 4.11 | TALC versus inversion carrier density at different oxide thickness.                                                      | 49                 |

| Figure 4.12 | Comparison of TALC with DTC at different oxide thickness.                                                                | 50                 |

| Figure 4.13 | Simulated dissipated power density versus gate voltage with different of thickness.                                      | oxide<br>51        |

| Figure 4.14 | Simulated dissipated power density versus gate voltage with different of thickness.                                      | oxide<br>52        |

| Figure 4.15 | Dissipated power density as a function of frequency considering Vg = considering thickness as a parameter.               | 1.8V<br>53         |

| Figure 4.16 | Simulated mobility profile inside the channel.                                                                           | 54                 |

| Figure 4.17 | Simulated mobility profile inside the channel with 1.67 nm EOT and 1.1 nm EOT.                                           | 56                 |

#### **ABBREVIATIONS**

DTC Direct Tunneling Current

FN Fowler-Nordheim

EOT Effective Oxide Thickness

MOSFET Metal Oxide Field Effect Transistor

QMTC Quantum Mechanical Transmission Co-efficient

QMWI Quantum Mechanical Wave Impedance

QPC Quantum Point Contact

TAT Trap Assisted Tunneling

TDDB Time Dependent Dielectric Breakdown

ULSI Ultra Large Scale Integration

VLSI Very Large Scale Integration

TALC Trap Assisted Leakage Current

WKB Wentzel-Kramer-Brillouin

#### **ABSTRACT**

Charge trapping dynamics in hafnium based dielectric stacks and their impact on various device performances of scaled MOS devices is studied A theoretical model has been presented to incorporate the charge trapping/detrapping mechanism in hafnium based dielectric stacks followed by studying the properties of carriers in inversion layers solving coupled Schrödinger's and Poisson's equations self consistently. Several important characteristics of device such as power dissipation, effect of dynamic stress, trap assisted leakage current density, threshold voltage instability, polaron effect and channel mobility degradation are investigated with decreasing effective oxide thickness as well as increasing gate voltage. Then the simulated results are compared with the reported experimental results.

# CHAPTER 1

# INTRODUCTION

#### 1.1 GENERAL OVERVIEW

In order to provide better performance and higher packing density on the limited space, scaling down of the channel length is essential in ULSI fabrication technologies. Although the thermally grown or rapid thermally grown oxynitride with Effective Oxide Thickness (EOT) of 18~25Å has been introduced in the manufacturing area for the replacement of SiO<sub>2</sub> to further scale technology, the technology for beyond that still needs further thickness scaling of SiO<sub>2</sub> or oxynitride and is approaching the scaling limits. Therefore, new materials such as high-k dielectrics and metal gate electrodes have been investigated in order to ensure continued scaling of the technology. Among multiple candidates such as Ta<sub>2</sub>O<sub>5</sub>, TiO<sub>2</sub>, Al<sub>2</sub>O<sub>3</sub>, Y<sub>2</sub>O<sub>3</sub>, La<sub>2</sub>O<sub>3</sub>, ZrO<sub>2</sub>, the HfO<sub>2</sub>-based material has been presently considered the most attractive candidate for the gate dielectric application due to its high k value, better device performance and thermal stability, etc. However, various challenges for high-k devices implementation include low mobility and threshold voltage instability, which can be affected by the quality of the interfacial oxide and charge trapping. In particular, transient charge trapping was proposed to be one of the main resources for mobility reduction. Even though several process modifications, such as nitridation and silicate formation, suggest the ways for improvement of high-k dielectrics device performance, the effect of these changes has not been yet studied systematically. The reliability issues of the hafnium-based dielectrics, such as Time Dependent Dielectric Breakdown (TDDB), bias temperature instabilities, and hot carrier stability, needs to be addressed in order to introduce high-k technology in 45 nm technology node. Metallic impurity such as Hf and Ta could penetrate through dielectric layer resulting in degraded bulk minority carrier lifetime and inversion carrier mobility.

To minimize transient charging behavior in high-k devices, pulsed I-V measurement has been proposed. Using pulsed I-V measurement technique, the effects of interface treatment and dielectric stacks on transient characteristics of high-k transistors were studied. The results based on varying pulse frequency and trise & tfall supported that bulk traps appeared to be a main factor for threshold voltage shift. The results of bias instability suggested that the stress induced mobility degradation was primarily related with interface degradation.

From the study of transient charge trapping/detrapping characteristics in high-k n/pMOSFETs, transient charge trapping has been found to be an interface thickness limited phenomenon. Additionally, transient electron trapping/detrapping was dominant even in pMOSFETs.

High-k ring oscillator circuit study suggested that high-k device would operate in close to intrinsic mode in the actual circuit operation. At high Vdd regime, the propagation delay for high-k devices was shorter than that of SiO<sub>2</sub>. However, in the lower Vdd regime, high-k device showed slower circuit performance due to charge trapping.

Using ultra-short pulse measurement technique, we could get near intrinsic I-V curves of high-k devices. Mobility degradation was still observed even though negligible charge trapping takes place during ultra-short pulse measurement. Remote charge scattering appeared to be the main cause of intrinsic mobility degradation. Again, it was confirmed that trapped charges appear to locate in the bulk high-k layer rather than at the interfacial layer.

#### 1.2 LITERATURE REVIEW

Aggressive scaling down of MOSFETs continues to reduce the feature sizes into deep submicron regime. The continuous scaling of MOSFETs, as outlined in International Technological Roadmap for Semiconductor Devices [1], requires that the Equivalent Oxide Thickness (EOT) to become as thin as 0.5 nm in some cases in the next 10 years. However such thin SiO<sub>2</sub> suffers due to excessive direct tunneling current (DTC) and reliability problems. To overcome these problems, SiO<sub>2</sub> should be replaced by suitable high-k materials as gate insulators [1]. Using high-k (dielectric constant) material, both thicker physical thickness and several orders of magnitude lower gate leakage current can be achieved with similar oxide capacitance. While high-k materials can help to solve gate leakage problems, high densities of traps within high-k gate dielectrics adversely affect the device performance [2] in different ways. Trapping of charges in the preexisting bulk trap center inside high-k materials arises some important issues such as threshold voltage instability, dissipated power density and higher trap assisted leakage current density. Charge trapping dynamics in Hafnium based dielectric stacks and their impact on

the threshold voltage instability was studied by several researchers [3], [4], [5]. But the last two unnoticed issues (dissipated power density and higher trap assisted leakage current density) must be studied before using high-k material as a gate dielectric material. With further thinning of the gate oxide thickness, these trapped charges may detrapped through the oxide/gate interface. In paper [6], Farhan et al investigated the effect of detrapped charges from the oxide trap centers to the gate electrode on the threshold voltage shift. Such detrapping would reduce the amount of charges trapped in the dielectric, resulting in a reduction of the threshold voltage shift [6]. Garross et al [7] have also incorporated this detrapping term in their model but found the effect almost negligible during negative half of the ac cycle. In our paper [6], we concluded that the impact of these two simultaneous processes on device performance during positive half of the ac cycle should be studied. Also some other issues such as dissipated power density trap assisted leakage current density should be studied before neglecting these detrapped charges with farther scaling.

Over the last 10 years the power dissipation in the lead microprocessor has increased by a factor of 2.5 per generation, saturating at about 100 W levels [8]. Not only that, in present technologies that as SiO2 as the gate dielectric (90, 65 and some of 45 nm), there is a significant contribution of increasing gate leakage current. In contrast to the past researcher [9] this trend may be continued, with the introduction of high-k dielectrics having high bulk trap density. The mechanism will rapidly increase in severity as scaling proceeds. Various types of power dissipation and the details of these effects along with other scaling issues have been described by frank [10]. In case of using high-k materials having high bulk trap density such as HfO<sub>2</sub>, ZrO<sub>2</sub>; Al<sub>2</sub>O<sub>3</sub> as a gate dielectric dissipated power density should be re-calculated incorporating this detrapping mechanism.

Moreover gate leakage current density should also be recalculated incorporating trap assisted leakage current density with further thinning of oxide thickness. Scaling down allows the same performance with reduced voltage, leading to low power. As devices shrink to sub-micron dimensions, the supply voltage must be reduced to avoid damaging electric fields. This development, in turn, requires a reduced threshold voltage. On the other hand, for a given voltage, leakage current increases exponentially with a decrease in V<sub>th</sub>. Further, leakage occurs as long as power flows

through the circuit. This constant current can produce an increase in the chip temperature, which in turn causes an increase in the thermal voltage, leading to a further increase in leakage current. In some cases, this circle results in unconstrained thermal runaway. Also the poor future power scaling, combined with previously applied aggressive performance scaling techniques has made power the number one problem in modern chip design since high performance circuit will dissipate too much power.

Fully understanding the charge trapping/detrapping mechanism is the key to understanding device related issues associated with the high-k dielectrics. These detrapped charges may affect the device performances answering the question how far scaling can go with high-k dielectric materials having large bulk trap density. In this connection, here we study the leakage current density contributed by these detrapped charges and the dissipated power density associated with them.

#### 1.3 SCOPE OF THE WORK

With the advent of high-k dielectrics gate oxide can be scaled below keeping the gate leakage current density lower. But due to excessive bulk trap density of high-k dielectric, we believe, further scaling may be prohibited due increasing leakage current density as well as dissipated power density and these terms should be further studied for successful high-k integration into the Si CMOS technology. As systems became more power constrained, optimizing the power became more critical, viewing power reduction from an optimization perspective provides valuable insights. So Charge trapping /detrapping phenomena has become a decisive criterion as it makes the threshold voltage unstable. However, before their final integration in industry, significant issues remain to be overcome as there are mobility degradation, metal gate incompatibility and threshold voltage instability. To address this last issue it becomes important to know the trapping/detrapping mechanisms in preexisting defects. Although these models are useful for providing qualitative explanations, a device-level numerical model is nonetheless necessary to

quantitatively analyze the origin and impact of the electrical instability in such multi stack systems.

#### 1.4 THESIŞ LAYOUT

This thesis consists of five chapters of which chapter one gives an introduction followed by literature review and objective of this study.

Chapter 2 deals with brief description of MOSFET fundamentals and charge trap behavior and gate current. It also contains a brief description of the origin of traps creation, oxide degradation and an overview of charge trapping phenomenon.

In Chapter 3, threshold voltage calculation, dissipated power density, mobility degradation and the trap assisted discharged current density expression for MOS capacitors are discussed.

The simulation results are presented in Chapter 4 based on the expressions developed in Chapter 3. Conclusive remarks and discussions are given in chapter 5.

# CHAPTER 2

# HIGH-K GATE STACKS AND ITS IMPLICATION ON DEVICE CHARACTERISTICS

#### 2.1 INTRODUCTION AND MOTIVATION

The MOSFET (Metal-Oxide-Silicon Field-Effect- Transistor) or MOS Transistor (MOST) is a three dimensional electronic device. It operates on the conductivity modulation principle in a thin semiconductor layer by a controlling electric field to give amplifying and switching functions between three electrical terminals (input, output and common) connected to the film.

It is the building block of the complex Integrated Circuits (IC), such as microprocessors, graphics, and Digital Signal Processing (DSP) chips. Each IC packs more than 100 million MOS transistors on a single chip. Integration of one billion transistors into a single chip will become a reality before 2010.

#### 2.2 BACKGROUND OF MOSFET

A conceptually similar structure was first proposed and patented by Lilienfeld and Heil in 1930, but was not successfully demonstrated until 1960. The main technological problem was the control and reduction of the surface states at the interface between the oxide and the semiconductor. The operating principle of the MOSFET transistor was first described in Lilienfield's historical patent issued in 1926. It took another 34 years before Dawon Kahng and Martin Atalla successfully built a working MOSFET in 1960.

For the past 40 years, the semiconductor industry and academia have relentlessly pushed transistor scaling. Along with scaling, the MOSFET transistor evolved from the p-MOSFET in the 1960's to the n-MOSFET in the 1970's. A good understanding of gate oxide quality, such as interface traps, fixed and mobile charges, and a good control of gate oxide quality in a manufacturing environment enabled industry to make the transition from PMOS technology to a higher-performing NMOS technology in 1970's. Initially it was only possible to deplete an existing n-type channel by applying a negative voltage to the gate. Such devices have a conducting channel between source and drain even when no gate voltage is applied and are called "depletion-mode" devices.

A reduction of the surface states enabled the fabrication of devices which do not have a conducting channel unless a positive voltage is applied. Such devices are referred to as "enhancement-mode" devices. The electrons at the oxide-semiconductor interface are concentrated in a thin (~10 nm thick) "inversion" layer. By now, most MOSFETs are "enhancement-mode" devices.

#### 2.3 MOS STRUCTURE AND OPERATION

A traditional metal—oxide—semiconductor (MOS) structure is obtained by growing a layer of silicon dioxide (SiO<sub>2</sub>) on top of a silicon substrate and depositing a layer of metal or polycrystalline silicon (the latter is commonly used). As the silicon dioxide is a dielectric material, its structure is equivalent to a planar capacitor, with one of the electrodes replaced by a semiconductor.

When a voltage is applied across a MOS structure, it modifies the distribution of charges in the semiconductor. If we consider a P-type semiconductor (with  $N_A$  the density of acceptors, p the density of holes;  $p = N_A$  in neutral bulk), a positive voltage,  $V_G$ , from gate to body (Figure 2.1) creates a depletion layer by forcing the positively charged holes away from the gate-insulator/semiconductor interface, leaving exposed a carrier-free region of immobile, negatively charged acceptor ions. If  $V_G$  is high enough, a high concentration of negative charge carriers forms in an inversion layer located in a thin layer next to the interface between the semiconductor and the insulator (unlike the MOSFET where the inversion layer electrons are supplied rapidly from the source/drain electrodes, in the MOS capacitor they are produced much more slowly by thermal generation through carrier generation and recombination centers in the depletion region). Conventionally, the gate voltage at which the volume density of electrons in the inversion layer is the same as the volume density of holes in the body is called the threshold voltage.

This structure with P-type body is the basis of the N-type MOSFET, which requires the addition of an N-type source and drain regions.

1

Fig. 2.1: N-channel\_enhancement-type\_MOSFET [11]

A metal—oxide—semiconductor field-effect transistor (MOSFET) is based on the modulation of charge concentration by a MOS capacitance between a body electrode and a gate electrode located above the body and insulated from all other device regions by a gate dielectric layer which in the case of a MOSFET is an oxide, such as silicon dioxide. If dielectrics other than an oxide such as silicon dioxide (often referred to as oxide) are employed the device may be referred to as a metal—insulator—semiconductor FET (MISFET). The MOSFET includes two additional terminals (source and drain), each connected to individual highly doped regions that are separated by the body region. These regions can be either p or n type, but they must both be of the same type, and of opposite type to the body region. The source and drain (unlike the body) are highly doped as signified by a '+' sign after the type of doping.

If the MOSFET is an n-channel or nMOS FET, then the source and drain are 'n+' regions and the body is a 'p' region. As described above, with sufficient gate voltage,

above a threshold voltage value, electrons from the source (and possibly also the drain) enter the inversion layer or n-channel at the interface between the p region and the oxide. This conducting channel extends between the source and the drain, and current is conducted through it when a voltage is applied between source and drain. For gate voltages below the threshold value, the channel is lightly populated, and only a very small subthreshold leakage current can flow between the source and the drain.

If the MOSFET is a p-channel or pMOS FET, then the source and drain are 'p+' regions and the body is a 'n' region. When a negative gate-source voltage (positive source-gate) is applied, it creates a p-channel at the surface of the n region, analogous to the n-channel case, but with opposite polarities of charges and voltages. When a voltage less negative than the threshold value (a negative voltage for p-channel) is applied between gate and source, the channel disappears and only a very small subthreshold current can flow between the source and the drain.

The source is so named because it is the source of the charge carriers (electrons for n-channel, holes for p-channel) that flow through the channel; similarly, the drain is where the charge carriers leave the channel.

The device may comprise a Silicon On Insulator (SOI) device in which a Buried Oxide (BOX) is formed below a thin semiconductor layer. If the channel region between the gate dielectric and a Buried Oxide (BOX) region is very thin, the very thin channel region is referred to as an Ultra Thin Channel (UTC) region with the source and drain regions formed on either side thereof in and/or above the thin semiconductor layer. Alternatively, the device may comprise a SEMiconductor On Insulator (SEMOI) device in which other semiconductors than silicon are employed. Many alternative semicondutor materials may be employed.

#### 2.4 MOSFET SCALING AND RECENT TRENDS

Over the past decades, the MOSFET has continually been scaled down in size to achieve lower switching time, reduces cost and lower power consumption. Typical MOSFET channel lengths were once several micrometres, but modern integrated circuits are incorporating MOSFETs with channel lengths of less than a tenth of a micrometre long. Indeed Intel will begin production of a process featuring a 65nm

channel length in early 2006. Until the late 1990s, this size reduction resulted in great improvement to MOSFET operation with no deleterious consequences.

In order to increase circuit functionality and performance at lower cost, the scaling of integration technology was always one of the top priorities for semiconductor business and has aggressively driven that the semiconductor research became the quintessence of the technology and science in present-day.

Fig 2.1 shows how the technology node and transistor physical gate length in Intel processors has changed [12].

Fig. 2.2 Technology node and transistor physical gate length in Intel processors [2].

For the last four decades, the improvement of speed and shrinkage of chip area of integrated circuits were achieved by scaling down of physical thickness of the SiO<sub>2</sub> gate dielectrics and gate length (L). When the dimensions of a MOSFET are scaled down, both the voltage level and the gate-oxide thickness must also be reduced [13]. However, beyond the 100 nm node technology, SiO<sub>2</sub> has reached its physical limitations: higher leakage current and reliability concerns. Continuing scaling down of the MOSFET device with the minimum feature size of 90 nm and below requires EOT (Equivalent Oxide Thickness) less than 15 Å. A 10-15Å-thick SiO<sub>2</sub> layer corresponds to only around 3-4 mono-layers of SiO<sub>2</sub>. In this thinner EOT range, SiO<sub>2</sub> suffers from leakage current too high to be used (particularly) for low power operation due to the direct tunneling of electrons.

The most advanced MOS transistors used in volume production today are probably those of Intel's used in their 130nm logic technology with transistor gate length and gate oxide thickness are 60nm and 1.5nm, respectively. At IEDM 2003 [14], Intel presented a manufacturing-ready 90nm technology, with transistor gate length 50nm and gate oxide thickness 1.2nm. As of 2nd half of 2004, 90nm technology is at the beginning of manufacturing life cycle at a very limited number of top semiconductor manufacturers. For majority of IC manufacturers, 90nm technology is in the qualification stage or in the middle of development.

#### 2.5 QUANTUN CONFINEMENT IN MOS STRUCTURE

It has been well known since the late sixties, that for a better description of the MOS structure, the conventional semi-classical approach is not very adequate. In the semi-classical approach, the density of states above the conduction band is assumed to be continuous, and using this continuous density of states model and the Fermi function, the classical description of the electron concentration can be obtained. This approach works well if the bands are slowly varying compared to the electron's deBroglie wavelength. However, in case of an MOS C, Fig. 2.3 shows that the band bending near the surface can form a quantum well, which introduces energy quantization. So the semi-classical approach does not work well for these problems, and for a precise description a quantum mechanical approach has to be used.

Fig. 2.3: Potential well formed at oxide semiconductor interface.

So far we have outlined the mechanics of the quantum mechanical calculation for MOS structures. What we understood is: why we need quantum approach and how we solve the problem quantum mechanically. But, we may want to know how these quantum results differ from the semi-classical result. There are actually two key effects. To see this let us consider Fig. 2.4 and 2.5. Figure 2.4, shows one of the effects, that is the quantization of the energies above conduction band, which is assumed to be continuous in classical model. The direct effect of these on MOS capacitors or on MOSFETs is an increase of threshold voltage, because the threshold voltage is approximately the gate voltage for which, the conduction band goes below the Fermi level. However, due to the energy quantization, the lowest level that electrons occupy is not the bottom of conduction band, rather it is the first energy level, which is little higher than the conduction band edge. So to bend this band below the Fermi level, a little more gate voltage is needed. This gives rise to a threshold voltage rise in MOSFETs.

Fig. 2.4: Potential well formed at the oxide semiconductor interface. Horizontal lines represent the subbands.

Fig. 2.5: Classical and quantum mechanical charge distribution inside semiconductor.

Another effect comes from the spatial distribution of inversion charge. Both the classical and the quantum distribution of inversion charge along the depth of the device (x direction) are shown in Fig. 2.4. The classical distribution shows a peak at the oxide semiconductor interface while the quantum mechanical distribution is totally different from that and shows a peak inside. The net effect is that the actual profile (quantum mechanical) has an average distance from the surface that is larger

than that predicted by the classical calculations. As we know, the average carrier distance has the effect of increasing the effective oxide thickness. Thus the quantum mechanical calculation predicts a larger effective oxide thickness, which means a lower gate capacitance. Thus for a certain gate voltage, the amount of inversion charge will be somewhat smaller than that, predicted by the classical analysis. This is more important as the oxide thickness becomes smaller with each technology generation.

#### 2.6 THE GATE AND GATE DIELECTRICS

Early MOSFET used metal (such as aluminum) as a gate electrode; hence the name MOSFET was came. However, in fabrication processes high temperature causes metal to melt. Moreover, MOSFETs with metal gates have higher threshold voltage. Thus poly-crystalline silicon was preferable to metal as gate material as it has higher melting point. However, polysilicon is highly resistive (approximately 1000 times more resistive than metal) which reduces the signal propagation speed through the material. To lower the resistivity, dopants are added to the polysilicon. Sometimes additionally, high temperature metal such as Nickel layered onto the top of the polysilicon which decreases the resistivity. Such a blended material is called silicide. The silicide-polysilicon combination has better electrical properties than polysilicon alone and still does not melt in subsequent processing. Also the threshold voltage is not significantly higher than polysilicon alone, because the silicide material is not near the channel.

In case of the Gate Oxide, the insulator should be of high insulating property to resist leakage current from gate to the channel. As the device is scaled down, the tunneling phenomena becomes prominent leading to an increased power consumption. (The various degradation of oxide are discussed in the following sections). Insulators that have a larger dielectric constant than SiO<sub>2</sub>, such as group IV(B) metal silicates e.g. Hafnium and Zirconium Silicates and Oxides, are now being researched to reduce the gate leakage. Increasing the dielectric constant of the gate oxide material allows a thicker layer while maintaining a high capacitance. The higher thickness reduces the tunneling current between the gate and the channel. An

important consideration is the barrier height of the new gate oxide; the difference in conduction band energy between the semiconductor and the oxide will also affect the leakage current level. For the traditional gate oxide, silicon dioxide, the former barrier is approximately 3 eV. For many alternative dielectrics the value is significantly lower, somewhat negating the advantage of higher dielectric constant.

#### 2.7 CHOICE OF HIO2 AS GATE DIELECTRIC

High-k gate dielectrics have been studied as alternative gate dielectrics for the 70 nm technology node and beyond to replace conventional SiO<sub>2</sub> or silicon oxynitrides (SiOxNy).

Principal requirements for high-k dielectric applications are

- high dielectric constant

- high band offset with electrodes (i.e. barrier height) to suppress leakage current thermally and chemically stable in contact with Si substrate.

- It must have a high enough K that it will be used for a reasonable number of years of scaling.

- The oxide is in direct contact with the Si channel, so it must be thermodynamically stable with it.

- It must be kinetically stable, and be compatible with processing to 1000 °C for 5 seconds.

- It must act as an insulator, by having band offsets with Si of over 1 eV to minimise carrier injection into its bands.

- It must form a good electrical interface with Si.

- It must have few bulk electrically active defects.

In Fig. 2.6, dielectric constants of high-k candidates were summarized. TiO2 and barium strontium titanate (BST) showing profoundly higher k in Fig. 2.6, were reported not to be thermally stable with silicon substrates [15]. It is worth mentioning that high-k dielectrics such as BST with a too high dielectric constant (>100) does not seem to be appropriate since the high dielectric constant causes field

induced barrier lowering (FIBL) which degrade short channel effects of MOSFETs [16].

Fig. 2.6 Various gate dielectrics and their dielectric constants, and concerns for the application into gate dielectrics [17].

According to a report [18], band offset less than 1.0 eV may lead to an unacceptably large leakage current. Based on the band offset in Fig. 2.7, Ta<sub>2</sub>O<sub>5</sub>, which has been studied widely for the application in DRAM storage capacitors appears to be inappropriate for the gate electrode application. Al<sub>2</sub>O<sub>3</sub> and Si<sub>3</sub>N<sub>4</sub> have too low k to be used for several generations as shown in Fig.2.7. Among these materials, HfO<sub>2</sub> has been shown to be compatible with poly-silicon gate, poly-SiGe, and TaN gates. In contrast, ZrO<sub>2</sub> has been reported that it was not compatible with poly-Si gate due to the reaction of Zr with poly-Si gate.

Fig. 2.7 Band offset of gate dielectric candidates with conduction band edge and valence band edge of Si substrate [19].

MOSFETs with HfO<sub>2</sub> dielectrics and TaN gate showed very low EOT (~10-12Å) and low leakage current even after the conventional CMOS process flow [10]. Considering the cost of development and implementation, HfO<sub>2</sub> gate dielectric needs to span two or three generations from the 75 nm to the 35 nm design rule. To meet the requirements for these generations, EOT should be scaled down to less than 10 Å while suppressing leakage current to below 1 A/cm<sup>2</sup> [20].

Among the high-k dielectrics being studied, HfO<sub>2</sub> appears promising due to its relatively high dielectric constant (25) as compared to Si<sub>3</sub>N<sub>4</sub> and Al<sub>2</sub>O<sub>3</sub> [21], its relatively high free energy of reaction with Si (47.6 Kcal/mole at 727 C) as compared to TiO<sub>2</sub> and Ta<sub>2</sub>O<sub>5</sub>, and its relatively large bandgap (5.8 eV). Although there has been some recent work done on HfO<sub>2</sub> and its MOS capacitors [22], [23], the charge-trapping properties of this material are still unclear. In this thesis, the effects of stress voltage, trapping time, backward detrapping, and gate electrode on charge trapping in HfO<sub>2</sub> are reported.

17

One problem with high K oxides is that they contain much higher defect concentrations than SiO<sub>2</sub>. The SiO<sub>2</sub> possessed such a low concentration of defects for three reasons. First, its high heat of formation means that offstoichiometry defects such as O vacancies are costly and so are rare. The second is that SiO2 has covalent bonding with a low coordination. The covalent bonding means that the main defects are dangling bonds, and the low coordination allows the SiO2 network to relax to remove any dangling bonds by rebonding the network. This occurs in particular for defects at the Si: SiO2 interface. The high K oxides differ in that their bonding is ionic, and they have higher coordination number. The greater ionic character of the bonding and the higher coordination numbers mean that the high K oxides are poorer glass formers. The effect of poor glass forming ability and high coordination is that the oxides have higher defect concentrations. The oxides have very high heats of formation, so the equilibrium concentration of non-stoichiometric defects should be low (except where mixed valence is possible, such as TiO<sub>2</sub>). However, the non-equilibrium concentration of defects is high, because the oxide network is less able to relax, to rebond and remove defects.

#### 2.8 ELECTRICAL CHARACTERISTICS OF HIGH-K DIELECTRICS

Currently Hf based material has been extensively investigated in order to overcome the intrinsic disadvantages of HfO<sub>2</sub> such as lower crystallization temperature, formation of interfacial oxide layer with Si substrate, low channel mobility, etc. Nitrogen8 incorporation into dielectric and Si surface nitridation by NH3 has proved that these fabrication techniques are effective to reduce EOT [22, 23]. Si or N incorporation has shown the improvement of thermal budget before the crystallization of dielectric, which resulted in leakage current reduction. Also optimization of annealing condition with forming gas or deuterium has demonstrated the improvement of electrical characteristics, particularly channel electron mobility [24, 25]. However, there are still lots of issues to be concerned. Due to the significant preexisting traps and fast transient charge trapping/detrapping, it is not easy to understand the electrical characteristics of high-k device using the conventional characterization technique for SiO<sub>2</sub> based devices [26, 27]. Reduced transistor performance in high-k dielectric such as reduced carrier mobility,

saturation current, and hysteresis was addressed that trapped charges during the conventional measurement were the primary reason. These trapped charges have very small time constant. Therefore, these easily jump up to the trap sites in dielectric layer and go back to substrate during very short characterization time. To characterize these transient charges, transient measurement technique has been proposed for high-k devices [28, 29].

For mobility characterization, the most important parameter is inversion charge density. The electron mobility was usually calculated from drain current-gate bias (Id-Vg) curve and gate to channel capacitance (Cgs) vs. Vg curves of the MOSFETs using a well-known equations (1) ~ (3).

Effective mobility of carrier can be expressed by a simple equation (1),

$$\mu_{eff}(V_g) = \frac{I_d/V_d}{(W/L)Q_{inv}(V_g)}$$

(2.1)

where  $\mu_{eff}(Vg)$  and  $Q_{inv}(Vg)$  represent effective mobility and inversion charge density as a function of gate voltage, respectively. If gate to channel capacitance (Cgs) is measured as a function of gate voltage, then  $Q_{inv}(Vg)$  is calculated from an integration of the Cgs for Vg from accumulation regions to  $V_g$  by equation (2). In addition, effective field  $E_{eff}$  is a function of inversion charge and depletion charge ( $Q_D$ ) with a relationship of equation (3).

$$Q_{inv}(V_g) = \int_{-\infty}^{V_g} C_{gs}(V_g) dV_g \qquad (2.2)$$

$$E_{\text{eff}} = \frac{(0.5Q_{im} + Q_D)}{\varepsilon_{Si}} \tag{2.3}$$

Some researchers reported that the reduced carrier mobility came from the under or overestimation of the inversion charge density using conventional capacitor-voltage measurement [30, 31]. They proposed the inversion charge extraction method using

ideal C-V correction technique and modified charge pumping technique. Interface formation on silicon surface that affect increasing of EOT and pinning effect with gate electrode is one of the biggest issues in high-k research and its effects on device characteristics is under investigation. Even though various attempts have been proposed, charge trapping characteristics of high-k devices has not fully understood yet. Therefore, it is worth further systematic studying on the transient characteristics of Hf-based dielectric device.

# 2.9 NEW CHALLENGES FOR HAFNIUM BASED DIELECTRICS

#### 2.9.1 Mobility degradation

In the several years study, hafnium based dielectric transistors were suffering from severe mobility degradation and poor interface state quality due to low-quality sub-oxide formation from high-k dielectric during and after annealing processes. Charge trapping and phonon scattering were proposed to be the main cause of mobility degradation. The mobility issue is complicated by the fact that mobility values demonstrate dependence on the gate stack EOT. Therefore, different process solutions may be needed for high performance (small EOT) and low power (greater EOT) applications. Process solutions yielding ~80% universal SiO<sub>2</sub> mobility have been reported only for EOT ~ 15 Å, while the high performance EOT range has not yet been addressed. Recently it was suggested that thinning HfO<sub>2</sub> could improve mobility. However, thin film quality at the scaling limit is often poor, making it difficult to simultaneously achieve mobility, EOT and Jg targets. Obtaining more than 90% universal SiO<sub>2</sub> mobility value is required to make use of high-k device in future technology.

Fig. 2.8. Schematic carrier mobility vs. vertical field in FETs in the universal mobility model, showing the mechanisms which limit the mobility, and their temperature dependences.

The objective of device scaling is to create smaller, faster devices. Speed follows source-drain drive current, which in turn depends on the carrier mobility. Carriers in the FET behave like a two-dimensional electron gas. The carrier density is determined by the vertical gate field which induces them, by Poisson's equation. The carrier mobility in 2D gases is found to depend in a universal way on this gate field, according to the so-called universal mobility model. This idea developed from observations by Sah, Plummer [32] and others. The most recent version is by Takagi et al. [33] in which the mobility of electrons and holes depends only on the effective gate field and the Si face, [100], [110] or [111]. The individual components of mobility add according to Matthiessen's rule,

$$\frac{1}{\mu} = \frac{1}{\mu_C} + \frac{1}{\mu_{PH}} + \frac{1}{\mu_{SR}}.\tag{2.4}$$

The mobility is limited by different mechanisms at different fields, as each obeys a different power law with field, see Figure 2.8. At low fields, mobility is limited by Coulombic scattering (C) by trapped charges in the oxide and/or channel and/or the gate electrode interface; at moderate field it is limited by phonon scattering (PH),

and at high fields by scattering by surface roughness (SR). CMOS devices with a SiO<sub>2</sub> gate oxide have mobility close to the universal limit. The mobility is limited mainly by interface roughness over the range of interest. The mobilities in devices with high K gate oxides presently lie well below the universal curve. This is particularly true of NMOS devices. The reduction in mobility for PMOS devices is fractionally less. Figure 2.9 shows typical examples.

Fig. 2.9. Carrier mobility of n-type Si, for various gate oxides, after Gusev et al. [32].

A major objective of present research is to understand the cause of this lowered mobility and to try to correct it. The cause is presently not well understood. There are two likely causes. First, there could be scattering by excessive amounts of trapped charge and interface states [34]. This is clearly true as other measurements show that high K oxides have much more trapped charge than SiO<sub>2</sub>. Secondly, there is the possibility of remote scattering by low lying polar phonon modes, as noted by Fischetti et al. [35]. The two contributions can be distinguished by their temperature and by their thickness dependence. It is also possible that the reduced mobility is due to a reduced induced channel carrier density in inversion, due to the filling of interface traps. This effect has been analyzed in detail by Ma et al. [36]. It can be excluded by direct measurements of Hall effect mobility which also shows a reduction.

## 2.9.2 Chare trapping/detrapping phenomena in gate dielectrics

We have already noted that high-K oxides possess a larger bulk density of defects and trapped charge than SiO<sub>2</sub> [37]. It is now well known that the channel mobility in a high-k gated MOSFET is typically much lower than its SiO2-gated counterpart. Since it is also well known that high-k gated MOSFET tends to have more oxide charge and interface traps than its SiO2-gated counterpart. It should be noted that trapping/detrapping time constants for some of the high-k gate dielectrics, including HfO2 and Al2O3, are much shorter than those for SiO2 [38], and therefore the DC measurement methodology commonly used for MOS devices with SiO2 gate dielectric will likely to miss these traps. A transient (pulsed) measurement methodology has been introduced to reveal more fully the traps in high-k gate dielectrics [38]. Charge trapping leads to instability in the flat band voltage and gate threshold voltage. It is seen as hysteresis on a drive current vs. gate voltage plot. The effect can be demonstrated by charge pumping experiments. It is notable that HfSiOx gate oxides have less hysteresis than HfO2 and also that nitrogen addition reduces it below 70 meV. The amount of trapped charge can be reduced by various annealing cycles and by design of the oxide. It would also be helped by a clearer understanding of its origin. The origin of this trapped charge is becoming clearer. The first source is intrinsic defects in the oxide and interface traps. Zafar et al. [39] showed that trapping in HfO2 and Al2O3 occurs by the filling of existing defect levels rather than the creation of new defects. This indicates that bulk defects in high K oxides are a serious problem. Kumar [40] showed that hot carriers can create additional defects, but this is an additional effect. The trapped charge can be reduced by annealing. This can be carried out in forming gas (N2/H2 mixture), or other nitrogen containing gases such as ammonia.

The detrapping process can originate from three possible mechanisms. The first may be due to a back tunnelling of electron from traps to substrate and the second, resulting from a Poole–Frenkel-like electrons conduction from traps to traps toward the gate electrode, which we have neglected. And the third mechanism is tunneling of electrons from channel to poly-silicon gate.

### 2.9.3 Threshold Voltage (V<sub>th</sub>) instability and reliability

One of main issues for high-k gate stack is the charge trapping characteristics during reliability test. Initial observation of instability was studied through capacitance-voltage (CV) characteristics in flat-band voltage change and current-voltage (IV) change. Since electrons can be trapped and detrapped in the high-k dielectrics with a minimal residual damage to its atomic structure, a threshold voltage instability associated with electron trapping/detrapping in high-k layer can significantly affect the transistor parameters and complicate the evaluation of the effects of stress-induced defect generation phenomenon on the high-k gate stacks, which typically is not an issue in the case of SiO2 dielectrics. Pulsed based Id-Vg technique is proposed to monitor charge trapping characteristics. However origin of the charge trapping have not been clearly understood yet. Intrinsic properties of high-k film have been refocused based on pulse measurement. Since those charge trapping affect significantly on Vth measurement and reliability characteristics, comprehensive study is required to detail understand and find the solution for high-k/metal gate stack.

### 2.10 CONCLUSION

Here in this chapter the choice of high-k dielectrics as a replacement of conventional SiO<sub>2</sub> is described. But due to higher bulk trap in HfO<sub>2</sub> another problem arises which is threshold voltage instability. In this dissertation effect of trapped charges on mobility degradation has been discussed. Another noticeable phenomena is with the further shrinking (EOT<2nm) of oxide thickness charges get detrapped through the gate oxide interfaces increasing dissipated power density which has been considering as a major disadvantages to take high-k dielectric instead of conventional SiO<sub>2</sub>

### **CHAPTER 3**

# CALCULATION OF TRAP ASSISTED LEAKAGE CURRENT DENSITY, DISSIPATED POWER DENSITY AND CHANNEL MOBILITY DEGRADATION

### 3.1 INTRODUCTION

Over the past decades, the MOSFET has continually been scaled down in size to achieve lower switching time, reduces cost and lower power consumption. The scaling trend for gate dielectric is such that for sub-100 nm generation devices an equivalent gate oxide thickness of less than 2 nm will be required. In order to meet the requirement, the conventional gate oxide dielectric will need to be replaced by higher dielectric constant materials. Hafnium based dielectrics are being widely investigated as a potential replacement for the silicon oxi-nitride. However, before the final integration in to the industry, several important issues, such as mobility degradation, metal gate incompatibility and threshold voltage instability is needed to be considered. As high k oxides posses a large bulk density of defects, charge trapping leads to instability in the gate threshold voltage. Although there is some recent work done on HfO<sub>2</sub> and its MOS capacitor, the effect of charge trapping needs further investigation to ascertain the quality of performance.

The Physical limitations of the conventional silicon dioxide as gate dielectric has reached the point where films thickness are only a few atomic layers thick [41]. This results in high leakage current and degrades the device performance. To get around this critical problem, high-k dielectrics such as hafnium, zirconium, aluminum oxides [42] have been introduced. In fact, while keeping the EOT constant high-k dielectrics allow us to increase the physical thickness of the gate stack. Hence, the gate leakage is found to be reduced by 2 to 3 orders of magnitude. Despite extensive investigation on the use of high-k dielectrics, many critical problems still remain which are yet to be explored. These problems include defects in the dielectrics which can lead to mobility degradation, metal gate incompatibility, power consumption and threshold voltage instability. As high-k dielectrics posses a large bulk density of defects, charge trapping leads to instability in the gate threshold voltage. Charge trapping dynamics in hafnium based dielectric stacks and their impact on the threshold voltage instability was studied by several researchers [3-5, 39,43]. Effect of charge trapping on threshold voltage instability has also been modeled recently [5, 6]. Before using high-k materials as a potential replacement of SiO<sub>2</sub> several issues such as dissipated power density, mobility degradation, capacitance etc. should be considered. To address these issues not only high quality

films need to be deposited but also excellent electrical characteristics need to be obtained before high-k materials can be integrated into standard CMOS technology [44].

In this work, these issues are investigated incorporating both forward and backward detrapping. A model is developed to explain the mechanism of trapping detrapping phenomena in high-k stack gate dielectrics. Several important characteristics of device such as power dissipation, capacitance, threshold voltage instability, effect of stress voltage and stress time and channel mobility degradation are investigated.

### 3.2 SELF-CONSISTENT MODEL

External electric fields can change the properties of semiconductor surfaces significantly, and the consequences of such changes have been systemically explored for many years. More recently there has been considerable work on the quantum effects that arise when band bending confines the carriers to a narrow surface channel. To model the effects of quantum confinement, quantum allows the self-consistent solution of the Schrödinger equation with Poisson's equation. Properties of carriers in MOS inversion layers are studied by solving coupled Schrödinger's and Poisson's equations self-consistently within the effective-mass approximation.

The 1D Schrödinger Equation is given by

$$\left[-\frac{\hbar^{2}}{2m_{Zi}}\frac{d^{2}}{dz^{2}}+eV(z)\right]\psi_{ij}(z)=E_{ij}\psi_{ij}(z)$$

(3.1)

Here  $m_{Zi}$  is the effective-mass perpendicular to the interface in the ith valley, V (z) is the electrostatic potential and  $E_{ij}$  and  $\Psi_{ij}$  are the eigenenergy and the wave function corresponding to the jth subband in the ith valley.

The potential is calculated from Poisson's equation which is as follows

$$\epsilon_0 \epsilon_r \frac{d^2 V(z)}{dz^2} = -[\rho_{dep}(z) - en(z)]$$

(3.2)

Where n(z) represents the total inversion electron density. The inversion layer electron can exist only at eigen energies and their spatial distribution in described by the respective wave function. Under such conditions, n(z) is calculated from

$$n(z) = \sum_{ij} (n_{vi} m_{di} k_B T / \pi \hbar^2) \ln \left( 1 + \exp \left( \frac{E_F - E_{ij}}{k_B T} \right) \right) \times \left| \psi_{ij} \right|^2$$

(3.3)

Where  $n_{vi}$  and  $m_{di}$  are the velley degeneracy and the density of states effective mass for the  $i^{th}$  valley, respectively.

The boundary conditions commonly used to solve Schrödinger's equation are that the wave function goes to zero at z = 0 and at z = 1 where z = 0 is at the silicon-oxide interface and z = 1 is deep inside silicon [45].

In this thesis, we use a technique, based on Green's function formalism, to solve Schrödinger's equation with wave function penetration. This technique is described in detail in [46], [47]. Open boundary conditions are used, which are based on the assumption that the potential profile is flat at deep inside the gate metal as well as at deep inside the bulk semiconductor. Our assumption implies that the wave function deep inside the semiconductor is exponentially decaying and deep inside the gate metal, the wave function is a plane wave.

The eigenenergies of the quasi-bound states are calculated by locating the peaks of the one-dimensional (1-D) density-of-states [47]. The corresponding wave functions including penetration can easily be obtained using the relationships described in [48]. Once the eigen-energies and the wave functions are calculated, the self-consistent formulation is applied with appropriate modifications to include penetration effects also in the solution of Poisson's equation. Since a fraction of inversion charge resides within the gate-oxide due to wave function penetration,

Poisson's equation is solved for the combined oxide and semiconductor regions with the boundary conditions applied at the gate metal-oxide interface

### 3.3 CHARGE TRAP MODEL

A rate equation [3.4] for the distributed trapped electrons incorporating detrapping of electrons to the gate is developed as follows

$$\frac{dn_{t}}{dt} = \frac{n}{N_{o}} \cdot \frac{N_{t} - n_{t}}{\tau^{*}} \left[ \frac{1}{1 + \exp((E_{t}^{*} - E_{f})/kT)} \right] - \frac{n}{N_{o}} \cdot \frac{n_{t}}{\tau_{1}} \left[ 1 - \frac{1}{1 + \exp((E_{t} - E_{f})/kT)} \right] - \frac{n_{g}}{N_{og}} \cdot \frac{n_{t}}{\tau_{2}} \left[ 1 - \frac{1}{1 + \exp((E_{t} - E_{fm})/kT)} \right]$$

(3.4)

where  $n_t$  is the trapped electron density,  $N_t$  the density of the uniform bulk traps in HfO<sub>2</sub>, n the electron concentration in the channel,  $N_0$  a unit normalization factor,  $E_t^*$  the empty defect level,  $E_t$  the occupied defect level,  $E_f$  the channel electron quasi-Fermi level. In this model, the tunneling of trapped electrons to the gate has been neglected, due to lowering of charged trap levels.

The equation basically consists of three terms, the first term represents the charge trapping rate from the channel and the second term accounts for the detrapping of the trapped charges back to the channel and the third term of the Eqn.3.4 incorporates the detrapping of electrons to the poly-silicon gate, where  $E_{fm}$  is the poly-silicon gate Fermi level,  $\tau^*$  is the tunneling time constant for the forward trapping process from channels to trap.  $\tau_1$  is the tunneling time constant for the detrapping process from occupied defect state to the channel and  $\tau_2$  is the tunneling time constant for the detrapping process from occupied defect states to the gate. All these time constants are obtained using WKB approximation [49]. For the forward tunneling process from channel to traps, it is given by

$$\tau^* = \tau_O \exp\left[\frac{4\sqrt{2m^*m_O}}{3\hbar qE} \times \left[ \left( E_C^{ox} - E_t^* - qEx \right)^{\frac{3}{2}} - \left( E_C^{ox} - E_t^* \right)^{\frac{3}{2}} \right]$$

(3.5)

Considering the fact that, trap level in the oxide layer is at a high energy level from the Fermi level of the gate, trapping from the gate side is neglected.

The detrapping time constant from occupied defect states to the gate for any position y inside the high-k dielectric is expressed as

$$\tau_{2} = \tau_{o} \exp\left(\frac{4\sqrt{2m^{*}}}{3\hbar qE} \times \left(\left(E_{c}^{ox} - E_{t} + qEy\right)^{\frac{3}{2}} - \left(E_{c}^{ox} - E_{t}\right)^{\frac{3}{2}}\right)\right)$$

(3.6)

For calculating the detrapping time constant from occupied defect states to the channel, x is replaced by y, where x is the depth of the trap into the dielectric from  $SiO_2/Si$  interface.

The electron-trap centers are distributed in the HfO<sub>2</sub> bulk region as well as in the HfO<sub>2</sub>/SiO<sub>2</sub> interface [25]. Liu et al. [3] have characterized the hysteresis phenomena on samples with different HfO<sub>2</sub> thickness. Their results suggest that trapping occurs mostly in the bulk on high-k materials rather than only at the interface. We also make the following assumptions:

- 1) The electrons tunnel from the channel to the empty defect states. While detrapping, trapped charges tunnel both to the channel and gate electrode.

- 2) Here we neglect the detrapping resulting from a Pool-Frenkel-like electrons [41] conduction from traps to traps. So we have adopted a general approach originally proposed for Schottky barrier tunneling [51] to model trapping/detrapping process.

# 3.4 TRAP ASSISTED LEAKAGE CURRENT DENSITY AND DISSIPATED POWER DENSITY

We calculate the power dissipation associated with the detrapped charges through the gate electrode/ oxide interfaces.

To calculate dissipated power density, we have used the detrapping part of Eqn. 3.4 The leakage current density associated with the detrapped charges termed as "Trap Assisted Leakage Current density (TALC)",  $J_{TALC}$  has been calculated for an entire pulse width using the following equation.

$$J_{TALC} = \frac{1}{T} \int_{0}^{T} J_{d} dt \tag{3.7}$$

Where  $J_d$  has been calculated using the third term of Eq. 3.4.

$$J_{d} = q \times \sum \frac{n_{g}}{N_{0g}} \frac{n_{t}}{\tau_{2}} \left\{ 1 - F(E_{t}, E_{fg}) \right\}$$

(3.8)

Where  $F(E_i, E_{fg})$  is given by

$$F(E_{t}, E_{fg}) = \frac{1}{1 + e^{\frac{E_{t} - E_{fg}}{kT}}}$$

(3.9)

Here we calculate *TALC* for a given instant time of the pulse width summing up all the current components associated with the detrapped charges form the electron-trap centers which are distributed in the high-k bulk region as well as in the high-k dielectric/SiO<sub>2</sub> interface. We neglect the off-state dissipated power density as the gate voltage is zero and the average dissipated power density for an entire time period has been calculated using the Eq. 3.9.

$$P_{dissipation} = \frac{1}{2} V_g J_{TALC} \tag{3.10}$$

Where T is the total time period having duty cycle 50%.

To compare the  $J_{DTC}$  density with the direct tunneling current (DTC) density we have also calculated  $J_{DTC}$  through the oxide barrier by summing up the contribution from all subbands current density arising from the i-th subband j-th valley as a function of gate voltage and the expression as

$$J_{DIC} = \sum q v_g \left| \psi_{ij} \right|^2 N_{ij} \tag{3.11}$$

### 3.5 MOBILITY CALCULATION

Modeling of MOS devices requires a mobility model which can accurately capture the dependence of effective mobility on Effective field in the inversion layer. We have calculated the mobility based on Darwish mobility model [52] and Klaassen model [53]. Here the functional dependence of surface roughness limited mobility on the inversion charge density, in addition to accounting for the coulomb screening effect in the bulk limited mobility [53] is taken into consideration

To evaluate the carrier mobility the Mathiessen rule has been used that approximates the local mobility,  $\mu_0(\vec{r})$ , at low longitudinal field as the sum of three terms [54]

$$\frac{1}{\mu_0(r)} = \frac{1}{\mu_b(r)} + \frac{1}{\mu_{ac}(r)} + \frac{1}{\mu_{sc}(r)}$$

$$(3.12)$$

where  $\mu_b(\vec{r})$  is the carrier mobility in the bulk,  $\mu_{ac}(\vec{r})$  is the carrier mobility limited by surface acoustic phonon scattering, and  $\mu_{sr}(\vec{r})$  is the carrier mobility limited by surface roughness. To emphasize the local nature of this model, we will use the variable  $(\vec{r})$  to designate spatial dependence.

The bulk mobility term  $\mu_b(r)$ , uses the Klaassen model [53], which takes into account coulomb screening effects, separately models majority and minority carrier mobilities, and includes temperature dependence

$$\frac{1}{\mu_b(r)} = \frac{1}{\mu_L} + \frac{1}{\mu_I(r)}$$

(3.13)

where

$$\mu_{L} = \mu_{\text{max}} (\frac{300}{T})^{\theta_{n}} \tag{3.14}$$

$$\mu_{I}(\overrightarrow{r}) = \mu_{N}(\underbrace{N_{I}(\overrightarrow{r})}_{N_{leff}})(\underbrace{N_{ref1}}_{ref1})^{\alpha 1} + \mu_{c}(\underbrace{n(\overrightarrow{r})}_{N_{leff}})$$

$$N_{leff}(\overrightarrow{r})$$

(3.15)

$$\mu_{N} = \frac{\mu_{\text{max}}^{2}}{\mu_{\text{max}} - \mu_{\text{min}}} \left(\frac{300}{T}\right)^{3\alpha_{1}-1.5}$$

(3.16)

$$\mu_c = \frac{\mu_{\min} \mu_{\max}}{\mu_{\max} - \mu_{\min}} \left(\frac{300}{T}\right)^{0.5} \tag{3.17}$$

where  $n(\vec{r})$  is the total carrier concentration (n+p) and  $N_1(\vec{r}) = N_A(\vec{r}) + N_D(\vec{r})$ . For electrons,  $N_{leff}(\vec{r}) = G(P_e)N_A(\vec{r}) + N_D(\vec{r})$ , where  $G(P_e)$  is the ratio between collision cross sections of repulsive and attractive screened coulomb potentials for electrons and is a function of the local carrier concentration,  $n(\vec{r})$ .