# **Single Phase Switch Mode Cycloconverters**

by

Md. Ashfanoor Kabir

MASTER OF SCIENCE IN ELECTRICAL AND ELECTRONIC ENGINEERING

Department of Electrical and Electronic Engineering

BANGLADESH UNIVERSITY OF ENGINEERING AND TECHNOLOGY

January 2012

The thesis titled "Single Phase Switch Mode Cycloconverters" submitted by Md. Ashfanoor Kabir, Student No.: 1009062036, Session: October, 2009, has been accepted as satisfactory in partial fulfillment of the requirement for the degree of MASTER OF SCIENCE IN ELECTRICAL AND ELECTRONIC ENGINEERING on January 21, 2012.

#### **BOARD OF EXAMINERS**

| l. |                                                                                                                                                                                  | _                        |

|----|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------|

|    | Dr. Mohammad Ali Choudhury  Professor  Department of Electrical and Electronic Engineering,  Bangladesh University of Engineering and Technology,  Dhaka – 1000, Bangladesh.     | Chairman<br>(Supervisor) |

| 2. |                                                                                                                                                                                  | _                        |

|    | Dr. Md. Saifur Rahman  Professor and Head  Department of Electrical and Electronic Engineering,  Bangladesh University of Engineering and Technology,  Dhaka – 1000, Bangladesh. | Member<br>(Ex-officio)   |

| 3. |                                                                                                                                                                                  | _                        |

|    | Dr. Kazi Mujibur Rahman  Professor  Department of Electrical and Electronic Engineering,  Bangladesh University of Engineering and Technology,  Dhaka – 1000, Bangladesh.        | Member                   |

| 4. |                                                                                                                                                                                  | _                        |

|    | Dr. Muhammed Fayyaz Khan  Professor and Head  Department of Electrical and Electronic Engineering, United International University, Dhaka-1209, Bangladesh.                      | Member<br>(External)     |

# **CANDIDATE'S DECLARATION**

| It is hereby declared that this thesis or any part of it has not been submitted elsewhere |

|-------------------------------------------------------------------------------------------|

| for the award of any degree or diploma and that all sources are acknowledged.             |

|                                                                                           |

|                                                                                           |

|                                                                                           |

|                                                                                           |

|                                                                                           |

| Signature of the Candidate                                                                |

|                                                                                           |

|                                                                                           |

|                                                                                           |

|                                                                                           |

| Md. Ashfanoor Kabir                                                                       |

| Mu. Ashlahuui Kauli                                                                       |

# **Dedication**

To my parents.

## Acknowledgement

First of all, I would like to thank Allah for giving me the ability to complete this thesis work.

I would like to express my sincere gratitude to my supervisor, Dr. Mohammad Ali Choudhury. This thesis would not have been completed without his support and guidance. His constant encouragement gave me the confidence to carry out my work.

I would like to thank all my teachers. They gave the knowledge and directions that have helped me throughout my life. I express my gratitude to my teachers from Bangladesh University of Engineering and Technology. The knowledge I learned from the classes in my B.Sc. and M.Sc. levels were essential for this thesis.

I want to thank my friends for providing my support and encouragement. Their suggestions helped me in countless ways.

Last but not the least, I would like to thank my parents. Their optimism and encouragement have allowed me to overcome any obstacle that I face. Their unconditional support made it possible for me to finish this thesis.

#### **ABSTRACT**

This thesis proposes new single phase cycloconverters based on switch mode topologies. Boost, Buck-Boost and Ćuk switch mode schemes are employed to control the output voltages. The proposed cycloconverters provide control in terms of both frequency and amplitude of the output voltage. The design of the proposed circuits is divided into two steps. First, the input AC signal is made unidirectional by employing full bridge rectifier. Based on the requirement of frequency and amplitude of the voltage at the load, this unidirectional voltage either applied on the same side or on opposite side of the load. The proposed topologies consist of two SMPS based converters namely the P and the N converters that are connected across the load. Input AC chopping at high frequency provides switched AC current that requires small filter to make the current waveform nearly sinusoid and in phase with input voltage. As a result, the input current THD reduces and the power factor improves. High frequency switch mode conversion for both positive and negative cycles of the input signal achieves this goal. Switch mode schemes in the P and N converters provide high frequency switching of the input current and thereby ensuring low input current THD and high input power factor which are the two desirable power quality criteria for power electronic converters.

Compared to conventional 8 SCR cycloconverters the proposed topologies are able to provide output voltages both higher and lower than the supply. Depending on the load demand it is possible to offer output frequencies higher or lower than the input signal. Moreover, the proposed topologies have reduced number of switches. The numbers of solid state switches for each converter are two and in total each of the proposed topologies consist four switches. This reduction of switches has incorporated some advantages in the switch mode cycloconverters. First, the reduction of switch count has reduced the switching losses. Consequently the efficiency of proposed converters is increased. Second, less number of isolation schemes will be required in the proposed circuits. Third, the number of signal drives is reduced and finally, the proposed topology has higher reliability as the number of switches is reduced.

The control scheme employed here is the open-loop sliding control. This scheme directly controls the gate pulses of the solid state switches without any current sensing and feedback. Compared to the reported cycloconverter control schemes that involve complex algorithms requiring current sensing and feedback, the proposed control schemes provides simplicity and improved reliability of operation. Results are obtained for standard metrics like, input current total harmonic distortion, input power factor and energy conversion efficiency. The obtained results showed that the proposed schemes are able to provide AC-AC conversion at high efficiencies maintaining low input current THD and high input power factors along the range of the duty cycle of the control signal.

# **CONTENTS**

| L | IST OF TA | ABLES                                                 | xi   |

|---|-----------|-------------------------------------------------------|------|

| L | IST OF FI | GURES                                                 | xii  |

| L | IST OF AI | BBRAVIATIONS                                          | xvi  |

| L | IST OF SY | MBOLS                                                 | xvii |

|   |           |                                                       |      |

| 1 | INTROI    | DUCTION                                               | 1    |

|   | 1.1 Cy    | cloconverters                                         | 1    |

|   | 1.2 Re    | view of Literature                                    | 3    |

|   | 1.3 Ob    | jective                                               | 6    |

|   | 1.4 Ou    | tline of the Thesis                                   | 7    |

| 2 | CYCLO     | CONVERTER TYPES                                       | 9    |

|   | 2.1 Cla   | assification Based on Criterion of Energy Conversion  | 9    |

|   | 2.1.1     | Single-phase to Single-phase (1φ-1φ) Cycloconverter   | 9    |

|   | 2.1.2     | Three-Phase to Single-Phase (3φ-1φ) Cycloconverter    | 11   |

|   | 2.1.3     | Three-Phase to Three-Phase (3φ-3φ) Cycloconverter     | 13   |

|   | 2.2 Cla   | assification Based on Method of Current Flow          | 15   |

|   | 2.2.1     | Blocking Mode Cycloconverters                         | 16   |

|   | 2.2.2     | Circulating Current Cycloconverters                   | 16   |

|   | 2.3 Ne    | wer Types of Cycloconverters                          | 18   |

|   | 2.3.1     | Matrix Converter                                      | 18   |

|   | 2.3.2     | Single-Phase to Three-Phase (1φ - 3φ) Cycloconverters | 19   |

| 3 | CYCLO     | CONVERTER CONTROL SCHEMES                             | 21   |

|   | 3.1 Co    | sine Wave Control:                                    | 21   |

|   | 3.2 Co    | rrection Methods for Cosine Wave Crossing Control     | 24   |

|   | 3.2.1     | Regular Sampling                                      | 24   |

|   | 3.2.2     | Ripple Voltage Integral Feedback                      | 24   |

|   | 3.2.3     | Current Feedback Method                               | 25   |

|   | 3.3 Int   | egral Control                                         | 26   |

|   | 3.4 Pre   | e-integral Control                                    | 27   |

|   | 3.5 Do    | uble Integral control [21]:                           | 29   |

|   | 3.6  | Spa  | ce Vector Modulation (SVM):                   | 29  |

|---|------|------|-----------------------------------------------|-----|

|   | 3.7  | Del  | ta Modulation (DM) Techniques:                | 30  |

|   | 3.8  | Gro  | oup Frequency (GF) Method:                    | 31  |

| 4 | POW  | VER  | QUALITY ANALYSIS OF CYCLOCONVERTERS           | 33  |

|   | 4.1  | Har  | monic Distortion                              | 33  |

|   | 4.2  | Ind  | ividual and Total Harmonic Distortion         | 37  |

|   | 4.3  | Pov  | ver Factor                                    | 39  |

|   | 4.4  | Dis  | placement and True Power Factor               | 41  |

| 5 | SINC | GLE  | PHASE BUCK-BOOST CYCLOCONVERTER               | 42  |

|   | 5.1  | Cir  | cuit Configuration                            | 42  |

|   | 5.2  | Ope  | eration                                       | 43  |

|   | 5    | .2.1 | The P-converter.                              | 43  |

|   | 5    | .2.2 | The N-converter                               | 48  |

|   | 5.3  | Sim  | nulation results:                             | 51  |

|   | 5    | .3.1 | Performance under variable control conditions | 51  |

|   | 5    | .3.2 | Open Loop Sliding Control                     | 52  |

|   | 5    | .3.3 | Typical Waveforms                             | 53  |

|   | 5    | .3.4 | Performance Under Variable Load Conditions    | 55  |

|   | 5    | .3.5 | Performance of Step-up Frequency Operation    | 57  |

|   | 5    | .3.6 | Performance with R-L Load                     | 59  |

|   | 5.4  | Dis  | cussion                                       | 60\ |

| 6 | ĆUK  | то   | POLOGY BASED CYCLOCONVERTER                   | 61  |

|   | 6.1  | Cir  | cuit Configuration                            | 61  |

|   | 6.2  | Ope  | eration                                       | 62  |

|   | 6    | .2.1 | P converter                                   | 63  |

|   | 6    | .2.2 | N converter                                   | 66  |

|   | 6.3  | Sin  | nulation Results                              | 68  |

|   | 6    | .3.1 | Performance at Variable Control Conditions    | 68  |

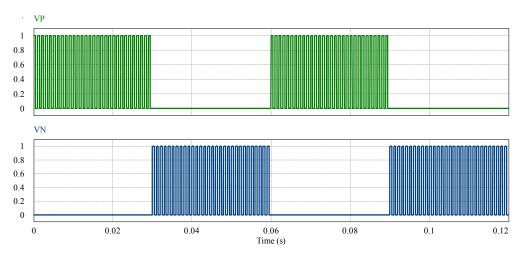

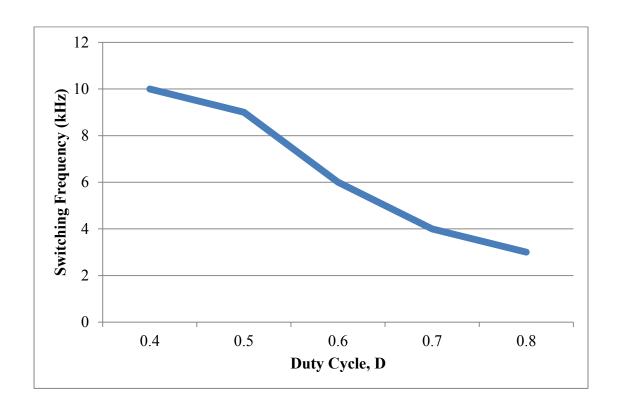

|   | 6    | .3.2 | Open Loop Sliding Control                     | 70  |

|   | 6    | .3.3 | Typical Waveforms                             | 71  |

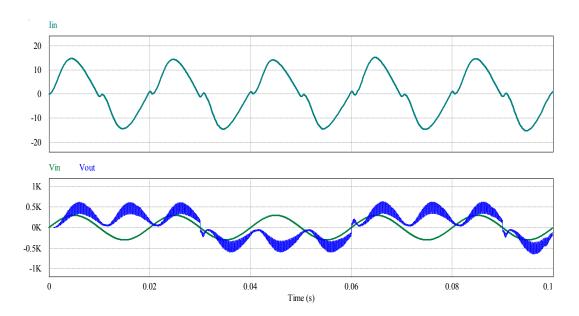

|   | 6    | .3.4 | Performance at Variable Load Conditions       | 73  |

|    | 6.3.5      | Performance of Step-up Frequency Operation  | 75  |

|----|------------|---------------------------------------------|-----|

|    | 6.3.6      | Performance with R-L Load                   | 76  |

|    | 6.4 Dis    | scussion                                    | 77  |

| 7  | SINGLE     | E PHASE BOOST CYCLOCONVERTER                | 78  |

|    | 7.1 Ci     | rcuit Configuration                         | 78  |

|    | 7.2 Op     | peration                                    | 79  |

|    | 7.2.1.     | . The P-converter                           | 79  |

|    | 7.2.2.     | . The N-converter                           | 84  |

|    | 7.3 Sir    | mulation results:                           | 87  |

|    | 7.3.1      | Performance at Different Control Conditions | 87  |

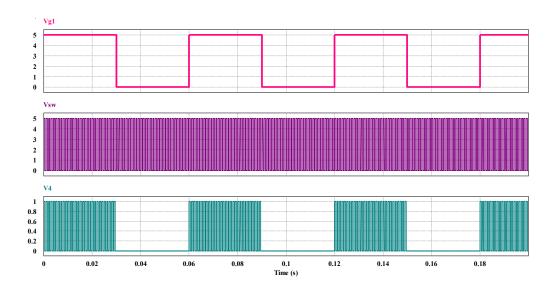

|    | 7.3.2      | Open Loop Sliding Control                   | 87  |

|    | 7.3.3      | Typical Waveforms                           | 89  |

|    | 7.3.4      | Performance at Variable Load Conditions     | 91  |

|    | 7.3.5      | Performance of Step-up Frequency Operation  | 94  |

|    | 7.3.6      | Performance with R-L Load                   | 95  |

|    | 7.4 Dis    | scussion                                    | 96  |

| 8  | COMPA      | ARISON OF RESULTS                           | 97  |

|    | 8.1 Sir    | ngle Phase 8 SCR Cycloconverter             | 97  |

|    | 8.1.1      | Gating Sequence:                            | 97  |

|    | 8.1.2      | Characteristics Waveforms                   | 98  |

|    | 8.1.3      | Simulation results                          | 100 |

|    | 8.2 Per    | rformance Comparison                        | 101 |

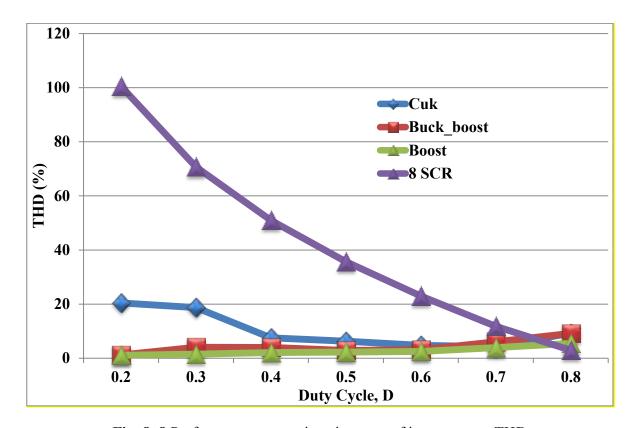

|    | 8.2.1      | Based on input current THD                  | 101 |

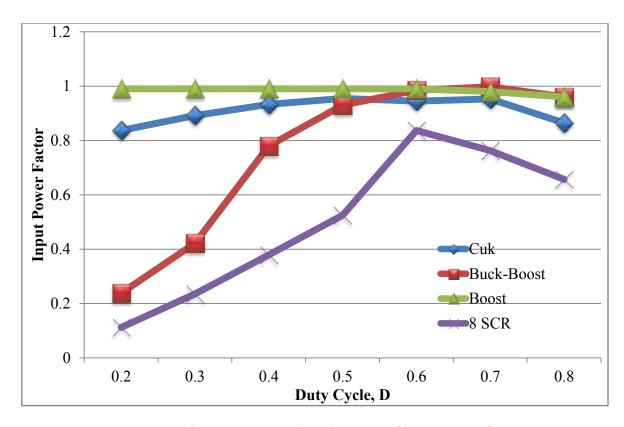

|    | 8.2.2      | Based on input power factor                 | 104 |

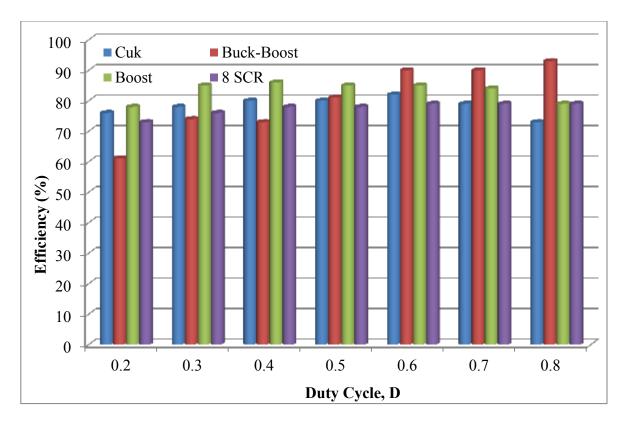

|    | 8.2.3      | Based on power conversion efficiency        | 105 |

|    | 8.3 Dis    | scussion                                    | 106 |

| 9  | CONCL      | USION                                       | 107 |

|    | 9.1. Su    | mmary                                       | 107 |

|    | 9.2. Sco   | ope for future work                         | 108 |

| ים | r pro priv | CEC                                         | 100 |

# LIST OF TABLES

| Table 3.1 Approximate maximum stable unit gain frequency of the feedback     |     |

|------------------------------------------------------------------------------|-----|

| loop for a 50 Hz input frequency, 3-pulse cycloconverter                     | 25  |

| Table 5.1 Simulation output for different duty cycle at different switching  |     |

| frequencies                                                                  | 52  |

| Table 5.2 Output behavior for sweeping characteristics of the converter      | 53  |

| Table 5.3 Change in output behavior with load                                | 56  |

| Table 5.4 Output behavior for output frequency double than input             | 58  |

| Table 5.5 Performance of the proposed Buck-Boost cycloconverter with R-L     |     |

| load                                                                         | 59  |

| Table 6.1 Performances under different switching frequencies and duty cycles | 69  |

| Table 6.2 Results from the open loop sliding control of the converter        | 70  |

| Table 6.3 Proposed Ćuk cycloconverter performance at varying loads           | 73  |

| Table 6.4 Simulation results for output frequency 150 Hz                     | 75  |

| Table 6.5 Performance of the proposed Ćuk cycloconverter with R-L load       | 76  |

| Table 7.1 Simulation output for different duty cycle at different switching  |     |

| frequencies                                                                  | 88  |

| Table 7.2 Output behavior for sweeping characteristics of the converter      | 88  |

| Table 7.3 Change in output behavior with load                                | 92  |

| Table 7.4 Output behavior for output frequency double than input             | 94  |

| Table 7.5 Performance of the proposed Boost cycloconverter with R-L load     | 95  |

| Table 8.1 Performance of the conventional 8 SCR cycloconverters              | 100 |

| Table 8.2 Variation of input current THD with the value of IGRs for single   |     |

| phase 8 SCR cycloconverters                                                  | 102 |

| Table 8.3 Comparison of proposed and conventional cycloconverters' input     |     |

| power factors in terms of certain range of input current THD (%)             | 104 |

# LIST OF FIGURES

| Fig. 2.1  | Single-phase to single-phase cycloconverter.                                         | 10 |

|-----------|--------------------------------------------------------------------------------------|----|

| Fig. 2.2  | Single-phase to single-phase cycloconverter waveforms.                               | 10 |

| Fig. 2.3  | 3ф-1ф half-wave cycloconverter                                                       | 12 |

| Fig. 2.4  | 3ф-1ф full-wave bridge cycloconverter                                                | 13 |

| Fig. 2.5  | 3ф-3ф half-wave cycloconverter                                                       | 14 |

| Fig. 2.6  | 3ф-3ф full-wave bridge cycloconverter                                                | 15 |

| Fig. 2.7  | Circulating current mode ( $3\varphi$ - $3\varphi$ half-wave) cycloconverter and IGR | 17 |

| Fig. 2.8  | Matrix Converter                                                                     | 18 |

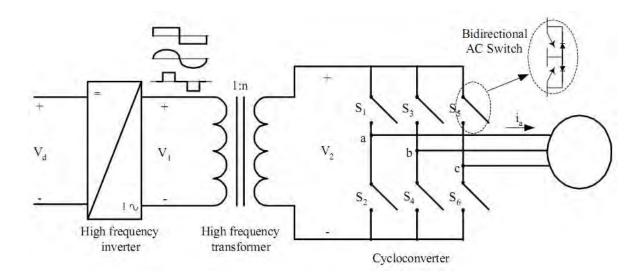

| Fig. 2.9  | High frequency AC link converter                                                     | 19 |

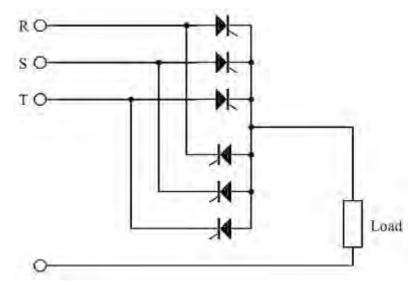

| Fig. 3.1  | Three phase, 3-pulse cycloconverter for cosine wave control                          | 21 |

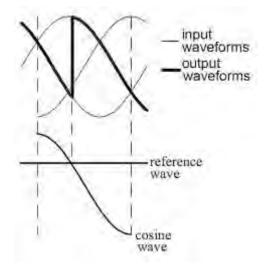

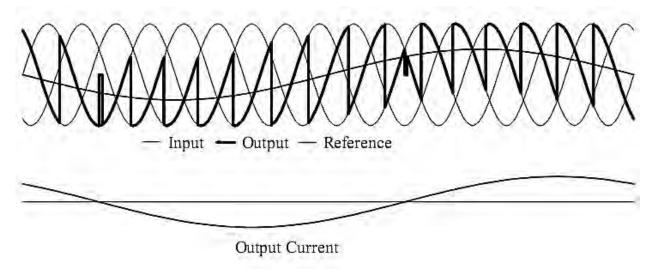

| Fig. 3.2  | Cosine wave crossing phase control method for 3 pulse cycloconverter                 | 22 |

| Fig. 3.3  | Idealized waveforms with cosine wave control for a 3-pulse                           |    |

| cyclocon  | verter with 45° lagging load current                                                 | 22 |

| Fig. 3.4  | Block diagram of cosine-wave modulation                                              | 23 |

| Fig. 3.5  | Simplified block diagram of ripple voltage integral feedback control                 |    |

| scheme .  |                                                                                      | 24 |

| Fig. 3.6  | Simplified block diagram of current feedback control scheme                          | 25 |

| Fig. 3.7  | Block diagram of integral control.                                                   | 26 |

| Fig. 3.8  | Waveforms obtained from a 2-pulse cycloconverter with integral                       |    |

| control   |                                                                                      | 27 |

| Fig. 3.9  | An example of instability for a 2-pulse cycloconverter with integral                 |    |

| control   |                                                                                      | 27 |

| Fig. 3.10 | Illustration of the pre-integral control method for positive load current            | 28 |

| Fig. 3.11 | Pre-integral control with discontinuous current                                      | 28 |

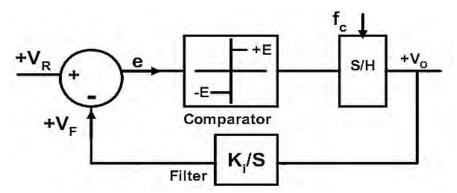

| Fig. 3.12 | Block diagram of delta modulator                                                     | 30 |

| Fig. 3.13 | Delta Modulation Technique; (a) Reference signal and carrier signal,                 |    |

| (b) Delta | a modulated switching functions, (c) Error signal with hysteresis band               |    |

| ±H        |                                                                                      | 31 |

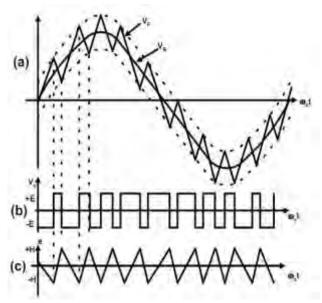

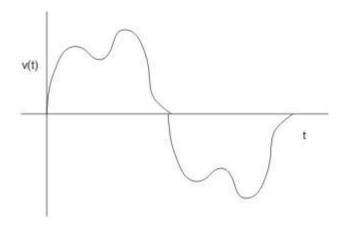

| Fig. 4.1  | Waveform with distortion.                                                            | 34 |

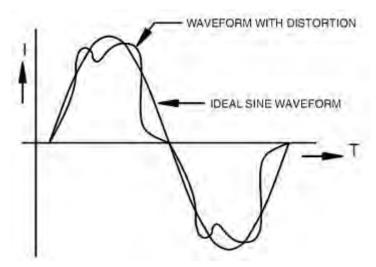

| Fig. 4.2  | Sinusoidal voltage and current functions of time (t). Lagging functions              |    |

| are indic | ated by negative phase angle and leading functions by positive phase                 |    |

| angle     |                                                                                      | 35 |

| Fig. 4.3 Non-sinusoidal voltage waveform Fourier series.                            | 35 |

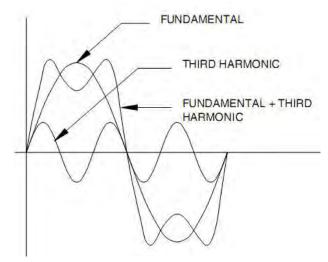

|-------------------------------------------------------------------------------------|----|

| Fig. 4.4 Creation of nonlinear waveform by adding the fundamental and third         |    |

| harmonic frequency waveforms.                                                       | 36 |

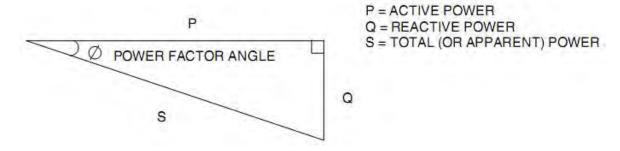

| Fig. 4.5 Power triangle and relationship among active, reactive, and apparent       |    |

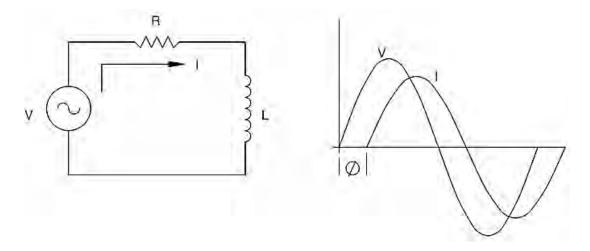

| power.                                                                              | 40 |

| Fig. 4.6 Voltage, current, and power factor angle in a resistive/inductive circuit  | 40 |

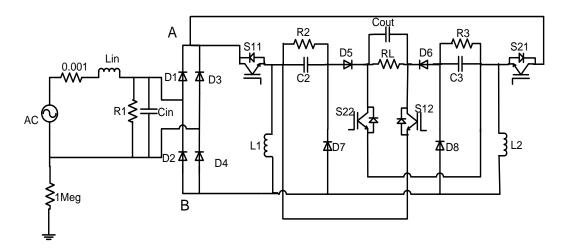

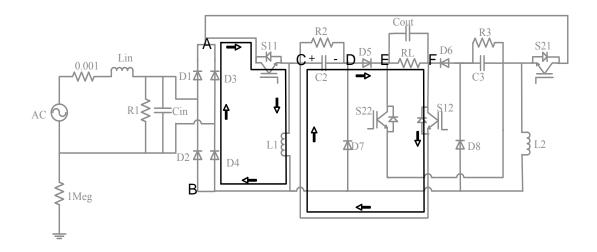

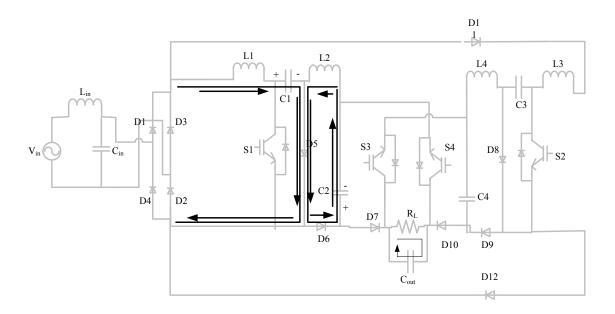

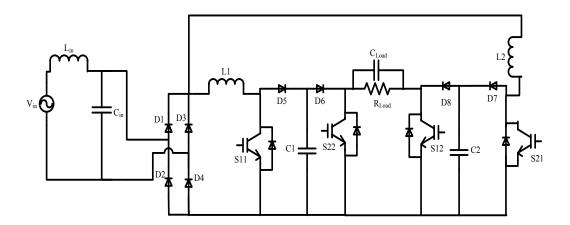

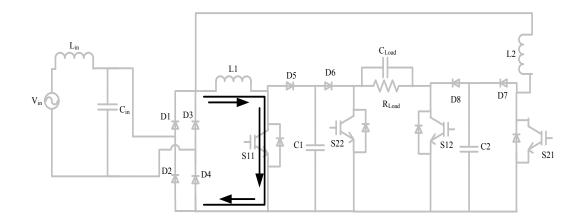

| Fig. 5.1 Proposed single phase cycloconverter based on Buck-Boost topology          | 42 |

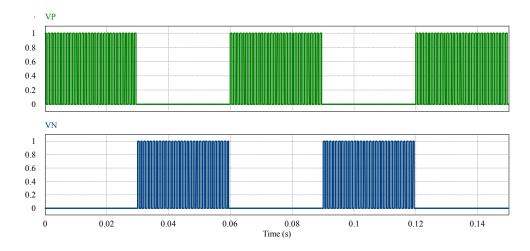

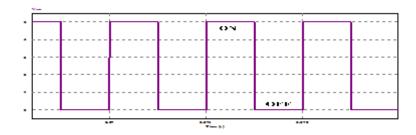

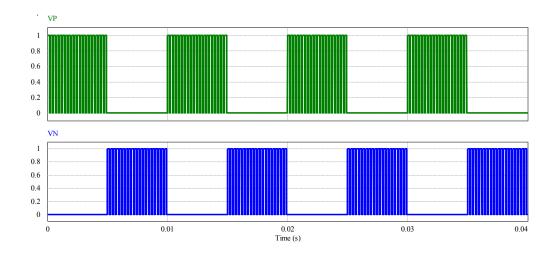

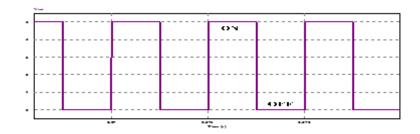

| Fig. 5.2 Switching characteristics of the P and N converter for Buck-Boost          |    |

| Topology                                                                            | 43 |

| Fig. 5.3 Buck-Boost topology based P-converter                                      | 44 |

| Fig. 5.4 Switching scheme of the P-converter                                        | 44 |

| Fig. 5.5 Current flow direction during switch is ON in P-converter                  | 45 |

| Fig. 5.6 On-Off cycle of the switches                                               | 45 |

| Fig. 5.7 Current flow direction when switch is OFF in P-converter                   | 46 |

| Fig. 5.8 Charging and discharging of the output capacitor at P conversion           | 47 |

| Fig. 5.9 Charging and discharging of the output capacitor at P conversion           | 48 |

| Fig. 5.10 Buck-Boost topology based N-converter                                     | 48 |

| Fig. 5.11 Current flow direction when switch is ON in N-converter                   | 49 |

| Fig. 5.12 Current flow direction when switch is OFF in N-converter                  | 50 |

| Fig. 5.13 Charging and discharging cycle of the output capacitor at N-              |    |

| conversion                                                                          | 50 |

| Fig. 5.14 Input and Output voltages at N-conversion                                 | 51 |

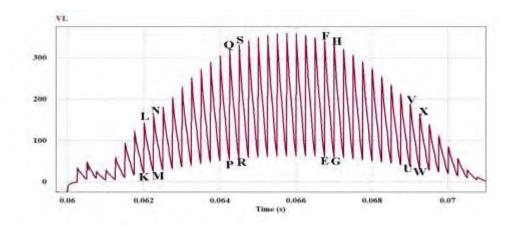

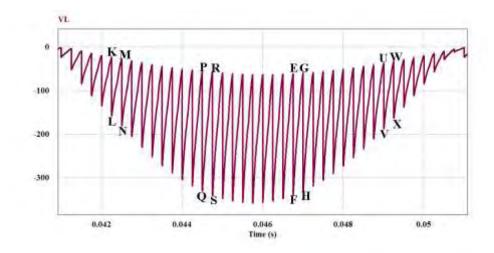

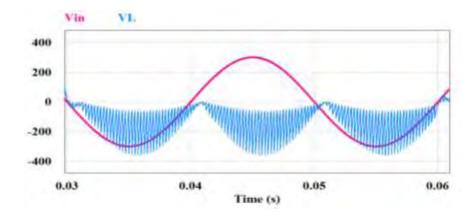

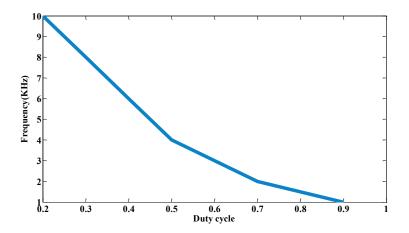

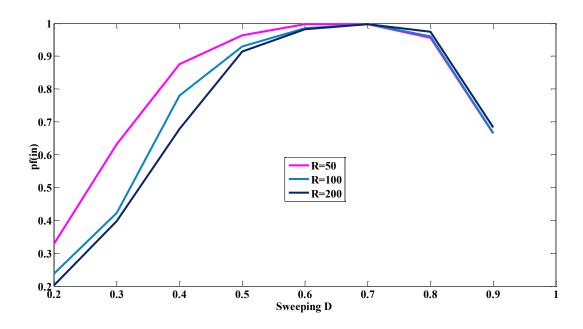

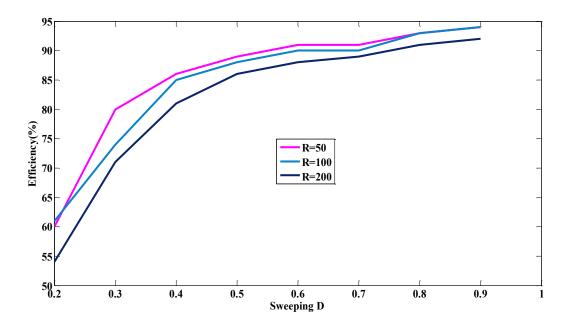

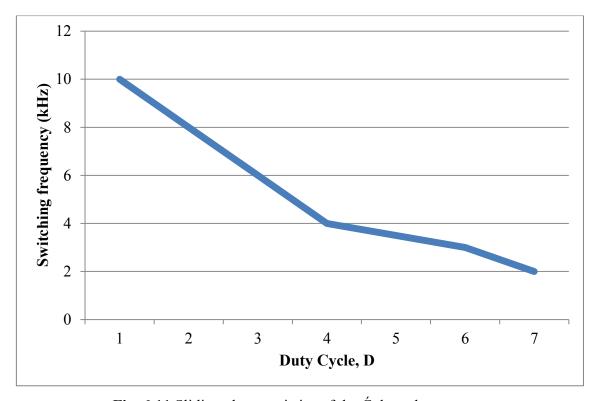

| Fig. 5.15 Sweeping characteristics for Buck-Boost cycloconverter                    | 53 |

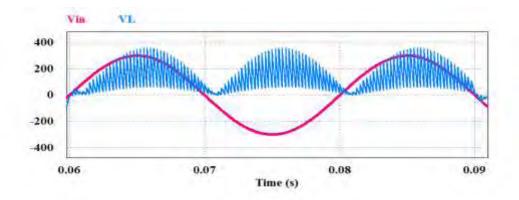

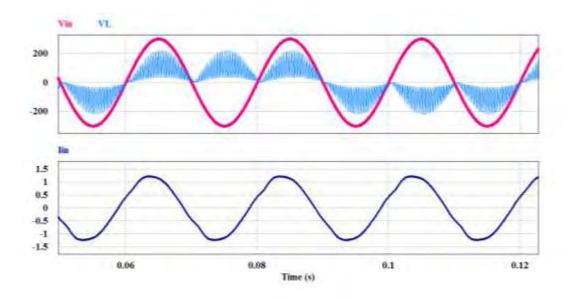

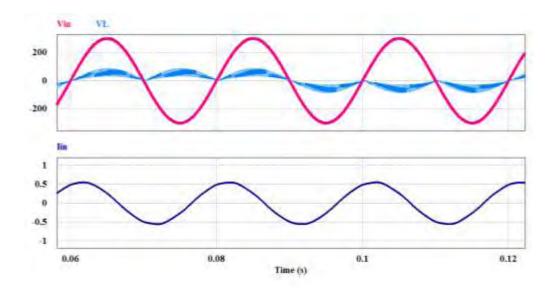

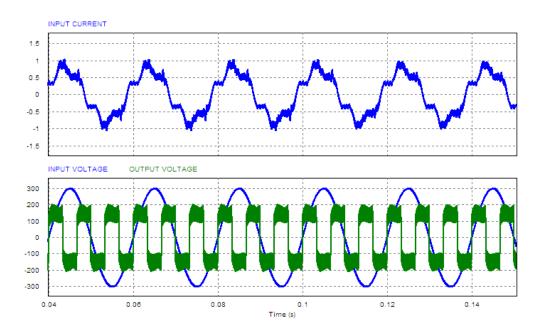

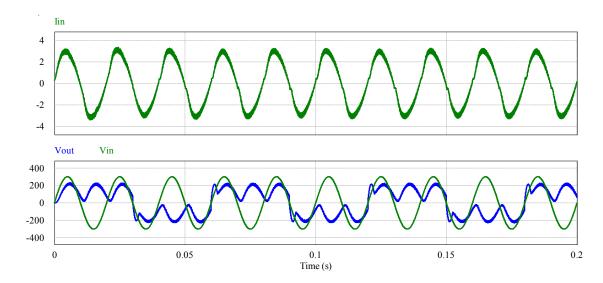

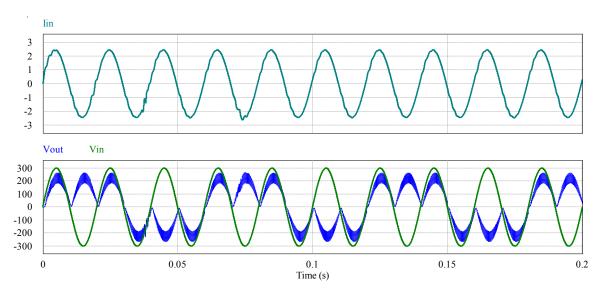

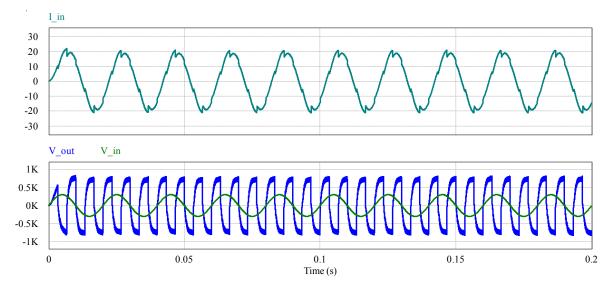

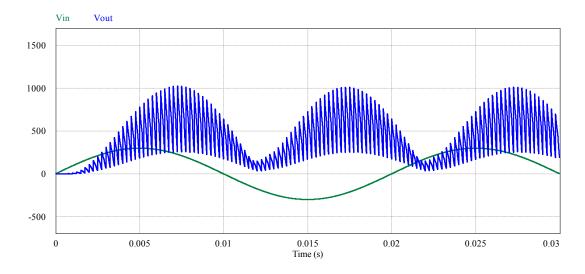

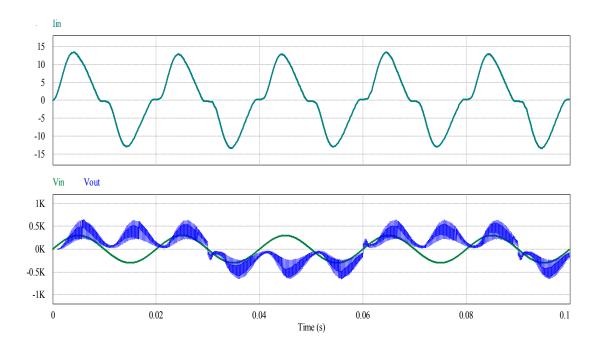

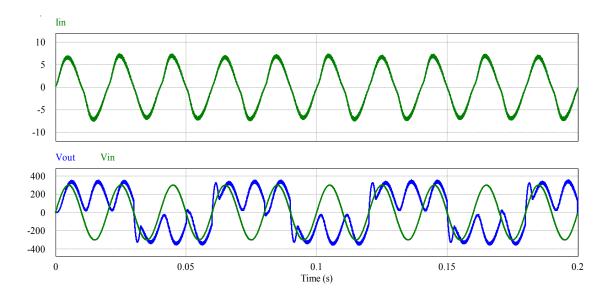

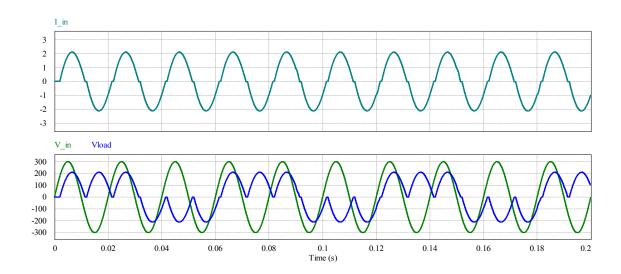

| Fig. 5.16 Input current and Input & Output voltages at D=0.5 and f=4 KHz            | 54 |

| Fig. 5.17 Input current and Input & Output voltages at D=0.3 and f=8 KHz            | 54 |

| Fig. 5.18 Input current and Input & Output voltages at D=0.7 and f=2 KHz            | 55 |

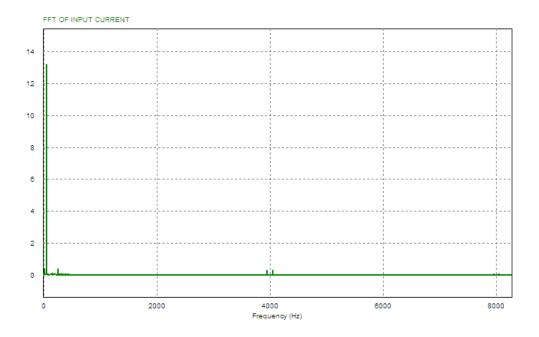

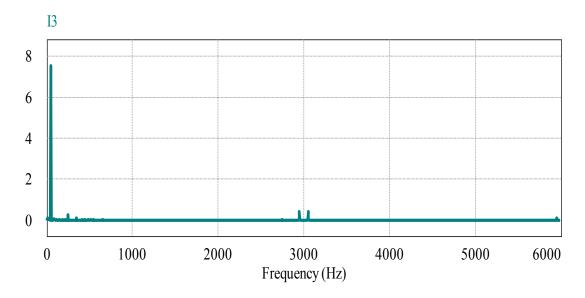

| Fig. 5.19 Spectrum of the input current for $D=0.5$ and $f=4$ kHz                   | 55 |

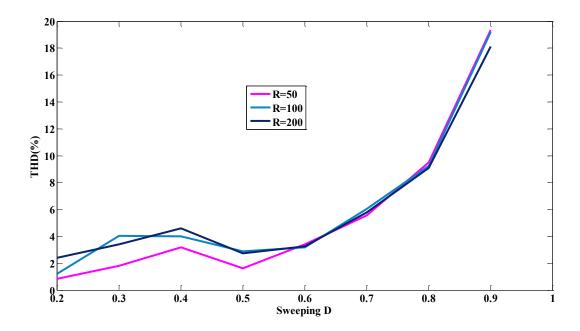

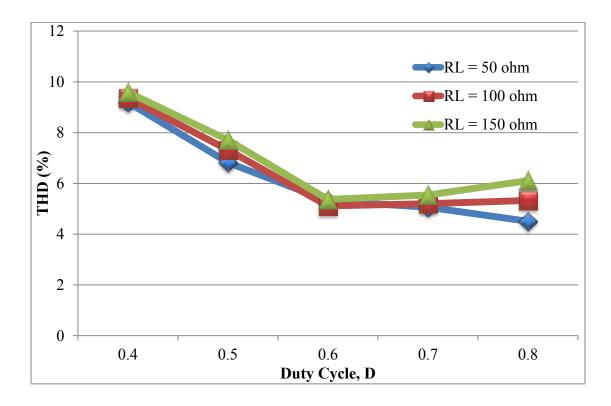

| Fig. 5.20 Variation in THD with different load at different position                | 56 |

| Fig. 5.21 Variation in input power factor with different load at different position | 57 |

| Fig. 5.22 Variation in efficiency with different load at different position         | 57 |

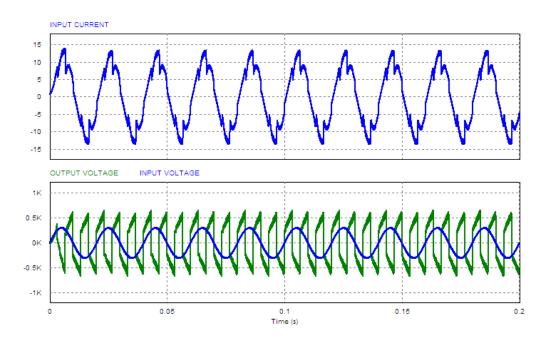

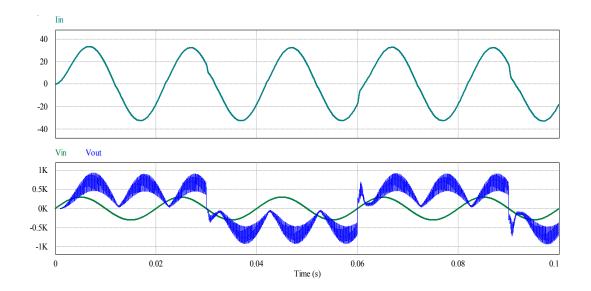

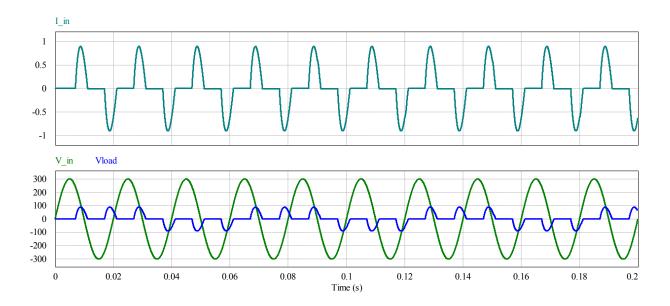

| Fig. 5.23 Input current and Output & Input voltages at D=0.3 and f=8 KHz            | 58 |

| Fig. 5.24 Input current and Output & Input voltages at D=0.7 and f=2 KHz            | 59 |

| Fig. 5.25 Input current, input and output voltages for R-L load with $D = 0.4$ and  |    |

| f=6 kHz                                                                             | 60 |

| Fig. 5.26 | Input current, input and output voltages for R-L load with $D = 0.8$ and               |    |

|-----------|----------------------------------------------------------------------------------------|----|

| f=1.5 kH  | z                                                                                      | 60 |

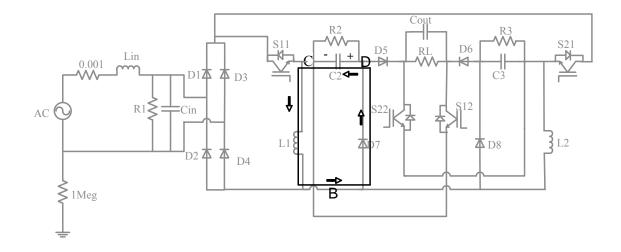

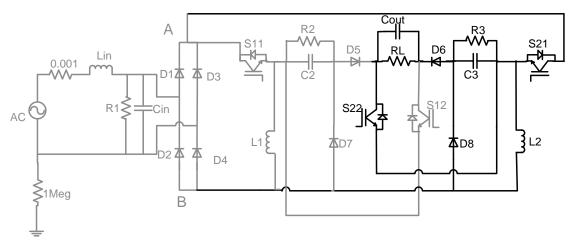

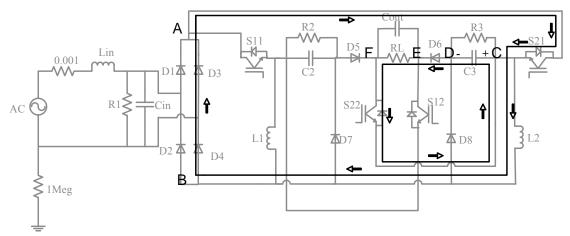

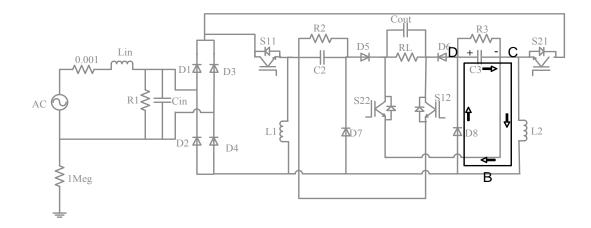

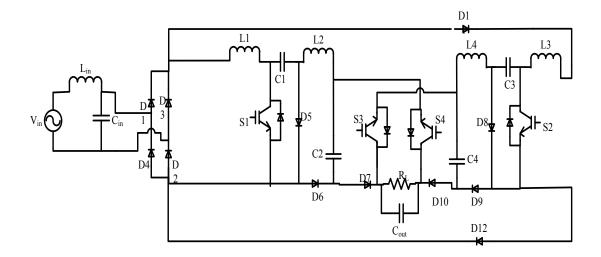

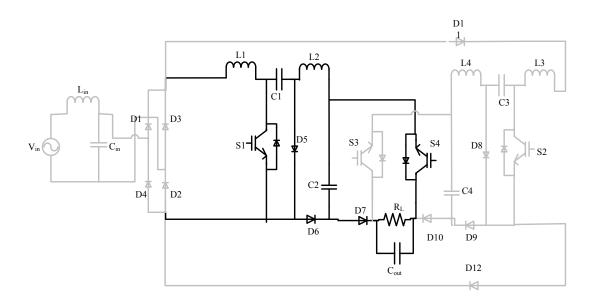

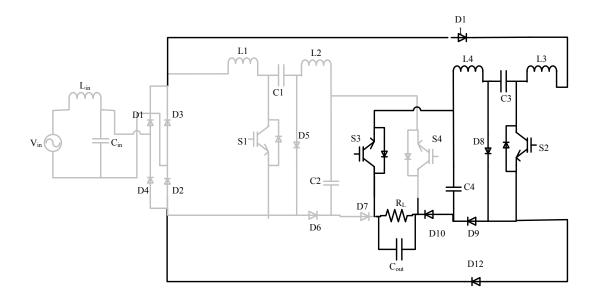

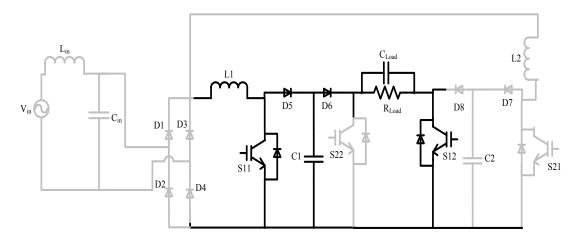

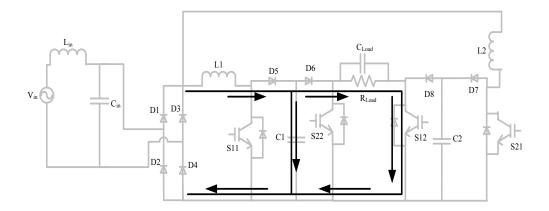

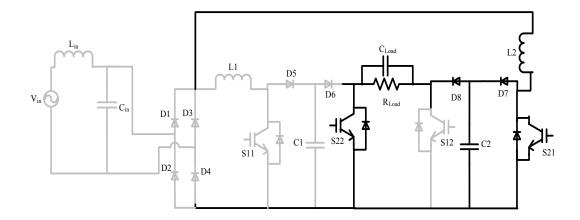

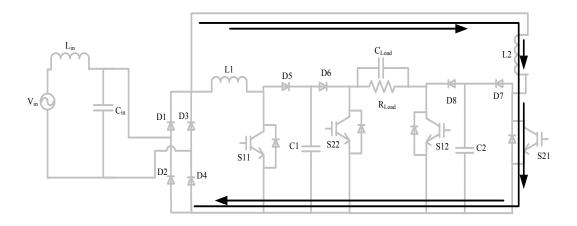

| Fig. 6.1  | Circuit diagram of a cycloconverter based on Ćuk topology.                             | 62 |

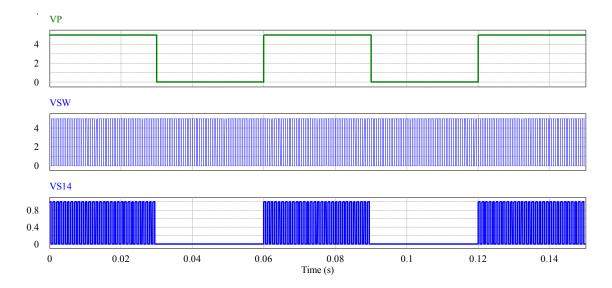

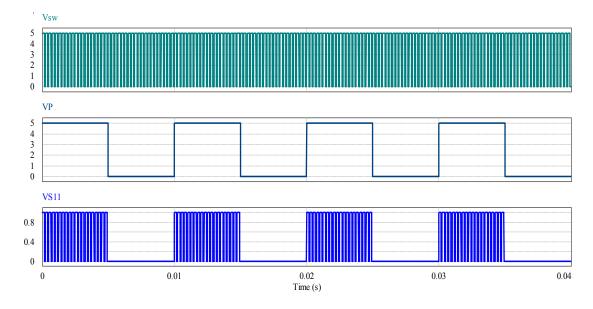

| Fig. 6.2  | Switching characteristics of the P and N converter for Ćuk Topology                    | 63 |

| Fig. 6.3  | The Ćuk topology based P converter                                                     | 63 |

| Fig. 6.4  | Switching scheme of the P-converter                                                    | 64 |

| Fig. 6.5  | Current flow path in Ćuk P converter switched ON mode                                  | 65 |

| Fig. 6.6  | On-Off cycle of the switches of P-converter                                            | 65 |

| Fig. 6.7  | Current flow path in Ćuk P converter switched OFF mode                                 | 66 |

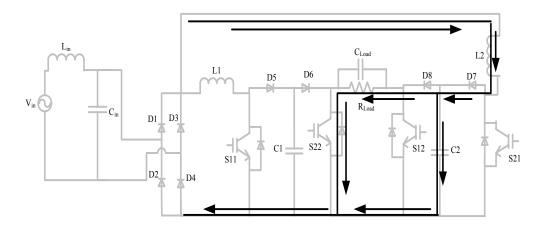

| Fig. 6.8  | The proposed Ćuk topology based N converter                                            | 66 |

| Fig. 6.9  | Current flow path in N converter switched on mode                                      | 67 |

| Fig. 6.10 | Current flow path in N converter switched off mode                                     | 68 |

| Fig. 6.11 | Sliding characteristics of the Ćuk cycloconverter                                      | 70 |

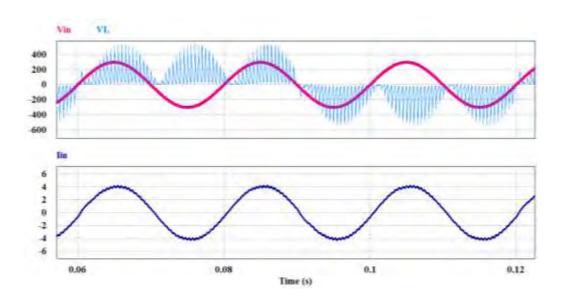

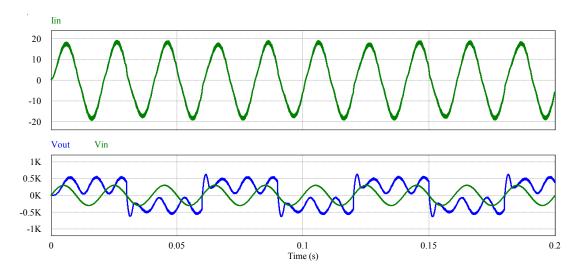

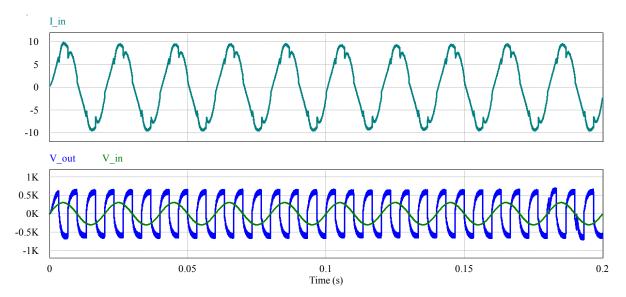

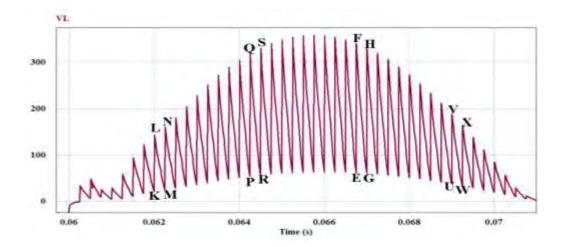

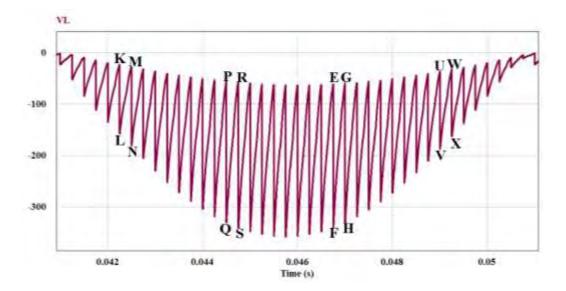

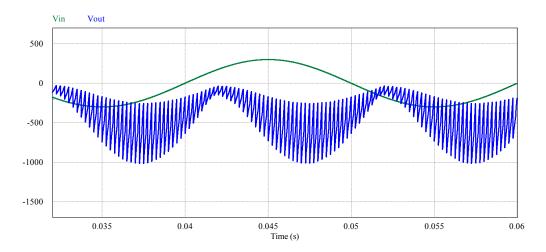

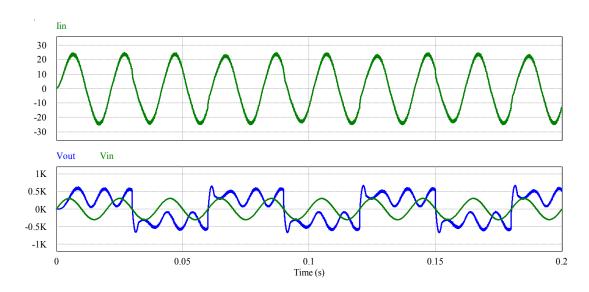

| Fig. 6.12 | Input current, input voltage and output voltage at D=0.5, f=6000 Hz                    | 71 |

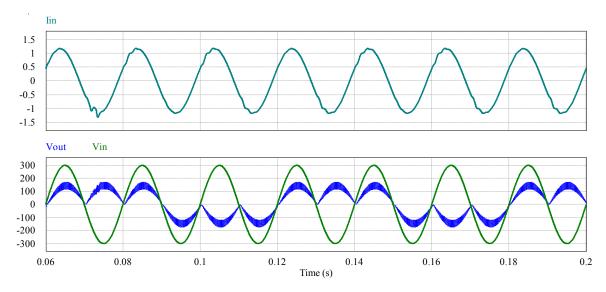

| Fig. 6.13 | Input current, input voltage and output voltage with D=0.3, f=10 kHz                   | 71 |

| Fig. 6.14 | Input current, input voltage and output voltage with D=0.8 , f=3.5 kHz $\dots$         | 72 |

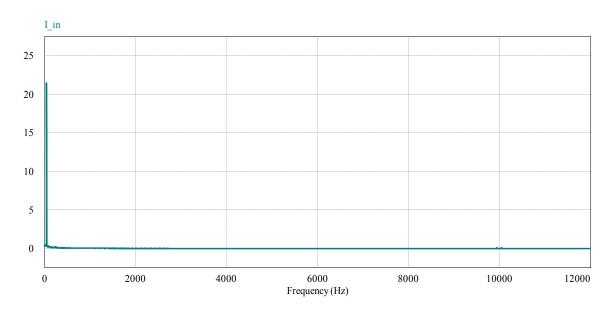

| Fig. 6.15 | Spectrum of the input current for $D=0.3$ and $f=10$ kHz                               | 72 |

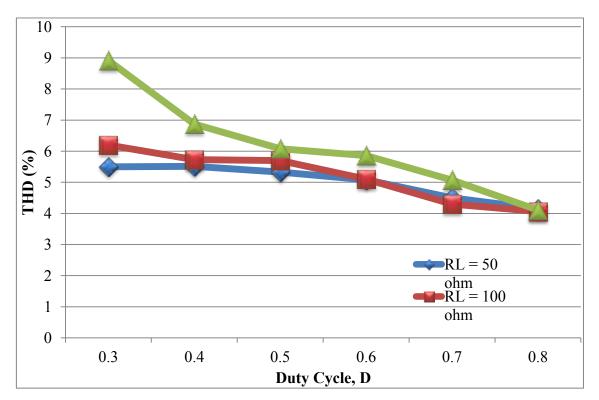

| Fig. 6.16 | 6 Variation of input current THD(%) of different loads at different                    |    |

| sliding p | oints                                                                                  | 73 |

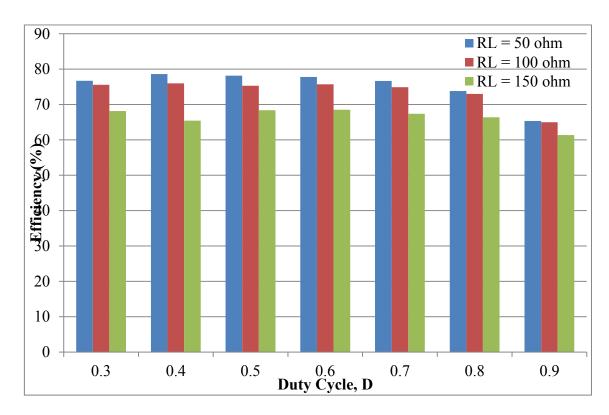

| Fig. 6.17 | Variation of efficiency of different loads at different sliding points                 | 74 |

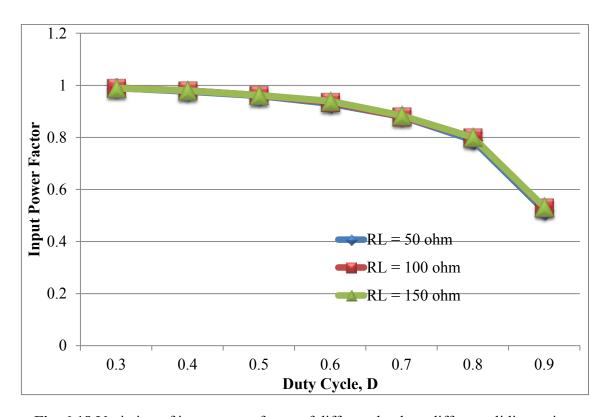

| Fig. 6.18 | 3 Variation of input power factor of different loads at different sliding              |    |

| points    |                                                                                        | 74 |

| Fig. 6.19 | Input current, input voltage and output voltage with D=0.6, f=4 kHz                    | 75 |

| Fig. 6.20 | Input current, input voltage and output voltage with D=0.3 , f= $10 \text{ kHz} \dots$ | 76 |

| Fig. 6.21 | Input current, input and output voltages for R-L load with D = 0.4 and                 |    |

| f=6 kHz   |                                                                                        | 77 |

| Fig. 6.22 | Input current, input and output voltages for R-L load with D = 0.8 and                 |    |

| f=1.5 kH  | z                                                                                      | 77 |

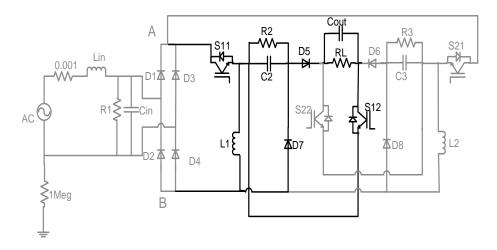

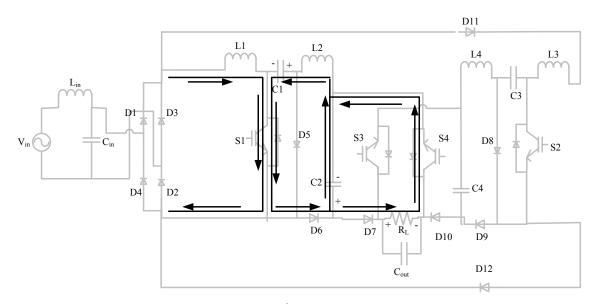

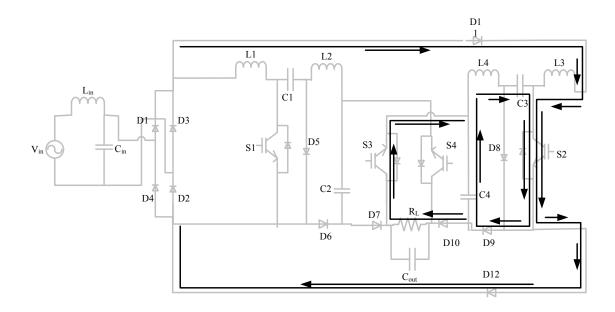

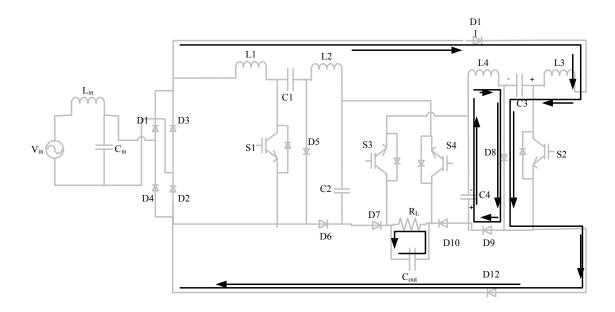

| Fig. 7.1  | Proposed single phase cycloconverter based on Boost topology                           | 78 |

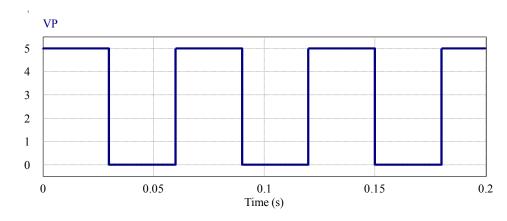

| Fig. 7.2  | Switching characteristics of the P and N converter for Boost Topology                  | 79 |

| Fig. 7.3  | Boost topology based P-converter                                                       | 80 |

| Fig. 7.4  | Switching scheme of the P-converter                                                    | 80 |

| Fig. 7.5  | Current flow direction during switch is ON in P-converter                              | 81 |

| Fig. 7.6  | On-Off cycle of the switches                                                           | 81 |

| Fig. 7.7 Current flow direction when switch is OFF in P-converter                   | 82  |

|-------------------------------------------------------------------------------------|-----|

| Fig. 7.8 Charging and discharging of the output capacitor at P conversion           | 83  |

| Fig. 7.9 Input and Output voltages at P-conversion                                  | 84  |

| Fig. 7.10 Boost topology based N-converter                                          | 84  |

| Fig. 7.11 Current flow direction when switch is ON in N-converter                   | 85  |

| Fig. 7.12 Current flow direction when switch is OFF in N-converter                  | 85  |

| Fig. 7.13 Charging and discharging cycle of the output capacitor at N-conversion    | 86  |

| Fig. 7.14 Input and Output voltages at N-conversion                                 | 87  |

| Fig. 7.15 Sweeping characteristics for Boost cycloconverter                         | 89  |

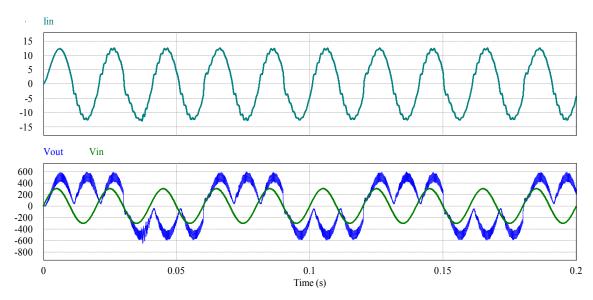

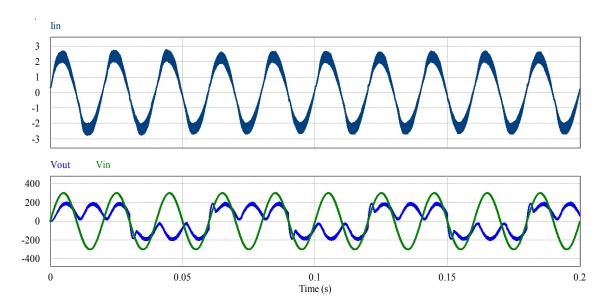

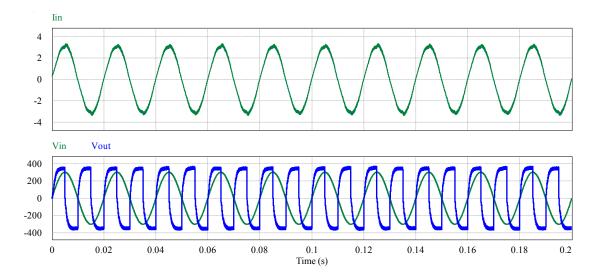

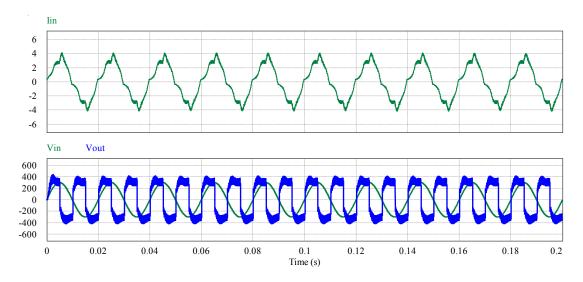

| Fig. 7.16 Input current and Input & Output voltages at D=0.4 and f=10 KHz           | 90  |

| Fig. 7.17 Input current and Input & Output voltages at D=0.6 and f=6 KHz            | 90  |

| Fig. 7.18 Input current and Input & Output voltages at D=0.8 and f=3 KHz            | 91  |

| Fig. 7.19 Spectrum of the input current for $D=0.8$ and $f=3$ kHz                   | 91  |

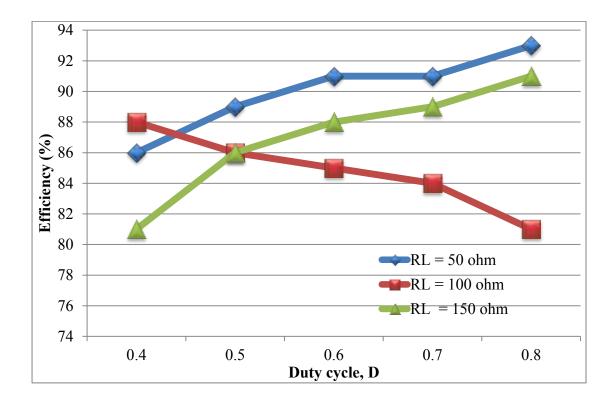

| Fig. 7.20 Variation in THD with different load at different position                | 92  |

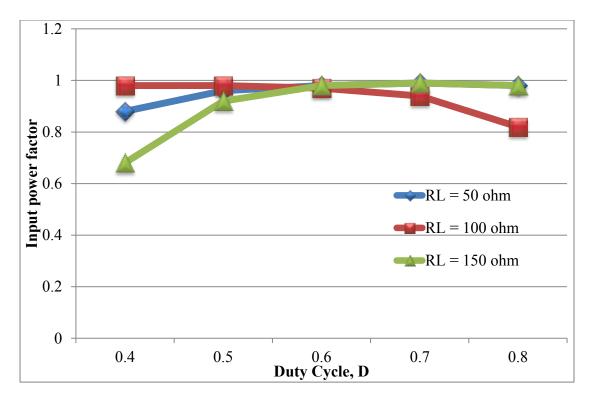

| Fig. 7.21 Variation in input power factor with different load at different position | 93  |

| Fig. 7.22 Variation in efficiency with different load at different position         | 93  |

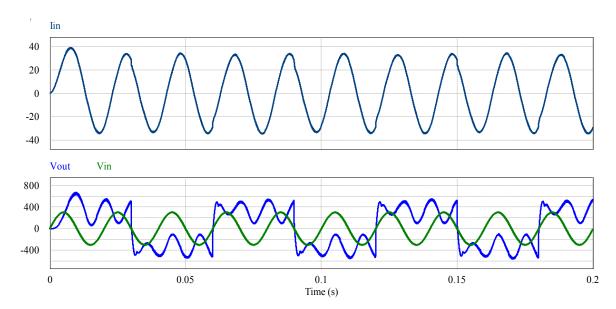

| Fig. 7.23 Input current and Output & Input voltages at D=0.5 and f=9 KHz            | 94  |

| Fig. 7.24 Input current and Output & Input voltages at D=0.8 and f=3 KHz            | 95  |

| Fig. 7.25 Input current, input and output voltages for R-L load with $D = 0.4$ and  |     |

| f=10 kHz                                                                            | 96  |

| Fig. 7.26 Input current, input and output voltages for R-L load with $D = 0.8$ and  |     |

| f=3 kHz                                                                             | 96  |

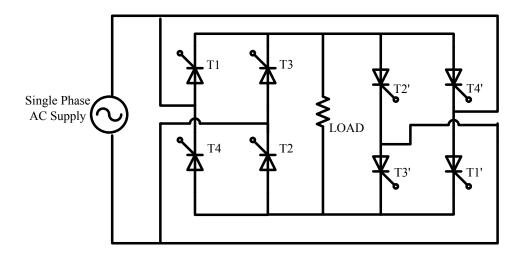

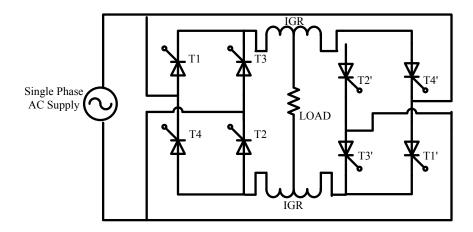

| Fig. 8.1 Single Phase 8 SCR Cycloconverters                                         | 97  |

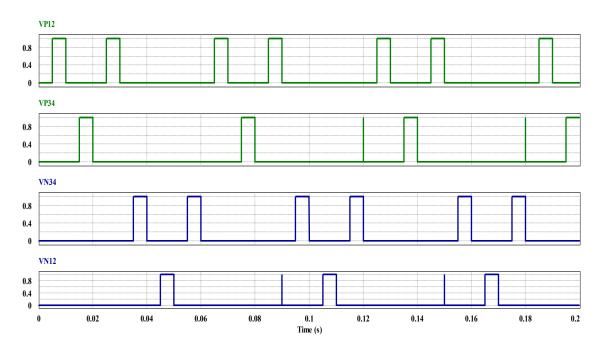

| Fig. 8.2 Gating sequence for a conventional single phase 8 SCR cycloconverter       | 98  |

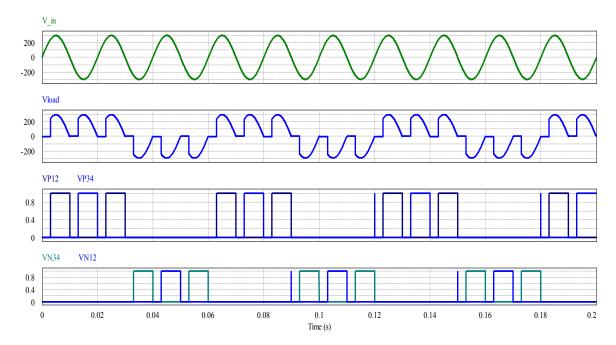

| Fig. 8.3 Waveforms of conventional cycloconverters with resistive load              | 99  |

| Fig. 8.4 Typical input current, input and output voltage of cycloconverters for     |     |

| $\alpha = 36^{0}$                                                                   | 99  |

| Fig. 8.5 Typical input current, input and output voltage of cycloconverters for     |     |

| $\alpha = 54^{0}$                                                                   | 100 |

| Fig. 8.6 Conventional 8 SCR cycloconverters with intergroup reactors (IGRs)         | 101 |

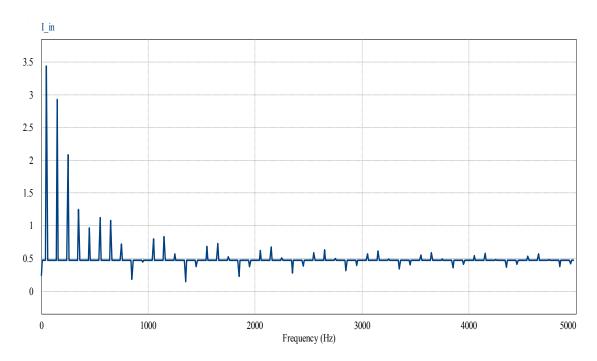

| Fig. 8.7 Fourier representation of 8 SCR cycloconverter input current               | 102 |

| Fig. 8.8 Performance comparison in terms of input current THD                       | 103 |

| Fig. 8.9 Performance comparison in terms of input power factor                      | 105 |

| Fig. 8.10 Performance comparison based on converter efficiency                      | 106 |

#### LIST OF ABBRAVIATIONS

**APF** : Active Power Filter

**DM** : Delta Modulation

**DVM** : Dynamic Voltage Restorer

FC : Frequency Changers

FCC : Forced Commutated Cycloconverter

**GF** : Group Frequency

**HFAC**: High Frequency Alternating Current

ICC : Integral Cycle Controller

**IGBT**: Insulated Gate Bipolar Transistor

**IGR** : Intergroup Reactor

**PF** : Power Factor

**PWM**: Pulse Width Modulation

SCR : Silicon Controlled Rectifier

SFC : Static Frequency Changer

**SMPS** : Switch Mode Power Supply

**SVM** : Space Vector Modulation

**THD** : Total Harmonic Distortion

**TRIAC**: Triode Alternating Current

**UPFC**: Unified Power Quality Conditioner

VSCF : Variable Speed Constant Frequency

## LIST OF SYMBOLS

$V_s, V_{in}$ : Input Voltage

$f_s, f_i$ : Input Frequency

$\alpha$  : Firing Angle

$f_o$  : Output Frequency

$V_d$ : DC Output of Each Rectifier

$V_{out}, V_L, V_{Load}$ : Output voltage

$I_{cc}$  : Circulating Current

$v_r$ : Reference voltage

e : Error Signal

$E_{GF}$ : Efficiency Factor

Duty Cycle of the Control Signal

$I_s$ ,  $I_{in}$ : Input Current

T : Thyristor Switches

*S* : IGBT Switches

$\eta$  : Overall Efficiency

$\phi$  : Phase of Supply Voltage

$I_d$ : Unidirectional Converter Current

$i_r$  : Reference current

H : Hysteresis Band of Error Signal

*E* • Quantized Error Signal

$N_{GF}$ : Number of Group Frequencies

$N_f$ : Total Number of Frequency Components

*Ø* : Power Factor Angle

$PF_{in}$ : Input Power Factor

# CHAPTER 1 INTRODUCTION

## 1.1 Cycloconverters

A cycloconverter is a static frequency changer (SFC) designed to convert constant voltage, constant frequency AC to variable voltage variable frequency AC without any DC link. A cycloconverter is a naturally commutated SFC capable of bidirectional power flow. Because of the omission of DC link, its efficiency is higher than other frequency changers (FCs). The idea of these converters were proposed by Hazeltine in 1926 [1], and the first cycloconverter was built in 1930s using mercury arc valves for converting standard 50Hz AC to 15, 16.5 and 25Hz AC and were used for traction drives [2]. The majority of cycloconverters are naturally commutated and the maximum output frequency is limited to a value that is only a fraction of the source frequency.

Practical and commercial cycloconverters were not available till thyristors were developed in 1960s [3]. Its size is limited by the availability of the rating of thyristors. Cycloconverters can be classified according to its input and output phases as, single phase to single phase, three phase to single phase, and three phase to three phase cycloconverters. Moreover, there are two main structures available for cycloconverters namely, circulating free and circulating current cycloconverter. Major applications of cycloconverters are low-speed ac motor drives usually above 1 MW with frequencies from 0 to 20 Hz. With the advent of thyristors of high power rating and development of microcomputer/microcontroller control strategies, cycloconverters are being used in heavy industries like rolling mills [4-6], electric traction [7], cement tube mill drive industries above 5 MW [8-10], wind tunnel fan drives [11], and ship propellers [12, 13], etc. [14].

The traditional cycloconverter requires a large number of thyristors, at least 36 and usually more for good motor performance, together with a complex control circuit, and it has some performance limitations, for satisfactory operation of the converter the realistic upper limit of the output frequency is about one third of the input frequency [15]. Cycloconverters deliver averaged sinusoidal output waveform which results low pulsating torque in rotary loads. Their input current is distorted and its Fourier series involves harmonics which include, a) higher order harmonics [7], b) sub-harmonics [16], and c) nonstandard

harmonics [2], [17]. Cycloconverter output voltages also involve harmonics and subharmonics. As a result, the control strategy must be chosen in a way to limit these harmonics and minimize their effect on output voltage. Generally, harmonic behavior of cycloconverters is dependent on their pulse number, structure and switching strategy. The higher the pulses number the better the cycloconverter performance [18]. Circulating current cycloconverters have better harmonic performance compared to the circulating current free cycloconverters [19].

The conventional methods of filter [20] cannot be used to reduce harmonics in cycloconverters. Different control strategies widely influence cycloconverter harmonic behavior. The change of a control strategy may result in the change of the input currents, and further, the electric power quality in the supply feeder. Several control strategies have been developed so far including cosine-wave control [2], ripple voltage integral feedback control [3], current feedback method [18], integral and double integral control [21] etc. Various modulation techniques are also employed [22] to improve the quality of load voltage.

In this thesis, switch mode power supply (SMPS) converters are employed to control the output voltages. In each cycle of the input AC signal the voltage is made unidirectional by employing full bridge rectifier. Then, depending on the required frequency at the load, this unidirectional voltage either appears on the same side or on the opposite side of the load. To provide output voltages at opposite polarities two SMPS topology based converters (one p and one n converter) are connected across the load [23]. The proposed topology differs from the available circuits in two ways. Firstly, for single phase AC-AC conversion, SMPS topology based converters is employed instead of conventional eight SCR cycloconverter scheme, thereby, output voltage both higher and lower than the supply voltage is achievable by controlling the duty cycle of the SMPS converter. Secondly, in case of single phase AC supply, the p and n type converters have reduced number of switches. The reduction of switches has four advantages compared to conventional cycloconverter topologies. Firstly, it reduces the switching losses and thereby increases the efficiency. Secondly, the proposed circuits have to deal with less number of isolation schemes. Thirdly, the number of drives is reduced and finally, the proposed topology has higher reliability as the number of switches is reduced. The performance of the proposed topology is evaluated in terms of THD, input power factor, output voltage, output frequency and efficiency along the range of the duty cycle of the control signal.

#### 1.2 Review of Literature

A cycloconverter consists of one or more pairs of back to back connected controlled rectifiers. The delay angles of those rectifiers are modulated so as to provide an AC output voltage at the desired frequency and amplitude to the load. The simplest three-phase cycloconverter, 3-pulse half-wave cycloconverter, consists of 18 thyristors. Higher pulse order systems are large and complicated and tend to be used for large loads such as applications of 1 MW or more.

A conventional cycloconverter is a naturally commutated converter with inherent capability of bidirectional power flow and there is no real limitations on its size which is otherwise restricted in the case of a thyristor inverter due to the size of commutating elements. Here the switching losses are considerably low, the regenerative operation at full power over complete speed range is inherent and it delivers a nearly sinusoidal waveform resulting in minimum torque pulsations and harmonic heating effects. It is capable of operation even with blowing out of individual thyristor fuse (unlike inverter) and the requirements regarding turn-off time, current rise time and dv/dt sensitivity of thyristors are low.

Based on the structure of the rectifiers used in cycloconverters, these converters are classified into half-wave cycloconverters and bridge cycloconverters. The three-phase 3-pulse half-wave cycloconverter is composed of three back to back connected half-wave rectifiers. Each rectifier contains a positive and a negative converter. It is common to use a 6-pulse half-wave cycloconverter to make the output voltage smoother. Six-phase transformers are required to provide voltages for a 6-pulse half-wave cycloconverter. Three-phase half-wave cycloconverters are often used as large motor drives such as rolling mills.

Another scheme is the bridge cycloconverter that consists of two back to back connected bridge rectifiers, called as a P converter and an N converter respectively. Single-phase bridge cycloconverters are extensively used in electric traction applications (e.g., output frequency is 25 Hz in the USA and 16.67 Hz in Europe). It is usual to use 12-pulse bridge cycloconverters to make the output voltage smoother. The 12-pulse bridge cycloconverter is composed of two series 6-pulse bridge cycloconverters. Their input voltages are provided from a 'wye-delta' transformer and a 'wye-wye' transformer, respectively [3]. The single-phase to three-phase cycloconverter induction motor drives can be used for a single-phase traction system. Control circuits for these devices are available in the literature [24].

Depending on the direction and continuity of current two major cycloconverter structures, non-circulating current or blocked mode and circulating current cycloconverters are considered.

Cycloconverters using high-frequency, self-controlled ac switches (e.g. IGBTs) are known as Matrix converters. For a 3 phase converter a matrix of nine switches is utilized where any input phase can be connected to any output phase. The switches are controlled by Pulse Width Modulation (PWM) to fabricate an output fundamental voltage whose amplitude and frequency can be varied to control an AC motor. Matrix converters offer the advantage over thyristor cycloconverters of being able to produce unity power factor (PF) line current. However, compared to PWM voltage-fed converters, the parts count is significantly higher.

The main limitations of the naturally commutated cycloconverters are limited frequency range (less than half of the input frequency) for sub-harmonic free and efficient operation and poor input displacement and power factor, particularly at low output voltages. However, with improved control techniques these problems are being overcome.

Significant developments have taken place in control, modeling, analysis, and application aspects of cycloconverter drives. The control strategies have been developed so far includes cosine-wave control [2], ripple voltage integral feedback control [3], current feedback method [18], integral and double integral control [21] etc. Various modulation techniques are also employed [22] to improve the quality of load voltage.

Cosine-wave modulation was first introduced by Pelly [2]. He mathematically proved that this modulation is the most suitable modulation in case of output voltage power quality and total harmonic distortion (THD) when applied to an idealized cycloconverter. This method produces an output voltage with fundamental amplitude proportional to the reference waveform amplitude. Although the method is severely used universally in motor drives, it has some serious limits when used in practice. The main limits are due to the production of sub-harmonics in output voltage. Sub-harmonics are non-standard harmonic (interharmonic) contents of a signal which have frequencies lower than the fundamental frequency.

Ripple voltage integral feedback was mainly developed to overcome classical cosine-wave sub-harmonics problem. This feedback attenuates sub-harmonics in cycloconverter output voltage. Current feedback is more popular than voltage feedback because of the simplicity of applying vector control. In the current feedback method the current signal is proportional

to the integral of the output voltage minus the back emf which is approximately equal to the wanted reference voltage. The current feedback and ripple voltage integral feedback operate the same way [25].

Many modulation technique based control strategies utilize carrier based PWM. For the cycloconverter, when the polarity of the output voltage is positive, the gate signals for the cycloconverter switches are the same as those for a conventional three phase full bridge inverter. On the other hand, when the polarity is negative, the gate signals for the cycloconverter switches can be obtained by reversing the PWM signals for the three phase inverter. To achieve this, it is essential to know the polarity of the secondary voltages which is difficult to sense as the AC voltage is high frequency with a high amplitudes due to the high switching noise.

To overcome the problem of PWM, digital control strategy based on space vector modulation (SVM) is proposed. In the control strategy, the three phase output line-to-line voltages are sampled and the Clark and Park transformations are applied to get the desired output. SVM has the advantages of low harmonics and a higher modulation index in addition to the feature of complete implementation with a digital signal processor [26, 27].

Delta modulation (DM) is simple and has characteristics advantageous to the operation of cycloconverters. These cycloconverters use high-frequency; self-controlled ac switches (e.g. IGBTs). To optimize the harmonics and improve the output, gate pulses to different IGBTs are modulated using Delta modulation technique. A delta modulator is a closed loop network consisting of a forward comparator and a feedback filter. Delta modulation [28] has become an established alternative to sine PWM for offering a sinusoidal output with low harmonic contents.

Cycloconverter today is a practical proposition in large power applications with synchronous or induction motors like gearless mill drive in cement industry [29-31], centrifugal pump and compressors [32], electric traction [33, 34], rolling mill [4, 35, 36], variable-speed constant frequency (VSCF) systems [37], static Scherbius drives [38, 39], mine winders [40], ship propellers [41] etc.

# 1.3 Objective

SMPS topology has the advantage to provide controllable output voltages. Moreover, employing high frequency switching enables the converter to chop the input current and thereby shifting the lower order harmonic components far apart from the fundamental. In the proposed topologies, the input AC is made unidirectional by employing full bridge rectifier at first. Afterwards, considering load frequency requirement this unidirectional voltage either appears on the same side or on opposite sides of the load. The output voltage amplitudes are controllable by the duty ratio of the high frequency switching pulse. Two SMPS topology based converters (one p and one n converter) are connected across the load to provide output voltages at opposite polarities [23]. The proposed topologies provide from the conventional eight SCR circuits in two ways. Firstly, output voltage both higher and lower than the supply voltage is achievable by controlling the duty cycle of the SMPS converters for single phase AC-AC conversion compared to conventional eight SCR cycloconverter scheme. Secondly, it has been possible to reduce the number of switches of the converters to four compared to eight SCR cycloconverters. The reduction of switches has four major advantages compared to conventional cycloconverter topologies. First, the efficiency has been improved as the switching loss is reduced. Second, the provision of isolation among switching pulses is simpler in the proposed scheme. Third, the number of required driving circuit is reduced and finally, the proposed topology has higher reliability due to less number of switches.

The objectives of this thesis are to investigate new single phase cycloconverter topologies that will provide controllable AC voltages both higher and lower than the input AC voltage at controllable frequencies. The target is to develop new cycloconverter topologies that will provide adjustable voltage and adjustable frequency AC with low input current total harmonic distortion (THD), high input power factor and maintain high efficiency. Design of switch mode cycloconverters with reduced switch topology (less than eight switches as required in 1-phase AC-AC SCR cycloconverter) will be proposed. The performance of the proposed topologies will be investigated and compared with conventional single phase 8-SCR cycloconverter. The outcome of this thesis will be new cycloconverter topologies to provide adjustable AC with low distortion and high input power factor at good efficiencies.

#### 1.4 Outline of the Thesis

This thesis is organized as follows:

**Chapter 1.** Introduces the research work. It comprises an introduction on cycloconverters along with its application and circuit types. Afterwards it provides a review on some of the state-of-the-art control techniques for cycloconverters and their corresponding problems. Then it presents the motivation towards this thesis and a brief overview of the positive features of the proposed switch mode cycloconverters. The layout of this thesis is also presented in this chapter.

**Chapter 2.** Illustrates the types of cycloconverters based on their constructions. It explains the classification of cycloconverters based on criteria like, characteristics of energy conversion and method of current flow. Some newer types of cycloconverters presented in the literature are also briefly discussed.

Chapter 3. Discusses the control topologies reported in the literature. It analyzes the principle of different control schemes and their impact on the performance of the conventional cycloconverters. This chapter also presents the relative advantages and disadvantages of reported control schemes.

**Chapter 4.** Provides basic ideas of power quality parameters used to justify the performance of the proposed switch mode cycloconverters. It explains the impact of these parameters in maintaining desirable operation and presents the equations to determine these parameters.

**Chapter 5.** Presents the proposed Buck-Boost topology based cycloconverter. It describes the circuit, analyzes its operation and presents its performance under different load conditions.

**Chapter 6.** Demonstrates the proposed cycloconverter based on Cuk topology. First the description of the proposed circuit is presented along with the analysis of its operation. Then it provides details on the performance of the proposed cycloconverter under different load conditions.

**Chapter 7.** Presents the proposed switch mode cycloconverter based on Boost topology. It describes the circuit configuration, analyzes its operation and presents its performance under different load conditions.

**Chapter 8.** Compares the performance of the proposed switch mode cycloconverters with conventional 8 SCR cycloconverter. First it analyzes the behavior of the conventional cycloconverter under different conditions of control and load. Then it presents the comparison of its performance with the proposed cycloconverters and shows the advantages of the proposed schemes compared to the conventional one.

**Chapter 9.** Concludes the thesis with a summary on the research. It also discusses the scopes for future development of the proposed switch mode cycloconverters.

# CHAPTER 2 CYCLOCONVERTER TYPES

Literature has different types of cycloconverters based on their circuit constructions. These classifications can be performed based on characteristics like, criteria of signal conversion, method of current flow etc. There are some newer types of cycloconverter circuits like, matrix converter or single phase to three phase cycloconverters.

Different constructions of cycloconverter circuits have classified them in various types. Separate criterions can be set to discrete cycloconverters. Firstly, there is criterion of input to output signal conversion. The energy conversion types may be single-phase to single-phase, three-phase to single-phase, or three-phase to three-phase. Next, depending on the path or method of current flow cycloconverters can be classified in blocked mode and circulating current mode cycloconverters. Finally, some new cycloconverter circuits proposed in literature will be discussed.

#### 2.1 Classification Based on Criterion of Energy Conversion

Cycloconverters are AC-AC variable frequency converters. Based on input and load connection architectures they can be classified in the following schemes.

# 2.1.1 Single-phase to Single-phase (1φ-1φ) Cycloconverter

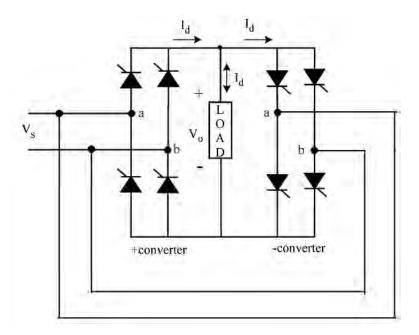

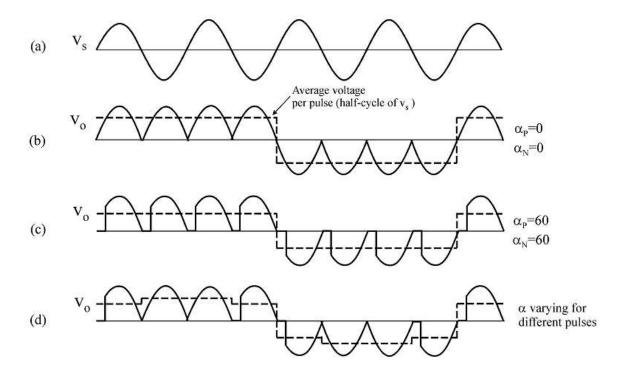

The circuit of a  $1\phi$ - $1\phi$  cycloconverter is shown in Fig. 2.1. This converter consists of back-to-back connection of two full-wave rectifier circuits. Fig 2.2 shows the operating waveforms for this converter with a resistive load. The input voltage,  $V_s$  is an AC voltage at a frequency,  $f_i$  as shown in Fig. 2.2. Assume that all the thyristors are fired at  $\alpha$ = $0^{\circ}$  firing angle, i.e. thyristors act like diodes.

Consider the operation of the cycloconverter to get one-fourth of the input frequency at the output. For the first two cycles of  $V_s$ , the positive converter operates supplying current to the load. It rectifies the input voltage; therefore, the load sees four positive half cycles as seen in Fig. 2.2(b). In the next two cycles, the negative converter operates supplying current to the load in the reverse direction. The current waveforms for the resistive load will have the same waveform as the voltage but only scaled by the resistance. When one of the converters operates the other one is disabled, so that there is no current circulating between the two rectifiers.

Fig. 2.1 Single-phase to single-phase cycloconverter

**Fig. 2.2** Single-phase to single-phase cycloconverter waveforms. a) Input voltage, b) Output voltage for zero firing angle, c) Output voltage with firing angle  $\pi/3$  rad, and d) Output voltage with varying firing angle

The frequency of the output voltage,  $V_o$  in Fig. 2.2(b) is four times less than that of  $V_s$ , i.e.  $f_o/f_i$ =1/4. Thus, this is a step-down in frequency cycloconverter. On the other hand, cycloconverters those have  $f_o/f_i > 1$  frequency relation are called step-up frequency cycloconverters. Note that step-down cycloconverters are more widely used than the step-up ones.

The frequency of  $V_o$  can be changed by varying the number of cycles the positive and the negative converters work. It can only change as integer multiples of  $f_i$  in  $1\varphi$ - $1\varphi$  cycloconverters. With the above operation, the  $1\varphi$ - $1\varphi$  cycloconverter can only supply a certain voltage at a certain firing angle  $\alpha$ . The DC output of each rectifier is:

$$V_d = \frac{2\sqrt{2}}{\pi} V \cos \alpha, \qquad 2.1$$

Where, V is the input root mean square (RMS) voltage. The DC value per half cycle is shown as dotted in Fig. 2.2(d). The peak of the fundamental output voltage is:

$$V_{o_{peak}} = \frac{4}{\pi} \frac{2\sqrt{2}}{\pi} \cos \alpha, \qquad 2.2$$

Equation 2.2 implies that the fundamental output voltage depends on  $\alpha$ . By varying  $\alpha$ , the fundamental output voltage can be controlled. Constant  $\alpha$  operation gives a crude output waveform with rich harmonic content. The dotted lines in Fig. 2.2(b) and (c) show a square wave. If the square wave can be modified to look more like a sine wave, the harmonics would be reduced. For this reason  $\alpha$  is modulated as shown in Fig. 2.2(d) where, the six-stepped dotted line is more like a sine-wave with fewer harmonics. The more pulses there are with different  $\alpha$ 's, the less are the harmonics.

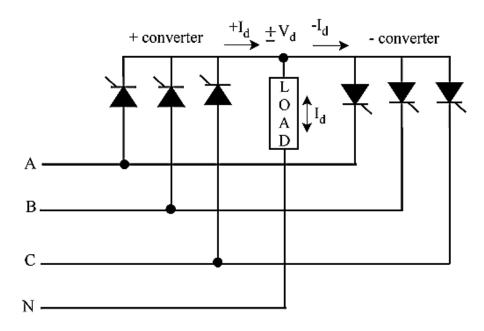

## 2.1.2 Three-Phase to Single-Phase (3φ-1φ) Cycloconverter

There are two types of three-phase to single-phase  $(3\phi-1\phi)$  cycloconverters:  $3\phi-1\phi$  half-wave cycloconverter as shown in Fig. 2.3 and  $3\phi-1\phi$  full-wave bridge cycloconverter as in Fig. 2.4. Like the  $1\phi-1\phi$  case, the  $3\phi-1\phi$  cycloconverter applies rectified voltage to the load. Both positive and negative converters can generate voltages at either polarity, but the positive converter can only supply positive current and the negative converter can only supply negative current. Thus, the cycloconverter can operate in four quadrants: (+v, +i)

and (-v, -i) rectification modes and (+v, -i), and (-v, +i) inversion modes. Sinusoidal output voltage is possible to obtain by sinusoidally modulating the firing angle  $\alpha$ .

The polarity of the current determines if the positive or negative converter should be supplying power to the load. When the polarity of the current changes, the converter previously supplying the current is disabled and the other one is enabled. The load always requires the fundamental voltage to be continuous. Therefore, during the current polarity reversal, the average voltage supplied by both of the converters should be equal. Otherwise, switching from one converter to the other one would cause an undesirable voltage jump. To prevent this problem, the converters are forced to produce the same average voltage at all times. Thus, the following condition for the firing angles should be met.

$$\alpha_P + \alpha_N = \pi \tag{2.3}$$

**Fig. 2.3** 3φ-1φ half-wave cycloconverter

Fig. 2.4 3φ-1φ full-wave bridge cycloconverter

The fundamental output voltage can be given as:

$$V_{o1} = \sqrt{2}V_o \sin(2\pi f_o t) \tag{2.4}$$

Where  $V_o$  is the RMS value of the fundamental voltage and  $f_o$  is the fundamental output frequency. The operation of the  $3\phi$ - $1\phi$  full-wave bridge cycloconverter is similar to the above  $3\phi$ - $1\phi$  half-wave cycloconverter with the pulse number being doubled.

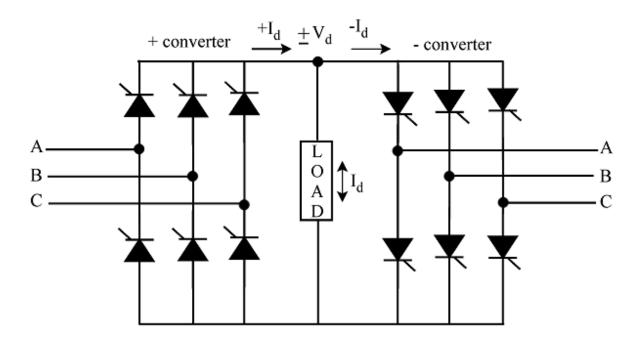

# 2.1.3 Three-Phase to Three-Phase (3ф-3ф) Cycloconverter

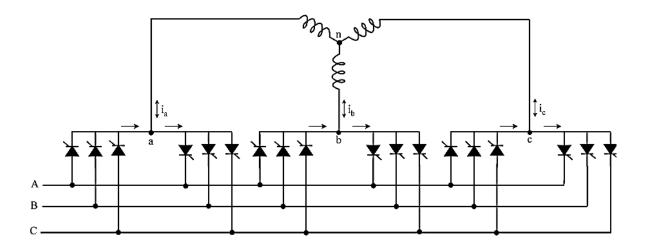

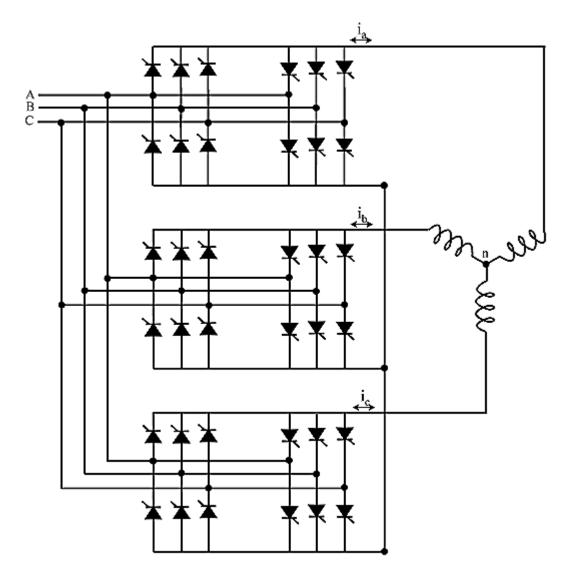

If the outputs of three  $3\varphi$ -1 $\varphi$  converters of the same kind are connected in wye or delta and if the output voltages are  $2\pi/3$  radians or  $120^\circ$  phase shifted from each other, the resulting converter is a three-phase to three-phase ( $3\varphi$ -3 $\varphi$ ) cycloconverter. The resulting half-wave cycloconverter is shown in Fig. 2.5 and full-wave cycloconverter is shown in Fig. 2.6 with wye connected loads. If the three converters connected are half-wave converters, then the new converter is called a  $3\varphi$ -3 $\varphi$  half-wave cycloconverter. If instead, bridge converters are used, then the result is a  $3\varphi$ -3 $\varphi$  bridge cycloconverter.

**Fig. 2.5** 3φ-3φ half-wave cycloconverter

$3\varphi$ - $3\varphi$  half-wave cycloconverter is also called a 3-pulse cycloconverter or an 18-thyristor cycloconverter. On the other hand, the  $3\varphi$ - $3\varphi$  bridge cycloconverter is also called a 6-pulse cycloconverter or a 36-thyristor cycloconverter. The operation of each phase is similar to  $3\varphi$ - $1\varphi$  cycloconverters except their load connections.

Fig. 2.6 3φ-3φ full-wave bridge cycloconverter

#### 2.2 Classification Based on Method of Current Flow

Depending on the direction and continuity of current two major cycloconverter structures, non-circulating current or blocked mode and circulating current cycloconverters are considered.

During the positive load current, the positive converter supplies the required voltage and the negative converter is disabled. On the other hand, when the load current is negative, then the negative converter supplies the required voltage and the positive converter is blocked. This operation is called the blocked mode operation, and the cycloconverters using this approach are called blocking mode cycloconverters. However, if in any case, both of the converters are enabled, then the supply is short-circuited.

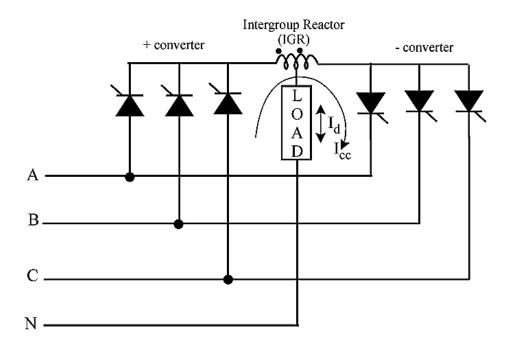

To avoid this short circuit, an intergroup reactor (IGR) can be connected between the converters as shown in Fig. 2.7. Instead of blocking the converters during current reversal, if they are both enabled, then a circulating current is produced. This current is called the circulating current. It is unidirectional because the thyristors allow the current to flow in only one direction. Some cycloconverters allow this circulating current at all times. These are called circulating current cycloconverters.

#### 2.2.1 Blocking Mode Cycloconverters

The circuit for blocking mode operation of 3φ-3φ half-wave cycloconverter is shown in Fig. 2.5. The operation of these cycloconverters has been explained in section 2.1.1. They do not let circulating current flow, and therefore they do not need a bulky IGR. When the current goes to zero both positive and negative converters are blocked. The converters stay off for a short delay time to assure that the load current ceases. Then, depending on the polarity, one of the converters is enabled. With each zero crossing of the current, the converter, which was disabled before the zero crossing, is enabled. A toggle flip-flop, which toggles when the current goes to zero, can be used for this purpose.

The blocking mode operation has some advantages and disadvantages over the circulating mode operation. During the delay time, the current stays at zero distorting the voltage and current waveforms. This distortion means complex harmonics patterns compared to the circulating mode cycloconverters. In addition to this, the current reversal problem brings more control complexity. However, no bulky IGRs are used, so the size and cost is less than that of the circulating current case. Another advantage is that only one converter is in conduction at all times rather than two. This means less losses and higher efficiency.

#### 2.2.2 Circulating Current Cycloconverters

The circuit diagram of Circulating current mode  $(3\phi-3\phi)$  half-wave) cycloconverter and IGR is shown in Fig. 2.7. In this case, both of the converters operate at all times producing the same fundamental output voltage. The firing angles of the converters satisfy the firing angle condition of Eq. (3.3), thus when one converter is in rectification mode the other one is in inversion mode and vice versa. If both of the converters are producing pure sine waves, then there would not be any circulating current because the instantaneous potential difference between the outputs of the converters would be zero. In reality, an IGR is connected between the outputs of two phase controlled converters (in either rectification or inversion mode). The voltage across the IGR is the difference of the instantaneous output voltages produced by the two converters. It becomes zero when both of the converters

produce the same instantaneous voltage. The center tap voltage of IGR is the voltage applied to the load and it is the mean of the voltages applied to the ends of IGR, thus the load voltage ripple is reduced.

Fig. 2.7 Circulating current mode (3φ-3φ half-wave) cycloconverter and IGR

The circulating current cycloconverter applies a smoother load voltage with fewer harmonics compared to the blocking mode case. Moreover, the control is simple because there is no current reversal problem. However, the bulky IGR is a big disadvantage for this converter. In addition to this, the number of devices conducting at any time is twice that of the blocking mode converter.

The blocking and circulating current cycloconverters can be combined to give a hybrid system, which has the advantages of both. The resulting cycloconverter looks like a circulating mode cycloconverter circuit, but depending on the polarity of the output current only one converter is enabled and the other one is disabled as with the blocking mode cycloconverters. When the load current decreases below a threshold, both of the converters are enabled. Thus, the current has a smooth reversal. When the current increases above a threshold in the other direction, the outgoing converter is disabled. This hybrid cycloconverter operates in the blocking mode most of the time so a smaller IGR can be used. The efficiency is slightly higher than that of the circulating current cycloconverter but much less than the blocking mode cycloconverter. Moreover, the distortion caused by the blocking mode operation disappears due to the circulating current operation around zero current. Moreover, the control of the converter is still less complex than that of the blocking mode cycloconverter.

## 2.3 Newer Types of Cycloconverters

#### 2.3.1 Matrix Converter

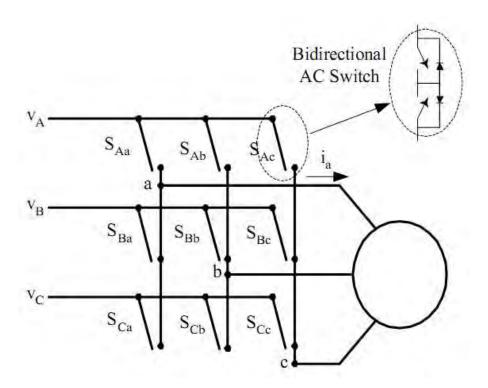

The matrix converter is a fairly new converter topology, which was first proposed in the beginning of the 1980s. A matrix converter consists of a matrix of 9 switches connecting the three input phases to the three output phases directly as shown in Fig. 2.8. Any input phase can be connected to any output phase at any time depending on the control. However, no two switches from the same phase should be on at the same time, otherwise this will cause a short circuit of the input phases. These converters are usually controlled by PWM to produce three-phase variable voltages at variable frequency.

Fig. 2.8 Matrix Converter

This direct frequency changer is not commonly used because of the high device count, i.e. 18 switches compared to 12 of a DC link rectifier-inverter system. However, the devices used are smaller because of their shorter ON time compared to the conventional cycloconverters.

## 2.3.2 Single-Phase to Three-Phase (1φ - 3φ) Cycloconverters

Recently, with the decrease in the size and the price of power electronics switches, single-phase to three-phase  $(1\varphi - 3\varphi)$  cycloconverters started drawing more research interest. Usually, an H-bridge inverter produces a high frequency single-phase voltage waveform, which is fed to the cycloconverter either through a high frequency transformer or else. If a transformer is used, it isolates the inverter from the cycloconverter. In addition to this, additional taps from the transformer can be used to power other converters producing a high frequency ac link. The single-phase high frequency ac (HFAC) voltage can be either sinusoidal or trapezoidal. There might be zero voltage intervals for control purposes or zero voltage commutation. Fig. 2.9 shows the circuit diagram of a typical HFAC link converter. These converters are not commercially available yet. They are in the research stage. Different types of single-phase to three-phase  $(1\varphi - 3\varphi)$  cycloconverters are available in literature. Two special types of cycloconverters will be addressed here.

Fig. 2.9 High frequency AC link converter

## A) Integral Pulse Modulated (1φ - 3φ) Cycloconverters [42]:

The input to these cycloconverters is single-phase high frequency sinusoidal or square waveforms with or without zero voltage gaps. Every half-cycle of the input signal, the control for each phase decides if it needs a positive pulse or a negative pulse using integral pulse modulation. For integral pulse modulation, the command signal and the output phase voltage are integrated and the latter result is subtracted from the former. For a positive difference, a negative pulse is required, and vice versa for the negative difference. For the

positive input half-cycle, if a positive pulse is required, the upper switch is turned on; otherwise, the lower switch is turned on.

The three-phase output voltage consists of positive and negative half-cycle pulses of the input voltage. This converter can only work at output frequencies which are multiples of the input frequency.

## B) Phase-Controlled (1φ - 3φ) Cycloconverter [43]:

This cycloconverter converts the single-phase high frequency sinusoidal or square wave voltage into three-phase voltages using the phase control principles. The voltage command is compared to a saw-tooth waveform to find the firing instant of the switches. Depending on the polarity of the current and the input voltage, the next switch to be turned on is determined. Compared to the previous one, this converter has more complex control but it can work at any frequency.

Cycloconverters are widely used in industry for AC-AC conversion. With recent device advances, newer forms of cycloconverters are being developed. These newer forms are drawing more research interest now a day. In this section, the most commonly known cycloconverter schemes are briefly described, and their operation principles are discussed.

# CHAPTER 3 CYCLOCONVERTER CONTROL SCHEMES

A cycloconverter control strategy refers to a set of firing signals that triggers cycloconverter thyristors to produce a specific output voltage. Different control strategies lead to different characteristics in input current and output voltage of cycloconverter. The control schemes deal with the regulation of cycloconverter outputs, input current shaping, dynamic performance, and efficiency etc. Various control schemes are presented in literature so far, some selective ones will be presented in this chapter. Among various phase control methods developed in the past, cosine wave crossing control has found widespread use. To overcome the limitations of cosine wave control, some correction methods like, regular sampling, ripple voltage integral feedback control and current feedback methods are employed. Integral phase control methods have also gained attentions because of their relative advantages over cosine wave control. Some control methods like, Space Vector Modulation (SVM), Delta Modulation (DM) and Group Frequency (GF) methods used for cycloconverter control are briefly described in this chapter.

### 3.1 Cosine Wave Control:

In the cosine wave crossing control method, the output reference wave is compared with cosine waves and when the two waveforms cross, the thyristors are triggered. The procedure is shown in Fig. 3.2 for a three phase three pulse cycloconverter as in Fig. 3.1. An example of an idealized output waveform for a 45° load phase angle with cosine wave control where the output load current is sinusoidal is shown in Fig. 3.3.

Fig. 3.1 Three phase, 3-pulse cycloconverter for cosine wave control

Fig. 3.2 Cosine wave crossing phase control method for 3 pulse cycloconverter

**Fig. 3.3** Idealized waveforms with cosine wave control for a 3-pulse cycloconverter with 45° lagging load current

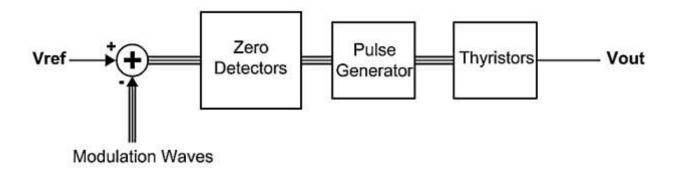

The cosine wave crossing control method was originally developed for DC output thyristor converters. For this application, the method produces an average output voltage which is directly proportional to the reference voltage for the idealized case of continuous output current. Cosine wave control is an open-loop control method which produces firing pulses based on wanted output voltage and modulation waves. Bock diagram [2] of this control method is depicted in Fig. 3.4. Pelly [17] showed that when applied to the idealized (continuous output current) cycloconverters, this method produces an output voltage whose fundamental component amplitude is proportional to the reference waveform amplitude and whose frequency spectrum contains no multiples of the fundamental components.

Fig. 3.4 Block diagram of cosine-wave modulation

Even though the cosine wave crossing control method is almost universally used for cycloconverter motor drives, the method has limitations. The main limitation is that the method generates intermodulation products on the output, the frequency of which may be less than the wanted output frequency. When this occurs, the intermodulation product is called a sub-harmonic.

For example, a 3-pulse cycloconverter which has an input frequency,  $f_i$ , of 50 Hz and a fundamental output frequency,  $f_o$  of 24 Hz can generate intermodulation products of frequencies  $(3nf_i + mf_o)$ , where, n and m are integers. The intermodulation product,  $(3f_i - 6f_o)$ , has a frequency of 6 Hz which is less than  $f_o$  and is thus a sub-harmonic. For cosine wave crossing control, assuming maximum output modulation and a load phase angle of 30° lagging, its amplitude is 9.5% of the fundamental [17, 21]. For an induction motor operating at a synchronous speed of 24 Hz, its impedance at 6 Hz would be very low and the currents and resulting torque pulsations produced from this sub-harmonic would be high.

Another major problem with cosine wave crossing control is the distortion produced from discontinuous output current. When the motor is operating under light load, the high ripple current may bring the output current in phase, turning off the conducting thyristor before the next thyristor turns on. The output voltage will then revert to the motor open circuit voltage rather than the input phase voltage, causing voltage distortion on the output. Cosine wave crossing control is not viable in this situation.

# 3.2 Correction Methods for Cosine Wave Crossing Control

There have been various techniques devised over the years to correct the deficiencies of the cosine wave crossing control method. Most commercial drives use one of these techniques. The important ones are described below.

### 3.2.1 Regular Sampling

The regular sampling method was developed by Bird and Ford [44] for circulating current cycloconverters. The method is to modify the reference waveform by doing a sample and hold at the start of each cosine wave. This was found to reduce the amplitudes of sub-harmonics on the output. Improved results could be obtained by pre-distorting the reference wave. This work also showed that this technique provides minimal improvement for circulating current free cycloconverters.

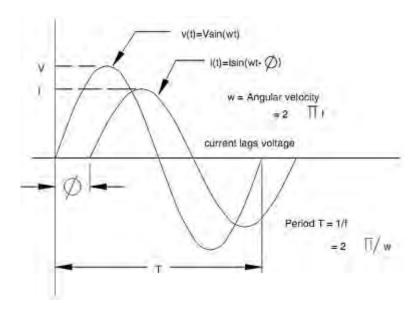

# 3.2.2 Ripple Voltage Integral Feedback

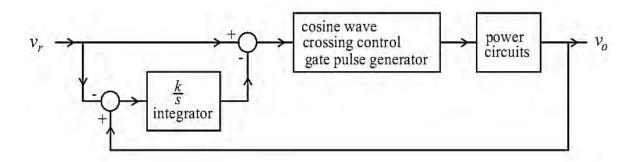

Ripple voltage integral feedback is a technique introduced by Gyugyi and Pelly [2]. It involves feeding back the integral of the difference between the output voltage and the reference voltage. A block diagram of this scheme is shown in Fig. 3.5. With this system, any low frequency sub-harmonics are attenuated by the feedback, the gain of which is inversely proportional to frequency. The feedback would also assist in reducing voltage distortion due to discontinuous current.

Fig. 3.5 Simplified block diagram of ripple voltage integral feedback control scheme

The limitation of this technique is that the maximum stable loop gain is rather low and is reduced as the maximum output frequency is increased. Table 3.1 shows the approximate maximum stable unity gain frequency of the feedback loop for a 50 Hz input frequency, 3-pulse cycloconverter for various output frequencies. This table is constructed from data presented by Gyugyi and Pelly [2].

| Output Frequency | Unity Gain     |  |  |  |  |

|------------------|----------------|--|--|--|--|

| (Hz)             | Frequency (Hz) |  |  |  |  |

| 5.56             | 9.5            |  |  |  |  |

| 8.33             | 7              |  |  |  |  |

| 16.67            | 5.5            |  |  |  |  |

| 25               | 4.5            |  |  |  |  |

| 33 33            | 3.5            |  |  |  |  |

**TABLE 3. 1** Approximate maximum stable unit gain frequency of the feedback loop for a 50 Hz input frequency, 3-pulse cycloconverter

It is evident from Table 3.1 that, for a 3-pulse cycloconverter operating up to 25 Hz, the feedback gain is quite low and of limited benefit. Assuming that the loop gain drops off by 20 dB per decade, then at 6 Hz, the maximum gain is only 0.75, producing only a marginal reduction in a sub-harmonic at this frequency. A way of increasing the maximum stable unity gain frequency is to increase the pulse number. For a 6-pulse cycloconverter, the maximum unity gain frequency can be multiplied by 4, and for 12-pulse, by 16. Gyugyi and Pelly [2] demonstrated good results using this system for a 6-pulse cycloconverter operating up to 2/3 of the input frequency and driving a 30 HP induction motor.

### 3.2.3 Current Feedback Method

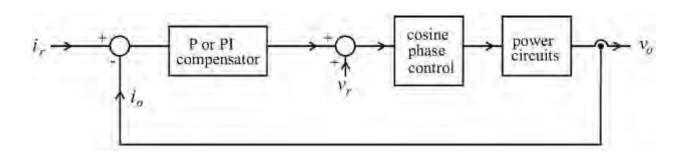

The most common commercial method of improving the output waveform is to consider the feedback of the output current. This method evolved from its use in thyristor controlled DC motor drives. A block diagram of current feedback control is shown in Fig. 3.6.

Fig. 3.6 Simplified block diagram of current feedback control scheme

In terms of feedback stability and gain, the current feedback system is virtually identical to ripple voltage integral feedback. The approximate equivalent circuit of the motor is a back e.m.f. in series with a leakage inductance, so the current signal is proportional to the integral of the output voltage minus the back e.m.f. which is approximately equal to the wanted reference voltage. This means that the maximum feedback gain without instability is similar to that which can be obtained from ripple voltage integral feedback. This limits the usefulness of current feedback to 6-pulse and higher cycloconverters. Even with 6-pulse cycloconverters, an estimate of the wanted output voltage must be added to the error voltage as shown in Fig. 3.6 to reduce the error in the output current.

Although there is little difference in performance between ripple voltage integral feedback and current feedback, current feedback is usually chosen in practice because it allows easier implementation of vector control.

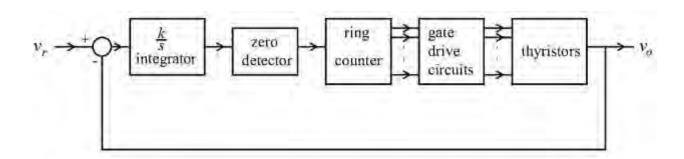

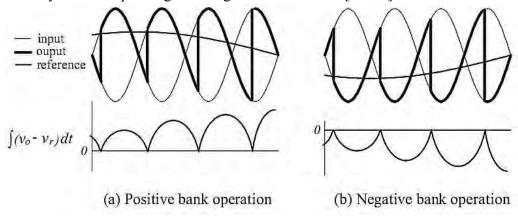

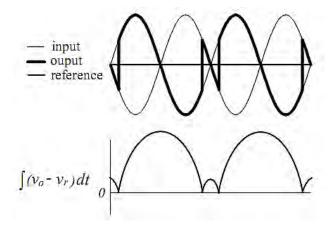

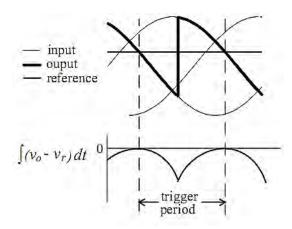

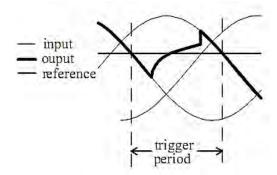

# 3.3 Integral Control