# Analysis of Double-Gate (DG) MOSFETs through a Non Charge-Sheet Model.

A thesis submitted to

the department of Electrical and Electronic Engineering

of

Bangladesh University of Engineering and Technology in partial fulfillment of the requirements for

the degree of

MASTER OF SCIENCE IN ELECTRICAL AND ELECTRONIC ENGINEERING

by Shaikh Asif Mahmood

DEPARTMENT OF ELECTRICAL AND ELECTRONIC ENGINEERING BANGLADESH UNIVERSITY OF ENGINEERING AND TECHNOLOGY

The thesis entitled "Analysis of Double-Gate (DG) MOSFETs through a Non Charge-Sheet Model" submitted by Shaikh Asif Mahmood Roll No.: 040406239P Session: April, 2004 has been accepted as satisfactory in partial fulfillment of the requirements for the degree of MASTER OF SCIENCE IN ELECTRICAL AND ELECTRONIC ENGINEERING on April 18, 2006.

#### **BOARD OF EXAMINERS**

-4-06

Chairman

(Dr. Md. Quamrul Huda) Professor Department of Electrical and Electronic Engineering, BUET, Dhaka-1000, Bangladesh

1.

4.

2. \*

(Dr. S. Shahnawaz Ahmed) Professor and Head Department of Electrical and Electronic Engineering, BUET, Dhaka-1000, Bangladesh

3.

(Dr. M. M. Shahidul Hassan) Professor Department of Electrical and Electronic Engineering, BUET, Dhaka-1000, Bangladesh

### A. Hanalo.

(Dr. A. K. M. Akther Hossain) Associate Professor Department of Physics, BUET, Dhaka-1000, Bangladesh

Member

Member

(Ex-officio)

## Declaration

It is hereby declared that this thesis or any part of it has not been submitted elsewhere for the award of any degree or diploma.

Signature of the candidate

÷,

(Shaikh Asif Mahmood)

## Acknowledgements

I wish to express my sincere gratitude to my supervisor Dr. Md. Quamrul Huda, Professor, Department of Electrical and Electronic Engineering (EEE), Bangladesh University of Engineering and Technology (BUET), Bangladesh, for his invaluable guidance and advice during every stage of this endeavor. I am greatly indebted to him for his continuing encouragement and support without which, it would not have been possible for me to complete this undertaking successfully. His insightful comments and suggestions have continually helped me to improve my understanding.

I am grateful to Head, Dept. of EEE, Bangladesh University of Engineering and Technology (BUET) and Dr. M. M. Shahidul Hassan, Professor, Dept. of EEE and lab in charge (RNS lab), who provided with all the facilities of simulation laboratory of the department.

I am grateful to my parents and other members of my family for their encouragement, patience and love.

\_ 1

# Dedication

To My Parents

## Contents

.

| Acknowledgements              |                                              | iii |

|-------------------------------|----------------------------------------------|-----|

| Dedication<br>List of Figures |                                              | iv  |

|                               |                                              | vii |

| A                             | bstract                                      | x   |

| 1                             | Introduction                                 | 1   |

|                               | 1.1 Transistor Scaling                       | 1   |

|                               | 1.2 Alternative Design Approach              | 2   |

|                               | 1.3 Modeling of DG MOSFET                    | 2   |

|                               | 1.4 Thesis Objective                         | 3   |

|                               | 1.5 Thesis Outline                           | 4   |

| 2                             | Analysis of SG and DG MOSFET                 | 5   |

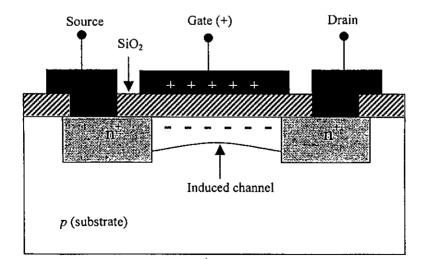

|                               | 2.1 Single-gate (conventional) MOSFET        | 5   |

|                               | 2.2 Short-Channel Effects and DG SOI MOSFETs | 6   |

|                               | 2.3 Double-gate metal-oxide-semiconductor    | 8   |

|                               | 2.4 Concept of volume inversion              | 8   |

|                               | 2.5 Literature review                        | . 9 |

| 3                             | Modeling of DG FET                           | 15  |

|                               | 3.1 Derivation of <i>I-V</i> model           | 15  |

|                               | 3.2 Determination of Potential profile       | 18  |

|                               | 3.3 Determination of pinchoff region         | 19  |

|                               | 3.4 Derivation of threshold voltage model    | 20  |

<u>ج</u> م

| 4  | Results and discussion                                                | 24  |

|----|-----------------------------------------------------------------------|-----|

|    | 4.1 Gate to gate potential variation                                  | 24  |

|    | 4.2 Effect of silicon thickness on volume inversion                   | 26  |

|    | 4.3 I-V characteristics with variation of silicon thickness           | 27  |

|    | 4.4 Effect of silicon thickness on the sheet density of mobile charge | 29  |

|    | 4.5 Electron density profile                                          | 31  |

|    | 4.6 Effect of drain voltage on volume inversion                       | 32  |

|    | 4.7 Potential variation along the channel                             | 35  |

|    | 4.8 Electric field variation                                          | 38  |

|    | 4.9 Effect of oxide thickness                                         | 42  |

|    | 4.10Short channel effect                                              | 44  |

|    | 4.11 Comparison of three types of DG MOSFET structure                 | 47  |

| 5  | Conclusion                                                            | 50  |

|    | 5.1 Summary                                                           | 50  |

|    | 5.2 Possible future work                                              | 51  |

| Al | PPENDIX I                                                             | 52  |

| Al | PPENDIX II                                                            | 54  |

| Bi | bliography                                                            | 59~ |

•

## List of Figures

| Figure 2.1 Basic structure of a single-gate (SG) MOSFET.                                                    | 5     |  |  |  |

|-------------------------------------------------------------------------------------------------------------|-------|--|--|--|

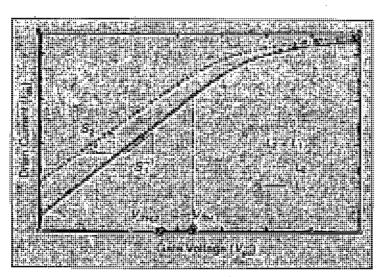

| Figure 2.2 Impact of short-channel effects on drain current. As the channel length $(L)$ is                 |       |  |  |  |

| reduced, subthreshold swing increases ( $S_2 > S_1$ ) and threshold voltage decreases ( $V_{TH,2} <$        |       |  |  |  |

| $V_{TH,I}$ ).                                                                                               | 6     |  |  |  |

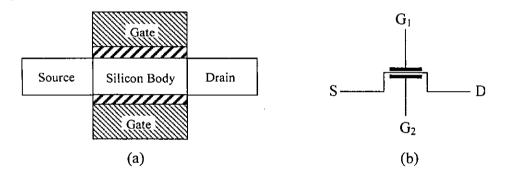

| Figure 2.3 (a) SOI MOSFET with top and bottom gate (b) Circuit Symbol                                       | 8     |  |  |  |

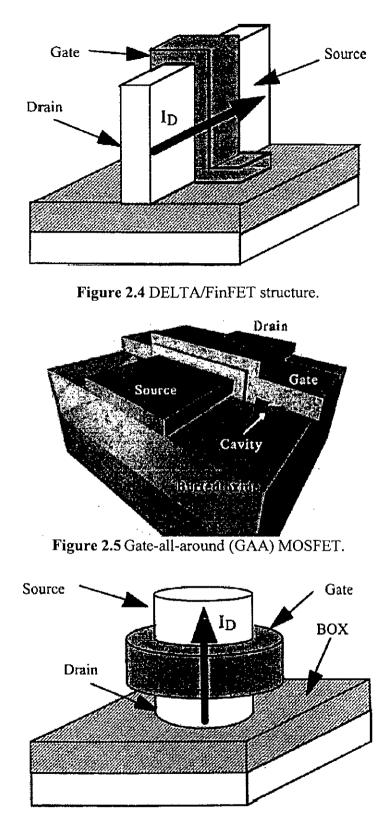

| Figure 2.4 DELTA/FinFET structure.                                                                          | 10    |  |  |  |

| Figure 2.5 Gate-all-around (GAA) MOSFET.                                                                    | 10    |  |  |  |

| Figure 2.6 CYNTHIA/surrounding-gate MOSFET structure.                                                       | 10    |  |  |  |

|                                                                                                             |       |  |  |  |

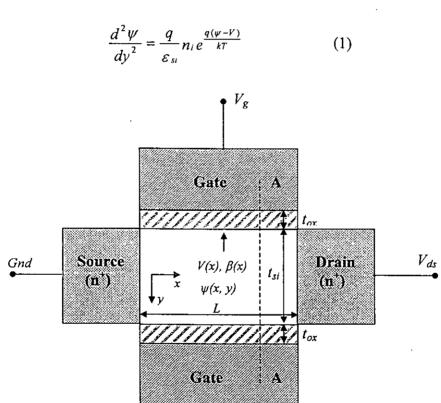

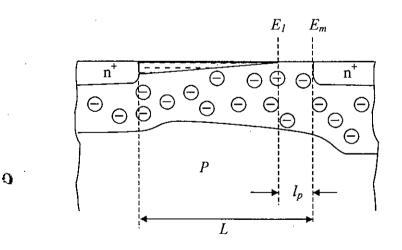

| Figure 3.1(a) Schematic diagram of a DG MOSFET                                                              | 15    |  |  |  |

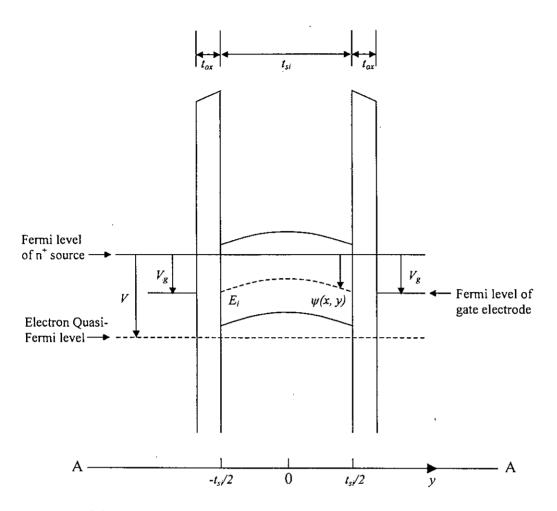

| Figure 3.1(b) Band diagram along a vertical cut (AA) in (a).                                                | 16    |  |  |  |

| Figure 3.3 Channel above pinchoff for a single-gate MSOFET                                                  | 19    |  |  |  |

|                                                                                                             |       |  |  |  |

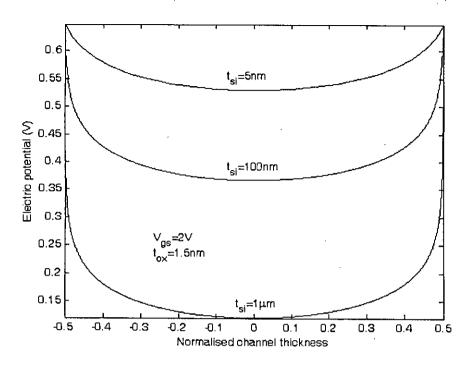

| Figure 4.1 Potential $\psi$ as a function of normalized channel thickness $(y/t_{si})$ at the so            | ource |  |  |  |

| end $(x=0)$ for three different values of $t_{si}$ .                                                        | 25    |  |  |  |

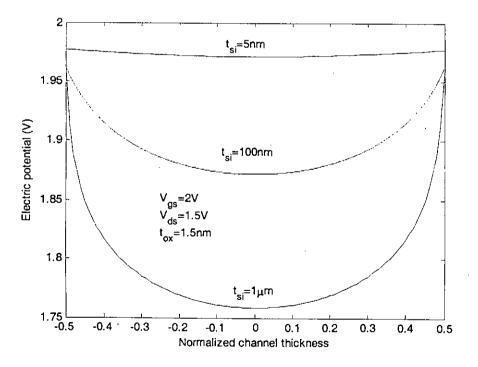

| Figure 4.2 Potential $\psi$ as a function of normalized channel thickness $(y/t_{si})$ at the drain         |       |  |  |  |

| end $(x=L)$ when $V_{ds}=1.5V$ .                                                                            | 25    |  |  |  |

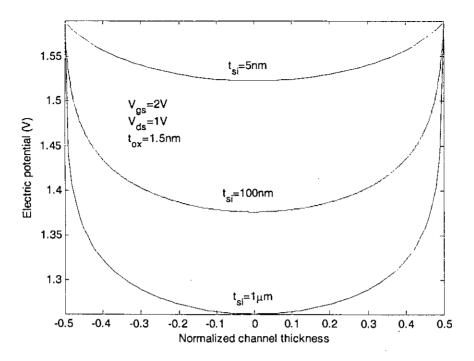

| Figure 4.3 Potential $\psi$ as a function of normalized channel thickness ( $y/t_{si}$ ) at the drai        | n     |  |  |  |

| end $(x=L)$ when $V_{ds}=IV$ .                                                                              | 26    |  |  |  |

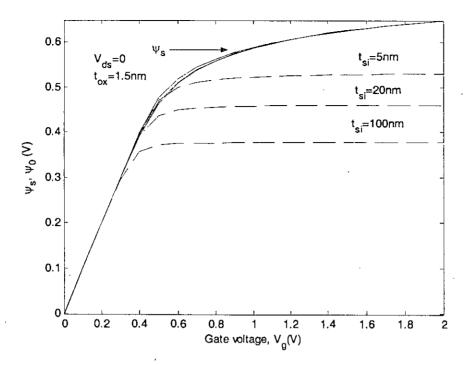

| Figure 4.4 Potential variation at the surface $\psi_s$ (continuous lines) and at the center of              | the   |  |  |  |

| silicon film $\psi_0$ (broken lines) as a function of gate voltage for three different values of $t_{si}$ . |       |  |  |  |

|                                                                                                             | 27    |  |  |  |

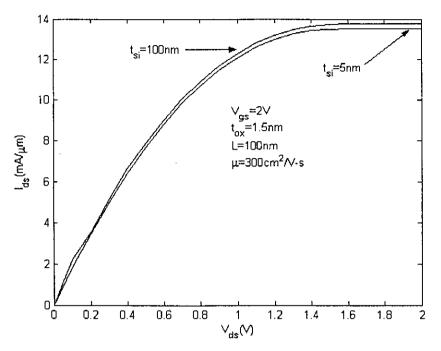

| Figure 4.5 $I_{ds}$ - $V_{ds}$ curves for two different film thicknesses.                                   | 27    |  |  |  |

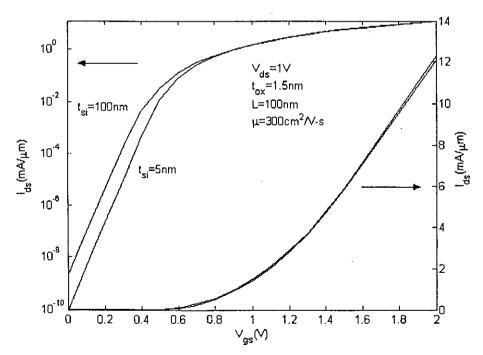

| Figure 4.6 $I_{ds}$ - $V_g$ characteristics for two different values of $t_{si}$ .                          | 28    |  |  |  |

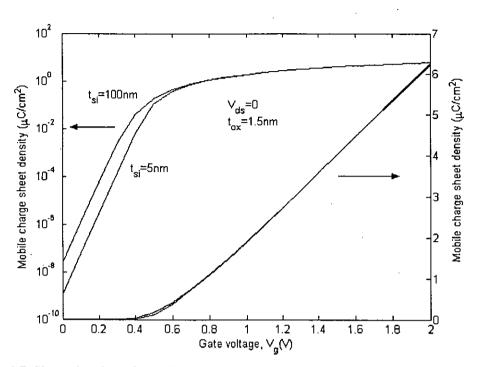

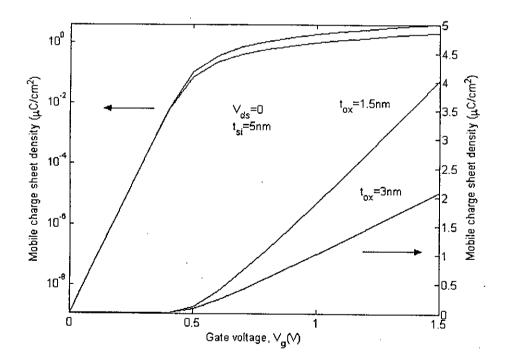

| Figure 4.7 Sheet density of mobile charge as a function of gate voltage for two silicon                     |       |  |  |  |

| film shi alim ana a                                                                                         |       |  |  |  |

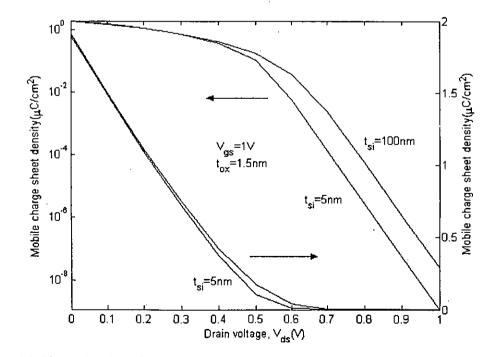

| 30<br>Figure 4.8 Sheet density of mobile charge as a function of drain voltage for two silicon              |       |  |  |  |

| film thicknesses.                                                                                           |       |  |  |  |

|                                                                                                             | 30    |  |  |  |

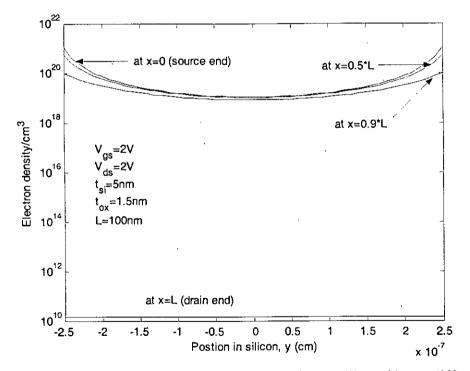

| Figure 4.9 Electron density as a function of position in the silicon film at different                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |        |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------|

| positions along the channel.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 31     |

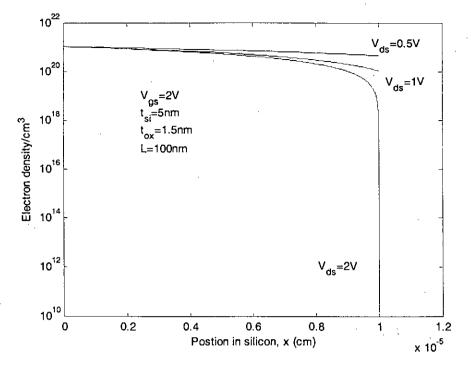

| Figure 4.10 Electron density as a function of position along the channel at different of                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | drain  |

| voltage.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 32     |

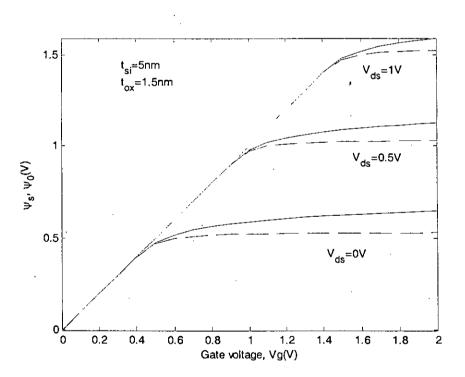

| <b>Figure 4.11</b> Surface potential $\psi_s$ (continuous lines) and potential at the center of the                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |        |

| channel $\psi_0$ (broken lines) versus the gate voltage.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 33     |

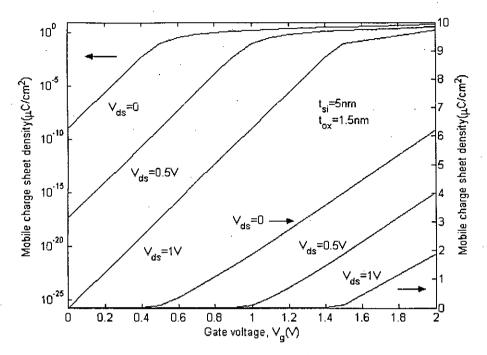

| Figure 4.12 Sheet density of mobile charge as a function of gate voltage for three va                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | lues   |

| of drain voltages.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 34     |

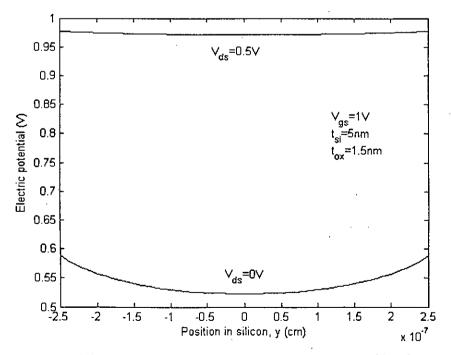

| <b>Figure 4.13</b> Potential $\psi$ as a function of position in the silicon film for two values of                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 2      |

| drain voltages.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 34     |

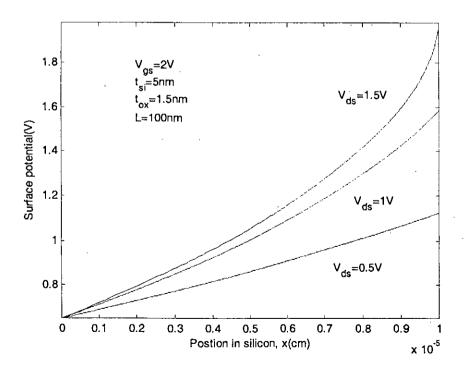

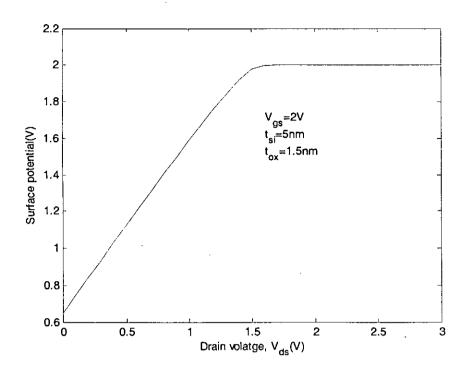

| <b>Figure 4.14</b> Variation of surface potential $\psi_s$ along the channel (source to drain)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 35     |

| <b>Figure 4.15</b> Surface potential $\psi_s$ at the drain end as a function of drain voltage for a potential $\psi_s$ at the drain end as a function of drain voltage for a potential $\psi_s$ at the drain end as a function of drain voltage for a potential $\psi_s$ at the drain end as a function of drain voltage for a potential $\psi_s$ at the drain end as a function of drain voltage for a potential $\psi_s$ at the drain end as a function of drain voltage for a potential $\psi_s$ at the drain end as a function of drain voltage for a potential $\psi_s$ at the drain end as a function of drain voltage for a potential $\psi_s$ at the drain end as a function of drain voltage for a potential $\psi_s$ at the drain end as a function of drain voltage for a potential $\psi_s$ at the drain end as a function of drain voltage for a potential $\psi_s$ at the drain end as a function of drain voltage for a potential $\psi_s$ at the drain end as a function of drain voltage for a potential $\psi_s$ at the drain end as a function of drain voltage for a potential $\psi_s$ at the drain end as a function of drain voltage for a potential $\psi_s$ at the drain end as a function of drain voltage for a potential $\psi_s$ at the drain end $\psi_s$ at the drain | given  |

| V <sub>g</sub> .                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 36     |

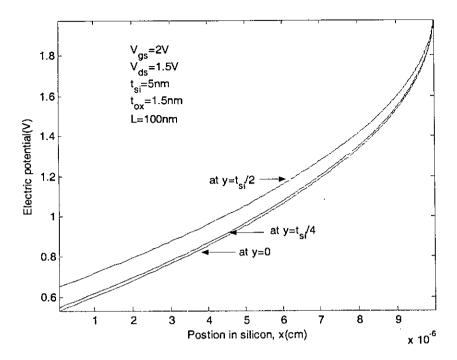

| Figure 4.16 Electric potential profile from source to drain at different depths o                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | of the |

| silicon channel for $V_{ds} = 1.5V$ .                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 37     |

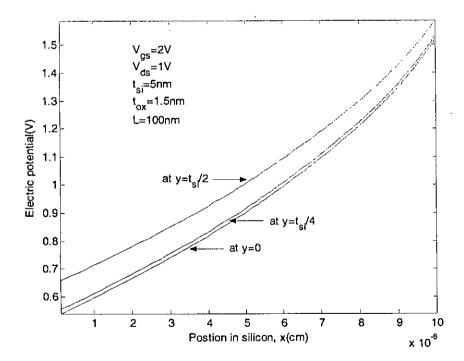

| Figure 4.17 Electric potential profile from source to drain at different depths o                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | of the |

| silicon channel for $V_{ds} = IV$ .                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 37     |

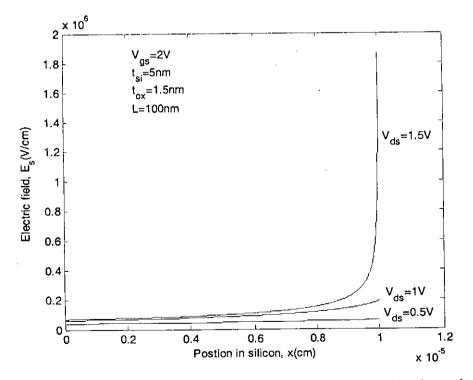

| Figure 4.18 Variation of electric field at the surface, $E_s$ along the channel (sour                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | ree to |

| drain)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 38     |

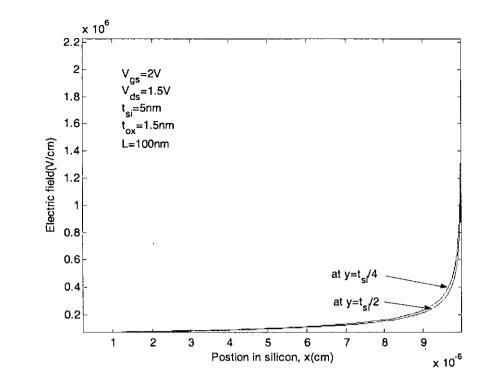

| Figure 4.19 Electric field profile from source to drain at different depths of the si                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | ilicon |

| channel for $V_{ds} = 1.5V$ .                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 39     |

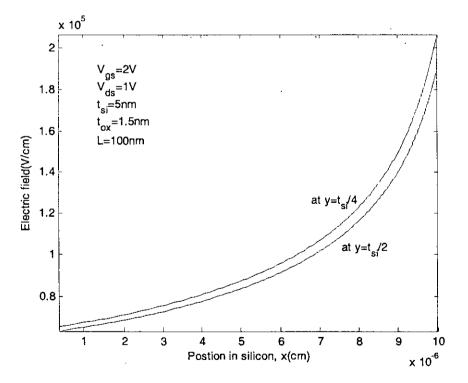

| Figure 4.20 Electric field profile from source to drain at different depths of the si                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | ilicon |

| channel for $V_{ds} = IV$ .                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 39     |

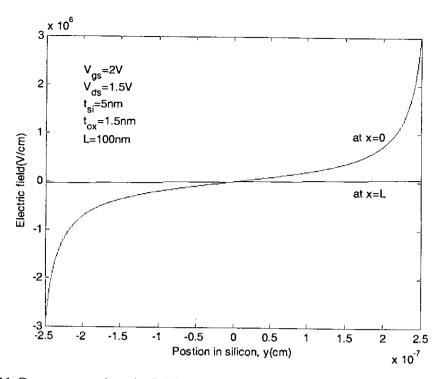

| <b>Figure 4.21</b> Gate to gate electric field profile at the source $(x=0)$ and at the drain $(x=0)$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | :L).   |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 40     |

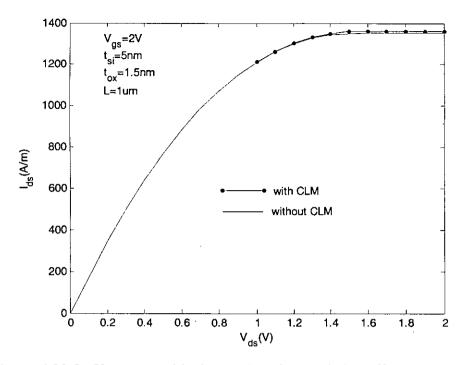

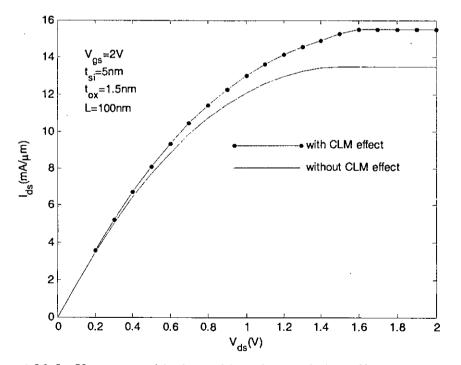

| <b>Figure 4.22</b> $I_{ds}$ - $V_{ds}$ curves with channel length modulation effect when $L = I \mu m$ .                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 41     |

| <b>Figure 4.23</b> $I_{ds}$ - $V_{ds}$ curves with channel length modulation effect when $L = 100nm$ .                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 41     |

| Figure 4.24 Sheet density of mobile charge at the source end as a function of gate                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |        |

| voltage for two oxide thicknesses.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 42     |

,

÷

.

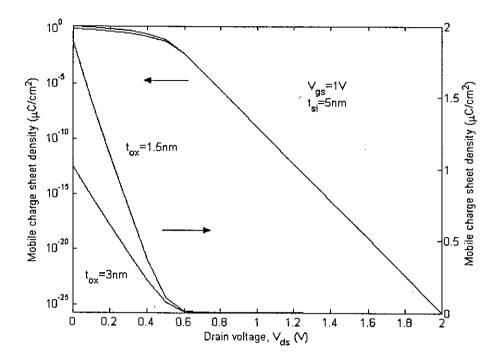

| Figure 4.25 Sheet density of mobile charge as a function of drain voltage for two oxide          | e  |  |  |  |

|--------------------------------------------------------------------------------------------------|----|--|--|--|

| thicknesses.                                                                                     | 43 |  |  |  |

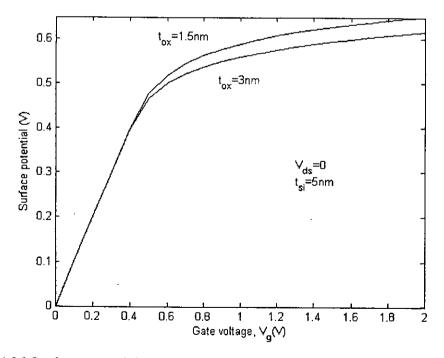

| Figure 4.26 Surface potential, $\psi_s$ as a function of gate voltage for two oxide thicknesses, |    |  |  |  |

| assuming zero drain-to-source voltage.                                                           | 43 |  |  |  |

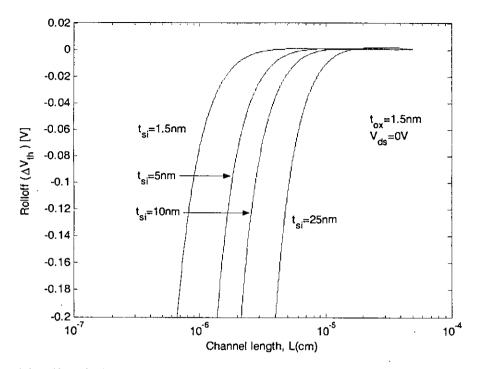

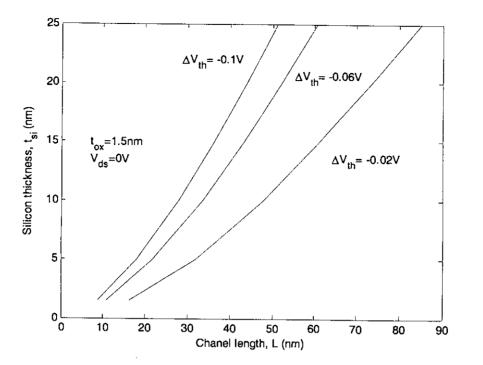

| Figure 4.27 Threshold voltage rolloff as a function of channel length for different silicon      |    |  |  |  |

| thicknesses when $V_{ds}=0$ .                                                                    | 45 |  |  |  |

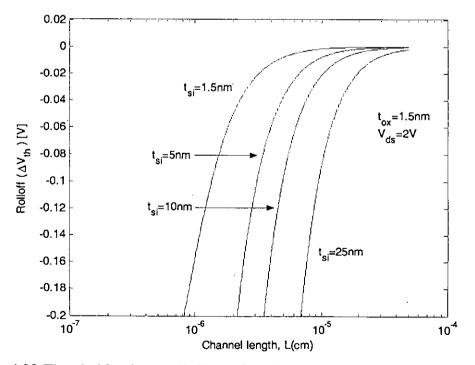

| Figure 4.28 Threshold voltage rolloff as a function of channel length for different silicon      |    |  |  |  |

| thicknesses when $V_{ds} = 2V$ .                                                                 | 45 |  |  |  |

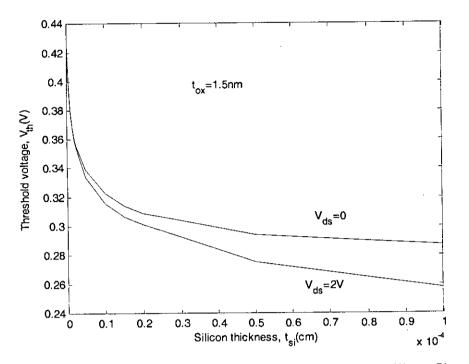

| Figure 4.29 Threshold voltage of a long channel DGFET versus silicon film thickness.             |    |  |  |  |

|                                                                                                  | 46 |  |  |  |

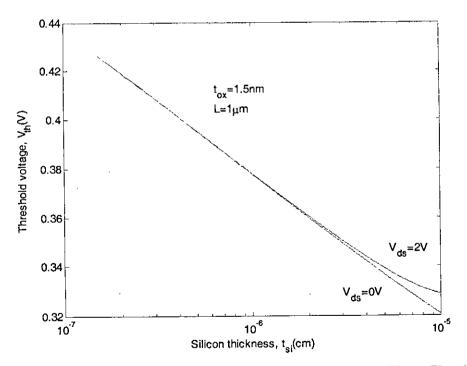

| Figure 4.30 Threshold voltage of long channel DGFET versus silicon film thickness.               | 46 |  |  |  |

| Figure 4.31 Silicon thickness versus channel length for different threshold rolloff.             | 47 |  |  |  |

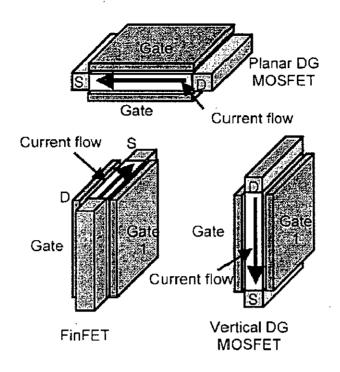

| Figure 4.32 Planar, Vertical and FinFET Architectures.                                           | 48 |  |  |  |

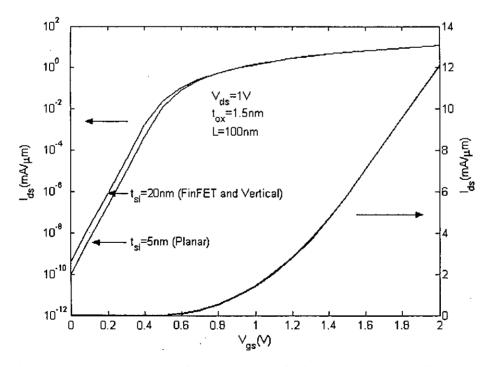

| Figure 4.33 $I_{ds}$ - $V_g$ characteristics for Planar, Vertical and FinFET Architectures.      | 48 |  |  |  |

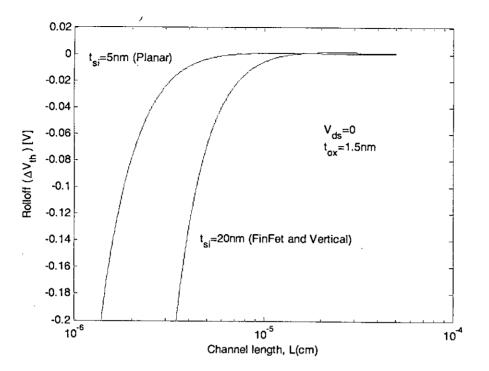

| Figure 4.34 Threshold voltage rolloff as a function of channel length for Planar, Vertical       |    |  |  |  |

| and FinFET Architectures.                                                                        | 49 |  |  |  |

ŀ

### Abstract