# CLOSED LOOP ĈUK TOPOLOGY BASED SINGLE PHASE HIGH PERFORNACE AC-DC CONVERTER

By

Md. Ismail Hossain

# DEPARTMENT OF ELECTRICAL AND ELECTRONIC ENGINEERING BANGLADESH UNIVERSITY OF ENGINEERING AND TECHNOLOGY

2013

# CLOSED LOOP ĈUK TOPOLOGY BASED SINGLE PHASE HIGH PERFORNACE AC-DC

| CONVERTER                                                                                   |  |  |

|---------------------------------------------------------------------------------------------|--|--|

|                                                                                             |  |  |

|                                                                                             |  |  |

|                                                                                             |  |  |

| By                                                                                          |  |  |

| Md. Ismail Hossain                                                                          |  |  |

|                                                                                             |  |  |

|                                                                                             |  |  |

| A thesis Submitted to the Department of Electrical and Electronic Engineering of Bangladesh |  |  |

| University of Engineering and Technology in partial Fulfillment of the Requirement for the  |  |  |

| Degree of                                                                                   |  |  |

|                                                                                             |  |  |

|                                                                                             |  |  |

|                                                                                             |  |  |

|                                                                                             |  |  |

|                                                                                             |  |  |

| MASTER OF SCIENCE IN ELECTRICAL AND ELECTRONIC ENGINEERING                                  |  |  |

|                                                                                             |  |  |

|                                                                                             |  |  |

|                                                                                             |  |  |

| DEPARTMENT OF ELECTRICAL AND ELECTRONIC ENGINEERING                                         |  |  |

| BANGLADESH UNIVERSITY OF ENGINEERING AND TECHNOLOGY                                         |  |  |

|                                                                                             |  |  |

September 2013

#### **APPROVAL**

This thesis titled "Closed loop Ĉuk topology based single phase high performance AC-DC converter" submitted by Md. Ismail Hossain, Roll No. 0411062239P, Session: April, 2011 has been accepted as satisfactory in partial fulfillment of the requirement for the degree of Master of Science in Electrical and Electronic Engineering on 1 September, 2013.

#### **BOARD OF EXAMINERS**

| Dr. Mohammad Jahangir Alam                | Chairman           |

|-------------------------------------------|--------------------|

| Professor                                 | (Supervisor)       |

| Department of EEE                         |                    |

| BUET, Dhaka                               |                    |

|                                           | 24.                |

| Dr. Pran Kanai Saha<br>Professor and Head | Member (Evanticia) |

|                                           | (Ex-officio)       |

| Department of EEE BUET, Dhaka             |                    |

|                                           |                    |

| Dr. Mohammad Ali Choudhury                | Member             |

| Professor                                 |                    |

| Department of EEE                         |                    |

| BUET, Dhaka                               |                    |

|                                           | <b>N</b> 1         |

| Dr. Md. Raju Ahmed                        | Member             |

| Assistant Professor                       | (External)         |

| Department of EEE                         |                    |

| DUET, Gazipur                             |                    |

## **CANDIDATE'S DECLARATION**

| This is hereby declared that this thesis titled "Closed loop Ĉuk topology based single phase |  |  |  |  |

|----------------------------------------------------------------------------------------------|--|--|--|--|

| high performance AC-DC converter" or any part of it has not been submitted elsewhere for     |  |  |  |  |

| he award of any degree or diploma.                                                           |  |  |  |  |

|                                                                                              |  |  |  |  |

|                                                                                              |  |  |  |  |

|                                                                                              |  |  |  |  |

|                                                                                              |  |  |  |  |

|                                                                                              |  |  |  |  |

| Signature of the candidate                                                                   |  |  |  |  |

|                                                                                              |  |  |  |  |

|                                                                                              |  |  |  |  |

| Md. Ismail Hossain                                                                           |  |  |  |  |

### **DEDICATED**

TO

MY PARENTS AND MY WIFE

NAZNIN AKTER

# TABLE OF CONTENTS

| Title                                                                               | II   |

|-------------------------------------------------------------------------------------|------|

| Approval                                                                            | II   |

| Candidate declaration                                                               | IV   |

| Dedication                                                                          | V    |

| Table of Contents                                                                   | VI   |

| List of Figures                                                                     | VIII |

| List of Tables                                                                      | XIV  |

| List of Abbreviation                                                                | XV   |

| Acknowledge                                                                         | XVI  |

| Abstract                                                                            | XVII |

| Chapter 1: Introduction                                                             |      |

| 1.1 Introduction                                                                    | 1    |

| 1.2 Background                                                                      | 1    |

| 1.3 Brief Review of the Digital Signal controller                                   | 2    |

| 1.4 Goal of Thesis                                                                  | 4    |

| 1.5 Thesis Organization                                                             | 4    |

| Chapter 2: Conventional and Ĉuk open/closed loop single phase AC-DC rectifier.      |      |

| 2.1 Full bridge Diode rectifier                                                     | 6    |

| 2.2 Open loop Ĉuk AC-DC converter                                                   | 16   |

| 2.3 Proposed close loop Ĉuk AC-DC converter                                         | 29   |

| 2.3.1 Close loop Ĉuk AC-DC converter                                                | 29   |

| 2.3.2 Close loop response analysis AC –DC Ĉuk converter using State space Averaging | 36   |

| Technique                                                                           |      |

| 2.4 Stability analysis of the controller using Bode plot                            | 41   |

| 2.5 Simulation under load change                                                    | 53   |

| 2.6 Simulation under input voltage change                                           | 54   |

# Chapter 3: Real time Program Algorithm and Simulation Using Proteus software through DSP processor

| 3.1 PROTEUS SIMULATION SOFTWARE                                                                                                      | 58  |

|--------------------------------------------------------------------------------------------------------------------------------------|-----|

| 3.2 Sensing network design.                                                                                                          | 59  |

| 3.2.1 Input rectified AC voltage and output DC voltage.                                                                              | 59  |

| 3.2.2 Input rectified Current.                                                                                                       | 60  |

| 3.3 Gate drive circuit                                                                                                               | 62  |

| 3.4 Complete circuit diagram                                                                                                         | 62  |

| 3.5 Average voltage computation in digital domain                                                                                    | 64  |

| 3.6 Analog to digital conversion                                                                                                     | 67  |

| 3.7 PWM signal generation                                                                                                            | 71  |

| 3.8 Digital implementation of proportional integral control                                                                          | 74  |

| 3.9 Timing logic for the software implementation                                                                                     | 76  |

| 3.10 Program Flowchart of the system                                                                                                 | 77  |

| 3.11 Simulation                                                                                                                      | 79  |

| 3.12 Relative performance between normal diode rectifier, open loop Ĉuk AC-DC converter and proposed close loop Ĉuk AC-DC converter. | 108 |

| 4. Conclusion and Recommendations for Future Work                                                                                    |     |

| 4.1 Conclusion                                                                                                                       | 113 |

| 4.2 Recommendations for Future Work                                                                                                  | 113 |

| REFERENCES                                                                                                                           | 114 |

| APPENDIX                                                                                                                             | 118 |

# LIST OF FIGURES

| 2.1:  | AC to DC converter using Full bridge Diode rectifier                                          | 6  |

|-------|-----------------------------------------------------------------------------------------------|----|

| 2.2:  | Input current and input voltage for $400\Omega$ load resistance                               | 7  |

| 2.3:  | FFT component of input current for $400\Omega$ load resistance and $410V$ (peak)              | 7  |

|       | input voltage.                                                                                |    |

| 2.4:  | Output voltage for $400\Omega$ load resistance and $410V$ (peak) input voltage.               | 8  |

| 2.5:  | Input current for $267\Omega$ load resistance and $410V$ (peak) input voltage.                | 8  |

| 2.6:  | FFT component of input current for $267\Omega$ load resistance and $410V$ (peak)              | 9  |

|       | input voltage                                                                                 |    |

| 2.7:  | Output voltage for $267\Omega$ load resistance and $410V$ (peak) input voltage                | 9  |

| 2.8:  | Input current for $200\Omega$ load resistance and $410V$ (peak) input voltage                 | 10 |

| 2.9:  | FFT component of input current for $200\Omega$ load resistance and 410V (peak)                | 10 |

|       | input voltage.                                                                                |    |

| 2.10: | Output voltage for $200\Omega$ load resistance and 410V (peak) input voltage.                 | 11 |

| 2.11: | Output voltage for $400\Omega$ load resistance and $325V$ (peak) input voltage                | 11 |

| 2.12: | Output voltage for $400\Omega$ load resistance and $282.8V$ (peak) input voltage              | 12 |

| 2.13: | Output voltage for $400\Omega$ load resistance and $368V$ (peak) input voltage                | 12 |

| 2.14: | Output voltage at different input voltages with $400\Omega$ load resistance                   | 13 |

| 2.15: | Input THD at different loads and 410V (peak) input voltage                                    | 14 |

| 2.16: | Efficiency at different loads and 410V (peak) input voltage                                   | 14 |

| 2.17: | Output voltage at different loads and 410V (peak) input voltage.                              | 15 |

| 2.18: | Input PF at different loads and 410V (peak) input voltage.                                    | 15 |

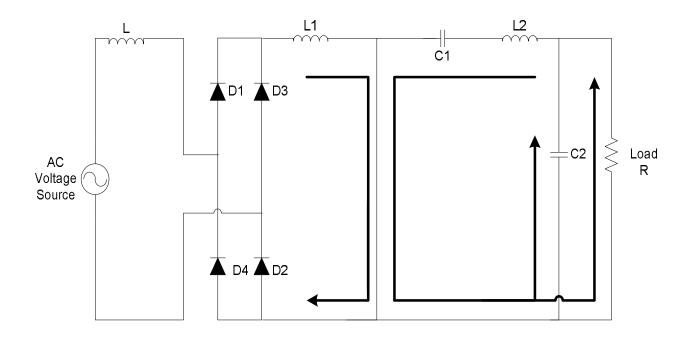

| 2.19: | Open loop ĈUK regulator based full bridge single phase rectifier                              | 16 |

| 2.20: | Mode-1 when Switch is closed                                                                  | 17 |

| 2.21: | Mode-2 when Switch is opened                                                                  | 17 |

| 2.22: | Input current for $400\Omega$ load resistance and $325V$ (peak) input voltage                 | 19 |

| 2.23: | FFT component of input current for $400\Omega$ load resistance and $325V(peak)$ input voltage | 19 |

| 2.24: | Output voltage for $400\Omega$ load resistance and $325V$ (peak) input voltage                | 20 |

| 2.25:    | Input current for 267 $\Omega$ load resistance and 325V (peak) input voltage                  | 20 |

|----------|-----------------------------------------------------------------------------------------------|----|

| 2.26:    | FFT component of input current for $267\Omega$ load resistance and $325V(peak)$ input voltage | 21 |

| 2.27:    | Output voltage for $267\Omega$ load resistance and $325V$ (peak) input voltage                | 21 |

| 2.28:    | Input current for $200\Omega$ load resistance and $325V$ (peak) input voltage                 | 22 |

| 2.29:    | FFT component of input current for $200\Omega$ load resistance and $325V(peak)$ input         | 22 |

|          | voltage                                                                                       |    |

| 2.30:    | Output voltage for $200\Omega$ load resistance and $325V$ (peak) input voltage                | 23 |

| 2.31:    | Output voltage for $400\Omega$ load resistance and $282.8V$ (peak) input voltage              | 23 |

| 2.32:    | Output voltage for $400\Omega$ load resistance and $367.69V$ (peak) input voltage             | 24 |

| 2.33:    | Output voltage at different input voltage with $400\Omega$ load resistance.                   | 25 |

| 2.34:    | Output voltage at different load and 325V (peak) input voltage.                               | 25 |

| 2.35:    | Input PF at different load and 325V (peak) input voltage.                                     | 26 |

| 2.36:    | Input THD at different load and 325V (peak) input voltage                                     | 26 |

| 2.37:    | Efficiency at different load and 325V (peak) input voltage                                    | 27 |

| 2.38:    | Proposed close loop ĈUK regulator based AC-DC converter                                       | 29 |

| 2.39:    | Proposed close loop ĈUK AC-DC converter in Matlab simulink                                    | 30 |

| 2.40:    | Customized representation of proposed close loop ĈUK AC-DC converter in Matlab                | 31 |

|          | simulink                                                                                      |    |

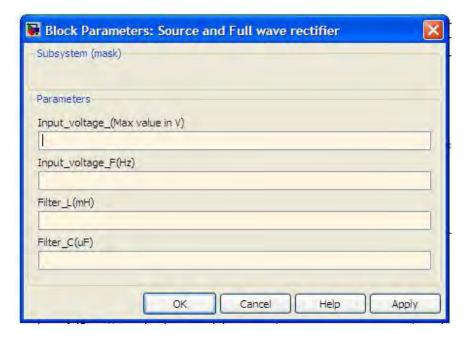

| 2.41:    | Input parameter of source and Full wave rectifier                                             | 31 |

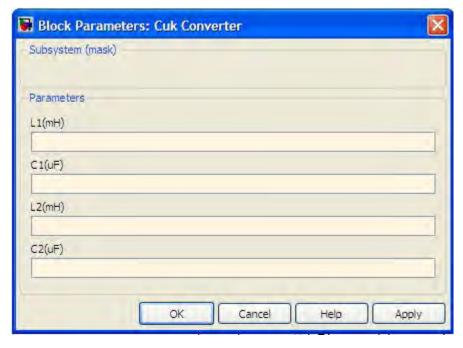

| 2.42:    | Input parameter of ĈUK converter                                                              | 32 |

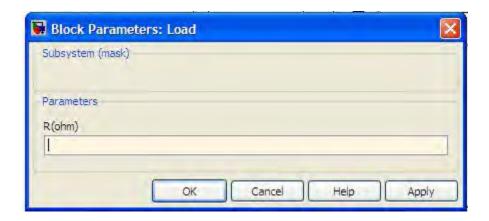

| 2.43:    | Input parameter of load block                                                                 | 32 |

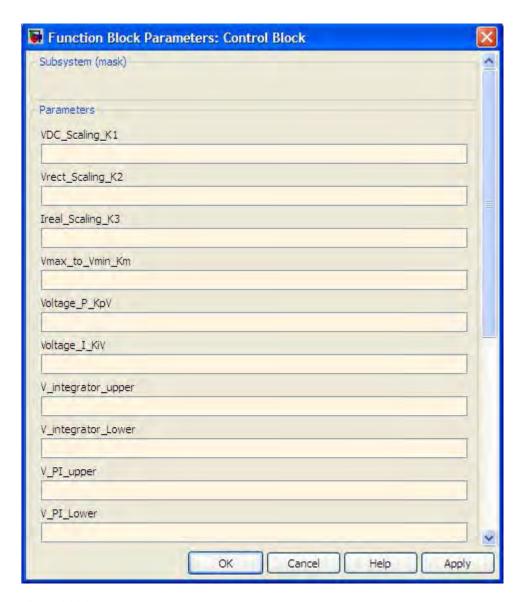

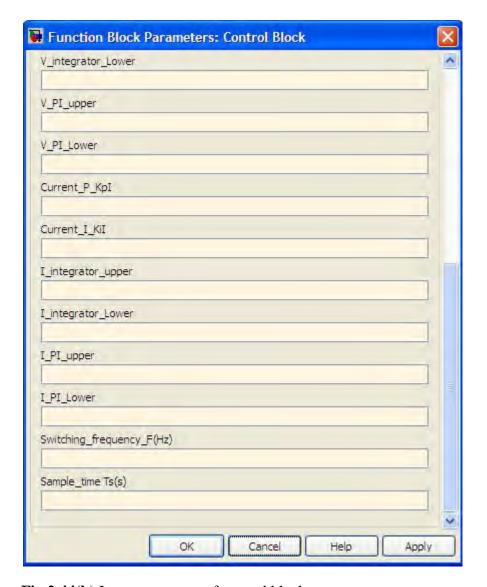

| 2.44(a): | Input parameter of control block                                                              | 33 |

| 2.44(b): | Input parameter of control block                                                              | 34 |

| 2.45:    | Determination of power factor in matlab simulink                                              | 35 |

| 2.46:    | ĈUK converter (a) when switch is closed (b) when switch is opened                             | 39 |

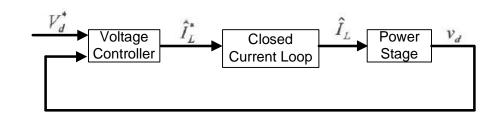

| 2.47:    | control loop of the proposed control system.                                                  | 42 |

| 2.48:    | current loop                                                                                  | 42 |

| 2.49:    | voltage loop                                                                                  | 43 |

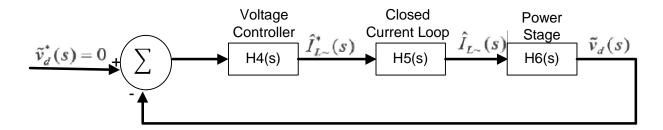

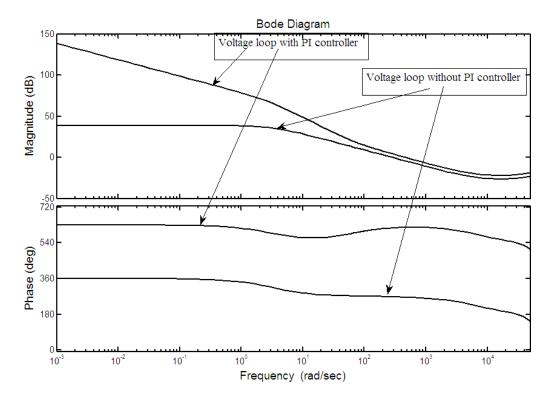

| 2.50:    | Stability analysis of current loop using bode plot                                            | 44 |

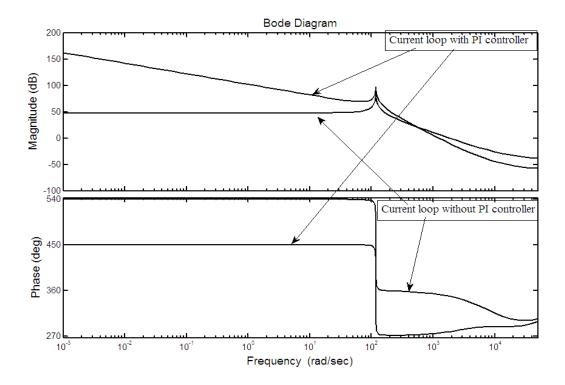

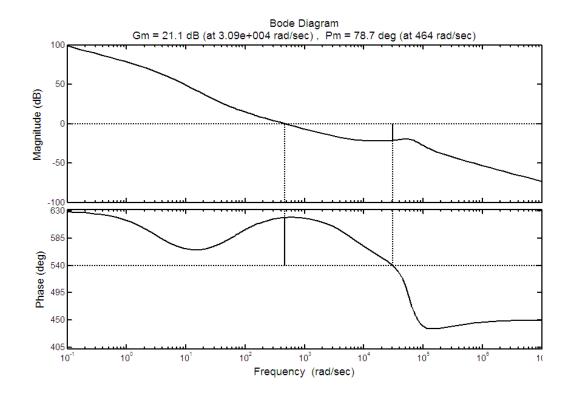

| 2.51:    | Phase margin and gain margin of current loop using bode plot with PI controller               | 45 |

| 2.52: | Stability analysis of voltage loop using bode plot                                                   | 45 |

|-------|------------------------------------------------------------------------------------------------------|----|

| 2.53: | Phase margin and gain margin of voltage loop using bode plot with PI                                 |    |

|       | controller                                                                                           | 46 |

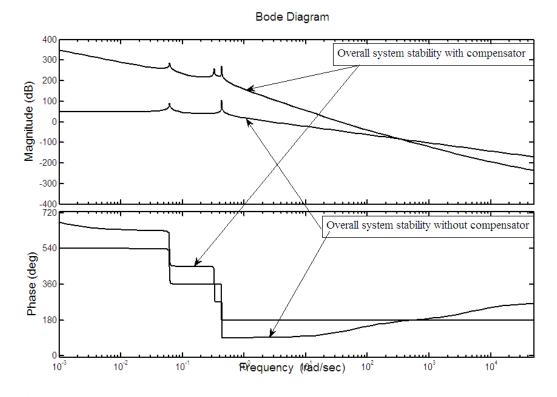

| 2.54: | Stability analysis of overall system (output voltage to duty ratio) using bode                       |    |

|       | plot                                                                                                 | 46 |

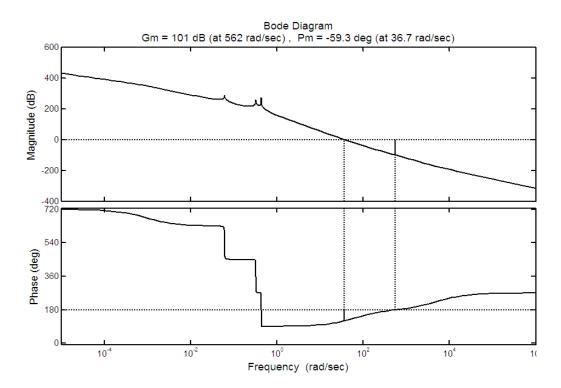

| 2.55: | Phase margin and gain margin of overall system (output voltage to duty ratio)                        | 47 |

|       | with compensator                                                                                     |    |

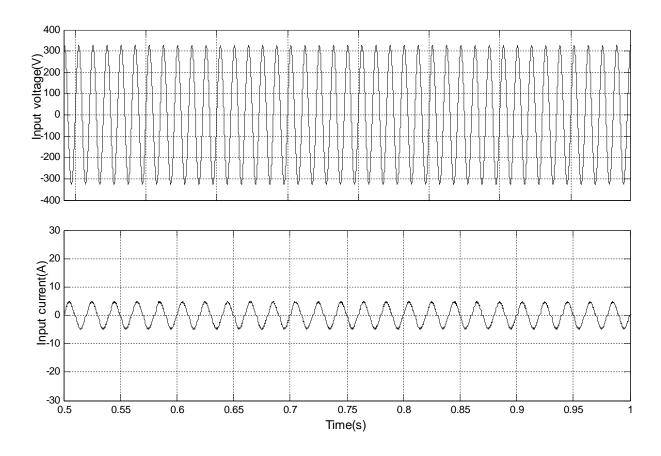

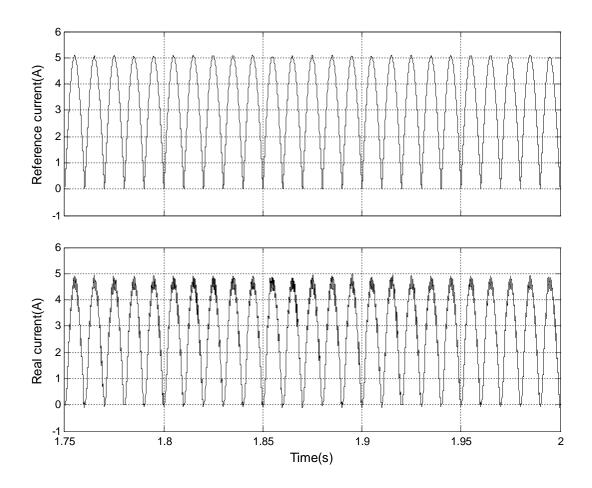

| 2.56: | Input voltage 325V (peak) and input current for 255 $\Omega$ load and -400V output voltage reference | 48 |

| 2.57: | Reference current and real current for $255\Omega$ load and -400V output voltage                     | 49 |

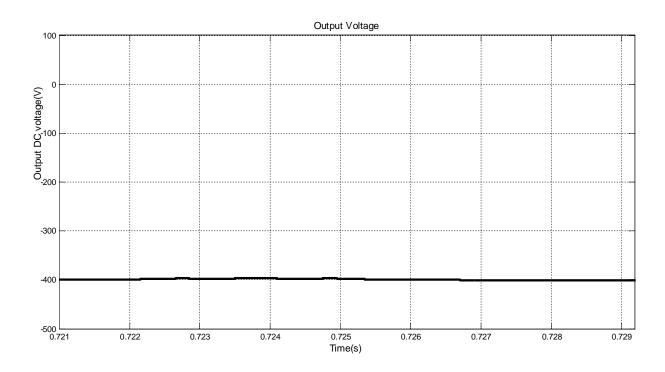

| 2.58: | Output voltage for $255\Omega$ load and $325V$ (peak) input voltage                                  | 50 |

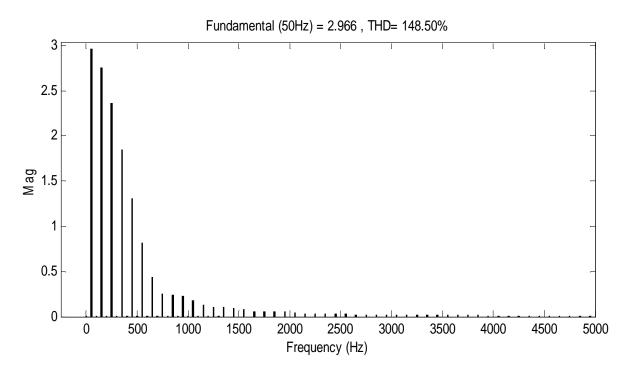

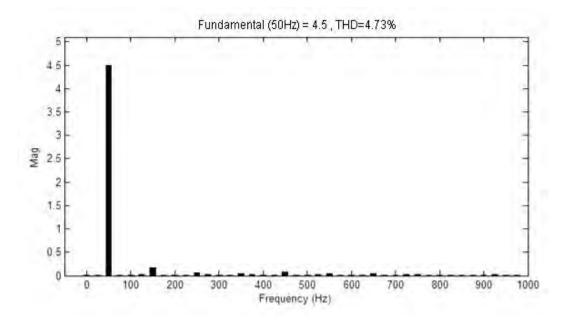

| 2.59: | THD of input current for $255\Omega$ load and $325V$ (peak) input voltage                            | 50 |

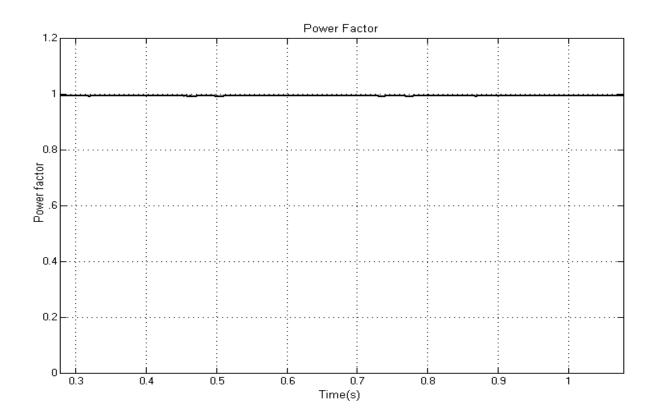

| 2.60  | Input power factor for $255\Omega$ load and $325V$ (peak) input voltage                              | 51 |

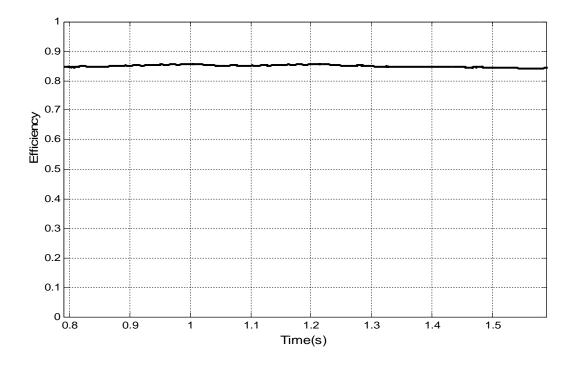

| 2.61: | Efficiency for $255\Omega$ load and $325V$ (peak) input voltage                                      | 51 |

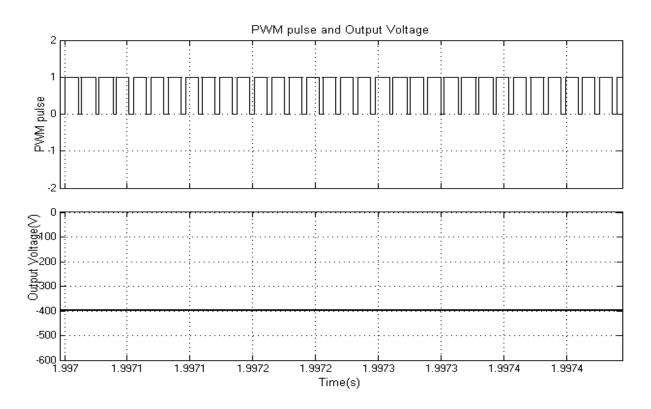

| 2.62: | PWM pulse and output voltage for $400\Omega$ load resistance                                         | 52 |

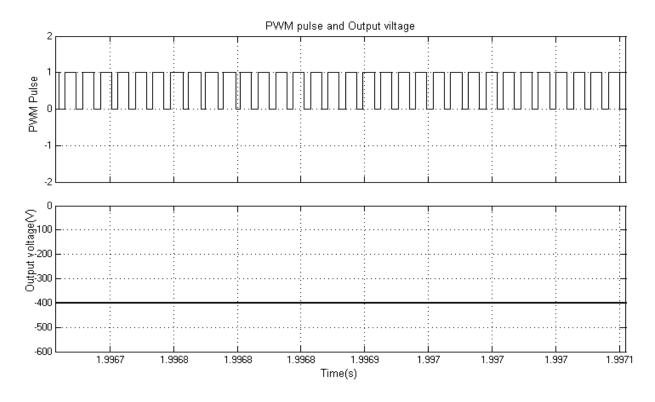

| 2.63: | PWM pulse and output voltage for $800\Omega$ load resistance                                         | 52 |

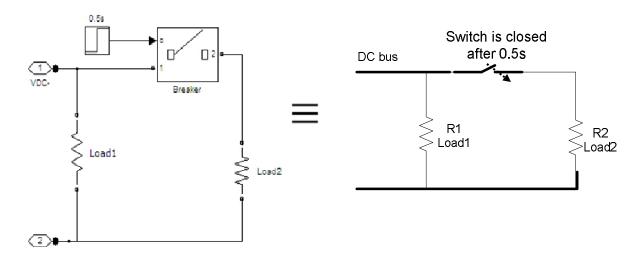

| 2.64: | Load changing after 0.5s                                                                             | 53 |

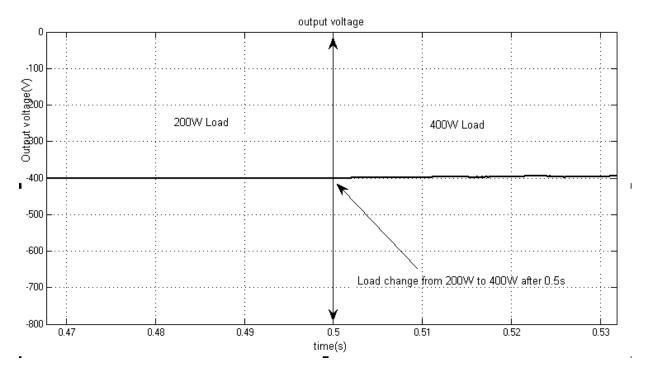

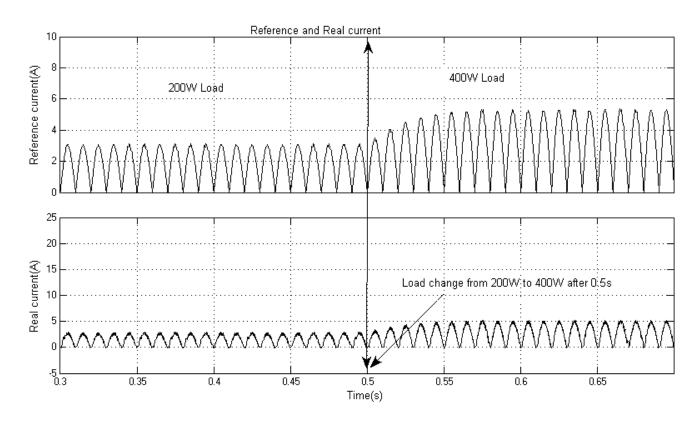

| 2.65: | Output voltage under load change from 200W to 400W                                                   | 53 |

| 2.66: | Reference and real current under load change from 200W to 400W                                       | 54 |

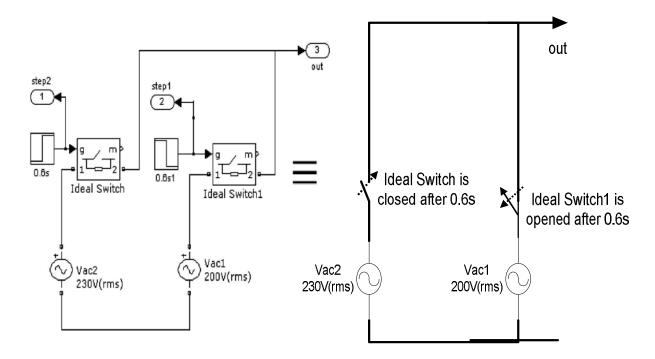

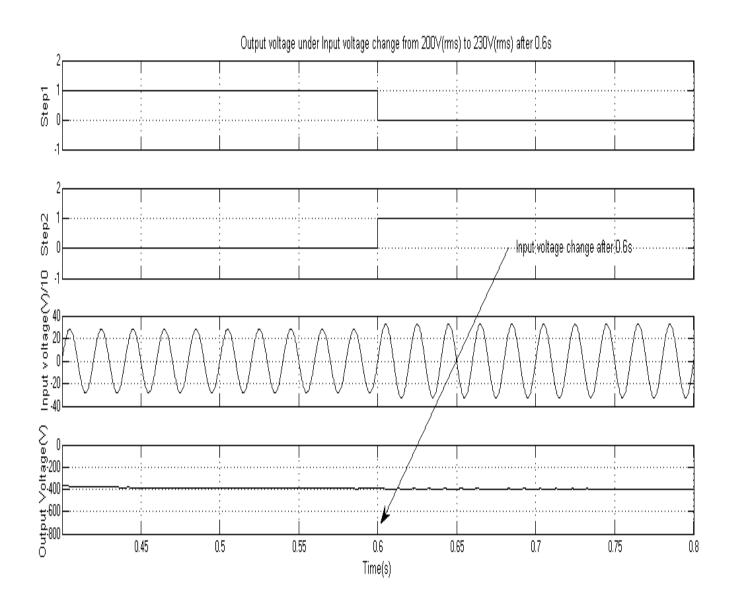

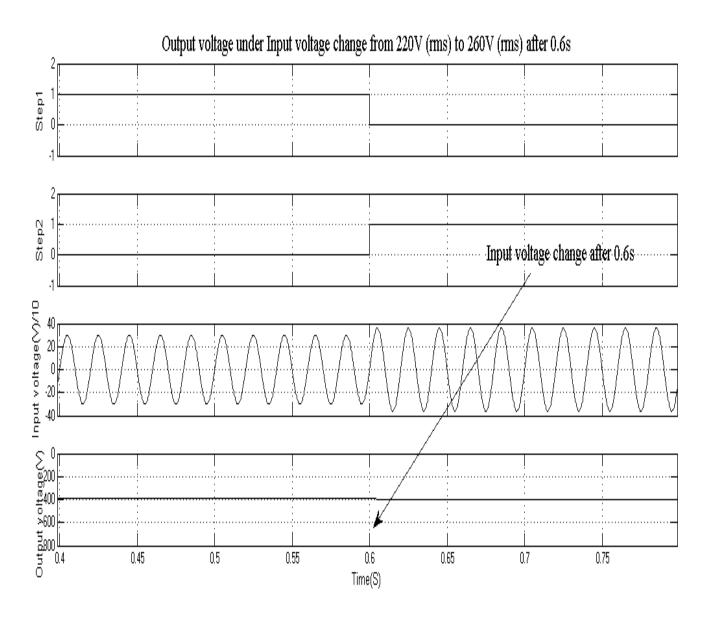

| 2.67: | Input voltage changing arrangement                                                                   | 55 |

| 2.68: | Output voltage under input voltage change from scaled 283V (peak) to scaled 325V (peak) after 0.6s   | 56 |

| 2.69: | Output voltage under input voltage change from scaled 311V (peak) to scaled                          | 57 |

|       | 367V (peak) after 0.6s                                                                               |    |

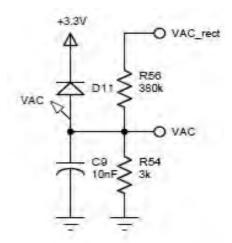

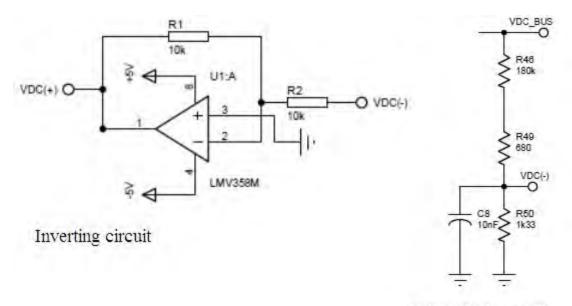

| 3.1:  | Voltage dividing resistor network                                                                    | 59 |

| 3.2:  | Voltage dividing resistor network and inverting network                                              | 60 |

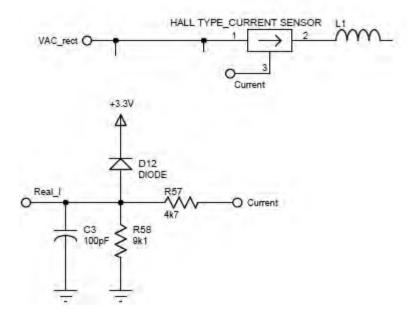

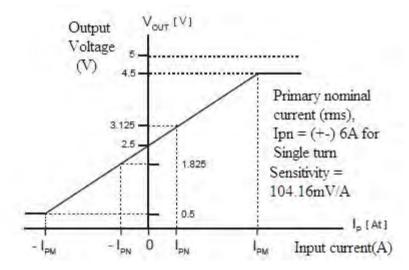

| 3.3:  | Current sensing circuit                                                                              | 61 |

| 3.4:  | Input current versus output voltage characteristic curve                                             | 61 |

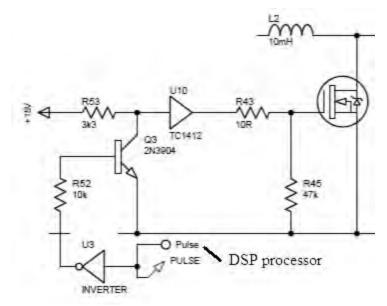

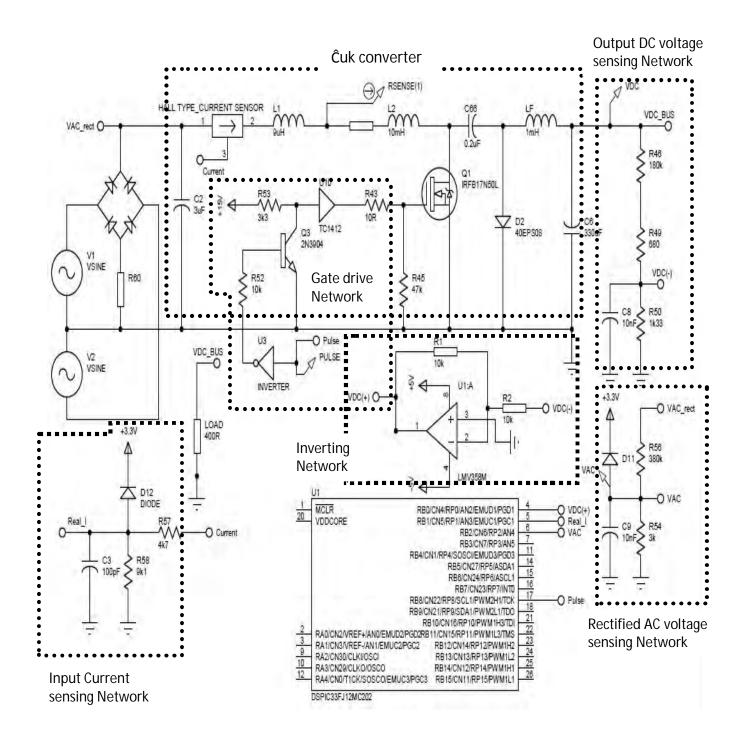

| 3.5:  | Gate drive circuit                                                                                   | 62 |

| 3.6:  | Complete circuit diagram of the proposed closed loop Ĉuk AC-DC converter                             | 63 |

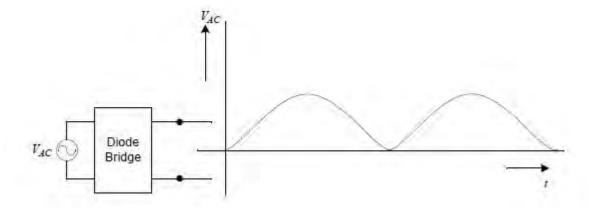

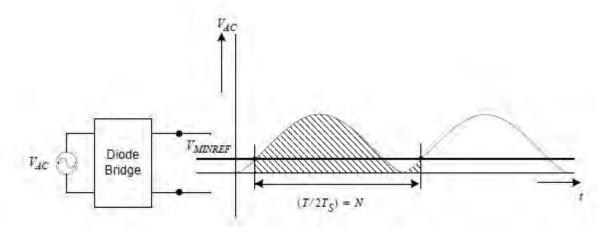

| 3.7:  | Rectified AC voltage                                                                                 | 65 |

| 3.8:  | Calculation of average AC voltage                                                              | 66 |

|-------|------------------------------------------------------------------------------------------------|----|

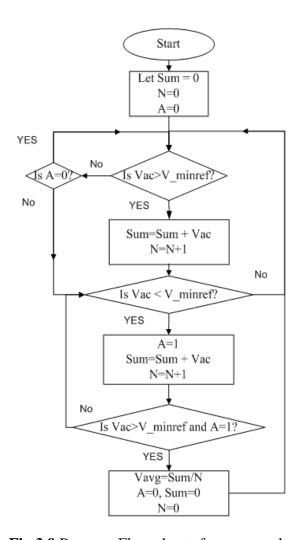

| 3.9:  | Program Flow chart of average voltage computation in digital domain                            | 66 |

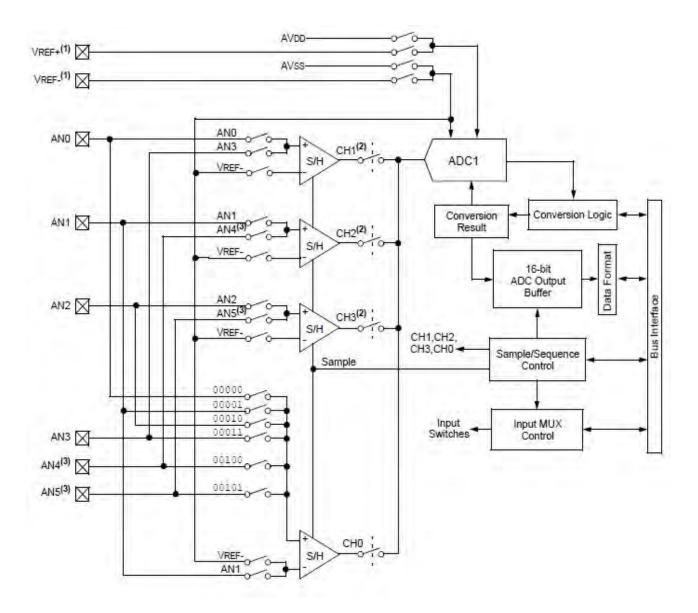

| 3.10: | ADC Module block diagram                                                                       | 70 |

| 3.11: | ADC conversion clock period block diagram                                                      | 70 |

| 3.12: | 2-Channel PWM Module block diagram (PWM2)                                                      | 73 |

| 3.13: | Edge aligned PWM                                                                               | 74 |

| 3.14: | Program Flow chart of PI control                                                               | 75 |

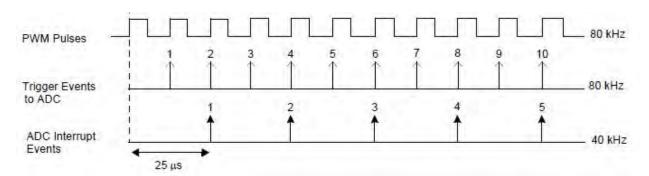

| 3.15: | Timing logic                                                                                   | 76 |

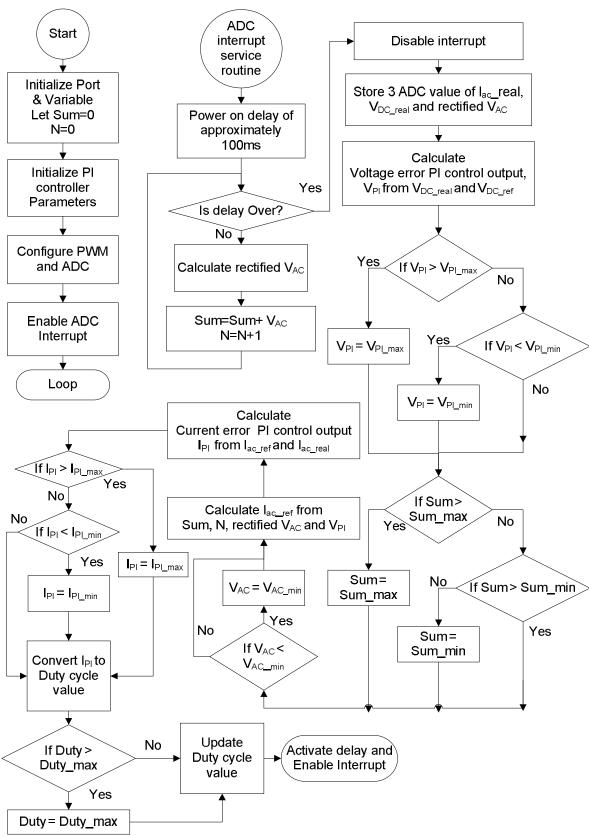

| 3.16: | Program Flow chart of the system                                                               | 78 |

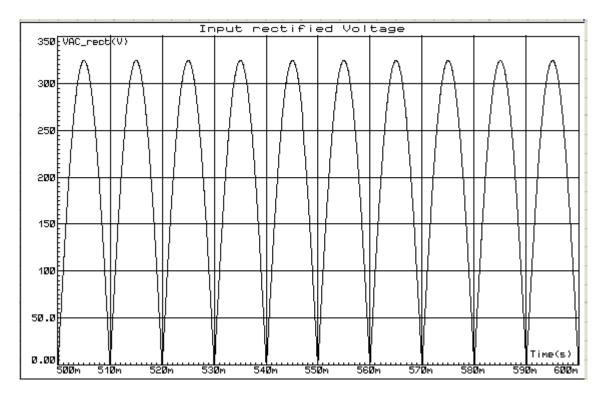

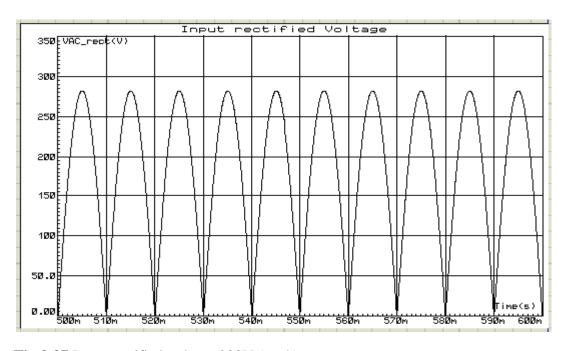

| 3.17: | Input rectified voltage 325V (peak)                                                            | 79 |

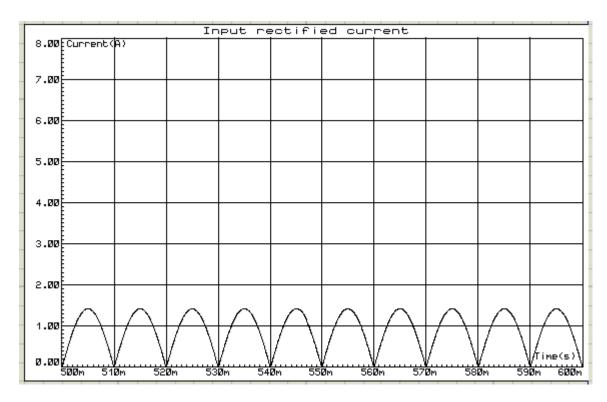

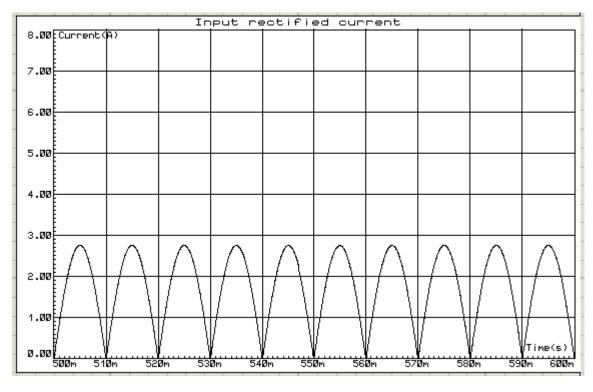

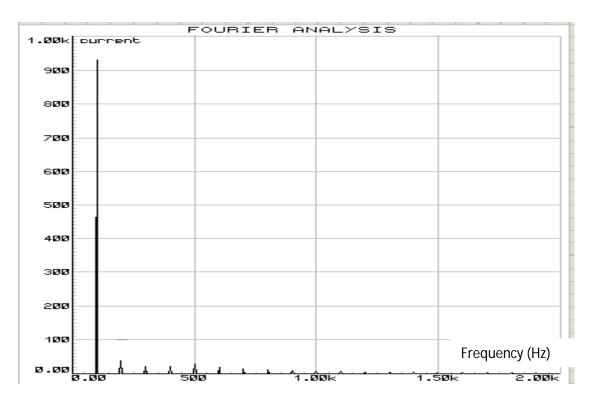

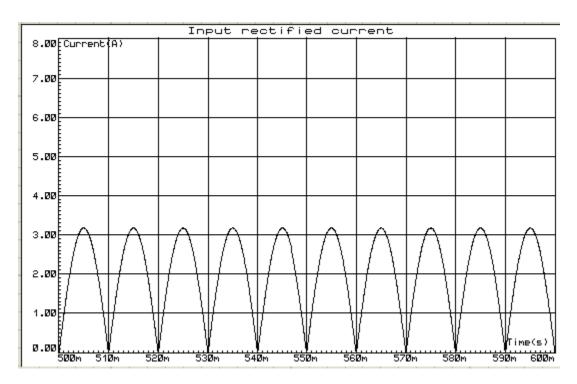

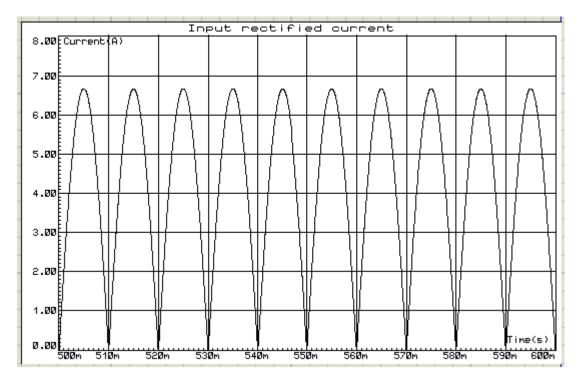

| 3.18: | Input rectified current for $800\Omega$ load resistance and $325V$ (peak) input voltage        | 80 |

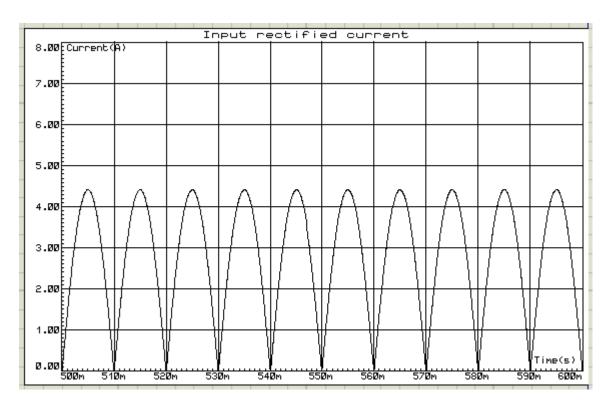

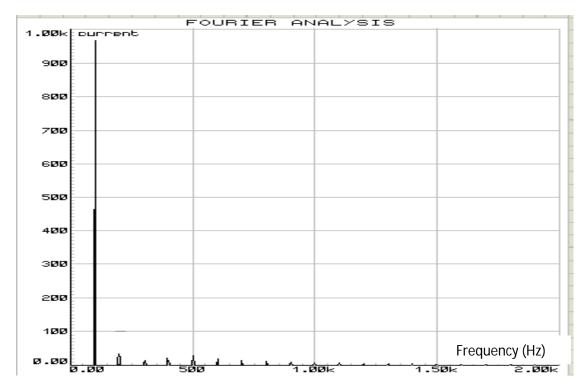

| 3.19: | Input rectified current for $400\Omega$ load resistance and $325V$ (peak) input voltage        | 80 |

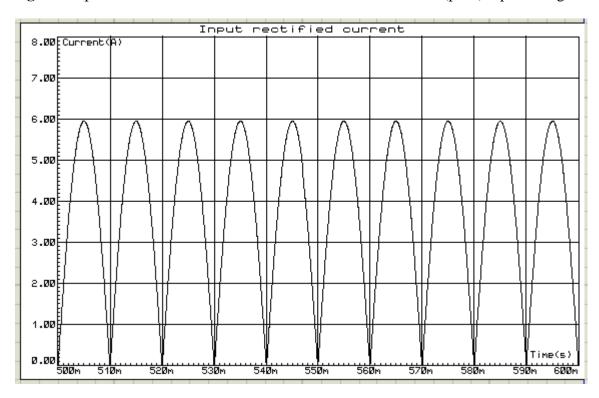

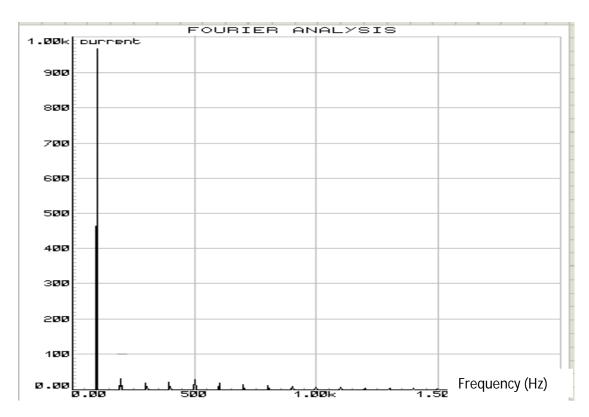

| 3.20: | Input rectified current for $267\Omega$ load resistance and $325V$ (peak) input voltage        | 81 |

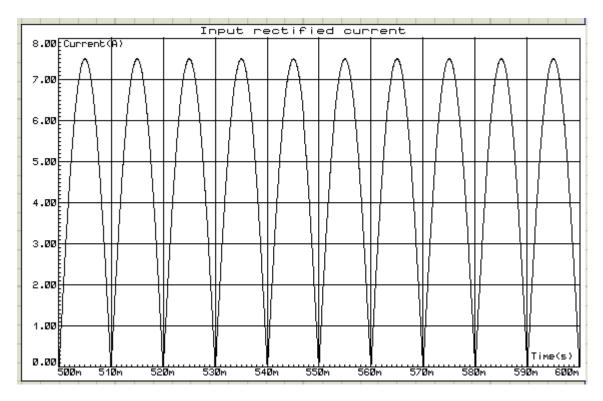

| 3.21: | Input rectified current for $200\Omega$ load resistance and $325V$ (peak) input voltage        | 81 |

| 3.22: | Input rectified current for $160\Omega$ load resistance and $325V$ (peak) input voltage        | 82 |

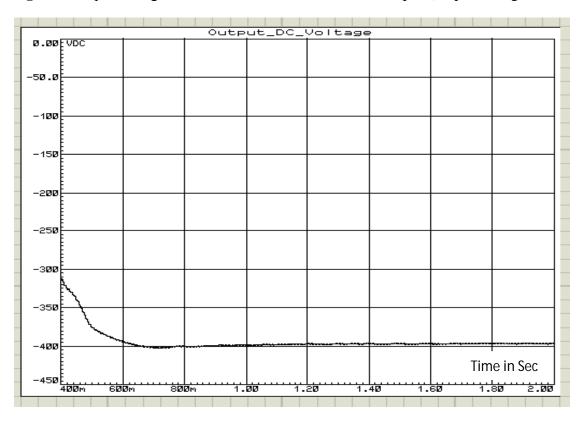

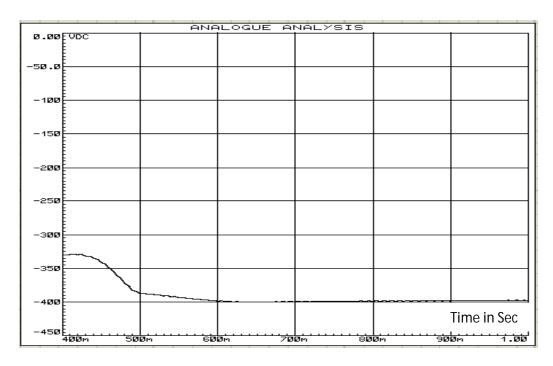

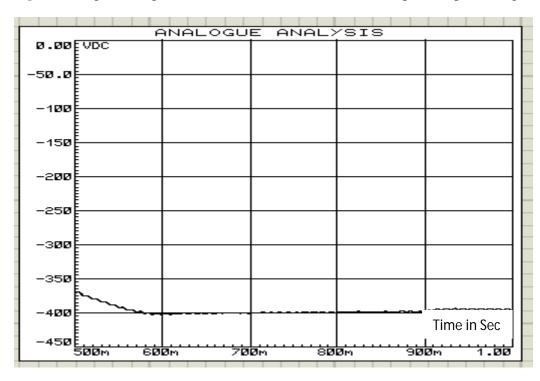

| 3.23: | Output voltage for $800\Omega$ load resistance and 325V (peak) input voltage                   | 82 |

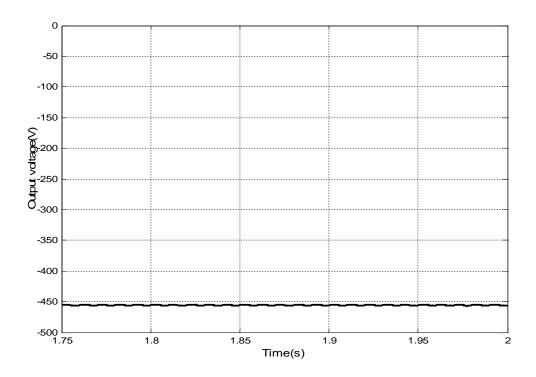

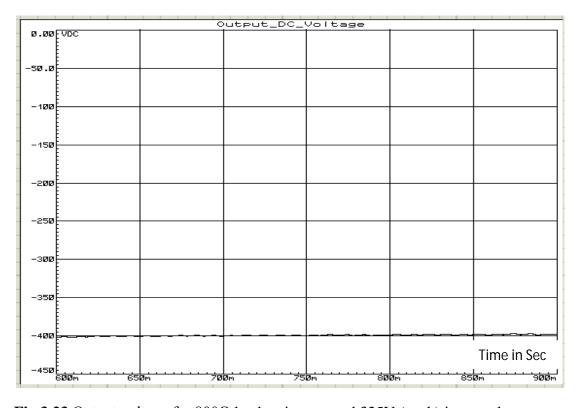

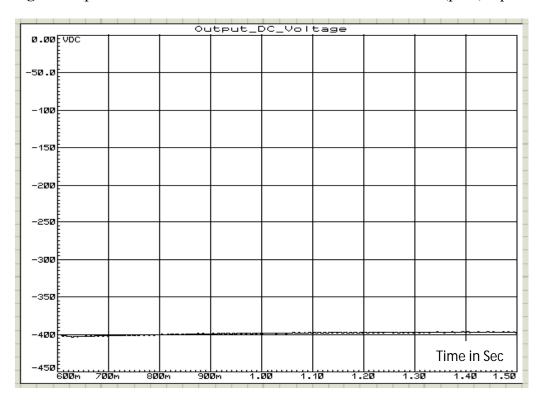

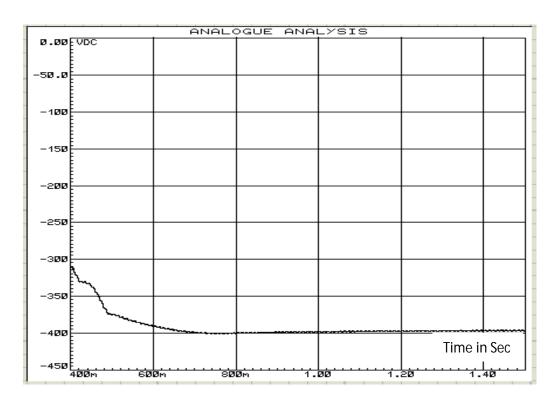

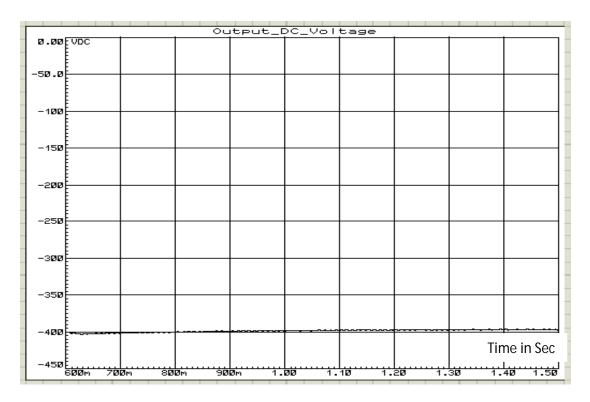

| 3.24: | Output voltage for $400\Omega$ load resistance and $325V$ (peak) input voltage                 | 83 |

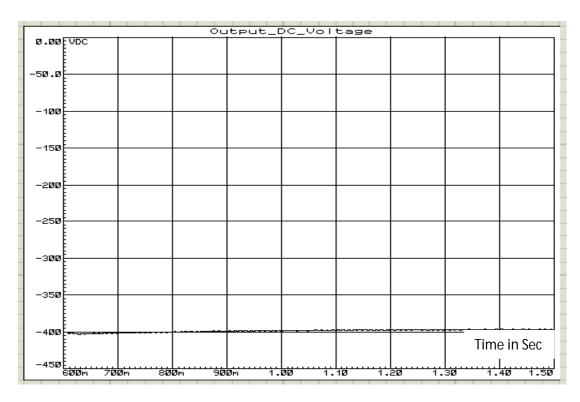

| 3.25: | Output voltage for $267\Omega$ load resistance and $325V$ (peak) input voltage                 | 83 |

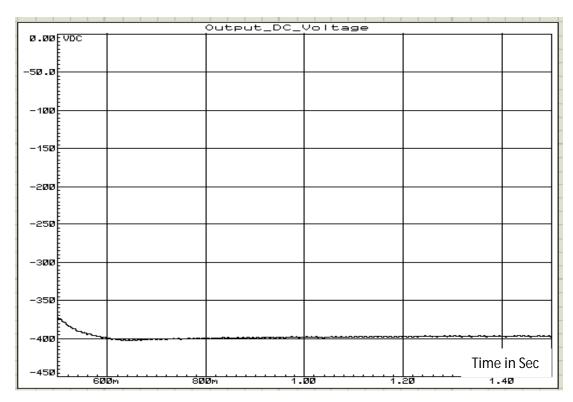

| 3.26: | Output voltage for $200\Omega$ load resistance and $325V$ (peak) input voltage                 | 84 |

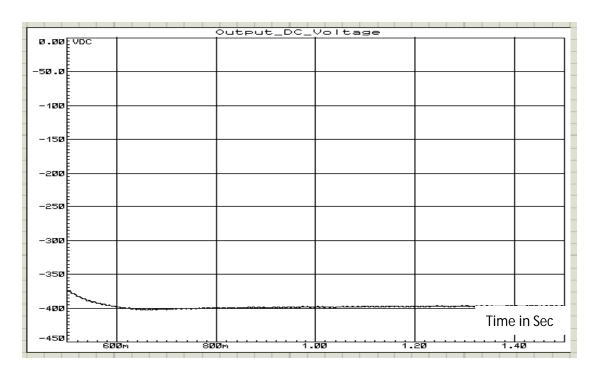

| 3.27: | Output voltage for $160\Omega$ load resistance and $325V$ (peak) input voltage                 | 84 |

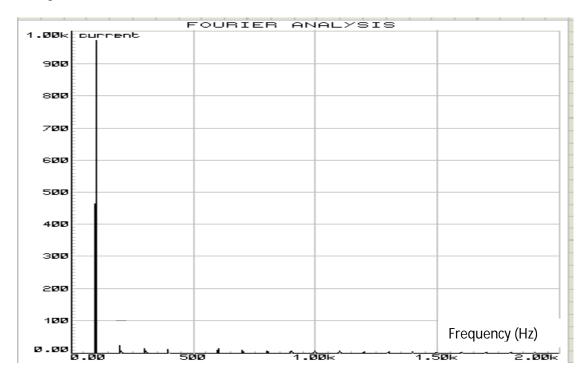

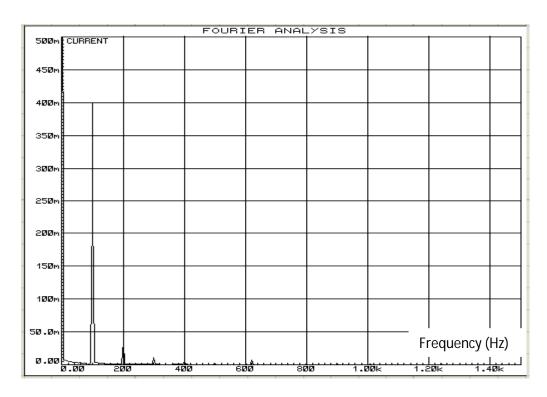

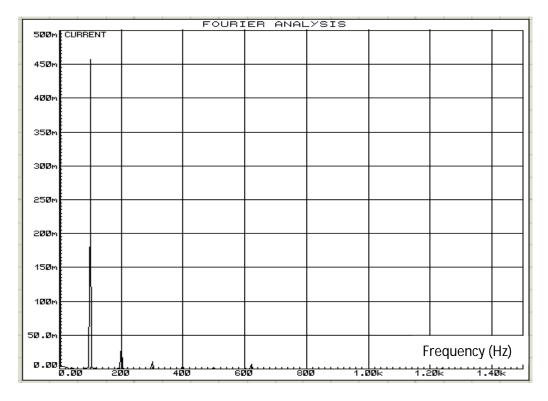

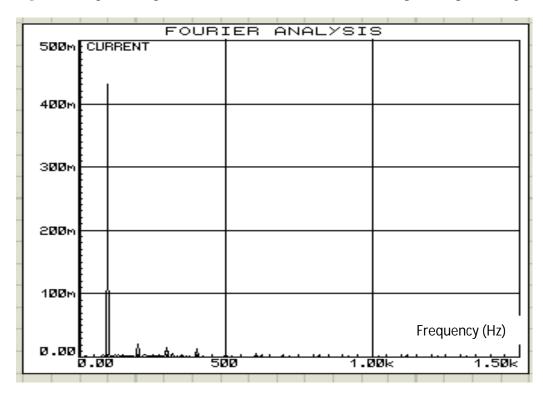

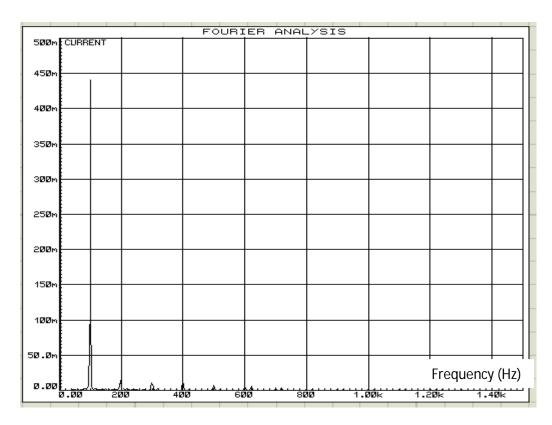

| 3.28: | FFT component of input current for $800\Omega$ load resistance and 325V (peak) input voltage   | 85 |

| 3.29: | FFT component of input current for $400\Omega$ load resistance and 325V (peak) input voltage   | 85 |

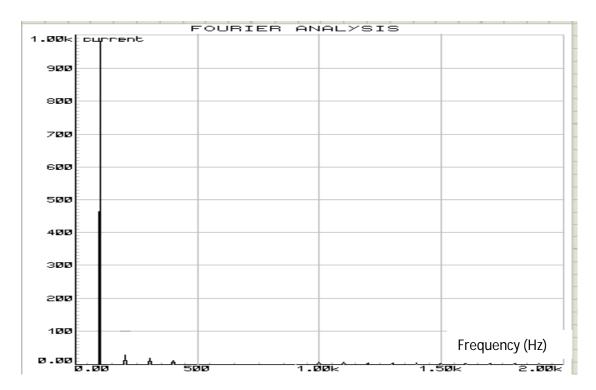

| 3.30: | FFT component of input current for $267\Omega$ load resistance and $325V$ (peak) input voltage | 86 |

| 3.31: | FFT component of input current for $200\Omega$ load resistance and $325V$ (peak) input voltage | 86 |

| 3.32: | FFT component of input current for $160\Omega$ load resistance and 325V (peak) input voltage   | 87 |

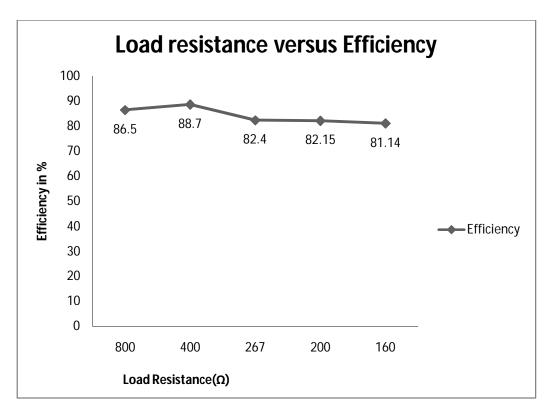

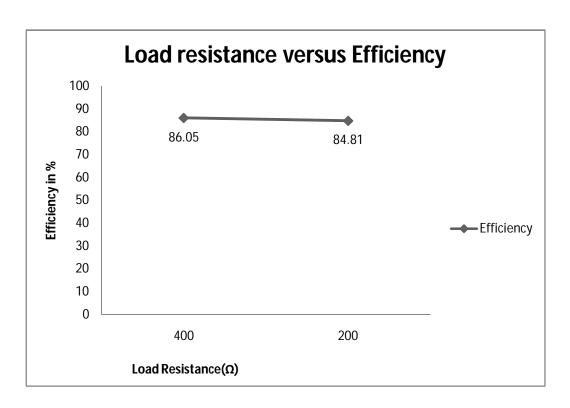

| 3.33: | Efficiency at different loads and 325V (peak) input voltage                                    | 88 |

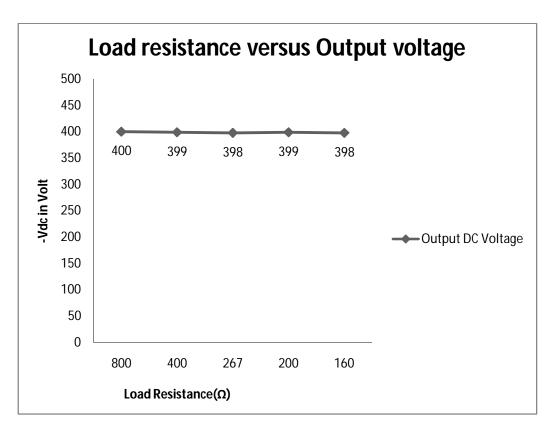

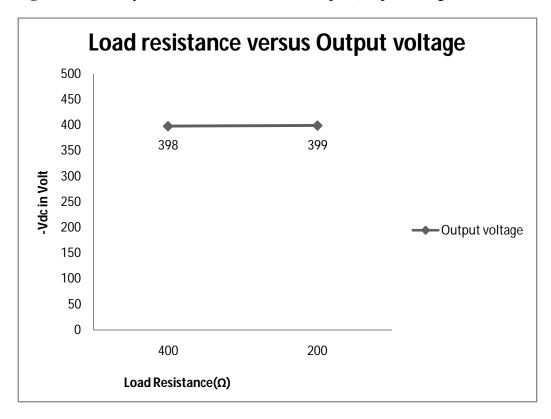

| 3.34: | Output voltage at different loads and 325V (peak) input voltage                                | 89 |

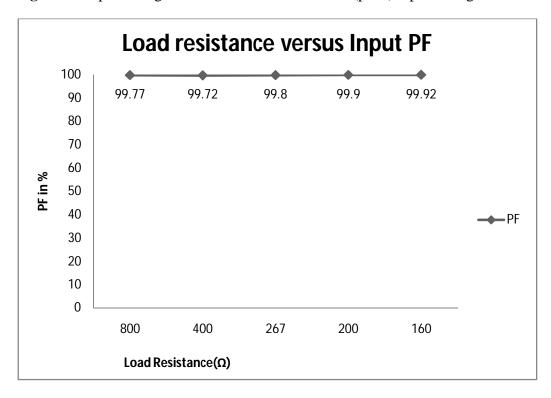

| 3.35: | Input PF at different loads and 325V (peak) input voltage                                      | 89 |

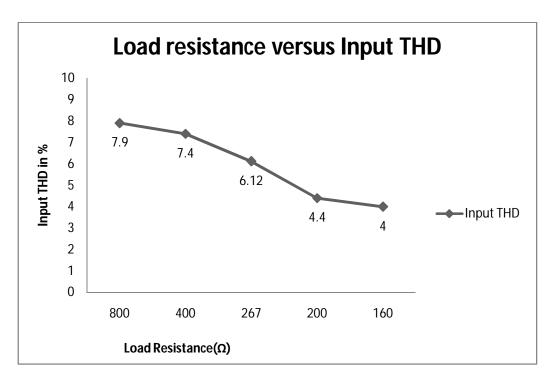

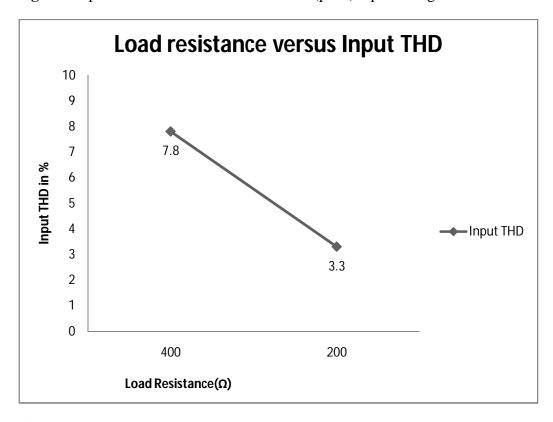

| 3.36: | Input THD at different loads and 325V (peak) input voltage                                     | 90  |

|-------|------------------------------------------------------------------------------------------------|-----|

| 3.37: | Input rectified voltage 283V (peak)                                                            | 90  |

| 3.38: | Input rectified current for $400\Omega$ load resistance and $283V$ (peak) input voltage        | 91  |

| 3.39: | Input rectified current for $200\Omega$ load resistance and $283V$ (peak) input voltage        | 91  |

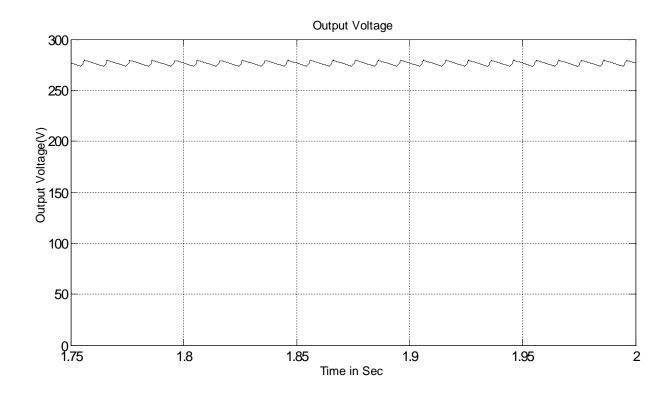

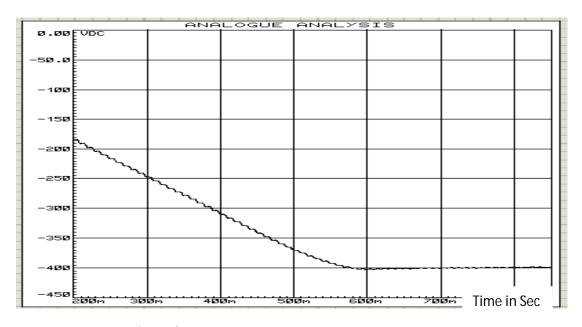

| 3.40: | Output voltage for $400\Omega$ load resistance and $283V$ (peak) input voltage                 | 92  |

| 3.41: | Output voltage for $200\Omega$ load resistance and $283V$ (peak) input voltage                 | 92  |

| 3.42: | FFT component of input current for $400\Omega$ load resistance and 283V (peak) input voltage   | 93  |

| 3.43: | FFT component of input current for $200\Omega$ load resistance and $283V$ (peak) input voltage | 93  |

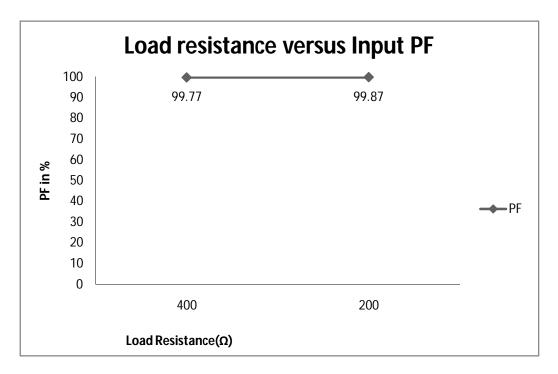

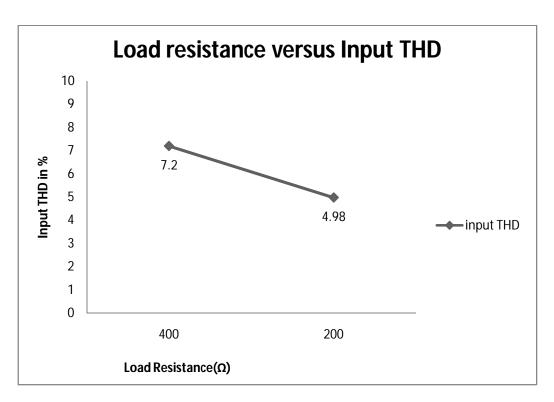

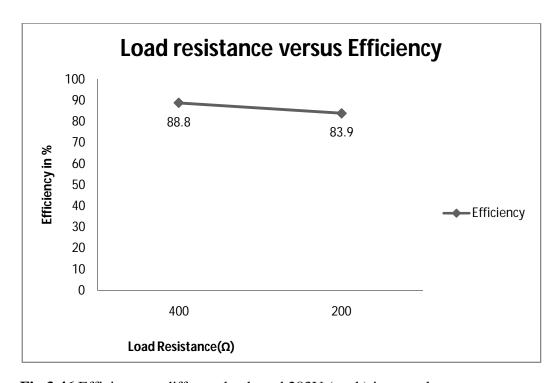

| 3.44: | Input PF at different loads and 283V (peak) input voltage                                      | 94  |

| 3.45: | Input THD at different loads and 283V (peak) input voltage                                     | 95  |

| 3.46: | Efficiency at different loads and 283V (peak) input voltage                                    | 95  |

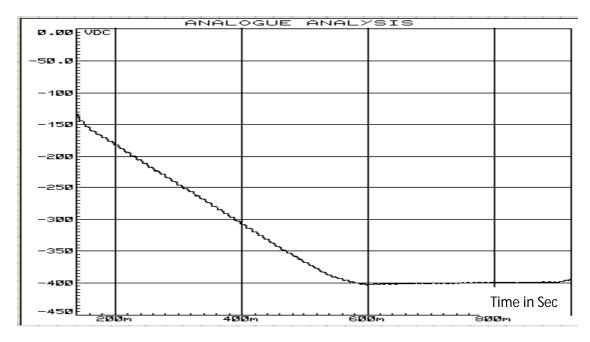

| 3.47: | Output voltage at different loads and 283V (peak) input voltage                                | 96  |

| 3.48: | Input rectified voltage 367V (peak)                                                            | 97  |

| 3.49: | Input rectified current for $400\Omega$ load resistance and $367V$ (peak) input voltage        | 97  |

| 3.50: | Input rectified current for $200\Omega$ load resistance and $367V$ (peak) input voltage        | 98  |

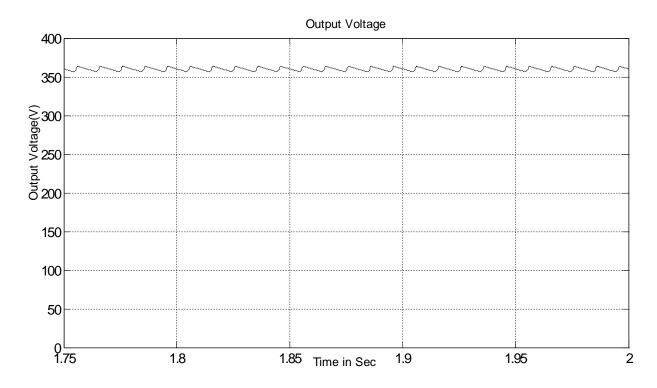

| 3.51: | Output voltage for $400\Omega$ load resistance and $367V$ (peak) input voltage                 | 98  |

| 3.52: | Output voltage for $200\Omega$ load resistance and 367V (peak) input voltage                   | 99  |

| 3.53: | FFT component of input current for $400\Omega$ load resistance and 367V (peak) input voltage   | 99  |

| 3.54: | FFT component of input current for $200\Omega$ load resistance and 367V (peak) input voltage   | 100 |

| 3.55: | Input PF at different loads and 367V (peak) input voltage                                      | 101 |

| 3.56: | Input THD at different loads and 367V (peak) input voltage                                     | 101 |

| 3.57: | Efficiency at different loads and 367V (peak) input voltage                                    | 102 |

| 3.58: | Output voltage at different loads and 367V (peak) input voltage                                | 102 |

| 3.59: | Output voltage at different input voltages                                                     | 103 |

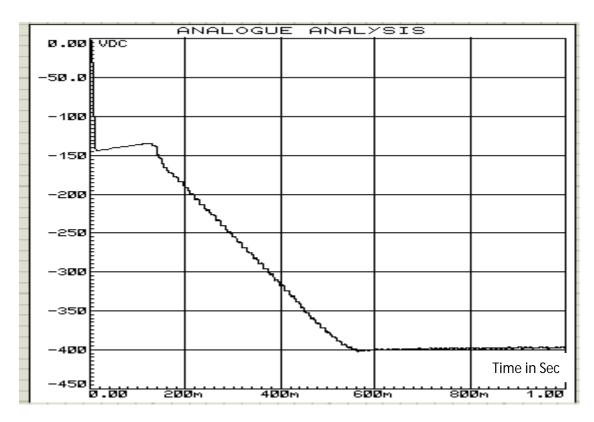

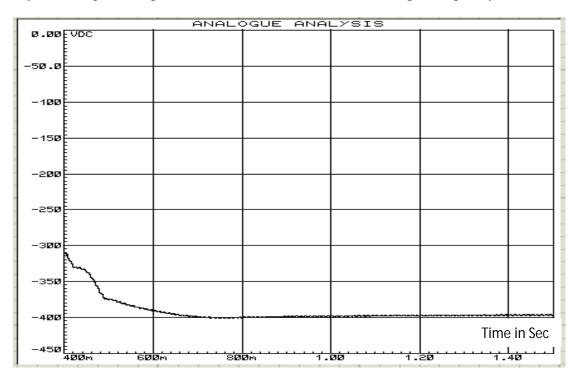

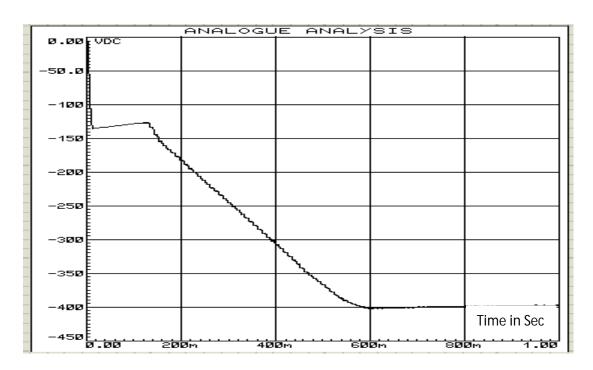

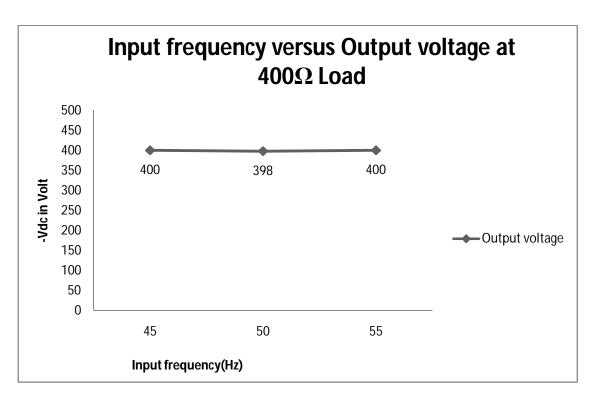

| 3.60: | Output voltage for $400\Omega$ load resistance and 45Hz input frequency                        | 103 |

| 3.61: | Output voltage for $400\Omega$ load resistance and 50Hz input frequency                        | 104 |

| 3.62: | Output voltage for $400\Omega$ load resistance and 55Hz input frequency                        | 104 |

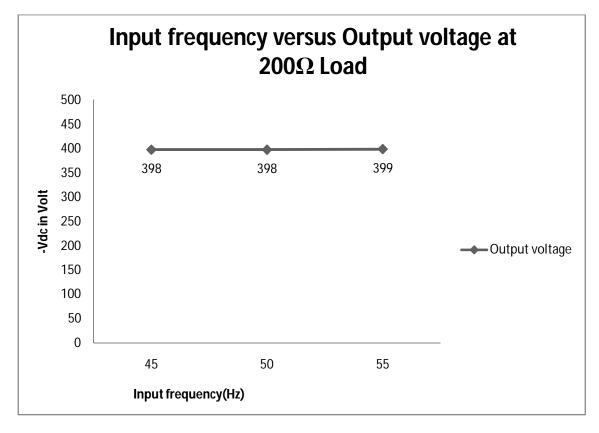

| 3.63: | Output voltage for $200\Omega$ load resistance and 45Hz input frequency                        | 105 |

| 3.64: | Output voltage for $200\Omega$ load resistance and 50Hz input frequency                        | 105 |

| 3.65: | Output voltage for $200\Omega$ load resistance and 55Hz input frequency     | 106 |

|-------|-----------------------------------------------------------------------------|-----|

| 3.66: | Output voltage at different input frequency and $400\Omega$ load resistance | 107 |

| 3.67: | Output voltage at different input frequency and $200\Omega$ load resistance | 107 |

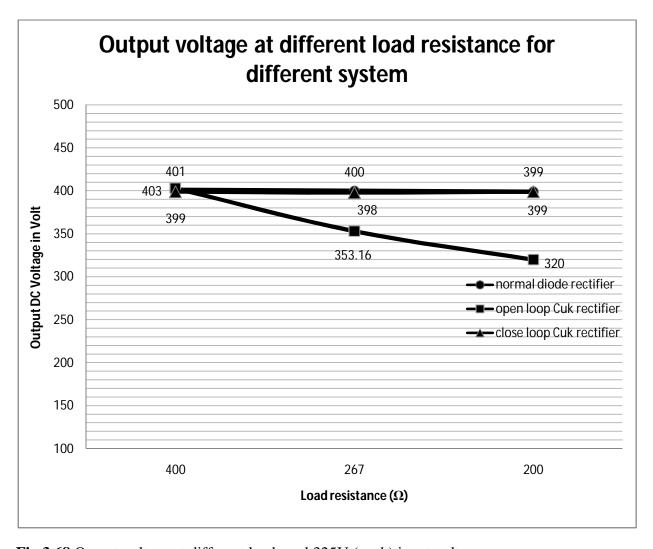

| 3.68: | Output voltage at different loads and 325V (peak) input voltage             | 108 |

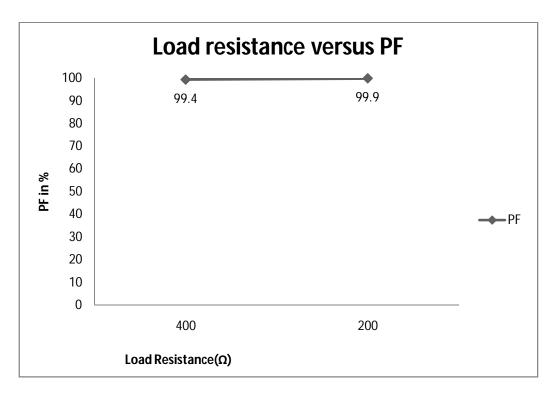

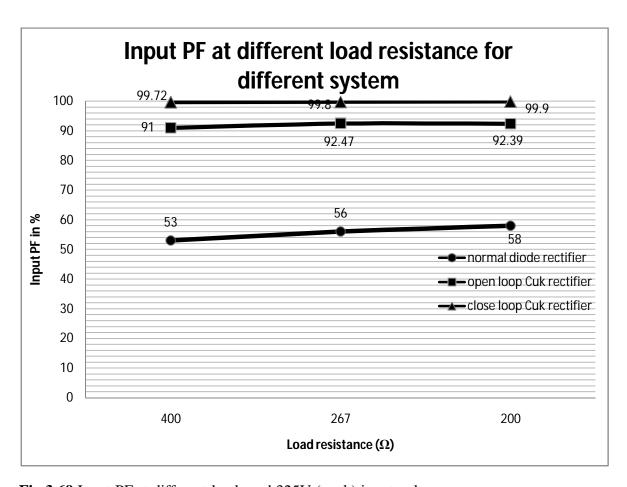

| 3.69: | Input PF at different loads and 325V (peak) input voltage                   | 109 |

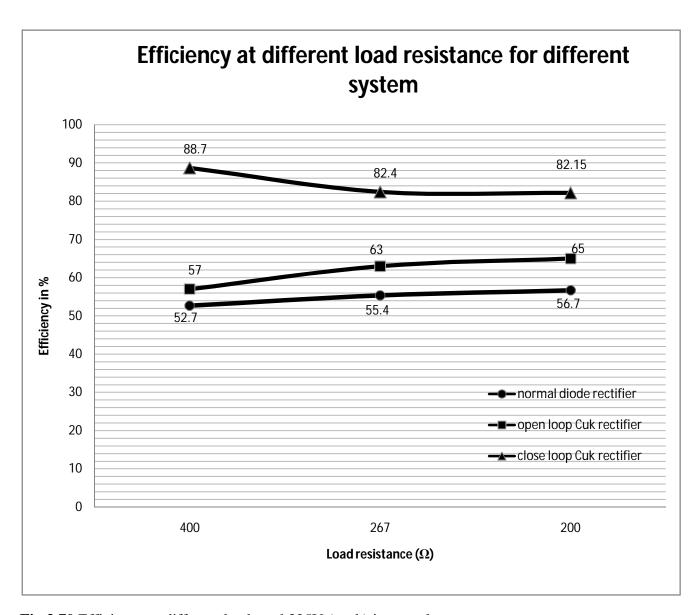

| 3.70: | Efficiency at different loads and 325V (peak) input voltage                 | 110 |

| 3.71: | Input current THD at different loads and 325V (peak) input voltage          | 111 |

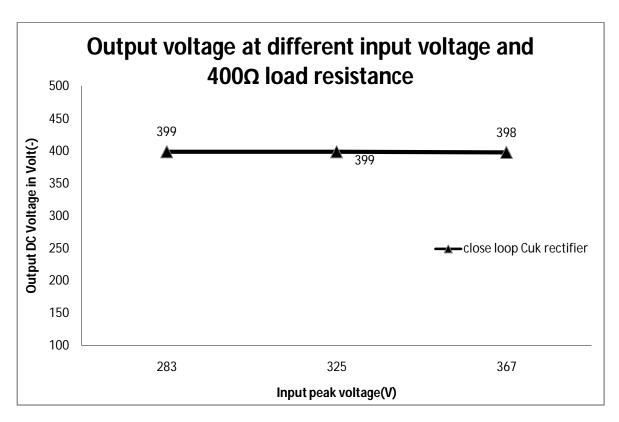

| 3.72: | Output voltage at different input voltages with $400\Omega$ load resistance | 112 |

# LIST OF TABLES

| Table No. | Title of table                                                                                                                                              | Page No. |

|-----------|-------------------------------------------------------------------------------------------------------------------------------------------------------------|----------|

| 1         | Microchip product feature and application                                                                                                                   | 3        |

| 2.1       | Data for $400\Omega$ to $200\Omega$ load resistance at 410V (peak) input voltage, 50Hz supply frequency and 400V reference output voltage                   | 13       |

| 2.2       | Data for $800\Omega$ to $200\Omega$ load resistance at $325V$ (peak) input voltage, $50Hz$ supply frequency and -400V reference output voltage              | 24       |

| 3.1       | ADC Module configuration                                                                                                                                    | 68       |

| 3.2       | PWM2 Module configuration                                                                                                                                   | 71       |

| 3.3       | Data for $800\Omega$ to $160\Omega$ load resistance at $325V$ (peak) input voltage, $50Hz$ supply frequency and -400V output voltage                        | 88       |

| 3.4       | Data for $400\Omega$ to $200\Omega$ load resistance at 283V (peak) input voltage, 50Hz supply frequency and -400V output voltage                            | 94       |

| 3.5       | Data for $400\Omega$ to $200\Omega$ load resistance at 367V (peak) input voltage, 50Hz supply frequency and -400V output voltage                            | 100      |

| 3.6       | Data for $400\Omega$ to $200\Omega$ load resistance at $325V$ (peak) input voltage, and different input supply frequency and -400V output voltage reference | 106      |

### LIST OF ABBREVIATION

SMPS = Switch mode power supply

MOSFET = Metal oxide semiconductor field effect transistor

PWM = Pulse Width Modulation

OPAMP = Operational Amplifier

rms = Root mean square

THD = Total Harmonic Distortion

PF = Power Factor

DSP = Digital signal processor

DSC = Digital signal controller

ADC = Analog to Digital Converter

PI = Proportional Integral

IGBT = Insulated Gate Bipolar Transistor

SSA = State Space Averaging

PFC = Power Factor Correction

MIPS = Million Instructions per Second

#### **ACKNOWLEDGEMENT**

I would like to express my sincere appreciation to my supervisor, Dr. Mohammad Jahangir Alam, Professor Department of Electrical and Electronic Engineering, BUET, Dhaka for his guidance, encouragement and continuous support.

I also extend my appreciation to **Professor Dr. Mohammad Ali Choudhury** Department of Electrical and Electronic Engineering, BUET for his valuable suggestion, comments and discussions. My thanks are to all staffs of BUET central Library and EEE departmental Library for their cooperation and material support.

Finally I acknowledge to my parents and my wife Naznin Akter for their constant inspiration towards the completion of this work.

#### **ABSTRACT**

Single phase rectifiers are commonly used in low and medium power application due to their low cost and ease of control. Rectifiers are non-linear in nature and draw non sinusoidal input current from the AC power sources. This causes a number of problems in sensitive electronics equipments and in the power distribution networks. Moreover it increases in reactive power drawn and reduce the input power factor. To reduce these problems switch mode regulated rectifiers are used. This thesis focuses on the study and digital implementation of a power factor correction (PFC) converter using close loop Ĉuk topology. This thesis work controls output voltage of a rectifier by inner current control based power factor correction (PFC). It provides high efficiency (more than 80%), less input current THD, nearly unity power factor and better output voltage regulation of AC-DC converter under variable input voltage, frequency and output load. Small signal model analysis is carried out through state space averaging technique and mathematical expression is developed for obtaining frequency response and checking the stability of the system. An algorithm is developed for digital implementation of proportional integral control. It presents a customized simulink model to represent the whole system and then an algorithm for digital implementation is developed. It also shows the real time simulation of simulink model through voltage sensor, current sensor and Digital signal controller. Finally real time C and assembly code for programming the Digital signal controller is presented.

#### **CHAPTER-1**

#### INTRODUCTION

#### 1.1 Introduction

Uses of Computer and telecommunications equipment have become important in our society. Electric vehicle is rapidly increasing in use due to its environment friendly technology. DC power supply is the heart of these devices. DC supplies of these mostly have come from AC supply. The efficiency, total harmonic distortion of input current, input power factor and regulated output voltage etc are the main concern of these AC-DC converters.

Uncontrolled diode rectifiers followed by L-C smoothing filters are widely used as a cheap power supply. Un-controlled charging of DC filter capacitor results in fifty hertz pulsed ac current waveform at the input of the rectifier. Several power quality problems arise at the source side, which includes poor power factor, high input current total harmonic distortion (THD), failure of transformers due to overheating and harmonic pollution on grid [1, 2] etc. Grid disturbances may result in malfunction or damage of electrical devices. Many methods for elimination of harmonic pollution in the power system are in use and new methods are being investigated. Restrictions on current and voltage harmonics are maintained in many countries through IEEE 519-1992 and IEC 61000-3-2/IEC 61000-3-4[3] standards. The restrictions are associated with the idea of "clean power". The power factor correction (PFC) converter topology using active wave shaping techniques can overcome the problem in line current. The PFC converter forces the line to draw near sinusoidal AC current in phase with its voltage.

#### 1.2 Background

Most of the single phase AC to DC conversion PFC works are done with Buck, Boost, and buck-boost or fly-back topologies [4-14] between the source and the load. Very few works are done with Ĉuk topology and the reported ones are based on open loop fixed duty cycle [15-19] control.

Regardless of the input line voltage and output load variations, input current drawn by the buck or buck-boost converter is always discontinuous [4-14]. The input current in Ĉuk converter is comparable to boost converter's input current [6]. Since in Boost topology large value capacitance is required to minimize the output voltage ripple therefore initial inrush current is higher than Ĉuk converter [20-21]. Ĉuk converters require low value intermediate capacitance to transfer energy to output capacitance and load [22-23].

As for applications, the Ĉuk converters is widely used in the industries such as wind energy [24], photovoltaic power system [24-27], electrical vehicle [27-28], radar transmission and receiving [29], light emitting diode driver [30], telecommunication systems [31], energy harvesting from exercise bicycles [32], and compressor and motor controllers [33-34].

Open loop Ĉuk topology provides ripple and variation in output voltage and also phase differences between input voltage and input current under variable input voltage [15-19, 35-37]. In this thesis work output voltage and input current control variable duty cycle Ĉuk converter has been proposed for minimizing output voltage variation due to line voltage and load change and obtaining near sinusoidal AC mains current.

#### 1.3 Brief Review of the Digital Signal controller

Digital signal controller (DSC) is widely used in the motor control, inverter, converter and many embedded systems because of its ability to handle deterministic operation and deal with interruptions, and its strong computation ability.

As the technology advances, the cost continues to drop and more and more functionalities have been integrated. Analog-to-digital converter (ADC) and pulse-width-modulation (PWM) are standard for most motor control-oriented DSC.

Currently DSCs are being marketed as green technologies for their potential to reduce power consumption in electric motors and power supplies. In order of market share, the top three DSC vendors are <u>Texas Instruments</u>, <u>Freescale</u>, and <u>Microchip Technology</u>, according to market research firm Forward Concepts 2007. These three companies dominate the DSC market, with

other vendors such as Infineon and Renesas taking a smaller slice of the pie. Table 1 shows current DSC Microchip product feature and application [39].

Table 1 Microchip product feature and application

| Table 1 Microchip product feature and application             |                                                                                                                                                                                                                                                                                                                                                                       |  |  |  |  |

|---------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

| Enabling Features of the microchip                            | Applications                                                                                                                                                                                                                                                                                                                                                          |  |  |  |  |

| dsPIC DSC                                                     |                                                                                                                                                                                                                                                                                                                                                                       |  |  |  |  |

| - 1612                                                        | ATTACON CONTRACTOR OF A CONTRACTOR OF                                                                                                                                                                                                                                                                                                                                 |  |  |  |  |

| • 16 bit operation                                            | •Heating, ventilation and air conditioning                                                                                                                                                                                                                                                                                                                            |  |  |  |  |

| • 1 or 2 fault pins                                           | Absolute encoders and resolvers                                                                                                                                                                                                                                                                                                                                       |  |  |  |  |

| • 28-, 40-, 64-, 80- and 100-pin variants                     | • Blowers and lawn equipment                                                                                                                                                                                                                                                                                                                                          |  |  |  |  |

| • 6 or 8 motor PWM output                                     | •Electronic Power Steering                                                                                                                                                                                                                                                                                                                                            |  |  |  |  |

| • Complementary or independent PWM                            | •Industrial gate openers                                                                                                                                                                                                                                                                                                                                              |  |  |  |  |

| Center-aligned or edge-aligned PWM                            | •Seat belt tensioners                                                                                                                                                                                                                                                                                                                                                 |  |  |  |  |

| <ul> <li>A/D sampling synchronized to PWM cycle</li> </ul>    | •Exercise equipment                                                                                                                                                                                                                                                                                                                                                   |  |  |  |  |

| • 10-bit, 1 to 2.2 Msps A/D converter                         | •Washing machines                                                                                                                                                                                                                                                                                                                                                     |  |  |  |  |

| • 2, 4 or 8 simultaneous A/D samples                          | •Sewing machines                                                                                                                                                                                                                                                                                                                                                      |  |  |  |  |

| • 5V native operation for noisy environments                  | •Industrial pumps                                                                                                                                                                                                                                                                                                                                                     |  |  |  |  |

| (dsPIC30F)                                                    | •Stability control                                                                                                                                                                                                                                                                                                                                                    |  |  |  |  |

| • On-chip Quadrature Encoder Interface (QEI)                  | •Power tools                                                                                                                                                                                                                                                                                                                                                          |  |  |  |  |

| <ul> <li>Motor control algorithm reference designs</li> </ul> | Refrigeration                                                                                                                                                                                                                                                                                                                                                         |  |  |  |  |

| • Up to 2 programmable dead time settings                     | Printing machines                                                                                                                                                                                                                                                                                                                                                     |  |  |  |  |

| <ul> <li>One or two CAN/ECAN 2.0B modules</li> </ul>          | •Power and environment monitor in servers                                                                                                                                                                                                                                                                                                                             |  |  |  |  |

| <ul> <li>LIN support through UART and software</li> </ul>     | •Power management for equipment                                                                                                                                                                                                                                                                                                                                       |  |  |  |  |

| • SPITM, I2CTM and UART communication                         | •Circuit breakers                                                                                                                                                                                                                                                                                                                                                     |  |  |  |  |

| ports                                                         | •Arc fault detection                                                                                                                                                                                                                                                                                                                                                  |  |  |  |  |

| <ul> <li>Visual design guide motor control GUI</li> </ul>     | •Auxiliary power unit                                                                                                                                                                                                                                                                                                                                                 |  |  |  |  |

| (MPLAB plug-in)                                               | •Electric vehicles                                                                                                                                                                                                                                                                                                                                                    |  |  |  |  |

| • 8 channel DMA controller                                    | • AC to DC converters                                                                                                                                                                                                                                                                                                                                                 |  |  |  |  |

| • 40 MIPS @3.3V                                               | •DC to DC converters                                                                                                                                                                                                                                                                                                                                                  |  |  |  |  |

| • -40° to 85°C (extended temp. planned)                       | •Power factor correction                                                                                                                                                                                                                                                                                                                                              |  |  |  |  |

|                                                               | •Inverters                                                                                                                                                                                                                                                                                                                                                            |  |  |  |  |

| • Data EEPROM emulation in Program Flash                      | Online UPS                                                                                                                                                                                                                                                                                                                                                            |  |  |  |  |

|                                                               | •Welding machines                                                                                                                                                                                                                                                                                                                                                     |  |  |  |  |

|                                                               |                                                                                                                                                                                                                                                                                                                                                                       |  |  |  |  |

|                                                               |                                                                                                                                                                                                                                                                                                                                                                       |  |  |  |  |

|                                                               |                                                                                                                                                                                                                                                                                                                                                                       |  |  |  |  |

|                                                               |                                                                                                                                                                                                                                                                                                                                                                       |  |  |  |  |

|                                                               | • Electronic power steering                                                                                                                                                                                                                                                                                                                                           |  |  |  |  |

|                                                               |                                                                                                                                                                                                                                                                                                                                                                       |  |  |  |  |

|                                                               |                                                                                                                                                                                                                                                                                                                                                                       |  |  |  |  |

|                                                               | ž .                                                                                                                                                                                                                                                                                                                                                                   |  |  |  |  |

|                                                               |                                                                                                                                                                                                                                                                                                                                                                       |  |  |  |  |

|                                                               |                                                                                                                                                                                                                                                                                                                                                                       |  |  |  |  |

|                                                               |                                                                                                                                                                                                                                                                                                                                                                       |  |  |  |  |

|                                                               | 1                                                                                                                                                                                                                                                                                                                                                                     |  |  |  |  |

| (MPLAB plug-in) • 8 channel DMA controller                    | <ul> <li>Electric vehicles</li> <li>AC to DC converters</li> <li>DC to DC converters</li> <li>Power factor correction</li> <li>Inverters</li> <li>Online UPS</li> <li>Welding machines</li> <li>Electrically assisted hydraulic steering</li> <li>Electronic clutch and gearboxes</li> <li>Roll and stability controllers</li> <li>Seat belt pretensioners</li> </ul> |  |  |  |  |

The Texas product TMS320C28x generation of digital signal controllers is the industry's first 32-bit DSP-based controllers with on-board Flash memory and performance up to 150 MIPS. They target industrial control, optical networking, and automotive control applications. The C28x core is a high performance control optimized controller and offers up to 150 MIPS of computational bandwidth to handle numerous sophisticated control algorithms in real-time, such as sensorless speed control, random PWM, and power factor correction[40]. Due to rapid advances of Digital signal controller and lower cost it is better to use it in PFC controller implementation as an alternative of analog circuit for getting more reliable and high performance.

#### 1.4 Goal of Thesis

The goal of this thesis is to design the control strategy of a single phase AC to DC converter using close loop ĈUK topology which will ensure high power factor, less input current THD, high efficiency and regulated DC voltage for variable line voltage, frequency and load. Matlab simulink is to be used to analyze the result and performance. Finally real time program algorithm is to be designed for digital implementation and its effectiveness will be evaluated through Proteus software.

#### 1.5 Thesis Organization

Chapter-1 is the introduction to this thesis, and provides a summary of the background of AC-DC converter and Digital signal controller. This chapter also includes the objective of the thesis work.

Chapter-2 surveys the performance of full bridge diode rectifier and open loop Ĉuk rectifier by considering efficiency, input current THD, PF and output voltage regulation. This chapter deals with the goal of this thesis work and provides detail description of Close loop Ĉuk based AC-DC converter. It presents the Matlab simulink model of proposed system and simulation result. It provides customized user friendly simulink model to reduce the system complexity and quick parameters changing option. It also presents a mathematical model for stability analysis using bode plot of outer voltage loop and inner current loop. The small signal transfer function for Ĉuk converter through state space averaging technique is described in this chapter.

Chapter-3 describes the real time program algorithm for digital implementation, analog to digital conversion, PWM generation and complete circuit diagram for mixed signal (Analog and digital) simulation. This chapter includes the performance result, graphical simulation under the variable input voltage, input frequency and output load. The chapter also provides the relative performance comparison of full bridge diode rectifier, open loop Ĉuk rectifier and proposed close loop Ĉuk rectifier.

Chapter-4 concludes the thesis with summary and suggestion of future work. Real time program mixing with C and Assembly language has been given in Appendix and also Matlab program is given in Appendix for stability analysis.

### **CHAPTER-2**

# CONVENTIONAL AND ĈUK OPEN/CLOSED LOOP SINGLE PHASE ACDC RECTIFIER

#### 2.1 Full bridge Diode rectifier

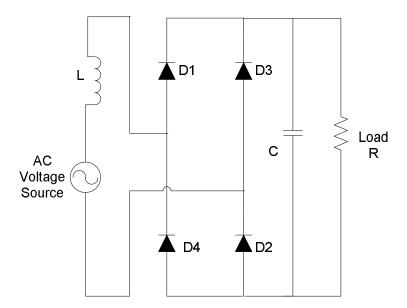

Full wave diode rectifier is versatile and is used AC to DC converter. It's efficiency and input power factor are low with high input current THD. Since it is uncontrolled rectifier so output voltage varies with change of input voltage and load. Fig. 2.1 shows a full bridge diode rectifier based AC-DC converter.

Fig 2.1 AC to DC converter using Full bridge Diode rectifier

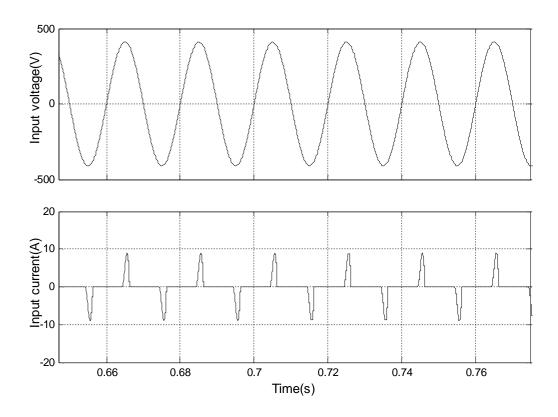

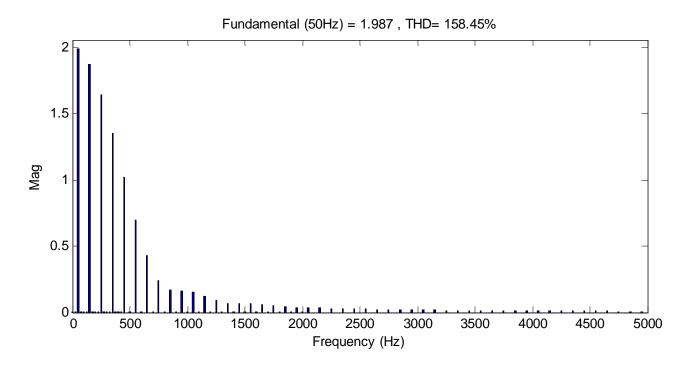

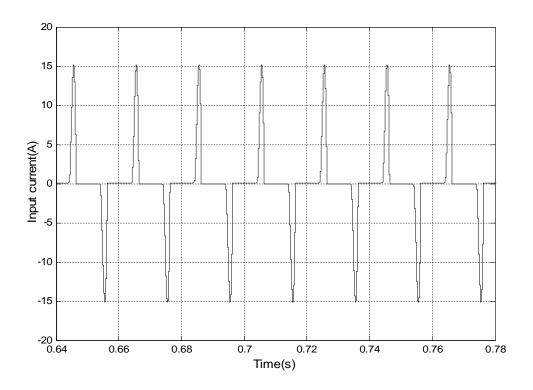

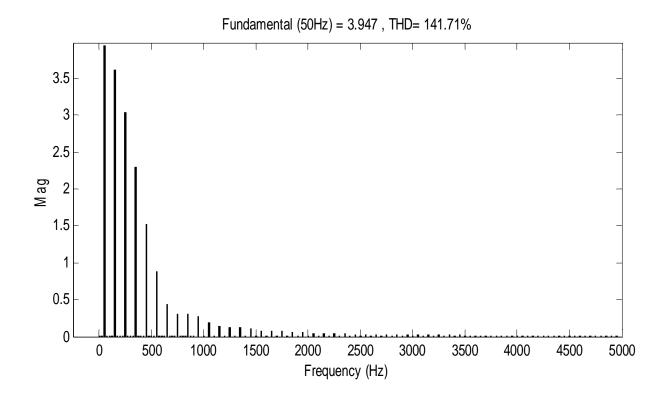

L= 1mH and C= 1000uF are used for simulation. Fig. 2.2 to Fig. 2.4 show input voltage/current, FFT component and output voltage respectively for 400V reference output voltage at 400 $\Omega$  load resistance, 410V (peak) input voltage and 50Hz supply frequency. Similarly Fig. 2.5 to Fig. 2.7 for 267 $\Omega$  load resistance and Fig. 2.8 to Fig. 2.10 for 200 $\Omega$  load resistance. Fig. 2.11 to Fig. 2.13 show the output voltage for different input voltages and 400 $\Omega$  load resistance.

Fig 2.2 Input current and input voltage for  $400\Omega$  load resistance

Fig 2.3 FFT component of input current for  $400\Omega$  load resistance and 410V (peak) input voltage.

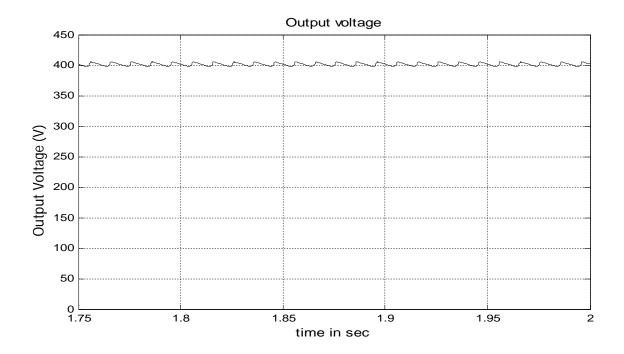

Fig 2.4 Output voltage for  $400\Omega$  load resistance and 410V (peak) input voltage.

Fig 2.5 Input current for  $267\Omega$  load resistance and 410V (peak) input voltage.

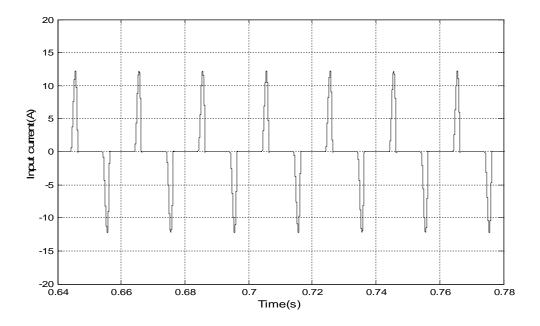

Fig 2.6 FFT component of input current for  $267\Omega$  load resistance and 410V (peak) input voltage.

Fig 2.7 Output voltage for  $267\Omega$  load resistance and 410V (peak) input voltage.

Fig 2.8 Input current for  $200\Omega$  load resistance and 410V (peak) input voltage.

Fig 2.9 FFT component of input current for  $200\Omega$  load resistance and 410V (peak) input voltage.

Fig 2.10 Output voltage for  $200\Omega$  load resistance and 410V (peak) input voltage.

Fig 2.11 Output voltage for  $400\Omega$  load resistance and 325V (peak) input voltage

Fig 2.12 Output voltage for  $400\Omega$  load resistance and 282.8V (peak) input voltage

Fig 2.13 Output voltage for  $400\Omega$  load resistance and 368V (peak) input voltage

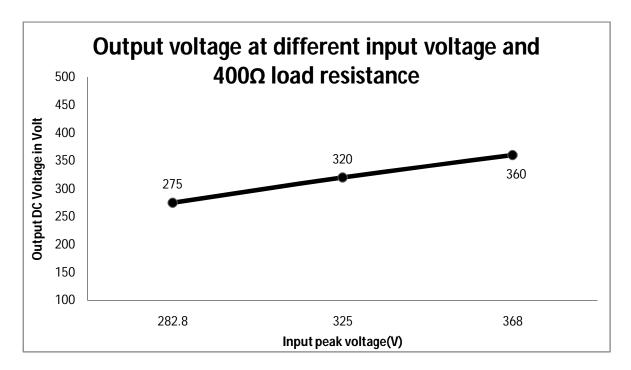

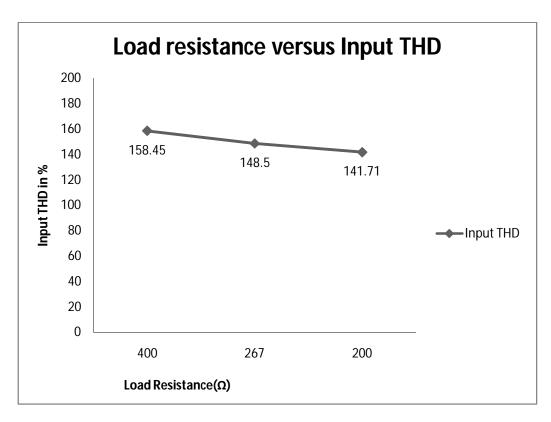

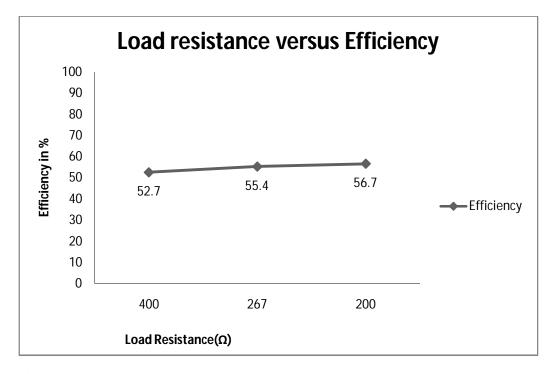

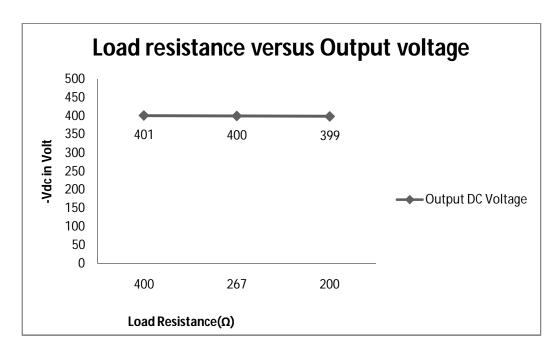

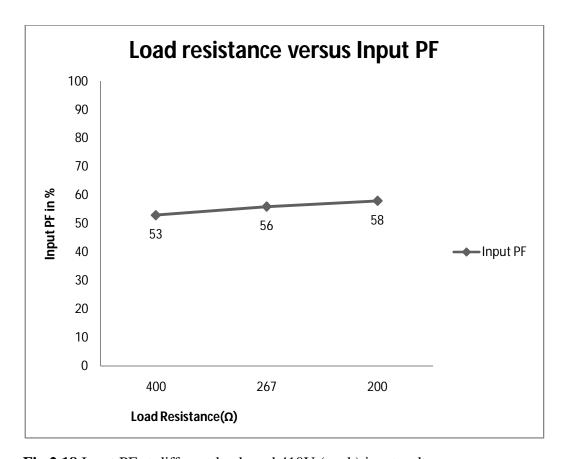

Table 2.1 summarizes the result from Fig. 2.2 to Fig. 2.10. Fig. 2.14 shows the output voltage at different input voltage. Fig. 2.15 to Fig. 2.18 show the input current THD, efficiency, output voltage and input power factor respectively for different load.

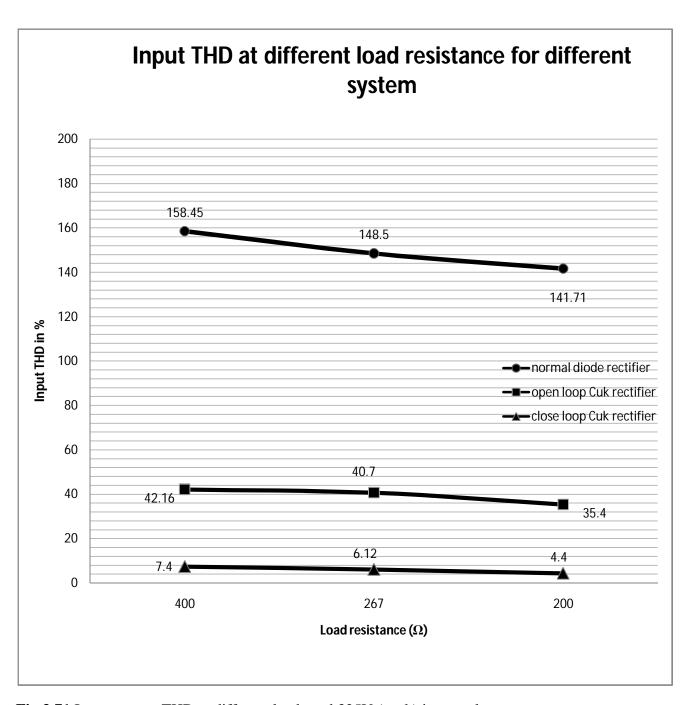

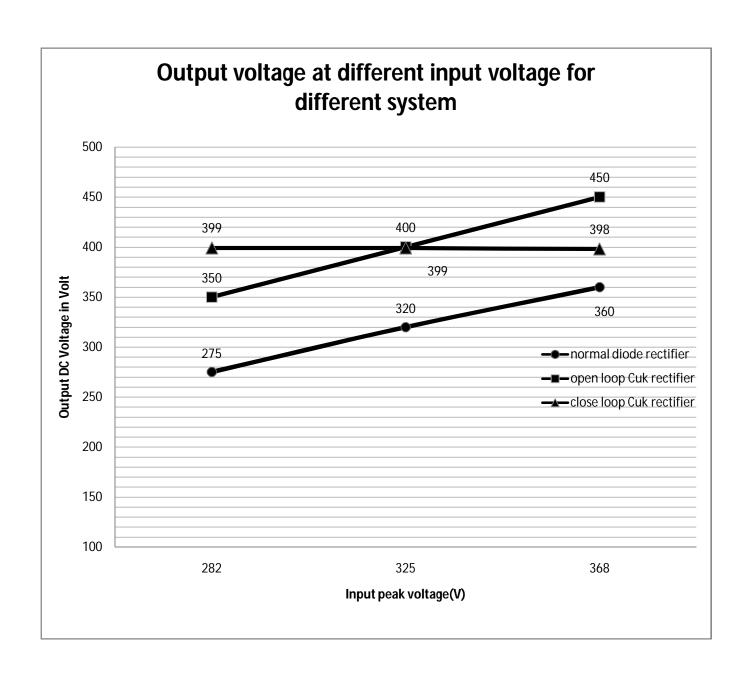

**Table 2.1:** Data for  $400\Omega$  to  $200\Omega$  load resistance at 410V (peak) input voltage, 50Hz supply frequency and 400V reference output voltage

| Resistive | Input rms  | Input rms  | Output     | Load    | Input  | Input | Efficiency |

|-----------|------------|------------|------------|---------|--------|-------|------------|

| load in   | current(A) | Voltage(V) | DC         | current | THD    | PF    | In %       |

| Ohm       |            |            | voltage(V) | (A)     | in %   |       |            |

| 400       | 2.63       | 290        | 401        | 1       | 158.45 | 0.53  | 52.7       |

| 267       | 3.75       | 290        | 400        | 1.5     | 148.5  | 0.56  | 55.4       |

| 200       | 4.84       | 290        | 399        | 2       | 141.71 | 0.58  | 56.7       |

Fig 2.14 Output voltage at different input voltages with  $400\Omega$  load resistance.

Fig 2.15 Input THD at different loads and 410V (peak) input voltage.

Fig 2.16 Efficiency at different loads and 410V (peak) input voltage.

Fig 2.17 Output voltage at different loads and 410V (peak) input voltage.

Fig 2.18 Input PF at different loads and 410V (peak) input voltage.

### 2.2 Open loop Ĉuk AC-DC converter

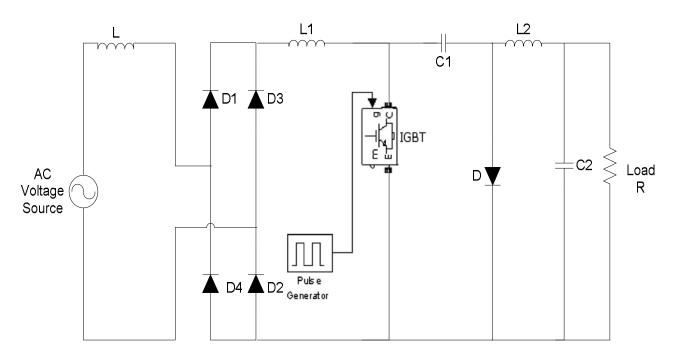

The circuit arrangement of the open loop Ĉuk regulator [10] is shown in Fig. 2.19. It provides an output voltage that is less than or greater than the input voltage and of opposite polarity from its input voltage. The circuit operation can be divided into two modes. Mode-1 is shown in Fig. 2.20 begins when transistor (IGBT) is turned on. The current through inductor L1 rises. At the same time the voltage of capacitor C1 reverse biases diode D and turns it off. The capacitor C1 discharges its energy to the circuit formed by C1, C2, the load and L2. Mode-2 is shown in Fig. 2.21 begins when transistor (IGBT) is turned off. The current through inductor L1 falls. The capacitor C1 is charged from the input supply and the energy stored in the inductor L2 is transferred to the load. The diode D and transistor (IGBT) provide a synchronous switching action. The capacitor C1 is the medium for transferring energy from the source to the load.

Fig 2 .19 Open loop Ĉuk regulator based full bridge single phase rectifier

Fig 2 .20 Mode-1 when Switch is closed

Fig 2 .21 Mode-2 when Switch is opened

The ideal input/output voltage and current relations are defined by the following equations [22]

$$V_{out} = -\frac{kV_{in}}{1-k} (2.1)$$

$$I_{out} = \frac{(1-k)I_{in}}{k} \tag{2.2}$$

Where,

k is the duty cycle =

$$\frac{T_{on}}{T}$$

$T_{on}$  = on time of the switch

$T_{\text{off}} = \text{off time of the switch}$

$T = T_{on} + T_{off} = period of the switch$

$V_{in}$  = Average value of the input rectified AC voltage

$V_{out}$  = Output voltage across the load

$I_{in}$  = input current through the inductor and  $I_{out}$  = output current through the load

The condition for continuous inductor current and capacitor voltage is given by the following equation [22]

$$L1 = \frac{(1-k)^2 R}{2kf}$$

(2.3)

$$L2 = \frac{(1-k)R}{2f}... (2.4)$$

$$C1 = \frac{k}{2fR} \tag{2.5}$$

$$C2 = \frac{k}{8fR} \tag{2.6}$$

Where,

f = Switching frequency and R= Load resistance

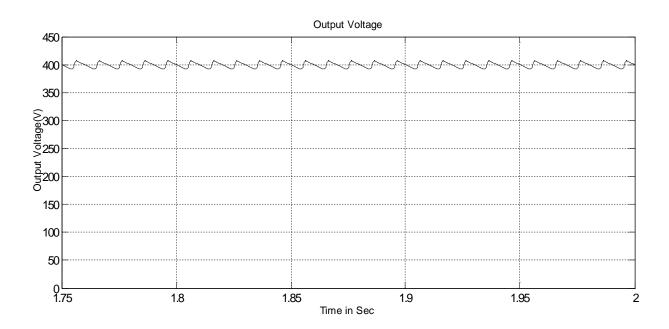

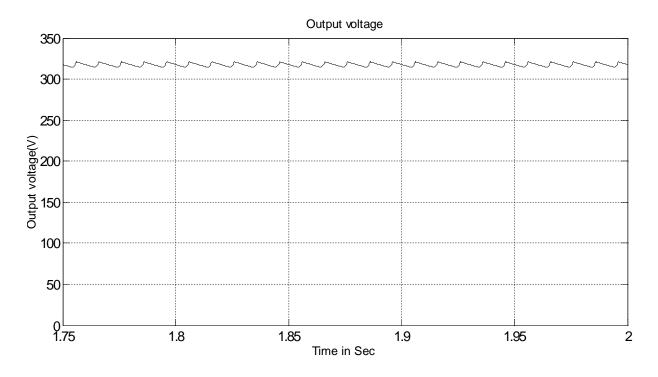

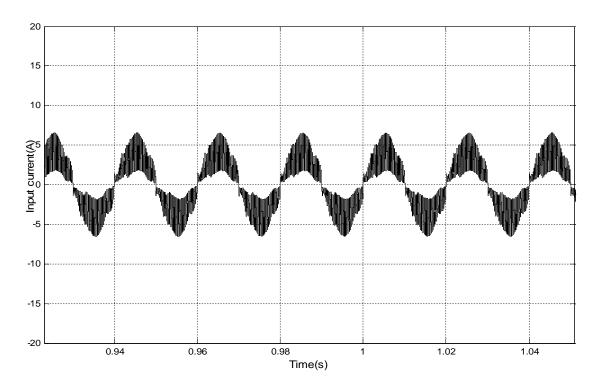

Fig. 2.22 to Fig. 2.35 are obtained for f=80000Hz, k=0.65, L=100uH, L1=10mH, L2=1.8mH, C1=0.1uF, C2=2000uF. Fig. 2.22 to Fig. 2.24 show input voltage/current, FFT component and output voltage respectively for -400V reference output voltage at  $400\Omega$  load resistance and 410V

(peak) input voltage and 50Hz supply frequency using open loop  $\hat{C}uk$  rectifier. Similarly Fig. 2.25 to Fig. 2.27 for  $800\Omega$  load resistance, Fig. 2.28 to Fig. 2.30 for  $267\Omega$  load resistance and Fig. 2.31 to Fig. 2.33 for  $200\Omega$  load resistance. Fig. 2.34 to Fig. 2.35 show the output voltage for  $400\Omega$  load resistance and different input voltages.

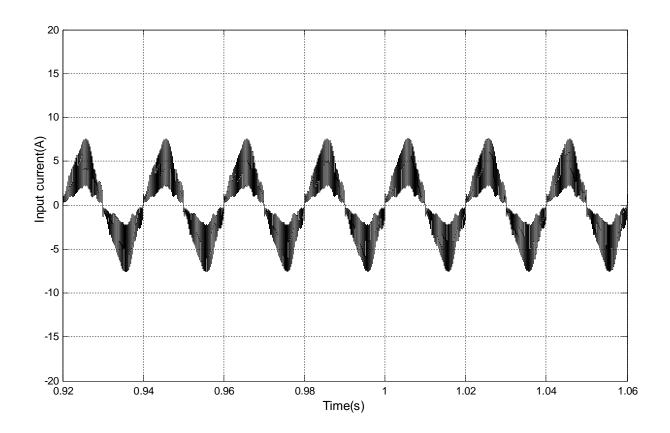

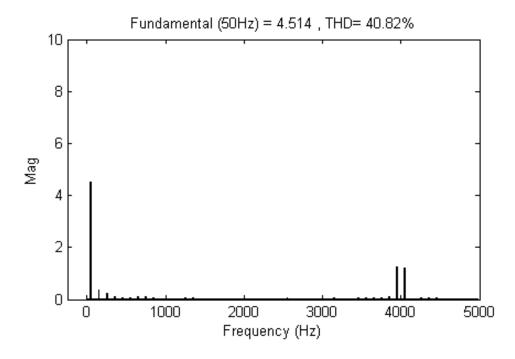

Fig 2.22 Input current for  $400\Omega$  load resistance and 325V (peak) input voltage

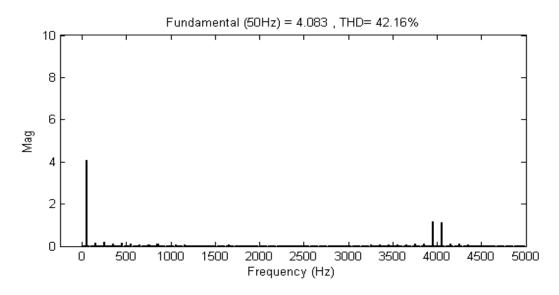

Fig 2.23 FFT component of input current for  $400\Omega$  load resistance and 325V(peak) input voltage

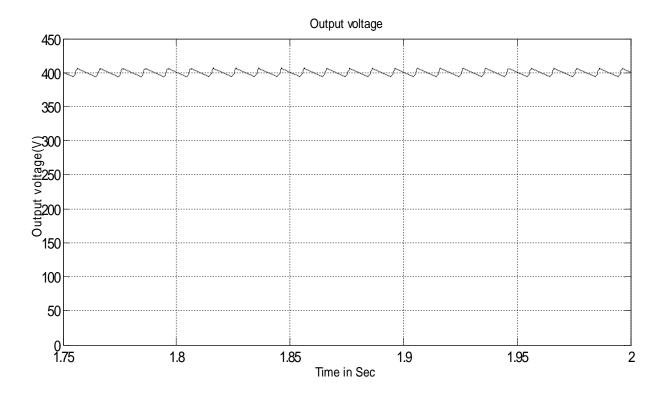

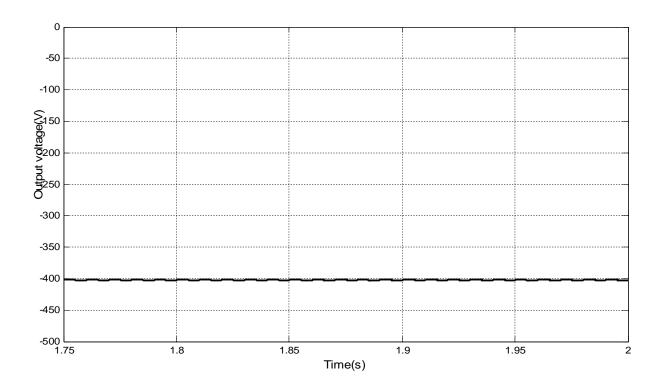

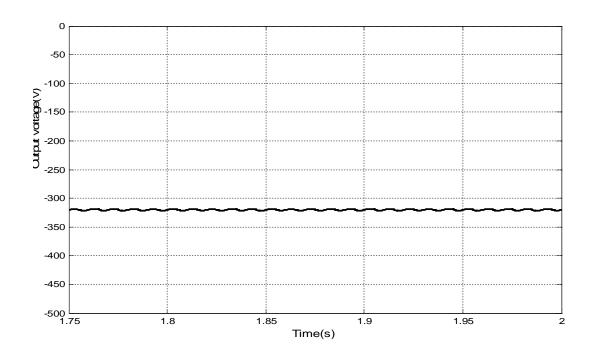

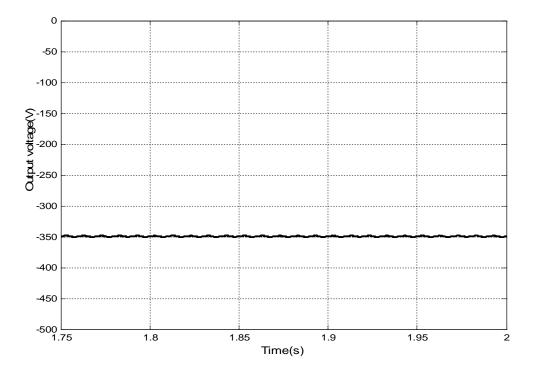

Fig 2.24 Output voltage for  $400\Omega$  load resistance and 325V (peak) input voltage

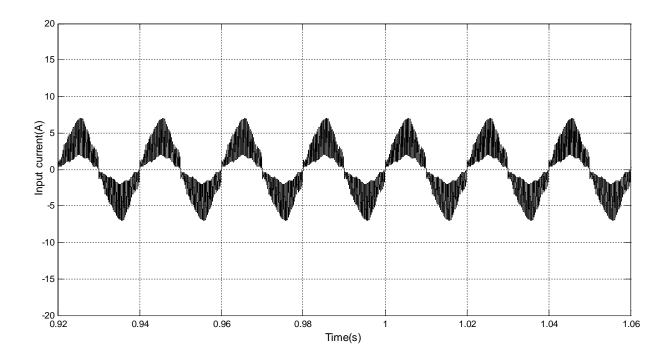

Fig 2.25 Input current for 267 $\Omega$  load resistance and 325V (peak) input voltage

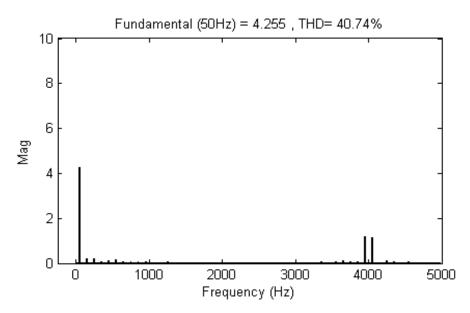

Fig 2.26 FFT component of input current for  $267\Omega$  load resistance and 325V(peak) input voltage

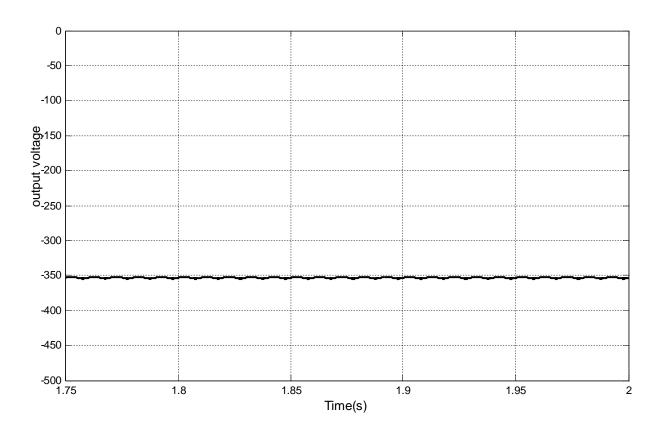

Fig 2.27 Output voltage for  $267\Omega$  load resistance and 325V (peak) input voltage

Fig 2.28 Input current for  $200\Omega$  load resistance and 325V (peak) input voltage

Fig 2.29 FFT component of input current for  $200\Omega$  load resistance and 325V(peak) input voltage

Fig 2.30 Output voltage for  $200\Omega$  load resistance and 325V (peak) input voltage

Fig 2.31 Output voltage for  $400\Omega$  load resistance and 282.8V (peak) input voltage

Fig 2.32 Output voltage for  $400\Omega$  load resistance and 367.69V (peak) input voltage

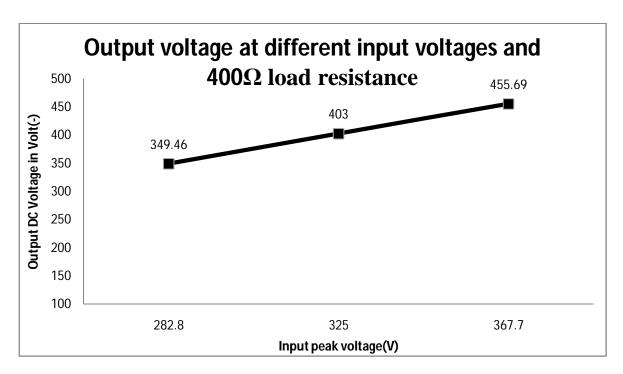

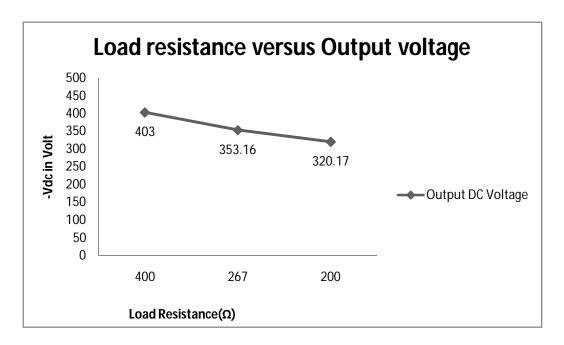

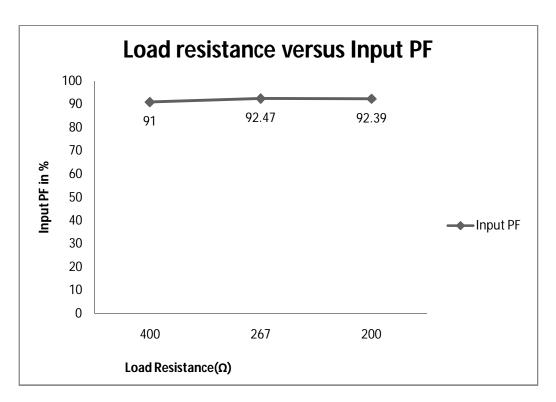

Table 2.2 summarizes the result from Fig. 2.22 to Fig. 2.30. Fig. 2.33 shows the output voltage at different input voltage. Fig. 2.34 to Fig. 2.37 show the output voltage, Input power factor, input current THD and efficiency respectively for different load.

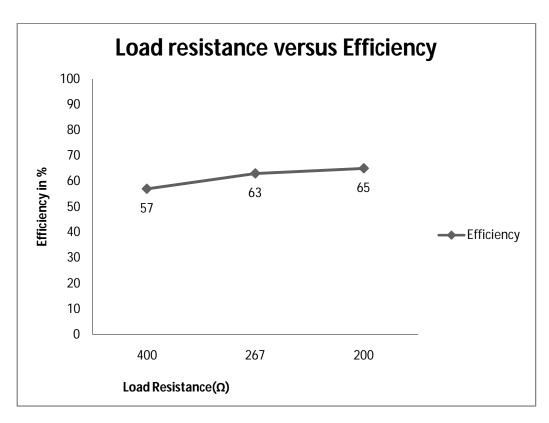

**Table 2.2:** Data for  $800\Omega$  to  $200\Omega$  load resistance at 325V (peak) input voltage, 50Hz supply frequency and -400V reference output voltage

| Resistive | Input rms  | Input rms  | Output     | Load    | Input | Input  | Efficiency |

|-----------|------------|------------|------------|---------|-------|--------|------------|

| load in   | current(A) | Voltage(V) | DC         | current | THD   | PF     | In %       |

| Ohm       |            |            | voltage(V) | (A)     | in %  |        |            |

| 400       | 3.13       | 230        | 403        | 1.01    | 42.16 | 0.91   | 57         |

| 267       | 3.25       | 230        | 353.16     | 1.32    | 40.74 | 0.9247 | 63         |

| 200       | 3.45       | 230        | 320.17     | 1.60    | 40.82 | 0.9239 | 65         |

Fig 2.33 Output voltage at different input voltage with  $400\Omega$  load resistance.

Fig 2.34 Output voltage at different load and 325V (peak) input voltage.

Fig 2.35 Input PF at different load and 325V (peak) input voltage.

Fig 2.36 Input THD at different load and 325V (peak) input voltage.

Fig 2.37 Efficiency at different load and 325V (peak) input voltage.

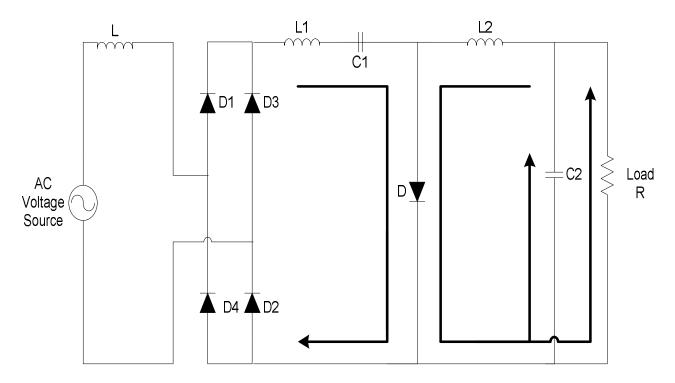

## 2.3 Proposed close loop Ĉuk AC-DC converter

## 2.3.1 Close loop Ĉuk AC-DC converter

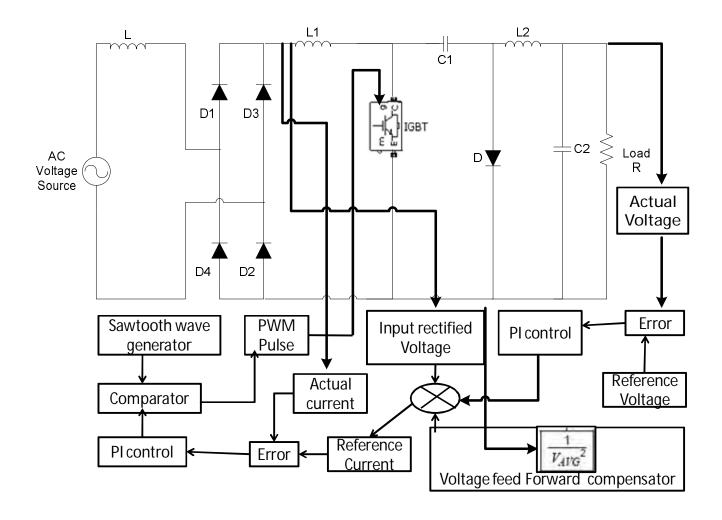

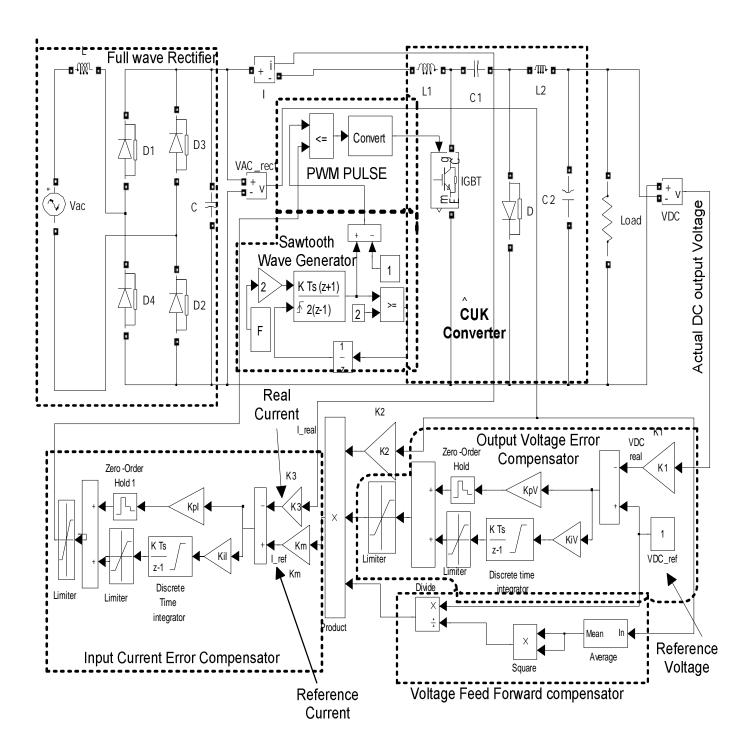

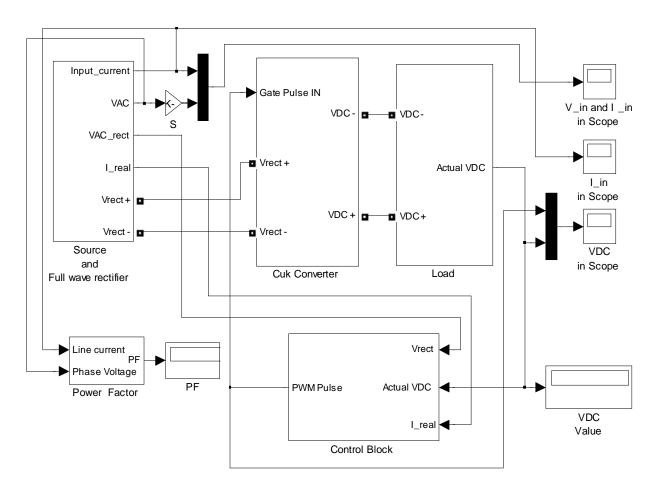

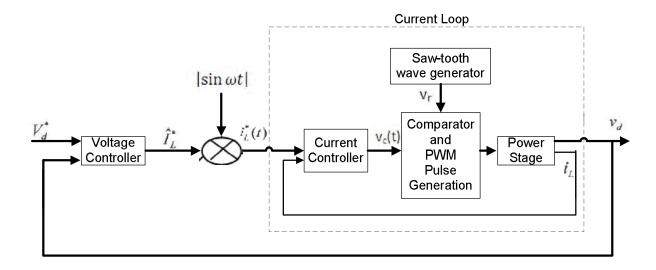

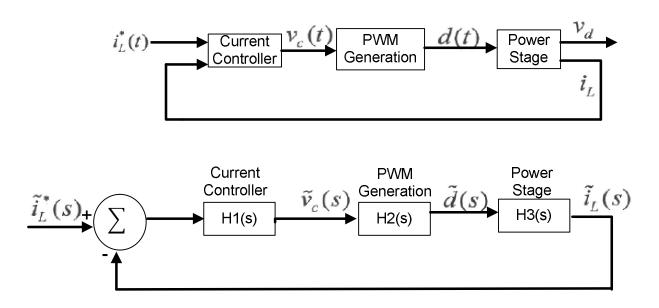

From the previous chapter we have seen that both Normal diode rectifier and open loop Ĉuk rectifier have the problem of output voltage variation due to its input voltage changes, Low power factor and higher input THD. To minimize this problem and obtain better performance close loop Ĉuk regulator based AC-DC converter which is shown in Fig. 2.38 is proposed. The technique used here is the Average Current Mode control. In Average Current Mode control, the output voltage is controlled by varying the average value of the current amplitude signal. The output voltage is controlled by the output voltage error compensator and input current is controlled by the input current error compensator. The Voltage feed forward compensator controls the input voltage variation in such way that if the input voltage reduces then the output of Voltage feed forward compensator increases and vice versa. The actual output DC voltage is sensed and compared with a reference voltage then the voltage error is processed through the proportional integral controller. The output of the proportional integral controller is multiplied with the rectified input voltage and output of voltage feed forward compensator to make a reference current in phase with rectified input voltage. The real current is forced to track the reference current through current error compensator. The error between the actual current and reference current is processed through the proportional integral controller and then its output is compared with the Saw-tooth wave to generate the required PWM signal. Matlab simulink presentation of the proposed system is shown in Fig. 2.39. Fig. 2.40 to Fig. 2.44 show the customized matlab simulink block presentation of the proposed system.

Fig 2.38 Proposed close loop ĈUK regulator based AC-DC converter.

Fig 2.39 Proposed close loop ĈUK AC-DC converter in Matlab simulink.

Fig 2.40 Customized representation of proposed close loop ĈUK AC-DC converter in Matlab simulink

Fig 2.41 Input parameter of source and Full wave rectifier

Fig 2.42 Input parameter of  $\hat{C}uk$  Converter

Fig 2.43 Input parameter of load block

Fig 2.44(a) Input parameter of control block

Fig 2.44(b) Input parameter of control block

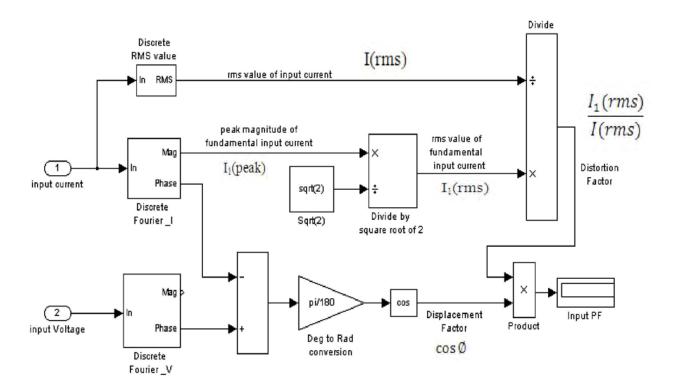

Since Matlab has no block to determine power factor directly. Fig. 2.45 shows the way to determine the power factor.

We know the Power factor = Displacement Factor  $\times$  Distortion Factor

Where Displacement Factor =  $\cos \emptyset$

And Distortion Factor =

$$\sqrt{\frac{1}{1 + (\frac{I_2}{I_1})^2 + (\frac{I_3}{I_1})^2 + \dots + (\frac{I_n}{I_1})^2}} = \frac{I_1}{I} = \frac{1}{\sqrt{1 + THD^2}}$$

Here Ø is the angle between the fundamental component of input current and input voltage

$I_2, I_3 \dots I_n$  are the harmonics component of input current

I is the rms value of input current and  $I_1$  is the rms value of fundamental component of input current

Efficiency is calculated in the following way

$$Efficiency = \frac{\textit{Output power}}{\textit{input apparent power}} = \frac{\frac{\textit{output voltage}^2}{\textit{load resistance}}}{\textit{input rms voltage} \times \textit{input rms current}}$$

Fig 2.45 Determination of power factor in matlab simulink

# 2.3.2 Close loop response analysis of AC –DC Ĉuk converter using State space Averaging Technique

For analysis the stability of the proposed control system using bode plot open loop transfer function is needed. For continuous conduction mode (CCM), dc-dc converters operate in two circuit states in one switching period, (i) when switch is on for a time interval dT and (ii) when switch is off for a time interval (1-d) T, where d is a duty cycle and T is switching period. According to Leverrier.s Algorithm modeling of dc-dc converters using SSA method needs three steps in general as discussed below.

a. During each circuit state, the linear circuit is described by the state variable vector x. Generally inductor currents and Capacitor voltages are chosen as state variables. The state space equations of two circuit states, in standard form, are obtained as

When switch is on during time interval dT, state-space equations of converter can be written as

$$\frac{dx(t)}{dt} = A_1 x(t) + B_1 u(t) \text{ and}$$

$$y(t) = C_1 x(t) + E_1 u(t)$$

.....(2.7)

The matrices  $A_1$ ,  $B_1$ ,  $C_1$  and  $E_1$  describe the network connections during the time interval dT x(t), u(t) and y(t) are the state variable, input variable and output variable respectively.

When switch is off during time interval (1-d)T, state-space equations of converter can be written as

$$\frac{dx(t)}{dt} = A_2 x(t) + B_2 u(t) \text{ and}$$

$$y(t) = C_2 x(t) + E_2 u(t)$$

....(2.8)

The matrices A<sub>2</sub>, B<sub>2</sub>, C<sub>2</sub> and E<sub>2</sub> describe the network connections during the time interval 1(-d)T

b. Equation (2.7) and (2.8) are time weighted and averaged over one switching period as

$$\frac{dx(t)}{dt} = A_{12}x(t) + B_{12}u(t)$$

and

$$y(t) = C_{12}x(t) + E_{12}u(t)$$

....(2.9)

Where

$$A_{12} = A_1 d + A_2 (1 - d)$$

$$B_{12} = B_1 d + B_2 (1 - d)$$

$$C_{12} = C_1 d + C_2 (1 - d)$$

$$E_{12} = E_1 d + E_2 (1 - d)$$

c. Now Linearization by introducing small ac perturbation around a DC operating point. To obtain a small signal ac model around a quiescent operating point, the following small perturbation as shown in equation (2.10) is added to state space model represented by equation (2.9),

$$\mathbf{x}(\mathbf{t}) = \mathbf{X} + \tilde{\mathbf{x}}(\mathbf{t})$$

$$y(t) = Y + \tilde{y}(t)$$

$$\mathbf{u}(\mathbf{t}) = \mathbf{U} + \tilde{u}(t)$$

$$d(t) = D + \tilde{d}(t)$$

....(2.10)

The capital letter represents a DC value. Small signal linearization is justified under the following condition

$$X > \tilde{x}(t)$$

$$Y > \tilde{y}(t)$$

$$U > \tilde{u}(t)$$

$$D > \tilde{d}(t)$$

Now replacing equation (2.10) in equation (2.9) we can get small signal state space model [41] as

$$\frac{d\tilde{x}(t)}{dt} = A\tilde{x}(t) + B\tilde{u}(t) + B_d\tilde{d}(t)$$

$$\tilde{y}(t) = C\tilde{x}(t) + E\tilde{u}(t) + E_d\tilde{d}(t). \tag{2.11}$$

Where

$$A = A_1D + A_2(1-D)$$

$$B = B_1 D + B_2 (1 - D)$$

$$C = C_1 D + C_2 (1 - D)$$

$$E = E_1 D + E_2 (1 - D)$$

$$B_d = [(A_1 - A_2)X + (B_1 - B_2)U]$$

$$E_d = [(C_1 - C_2)X + (E_1 - E_2)U]$$

Taking Laplace transform of equation (11) we have

$$\tilde{X}(s) = (sI - A)^{-1} [B\tilde{u}(s) + B_d\tilde{d}(s)]...$$

(2.12)

$$\tilde{Y}(s) = C(sI - A)^{-1} [B\tilde{u}(s) + B_d\tilde{d}(s)] + E\tilde{u}(s) + E_d\tilde{d}(s)....(2.13)$$

Using equation (2.14) and (2.15) for DC value of input voltage  $V_{IN}$ , output Voltage  $V_O$  and duty Cycle D, the control-to-output and the input-to-output small signal transfer functions of the converter are respectively given as

$$\frac{\tilde{V_O}(s)}{\tilde{d}(s)} = C(sI - A)^{-1}B_d + E_d...$$

(2.14)

$$\frac{\widetilde{V_0}(s)}{\widetilde{V_{IN}}(s)} = C(sI - A)^{-1}B + E.$$

(2.15)

Now for  $\hat{C}uk$  converter in Fig. 2.48 the parameter  $A_1$ ,  $B_1$ ,  $C_1$  and  $E_1$  is derived by the following way

When switch is on for dT time then from Fig 2.46(a) we have

$$\frac{dil.1}{dt} = \frac{V_{rect\_average}}{L1} \qquad (2.16)$$

$$\frac{dil.2}{dt} = \frac{VC1-VC2}{L2} \qquad (2.17)$$

$$\frac{dVC1}{dt} = \frac{-iL2}{C1} \qquad (2.18)$$

$$\frac{dVC2}{dt} = \frac{iL2-\frac{VC2}{R}}{C2} \qquad (2.19)$$

$$V_{out} = -VC2 \qquad (2.20)$$

$$V_{out} = -VC2 \qquad (2.20)$$

$$\frac{+VL1}{L1} \qquad +VC1 \qquad -VL2 + \qquad -VC2 \qquad (2.20)$$

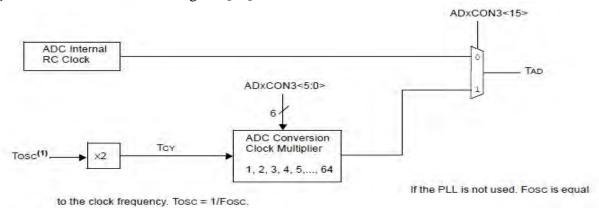

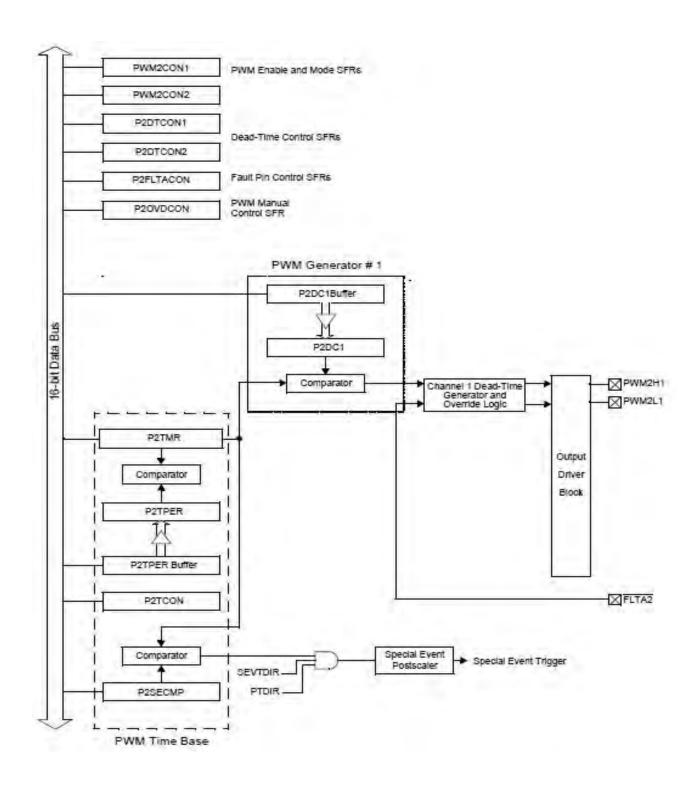

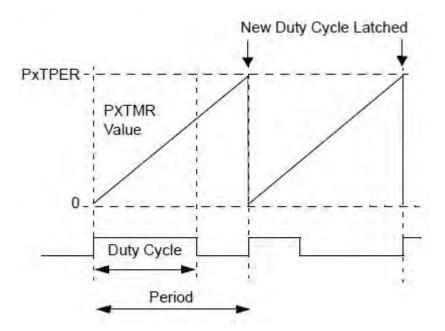

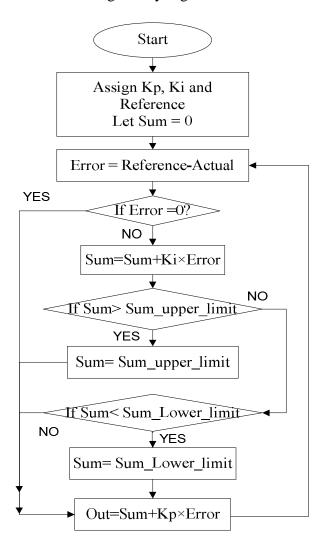

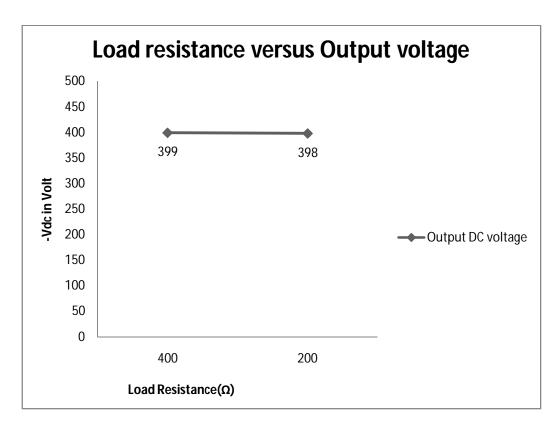

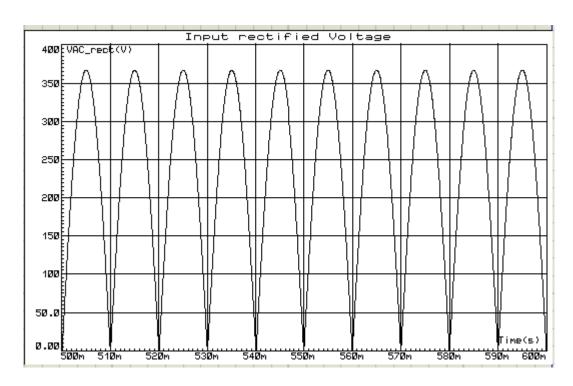

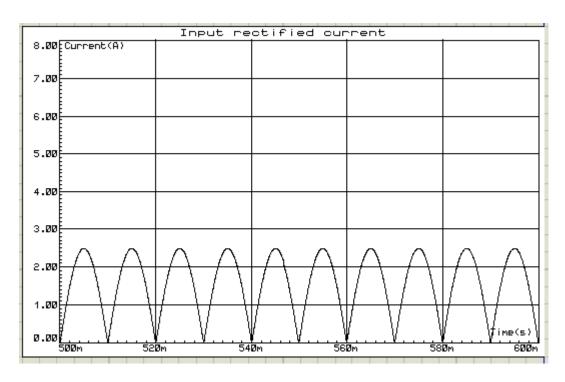

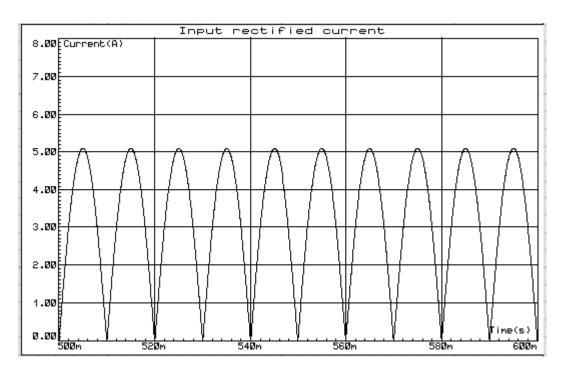

$$\frac{+VL1}{L1} \qquad +VC1 \qquad -VL2 + \qquad -VC2 \qquad$$