## Design and Analysis of a Low THD Electronic Ballast with Improved Input Power Factor

by

Aminul Islam Khan

A thesis submitted in partial fulfillment of the requirements for the degree of MASTER OF SCIENCE IN ELECTRICAL AND ELECTRONIC ENGINEERING

**Department of Electrical and Electronic Engineering**

BANGLADESH UNIVERSITY OF ENGINEERING AND TECHNOLOGY

July, 2013

The thesis titled **"Design and Analysis of a Low THD Electronic Ballast with Improved Input Power Factor",** (proposal passed by CASR Meeting 225 resolution number 37, dated 4/1/2011, board of examiners passed by CASR Meeting 229, resolution number 47, dated 25/7/2011) submitted by Aminul Islam Khan, Roll No: 0409062106F, Session: April/2009, to the Department of Electrical and Electronic and Engineering, Bangladesh University of Engineering and Technology, has been accepted as satisfactory in partial fulfillment of the requirement for the degree of Master of Science in Engineering (Electrical and Electronic) and approved as to its style and contents for the examination held on July 06, 2013 .

#### **BOARD OF EXAMINERS**

1.

3.

Dr. Mohammad Ali Choudhury Professor Department of EEE, BUET, Dhaka. Chairman (Supervisor)

2. Dr. Pran Kanai Saha Professor and Head Department of EEE, BUET, Dhaka. Member (Ex-Officio)

Member

Dr. Kazi Mujibur Rahman Professor Department of EEE, BUET, Dhaka.

4. Dr. Md. Fayyaz Khan Professor Faculty of Engineering United International University, Dhanmondi, Dhaka Bangladesh Member (External) It is hereby declared that this thesis or any part of it has not been submitted elsewhere for the award of any degree or diploma.

Signature of the Candidate

Aminul Islam Khan

| List of Figures                                          | vi            |

|----------------------------------------------------------|---------------|

| List of Tables                                           | ix            |

| Acknowledgement                                          | x             |

| Abstract                                                 | xi            |

| Chapter 1 Introduction                                   | 1             |

| 1.1 Background and present state of the problem          | 1             |

| 1.2 Objective of the thesis                              | 3             |

| 1.3 Thesis Outline                                       | 3             |

| Chapter 2 Literature Review                              | 4             |

| 2.1 Incandescent lamps Vs. Fluorescent lamps             | 5             |

| 2.2 Magnetic Ballast vs. Electronic Ballast              | 6             |

| 2.3 Basic Requirements of Electronic Ballasts            | 9             |

| 2.4 Harmonics and Power Quality Standards                | 10            |

| 2.5 Power factor                                         | 14            |

| 2.6 Review on Resonant Inverter Topologies in Electronic | Ballast 16    |

| 2.6.1 Half-Bridge Resonant Inverters                     | 17            |

| 2.6.2 Push-Pull Inverter Configuration                   | 20            |

| 2.6.3 Class E <i>LCC</i> Resonant Inverter               | 20            |

| 2.6.4 Current Source Inverters for Electronic Ballast    | 21            |

| 2.7 Power Factor Correction (PFC) Techniques in Electron | ic Ballast 22 |

| 2.7.1 Passive PFC in Electronic Ballasts                 | 24            |

| 2.7.1.1 L-C Filter Approach                              | 24            |

| 2.7.1.2 PFC with valley-fill Circuit                     | 25            |

| 2.7.1.3 PFC with Charge-pump Technique                   | 27            |

| 2.7.2 Limitations of Passive PFC Circuits                | 28            |

| 2.7.3 Active Power Factor Correction Methods             | 29            |

| 2.7.3.1 Low Frequency Active PFC                         | 29            |

| 2.7.3.2 High Frequency Active PFC                        | 31            |

| 2.7.3.2.1 Buck Converter Based Active PF                 | SC 32         |

| 2.7.3.2.2 Boost Converter Based Active PI                | FC 33         |

| 2.7.3.2.3 Buck-Boost Converter Based Act                 | tive PFC 36   |

| 2.7.3.2.4 Cuk Converter Based Active PFC                   | 37 |

|------------------------------------------------------------|----|

| 2.8 Zero Voltage Switching Resonance Converters            | 39 |

| Chapter 3 Design and Analysis of Electronics Ballast       | 43 |

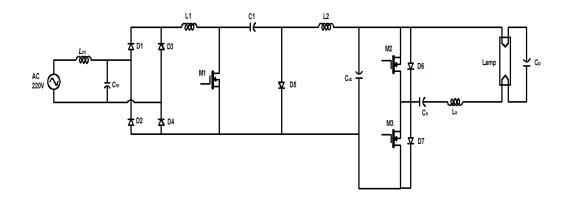

| 3.1 Proposed Electronics Ballast                           | 44 |

| 3.2 Analysis of proposed Ballast                           | 45 |

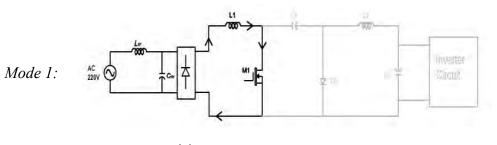

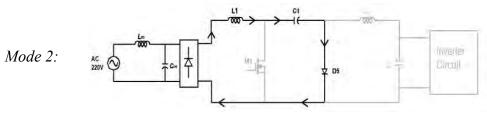

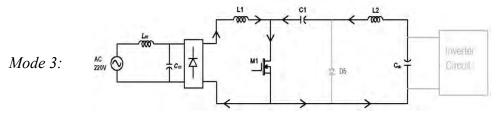

| 3.2.1 Analysis of PFC stage                                | 46 |

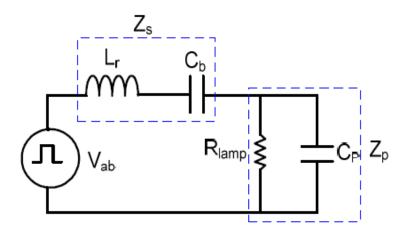

| 3.2.2 Analysis of half bridge series resonance inverter    | 48 |

| 3.3 Operating frequency of the Ballast                     | 52 |

| 3.4 Components Selection                                   | 53 |

| 3.4.1 Selection of Components of Cuk Converter             | 53 |

| 3.4.2 Selection of Components of Series Resonance Inverter | 54 |

| Chapter 4 Practical Implementation                         | 56 |

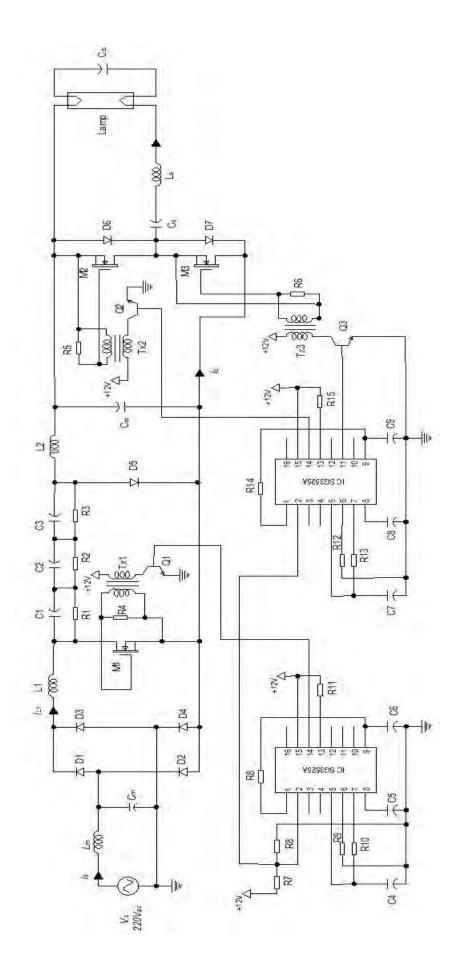

| 4.1 Proposed Ballast in practice                           | 56 |

| 4.2 Choice of component values                             | 59 |

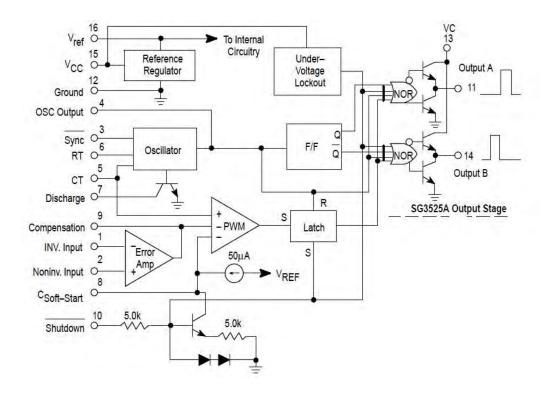

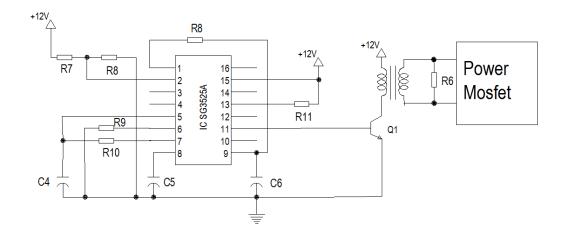

| 4.3 High Frequency Pulse Generation Circuit                | 62 |

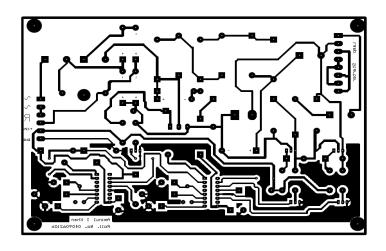

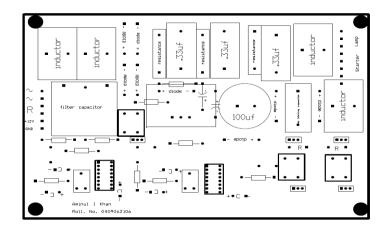

| 4.4 PCB design and EMI consideration                       | 63 |

| 4.5 Simulation Results                                     | 65 |

| 4.6 Experimental Results                                   | 67 |

| 4.7 Design to Work                                         | 74 |

| Chapter 5 Summary and Conclusions                          | 74 |

| 5.1 Summary                                                | 74 |

| 5.2 Future works                                           | 75 |

# List of Figures

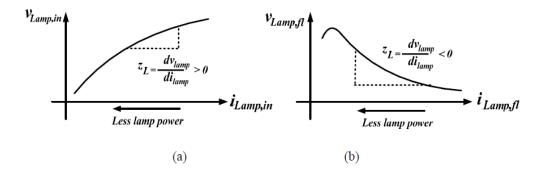

| Figure 2.1  | (a) Incandescent lamp V-I curve; (b) Fluorescent lamp V-I             |    |

|-------------|-----------------------------------------------------------------------|----|

|             | Characteristics                                                       | 6  |

| Figure 2.2  | Efficacy of fluorescent lamp VS lamp operating frequency              | 8  |

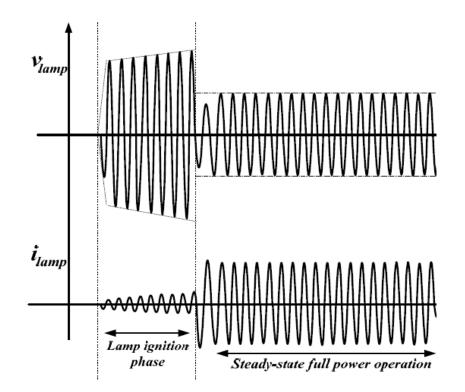

| Figure 2.3  | Illustration of typical voltage and current waveforms                 |    |

|             | in electronic ballast                                                 | 8  |

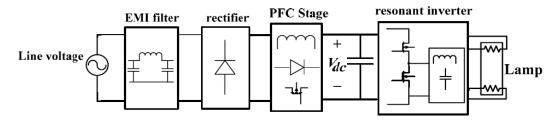

| Figure 2.4  | Block diagram of electronic ballast with PFC in commercial            |    |

|             | fluorescent lamps                                                     | 10 |

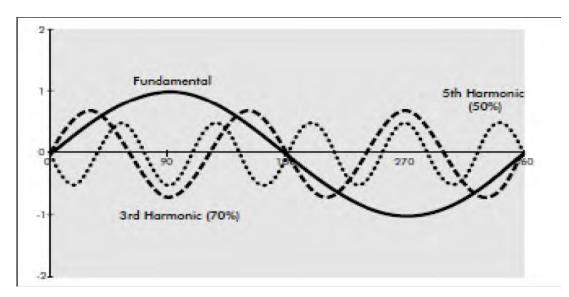

| Figure 2.5  | Harmonic phenomena                                                    | 10 |

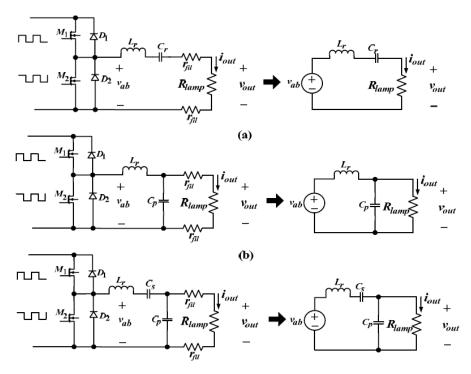

| Figure 2.6  | Basic Voltage Source Resonant Inverter Topologies                     | 18 |

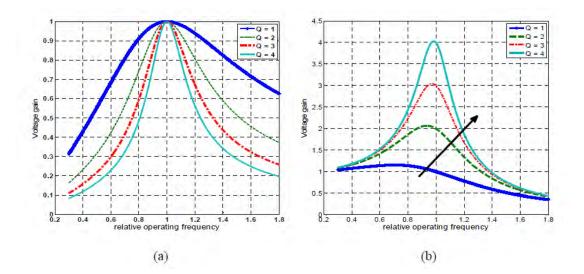

| Figure 2.7  | Voltage gain plots: (a) series LC resonant; (b) parallel LC resonant; |    |

|             | (c) series-parallel LC resonant                                       | 19 |

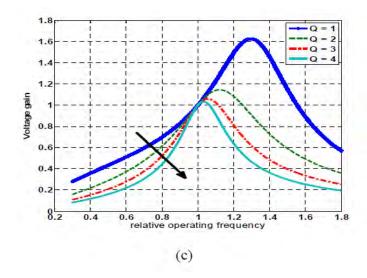

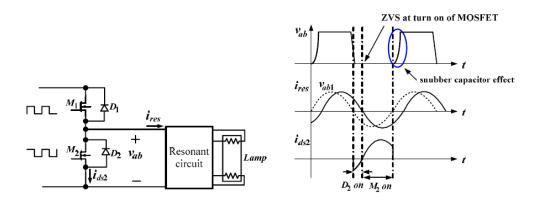

| Figure 2.8  | ZVS operating waveforms for voltage fed half-bridge                   |    |

|             | resonant inverters                                                    | 19 |

| Figure 2.9  | (i) Class E resonance inverter                                        | 21 |

| Figure 2.9  | (ii) Class E resonant inverters key waveforms:                        |    |

|             | (a) Simulation waveforms; (b) simulation waveforms                    | 21 |

| Figure 2.10 | Current fed resonant inverter in electronic ballast                   | 22 |

| Figure 2.11 | (a): Electronic ballast without DC-link capacitor;                    |    |

|             | (b) with DC-link capacitor                                            | 23 |

| Figure 2.12 | Passive L-C filter of PFC in electronic ballast                       | 25 |

| Figure 2.13 | (a): Valley-fill PFC electronic ballast; (b) its key waveforms:       |    |

|             | (i) theoretical waveforms; (ii) simulation waveforms                  | 26 |

| Figure 2.14 | Modified valley-fill PFC circuit                                      | 27 |

| Figure 2.15 | Charge-pump PFC electronic ballast                                    | 28 |

| Figure 2.16 | (a). Typical schematic of a low frequency active PFC circuit          | 30 |

| Figure 2.16 | (b). Simulated input current and voltage waveforms for a              |    |

|             | 250 W constant power load with low frequency active PFC               |    |

|             | circuit and inductance values of 75 mH and 150 mH.                    | 30 |

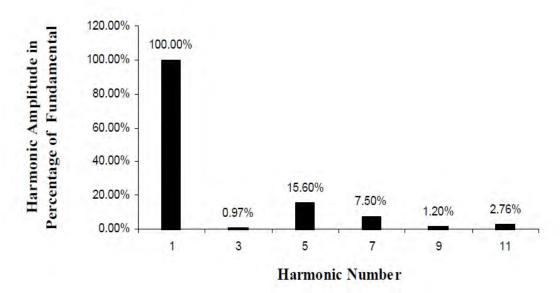

| Figure 2.16 | (c). Odd line current harmonics normalized to the fundamental         |    |

|             | with a 250 W constant power load for a low frequency active           |    |

|             | PFC circuit with an inductance value of 75 mH.                        | 30 |

| Figure 2.16 | (d). Odd line current harmonics normalized to the fundamental |    |

|-------------|---------------------------------------------------------------|----|

|             | with a 250 W constant power load for a low frequency active   |    |

|             | PFC circuit with an inductance value of 150 mH.               | 31 |

| Figure 2.17 | (a). Buck converter based high frequency active PFC circuit.  | 32 |

| Figure 2.17 | (b) Current and voltage waveforms of a Buck converter         |    |

|             | based PFC circuit.                                            | 33 |

| Figure 2.18 | (a). Boost converter based high frequency active PFC circuit. | 33 |

| Figure 2.18 | (b). Current and voltage waveforms of a CCM boost             |    |

|             | converter based PFC circuit.                                  | 34 |

| Figure 2.19 | Comparison of inductor current for CCM and CRM                |    |

|             | operating modes                                               | 36 |

| Figure 2.20 | (a). Buck-boost converter based high frequency active         |    |

|             | PFC circuit                                                   | 37 |

| Figure 2.20 | (b). Current and voltage waveforms of buck-boost converter    |    |

|             | based PFC circuit                                             | 37 |

| Figure 2.21 | (a). Cuk converter based high frequency active PFC circuit    | 38 |

| Figure 2.21 | (b). Current and voltage waveforms of Cuk converter based     |    |

|             | PFC circuit                                                   | 38 |

| Figure 2.22 | Switch Configurations for ZVS Resonant Converters             | 39 |

| Figure 2.23 | ZVS circuit                                                   | 40 |

| Figure 2.24 | Modes of operation with equivalent circuit                    | 40 |

| Figure 2.25 | Waveform of ZVS resonance converters                          | 40 |

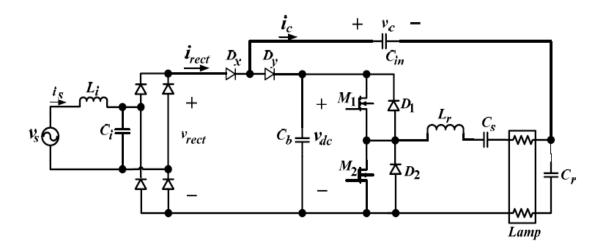

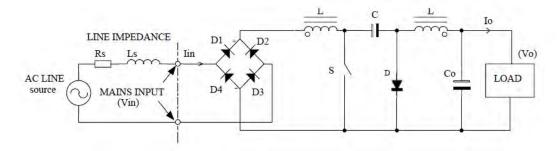

| Figure 3.1  | Proposed electronics ballast                                  | 44 |

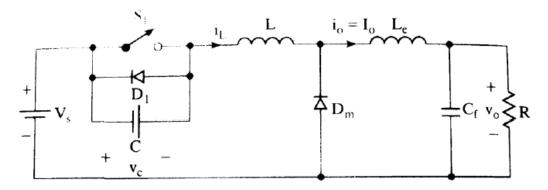

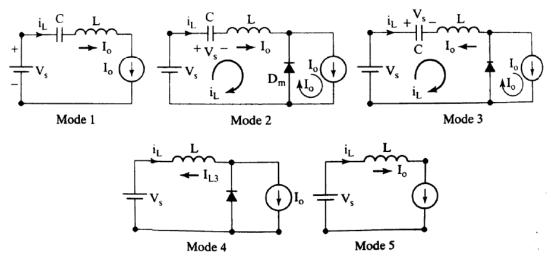

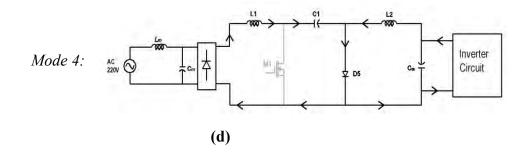

| Figure 3.2  | Operating modes of PFC stage                                  | 47 |

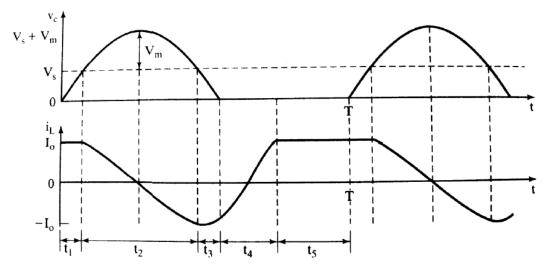

| Figure 3.3  | Operating waveform of PFC stage                               | 48 |

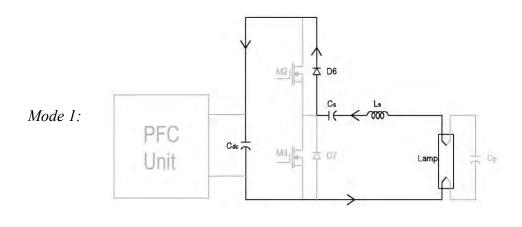

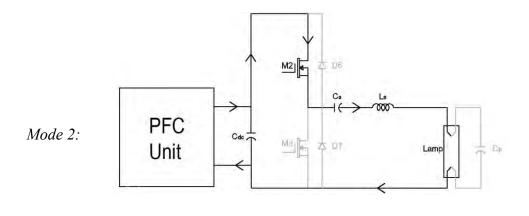

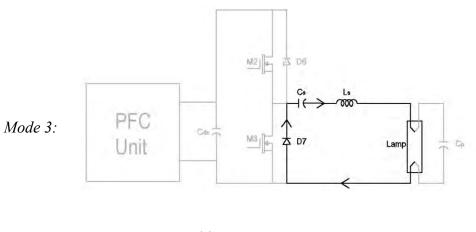

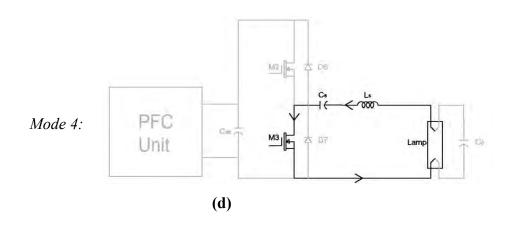

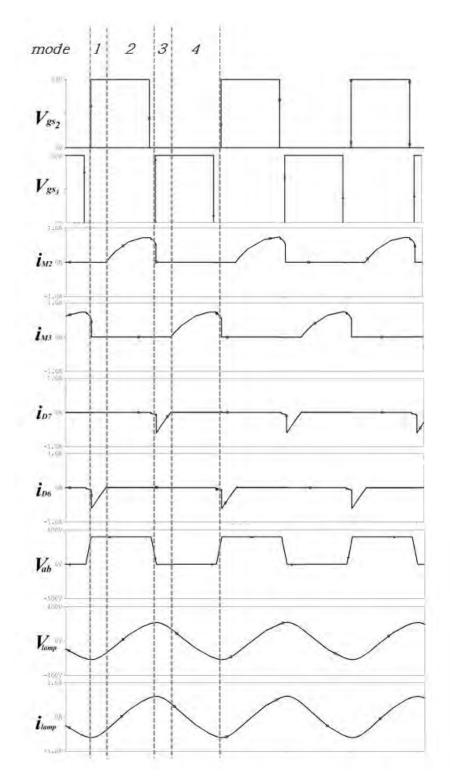

| Figure 3.4  | Operating modes of half bridge series resonance inverter      | 50 |

| Figure 3.5  | Operating waveform of half bridge series resonance inverter   | 51 |

| Figure 3.6  | Series resonance parallel loaded inverter (SRPLI) equivalent  |    |

|             | Circuit                                                       | 54 |

| Figure 4.1  | Detail schematic circuit of proposed electronics ballast      | 57 |

| Figure 4.2  | Internal block diagram of SG 3525A                            | 62 |

| Figure 4.3  | High frequency pulse generating circuit                       | 63 |

| Figure 4.4  | Bottom layer of Ballast (PCB layer)                           | 64 |

| Figure 4.5  | Top layer of Ballast PCB (component layer)                       | 64 |

|-------------|------------------------------------------------------------------|----|

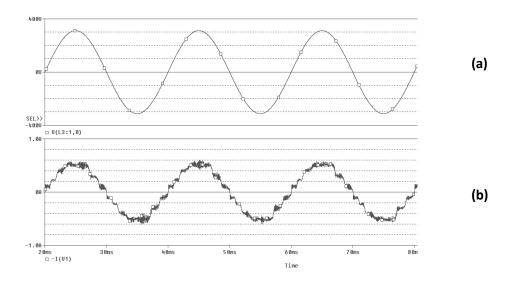

| Figure 4.6  | input (a) voltage and (b) Current waveform of proposed ballast   | 66 |

| Figure 4.7  | Output (a) Voltage and (b) Current waveform of proposed ballast. | 66 |

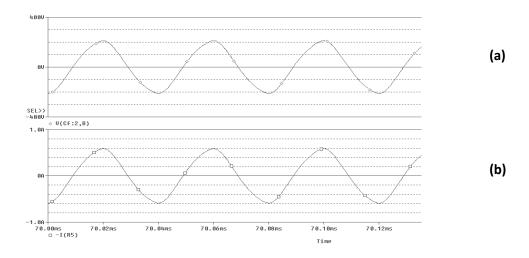

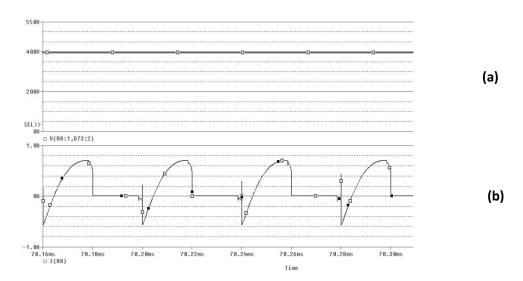

| Figure 4.8  | (a) Dc link voltage across capacitor Cdc and                     |    |

|             | (b) inverter input current.                                      | 67 |

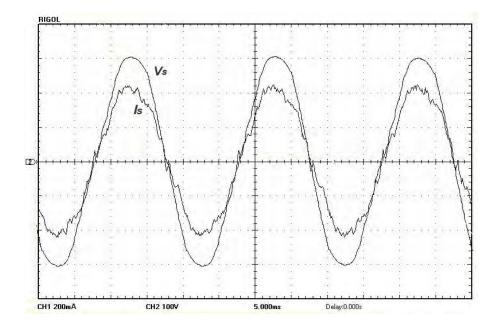

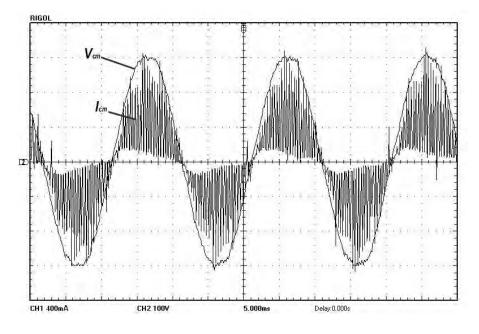

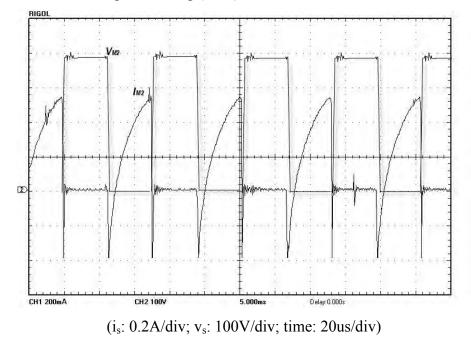

| Figure 4.9  | Practical input current and voltage waveform                     | 68 |

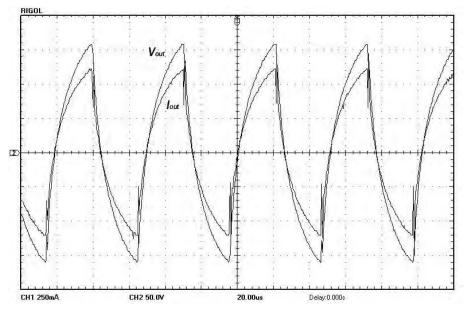

| Figure 4.10 | Practical output current and voltage waveform                    | 70 |

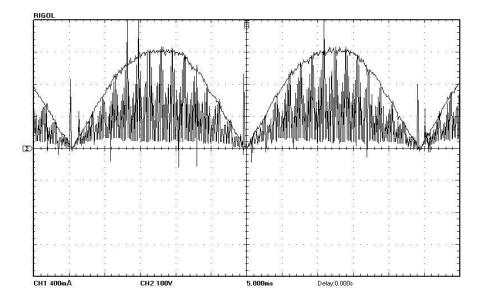

| Figure 4.11 | Current and voltage waveform prior to filtering unit             | 71 |

| Figure 4.12 | Current and voltage waveform after filtering unit                | 71 |

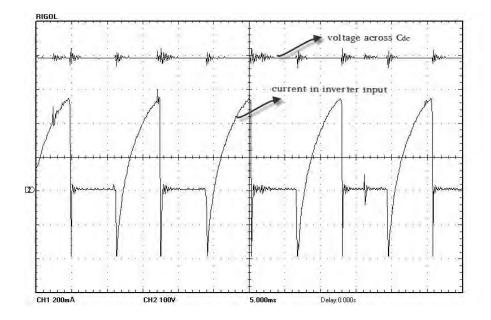

| Figure 4.13 | Inverter input current and voltage waveform                      | 72 |

| Figure 4.14 | Current and voltage waveform across MOSFET M2                    | 72 |

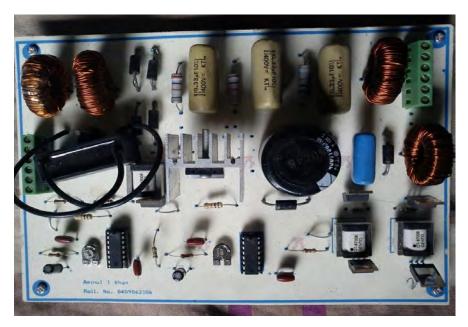

| Figure 4.15 | Project on PCB Board                                             | 73 |

## List of Tables

| Table 2.1 | Harmonic limits for IEC1000-3-2 Class C equipment                 | 23 |

|-----------|-------------------------------------------------------------------|----|

| Table 4.1 | Circuit parameter for proposed electronics ballast                | 65 |

| Table 4.2 | List of component value                                           | 67 |

| Table 4.3 | Fourier component of input current of proposed electronic Ballast | 69 |

Alhamdulillah, all praises for Allah subhanahu t"ala who is our creator and sustainer. All my thanks belong to Him for his uncountable favors bestowed upon me. It is He who has given me "toufiq" (opportunity) to accomplish the research work and complete the dissertation. Without His help nothing is possible to do in this world. It is impossible to express gratitude towards Him with mere words of praises.

Then I would like to express my sincere gratitude and deep appreciation to my supervisor, Professor Dr. Mohammad Ali Choudhury, for his guidance, encouragement and assistance in the process of completing this work.

My thanks also go to the respectable faculties of the Electrical and Electronic Engineering department, BUET, especially Professor Dr. Kazi Muzibur Rahman, for his support and providing the laboratory facility.

Sincerest thanks to all of those who extended their hands, directly or indirectly, to complete this research work.

Finally, I would like to pay my profound gratitude to my parents, relatives and friends for their inspiration towards the completion of this work.

## <u>Abstract</u>

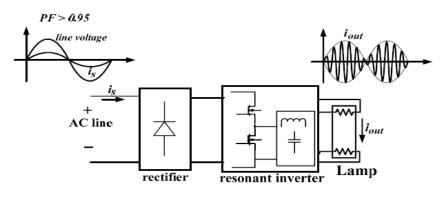

This thesis proposes a two-stage high-power factor and low THD electronics ballast for a 40W commercial fluorescent tube lamp. The proposed ballast uses a Cuk Buck-Boost ac-dc converter in continuous conduction mode (CCM) as a power factor and input current shaper/pre-regulator. The dc-dc Ĉuk converter between acdc diode rectifier and the resonant inverter of the ballast makes the input current high frequency switched. As a result of in phase high frequency switching, the input current can be easily filtered with small sized filter to obtain low THD input current and also to maintain high input power factor. In the proposed electronic ballast topology, a self oscillating half bridge series resonant parallel loaded inverter (SRPLI) is used for the conversion of dc supply obtained by bridge rectifier to high frequency ac supply. Use of high frequency ac for fluorescent lights allows better conversion of energy to light than in the utility supply low frequency ac supply. Also, the ignition cum voltage balancing inductors used in these lamps are reduced in size providing further increase of efficiency by reducing copper loss in the inherent resistance in inductors. The design, modeling and simulation of the proposed topology is carried out in Orcad environment for a 40W, 220V, 50Hz fluorescent lamp. The design is implemented practically. The zero voltage switching (ZVS) is achieved which reduces the switching losses. The power quality indices like total harmonic distortion of ac mains current (THDi), power factor (PF) and energy conversion efficiency are evaluated to demonstrate the behavior of proposed electronic ballast.

## **Chapter 1**

## <u>Introduction</u>

### **1.1 Background and present state of problem**

Worldwide energy crisis has lead to interests in using energy efficient gadgets and loads. In household and commercial use, incandescent lamps are inefficient loads. Fluorescent lamps are well known for their higher luminous (lm/watt) efficiency. However, all discharge lamps require adequate striking voltage at the time of starting and current limiting control after the ignition process. This can be achieved by using magnetic or hybrid or electronic ballast. The magnetic ballast is large in size and weight, produces audible noise and flickering. The magnetic ballasts have iron and copper losses and have poor input power factor. When the fluorescent lamps are driven at high frequency by using electronic ballast, then the luminous efficacy improves by 10-15%, resulting in reduction in audible noise and flicker. High frequency allows smaller choke coils of low internal resistances which reduce the copper loss. As a result the overall efficiency improves.

Electronic ballasts use semiconductor components to increase the frequency of fluorescent lamp operation, typically in the 20 - 40 kHz range rather than 50/60 Hz supply as normally used. The conventional magnetic ballast needs a starter to ignite the lamp and the lamp flickers during the ignition process. This flicker causes high intermittent starting current. The event consumes extra power during start and consumers are to pay for this. Intermittent high starting current reduces the lamp performance with time as the filament property changes eventually damaging the filament property all together. Electronic ballasts consist of solid state devices to generate a high frequency ac voltage to drive the compact fluorescent lamp. The line voltage supplied to the ballast is converted into a dc voltage using a full-wave diode bridge rectifier (DBR) and a filter capacitor. Then an inverter is used to feed high frequency (20 to 100 kHz) current to the lamp. In the existing electronic ballast, the relatively small conduction time of DBR and input filter components distorts the input ac mains current waveform, which is rich in odd harmonics. However, this electronic ballast has power quality problems like poor power factor (PF), high crest factor (CF) and high total harmonic distortion (THD) of ac mains current which do not comply with the international regulations such as IEC 61000-3-2 [1]. This nonsinusoidal shape of the input current drawn by the rectifiers causes a number of problems for the power distribution network and for other electrical systems in the vicinity of the rectifier including:

- Phase displacement of the current and voltage fundamentals requires that the source and distribution equipment handle excess reactive power increasing their volt-ampere ratings,

- 2) High input current harmonics and low input power factor,

- 3) Lower rectifier efficiency because of the large rms value of the input current,

- Input ac main's voltage distortion because of the associated higher peak currents,

- 5) High reactive components size,

- 6) Heat loss due to  $I^2R$  drop in wire and eddy-current loss and core loss in the transformer core result in lower overall efficiency,

- 7) Lower power conversion,

- 8) Excitation of system resonances,

- 9) The inefficient use of electric energy, the discontinuous conduction of the bridge rectifier results in a high total harmonic distortion (THD) in the input Lines and

- 10) Malfunctioning of the sensitive electronic equipments.

A dc-dc converter interfacing with diode bridge rectifier (DBR) and a small low pass filter improves the power factor to nearly unity. By proper control of the dc-dc converter, the input current may be shaped almost in phase with the input voltage.

The active power factor corrected (PFC) electronic ballast draws the input current to follow ac mains voltage and hence the input power factor is improved nearly to unity when filtered by a small filter (because of high frequency switched input current nature). The harmonic pollution of ac mains can be effectively be reduced when a high power factor (HPF) with low total harmonic distortion (THD) of the input current is achieved. The other advantages of the HPF are reduction of ac main"s ms current and the crest factor of ac main"s current [1]. HPF can be obtained using two power processing stages. The first one is a high power factor pre-regulator (PFP) stage, which converts the ac mains voltage to a dc voltage. The second stage transforms the dc voltage to a high frequency ac voltage to drive the fluorescent lamp.

### **1.2 Objective of the Thesis**

The specific aims of this research are:

- 1. To design a schematic model of electronic ballast with low THD and high power factor,

- Analyze the design procedure for various portion of proposed electronics ballast and

- 3. To implement proposed ballast in practical for 40W tube light.

### **1.3 Thesis outline**

This thesis includes five chapters. Background and present state of problems are presented in chapter-I. Literature review that includes different PFC schemes and resonance converter topologies are presented in chapter 2. Comparisons such as Incandescent lamps VS Fluorescent lamps, magnetic VS electronics ballast are also included in this chapter. In chapter 3, design procedure of proposed electronics ballast and analysis of them with mode in operation are described. Choice and selection of different component values and their operating voltage are included in this chapter. Practical circuit of proposed electronics ballast is given in chapter 4. Details practical circuit diagram combination with pulse generating circuit is included here. PCB layout includes top view and bottom view. The chapter at the end presents simulated and experimental results of the ballast circuit. Chapter 5 is conclusion chapter. Summary of the thesis and suggestions for future research is given here.

## **Chapter 2**

## **Literature Review**

Over time, incandescent lamps, known as electric lamps, have proven to be a reliable source of light and have, therefore, dominated the lighting industry. While incandescent lamps are able to provide excellent light quality and performance, they suffer from low power conversion efficiency. The power efficiency of an incandescent lamp can be as low as 10%; the majority of the energy consumed by the lamp is dissipated as heat rather than visible light [2]. The incandescent lamp's low power conversion efficiency prompted the development of alternative lighting solutions such as high power light emitting diodes (LED) and energy efficient fluorescent lamps.

An LED presents many advantages over an incandescent lamp. These include, low energy consumption, longer life, robustness, small size, and durability. However, due to the use of semiconductor diodes in LED lamps, current LED lighting products are expensive than incandescent lamps and fluorescent lamps of comparable light output. Another disadvantage is that LEDs require very precise current and heat management. The performance of an LED lamp is highly sensitive to the ambient temperature of the operating environment [3][4]. When the LED is operating in a high ambient temperature environment with a high driving current, the LED package can overheat and eventually lead to device failure. LED lamp is also prone to producing non-uniform light intensity; it cannot produce the same light intensity in all directions [3]. This particular shortcoming of LED lamps limit their applications needing a continuous spherical field of light. The aforementioned problems associated with the LEDs have hindered its entrance into the mainstream lighting industry so far. However, effort is going on to overcome the problems. If the problems can be tackled at feasible costs, LEDs will enter the ligh industry and dominate the market in future.

#### 2.1 Incandescent lamps VS Fluorescent lamps

One of the major differences between fluorescent and incandescent lamps is the way they generate light. Incandescent lamps use the Joule-heating process by electrically heating the tungsten filaments inside the glass tube to increase the lamp brightness. Since the resistance of an incandescent lamp is governed by the tungsten filament (which behaves like a resistor), the lamp current is simply equal to the applied input voltage divided by the filament resistance of the lamp. Essentially, incandescent lamp behaves as a resistive load as shown in Figure 2.1(a). The power of the lamp is easily adjusted since the lamp voltage and current are more or less directly proportional to each other. However, only 10% the energy consumed by the incandescent bulb is converted to visible light. The incandescent lamp has such poor efficiency because the majority of the energy is wasted in the form of heat and infrared radiation.

In a bid to solve the poor energy conversion efficiency of incandescent lamps, low pressure gas discharge lamps (also known as fluorescent lamps) were developed. Rather than heating up the tungsten filament to generate light, the fluorescent lamp generates light by utilizing the phenomenon of inelastic scattering of electrons. Visible light is produced by a chemical reaction called fluorescence. Three key elements are required in the transformation of electrical energy into visible light: highly mobile electrons, mercury atoms, and phosphor. When a highly mobile electron collides with a mercury atom in the gas inside the fluorescent tube, the electron transfers energy to the atom<sup>\*\*</sup>s outer electron and causes that electron to jump to a higher energy level. Since this energy level is highly unstable, the electron falls back to a lower energy level and an ultraviolet photon will be emitted from the atom. However, the ultraviolet photon is emitted at a wavelength that is not visible to human eyes. A phosphor layer is then coated on the interior of the tube so that the photon is emitted at wavelengths that are visible to human eyes.

From the above description, it can be observed that the structural design of a fluorescent lamp is more complicated than the incandescent lamp. When the fluorescent lamp is turned on, the electric power quickly heats up the electrodes that are located at the end of the tube to emit electrons. These electrons then collide with

and ionize the gas atoms surrounding the filament. As a result of avalanche ionization, the conductivity of the ionized gas rapidly increases, allowing higher currents to flow through the lamp. If the voltage and current of the fluorescent lamp is displayed graphically according to the aforementioned explanation, it can be deduced that fluorescent lamp essentially inherits negative resistance as shown in Figure 2.1(b). The presence of this negative resistance physically means that as the fluorescent lamp current increases, the lamp voltage decreases, which lead to the lamp resistance to decease and allow more current to flow through the lamp. If the lamp is connected directly to a constant-voltage supply, the lamp will be damaged due to the uncontrolled current flow. As a result, a lamp current stabilization element called ballast must be required in all the fluorescent lamps to prevent the uncontrolled amount of current flowing into the lamp.

Figure 2.1: (a) Incandescent lamp V-I curve; (b) Fluorescent lamp V-I characteristics [5]

#### 2.2 Magnetic Ballast VS Electronic Ballast

Fluorescent lamps cannot be directly connected to the AC main since it will cause the lamp current to become unstable and will eventually destroy the lamp. In order for stable lamp operation, it is necessary to have a device (known as a ballast) to act as an interface between the AC mains and the lamp. In electronic circuits, the simplest way to limit the lamp current is to place a reasonable sized resistor between the input voltage source and the lamp. However, the placement of a resistor in the circuit will result in significant power loss. Since the signals at the fluorescent lamp terminals are AC, a reasonably large inductor can be used to provide the necessary impedance to limit the lamp current (once the lamp has been ignited) in place of a resistor. There are two main types of ballasts: Magnetic and electronic. Early ballasts used with fluorescent lamps were magnetic and its two major advantages are its cost effectiveness and its simplicity. Magnetic ballasts mainly consist of a large magnetic coil that operates at the line frequency. Their application has following disadvantages: (1) the magnetic coil is large and is very heavy; (2) since the ballast operates at the line frequency, the arc within the lamp glass tube is reignited twice during each line frequency cycle (this results in significant wear on the lamp electrodes and visible flickering); (3) there is no way to implement advanced dimming control to adjust lamp power; (4) the lamp efficacy, which is defined as lumens per watt, is very poor when the lamp operates at very low frequency. The last point is illustrated by Figure 2.2, which shows the relationship between the output lumens of a fluorescent lamp as a function of the lamp operating frequency [5]. It is observed that as the operating frequency is increased to above 20 kHz, an improvement of more than 10% is achieved in the lamp efficacy.

The drawbacks of the magnetic ballasts led to the development of high frequency electronic ballasts based on advanced electronic circuitry. Unlike magnetic ballasts, electronic ballasts are designed to operate at high frequency. High frequency operation improves the lamp efficacy, reduces the circuit component size, and allows easy lamp starting. In addition, when the ballast operates at high frequency, the ions inside the discharge tube do not have enough time to recombine with the highly mobile electrons. Because the recombination does not take place, the magnetic ballast"s re-ignition problem and flickering noise do not exist in electronic ballasts. Figure 2.3 shows the typical current and voltage waveforms of a fluorescent lamp that uses a high frequency electronic ballast. It can be observed in the figure that a high output voltage must be provided until the arc is established inside the lamp so that the lamp current will start to flow. Due to the negative lamp impedance phenomenon, the envelope signal of the lamp voltage and current changes in the opposite direction when the lamp power changes. The lamp current decreases at a much faster rate than the lamp voltage"s rate of increase. Therefore, due to their many advantages over magnetic ballasts, electronic ballasts are widely used in the fluorescent lighting industry and its design plays a key role in providing consumers with highly energy efficient fluorescent lighting.

Fluorescent lamps efficiency relative to 50 Hz operation increases rapidly when the operating frequency changes from 1 kHz to approximately 20 kHz, than increases much more gradually beyond 20 kHz. However, electromagnetic interference (EMI) increases with frequency. To increase efficiency while limiting EMI, electromagnetic ballasts typically operate at a frequency between 20 and 50 kHz.

Figure 2.2: Efficacy of fluorescent lamp VS lamp operating frequency [5]

Figure 2.3 Typical voltage and current waveforms in electronic ballast [5]

#### 2.3 Basic Requirements of Electronic Ballasts

An electronic ballast is essentially an electronic device that converts the low line frequency AC signal to a high frequency AC signal to drive the fluorescent lamp. The basic functions of the electronic ballast are: (1) to provide sufficient high voltage across the lamp electrodes during the lamp ignition process; (2) to stabilize the high frequency lamp current after the lamp is successfully ignited; (3) to perform power factor correction (PFC) so that the harmonics of the line current is minimized.

Power factor correction is critical in ballast designs because the fluorescent lamp is essentially a load that consumes power from the AC main and (depending on the circuit design) can inject harmonics into the utility. The more harmonics the line current has, the more harmonics are injected and the overall power factor drops. The significance of PFC will be further discussed in the next section. Magnetic ballasts also incorporate PFC since the inductive coil introduces a lagging power factor (PF) at the line input. PFC is implemented in magnetic ballasts by placing a capacitor in parallel with the ballast so that the input sinusoidal line current becomes in phase with the line voltage. Electronic ballasts, on the other hand, implement PFC by using advanced power electronic circuits. The details regarding the PFC techniques used in electronic ballasts will be discussed later in this chapter. Figure 2.4 is a general block diagram of commercial fluorescent lamp electronic ballast. The commercial ballast consists of three main parts: (1) a diode rectifier that converts the AC line voltage to a rectified sinusoidal voltage; (2) a PFC circuit that allows the input current becomes a sinusoidal signal that is in phase with the line voltage; (3) a DC-AC inverter that converts the DC voltage into high frequency signal to drive the fluorescent lamp. In addition, a control circuit can be included to provide more advanced functions such as dimming control of the lamp, lamp end-of-life detection, or lamp over-voltage protection.

Figure 2.4 Block diagram of electronic ballast with PFC in commercial fluorescent lamps [6].

### 2.4 Harmonics and Power Quality Standards

Harmonics are defined as unwanted frequency components on the source power generated by the loads. Harmonics cause equipment malfunction, equipment failure, unnecessary high operating costs and in some cases fires. Harmonics are created when electronic devices draw current in a non-linear fashion. This causes line voltage distortion, which is an irregularity in the shape of the voltage waveform. Voltage distortion produces such effects as motors prematurely burning out, clocks running fast, computers freezing up and system crashes. The percentage of harmonics in a waveform is called THD (total harmonic distortion). As the THD increases, the efficiency of the system is greatly reduced.

Figure 2.5 Harmonics phenomena [7]

The ever expanding application of power electronics load and increasing dependency upon energy saving electronics lighting equipments has produced serious concern about power quality. The term Power quality broadly refers to maintaining a waveform close to sinusoidal waveform of bus voltage magnitude and frequency. The standard organization IEEE guides references for power quality issues.

Although distortion problems happen particularly in the final customer, this problematic issue has other implications to be considered in the production, propagation and resolution of this type of disturbances. The harmonics increasing disturbances brought a set of standards (resulting from previous guidelines), recommendations and limits, to assure the compatibility between equipment, devices and power distribution systems. When a equipment draws current from the utility in a nonlinear or choppy manner, this is called current distortion. It always produces harmonics in the load current waveform and can produce significant harmonics in the voltage waveform at the point of common coupling (PCC) and elsewhere. The harmonic distortion of voltage and/or current waveform corresponds to a specific case in the power quality issues. In the network that have current and voltage harmonic sources (CFL, FL run by EB.) this may exceed the permissible limit.[8]-[9] Typically, the standard limits are applied to individual loads. Nevertheless, monitoring all the loads is a strong challenge as IEEE Std 519 limits for current distortion. But we can assume for all lighting, motor drives, power supplies, and other equipment sharing a common electrical bus or panel with sensitive electronic loads THD value limits 15 percent. [10]

According to the International Standards, the norms 1000 of the International Electro-technical Commission (IEC) define the current and voltage harmonic levels that must not to be exceeded. The IEC 61000-3-2 Standard foresees limits for the current harmonics components emission in equipment (class grouped) for lesser than 16 A rms (per phase). For equipment with current superior to 16 A, this Standard recommends the application of the IEC 61000-3- 4.Norms IEC-1000-2-2 and IEC-1000-2-4 specify the voltage harmonic levels to be respected at the interconnection point of low voltage distribution network, for public and industrial customers, respectively.

The European Standard EN 50 160:1994 gives the main characteristics of the voltage, including harmonics voltage, in the customer delivery point for low and medium voltage under normal operating conditions.[11]

However, the main reference for this subject is the American Standard that was presented by the IEEE in the recommendation 519-1992: IEEE Recommended Practices and Requirements for Harmonic Control in Electric Power Systems, initially proposed in 1981 and revised in 1992.[9]

IEEE Std 519 was introduced in 1981 and most recently revised at 1992. The standard recognizes the responsibility of an electricity user to not degrade the voltage of the utility by drawing heavy nonlinear or distorted current. It also recognizes the responsibility of utility to provide users with a near sine wave voltage. According to IEEE Std 519, harmonic voltage distortion of power systems 69 KV or below is limited to five percent with each individual limits of three percent. The current harmonics limits based on short circuit strength of the system. Essentially, the customers allowed to inject in a system is depend on the system able to handle harmonic currents.[9]

Widespread use of static rectification equipment in industrial loads on small and medium power transformers has resulted in a dramatic increase in the harmonic content of the load current for this equipment. It is quite common for the harmonic factor of the current to exceed 0.05 per unit, which is the limit specified for usual service conditions in IEEE Std C57.12.00- 1993 and IEEE Std C57.12.01-1998. It is also well known that higher harmonic content in the current causes higher eddy current loss in winding conductors and structural parts linked by the transformer leakage flux and consequently, higher operating temperatures.[12]

IEEE Std C57.110-1998 (Revision of IEEE Std C57.110-1986) describes transformer de-rating for harmonic loads. This recommended practice set forth by the American National Standards Institute (ANSI) and the Institute of Electrical and Electronics Engineers (IEEE) establishes two methods for the current de-rating of power transformers when connected to loads which consume non-sinusoidal currents. The standard applies to non-sinusoidal load currents which have a harmonic load factor (which is defined as the ratio of the effective value of all the harmonics to the effective value of the fundamental harmonic) greater than 0.05 per The Requirements of IEEE-519-1992 IEEE-519-1992 describes the unit. recommended practices and requirements for Harmonic Control in Electrical Power Systems. The scope of IEEE-519-1992 is clearly stated as the intention of establishing goals for the design of electrical systems that include both linear and non-linear loads. The document describes the voltage and current waveforms that may exist throughout the system and establish waveform distortion goals. It defines the interface between sources and loads as the point of common coupling with observances of the design goals to minimize interference between electrical equipment. It is the responsibility of any reputable equipment supplier to provide their customers with equipment, at the best possible cost per performance ratio, that will meet the known operating requirements of the 1 of 4 customers. Included with the purchase of that equipment is the less tangible but equally important application experience that the supplier can share with the customer. Lastly, the equipment supplier should be able to supply any necessary service and application support directly associated with the performance of that equipment and its impact on other electrical equipment utilizing the same PCC.

The generation of harmonics in a power system can be attributed to the use of rectifiers, arc furnaces, static var compensators, inverters, electronic phase controllers, cyclo-converters, switched mode power converters, and pulse width modulated drives, as defined in IEEE Standard 519-1992. All of these devices may cause harmonics in the voltage and or current wave shape provided by the utility. In the case of devices containing solid state components to achieve switching, voltage harmonics can be attributed to voltage notching due to commutation periods while current harmonics can be attributed to discontinuous conduction due to the switching of the solid state components. The system response characteristics to harmonic loads on a distribution system determine the effect of these loads. The flow of harmonic currents in a distribution network is dependent on the system short-circuit capacity, the placement and size of capacitor banks, the characteristics of the loads on the system, anti finally, the balanced or unbalanced conditions of the system. IEEE Standard 519-1992 provides recommended practices for harmonic control for both the utility and individual customer. Because of the wide range of harmonic- producing loads described above, three harmonic indices have been recommended for the individual customer to provide a meaningful insight of harmonic effects.[9] These indices include:

- i) Depth of notches, total notch area, and distortion (RSS) of bus voltage distorted by commutation notches (low-voltage systems),

- ii) Individual and total voltage distortion, and

- iii) Individual and total current distortion.

Voltage Notching: Whenever ac voltage is rectified to dc with solid state switching devices, a phenomenon called commutation notching can occur. The duration of these notches in each ac voltage cycle is typically only a few microseconds, but they can last longer and cause equipment malfunction or resonance with attendant damage or loss to neighboring electrical equipment or the processes they control. Current Distortion When a customer's equipment draws current from the utility in a nonlinear or choppy manner, this is called current distortion. It always produces harmonics in the load current waveform and can produce significant harmonics in the voltage waveform at the PCC and elsewhere.

Current Distortion: The distribution side having responsibility to provide quality voltage to all its customers. If customers keep their voltage notching and current distortion within the limits, this will allow distribution to provide this service. Specifically, this service is defined as voltage having distortion levels within the limits.

#### 2.5 Power factor

Power factor is defined as the ratio of the average power to the apparent power drawn by a load from an AC source. Assuming an ideal sinusoidal input voltage source, the power factor can be expressed as the product of the distortion power factor and the displacement power factor, as given in equation (2.1). The distortion power factor  $K_d$  is the ratio of the fundamental root-mean-square (RMS) current ( $I_{rms(1)}$ ) to the total RMS current ( $I_{rms}$ ). The displacement power factor  $K_{\theta}$  is the cosine of the displacement angle between the fundamental input current and the input voltage [13].

$$PF = K_d K_\theta \tag{2.1}$$

The distortion power factor  $K_d$  is given by the following equation.

$$K_d = I_{rms(l)} / I_{rms} \tag{2.2}$$

The displacement power factor  $K_{\theta}$  is given by the following equation.

$$K_{\theta} = \cos\theta \tag{2.3}$$

The displacement power factor  $K_{\theta}$  can be made unity with a capacitor or inductor but making the distortion power factor  $K_d$  unity is more difficult. When a converter has less than unity power factor, it means that the converter absorbs apparent power that is higher than the active power it consumes. This implies that the power source should be rated to a higher VA rating than what the load needs. In addition, the current harmonics generated by the converter deteriorates the power quality [14] of the source, which eventually affects other equipment. High power factor and low harmonics do not go hand-in-hand. Though there is no a direct correlation between the two, the following equations link total harmonic distortion *(THD)* to power factor in some way.

$$THD(\%) = 100 \times \sqrt{\frac{1}{K_d^2} - 1}$$

(2.4)

The distortion power factor  $K_d$  is also given by the following equation.

$$K_{d} = \frac{1}{\sqrt{1 + \left(\frac{THD(\%)}{100}\right)^{2}}}$$

(2.5)

Therefore, when the fundamental component of the input current is in phase with the input voltage,  $K_{\theta}=1$ . We then have,

$$PF = K_d K_{\theta} = K_d \tag{2.6}$$

Substituting (2.5) in (2.6), we have

$$PF = \frac{1}{\sqrt{1 + \left(\frac{THD(\%)}{100}\right)^2}}$$

(2.7)

Moreover, a perfectly sinusoidal current could also have a poor power factor if its phase was not in line with the voltage. From (2.7) it is apparent that a 10% THD corresponds to a Power Factor of approximately 0.995. Thus it is clear that specifying limits for each of the harmonics will help in the control of input current "pollution" better, both from the standpoint of minimizing the circulating currents and reducing the interference with other equipment. So, while the process of shaping this input current is commonly called "power factor correction," the measure of its effectiveness towards complying with international regulations is the amount of reduction in the harmonic content of the input current.

#### 2.6 Review on Resonant Inverter Topologies in Electronic Ballast

As shown in Figure 2.6, electronic ballasts have a resonant inverter stage that converts the DC link voltage into high frequency AC signal to drive the fluorescent lamp. Most of the DC-AC conversion process in electronic ballasts is performed by using voltage source resonant inverters (VSI) due to its robustness, circuit simplicity (ease of achieving soft-switching), and it is easily implemented. The three basic types of resonant tank circuits used in VSIs are [15]: series loaded resonant (SLR); parallel loaded resonant (PLR); and series-parallel loaded resonant (SPLR). All of the aforementioned VSI resonant circuits are displayed in Figure 2.6. In the analysis presented in the next section, the lamp resistance is considered to be extremely high during the lamp ignition stage so the load of the resonant circuit is represented by an open circuit. After the lamp ignition, the lamp becomes a finite resistive load at the output of the resonant circuit and it begins to consume power at this stage. In Figure 2.6, *rfil* represents the lamp filament resistance and *R*<sub>lamp</sub> represents the steady-state lamp resistance.

#### 2.6.1 Half-Bridge Resonant Inverters [6]

The voltage source half-bridge resonant inverter is a common type of VSI that is used in electronic ballasts. There are three variations of the voltage source half-bridge resonant inverter configuration and they are illustrated in Figure 2.6. Since a high quality factor (Q) is normally selected for resonant circuit design (to reduce the harmonics at the output load), fundamental approximation is always used to simplify the circuit analysis. When performing fundamental approximation, only the fundamental component of the input square wave voltage  $(v_{ab})$  is considered. The voltage gain plots  $(|v_{out}/v_{abl}|)$  of the SLR, PLR and SPLR resonant circuits are given by Figure 2.7, where  $v_{ab1}$  represents the fundamental component of  $v_{ab}$ . In the SLR circuit case, it can be observed that  $|v_{out}/v_{abl}|$  is always equal to one regardless of any changes in  $Q_s$ .  $Q_s$  is defined by (Eq. 2.4), where  $f_o$  equals to the corner frequency of the resonant circuit and is given by (Eq. 2.5). When the SLR circuit operates close to resonance, the impedance provided by  $L_r$  and  $C_r$  cancels out each other. The ballast circuit elements then cannot provide current limiting function as  $v_{ab}$  is connected directly to the lamp. As a result, SLR circuit cannot be used in electronic ballast applications in an open-loop fashion. A control circuit is required to provide stable operation for the lamp current.

In the PLR circuit, the  $Q_p$  is defined by (Eq. 2.6), it can be observed that a high output voltage is obtained when  $Q_p$  is high (i.e. when  $R_{lamp}$  is large). Physically, this means that a high output voltage can be achieved during the lamp ignition process even in the absence of a step-up transformer [16]. A high output voltage can be obtained even when the input of the inverter is connected to a rectifier with low input line voltage [16]. After lamp ignition,  $R_{lamp}$  decreases and hence, Q decreases. According to Figure 2-8,  $|v_{out}/v_i|$  then decreases and allows the lamp voltage drops to its rated value. Therefore, the voltage gain characteristics of the PLR circuit are very desirable for electronic ballast applications. The SPLR circuit has the characteristics of both the SLR circuit and the PLR circuit. As a result, it has the advantages of the PLR circuit and the disadvantages of the SLR circuit. With regards to the SPLR, the series capacitor  $C_s$  and the parallel resonant capacitor  $C_p$  need to be properly tuned so that a sufficiently high voltage can be ensured during the lamp ignition process.

Figure 2.6 Basic Voltage Source Resonant Inverter Topologies.[6]

$$Q_s = \frac{2\pi f_0 L_r}{R_{lamp}}$$

(2.4)

$$f_0 = \frac{1}{2\pi f \sqrt{L_r C_r}} \tag{2.5}$$

$$Q_p = \frac{R_{lamp}}{2\pi f_0 L_r} \tag{2.6}$$

Figure 2.7 Voltage gain plots: (a) series LC resonant; (b) parallel LC resonant; (c) series parallel LC resonant [6]

In voltage source half-bridge resonant inverters, above resonance operation is preferred. By operating the resonant inverter at slightly above resonance, zero voltage switching (ZVS) is achieved at the switch turn-on transition. The key waveforms for above resonance operation are illustrated in Figure 2.8, where  $v_{ab}$ represents the input voltage of the resonant circuit and *id* represents the MOSFET drain-to-source current. When the resonant current ( $i_{res}$ ) is lagging behind the fundamental component of the MOSFET voltage ( $v_{ab1}$ ), the negative  $i_{res}$  flows through the anti-parallel diode of the MOSFET to allow the MOSFET to turn on with almost zero voltage drop. The turn-off switching loss can be minimized by adding a snubber capacitor across the switch (encircled in Figure 2.8) to slow down the turn-off rate of the switch voltage.

Figure 2.8 ZVS operating waveforms for voltage fed half-bridge resonant inverters[6]

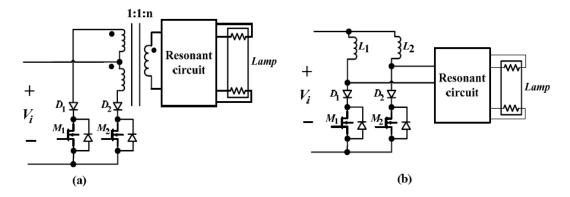

#### 2.6.2 Push-Pull Inverter Configuration [6]

Rather than having the MOSFETs arranged in a half-bridge configuration, they can alternatively be arranged in a push-pull configuration to form a different VSI topology for ballast applications. The main advantage of this topology is the isolation transformer located in front of the resonant tank circuit; it provides electrical isolation to the entire system with both switches referenced to ground. By doing so, isolation devices are not required to provide isolation in the driver circuit. However, it should be noted that the added transformer in the resonant circuit increases the weight and size of the power circuit. In addition, each switch will suffer a voltage stress of twice the input voltage when the other switch is off. Therefore, the push-pull configuration will usually require a MOSFET with a voltage rating much higher than that of the half-bridge inverter to achieve the same output power.

#### 2.6.3 Class E LCC Resonant Inverter [6]

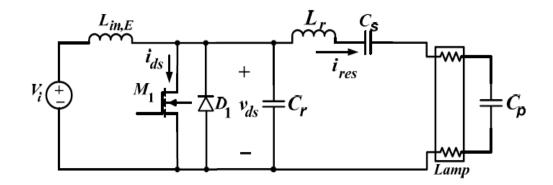

Class E LCC resonance inverter is another popular type of inverter circuit. The MOSFET gate driver circuit is much simpler. Figure 2.9 illustrates the operating waveforms of the class E inverter. By allowing the anti-parallel diode (D1) turn on prior to the turn-on of the MOSFET ( $to \sim t1$ ), ZVS is achieved at the turn-on of the MOSFET. The presence of  $C_r$  helps to reduce the turn-off switching loss (i.e. at t2). The resonant circuit composes of a series inductor  $(L_s)$ , a series DC-blocking capacitor  $(C_s)$  and a parallel capacitor  $(C_p)$ . The main drawback with the class E resonant inverter is the high voltage and current stress across the MOSFET. When the MOSFET is on, the current flowing through the MOSFET is comprised of both the input current  $(i_{in})$  and the resonant current  $(i_{res})$ . Thus, the conduction loss of the MOSFET will be higher than the total conduction loss of the two MOSFET in the half-bridge inverter configuration. In addition, when the class E inverter MOSFET is off, its peak voltage is equal to three to five times the input DC voltage. The increased current and voltage stress on the MOSFET, makes the class E resonant inverter less appealing for ballast applications where high line voltage (220-240 V<sub>rms</sub>) is required.

Figure 2.9(i) Class E resonance inverter [6]

Figure 2.9(ii) Class E resonant inverters key waveforms: (a) theoretical waveforms; (b) simulation waveforms.[6]

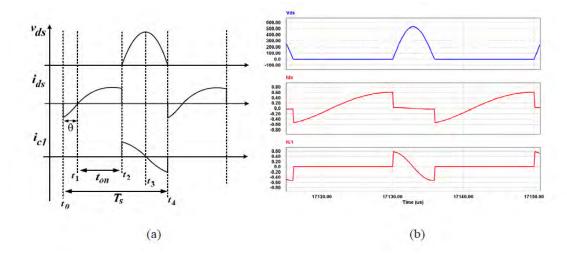

### 2.6.4 Current Source Inverters for Electronic Ballast.[18]

Current source inverter (CSI) is implemented by placing an inductor in series with the input DC voltage source so that a constant current input source can be formed for the inverter circuit. A common way to implement a CSI is to implement the switches in a push-pull configuration [17][18][19] as shown in Figure 2.10 (a). In some cases, instead of using the push-pull configuration at the inverter stage, the two primary windings are implemented by using two separate input inductors, as shown in Figure 2.10 (b) [20][21][22], to save one winding compared to the push-pull configuration. In both circuits, one diode is connected to each of the MOSFETs to disable the anti-parallel diode of the MOSFET. This allows a current square waveform generated at the input of the resonant circuit. To minimize the reverse-recovery loss in the series diodes, the input voltage of the resonant circuit [23][24].

Figure 2.10 Current fed resonant inverter in electronic ballast[18][21]

One advantage of using CSI at the inverter stage is that electrical isolation can be provided naturally for the MOSFET drivers and the power circuit without additional isolation devices. CSIs inherently have PFC when it is connected directly to the output of a rectifier. Its continuous input current is reflected back to the input of the rectifier and the line current is continuous and will naturally follow the sinusoidal shape of the line voltage. However, the direct connection between the CSI and the rectifier cannot be used for electronic ballast applications as the rectified line voltage will generate a sinusoidal envelope on the lamp current waveform, causing the lamp CF at the output to be very high. So, in order to use CSI for electronic ballast applications, some additional means of passive PFC is required.

## 2.7 Power Factor Correction (PFC) Techniques in Electronic Ballast [6]

Fluorescent lamps, like other electronic loads, draw current from the utility to function. Since the current drawn by the lamp is the same current that will be seen by the utility, it should have minimal amount of harmonics (high input PF) so that the least amount of energy will be wasted as reactive power. In electric lighting applications, the ballasts are required to comply with a certain set of regulations entitled IEC-1000-3-2 Class C (International Electro-technical Commission) [25] (see Table 2.1). According to Table 2.1, it can be observed that the maximum allowable THD is proportional to the PF of the ballasts to draw high PF; higher the PF, the less stringent the restriction on THD becomes.

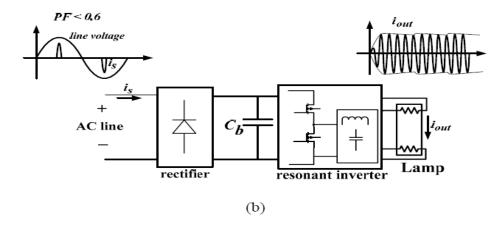

The simplest approach to implement PFC in electronic ballast designs is to connect the output of the rectifier directly cross the input of the inverter stage as shown in Figure 2.11. Although high PF is achieved, the lamp CF is high at the output. With a pure sinusoidal envelope imposed on the high frequency lamp current at the output, the lamp CF can easily go over the limit according to the ANSI standards [26]. However, if *Cb* is increased to reduce the output lamp CF, the presence of a large *Cb* significantly reduces the conduction time of the line current, which results in poor PF.

Table 2.1 Harmonic limits for IEC1000-3-2 Class C equipment [25]

| Harmonic Order (n) | Max harmonic as a % of fundamental of line current (%) |

|--------------------|--------------------------------------------------------|

| 2                  | 2                                                      |

| 3                  | 30*PF                                                  |

| 5                  | 10                                                     |

| 7                  | 7                                                      |

| 9                  | 5                                                      |

| 11 < n < 39        | 3                                                      |

(a)

Figure 2.11 (a): Electronic ballast without DC-link capacitor; (b) with DC-link capacitor. [6]

Therefore, electronic ballasts should have a PFC stage that allows the circuit to achieve both a high PF at the input and a good CF at the output. There are two different types of PFC techniques: active PFC and passive PFC. Different PFC circuits have been proposed for electronic ballast applications.

The major difference between active PFC and passive PFC is the way that they are implemented. Active PFC uses a DC-DC converter with modulation techniques that control the switch to shape the input line current. Passive PFC, on the other hand, only uses passive circuit components such as inductors, capacitors and diodes to achieve PFC. Numerous studies and comparisons have been conducted on the two different types of PFC techniques [27][28]. This section will highlight and describe the different kinds of PFC techniques that are used in electronic ballasts. This section will focus on the comparison between the performance of active PFC and passive PFC in electronic ballasts.

#### 2.7.1 Passive PFC in Electronic Ballasts [6]

Passive PFC, as its name implies, only passive circuit elements are used to achieve PFC. There is no control circuits required since switches are not used for PFC. The main advantage of using passive PFC over active PFC is that it has less circuit complexity, and is more cost effective. The main drawback of this approach however, is that large filters are required at the input to achieve comparable performance with that of active PFC. The three major types of passive PFC techniques used in electronic ballast applications are: (1) L-C filter approach, (2) valley-fill circuit approach and (3) Charge pump capacitors approach.

#### (1) L-C Filter Approach[29]

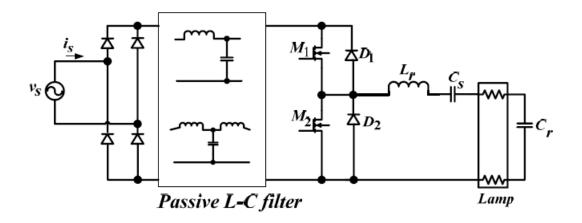

Several types of L-C filter circuits for passive PFC have been discussed in literature [29][30]. By placing a properly designed L-C filter between the rectifier and the inverter stage, as shown in Figure 2.12, the harmonic components of the input line current can be filtered out. Since the L-C filter is required to filter out the harmonics located at the multiples of the line frequency, an extremely large inductor and capacitor is necessary. It should also be noted that when a large capacitor is used in the L-C filter, it can introduce a phase difference between *vs* and *is*. Hence, the L-

C circuit is not used for PFC purposes; rather, it is only used as an electromagnetic interference (EMI) filter in electronic ballasts where smaller inductors and capacitors are used.

Figure 2.12 Passive L-C filter PFC electronic ballast [29]

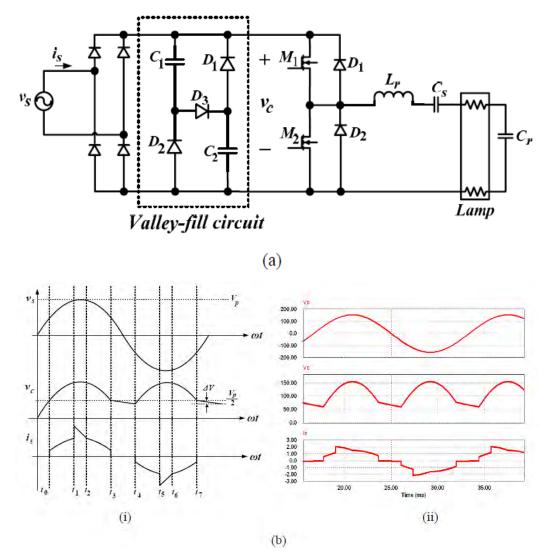

#### (2) PFC with valley-fill Circuit[32]

The valley-fill PFC approach is used in electronic ballast applications because the valley-fill circuit can achieve an input PF of 0.9 and is more costeffective than all the active PFC options. The valley-fill circuit consists of two capacitors and three diodes as shown in Figure 2.13(a) [31][32][33]. The key waveforms of the valley-fill circuit are shown in Figure 2.13(b). From Figure 2.13(b), it can be observed that at t = t1, diode D3 turns on, and the line voltage charges up both capacitors C1 and C2. This charging action of the both capacitors causes a peak in *is*. During the period t3 < t < t4, the voltage at the output of the rectifier (vc) is less than the line voltage and as a result, is equals to zero. One drawback of this PFC approach is the limited line current conduction time. The limited conduction time leads to a high THD where the magnitudes of the harmonics can exceed the IEC 1000-3-2 Class C standard. Another disadvantage of the valleyfill circuit is the low frequency voltage envelope generated at the input of the resonant inverter that results in high lamp current CF. In [33], frequency modulation control was proposed to regulate the lamp current so that the lamp current envelope will not affected by the low frequency voltage (generated by the valley-fill circuit).

Figure 2.13 (a): Valley-fill PFC electronic ballast; (b) its key waveforms: (i) theoretical waveforms; (ii) simulation waveforms [32][34]

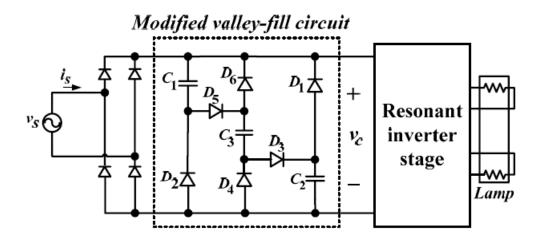

To improve the THD problem in the conventional valley-fill circuit, the authors in [34] proposed a modified VF circuit (see Figure 2.14). An additional capacitor and three diodes were added to the conventional circuit to extend the line current conduction angle. With the modified VF circuit, a PF of at least 0.97 was achieved. This circuit also generates larger voltage variation at the input of the inverter stage when compared to the conventional valley-fill circuit. This means that the lamp CF will be higher when the modified valley-fill circuit is used rather than the conventional valley-fill circuit. However, frequency modulation (as discussed in [33]) can be used for the modified valley-fill circuit to regulate the lamp cF is maintained.

Figure 2.14 Modified valley-fill PFC circuit.[34]

#### (3) PFC with Charge-pump Technique.[35]

Another passive PFC circuit used in electronic ballasts is based on the charge pump PFC concept [35] [36]. This PFC circuit was developed to eliminate the need of a large inductor that would normally be used in the boost PFC circuit. The circuit diagram of a charge-pump PFC electronic ballast is given in Figure 2.15. By using the charge-pump PFC circuit, the line current is regulated to follow the input line voltage by diode  $D_{in}$  and capacitor  $C_{in}$ . The idea behind this PFC strategy is to have  $C_{in}$  regulate the input current by forcing the voltage DC-link voltage  $v_{dc}$  to always be higher than the input voltage vs. In this way, the positive input current will be equal to the charging current of  $C_{in}$ . If the voltage variation across  $C_{in}$  follows the input sine rectified voltage, the input current will follow the shape of the input voltage and thus high PF will be achieved. This PFC technique is very attractive for high PF ballast circuit designs because the conventional PFC inductor used in the DCM boost converter is too bulky and needs to handle high current. Careful design of the boost PFC inductor is always required.

Figure 2.15 Charge-pump PFC electronic ballast.[35]

Although charge-pump PFC concept is able to reduce the overall cost by reducing the number of inductors, it has its disadvantages as well. Since a high value of  $v_{dc}$  is necessary to provide the required ignition voltage across the lamp, the first disadvantage is the high DC-link voltage across  $C_b$  during the lamp ignition process. Secondly, the charge-pump has a high lamp CF at the output. Since the capacitor  $C_{in}$  becomes part of the resonant circuit at the inverter stage, the voltage across  $C_{in}$ , has the shape of a rectified sinusoidal signal and is reflected on the envelope of the output lamp current. Consequently, a continuously varying voltage signal with twice the line frequency will be imposed on the lamp CF problem is to modify the charge-pump circuit by adding clamping diodes to the original circuit. These diodes limit the peak of the sinusoidal envelope imposed on the high frequency output signal. It should also be noted that the addition of the clamping diodes does not affect the high PF achieved at the input (as with the original circuit). Therefore, low lamp CF can be achieved at the expense of additional diodes in the ballast power circuit.

#### 2.7.2 Limitations of Passive PFC Circuits

The simplicity, reliability, insensitivity to noise and surges and the nongeneration of any high-frequency EMI offered by passive power factor circuits are of significant usefulness. However, the bulky size of these filters, their poor dynamic response, complexity and high cost, the lack of voltage regulation and their sensitivity to line-frequency, limits their use to below 200 W applications. Moreover, even though line current harmonics are reduced, the fundamental component may show an excessive phase shift resulting in reduction in power factor.

### **2.7.3** Active Power Factor Correction Methods

Active PFC circuits that have better characteristics and do not have many of the above drawbacks are reviewed in the following sections.

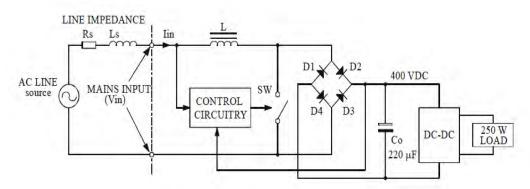

## 2.7.3.1 Low Frequency Active PFC.[37]

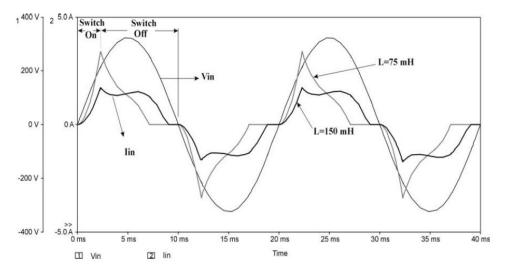

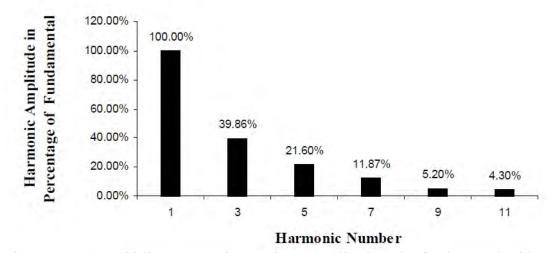

An active low frequency PFC circuit for a 250W constant power load is shown in Figure 2.16(a). Input Power factors as high as 0.95 can be achieved with an active low frequency PFC circuit design. In this scheme, the switch (SW) is bidirectional and it is operated for a constant period after the line voltage zero crossing. After this constant on-period after the line voltage zero crossing or when the output voltage tries to increase beyond the set limits, this switch (SW) is turned off. This forces an increase in the conduction angle [38] of the input bridge rectifiers, giving rise to an acceptable current waveform. Simulated input current and voltage waveforms for an active low frequency PFC circuit with a 250 W constant power load and two different inductance values of 150 mH and 75 mH, is shown in Figure 2.16(b). The odd line current harmonics normalized to the fundamental is shown in Figure 2.16(c) and Figure 2.16(d). This scheme has the advantage that it generates less EMI, requires a smaller inductor when compared to the passive PFC and the simple low frequency circuit is more reliable and efficient when compared to the active high frequency PFC scheme described later. However, when compared to the high frequency active PFC circuit, the reactive elements are larger and the regulation of the output voltage is slower.

Figure 2.16(a). Typical schematic of a low frequency active PFC circuit.[37]

Figure 2.16(b). Simulated input current and voltage waveforms for a 250 W constant power load with low frequency active PFC circuit and inductance values of 75 mH and 150 mH.[37]

Figure 2.16(c). Odd line current harmonics normalized to the fundamental with a 250 W constant power load for a low frequency active PFC circuit with an inductance value of 75 mH.[37]

Figure. 2.16(d). Odd line current harmonics normalized to the fundamental with a 250 W constant power load for a low frequency active PFC circuit with an inductance value of 150 mH.[37]

## 2.7.3.2 High Frequency Active PFC

The high frequency active PFC circuit can be realized by placing a buck or a boost or a buck-boost or a cuk (inverse buck-boost) converter in between the bridge rectifier and the filter capacitor of a conventional rectifier filter circuit and operating it by a suitable control method that would shape the input current. For all converter topologies, the switching frequency is much higher than the line-frequency, the output voltage ripple is twice the line-frequency and the output DC is usually regulated. The PFC output voltage can be higher or lower, depending on the type of converter being used. With a buck converter the output voltage can be lower, for a boost converter the output voltage can be higher, while for a buck-boost converter the output voltage can be higher or lower than the maximum amplitude of the input voltage and for a cuk converter is same as buck-boost but output is opposite to the input voltage. The inductor current in these converters can be either continuous or discontinuous. In the continuous conduction mode (CCM) the inductor current never reaches zero during one switching cycle while in the discontinuous conduction mode (DCM), the inductor current is zero during intervals of the switching cycle. However, though the inductor current can be continuous in all the three types of converters, the high frequency switching current components of the AC input

current can be continuous only in the case of the boost converter. This is because for the buck and the buck-boost converter, the converter switch interrupts the input current in every switching cycle. This is apparent from the operating characteristics of each converter described below. The given waveforms are representative and shown only for explanation of the topology specific characteristics. In reality, the switching frequency is much higher than the line-frequency and the input AC current waveform is dependent on the type of control being used. The inductors are assumed to be in the CCM of operation.

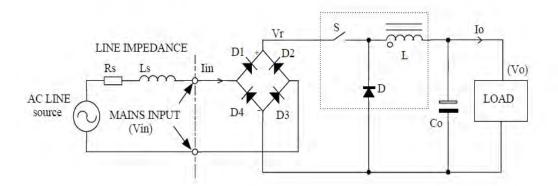

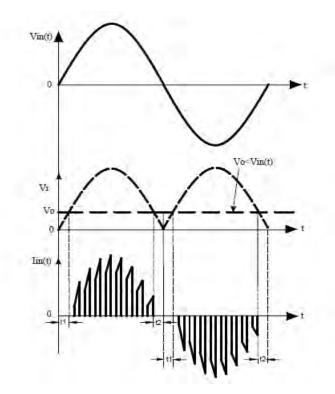

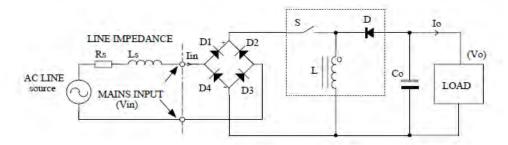

## 2.7.3.2.1 Buck Converter Based Active PFC [39]

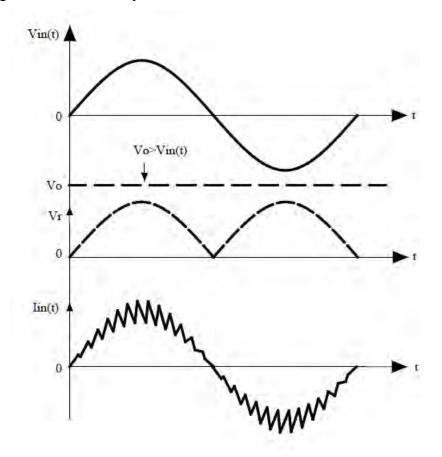

A buck converter based PFC circuit that steps down the input voltage is shown in Figure 2.17(a) and Figure 2.17(b) shows its associated waveforms. However since the converter can operate only when the instantaneous input voltage  $V_{in}(t)$  is higher than the output voltage  $V_o$ , there is no current flow from the AC input during the period t1 and t2. This gives the line current envelope a distortion near the input voltage zero crossing. Moreover, even if the inductor current is continuous, the input switching current of the converter is discontinuous as the high frequency switch S interrupts the input current during every switching cycle. Thus, the input current has a significant high-frequency component that increases EMI and filtering requirements.

Figure 2.17(a). Buck converter based high frequency active PFC circuit.[39]

Figure 2.17(b) Current and voltage waveforms of a Buck converter based PFC circuit.[39]

# 2.7.3.2.2 Boost Converter Based Active PFC.[39]

The boost converter, the most common topology used for power factor correction, can operate in two modes – continuous conduction code (CCM) and discontinuous conduction mode (DCM). The transition mode control, also referred to as critical conduction mode (CRM) or boundary conduction mode, maintains the converter at the boundary between CCM and DCM by adjusting the switching frequency. A CCM boost converter based PFC circuit and its associated waveforms are shown in Figure (a) and Figure 2.18(b).

Figure 2.18(a). Boost converter based high frequency active PFC circuit.[39]

This topology steps up the input voltage. Since the converter can operate throughout the line-cycle, the input current does not have crossover distortions. This gives the line current envelope no distortion near the input voltage zero crossing. Moreover, the input switching current of the converter is continuous as the boost inductor is placed in series with the input, and the high frequency switch S does not interrupt the input current. Thus, the input current has lesser high-frequency components resulting in lower EMI and reduced filtering requirements. The output capacitor Co limits the switch S"s turn-off voltage to almost the output voltage through diode D and thus protects the switch.

Figure 2.18(b). Current and voltage waveforms of a CCM boost converter based PFC circuit.[39]

In the above converter, the control scheme can force the current in the inductor to be either continuous or discontinuous. The DCM converter operates at fixed frequency and has switching current discontinuities in comparison to the CCM or CRM techniques. Due to the large peak currents and EMI associated with the

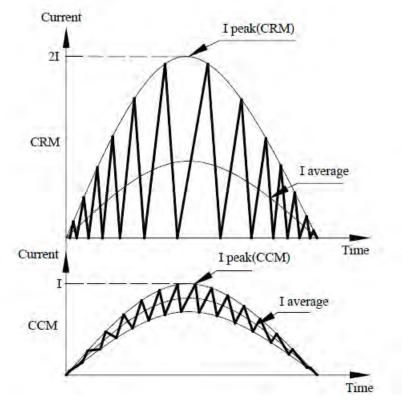

DCM converter, it is rarely or never used. These large peak currents are due to the dead time needed at certain instantaneous input voltages to remain discontinuous over all input line variations. On the other hand the CRM converter typically uses a variation of hysteretic control with the lower boundary equal to zero current. It is a variable frequency control technique that has an inherently stable input current control while eliminating reverse recovery rectifier losses. For a given set of input and output parameters, the on-time remains the same, but the off- time is varied. The result of this is that the switching frequency of the power converter is highest when the instantaneous input voltage is the lowest, and vice versa.

The power stage equations and the transfer functions of the CRM converter are the same as the CCM converter. Transition mode forces the inductor current to operate just at the border of CCM and DCM. The current profile is also different and affects the component power loss and filtering requirements. The peak current in the CRM boost converter is twice the amplitude of the CCM boost converter leading to higher conduction losses. The peak-to-peak ripple is twice the average current, which affects MOSFET switching losses and AC losses in the boost inductor. The main trade-off in using the CRM boost converter is lower losses due to no reverse recovery in the boost diode at the expense of higher inductor ripple and peak currents.

For medium to higher power applications, where the input filter requirements dominate the size of the magnetic, the CCM boost converter is a better choice due to lower peak currents (which reduces conduction losses) and lower ripple current (which reduces input filter requirements and inductor AC losses).

For these reasons, the CCM converter is popular and used widely for PFC circuit applications where the power rating is greater than 100 W. The inductor current for a 100 W converter operating in the CCM and CRM mode, are compared in Figure 2.19. The peak inductor current is shown as  $I_{peak}$  while the average inductor current is shown as  $I_{average}$ .

Figure 2.19. Comparison of inductor current for CCM and CRM operating modes.[39]

## 2.7.3.2.3 Buck-Boost Converter Based Active PFC.[39]

The buck-boost converter based PFC circuit and its associated waveforms are shown in Figure 2.20(a) and Figure 2.20(b). This can step up or step down the input voltage. The output voltage is inverted, which translates into higher voltage stress for the switch. Since the converter can operate throughout the line-cycle, the input current does not have crossover distortions. This gives the line current envelope no distortion near the input voltage zero crossing. However, even if the inductor current is continuous, like the buck converter, the input switching current of the converter is discontinuous as the high frequency switch S interrupts the input current. Thus, the input current has significant high-frequency components that increase EMI and filtering requirements.

Figure 2.20(a). Buck-boost converter based high frequency active PFC circuit.[39]

Figure 2.20(b). Current and voltage waveforms of buck-boost converter based PFC circuit.[39]

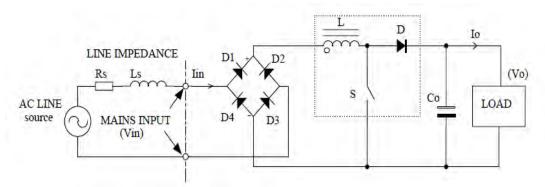

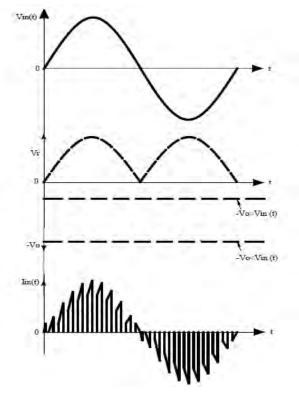

# 2.7.3.2.4 Cuk Converter Based Active PFC [39]

Lastly, the cuk converter based PFC circuit and its main advantage is it operates in continuous conduction mode (CCM) and so the input current follow the input voltage wave. Two inductors and one capacitor are used for energy transfer and continuous conduction is occurring though those capacitor and inductor. The converter based PFC circuit and associated waveforms are shown in Figure 2.21(a) and Figure 2.21(b). This can step up or step down the input voltage. Since the converter can operate throughout the line-cycle, the input current does not have crossover distortions. This gives the line current envelope no distortion near the

input voltage zero crossing. Moreover, the input switching current of the converter is continuous as the inductor is placed in series with the input, and the high frequency switch S does not interrupt the input current. Thus, the input current has lesser high-frequency components resulting in lower EMI and reduced filtering requirements. The capacitor C limits the switch S''s turn-off voltage to almost the output voltage through diode D and thus protects the switch. The output voltage is inverted like buck-boost converter.

Figure 2.21(a). Cuk converter based high frequency active PFC circuit.[39]

Figure 2.21(b). Current and voltage waveforms of Cuk converter based PFC circuit.[39]

## 2.8 Zero-Voltage-Switching Resonance Converters [40]

The switches of ZVS resonant converters turn on and off at zero voltage.

(c) Ful-wave

Figure 2.22 Switch Configurations for ZVS Resonant Converters.[40]

The capacitor C is connected in parallel with the switch S1 to achieve ZVS. The internal switch capacitance Cj is added with the capacitor C and it affects the resonant frequency only, thereby contributing no power dissipation in the switch. If the switch is implemented with transistor Q1 and an anti-parallel diode D1 as shown, the voltage across C is clamped by D1 and the switch is operated in half wave configuration. If the diode D1 is connected in series with Q1 as shown, the voltage across C can oscillate freely and the switch is operated in full wave configuration. A ZVS resonant converter is shown. A ZVS resonant converter is the dual of ZCS resonant converter.

Figure 2.23 ZVS circuit [40]

Figure 2.24 modes in operation with equivalent circuit [40]

Figure 2.25 Waveform of ZVS resonance converters [40]