# Analytical Modeling of Current-Voltage Characteristics of Ferroelectric Tunneling Field Effect Transistor

A thesis submitted in partial fulfillment of the requirement of the degree of Master of Science in Electrical and Electronic Engineering

> by S. M. Farhaduzzaman Azad

Department of Electrical and Electronic Engineering Bangladesh University of Engineering and Technology (BUET) Dhaka-1000, Bangladesh April 2013

# DECLARATION

It is hereby declared that this thesis or any part of it has not been submitted elsewhere for the award of any degree or diploma.

Signature of the candidate

(S. M. Farhaduzzaman Azad)

### APPROVAL CERTIFICATE

The thesis titled **"Analytical Modeling of Current-Voltage Characteristics of Ferroelectric Tunneling Field Effect Transistor"** submitted by S. M. Farhaduzzaman Azad, Roll No.: 040806209P, Session: April 2008 has been accepted as satisfactory in partial fulfillment of the requirement for the degree of Master of Science in Electrical and Electronic Engineering on April 10, 2013.

### **BOARD OF EXAMINERS**

1.

2.

3.

Chairman

Department of Electrical and Electronic Engineering BUET, Dhaka-1000, Bangladesh

Dr. Quazi Deen Mohd Khosru

Professor

Dr. Pran Kanai Saha Professor and Head Department of Electrical and Electronic Engineering BUET, Dhaka-1000, Bangladesh

Member

Member

(Ex-officio)

Dr. Md. Shafiqul Islam Professor Department of Electrical and Electronic Engineering BUET, Dhaka-1000, Bangladesh

4.

Dr. Md. Anwarul Abedin Professor Department of Electrical and Electronic Engineering DUET, Gazipur-1700, Bangladesh Member (External)

#### ACKNOWLEDGEMENT

I am highly pleased to express my sincere and profound gratitude to my supervisor Dr. Quazi Deen Mohd Khosru, Professor, Department of Electrical and Electronic Engineering (EEE), Bangladesh University of Engineering and Technology, Dhaka, for providing me the opportunity to conduct graduate research in semiconductor devices. I wish my hearty thanks to him for his continuous guidance, suggestions and wholehearted help throughout the course of the work.

I would also like to thank specially, Md. Nadim Chowdhury, Lecturer, Department of EEE, BUET and Md. Ahmad Zubair, Lecturer, Department of EEE, BUET for their support and continuous encouragement. I am also thankful to all personnel of departmental library, BUET reference library and IEEE Bangladesh section.

I like to express my heartfelt thanks and the deepest gratitude to my parents and specially my wife for their invaluable encouragement and patience.

Finally, I am grateful to Almighty Allah for enabling me to complete the thesis.

S. M. Farhaduzzaman Azad

BUET, Dhaka Bangladesh April 2013.

#### ABSTRACT

In this work a modified structure of Tunneling Field Effect Transistor (TFET) has been proposed incorporating Ferroelectric oxide as the gate oxide, called the Ferroelectric Tunneling FET (Fe-TFET). The TFET device is one of the novel devices for a low-power digital application due to their band to band tunneling mechanism and it exhibits a very small leakage current, high drive current and lower subthreshold slope. Fe-FET is also introduced by integrating ferroelectric material operating in the negative capacitance region that acts as a step-up transformer of the surface potential in a traditional MOSFET structure to achieve a steeper subthreshold slope. The proposed device (Fe-TFET) effectively combines the mechanism of TFET and the theoretical concept of Fe-FET. A simple tentative analytical ON current model of the proposed device is also presented here. By using the double gate configuration of this newly modified device named Fe-TFET, it is feasible to achieve much lower SS and can get sufficiently high drive current at a very low operating voltage. Fe-TFET gives ON current as high as 0.02 A/µm for a gate voltage of 0.4V, according to the results yielded from the analytical model. Thus the  $I_{\text{ON}}/I_{\text{OFF}}$  ratio becomes  $\sim 10^8$  which is greater than that of a MOSFET and also for traditional TFET. OFF current exponentially increases with the threshold voltage reduction. So, in order to limit OFF current while maintaining a satisfactory ON current the subthreshold slope has to go down. This work provides physics based reasoning behind the multiplicative improvement in the subthreshold slope for the proposed device which gives ~40mV/dec subthreshold slope. Finally it demonstrates that the device performance can be amended in accordance with the technology of different band gap materials like Si, GaAs, Ge and InAs and different Ferroelectric oxides like BaTiO<sub>3</sub> and SrTiO<sub>3</sub>.

# **Table of Contents**

| Contents             | Page<br>no. |

|----------------------|-------------|

|                      | 101         |

| Declaration          | ii          |

| Approval Certificate | iii         |

| Acknowledgement      | iv          |

| Abstract             | V           |

| List of Figures      | ix          |

| List of Tables       | XV          |

| List of Symbols      | xvii        |

# **Chapter 1: Introduction**

| 1.1 Preface                               | 1  |

|-------------------------------------------|----|

| 1.2 Literature Review                     | 2  |

| 1.3 Basic Structure of Tunneling FET      | 3  |

| 1.4 TFET Characteristics                  | 4  |

| 1.4.1 Band to Band tunneling              | 5  |

| 1.4.2 Subthreshold Slope                  | 6  |

| 1.5 Ferroelectric FET Structure           | 8  |

| 1.6 Proposal of Ferroelectric TFET device | 12 |

| 1.7 Objective of this Study               | 13 |

| 1.8 Thesis Outline                        | 13 |

# Chapter 2: Double Gate Ferroelectric TFET

| 2.1 Introduction                                    | 15 |

|-----------------------------------------------------|----|

| 2.2 Double Gate Structure of Fe-TFET                | 15 |

| 2.3 Ferroelectric Oxide                             | 16 |

| 2.4 Double Gate Ferroelectric TFET Device Structure |    |

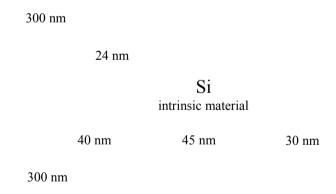

| 2.4.1 Si Tunneling Fe-TFET Scheme                   | 20 |

| 2.4.2 Ge Tunneling Fe-TFET Scheme                   | 20 |

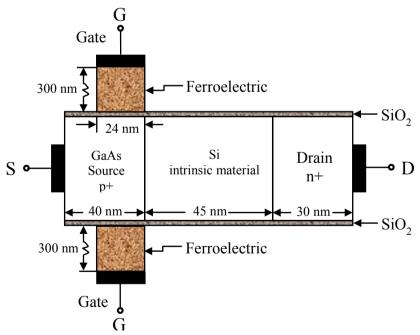

| 2.4.3 GaAs Tunneling Fe-TFET Scheme                 | 21 |

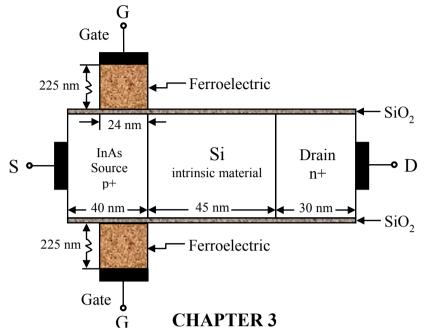

| 2.4.4 InAs Tunneling Fe-TFET Scheme                 | 21 |

# **Chapter 3: Analytical Modeling of Double Gate Fe-TFET**

| 3.1 Introduction                                                  | 22 |

|-------------------------------------------------------------------|----|

| 3.2 Solve 1-D Poisson's Equation                                  | 23 |

| 3.3 Modeling of Surface Potential using Landau-Khalatnikov Method | 24 |

| 3.4 Evaluation of onset voltage, V <sub>onset</sub>               | 27 |

| 3.5 Evaluation of ON Current Equation using Kane's Model          | 27 |

# **Chapter 4: Optimization of Device Performance**

| 4.1 Introduction                                     | 32 |

|------------------------------------------------------|----|

| 4.2 Device characteristics for Si, GaAs, Ge and InAs | 33 |

| 4.3 Impact of different Ferroelectric material       | 36 |

| 4.4 Impact of Oxide thickness                        | 40 |

| 4.5 Impact of Source Doping Concentration            | 50 |

| 4.6 Impact of Gate Length                            | 57 |

| 4.7 Comparison with semi classical Double Gate TFET  | 61 |

| 4.8 Optimization of Subthreshold Slope (SS)          | 63 |

| 4.9 Improvement of $I_{ON}/I_{OFF}$                  | 67 |

# **Chapter 5: Conclusion**

| 5.1 Conclusion of This Study    | 70 |

|---------------------------------|----|

| 5.2 Suggestion for Future Works | 71 |

# Bibliography

74

#### **List of Figures**

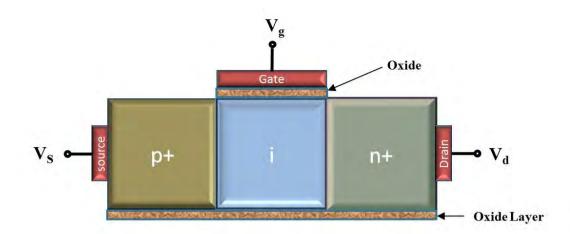

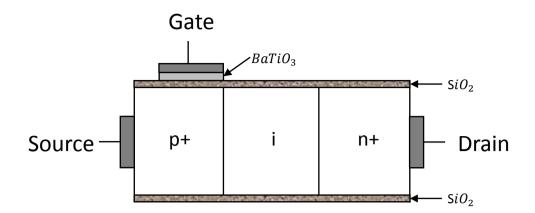

- **Figure 1.1** A simple Tunnel FET device structure, a p-i-n diode with one 4 gate

- **Figure 1.2** A simple Tunnel FET device structure, an n-i-p diode with one 4 gate.

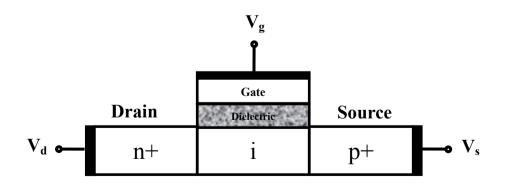

- Figure 1.3 Energy band diagrams taken horizontally across the body of a 5 TFET in (a) the off-state where the only current comes from p-i-n leakage, (b) the on-state with a negative bias on the gate leading to p-type TFET behavior, and (c) the on-state with a positive bias on the gate leading to n-type TFET behavior.

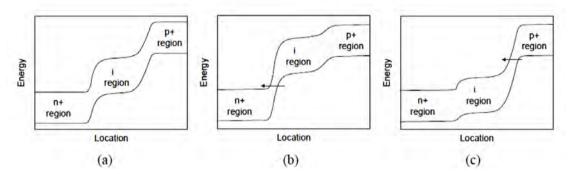

- **Figure 1.4** Energy barrier width dependence with the variation of gate 6 voltage for several different gate dielectric constants

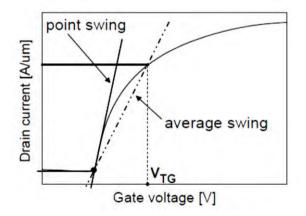

- Figure 1.5 Visual definitions of point swing, taken at the steepest point of 7 the  $I-V_g$  curve, and average swing, taken as the average from turn-on to threshold.

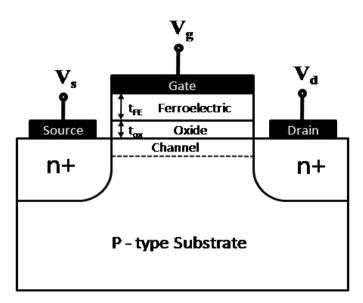

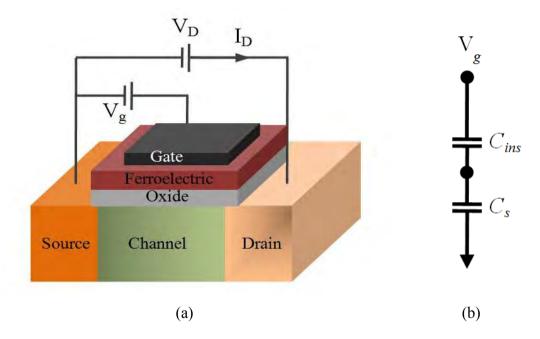

- Figure 1.6 Cross-section of Ferroelectric FET.

9

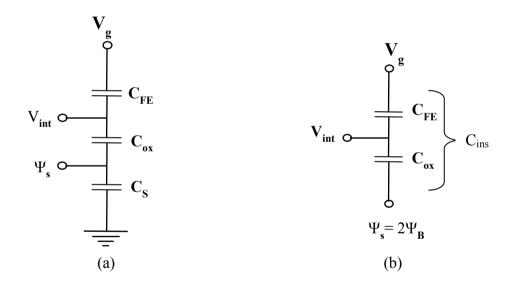

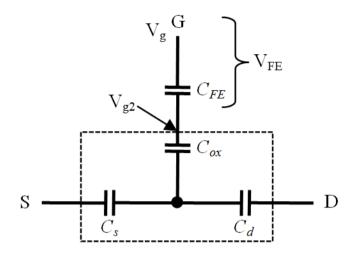

- Figure 1.7 (a) The equivalent capacitance model in the substrate to gate 9 region (b) The capacitance model in the ferroelectric and oxide region.

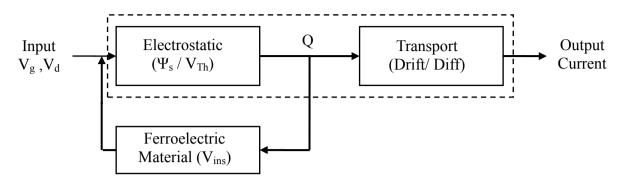

- **Figure 1.8** The integration of the ferroelectric material into traditional FET 10 model

- Figure 1.9 The insulator capacitance  $C_{ins}$  is in series with another 11 capacitance  $C_s$ .  $C_s$  comprises of the body capacitance, the channel to source capacitance, the channel to drain capacitance

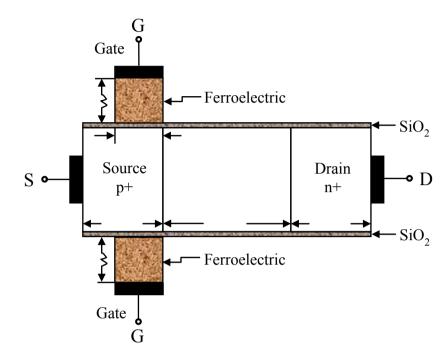

- Figure 1.10Cross section of Ferroelectric Tunneling FET with one gate13

- **Figure 2.1** (a) The energy landscape of ferroelectric showing negative 16 capacitance. (b) The energy landscape of a usual capacitor. The landscape shows well known  $Q^2/2C$  dependence. (c) Derivative dU/dQ vs. Q found from (a). (d) Derivative dU/dQ vs. Q found from (b).

- Figure 2.2 (a) Schematic of a FET with the gate circuit. (b) The insulator 17 capacitance  $C_{ins}$  is in series with another capacitance  $C_s$ .  $C_s$  comprises of the body capacitance, the channel to source capacitance, the channel to drain capacitance.

- **Figure 2.3** The capacitive model shown in Figure 2.2(a) is modified by 18 putting a ferroelectric insulator on top of a SiO<sub>2</sub> layer

- **Figure 2.4** Design considerations: Variation of  $Vg_2$  and  $V_{FE}$  as a function of 19 particle density inside the channel. For the low bias region the more dominant parameter is  $\alpha$  and for high bias region it is  $\beta$ . Hence an appropriate combination of  $\alpha$  and  $\beta$  will provide a suitable matching.

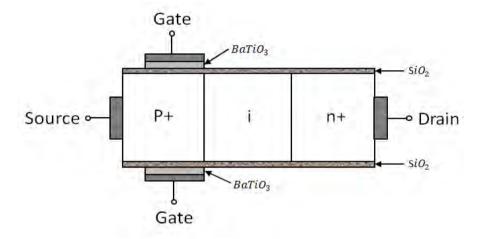

- Figure 2.5 Double Gate ferroelectric tunnel field effect transistor with the 19 gate is located fully on top of the source

- Figure 2.6Double Gate ferroelectric Si tunneling field effect transistor with20the gate is located fully on top of the Source

- Figure 2.7 Double Gate ferroelectric Ge tunneling field effect transistor 20 with the gate is located fully on top of the Source

- **Figure 2.8** Double Gate ferroelectric GaAs tunneling field effect transistor 21 with the gate is located fully on top of the Source

- **Figure 2.9** Double Gate ferroelectric InAs tunneling field effect transistor 21 with the gate is located fully on top of the Source

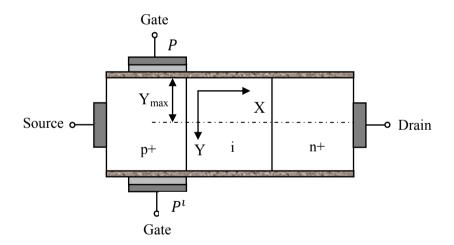

- **Figure 3.1** DG Fe-TFET with positive gate bias applied such that a 23 depletion region with thickness Y<sub>max</sub> exists (only upper half shown)

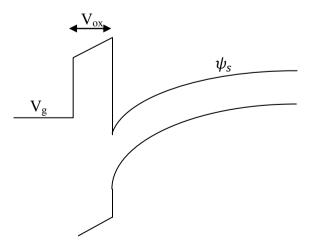

- **Figure 3.2** Energy band diagram of metal, ferroelectric oxide and 24 semiconductor junction

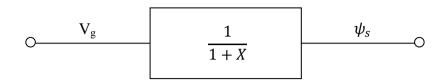

- Figure 3.3 Auto-Transformer relationship between gate voltage and surface 26 potential

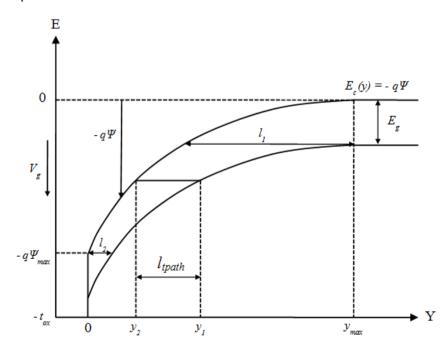

- Figure 3.4 Band diagram of the cross-section  $P-P^1$  from Figure 3.1 28 indicating  $l_{tpath}$

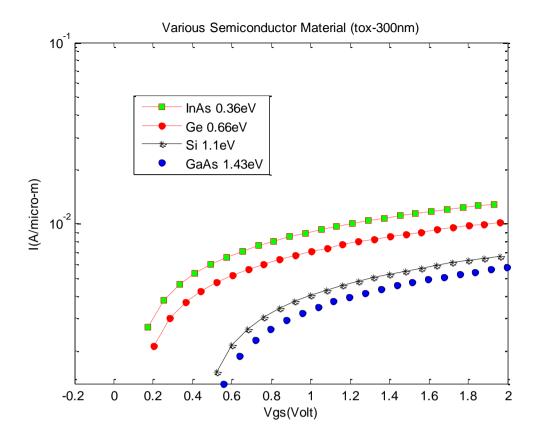

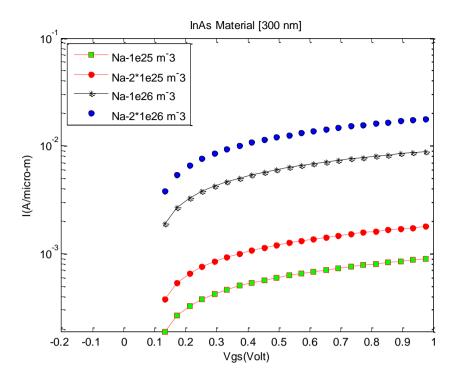

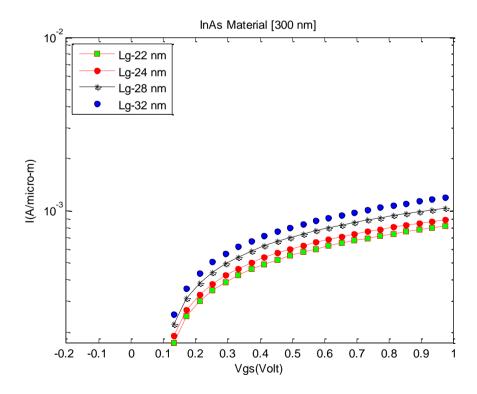

- Figure 4.1 I-V<sub>gs</sub> characteristics curve of DG Fe-TFET for different 34 semiconductor material with fixed ferroelectric oxide thickness,  $t_{ox} = 300 \text{ nm}$

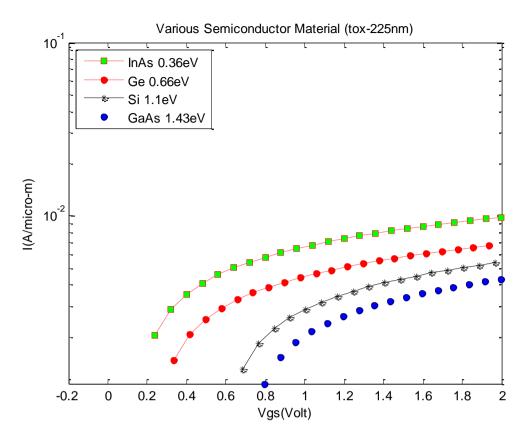

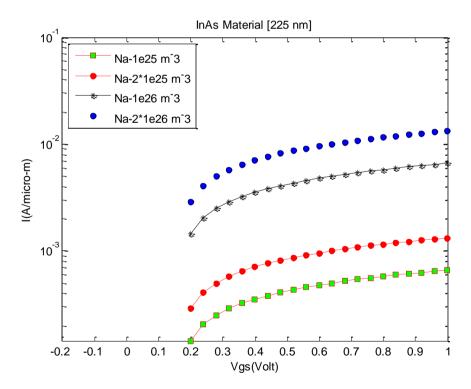

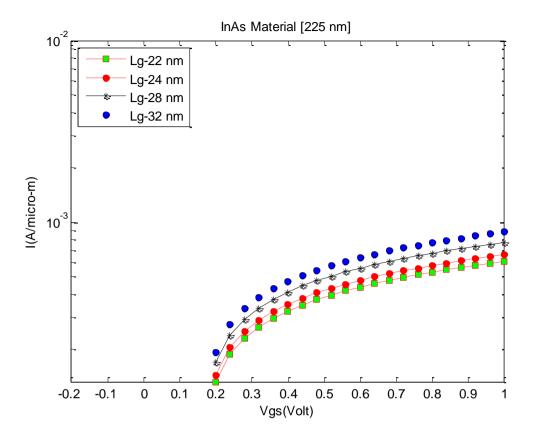

- Figure 4.2 I-V<sub>gs</sub> characteristics curve of DG Fe-TFET for different 35 semiconductor material with fixed ferroelectric oxide thickness,  $t_{ox} = 225 \text{ nm}$

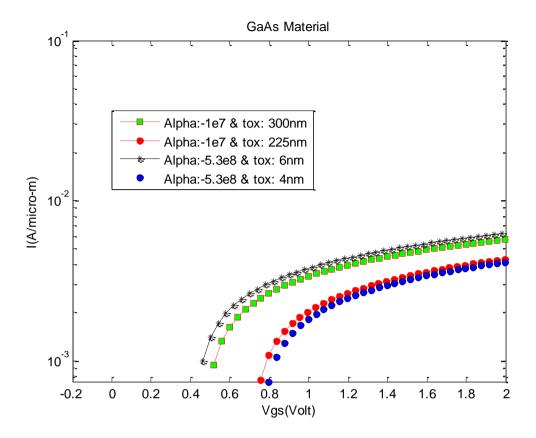

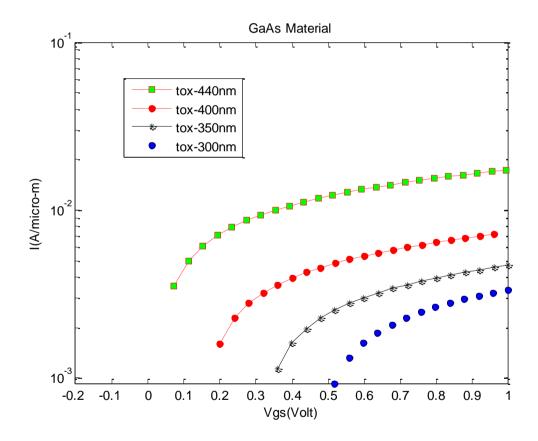

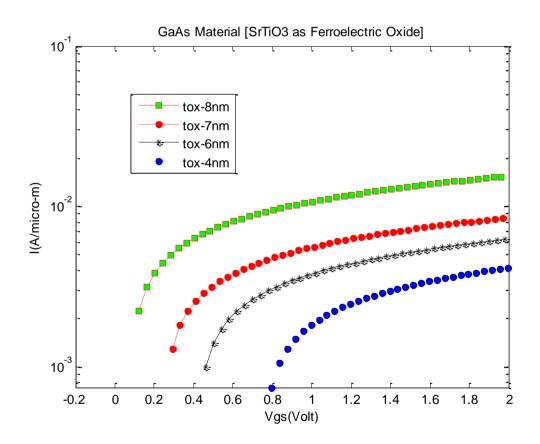

- Figure 4.3 Impact of varying the ferroelectric material on the log scale  $I-V_{gs}$  37 transfer characteristics for the DG Fe-TFET with fixed gate length,  $L_g = 24$  nm and also varying the ferroelectric oxide thickness for different consideration in case of GaAs Material.

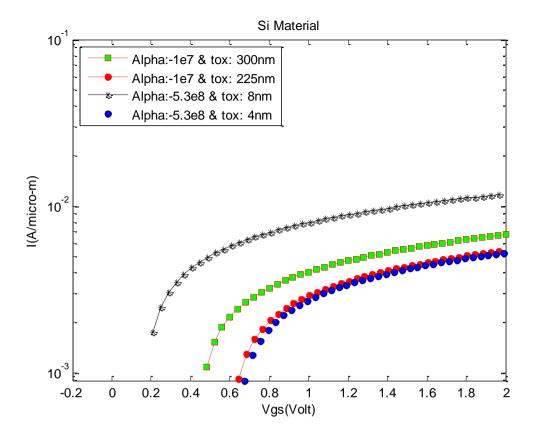

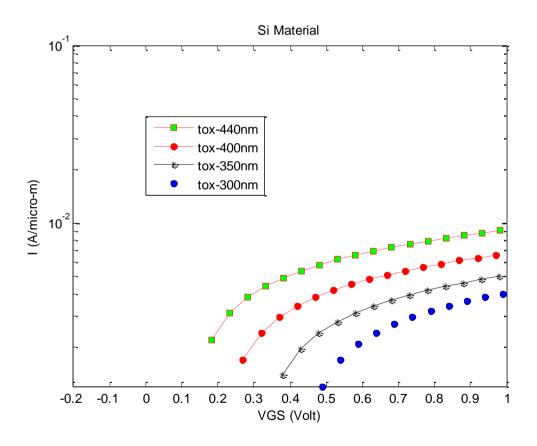

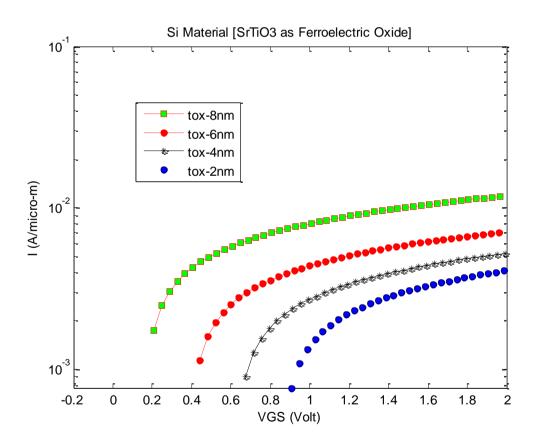

- Figure 4.4 Impact of varying the ferroelectric material on the log scale  $I-V_{gs}$  38 transfer characteristics for the DG Fe-TFET with fixed gate length,  $L_g = 24$  nm and also varying the ferroelectric oxide thickness for different consideration in case of Si Material.

- Figure 4.5 Impact of varying the ferroelectric material on the log scale  $I-V_{gs}$  39 transfer characteristics for the DG Fe-TFET with fixed gate length,  $L_g = 24$  nm and also varying the ferroelectric oxide thickness for different consideration in case of Ge Material.

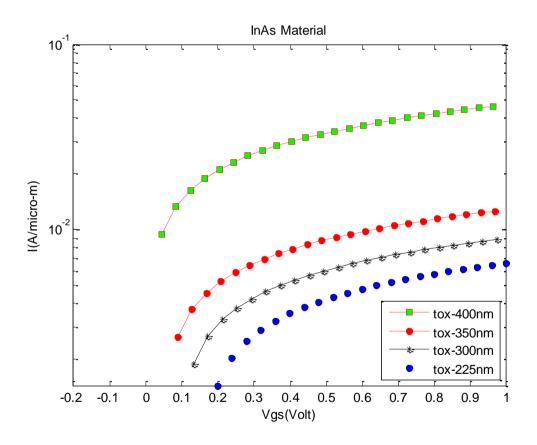

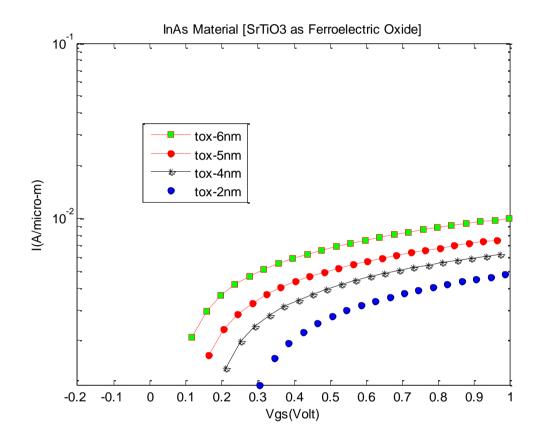

- **Figure 4.6** Impact of varying the ferroelectric material on the log scale  $I-V_{gs}$  40 transfer characteristics for the DG Fe-TFET with fixed gate length,  $L_g = 24$  nm and also varying the ferroelectric oxide thickness for different consideration in case of InAs Material.

- Figure 4.71 Transfer characteristics of showing the impact of varying the 42 thickness of ferroelectric oxide, BaTiO<sub>3</sub> on I-V<sub>gs</sub> curve of DG Fe-TFET in case of GaAs Material with Source Doping Concentration, Na= $10^{25}$  m<sup>-3</sup>

- Figure 4.72 Transfer characteristics of showing the impact of varying the 43 thickness of ferroelectric oxide,  $SrTiO_3$  on  $I-V_{gs}$  curve of DG Fe-TFET in case of GaAs Material with Source Doping Concentration,  $Na=10^{25}$  m<sup>-3</sup>

- Figure 4.81 Transfer characteristics of showing the impact of varying the 44 thickness of ferroelectric oxide,  $BaTiO_3$  on  $I-V_{gs}$  curve of DG Fe-TFET in case of Si Material with Source Doping Concentration, Na=10<sup>25</sup> m<sup>-3</sup>

- **Figure 4.82** Transfer characteristics of showing the impact of varying the 45 thickness of ferroelectric oxide,  $SrTiO_3$  on  $I-V_{gs}$  curve of DG Fe-TFET in case of Si Material with Source Doping Concentration, Na=10<sup>25</sup> m<sup>-3</sup>

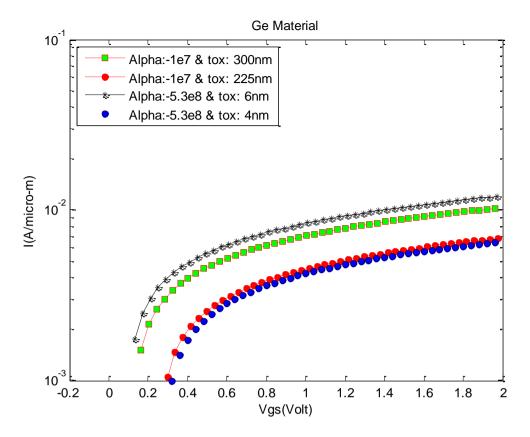

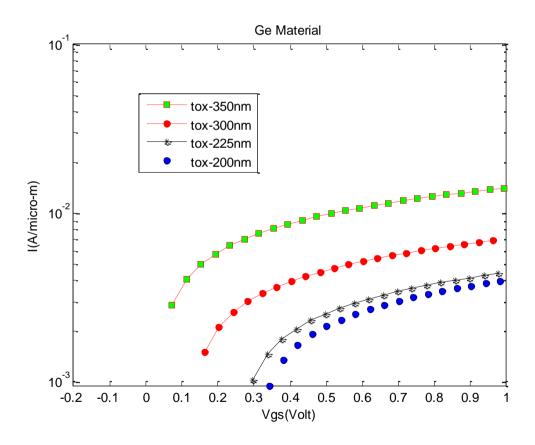

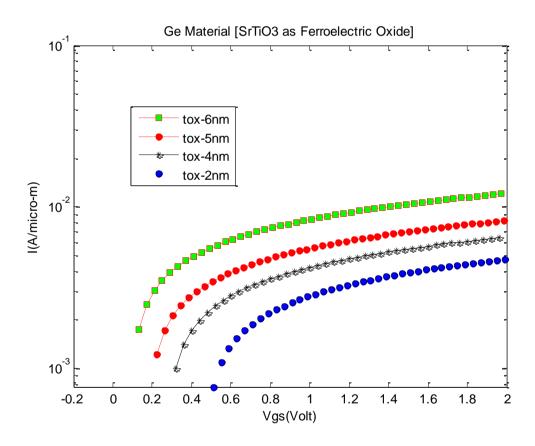

- Figure 4.91 Transfer characteristics of showing the impact of varying the 46 thickness of ferroelectric oxide,  $BaTiO_3$  on  $I-V_{gs}$  curve of DG Fe-TFET in case of Ge Material with Source Doping Concentration,  $Na=10^{25}$  m<sup>-3</sup>

- **Figure 4.92** Transfer characteristics of showing the impact of varying the 47 thickness of ferroelectric oxide,  $SrTiO_3$  on  $I-V_{gs}$  curve of DG Fe-TFET in case of Ge Material with Source Doping Concentration, Na=10<sup>25</sup> m<sup>-3</sup>

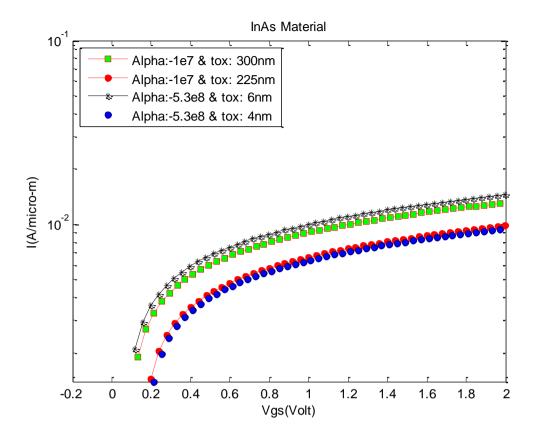

- Figure 4.101 Transfer characteristics of showing the impact of varying the 48 thickness of ferroelectric oxide,  $BaTiO_3$  on  $I-V_{gs}$  curve of DG Fe-TFET in case of InAs Material with Source Doping Concentration,  $Na=10^{25}$  m<sup>-3</sup>

- Figure 4.102 Transfer characteristics of showing the impact of varying the 49 thickness of ferroelectric oxide,  $SrTiO_3$  on  $I-V_{gs}$  curve of DG Fe-TFET in case of InAs Material with Source Doping Concentration, Na=10<sup>25</sup> m<sup>-3</sup>

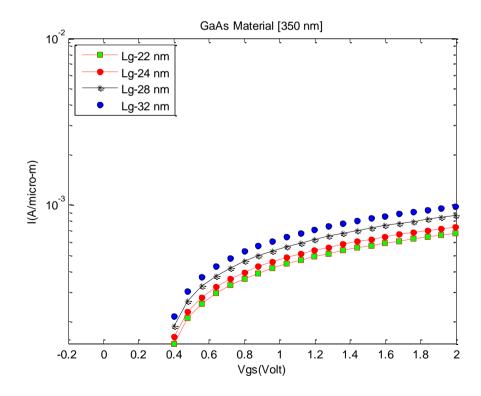

- Figure 4.11 Transfer characteristics of showing the impact of varying the 51 source doping concentration on  $I-V_{gs}$  curve of DG Fe-TFET in case of GaAs Material with ferroelectric oxide thickness,  $t_{ox}$  =350 nm

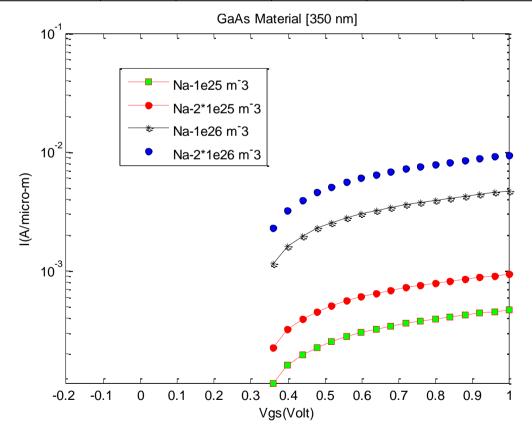

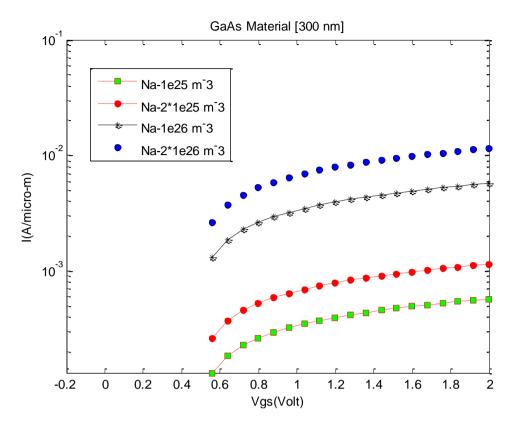

- Figure 4.12 Transfer characteristics of showing the impact of varying the 52 source doping concentration on  $I-V_{gs}$  curve of DG Fe-TFET in case of GaAs Material with ferroelectric oxide thickness,  $t_{ox}$  =300 nm

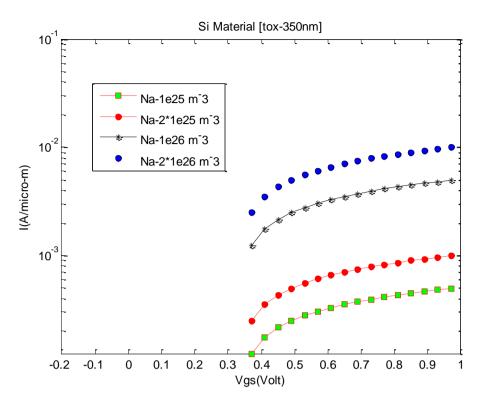

- Figure 4.13 Transfer characteristics of showing the impact of varying the 53 source doping concentration on  $I-V_{gs}$  curve of DG Fe-TFET in case of Si Material with ferroelectric oxide thickness,  $t_{ox} = 350$  nm

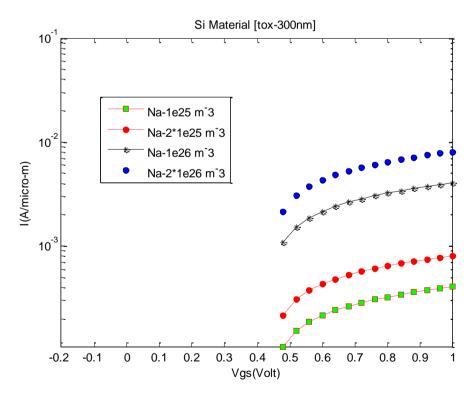

- Figure 4.14 Transfer characteristics of showing the impact of varying the 53 source doping concentration on  $I-V_{gs}$  curve of DG Fe-TFET in case of Si Material with ferroelectric oxide thickness,  $t_{ox} = 300$  nm

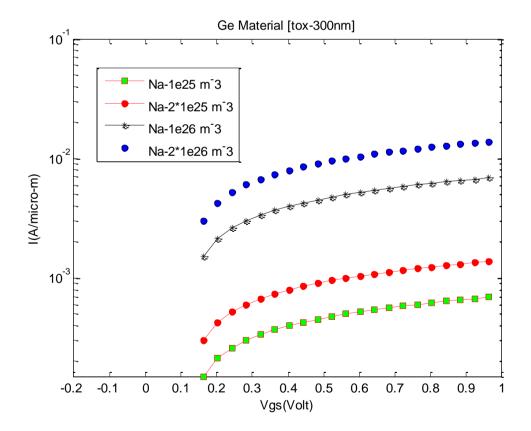

- Figure 4.15 Transfer characteristics of showing the impact of varying the 54 source doping concentration on  $I-V_{gs}$  curve of DG Fe-TFET in case of Ge Material with ferroelectric oxide thickness,  $t_{ox} = 300$  nm

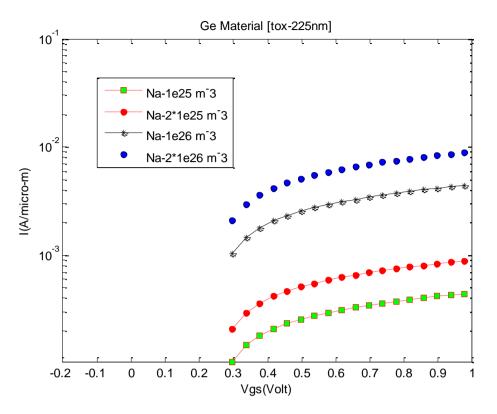

- Figure 4.16 Transfer characteristics of showing the impact of varying the 55 source doping concentration on I-V<sub>gs</sub> curve of DG Fe-TFET in case of Ge Material with ferroelectric oxide thickness,  $t_{ox} = 225$  nm

- Figure 4.17 Transfer characteristics of showing the impact of varying the 56 source doping concentration on  $I-V_{gs}$  curve of DG Fe-TFET in case of InAs Material with ferroelectric oxide thickness,  $t_{ox} = 300$  nm

- Figure 4.18 Transfer characteristics of showing the impact of varying the 56 source doping concentration on  $I-V_{gs}$  curve of DG Fe-TFET in case of InAs Material with ferroelectric oxide thickness,  $t_{ox} = 225$  nm

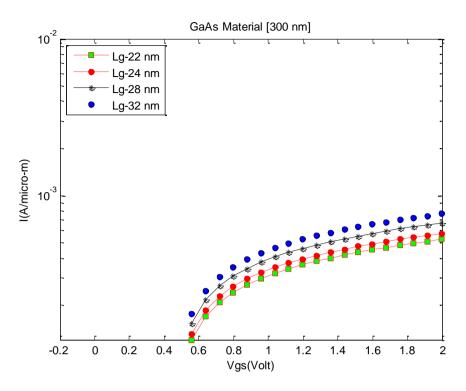

- Figure 4.19 Impact of varying gate length ( $L_g$ ) on I-V<sub>gs</sub> Curve for the DG Fe- 57 TFET in case of GaAs Material with ferroelectric oxide thickness, t<sub>ox</sub> = 350 nm

- Figure 4.20 Impact of varying gate length ( $L_g$ ) on I-V<sub>gs</sub> Curve for the DG Fe- 58 TFET in case of GaAs Material with ferroelectric oxide thickness, t<sub>ox</sub> = 300 nm

- Figure 4.21 Impact of varying gate length ( $L_g$ ) on I-V<sub>gs</sub> Curve for the DG Fe- 58 TFET in case of Si Material with ferroelectric oxide thickness,  $t_{ox} = 350$  nm

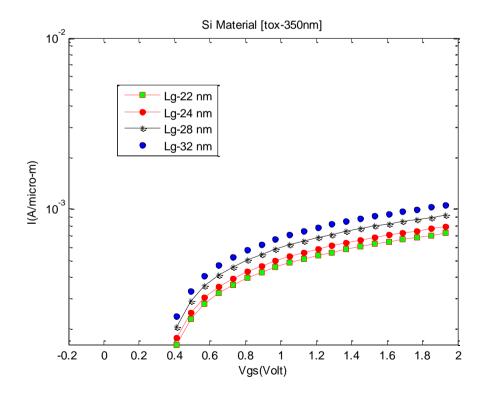

- Figure 4.22 Impact of varying gate length (L<sub>g</sub>) on I-V<sub>gs</sub> Curve for the DG Fe- 59 TFET in case of Si Material with ferroelectric oxide thickness,  $t_{ox} = 300$  nm

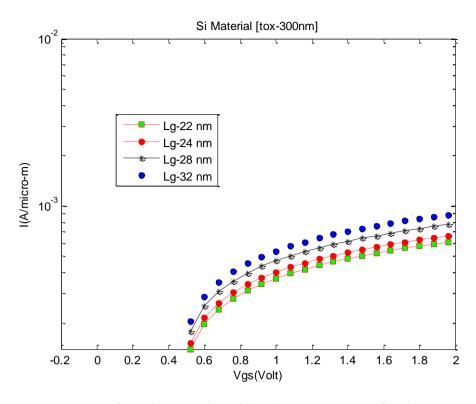

- Figure 4.23 Impact of varying gate length ( $L_g$ ) on I-V<sub>gs</sub> Curve for the DG Fe- 59 TFET in case of Ge Material with ferroelectric oxide thickness,  $t_{ox} = 300$  nm

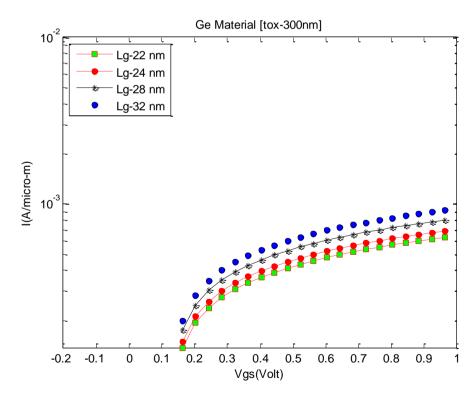

- Figure 4.24 Impact of varying gate length ( $L_g$ ) on I-V<sub>gs</sub> Curve for the DG Fe- 60 TFET in case of Ge Material with ferroelectric oxide thickness,  $t_{ox} = 225$  nm

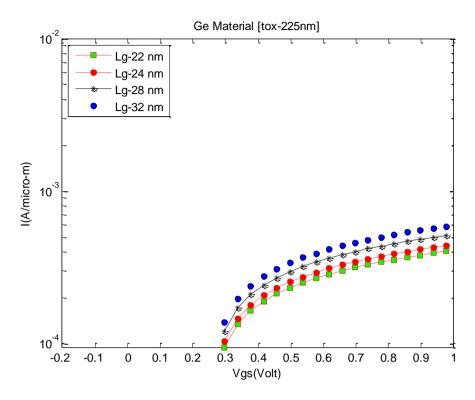

- Figure 4.25 Impact of varying gate length ( $L_g$ ) on I-V<sub>gs</sub> Curve for the DG Fe- 60 TFET in case of InAs Material with ferroelectric oxide thickness, t<sub>ox</sub> = 300 nm

- Figure 4.26 Impact of varying gate length ( $L_g$ ) on I-V<sub>gs</sub> Curve for the DG Fe- 61 TFET in case of InAs Material with ferroelectric oxide thickness, t<sub>ox</sub> = 225 nm

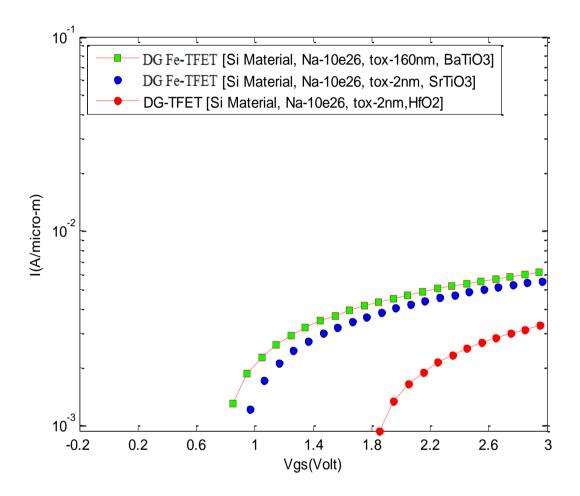

- Figure 4.27 Comparison of  $I-V_{gs}$  characteristics curve between DG Fe-TFET 62 with BaTiO<sub>3</sub> [ $t_{ox}$ =160nm] and SrTiO<sub>3</sub> [ $t_{ox}$ =2nm] as ferroelectric oxide and semi classical DG TFET with HfO<sub>2</sub> [ $t_{ox}$ =2nm] as high k dielectric oxide.

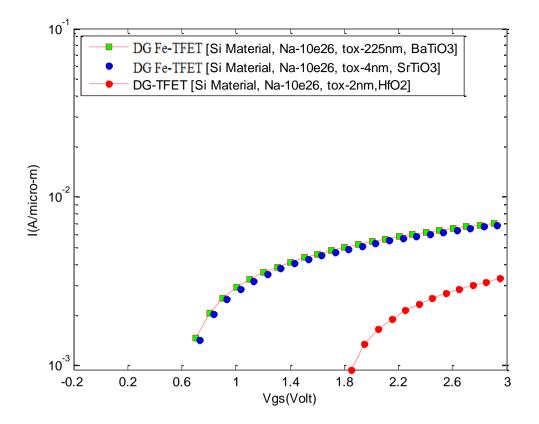

- **Figure 4.28** Comparison of I-V<sub>gs</sub> characteristics curve between DG Fe-TFET 63 with BaTiO<sub>3</sub> [ $t_{ox}$ =225nm] and SrTiO<sub>3</sub> [ $t_{ox}$ =4nm] as ferroelectric oxide and semi classical DG TFET with HfO<sub>2</sub> [ $t_{ox}$ =2nm] as high k dielectric oxide.

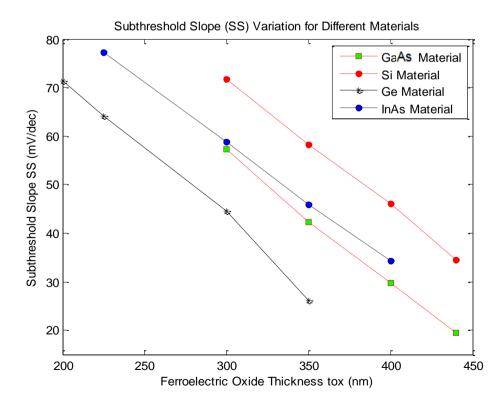

- Figure 4.291 Variation of SS as a function of thickness (t<sub>ox</sub>) of ferroelectric 66 oxide, BaTiO<sub>3</sub> for GaAs, Si, Ge, InAs Material.

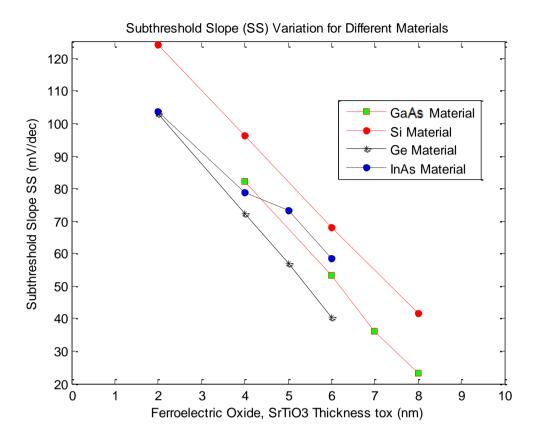

- Figure 4.292 Variation of SS as a function of thickness (t<sub>ox</sub>) of ferroelectric 67 oxide, SrTiO<sub>3</sub> for GaAs, Si, Ge, InAs Material.

### List of Tables

- **Table 1.1** Values of  $V_{onset}$ , Biasing  $V_g$ ,  $I_{ON}$ ,  $I_{OFF}$  for different Material at34ferroelectric oxide thickness ( $t_{ox}$ ) = 300 nm

- **Table 1.2**Values of  $V_{onset}$ , Biasing  $V_g$ ,  $I_{ON}$ ,  $I_{OFF}$  for different Material at35ferroelectric oxide thickness  $(t_{ox}) = 225$  nm

- Table 1.3

Values of Vonset, Biasing Vg, ION for different ferroelectric

36

materials (anisotropy constant α) at certain oxide thickness (tox)

in case of GaAs Material

- **Table 1.4**Values of  $V_{onset}$ , Biasing  $V_g$ ,  $I_{ON}$  for different ferroelectric37materials (anisotropy constant  $\alpha$ ) at certain oxide thickness ( $t_{ox}$ )in case of Si Material

- **Table 1.5**Values of  $V_{onset}$ , Biasing  $V_g$ ,  $I_{ON}$  for different ferroelectric38materials (anisotropy constant  $\alpha$ ) at certain oxide thickness ( $t_{ox}$ )in case of Ge Material

- **Table 1.6**Values of  $V_{onset}$ , Biasing  $V_g$ ,  $I_{ON}$  for different ferroelectric39materials (anisotropy constant  $\alpha$ ) at certain oxide thickness ( $t_{ox}$ )in case of InAs Material

- **Table 1.71** Values of Vonset, Biasing Vg, ION for different thickness (tox) of42ferroelectric oxide, BaTiO3 in case of GaAs Material

- **Table 1.72** Values of Vonset, Biasing Vg, ION for different thickness (tox) of43ferroelectric oxide, SrTiO3 in case of GaAs Material

- **Table 1.81**Values of Vonset, Biasing Vg, ION for different thickness (tox) of44ferroelectric oxide, BaTiO3 in case of Si Material

- **Table 1.82** Values of Vonset, Biasing Vg, ION for different thickness (tox) of45ferroelectric oxide, SrTiO3 in case of Si Material

- **Table 1.91**Values of Vonset, Biasing Vg, ION for different thickness (tox) of46ferroelectric oxide, BaTiO3 in case of Ge Material

- **Table 1.92** Values of Vonset, Biasing Vg, ION for different thickness (tox) of47ferroelectric oxide, SrTiO3 in case of Ge Material

- Table 1.101Values of Vonset, Biasing Vg, ION for different thickness (tox) of48ferroelectric oxide, BaTiO3 in case of InAs Material

- Table 1.102Values of Vonset, Biasing Vg, ION for different thickness (tox) of49ferroelectric oxide, SrTiO3 in case of InAs Material

- Table 1.11 Values of I<sub>ON</sub>, V<sub>onset</sub>, Biasing V<sub>g</sub> for different source doping 51 concentration (N<sub>a</sub>) at certain oxide thickness (t<sub>ox</sub>) in case of GaAs Material

- **Table 1.12**Values of I<sub>ON</sub>, V<sub>onset</sub>, Biasing V<sub>g</sub> for different source doping52concentration (N<sub>a</sub>) at certain oxide thickness (t<sub>ox</sub>) in case of SiMaterial

- Table 1.13 Values of I<sub>ON</sub>, V<sub>onset</sub>, Biasing V<sub>g</sub> for different source doping 54 concentration (N<sub>a</sub>) at certain oxide thickness (t<sub>ox</sub>) in case of Ge Material

- **Table 1.14**Values of I<sub>ON</sub>, V<sub>onset</sub> and Biasing V<sub>g</sub> for different source doping55concentration (N<sub>a</sub>) at certain oxide thickness (t<sub>ox</sub>) in case of InAsMaterial

- Table 1.151Values of Biasing Vg, ION, IOFF and SS for different thickness64(tox) of ferroelectric oxide, BaTiO3 in case of GaAs Material

- Table 1.152Values of Biasing Vg, ION, IOFF and SS for different thickness64(tox) of ferroelectric oxide, SrTiO3 in case of GaAs Material

- Table 1.161Values of Biasing Vg, ION, IOFF and SS for different thickness64(tox) of ferroelectric oxide, BaTiO3 in case of Si Material

- Table 1.162Values of Biasing Vg, ION, IOFF and SS for different thickness65(tox) of ferroelectric oxide, SrTiO3 in case of Si Material

- Table 1.171Values of Biasing  $V_g$ ,  $I_{ON}$ ,  $I_{OFF}$  and SS for different thickness65 $(t_{ox})$  of ferroelectric oxide, BaTiO3 in case of Ge Material

- Table 1.172Values of Biasing Vg, ION, IOFF and SS for different thickness65(tox) of ferroelectric oxide, SrTiO3 in case of Ge Material

- Table 1.181Values of Biasing  $V_g$ ,  $I_{ON}$ ,  $I_{OFF}$  and SS for different thickness66 $(t_{ox})$  of ferroelectric oxide, BaTiO3 in case of InAs Material

- Table 1.182Values of Biasing Vg, ION, IOFF and SS for different thickness66(tox) of ferroelectric oxide, SrTiO3 in case of InAs Material

# **Table 1.19** Values of $I_{ON}$ , $I_{OFF}$ and $I_{ON}$ / $I_{OFF}$ for ferroelectric oxide thickness68 $(t_{ox})$ in case of GaAs Material

- **Table 1.20** Values of  $I_{ON}$ ,  $I_{OFF}$  and  $I_{ON}/I_{OFF}$  for ferroelectric oxide thickness68 $(t_{ox})$  in case of Si Material

- **Table 1.21** Values of  $I_{ON}$ ,  $I_{OFF}$  and  $I_{ON}$ /  $I_{OFF}$  for ferroelectric oxide thickness69 $(t_{ox})$  in case of Ge Material

- **Table 1.22** Values of  $I_{ON}$ ,  $I_{OFF}$  and  $I_{ON}/I_{OFF}$  for ferroelectric oxide thickness69 $(t_{ox})$  in case of InAs Material

# List of Symbols

| А                    | Area (m <sup>2</sup> )                                |

|----------------------|-------------------------------------------------------|

| $A_{kane}, B_{kane}$ | Parameter of Kane's Model                             |

| С                    | Constant                                              |

| Cinv                 | Inversion Layer Capacitance (F/m)                     |

| D                    | Material Dependent Parameter of Kane's Model          |

| E                    | Electric Field (V)                                    |

| $\overline{E}_{ext}$ | External Electric Field                               |

| $E_g$                | Band Gap Energy (eV)                                  |

| $E_y(avg)$           | Average Electric Field                                |

| G <sub>B2B</sub>     | Band to band generation rate                          |

| Ι                    | Band to band tunneling current (A or A/ $\mu$ m)      |

| I <sub>ON</sub>      | On-current (A or A/µm)                                |

| I <sub>OFF</sub>     | Off-current (A or A/µm)                               |

| k                    | Boltzmann constant (eV/K)                             |

| $l_1, l_2$           | Length (m)                                            |

| $L_g$                | Gate Length (m)                                       |

| $l_{tpath}$          | Tunneling Path (m)                                    |

| $m_{eff}$            | Carrier Effective Mass (kg)                           |

| Na                   | Hole Doping Concentration (m <sup>-3</sup> )          |

| Р                    | Polarization charge per unit area (Cm <sup>-3</sup> ) |

| Q                    | Charge (C)                                            |

| q                    | Magnitude of the Electronic Charge (C)                |

| <i>R</i> , <i>S</i>  | Variable Parameter                                    |

| SS                   | Subthreshold Slope (mV/decade)                        |

| $t_{ox}$             | Oxide thickness (m)                                   |

| U                    | Gibbs free energy                                     |

| $V_D$                | Supply Voltage (V)                                    |

| $V_{FB}$             | Flat Band Voltage (V)                                 |

| $V_g$                | Gate Voltage (V)                                      |

| $V_{ox}$             | Oxide Voltage (V)                                     |

|                      |                                                       |

| V <sub>onset</sub>      | Onset Voltage (V)                               |

|-------------------------|-------------------------------------------------|

| W                       | Wide Silicon Body (m)                           |

| X, Y, Z                 | Modified Anisotropy Constant                    |

| $\psi$                  | Surface potential (V)                           |

| $\psi_{v}$              | Valance Band Potential (V)                      |

| $\psi_c$                | Conduction Band Potential (V)                   |

| $\delta\psi$            | Perturbation of the electrostatic potential (V) |

| ρ                       | Volume Charge Density                           |

| $\epsilon_s$            | Permittivity of the Semiconductor               |

| $\epsilon_{si}$         | Dielectric Constant of Silicon                  |

| $\alpha, \beta, \gamma$ | Anisotropy Constant                             |

| ħ                       | Reduced Plank Constant                          |

| σ                       | Ferroelectric dependent parameter               |

# Dedicated

to

My Parents

# CHAPTER 1 Introduction

## 1.1 Preface

The foremost constraint of the conventional MOSFET is that the subthreshold slope (SS) cannot be reduced below 60mV/decade at room temperature due to the theoretical limitation of ln(10)kT/q which is known as Boltzmann tyranny [1]. Besides, the down-scaling of conventional MOSFETs has led to higher static power consumption and exhibits short-channel effects and gate leakages. In addition high SS and thus high operating voltage make power consumption a rising challenge.

Several FET devices have been introduced to overcome these limit. The tunneling FET device is one of the novel devices for a low-power digital application due to their band to band tunneling mechanism [2-7] and it exhibits a very small leakage current, high drive current and SS <60mV/decade [8-10]. By using DG-TFET, we can achieve lower SS and also lower operating supply voltage compared to the conventional MOSFETs. So, they are considered to replace the conventional MOSFET at low operating voltages for low power digital applications. In DG-TFET, electrons move from the highly p doped source to moderately lighter n doped drain by drift diffusion. Here, the drain voltage has no influence in tunneling. Fe-FET is also introduced by integrating ferroelectric material operating in the negative capacitance region [11] that acts as a step-up transformer of the surface potential in a traditional MOSFET structure to achieve a steeper SS [12].

Here we proposed a modified structure of tunneling FET which combines the mechanism of TFET and the theoretical concept of Fe-FET. By using the double gate configuration and the replacement of the gate oxide by ferroelectric material like BaTiO<sub>3</sub> of this newly modified device named Fe-TFET, it is possible to achieve much lower SS and can get sufficiently high drive current at a very low operating voltage. Thus the  $I_{ON}/I_{OFF}$  ratio becomes greater than that of a MOSFET and also for traditional TFET [13]. Our proposed device shows the tunneling mechanism for the ON Current which use band to band tunneling in their ON-state and show a very small leakage current, in range of femto-amperes due to the large tunneling barrier formed when the device is turned off.

### **1.2 Literature Review**

If the empirical Moore's law [14] holds forever, then by the year of 2025 the dissipative power density in a chip will be  $\sim 2MW/cm^2$  [15] which is well above the maximum heat removal limit of 1000 W/cm<sup>2</sup> [16] from an IC by using conventional technology. To reduce the power hunger of IC the transistors should be designed such that it can turn on at a very low voltage having significantly low sub-threshold slope with high I<sub>ON</sub>/I<sub>OFF</sub> ratio. With the continued miniaturization of MOSFET from micrometer to nano-meter regime the device geometry such as channel length, junction depth and oxide thickness has been reduced by about 3 orders of magnitude. To maintain a low power density, the power supply voltage V<sub>DD</sub> should also go down with the scaling of device dimensions. But the mere reduction of the  $V_{DD}$  reduces the ON current I<sub>ON</sub>, so to meet up the I<sub>ON</sub> requirement the threshold voltage V<sub>TH</sub> should be scaled with the scaling of the supply voltage. However, I<sub>OFF</sub> exponentially increases with the threshold voltage reduction, since  $I_{OFF} \propto 10^{-V_{TH}/SS}$ . So, to limit  $I_{OFF}$  while maintaining a satisfactory ION the SS has to go down. However, for the conventional MOSFET structure the SS cannot be reduced below 60mv/decade at room temperature, even with infinite gate capacitance because a fundamental physical limit of surface potential change of ln(10)kT is required to modulate the subthreshold current by one decade, which is known as Boltzmann Tyranny. In order to circumvent this limit a number of novel devices has recently been proposed to the literature such as Impact Ionization-MOSFET[17]-[19], FeedBack-FET [20], Nanoelectromechanical FET [21], Suspended Gate MOSFET [22], Tunneling FET [23-25], Fe-FET[26].

TFET is a gated reverse biased p-i-n diode which utilizes, unlike MOSFET that uses thermal carrier injection over the potential barrier, band to band tunneling as a source carrier injection mechanism. In the OFF state the tunnel barrier between the valance band of the source to the conduction band of the channel is so wide that effectively no tunneling occurs. But when the gate voltage exceeds the threshold voltage the tunneling barrier between the source and the channel is reduced enough to allow sufficiently high tunneling current. So by the exploitation of BTB tunneling mechanism TFET can supersede the fundamental SS limitation of conventional MOSFET. Zhang *et. al.* [27] theoretically showed that the Sub-threshold slope of TFET can be reduced below 60mv/dec. Choi et. al. [28] demonstrated 70nm n channel TFET with SS 52.8mv/decade. Ref. [29] presented a vertical Si/SiGe with an SS of 44mv/decade by device simulation.

Salahuddin and Dutta [30] theoretically demonstrated that a ferroelectric material operating in the negative capacitance region could act as a step-up transformer of the surface potential in Metal–Oxide–Semiconductor structure, opening a new way for the realization of transistors with steeper subthreshold characteristics(S< 60 mV/decade) without changing the basic physics of the FET. Chen et. al. [31] demonstrated that with a proper choice of the ferroelectric insulator thickness, the hysteresis shape can be tailored for operating voltages below 0.5 V to obtain a steeper SS.

In this work, we proposed a theoretical framework of combining the aforementioned two techniques of obtaining steeper SS to beat the fundamental physical limit, thus garnering further reduction in SS value.

$$SS = \frac{dV_g}{dlog(l)} = \frac{dV_g}{d\psi} \frac{d\psi}{dlog(l)} = F_1 F_2 \tag{1}$$

Here,  $\psi$  is the surface potential,  $F_1$  is the variation gate voltage with respect to surface potential and  $F_2$  is the variation of surface potential with respect to logarithmic term of drain current. By utilizing the band-to-band tunneling mechanism, TFET lowers the F<sub>2</sub> in eqn. (1) whereas Fe-FET utilizes negative capacitance to reduce the F<sub>1</sub> factor of eqn. (1).

### **1.3 Basic Structure of Tunneling FET**

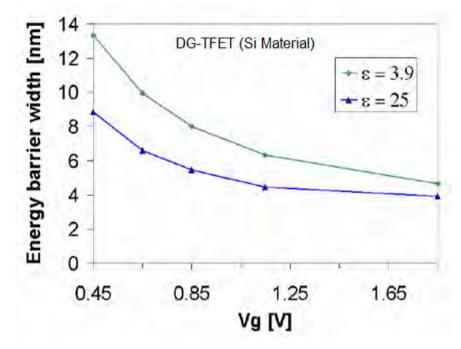

TFETs are gated p-i-n diodes. To switch the device on, the diode is reverse biased and a voltage is applied to the gate. In order to be consistent with MOSFET technology, the names of the device terminals are chosen such that voltages are applied in a similar way for TFET operation [32, 33]. Since a reverse bias is needed across the p-i-n structure in order to create tunneling and since an NMOS operates when positive voltages are applied to the drain and gate, the n-region of a TFET is referred to as its drain, and the p+ region as its source for an n-type device.

Figure 1.1: A simple TFET device structure, a p-i-n diode with one gate

Figure 1.1 shows the basic device structure for a typical p-i-n TFET. The structure shown is an n-type device with a p+ source and an n+ drain. In a p-type TFET, the source would be doped n+ and the drain would be doped p+.

## **1.4 TFET Characteristics**

TFETs are promising devices to replace conventional MOSFETs for low-power applications. They offer the potential for a very low OFF-current and a small SS. TFETs are interesting as low-power devices because of their quantum tunneling barrier. When the devices are turned on, the carriers must tunnel through the barrier in order for current to flow from source to drain. When the devices are off, the presence of the barrier keeps the OFF-current extremely low, several orders of magnitude lower than the OFF-current of a conventional MOSFET.

Figure 1.2: A simple TFET device structure, an n-i-p diode with one gate.

### 1.4.1 Band to Band tunneling

Tunneling is a quantum mechanical process where electrons move through potential energy barriers. Band-to-band tunneling is the effect when electrons travel from the valence band to the conduction band (or vice versa) through the forbidden energy band gap [34]. Understanding the nature of this band-to-band tunneling is important for understanding the approximations made in various simulation models. This understanding is also useful when optimizing design parameters of TFETs for maximum performance.

**Figure 1.3:** Energy band diagrams taken horizontally across the body of a TFET in (a) the OFF-state where the only current comes from p-i-n leakage, (b) the on-state with a negative bias on the gate leading to p-type TFET behavior, and (c) the on-state with a positive bias on the gate leading to n-type TFET behavior.

When a TFET is OFF, only p-i-n diode leakage current flows between the source and drain and this current can be extremely low which is less than a fA/ $\mu$ m. Figure 1.3(a) shows the energy bands horizontally across the body of a TFET in the OFF-state, with a reverse bias applied across the p-i-n junction, but no voltage applied to the gate. If a TFET is designed with similar doping levels and similar gate alignment in the n- and p-sides, then the device exhibits ambipolar behavior. Figure 1.3(b) shows the energy band diagram with a reverse bias applied across the device and a negative voltage applied to the gate. The energy bands in the intrinsic region under the gate are lifted, and the energy barrier is now small enough for band to band tunneling to take place between the valence band of the intrinsic region and the conduction band of the n+- region. When a positive voltage is applied to the gate, on the other hand, the energy bands in the intrinsic region are pushed down, as in Figure 1.3(c), and tunneling takes place between the valence band of the p+-region and the conduction band of the intrinsic region. The energy barrier width for band-to-band tunneling is the single most important factor that determines the amount of drain current through a TFET.

The ON-current of an n-type TFET depends on the width of the energy barrier between the intrinsic and p+ regions, and the current increases exponentially with a reduction in this barrier width. Figure 1.4 shows the dependence of the energy barrier width on the gate voltage for several different gate dielectric constants.

**Figure 1.4:** Energy barrier width dependence with the variation of gate voltage for several different gate dielectric constants

### 1.4.2 Subthreshold Slope

The SS is typically defined as the inverse of the rate of change in current as a function of gate voltage and it can be written as [35]:

$$SS = \frac{\partial V_g}{\partial (\log_{10} l)} \,[\text{mV/dec}] \tag{1}$$

The subthreshold slope of a MOSFET [33] is limited by the diffusion current physics of the device in weak inversion, such that the minimum possible swing in an ideal device is

$$SS_{MOSFET} = ln(10)\frac{kT}{q} \text{ [mV/dec]}$$

(2)

which is about 60 mV/dec at room temperature (300 K) known as Boltzmann Tyranny. On the other hand, a TFET does not experience the same physical limitation, because the current mechanism relies on the tunneling-barrier width rather than the formation of an inversion channel. Starting from Hurkx's band-to-band tunneling model [35] the subthreshold slope for a TFET can be expressed in terms of the gate voltage as

$$SS_{TFET} = \frac{V_g^2}{5.75(V_g + const)} \text{ [mV/dec]}$$

(3)

where the constant is determined by device dimensions and material parameters. Equation (3) shows that, the subthreshold slope is highly dependent on the gate voltage and one should distinguish between the point and the average slopes. This is an important remark for future benchmarking of new abrupt switch solutions, for which most reports currently point to the optimization of the point slope only.

Due to the changing values of slope along the  $I-V_g$  curve, it is useful to define two different types of swing that are point swing and average swing. These are illustrated in Figure 1.5. Point swing is the smallest value of the subthreshold swing anywhere on the  $I-V_g$  curve, typically found right as the device leaves the OFF-state and tunneling current starts to flow. Average swing is taken from the point where the device starts to turn on, up to threshold, often defined using the constant current technique. Average swing is the more useful value for circuit designers.

Figure 1.5: Visual definitions of point swing, taken at the steepest point of the  $I-V_g$  curve, and average swing, taken as the average from turn-on to threshold.

### 1.5 Ferroelectric FET (Fe-FET) Structure

It is of significant importance to have a steep subthreshold slope because lowers the supply voltage and hence the power dissipation can be achieved. However, in a traditional MOSFET, a fundamental limit of surface potential change of  $2.3k_BT$  is required to modulate the subthreshold current by 10 times, which is known as Boltzmann tyranny. Fe-FET is proposed by integrating ferroelectric material as a voltage amplifier in a traditional MOSFET structure to achieve the fast transition in subthreshold region. On the other hand, the aggressive scaling of CMOS technology inevitably leads to a drastic challenge in process variations, such as channel length variation, channel dopant fluctuations, and other layout-dependent proximity effects.

To enable the early-stage exploration of circuit design and better understand the impact on performance variability, it is necessary to develop an effective model that is able to physically capture the steep subthreshold slope and embed it into standard model parameters for circuit simulation. A new threshold voltage model of Fe-FET is proposed in to capture the steep subthreshold behavior. This model is derived from the first principle and physically captures the subthreshold behavior of Fe-FET such that model scalability is guaranteed for future technology generations.

Fe-FET is proposed in to speed up the transition by stacking a ferroelectric material on top of silicon dioxide as a voltage amplifier to boost surface potential in a MOSFET structure, as shown in the schematic in Figure 1.6. Figure 1.7 illustrates the equivalent capacitance model for a Fe-FET device, where the ferroelectric capacitance ( $C_{FE}$ ) is in series with the oxide capacitance ( $C_{ox}$ ) combined to form the insulator capacitance  $C_{ins}$ and the substrate capacitance ( $C_s$ ).  $V_{int}$  denotes the internal voltage between  $C_{FE}$  and  $C_{ox}$ .

Figure 1.6 Cross-section of Ferroelectric FET proposed by Salahuddin and Datta [9]

**Figure 1.7:** (a) The equivalent capacitance model in the substrate to gate region (b) The capacitance model in the ferroelectric and oxide region.

### Traditional FET model

Figure 1.8: The integration of the ferroelectric material into traditional FET model

The negative capacitance of the ferroelectric dielectric originates from the intrinsic feedback mechanism between the induced charge and the voltage drop on the capacitance; it is modeled by inserting an additional feedback path in traditional CMOS model, as shown in Figure 1.8. This feedback between charge and voltage drop is modeled by Eq. (1),

$$V_g - V_{int} \approx \alpha_0 Q + \beta_0 Q^3 + \gamma_0 Q^5 + \rho_0 \frac{dQ}{dt}$$

(1)

where  $\alpha_0$  and  $\beta_0$  are negative to account for the negative capacitance.  $\gamma_0$  is positive to describe the behavior of normal capacitance.  $\rho_0$  is the resistivity for the voltage drop. Those parameters ( $\alpha_0$ ,  $\beta_0$ ,  $\gamma_0$  and  $\rho_0$ ) are proportional to the thickness of ferroelectric dielectric (t<sub>FE</sub>), and are modeled in the following equations -

$$\alpha_0 = 2\alpha t_{FE}$$

,  $\beta_0 = 4\beta t_{FE}$ ,  $\gamma_0 = 6\gamma t_{FE}$  and  $\rho_0 = \rho t_{FE}$

Where,  $\alpha$ ,  $\beta$ ,  $\gamma$  and  $\rho$  are material co-efficient of the ferroelectric dielectric. The internal voltage (V<sub>int</sub>) which accounts for the change of voltage drop in C<sub>FE</sub>.

SS can be written as the following form incorporate with the effect of surface potential. By incorporating the ferroelectric material the value of SS becomes much lower to overcome the fundamental physical limit -

$$SS = \left(\frac{\partial V_g}{\partial \psi_s}\right) \left(\frac{\partial \psi_s}{\partial (\log_{10} l)}\right) \tag{2}$$

Figure 1.9: The insulator capacitance  $C_{ins}$  is in series with another capacitance  $C_s$ .  $C_s$  comprises of the body capacitance, the channel to source capacitance, the channel to drain capacitance

Here

$$F1 = \frac{\partial V_g}{\partial \psi_s} = 1 + \frac{c_s}{c_{ins}} \tag{3}$$

and

$$\frac{\partial \psi_s}{\partial (\log_{10} I)} = 2.3 k_B T/dec = 60 \ mV/dec$$

From Equation (3), one would see that it is a product of two terms. The first term is often called the 'body factor' *F1* of the FET. The second term, which represents the change of surface potential as a function of drain current, has a fundamental value of 60mV/dec at room temperature for a FET where the transport is dominated by thermionic emission. Eq. (3) shows the expression for *F1*. One would recognize that this is a ratio of the supply voltage V<sub>g</sub> to the internal node voltage  $\psi_s$ , which is, in the usual case, always larger than 1. This is why the subthreshold slope has the limit of 60mV/dec at room temperature. However, the same reasoning will also tell us that, if one could imagine an insulator with a negative capacitance, then in Eq. (3), *F1* will be less than 1, which will then bring down the subthreshold swing below 60 mV/decade. This negative capacitance is shown by the ferroelectric material like BaTiO<sub>3</sub>, SrTiO<sub>3</sub> and other related material that ensures the value of *F1* is less than 1 by adjusting some parameter which is related to the capacitive term.

### **1.6 Proposal of Ferroelectric TFET device**

Here we proposed a modified device structure of TFET including negative capacitive mechanism which shows some extra beneficial behavior over conventional MOSFET and also traditional TFET. This proposed structure combines the mechanism of tunneling FET and the theoretical concept of Fe-FET. Here we developed the tunneling mechanism for the ON Current which use band to band tunneling in their ON-state and show a very small leakage current, in range of femtoamperes due to the large tunneling barrier formed when the device is turned off. Double gate configuration and the replacement of the SiO<sub>2</sub> by the ferroelectric material like BaTiO<sub>3</sub> or SrTiO<sub>3</sub> tend to enhance the device performance.

The major crisis of the traditional MOSFET is that, when it aggressively scaled down it suffers high SS and thus high operating voltage which makes the power consumption a rising challenge. But by using DG-TFET, we can achieve SS < 60 mV/dec. It also operates a lower supply voltage than the conventional MOSFET. So, TFET is a excellent replacement of the conventional MOSFET at low operating voltages for low power digital applications. The subthreshold slop (SS) for DG-TFET is possible to achieve ~50 mV/dec [36]. Fe-FET is also a superior alternative device that can achieve much lower SS by using the theoretical concept of negative capacitive mechanism.

So, our proposed device named Fe-TFET combines the both phenomenon of band to band tunneling (BTBT) mechanism and negative capacitance (NC) behavior of ferroelectric material. By using this Fe-TFET, we can achieve much lower SS and get sufficiently high drive current at a very low operating voltage. Thus the  $I_{ON}/I_{OFF}$  ratio becomes greater than that of a MOSFET and also for traditional TFET.

Figure 1.10: Cross section of Ferroelectric Tunneling FET with one gate

# 1.7 Objective of this Study

The objectives of this work are:

- i. Study of a proposed structure of Ferroelectric Tunneling Field Effect Transistor (Fe-TFET).

- ii. Analytical modeling of I-V characteristics of the Fe-TFET.

The outcome of this work is to accomplish the following -

- i. Analytical modeling of Fe-TFET with different semiconductor material

- ii. Establishment of the better performance in terms of SS and  $I_{ON}/I_{OFF}$  ratio.

## **1.8 Thesis Outline**

**Chapter 2** describes the double gate structure of FET device and initiates the ferroelectric oxide in place of traditional oxide or high k dielectric material. The double gate ferroelectric tunneling FET Structure is considered for the Si, Ge, GaAs and InAs substrate. Reasons of modifications are clarified in this chapter.

**Chapter 3** at first 1-D Poisson's Equation is solved to evaluate the surface potential and the electric field. Then the Surface Potential is modeled to develop the relationship between the surface potential and the gate voltage by using Landau-Khalatnikov method. Finally the ON Current equation is modeled considering the onset voltage using Kane's Model.

**Chapter 4** presents the new proposed device characteristics in case of Si, GaAs, Ge and InAs. The impact of different Ferroelectric material, oxide thickness variation, source doping concentration and gate length are described with illustrations. Next the device performance of Double gate Ferroelectric TFET is compared with semi classical Double Gate TFET. Finally, optimization of SS and improvement of  $I_{ON}/I_{OFF}$  ratio are explained in this section.

**Chapter 5** draws the conclusion of this work. This chapter summarizes the findings of the study. It also puts forward suggestions regarding future scopes of works related to this thesis.

# CHAPTER 2 Double Gate Ferroelectric TFET

### 2.1 Introduction

Double Gate Ferroelectric Tunneling Field Effect Transistors (DG Fe-TFET) use the tunneling of electrons as the carrier transport method for device operation. They are generally designed as gated p-i-n diodes, where the gate is used to modulate an effective tunneling barrier height. Ideally, these devices exhibit a very low OFF-state current (proportional to reverse biased diode leakage), a very low subthreshold slope and high ON-current. TFETs can be generally classified as point and/or line tunneling devices. In a point tunneling device, the source does not appreciably deplete, but the gate causes the channel region to invert, resulting in tunneling from the source to the channel. In a line tunneling device, the source is inverted (generally by engineering an overlapped gate with an optimized source doping profile), resulting in tunneling into the inversion layer, similar to Gate-Induced Drain Leakage.

Here, we proposed a point tunneling device structure where gate is located fully top of the source region. Gate voltage allows the band bending of the depletion region under the portion that resides in the interface of the gate and source region. These band bending permits the transport of electron from valence band to conduction band causes the tunneling current. Simulation results show very low subthreshold slope at very low operating voltage in the range of 0.8 V. It also shows high ON current in the range of 0.02 A/ $\mu$ m. Gate leakage was neglected in the device that we propose here, because the thickness of oxide is large enough to limit the OFF-current in fabricated TFETs. So, it is evident that this device theoretically proves a very efficient. But in case of TFET, the experimental results show very low subthreshold slope at very low currents. However, unless TFETs improve to better match their simulation results, they have

## 2.2 Double Gate Structure of Fe-TFET

limited application for logic devices.

Double Gate TFET is a good consideration to increase the current at least double which is very much beneficial over the TFET with single gate [37-39]. In this way, in case of Fe-TFET, the ON-current is boosted, while the OFF-current, still in the femtoamperes or picoamperes range, increases by the same factor but remains

extremely low. When the device body is thin enough, however, the electrostatic control of the tunnel junction by the gate will be improved with a double-gate configuration, and the current will more than double. The double gate gives an advantage of about two decades of current in subthreshold and about one decade for high  $V_g$ . The subthreshold slope and threshold voltage are also reduced with the double-gate configuration.

### 2.3 Ferroelectric Oxide

Ferroelectric oxide shows different behavior than the traditional oxide  $SiO_2$  and the high k dielectric material. It exhibits negative capacitance in a certain range and this property distinguishes the ferroelectric from the regular capacitor.

**Figure 2.1:** (a) The energy landscape of ferroelectric showing negative capacitance. (b) The energy landscape of a usual capacitor. The landscape shows well known  $Q^2/2C$  dependence. (c) Derivative dU/dQ vs. Q found from (a). (d) Derivative dU/dQ vs. Q found from (b).

Figure 2.1 (a) and (b) show the energy landscapes of a ferroelectric and regular capacitor respectively. If we look at the region around zero charge, we notice that the curvature of energy landscape is opposite for the ferroelectric insulator in comparison to a regular capacitor. This gives the first hint that, in this region, the capacitance of the ferroelectric is negative. Formally, the capacitance is defined as the inverse slope of the derivative dU/dQ. The derivative plots for Figures. 2.1(a) and 2.1(b) are shown in 2.1(c) and 2.1(d). We see that in the region indicated by the circle, the slope is negative and hence the capacitance is negative. However, one would also notice that in this region, the material is unstable. This is because the arrow indicated region in 2.1(a) is far from the energy minima. One can show that this instability translates to the typical hysteretic behavior of a ferroelectric material (see the dashed lines).

**Figure 2.2:** (a) Schematic of a FET with the gate circuit. (b) The insulator capacitance  $C_{ins}$  is in series with another capacitance  $C_s$ .  $C_s$  comprises of the body capacitance, the channel to source capacitance, the channel to drain capacitance.

Now let us consider a combination of capacitances having a positive and a negative capacitor in series as shown in the gate circuit of Figure 2.2(b), so that the total capacitance is given by

$$\frac{1}{c} = \frac{1}{c_s} - \frac{1}{c_{ins}} \tag{1}$$

If this total capacitance of the series combination is positive, then the total system remains stable and will not show any hysteresis. Thus the ferroelectric can be part of a

stable system even though being in an unstable state of negative capacitance by itself. One would also see from Eq. (1) that the total capacitance in this series combination is larger than either of the two constituent capacitances, which means that the total capacitance is enhanced.

**Figure 2.3:** The capacitive model shown in Figure 2.2(a) is modified by putting a ferroelectric insulator on top of a  $SiO_2$  layer

The energy landscape of a ferroelectric material shown in Figure 2.1(a) is given by the following expression

$$U = \alpha P^2 + \beta P^4 + \gamma P^6 \tag{2}$$

Where P is the polarization and  $\alpha$ ,  $\beta$  and  $\gamma$  are anisotropy constants. This is often termed as the Gibb's free energy of the system [7].  $\alpha$  and  $\beta$  are usually negative and  $\gamma$ is positive. One would then see that the low charge region is dominated by  $\alpha$ , whereas the intermediate region by  $\beta$ . As a result, for low charge region the system is unstable and in a negative capacitance region. However for higher values of charge density,  $\gamma$ becomes more and more important and at some point overcomes the negative contribution from  $\alpha$  and  $\beta$  making the system stable again in a positive capacitance region.

#### 2.4 Double Gate Fe-TFET Device Structure

Our proposed device indicated in the figure is modified structure than the conventional TFET. Here Gate on Source is demonstrated to achieve the good control of the band to band tunneling current. Thus the band to band tunneling current is mostly influenced by the gate voltage and has a little effect on drain voltage. The device can be regarded as an extreme case of the short gate TFET as the gate does not even cover a part of the channel. It is important to note that in this device, the tunneling occurs in the direction orthogonal to the gate. The one-dimensional nature of the band to band tunneling region.

**Figure 2.5:** Double Gate ferroelectric tunnel field effect transistor with the gate is located fully on top of the source

In this work we propose a modified structure of TFET incorporating Ferroelectric capacitor as the gate oxide, called the Ferroelectric TFET (Fe-TFET). The proposed device effectively combines two different mechanisms of lowering the sub threshold slope (SS) for a transistor garnering a further lowered one compared to conventional TFET. A simple yet accurate ON current model of the proposed device is presented here. Fe-TFET gives ON current as high as 0.02 A/µm for a gate voltage of 0.6 V, OFF current of less than 1pA/µm and an improved lower SS, according to the results yielded from the analytical model. This work also provides physics based reasoning behind the multiplicative improvement in the SS for the proposed device.

# 2.4.1 Si Tunneling Fe-TFET Scheme

as

In the following device structure, Si material is used in the source region and barium titanate is used

ferroelectric oxide in between the metal gate and source interface.

**Figure 2.6:** Double Gate ferroelectric Si tunneling field effect transistor with the gate is located fully on top of the Source

# 2.4.2 Ge Tunneling Fe-TFET Scheme

In the following device structure, Ge material is used in the source region and barium titanate is used as ferroelectric oxide in between the metal gate and source interface.

**Figure 2.7:** Double Gate ferroelectric Ge tunneling field effect transistor with the gate is located fully on top of the Source

# 2.4.3 GaAs Tunneling Fe-TFET Scheme

In the following device structure, GaAs material is used in source region and barium titanate is used as ferroelectric oxide in between metal gate and source interface.

**Figure 2.8:** Double Gate ferroelectric GaAs tunneling field effect transistor with the gate is located fully on top of the Source

# 2.4.4 InAs Tunneling Fe-TFET Scheme

In the following device structure, InAs material is used in source region and barium titanate is used as ferroelectric oxide in between metal gate and source interface.

**Figure 2.9:** Double Gate ferroelectric GaAs tunneling field effect transistor with the gate is located fully on top of the Source

# **3.1 Introduction**

As MOSFETS reach nanometer dimensions, power consumption becomes a major blockage for further scaling. The continued reduction of the MOSFET size is leading to an increased leakage current due to short channel effects, such as Drain Induced Barrier Lowering (DIBL) and the power supply voltage cannot be reduced any further because of the subthreshold slope being limited to 60 mV/decade at room temperature. In this view, the exploration of alternative devices which possibly outperform the MOSFET at these nanometer dimensions is required.

A promising alternative for the MOSFET, which does not suffer from these limitations, is the Ferroelectric tunneling field-effect transistor (Fe-TFET). Throughout the rest of this work the term Fe-TFET will not refer to any specific implementation form, but the Fe-TFET is defined as a semiconductor device in which the gate controls the source-drain current through modulation of Band-to-Band Tunneling (BTBT). Band-to-Band Tunneling is a process in which electrons tunnel from the valence band through the semiconductor band gap to the conduction band or vice versa.

TFETs with a subthreshold slope lower than 60 mV/decade have already been demonstrated and due to their built in tunnel barrier, Si TFETs are expected to maintain low OFF currents for channel lengths down to 10 nm. An advantage of TFETs compared to other alternative device concepts is that their fabrication is compatible with standard CMOS processing since they can be implemented as a reverse biased gated p-i-n diode. So, our proposed device named Fe-TFET concocts the TFET mechanism and negative capacitance of Ferroelectric material. In this work, an analytical model for our novel device is developed. A new modified TFET device structure is presented for which the potential profile can be determined straightforwardly. As a result, the total current through the device can be calculated analytically. In order to obtain a closed expression for the current, an approximation regarding the behavior of the current around the band to band tunneling onset voltage needs to be made, as discussed.

# **3.2 Solve 1-D Poisson's Equation to evaluate Surface Potential and Electric Field**

Figure 3.1: DG Fe-TFET with positive gate bias applied such that a depletion region with thickness  $Y_{max}$  exists (only upper half shown)

For one dimensional approach, the electrostatic potential in a semiconductor by  $\psi$  is given by Poison's equation [40],

$$\frac{d^2\psi_s(y)}{dy^2} = -\frac{\rho(y)}{\epsilon_s}$$

Where  $\psi_s(y)$  is the surface potential,  $\rho(y)$  is the volume charge density and  $\epsilon_s$  is the permittivity of the semiconductor. Here,  $\rho(y) = -qN_a$

$$\therefore \frac{d^2 \psi_s(y)}{dy^2} = \frac{q N_a}{\epsilon_s} \tag{A}$$

By integrating equation (A) we have that

$$\psi_s(y) = \frac{qN_a}{2\epsilon_s}(y - y_{max})^2$$

As the electric field

$$E(y) = -\frac{d\psi_s(y)}{dy}$$

$$\therefore E(y) = -\frac{qN_a}{\epsilon_s}(y - y_{max})$$

Where,  $y_{max}$  is the length of the depletion region which is the function of gate voltage and *q* is the elementary charge.

## 3.3 Modeling of Surface Potential using Landau-Khalatnikov Method

Now we need to develop a relation between the gate voltage and surface potential in the highly doped source region.

Figure 3.2: Energy band diagram of metal, ferroelectric oxide and semiconductor junction

Here  $\psi_s$  is the surface potential. So,

$$V_g = V_{FB} + V_{ox} + \psi_s \tag{A}$$

The physics for the traditional MOS Capacitor is well known and needs no mention but the dynamics for the negative capacitor needs clarification to develop a simple linear intuitive model for optimization of device operation.

From LK (Landau-Khalatnikov) equation [41-43] we know

$$e\frac{d\bar{P}}{dt} + \overline{\nabla}_{\rm p} {\rm U} = 0 \tag{1}$$

Where, U is the Gibbs free energy. We can express it in terms of anisotropy energy.

$$U = \alpha P^2 + \beta P^4 + \gamma P^6 - \bar{E}_{ext} \bar{P}$$

(2)

Where,  $\overline{P}$  is the polarization charge per unit area. Putting equation (2) in (1) we get

$$\rho \frac{d\bar{P}}{dt} + 2\alpha P + 4\beta P^3 + 6\gamma P^5 - \bar{E}_{ext} = 0$$

At steady state

$$\frac{d\bar{P}}{dt}\approx 0$$

$$\therefore 2\alpha P + 4\beta P^3 + 6\gamma P^5 = \bar{E}_{ext}$$

Here in this case

$$E_{ext} = \frac{V_{ox}}{t_{ox}}$$

$$V_{ox} = 2\alpha t_{ox}P^2 + 4\beta t_{ox}P^3 + 6\gamma t_{ox}P^5$$

$$V_{ox} = \alpha_0 P + \beta_0 P^3 + \gamma_0 P^5$$

Here

$$\alpha_0 = 2\alpha t_{ox}$$

,  $\beta_0 = 4\beta t_{ox}$  and  $\gamma_0 = 6\gamma t_{ox}$ .

For Ferroelectric material  $P \approx Q$

$$V_{ox} = \alpha_0 Q + \beta_0 Q^3 + \gamma_0 Q^5 \tag{3}$$

If the inversion layer capacitance is  $C_{\text{inv}}$  and charge is  $\boldsymbol{Q}$

Then,

$$C_{inv} = \frac{Q}{\psi_s}$$

$\therefore Q = C_{inv}\psi_s$

From equation (3) we get

$$V_{ox} = \alpha_0 C_{inv} \psi_s + \beta_0 C_{inv}{}^3 \psi_s{}^3 + \gamma_0 C_{inv}{}^5 \psi_s{}^5$$

$$V_{ox} = X \psi_s + Y \psi_s{}^3 + Z \psi_s{}^5$$

Here,  $X = \alpha_0 C_{inv}$ ,  $Y = \beta_0 C_{inv}^3$  and  $Z = \gamma_0 C_{inv}^5$ If we assume the effect of higher order term is negligible then

$$V_{ox} \approx X \psi_s \tag{4}$$

Putting the value of equation (4) to equation (A), we get

$$V_g = V_{FB} + X\psi_s + \psi_s$$

$$\therefore \psi_s = \left(\frac{V_g - V_{FB}}{1 + X}\right)$$

This is the relation between the surface potential and applied gate voltage.

Figure 3.3: Auto-Transformer relationship between gate voltage and surface potential

By making the (1 + X) < 1, we can get an amplified surface potential.

Here the functional block acts as if it were a transformer. The amplification phenomena introduced by the negative capacitance gate stack. Significantly reduces the gate voltage requirement for sufficient BTBT current.

## 3.4 Evaluation of onset voltage, Vonset

Thus along the x-direction, no potential change is considered, so the electric field will be changed along the y-direction. Here gate voltage is the function of surface potential and the parameter X which has great significance related to the properties of ferroelectric material. So, the gate voltage

$$V_g = V_{FB} + (1+X)\psi_s$$

For better understanding the mechanism of tunneling current, onset voltage  $V_{onset}$  is evaluated which marks the onset band to band tunneling current in the depletion region [30]. It can also say that the band to band tunneling begins when the band bending is equal to the energy gap.

So

$$V_{onset} = V_{FB} + (1+X)\frac{E_g}{q}$$

#### **3.5 Evaluation of ON Current Equation using Kane's Model**

The current I is found by the integration of the band to band generation rate  $G_{B2B}$  on the volume of the device

$$I = q \int \mathcal{G}_{B2B} \, dV = q W L_g \int \mathcal{G}_{B2B} \, dy \tag{B}$$

Where,  $L_g$  and W are the gate length and width respectively. By using Kane's Model [2], the band to band generation rate  $G_{B2B}$  can be calculated from the following equation

$$G_{B2B} = A_{kane} \frac{|E|^D}{\sqrt{E_g}} exp\left(-B_{kane} \frac{E_g^{3/2}}{|E|}\right)$$

(1)

Where,  $E_g$  is the band gap, D is the material dependent parameter of Kane's Model and  $A_{kane} = (e^2 m_{eff}^{1/2})/(18\pi\hbar^2)$  and  $B_{kane} = (\pi m_{eff}^{1/2})/(2q\hbar)$  are in general functions of carrier effective mass  $m_{eff}$  [3]

Thus neutral region does not contribute to the band to band tunneling current I. So, the current is evaluated considering only a depletion region instead of relying on the local electric field .

The average electric field in the y-direction is given by

$$E_{y}(avg) = \frac{E_{g}}{ql_{tpath}}$$

(2)

Where,  $l_{tpath}$  is the tunneling path.

**Figure 3.4:** Band diagram of the cross-section  $P-P^1$  from Figure 3.1 indicating  $l_{tpath}$

For calculating the tunneling path, two points  $[y_1 (valance band) \& y_2 (conduction band)]$  in the y direction are considered which are at the same potential

$$\psi_v(y_1) = \psi_c(y_2)$$

Here,

$$\psi_{\nu}(y_1) = \frac{qN_a}{2\epsilon_s}(y_1 - y_{max})^2 + \frac{E_g}{q}$$

and

$$\psi_c(y_1) = \frac{qN_a}{2\epsilon_s}(y_2 - y_{max})^2$$

$$\therefore (y_2 - y_{max})^2 = (y_1 - y_{max})^2 + C$$

Where

$$C = \frac{2E_g \epsilon_s}{q^2 N_a}$$

and  $l_{tpath} = y_1 - y_2$

$$\therefore (y_2 - y_{max})^2 = (l_{tpath} + y_2 - y_{max})^2 + C$$

Solving the above equation we get

$$y_2 = y_{max} - \frac{l_{tpath}^2 + C}{2l_{tpath}}$$

(3)

From the equation (3) we get the following equation for the expression of by

$$\therefore dy = \frac{1}{2} \left( \frac{C}{l_{tpath}^2} - 1 \right) dl_{tpath}$$

(4)

Putting the equation (1), (2) and (4) in equation (A) we get the following expression

$$I = \frac{qWL_gA_{kane}}{2} \int_{l_1}^{l_2} \frac{E_g^{D-\frac{1}{2}}}{q^D l_{tpath}^D} exp\left(-B_{kane}q\sqrt{E_g}l_{tpath}\right) \left(1 - \frac{c}{l_{tpath}^2}\right) dl_{tpath}$$

(C)

29

In case of non-degenerate semiconductor, the equation of  $l_1$  and  $l_2$  are same as in [4]

$$l_1 = \sqrt{C}$$

and

$$l_2 = \sqrt{\frac{qc}{E_g}} \left\{ \sqrt{\psi_s} - \sqrt{\psi_s - \frac{E_g}{q}} \right\}$$

(5)

Where,  $\Phi_s$  is the electrostatic potential at the end of the depletion region.

Since we have developed necessary equation to calculate the tunneling length  $l_1$  and  $l_2$ . Now we need to evaluate the approximate expression of tunneling current. The integral of the band to band tunneling current expression in equation (C) can be assumed by the following approximating expression

$$I \approx -\frac{WL_g A_{kane} E_g^{D-1}}{2B_{kane} q^D} \left(\frac{1}{l_2^D} - \frac{C}{l_2^{D+2}}\right) exp\left(-B_{kane} q \sqrt{E_g} l_2\right) \tag{D}$$

By using equation (5) and (D) for  $\psi_s = \frac{E_g}{q} + \delta \psi$ , we get the following equation

$$I \approx \frac{WL_g A_{kane} \sqrt{q}}{B_{kane} E_g^{3/2}} \left(\frac{E_g N_a}{2\epsilon_s}\right)^{D/2} exp\left(B_{kane} q \sqrt{2\epsilon_s E_g} / \sqrt{qN_a} \left(\sqrt{\delta\psi} - \sqrt{E_g/q}\right)\right) \sqrt{\delta\psi}$$

Where,  $\delta \psi$  is a perturbation of the electrostatic potential which is the function of gate voltage as well as onset voltage.

$$\delta \psi = (V_g - V_{onset})/\sigma$$

, where,  $\sigma = 1 + X$

Considering the value of D is 2 to get an optimized expression for the band to band tunneling current

$$I \approx WL_g R \exp\left(S \sqrt{V_g - V_{onset}}\right) \sqrt{V_g - V_{onset}}$$

With

$$R = \frac{A_{kane}N_a}{2B_{kane}\epsilon_s} \sqrt{\frac{q}{E_g\sigma}} exp(-B_{kane}q^2E_g\sqrt{2\epsilon_s}/\sqrt{N_a})$$

$$S = B_{kane} \sqrt{\frac{2qE_g\epsilon_s}{\sigma N_a}}$$

The respective positions of the quasi-Fermi levels also determine the ratio between band to band tunneling generation and band to band tunneling recombination. In the previous treatment for the depletion region the respective positions of the quasi-Fermi levels were ignored and band to band tunneling was entirely attributed to generation. This is an acceptable approximation as long as the valence band is filled and the conduction band is empty.

In the case of a non-degenerate semiconductor, the inversion regime sets in before the electron quasi-Fermi level and the conduction band meet. In the depletion region, only the tail of the Fermi-Dirac distribution occupies the conduction band which is negligible compared to the almost fully occupied valence band. In the inversion layer however, the conduction band is filled and band to band tunneling recombination can no longer be neglected.

Using the previous approach, the total current in the device equals the current generated in the depletion region. The influence of the gate voltage is straightforward, namely increasing the depletion region size and increasing the current accordingly.

In a degenerate semiconductor, the limits 11, 12 of the integration (5) need to be altered such that the integration only extends over the region of tunneling where the conduction band is (approximately) empty and the valence band is (approximately) full.

### **CHAPTER 4**

#### **Optimization of Simulation Parameters**

#### 4.1 Introduction

While the basic parameters to optimize in order to have superior Fe-TFET characteristics are known an abrupt doping profile at the tunnel junction, high capacitive coupling from the gate to the tunnel junction, etc. – it is crucial to also understand the sensitivity of device characteristics to parameter fluctuations. This is well-understood for conventional MOSFETs and the principal sources of fluctuation, including random discrete dopants, different dielectric materials, gate and channel length fluctuations and oxide thickness fluctuations, have been thoroughly studied. The same needs to be accomplished with Fe-TFET, so that the main sources of characteristic fluctuation can be pinpointed and then controlled.

The goals of this chapter are twofold: to optimize the device characteristics of the Fe-TFET using the additive booster technique and then to investigate the influence of the parameter fluctuations which are unavoidable in device fabrication and their impact on device characteristics. The critical parameters that will need to be the most tightly controlled when fabricating these devices are identified and the parameter variation is quantified.

Increasing short channel effects like drain induced barrier lowering (DIBL) and roll-off are serious impediments to further scaling of conventional MOSFET. These limitations instigate all researchers to look for innovative devices. Non-scalable sub-threshold slope in MOSFET limits its application in high speed and low power application.

Fe-TFET is a strong candidate in high speed and low power application because of its potential to get low Sub-Threshold Slope (<60 mV/decade). In the previous work it was demonstrated that silicon double gate TFET (DG-TFET) suffers from unacceptable low ON-current. Here we have shown that, by introducing the ferroelectric material in place of SiO<sub>2</sub>; layer high ON-current, low OFF-current and very low SS can be obtained in Double Gate Fe-TFET. Device structure is depicted. As doping profile is high band bending narrowing model is included. In both n-channels mode of operation and pchannel mode of operation conduction takes place by tunneling of electron from valance band of source to conduction band of drain region. Band to band tunneling is a strong function of electric field. As Vg increases from 0-0.8 V band bending becomes significant. In the OFF-state (V<sub>g</sub><0.2 V), current flows very low ( $<10^{-12}$  A/µm) and then tunneling current increases very sharply. From the input characteristic we can say that Double Gate Fe-TFET is almost free from drain induced barrier lowering problem. After channel length scaling, OFF-current increases and there is no significant increase of ON-current is seen. But in p-channel mode of operation sufficient band bending takes place at higher gate voltage. The ON-current can be improved by careful choice of ferroelectric material. Very low point subthreshold slope (~ 40mv/dec) is observed and because of that high  $I_{ON}$ /  $I_{OFF}$  ratio (~10<sup>11</sup>) is seen, which is useful to operate the device in low voltage range. In all low Subthreshold Slope, high ION/ IOFF ratio and low threshold voltage V<sub>Th</sub> make this device a strong candidate for ultralow power and ultralow voltage application.

#### 4.2 Device characteristics for Si, GaAs, Ge and InAs

Fe-TFET structure is better option for low power application.  $I_{ON}$  current is boosted up with the lowering the band gap which can be achieved by using Ge and InAs. Thus the band gap is reduced gradually then the band to band tunneling occurs by applying very low gate voltage  $V_g$  at a certain thickness of ferroelectric material. So, it is very much appreciating novel device to operate in a very small range of gate voltage. And the OFF current is hence supposed to be limited forming a large barrier by the forbidden band gap which should prevent tunneling to happen in the OFF-state.

The band gap is one of the most important parameters when considering a TFET, since it determines the "barrier" between valence and conduction band. The ON-current increases with decreasing band gap, while also  $V_{onset}$  is reduced since the voltage required to create a path from valence to conduction band is directly proportional to the band gap. A small band gap is therefore beneficial for a large Fe-TFET ON-current and is desirable as far as it does not jeopardize the Fe-TFET OFF-current.

**Table 1.1:** Values of  $V_{onset}$ , Biasing  $V_g$ ,  $I_{ON}$ ,  $I_{OFF}$  for different Material at ferroelectric oxide thickness ( $t_{ox}$ ) = 300 nm

| Material | Band Gap (eV) | $V_{\text{onset}}$ or $V_{\text{Th}}$ | Biasing $V_g$ | I <sub>ON</sub> | I <sub>OFF</sub>  |

|----------|---------------|---------------------------------------|---------------|-----------------|-------------------|

|          |               | (V)                                   | (V)           | (A/µm)          | (A/µm)            |

| GaAs     | 1.43          | 0.4776                                | 1.08          | 0.024           | 10 <sup>-13</sup> |

| Si       | 1.1           | 0.4400                                | 0.92          | 0.025           | 10 <sup>-10</sup> |

| Ge       | 0.66          | 0.1230                                | 0.62          | 0.033           | 10 <sup>-8</sup>  |

| InAs     | 0.36          | 0.0928                                | 0.416         | 0.033           | 10-6              |

**Figure 4.1:** I-V<sub>gs</sub> characteristics curve of DG Fe-TFET for different semiconductor material with fixed ferroelectric oxide thickness,  $t_{ox} = 300$  nm

| Material | Band Gap (eV) | $V_{\text{onset}}$ or $V_{\text{Th}}$ | Biasing V <sub>g</sub> | I <sub>ON</sub> | I <sub>OFF</sub>  |

|----------|---------------|---------------------------------------|------------------------|-----------------|-------------------|

|          |               | (V)                                   | (V)                    | (A/µm)          | (A/µm)            |

| GaAs     | 1.43          | 0.7157                                | 1.18                   | 0.021           | 10 <sup>-13</sup> |

| Si       | 1.1           | 0.6050                                | 0.99                   | 0.022           | 10 <sup>-10</sup> |

| Ge       | 0.66          | 0.2573                                | 0.65                   | 0.0256          | 10 <sup>-8</sup>  |

| InAs     | 0.36          | 0.1596                                | 0.56                   | 0.03            | 10 <sup>-6</sup>  |

**Table 1.2:** Values of  $V_{onset}$ , Biasing  $V_g$ ,  $I_{ON}$ ,  $I_{OFF}$  for different Material at ferroelectric oxide thickness ( $t_{ox}$ ) = 225 nm

**Figure 4.2:** I-V<sub>gs</sub> characteristics curve of DG Fe-TFET for different semiconductor material with fixed ferroelectric oxide thickness,  $t_{ox} = 225$  nm

#### 4.3 Impact of different Ferroelectric material