#### M.Sc. Engineering Thesis

# DESIGN OF A UWB TRANSMITTER WITH INTEGRATED ANTENNA FOR ON-CHIP RF WIRELESS INTERCONNECTS

By

Muhammad Abdullah Arafat (0409062229 P)

Submitted to

Department of Electrical and Electronic Engineering in partial fulfillment of the requirements for the degree of Master of Science in Electrical and Electronic Engineering

Department of Electrical and Electronic Engineering Bangladesh University of Engineering and Technology (BUET) Dhaka-1000

April, 2011

The thesis titled "DESIGN OF A UWB TRANSMITTER WITH INTEGRATED ANTENNA FOR ON-CHIP RF WIRELESS INTERCONNECTS" submitted by Muhammad Abdullah Arafat, Roll No.: 0409062229 P, Session: April 2009 has been accepted as satisfactory in partial fulfillment of the requirement for the degree of MASTER OF SCIENCE IN ELECTRICAL AND ELECTRONIC ENGINEERING on April 2, 2011.

#### **BOARD OF EXAMINERS**

moshir 2/4/ 2011

Dr. A. B. M. Harun-ur Rashid Professor Department of Electrical and Electronic Engineering BUET, Dhaka-1000, Bangladesh.

2. Dr. Md. Saifur Rahman

Dr. Md. Saifur Rahman Professor and Head Department of Electrical and Electronic Engineering BUET, Dhaka-1000, Bangladesh.

n. 02/04/2011 3.

Dr. Pran Kanai Saha Professor Department of Electrical and Electronic Engineering BUET, Dhaka-1000, Bangladesh.

4.

1.

611122 02/4/11

Dr. Md. Ashraful Hoque Professor Department of Electrical and Electronic Engineering Islamic University of Technology Gazipur, Dhaka, Bangladesh. Chairman (Supervisor)

Member

Member

(Ex-officio)

Member (External)

i

### **Candidate's Declaration**

This is to certify that the work presented in this thesis entitled "DESIGN OF A UWB TRANSMITTER WITH INTEGRATED ANTENNA FOR ON-CHIP RF WIRELESS INTERCONNECTS" is the outcome of the investigation carried out by me under the supervision of Professor Dr. A. B. M. Harun-ur Rashid in the Department of Electrical and Electronic Engineering, Bangladesh University of Engineering and Technology (BUET), Dhaka. It is also declared that neither this thesis nor any part thereof has been submitted or is being currently submitted anywhere else for the award of any degree or diploma.

A. Arafat 2.4.2011

Muhammad Abdullah Arafat Candidate Dedicated to My Parents

iii

# CONTENTS

| Board | i of Examiners i                               |

|-------|------------------------------------------------|

| Cand  | idate's Declaration ii                         |

| Dedic | iii                                            |

| Ackn  | owledgements xiii                              |

| Abstr | ract xiv                                       |

|       |                                                |

|       |                                                |

| CHA   | APTER 1 INTRODUCTION 1                         |

| 1.1   | Motivation1                                    |

| 1.2   | On-chip Wireless Interconnect Systems 3        |

| 1.3   | UWB Wireless Communication Systems 4           |

| 1.4   | UWB Transmitter                                |

| 1.5   | Research Objectives                            |

| 1.6   | Thesis Layout6                                 |

|       |                                                |

| CHA   | APTER 2 FUTURE OF INTERCONNECT TECHNOLOGY 8    |

| 2.1   | Background                                     |

| 2.2   | Conventional On-chip Wiring9                   |

| 2.3   | Logic and Wire Delays 12                       |

| 2.4   | Evolutionary Approaches to Global Interconnect |

| 2.5   | Revolutionary Techniques of Interconnection15  |

|       | 2.5.1. 3-D Integration15                       |

|       | 2.5.2. Optical Interconnect17                  |

|       | 2.5.3. Wireless Interconnect                   |

iv

| CHA | APTER  | <b>3 UWB WIRELESS CHIP-TO-CHIP<br/>COMMUNICATION</b>            |           |

|-----|--------|-----------------------------------------------------------------|-----------|

| 3.1 | Motiv  | ations for Developing UWB System                                | 23        |

| 3.2 | Funda  | mentals of Ultra-Wideband System                                | 25        |

|     | 3.2.1  | UWB Definition                                                  | 25        |

|     | 3.2.2  | UWB Advantages                                                  | 26        |

|     | 3.2.3  | UWB Signaling and Pulse Shapes                                  |           |

| 3.3 | Modu   | lation Types                                                    |           |

|     | 3.3.1  | On Off Keying (OOK)                                             | 32        |

|     | 3.3.2  | Binary Phase Shift Keying (BPSK)                                |           |

|     | 3.3.3  | Binary PPM                                                      |           |

| 3.4 | IR-UV  | WB Architecture for Interconnects System                        | 33        |

| 3.5 | Propos | sed Transceiver Architecture                                    | 35        |

|     | 3.5.1  | Definition of Transmitted reference (TR)                        | 36        |

|     | 3.5.2  | Importance of Transmitted Reference in Wireless Interconnects S | ystems 37 |

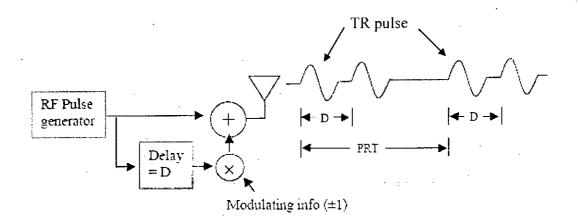

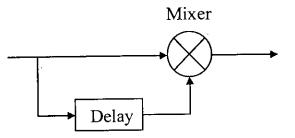

|     | 3.5.3  | UWB Pulse Generator with TR Pulse                               | 40        |

|     | 3.5.4  | Receiver Architecture for the Proposed Model                    | 40        |

|     | 3.5.5  | Self Synchronized Complete Transceiver Architecture for on-chi  | р         |

|     |        | Wireless Interconnects                                          | 41        |

| 3.6 | FCC F  | Regulations and UWB pulse Shape for Chip Interconnects          | 47        |

| CH  | APTER  | <b>4 UWB TRANSMITTER DESIGN</b>                                 | 53        |

| 4.1 | Desig  | n Sequence of UWB Pulse Generator                               | 53        |

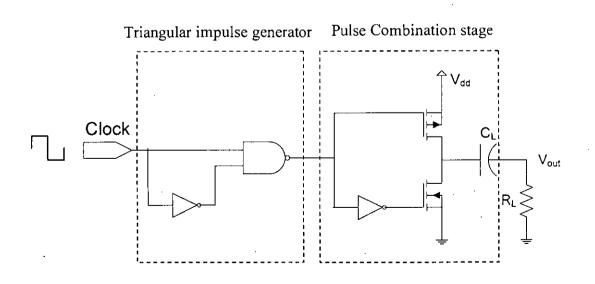

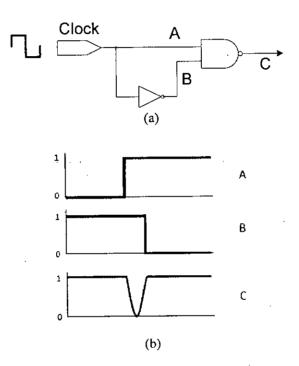

|     | 4.1.1. | Basic Principle: Triangular Impulse Generation                  | 54        |

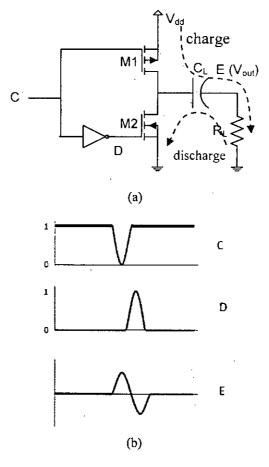

|     | 4.1.2. | Pulse Combining Stage                                           | 54        |

|     | 4.1.3. | Data Modulation: OOK                                            |           |

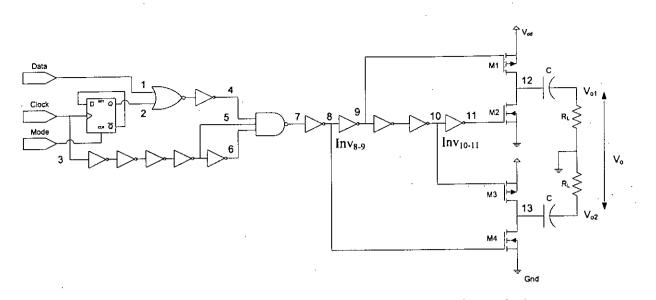

|     | 4.1.4. | Data with Transmitted Reference (TR)                            | 57        |

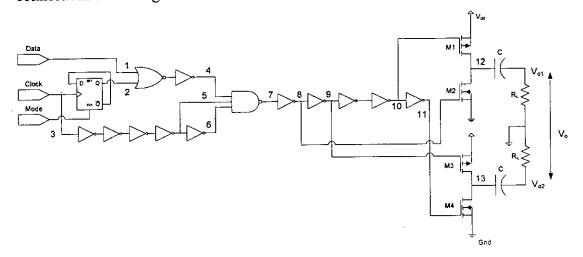

|     | 4.1.5. | UWB Transmitter with Differential Output                        | 59        |

|     | 4.1.6. | Proposed UWB BPSK Transmitter Design                            | 61        |

.

.

· V

. .

í.

|     | 4.1.7. N | Aodes of Operation and Data Rate            | .62  |

|-----|----------|---------------------------------------------|------|

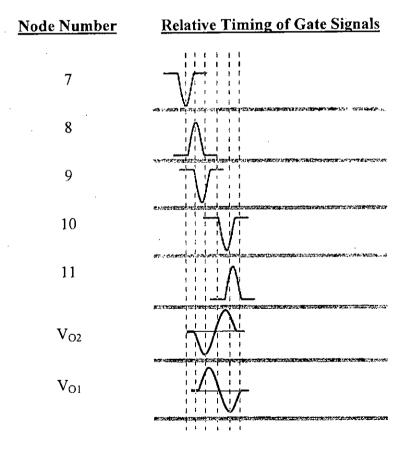

| 4.2 | Simulate | d Waveforms                                 | .63  |

| 4.3 | Perform  | ance Evaluation                             | .68  |

|     | 4.3.1 F  | Performance Comparison                      | .74  |

| 4.4 | Clock G  | enerator                                    | .76  |

|     | 4.4.1 F  | Ring Oscillator                             | .76  |

|     | 4.4.2 \$ | Single Ended Ring Oscillator with Inverters | . 77 |

|     | 4.4.3 \$ | Start-up Circuit for Ring Oscillators       | .78  |

| CHA | PTER   | 5 ON-CHIP ANTENNA SIMULATION                              | 81   |

|-----|--------|-----------------------------------------------------------|------|

| 5.1 | Transn | nitting and Receiving Antenna                             | . 81 |

| 5.2 | Dipole | Antenna                                                   | . 81 |

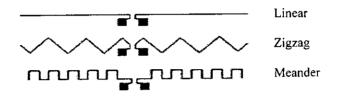

|     | 5.2.1  | Dipole Antenna Shapes                                     | .82  |

|     | 5.2.2  | Device Structure and Simulation Method                    | .82  |

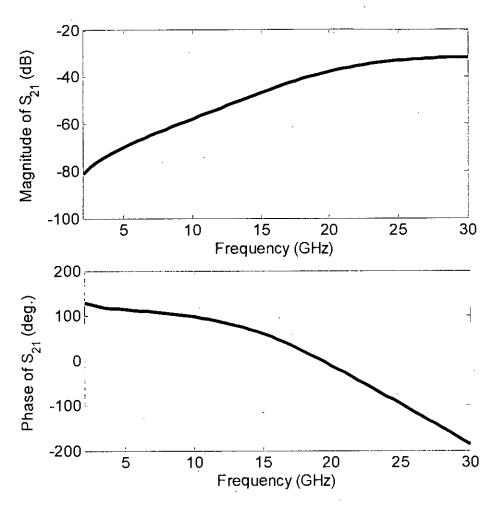

|     | 5.2.3  | Transmission Characteristics of Integrated Dipole Antenna | . 85 |

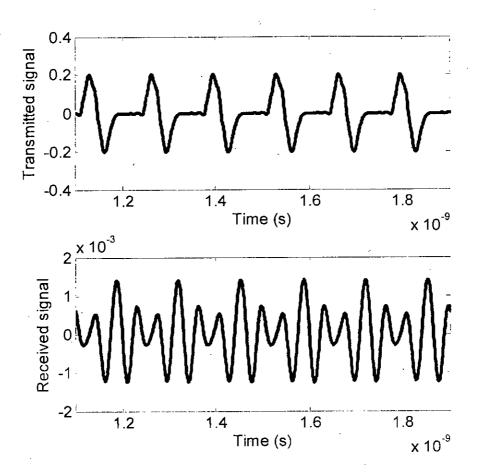

| 5.3 | Receiv | ed UWB Signal                                             | . 89 |

| CHAPTER 6 | CONCLUSION | 91 |

|-----------|------------|----|

|           |            |    |

| 6.1    | Summary91    |

|--------|--------------|

| 6.2    | Future Works |

|        |              |

| Refere | ences        |

vi

# List of Figures

| Figure 2.1: SEM photo of lower levels of interconnect (with dielectric material      |

|--------------------------------------------------------------------------------------|

| removed)                                                                             |

| Figure 2.2: Three Tier Architectural hierarchy for VLSI circuit design               |

| Figure 2.3: Sample cross-section of hierarchical wire scaling 11                     |

| Figure 2.4: International Technology Roadmap for Semiconductors 2001 predictions     |

| for device and wire delays13                                                         |

| Figure 2.5: Dense mesh of interconnect typical of modern high-performance integrated |

| circuits, with series resistance and shunt capacitance indicated                     |

| Figure 2.6: Calculated gate and interconnect delay versus technology generation      |

| Figure 2.7: Different approaches to fabricate 3-D circuits                           |

| Figure 2.8: optical interconnect concept                                             |

| Figure 2.9: Wireless interconnect using impulse radio for inter-chip communication19 |

| Figure 2.10: Chip-to-chip wireless links                                             |

| Figure 3.1: Block diagram of the impulse-radio transceiver                           |

| Figure 3.2 PSD of different wireless communication systems25                         |

| Figure 3.3: Ultra wideband signals                                                   |

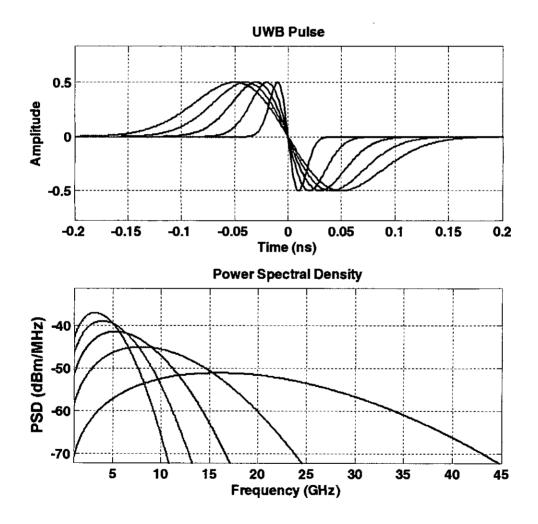

| Figure 3.4 (a) Generally adopted Gaussian pulse shapes in UWB communication          |

| $(\sigma = 0.1 \text{ns})$ (b) Fourier transform of the pulse shapes                 |

| Figure 3.5: Common UWB modulation techniques                                         |

| Figure 3.6: Conventional Architecture of UWB wireless transceiver                    |

| Figure 3.7: Signal demodulation using LPF36                                          |

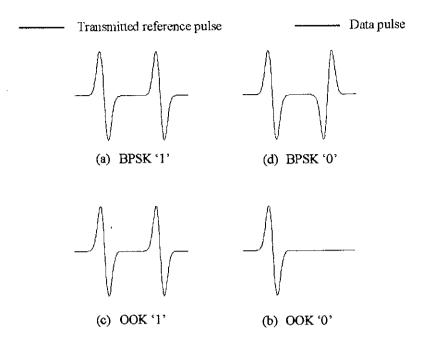

| Figure 3.8: Gaussian monocycle pulses with transmitted reference;                    |

| (a) and (b) represent BPSK '1' and '0' respectively;                                 |

| (c) and (d) represent OOK '1' and '0' respectively                                   |

| Figure 3.9: A typical transfer function of silicon integrated dipole antenna pair    |

| for on-chip wireless interconnects                                                   |

vii

| Figure 3.10: | Transmitted and received UWB signals through on-chip                 |

|--------------|----------------------------------------------------------------------|

|              | dipole antenna pair                                                  |

| Figure 3.11: | Conventional Scheme for generating TR UWB pulse40                    |

| Figure 3.12: | Demodulator used in UWB receiver for wireless interconnects          |

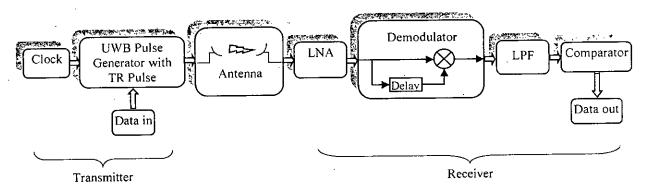

| Figure 3.13: | Proposed Single Link UWB Communication System Architecture for       |

|              | on-chip Wireless Interconnects                                       |

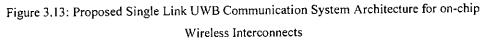

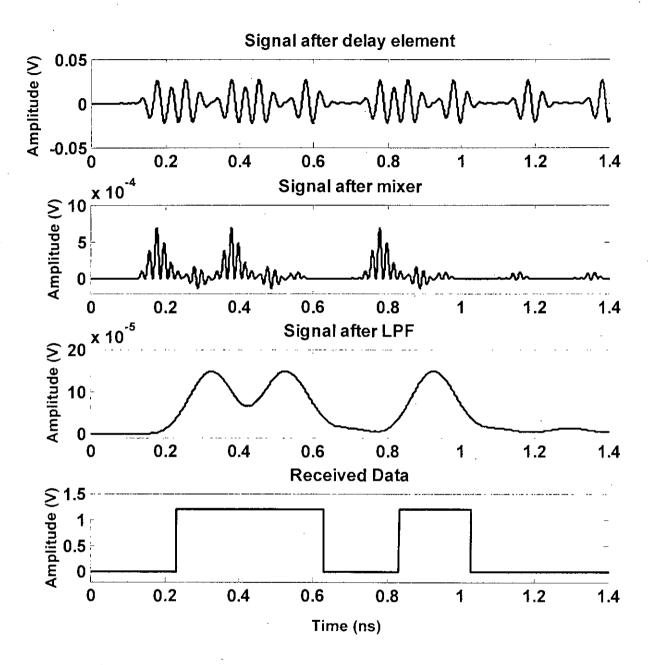

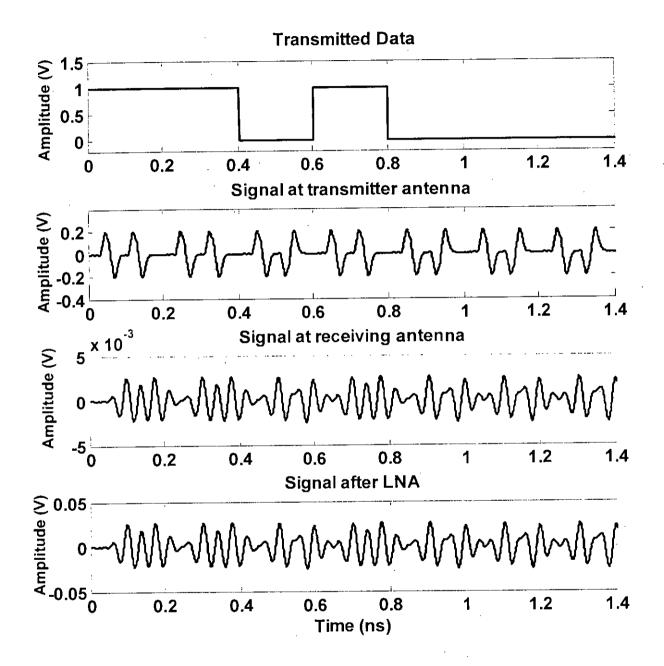

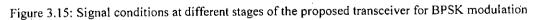

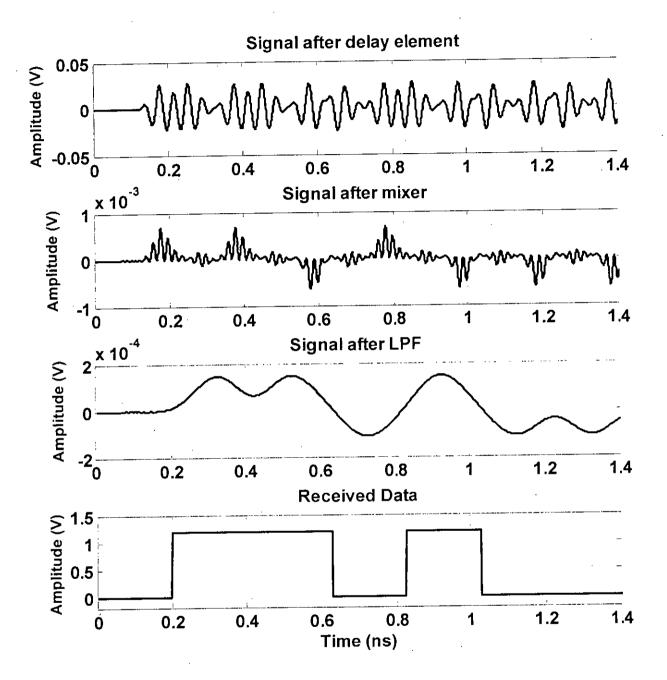

| Figure 3.14: | Signal conditions at different stages of the proposed transceiver    |

|              | for OOK modulation                                                   |

| Figure 3.15: | Signal conditions at different stages of the proposed transceiver    |

|              | for BPSK modulation 45                                               |

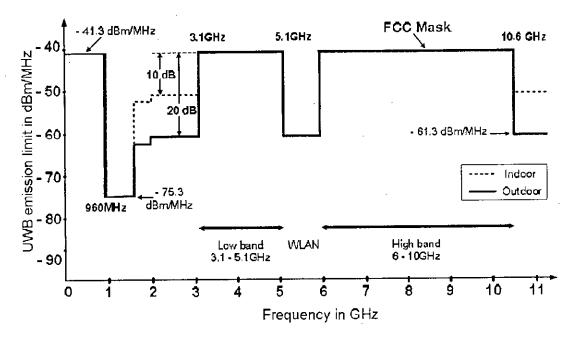

| Figure 3.16: | FCC spectral mask for UWB communication systems                      |

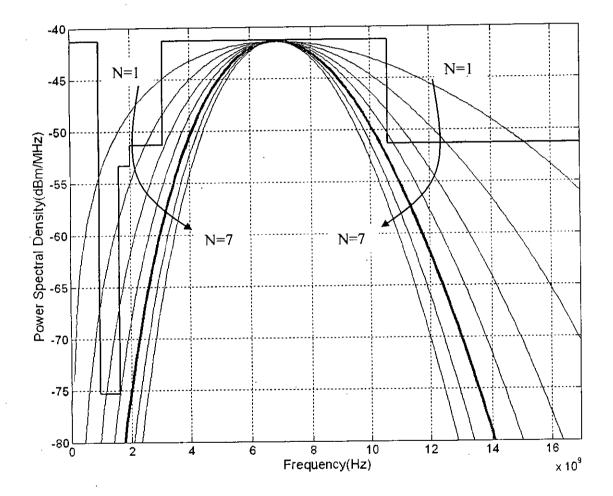

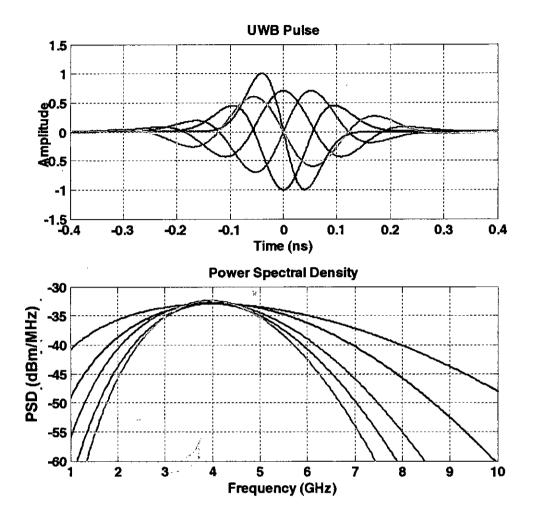

| Figure 3.17: | PSD of different Gaussian derivatives satisfying FCC mask48          |

| Figure 3.18: | PSD comparison for different Gaussian derivatives having             |

|              | the same width                                                       |

| Figure 3.19: | PSD comparison for different Gaussian derivatives having             |

|              | different widths 50                                                  |

| Figure 3.20: | PSD of Gaussian monocycle pulses having different widths 51          |

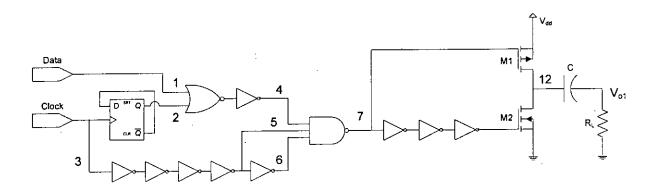

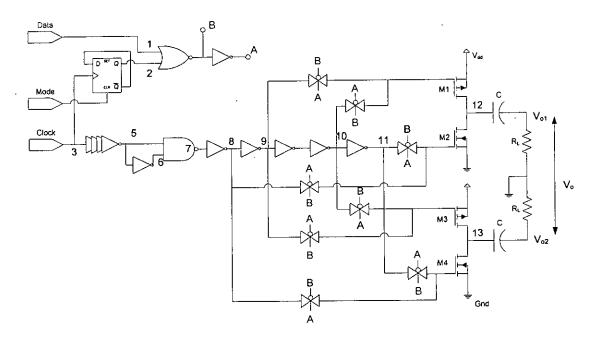

| Figure 4.1:  | Basic circuit for Gaussian Monocycle pulse generation53              |

| Figure 4.2:  | Basic triangular impulse generator (a) circuit                       |

|              | (b) signal waveform at various nodes                                 |

| Figure 4.3:  | Output stage of the pulse generator (a) circuit                      |

|              | (b) signal waveforms at various nodes                                |

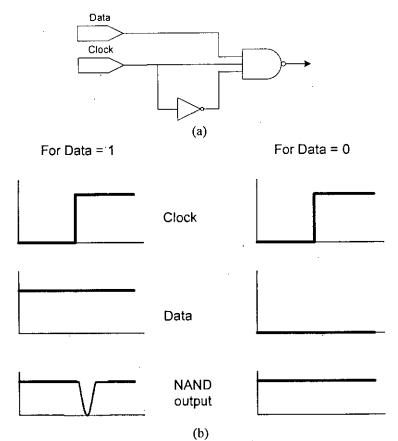

| Figure 4.4:  | Design step to include OOK modulation (a) circuit                    |

|              | (b) signal waveforms at various nodes                                |

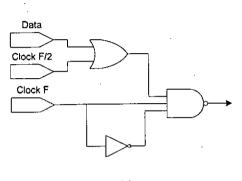

| Figure 4.5:  | • -                                                                  |

|              | (b) signal waveforms at various nodes 57                             |

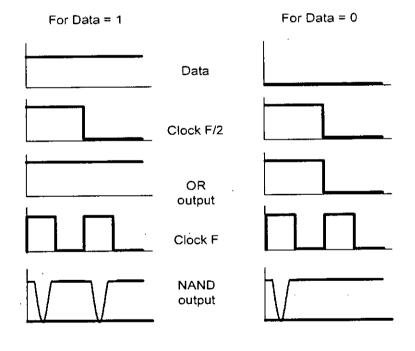

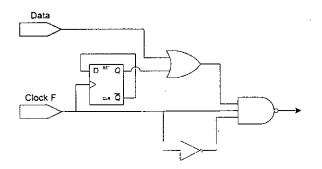

|              | Design step employing D flip-flop                                    |

|              | Single ended UWB Gaussian monocycle OOK transmitter with TR pulse 59 |

|              | Complete schematic of the differential UWB OOK transmitter60         |

| Figure 4.9:  | Timing waveforms at various nodes of the transmitter circuit60       |

.

.

viii

| Figure 4.10: Gate connections of UWB transmitter to produce inverted               |

|------------------------------------------------------------------------------------|

| Gaussian monocycle pulse61                                                         |

| Figure 4.11: Complete schematic of the differential UWB BPSK transmitter 61        |

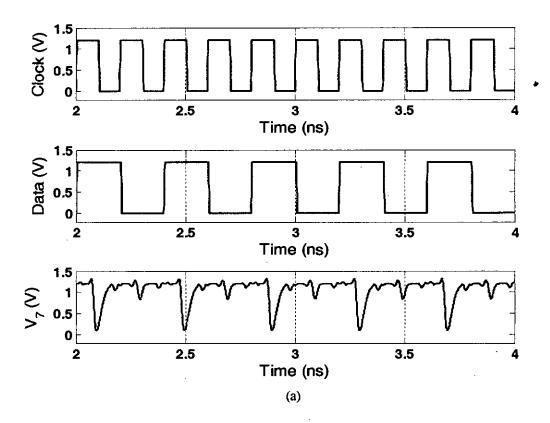

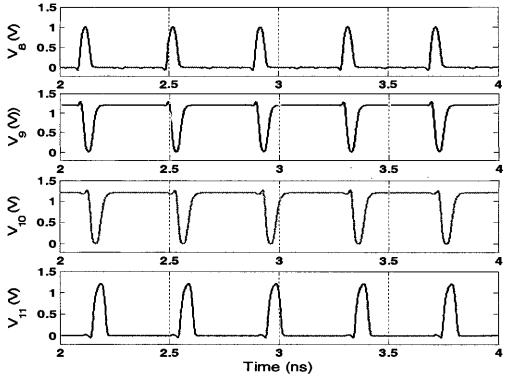

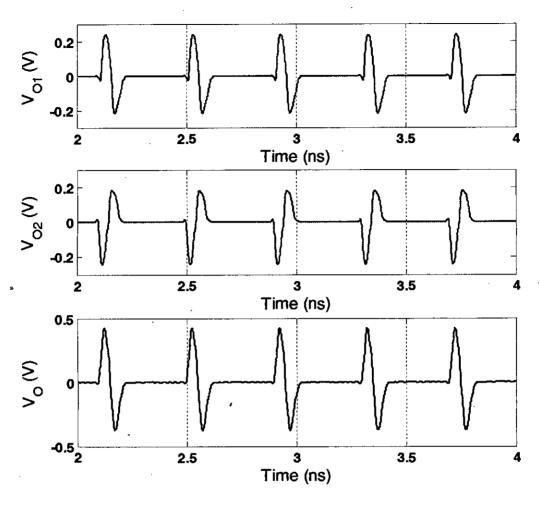

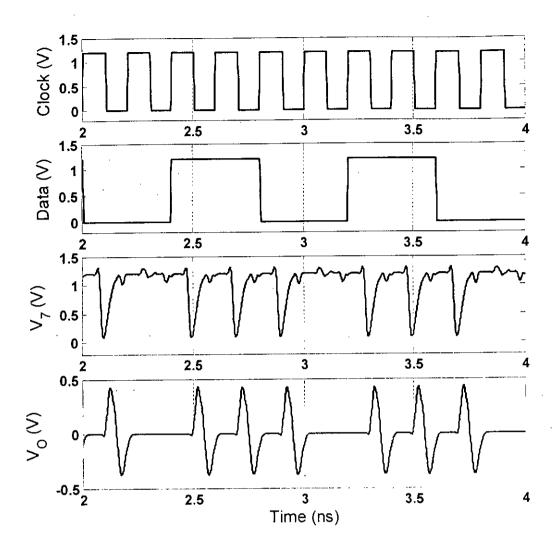

| Figure 4.12: (a)-(c) HSPICE Simulated waveforms at various nodes of the            |

| complete differential UWB Gaussian monocycle OOK transmitter                       |

| operated in SP mode (Clock frequency = 5 GHz, Data rate = 5 Gbps)65                |

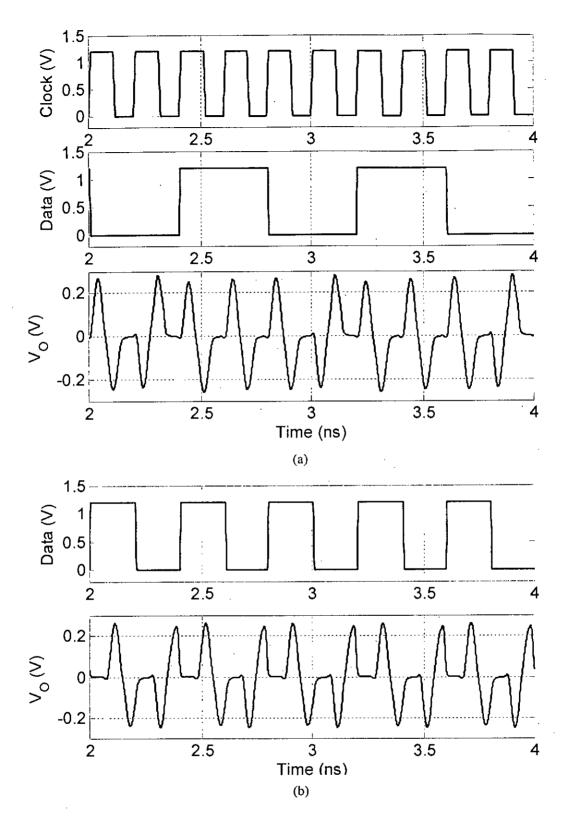

| Figure 4.13: HSPICE Simulated waveforms at various nodes of the complete           |

| differential UWB Gaussian monocycle OOK transmitter operated                       |

| in TR mode (Clock frequency = 5 GHz, Data rate = 2.5 Gbps)66                       |

| Figure 4.14: HSPICE Simulated waveforms of the differential UWB Gaussian           |

| monocycle BPSK transmitter operated in (a) TR mode and                             |

| (b) SP mode (Clock frequency = 5 GHz)67                                            |

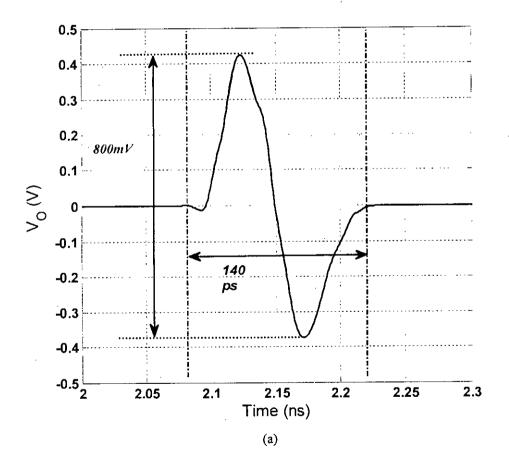

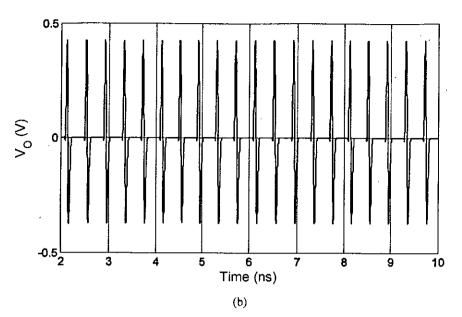

| Figure 4.15: (a) A single generated UWB monocycle pulse,                           |

| (b) a series of pulses at 2.5 Gpps69                                               |

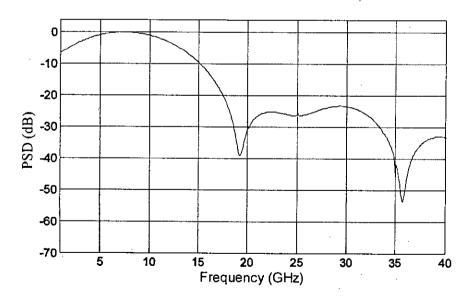

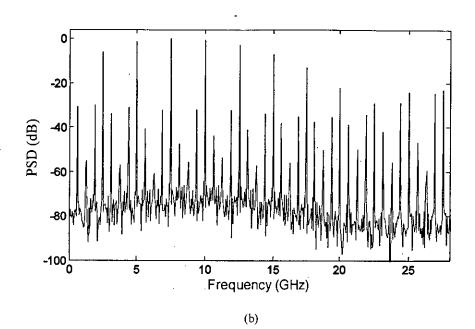

| Figure 4.16: Normalized frequency spectrum of generated Gaussian monocycle         |

| pulse (a) spectrum of a single pulse, (b) spectrum of a series                     |

| of pulses at 2.5 Gpps70                                                            |

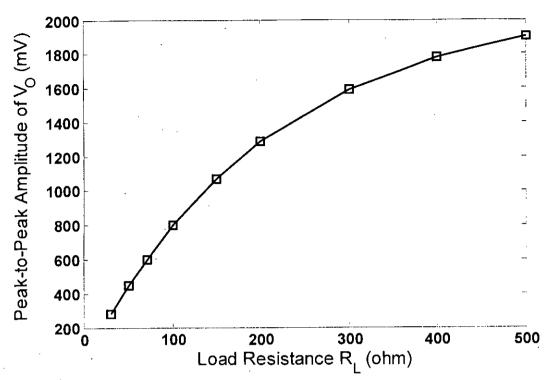

| Figure 4.17: Effect of load resistance on OOK transmitter output waveform71        |

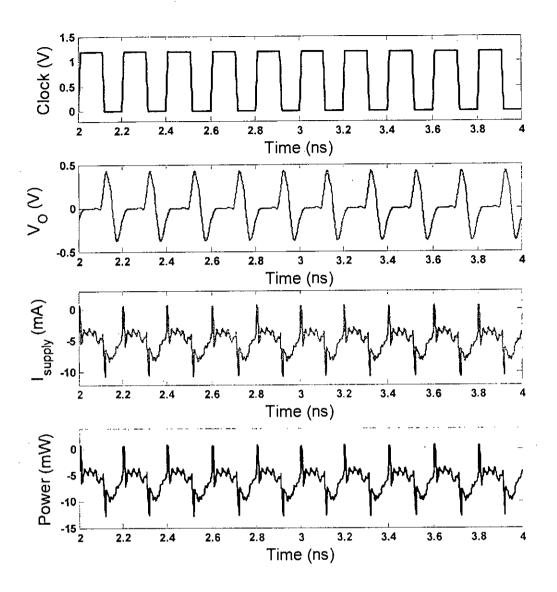

| Figure 4.18: Waveforms of instantaneous current and power supplied by the DC       |

| power source in OOK transmitter72                                                  |

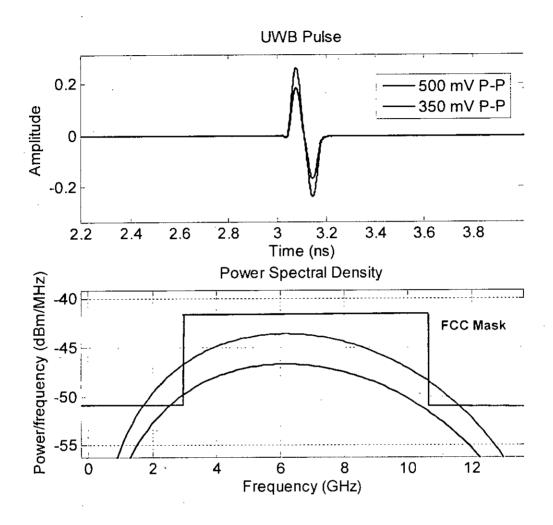

| Figure 4.19: Generated UWB Gaussian monocycle pulse and FCC regulations73          |

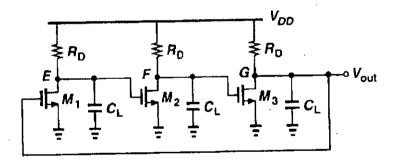

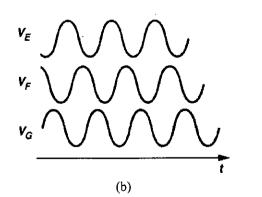

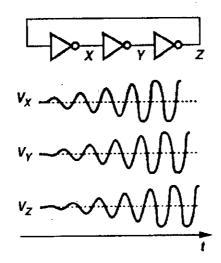

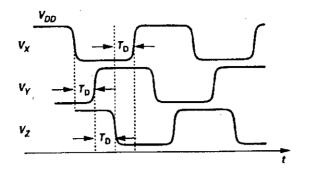

| Figure 4.20: Three-stage ring oscillator (a) circuit, (b) waveforms74              |

| Figure 4.21: Ring oscillator using CMOS inverters                                  |

| Figure 4.22: Waveforms of ring oscillator when one node is initialized at $V_{DD}$ |

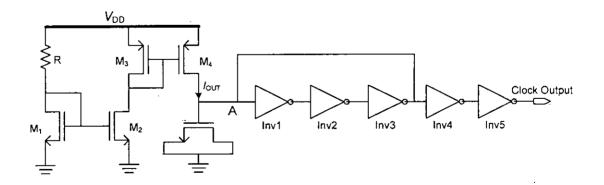

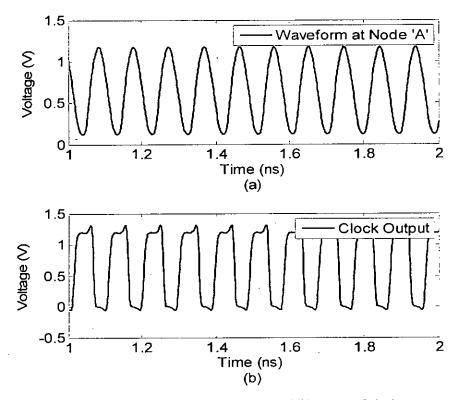

| Figure 4.23: Clock generator circuit using current source                          |

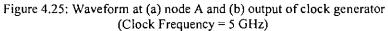

| Figure 4.24: Waveform at (a) node A and (b) output of clock generator              |

| (Clock Frequency = 10 GHz)79                                                       |

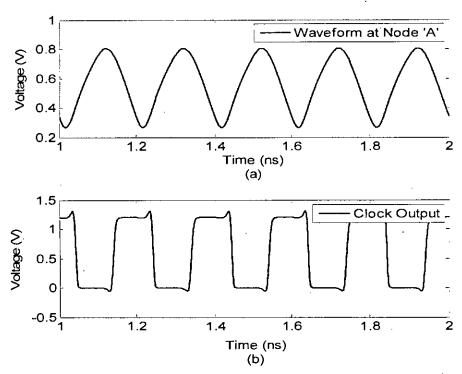

| Figure 4.25: Waveform at (a) node A and (b) output of clock generator              |

| (Clock Frequency = 5 GHz)                                                          |

(

ix

| (b) Cross section (not to the scale)                                                                     | Figure 5.2: Shapes of Dipole Antenna                                      |    |

|----------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------|----|

| <ul> <li>(b) Cross section (not to the scale)</li></ul>                                                  |                                                                           | 82 |

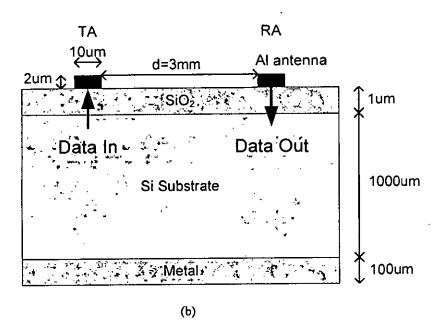

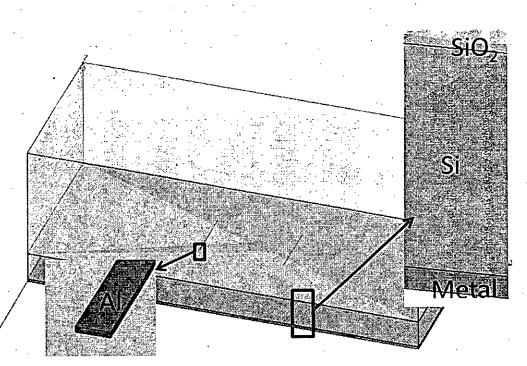

| gure 5.4: 3D structure of the antenna device in HFSS                                                     | Figure 5.3: Schematics of the geometry of antenna structure (a) Top view, |    |

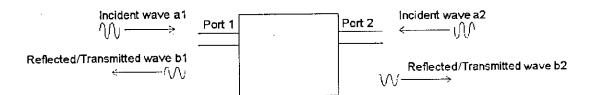

| gure 5.5: Scattering parameter definition                                                                | (b) Cross section (not to the scale)                                      | 83 |

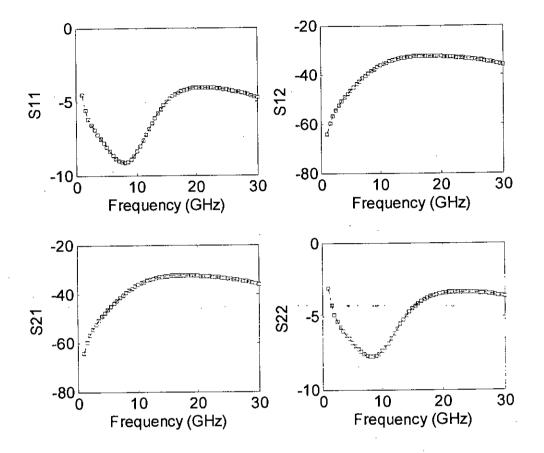

| gure 5.6: Transmission characteristics of integrated dipole antenna<br>( <i>l</i> = 4mm, <i>d</i> = 3mm) | Figure 5.4: 3D structure of the antenna device in HFSS                    | 84 |

| (l = 4mm, $d = 3$ mm)                                                                                    | Figure 5.5: Scattering parameter definition                               | 85 |

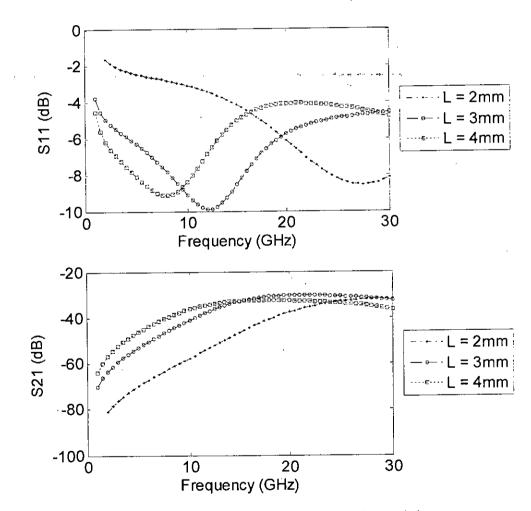

| gure 5.7: Effect of antenna length on transmission characteristics                                       | Figure 5.6: Transmission characteristics of integrated dipole antenna     |    |

|                                                                                                          | (l = 4mm, $d = 3$ mm)                                                     | 86 |

| gure 5.8: Effect of antenna separation on transmission characteristics                                   | Figure 5.7: Effect of antenna length on transmission characteristics      | 87 |

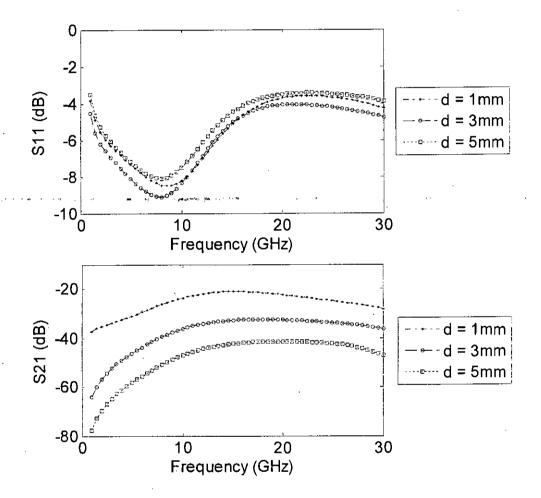

|                                                                                                          | Figure 5.8: Effect of antenna separation on transmission characteristics  | 88 |

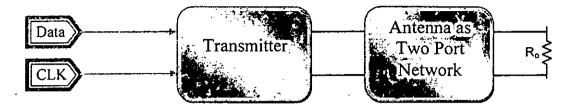

| gure 5.9: Simulation of antenna output signal in Hspice                                                  | Figure 5.9: Simulation of antenna output signal in Hspice                 | 89 |

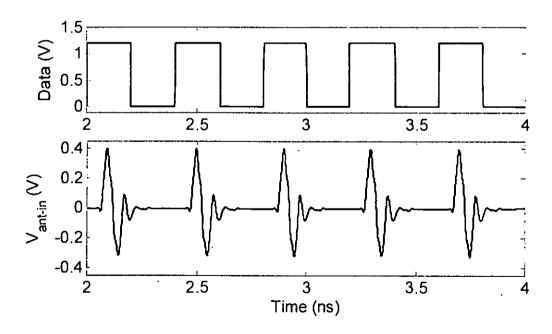

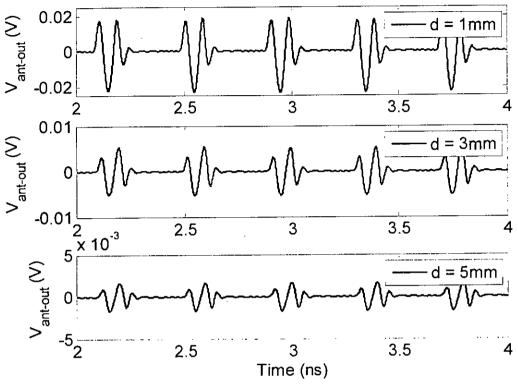

| gure 5.10: (a) Transmitted UWB signal (b) Received UWB signal                                            | Figure 5.10: (a) Transmitted UWB signal (b) Received UWB signal           |    |

| for various distances                                                                                    | for various distances                                                     | 90 |

X

# List of Tables

| Table 4.1: Data Rates for different modes of operation       | 63 |

|--------------------------------------------------------------|----|

| Table 4.2: Properties of the designed UWB transmitter        | 74 |

| Table 4.3: Performance Comparison of UWB transmitters        | 75 |

| Table 5.1: Properties of materials used in antenna structure | 84 |

# List of Abbreviations

| IR-UWBImpulse Radio Ultra WidebandTRTransmitted ReferenceOOKOn Off KeyingBPSKBipolar Phase Shift KeyingPPMPulse Position Modulation |

|-------------------------------------------------------------------------------------------------------------------------------------|

| OOKOn Off KeyingBPSKBipolar Phase Shift Keying                                                                                      |

| BPSK Bipolar Phase Shift Keying                                                                                                     |

|                                                                                                                                     |

| PPM Pulse Position Modulation                                                                                                       |

|                                                                                                                                     |

| FCC Federal Communication Commission                                                                                                |

| ITRS International Technology Roadmap for Semiconductors                                                                            |

| RF Radio Frequency                                                                                                                  |

| PCIe Peripheral Component Interconnect express                                                                                      |

| SP Single Pulse                                                                                                                     |

| SNR Signal to Noise Ratio                                                                                                           |

| PSD Power Spectral Density                                                                                                          |

| LNA Low Noise Amplifier                                                                                                             |

| LPF Low Pass Filter                                                                                                                 |

| PRR Pulse Repetition Rate                                                                                                           |

| GMP Gaussian Monocycle Pulse                                                                                                        |

| DGP Derivative of Gaussian Pulse                                                                                                    |

| GP Gaussian Pulse                                                                                                                   |

| MP Monocycle Puise                                                                                                                  |

xii

### Acknowledgements

Every honor and every victory on earth is due to Allah, descended from Him and must be ascribed to Him. He has endowed me with good health and with the capability to complete this work. I convey my utmost praise to Him for letting me the opportunity to submit this thesis.

I am very grateful to my supervisor, Professor Dr. A. B. M. Harun-ur Rashid for his soft and kind hearted attitude towards me and convey my deepest thanks for his continuous guidance, suggestions and wholehearted supervision throughout the progress of the work. Besides giving academic guidance, he was openhearted to provide me all the official formalities regarding the thesis work.

I would like to thank Professor Dr. Md. Saifur Rahman for his inspirations throughout my career and encouragement to complete the work. My heartfelt acknowledgement goes to all other respected members of the board of examiners: Professor Dr. Pran Kanai Saha and Professor Dr. Md. Ashraful Hoque, for their valuable suggestions, advice and corrections.

I would also like to acknowledge with sincere thanks the all-out cooperation and services rendered by the members of our On-chip Wireless Interconnect Group.

Last but not the least, I remember my parents who are always a source of my inspiration in every good action.

xiii

### Abstract

With the continued growth in the integration density of CMOS and clock frequency of ultra-large-scale integrated circuits, the wire interconnects technology is emerging as the major bottleneck to the improvement of integrated circuit (IC) technology. The semiconductor industry has sought to address this primary problem by increasing the thickness of the wires, using more exotic substrate materials with lower dielectric loss tangents, and employing more sophisticated input/output drivers. However, all of these potential solutions are costly, thereby making wireless interconnect technology an increasingly attractive alternative. In this thesis, we have proposed a simple impulse radio ultra wideband (IR-UWB) wireless interconnect system with integrated antennas, transmitters, and receivers for inter-chip and intra-chip communications. To avoid complicated inter-chip/intra-chip channel estimation methods and to reduce electronic overhead in terms of circuit components in the receiver transmitted reference ultra wideband (TR-UWB) signaling scheme has been incorporated in the system architecture that provides straight-forward synchronization. Various UWB pulses have been investigated to explore the ultimate pulse shape which satisfies the FCC regulations and also provides the highest data transmission rate. Novel circuit topologies have been proposed to design complete digital OOK/BPSK UWB transmitters in IBM 90nm CMOS technology. For the transmitters, a Gaussian monocycle UWB pulse is generated using triangular impulse generation technique with novel methodology to include TR pulse. A differential operation has been employed to increase the maximum achievable voltage swing and to immunize environmental noise. The circuits have been developed in an integrated fashion with low power requirements desirable for on-chip wireless interconnects. The performance of the proposed transmitters has been evaluated and compared with some other available UWB transmitters, which shows superior performance over the conventional transmitters. The transmitters together with the on-chip dipole antenna have been simulated to confirm the effective reception of the transmitted signal.

# CHAPTER 1 INTRODUCTION

ſ٦

#### 1.1 Motivation

Modern electronics technology has changed the world in a short time span. A good share of the credit should go to microelectronics. Since the invention of the integrated circuits in the late 1950s, the development of this remarkable device has been blessed by the laws of physics and the science of materials. The initial material choices – silicon substrates, silicon dioxide gate, intermediate dielectrics, aluminum interconnection and process such as planer technology and photolithography have stood the test of 50 years. In addition, the industry has taken the advantage of the fact that decreasing transistor size not only reduced cost, but also improved performance in terms of speed, functionality and power dissipation. However, the laws of physics and the science of materials are becoming less friendly as we approach 100 nm design regime. Despite remarkable experimental results for transistors well below this dimension, there are growing challenges to our ability to effectively stay on the technology roadmap [1].

From the invention of the first transistor the industries have come a long ways to the brink of integrating billions of components on a single chip. Scaling of device dimensions continues to play an important role. Continuous advancements in technology have resulted in integrated circuits with smaller device dimensions and larger area and complexity. Decrease in minimum feature size has led to a decrease in interconnect cross sectional area and pitch. Increase in chip area has resulted in increase in communication distance (wire length). Increase in chip complexity has demanded more communication channels. This has also resulted in an increase in the number of metal layers. For the foreseeable future the scaling of the device dimensions will continue and IC chips with several billion components will be built in the future. To quantify the magnitude of the problem, the delay associated with an interconnect of length, *d*, with negligible series

resistance, is proportional to *d* and the square root of the relative dielectric constant,  $\varepsilon_r$ , of the inter level dielectric (ILD). The delay time is usually called the time of flight (TOF) across the signal line of the given length. For an ILD of  $\varepsilon_r = 4.0$  (SiO<sub>2</sub>), the TOF is about 6ps/mm. For an x-direction signal of interest, it is usually surrounded by many y-direction signal lines on an adjacent wiring layer. These orthogonal signal lines will add capacitance and further degrade the TOF to as much 8ps/mm. These numbers can be compared to the delays of a NAND gate with a fan out of 3, which are around 70, 30 and 12 ps for the 250-, 130- and 45- nm technologies respectively [2].

A microprocessor often requires a long interconnection line between the arithmetic logic unit (ALU) and the cache storage. As a first approximation, the length of this 'global' signal line can be assumed to be equal to the edge dimension of the chip- around 15 mm, 20 mm and 30 mm for the 250-, 130- and 45-nm chip generations. The TOFs for such lines would lie in the 125 to 250 ps range, increasing as the lines got smaller and the chips larger. These numbers range from 2 to 20 times the gate delay for the equivalent design rule, and are totally unacceptable burden in the device performance [3].

ULSI designers have identified various measures that could be undertaken to solve some, if not all of the problems being faced. The shift from aluminum to copper for metallization, the use of low k dielectric layer, reverse scaling of wire geometries, the inclusion of repeaters, and standard cell modification are some that already been successfully implemented. Nevertheless, these evolutionary approaches may soon encounter fundamental material limits. Revolutionary methods and techniques must be pursued to carry on the fast progress of future ULSI technology. One of such possibilities is to use "wireless interconnect using Si integrated antenna" [4, 5].

#### 1.2 On-chip Wireless Interconnect Systems

With appropriate designs, RF/microwave signals can be transmitted efficiently through either free space or guided mediums. However, the efficient transmission and receiving of the RF/microwave signals in free space require the size of antennas to be comparable with their wavelengths. As the CMOS device dimensions continue to scale down, operating speeds and cut-off frequencies ( $f_t$  and  $f_{max}$ ) of CMOS devices will exceed 100 GHz in the near future. At 24 GHz, the wavelength of electromagnetic waves in free space is 12.5 mm and in silicon it is 3.7 mm. This means a quarter wave antenna needs to be only 3 and 0.9 mm in free space and silicon respectively. These in conjunction with the increase of chip sizes to 2 cm x 2 cm have made the integration of antenna for wireless interconnection possible.

Based on these considerations, a wireless interconnects system acts as a miniature wireless LAN (local-area network). Compared to global electrical wires, this wireless scheme potentially offers several advantages. First, circuits can be synchronized over much larger chip sizes because wireless approach provides three to ten times' faster transmission of signals, compared to global wires. In addition, the bandwidth of the wireless interconnect system is only limited by the bandwidth of the transmitting and receiving components and not by the transmission medium, as in the case of global wires. Also the cross talk between channels should be much improved using FDMA and CDMA communication technique. Furthermore, wireless approach can provide new flexibility to reconfigure the interconnect system simply by changing the CDMA codes.

### **1.3 UWB Wireless Communication Systems**

To realize the aforementioned advantages of wireless interconnect systems, the potentials of using Ultra Wideband (UWB) communication technology as the signal transmission technique are being investigated [6, 7]. Ultra-wideband (UWB) is regulated for commercial use in the band from 3.1-10.6 GHz by Federal Communication Commission (FCC) with the constraints of spectral mask which determined the maximum average equivalent radiated isotropic power spectral density of -41.25dBm/MHz and a minimum bandwidth of 500 MHz [8]. There are two approaches for UWB applications, which are Multi-band OFDM UWB and Impulse-Radio UWB (IR-UWB). Recently, low-cost, short-range wireless communication applications like radio frequency identification (RF-ID) and wireless sensor network have drawn much attention from the researcher as well as industries [9]. IR-UWB, without carrier signal, is one of the prominent candidates for those applications since circuit implementation is simpler, no up/down conversion or mixer is needed leading to substantial reduction in chip area and power consumption. IR-UWB uses the nano-second monocycle pulses to transmit the data signal over much wider frequency band than any conventional carrier based wireless systems.

These entire features make UWB scheme attractive for wireless interconnects systems. Moreover, it creates less electrical overhead on the existing circuitry of the chip because of its simplified transceiver architecture [10]. It has been shown that on chip antenna can be effectively utilized for UWB pulse generator thus avoiding expensive and power hungry analog components [11]. Also, to achieve a high data rate with low BER using conventional data transmission technique, one needs a substantial amount of transmitted power. Large transmitted power results in increased power consumption, which generates extra heat in the chip. Since UWB systems use ultra short pulses to transmit data, active signal occupies a small fraction of the total transmission time and hence the average power requirement is very low [12]. Thus the problem of heat generation and area penalty that originates from the circuitry of the intra/inter-chip wireless interconnect systems is radically solved by the use of UWB signal transmission technique.

#### 1.4 UWB Transmitter

UWB transmitter is an indispensable part in the IR-UWB transceivers. Since part 15 of the FCC regulation has been revised for UWB systems [8], several types of UWB systems have been proposed, such as Impulse Radio (IR), Direct- Sequence UWB (DS-UWB), and Multi-Band OFDM (MB-OFDM) [10], [13]. Although the DS-UWB and MBOFDM are potential candidates for wireless personal area network (WPAN) applications, IR has been more attractive for UWB wireless interconnects [13]. A several papers about pulse generator have been published [14]-[34]. Some early works show that pulse generation could be performed by direct synthesis, using step recovery diode and transmission line [35] or using BJT characteristic [36], which is not easy for integration, low cost, low complexity purposes. Many of the papers are based on the analog technique since the digital technique circuitry [37] is complicated. In [38]-[40] analog based pulse generator circuits were presented. Recently, some digital UWB transmitters have been proposed [17], [25], [27] but those published works consume much power and can't provide high data rate. To satisfy the bandwidth, many types of pulses can be the candidates [41], but the Gaussian pulse is preferred since it has no side lobes and a sharp roll-off compared to other pulses. The theory analysis shows that, the higher order derivative of Gaussian pulse, the better roll-off we have and the pulse itself can satisfy the FCC spectral mask without using the filter. But increasing the order of derivatives, hence increasing the complexity of the circuit, increases the pulse width which put a severe limitation on the data transmission rate. All the traditional IR-UWB transmitters did not aware of this limitation because they were based on approaches developed for radar, RFID and wireless sensor networks applications emphasizing much on FCC regulations. Therefore, finding the ultimate pulse shape which will satisfy both FCC regulation and high data rate requirement for wireless interconnects applications deserves attention before designing the transmitter. The digital generation of UWB pulses, which can satisfy the FCC spectral mask with low power and low complexity, is still a challenge at present.

#### 1.5 Research Objectives

The ultimate goal of this work is to develop an ultra wideband transmission technology and to design a low power high data rate UWB transmitter to be used for wireless interconnects systems for the future ULSI. The design objectives for this UWB interconnects systems are as follows:

- ↓ To develop an appropriate UWB communication scheme suitable for on-chip wireless interconnects.

- + To find the most appropriate UWB pulse for chip interconnects for achieving maximum throughput.

- 4 To design a low power high data rate UWB transmitter for on-chip wireless interconnects.

- 4 To assure proper reception of the UWB pulses in the receiver by the on-chip antenna with a power level suitable for the LNA of the receiver.

#### 1.6 Thesis Layout

This thesis comprises of six chapters. In **chapter 1** we gave a brief introduction on the limitations of present day IC technology which has initiated a tremendous research effort to stay on the technology roadmap for the future ULSI. The potentials of using UWB communication technology as the signal transmission technique for wireless interconnects and the present state of UWB transmitter design are discussed. Finally this chapter gives an outline of the objectives of this work.

**Chapter 2** provides a detail literature review of the interconnect technology with its future prospect. It was shown that the main design constraint is the interconnect delay aroused due to the constant scaling down of interconnects which requires innovative techniques to solve. Some revolutionary techniques for interconnects such as 3-D

integration, optical interconnects and wireless interconnects are discussed. The chapter also provides some fundamental preliminaries on wireless interconnect and concludes by describing its promising advantages in wireless chip interconnects.

In chapter 3, we give an overview of the ultra wideband technology which includes the motivation of using UWB technology, UWB definition, advantages of UWB, UWB signaling and pulse shapes, modulation techniques. This chapter also provides the proposed IR-UWB transceiver architecture for wireless IC interconnects and introduces transmitted reference (TR) scheme for communication. The FCC regulation for UWB communication is then described and the ultimate pulse shape for high speed IR-UWB communication is proposed at the end of this chapter.

In chapter 4, we present the complete differential UWB transmitter design with step-by-step demonstration. OOK and BPSK transmitters are devised separately and both include TR scheme. The performances of the transmitters are evaluated and shown with simulation waveforms. A high speed digital clock generator circuit using CMOS inverters is also presented at the end of this chapter.

The on-chip antenna simulation in HFSS is done in **chapter 5** which confirms the successful reception of the transmitted UWB signal. The effect of various parameters of the antenna is also discussed in this chapter.

The thesis is finally concluded in **chapter 7** by presenting a summary of the overall research along with some suggestions for future work.

### CHAPTER 2

### FUTURE OF INTERCONNECT TECHNOLOGY

#### 2.1 Background

The semiconductor industry has evolved at an incredible rate, particularly in the past two decades. Transistor channel lengths have steadily decreased from 2.0  $\mu$ m in 1980 to 0.5  $\mu$ m in 1992 to current (2011) development processes that incredibly have channel lengths as small as 32 nm. Each new generation of devices requires less area and has faster switching speeds than the preceding one. These benefits are reflected at both circuit and chip levels. At the circuit level, a particular function can be computed in less time and implemented in less silicon area. As a result, chips do not have to increase in size to possess more functionality. As a consequence of the transistor scaling, the number of transistors on each chip is increasing, and perhaps more significantly, their density is also increasing. This is a problem when one considers that each device must communicate with other devices, each circuit block needs to talk to other circuit blocks, and so on up the hierarchy. The interconnections required to support this communication grow increasingly more complex. Furthermore, due to the higher clock frequencies, these interconnections need to support higher bandwidths.

It is easy to imagine what problems may occur if this congestion is not addressed. The problem is as familiar as the rush-hour traffic encountered in daily commuting. The obvious solutions of building more highways and widening lanes are prohibitively expensive. Similarly, adding more metal levels and increasing chip size to accommodate more interconnects can significantly add to the overall cost. In short, interconnect design for a high-performance digital system is a growing problem that needs to be addressed early on in a design flow [42].

### 2.2 Conventional On-chip Wiring

On-chip wires have always been necessary to connect circuits together. While the metal and dielectric materials are undergoing changes, the wires largely have remained the same in function and usage. One significant difference is in their growing number. Figure 2.1 shows a Scanning Electron Microscope (SEM) photo of local interconnect with the dielectric material removed [43]. These on-chip wires are thin and narrow with cross-sectional dimensions typically less than half of a micron.

Figure 2.1: SEM photo of lower levels of interconnect (with dielectric material removed) [43]

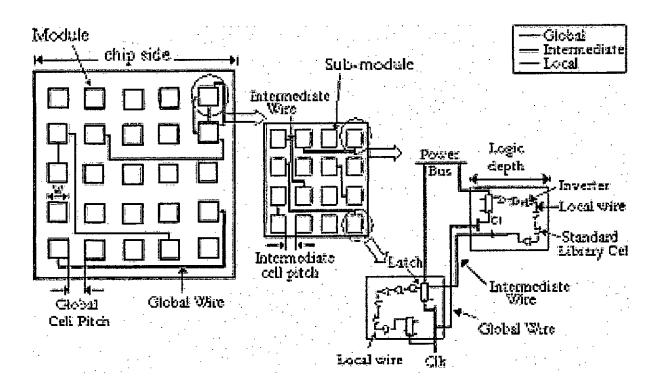

The three tier architectural hierarchy of high-end microprocessor, shown in Figure 2.2, exhibits three distinct levels of wiring hierarchy. The first tier referred to as "local" comprises logic blocks built using standard cells, inverters and latches. These blocks are referred to hereafter as sub-modules. Approximately 80% of the wires on the chip begin and end within these sub-modules. The defining characteristics of these so-called "local wires" are that they are shorter in length and usually carry signals between various layers

of logic within the sub-module. The size of a sub-module is of the order of 10 K to 50 K gates depending upon the design and layout of the microchip.

Sub-modules are used to construct modules that belong to the second tier of the architectural hierarchy. Intermediate wires are defined as those that interconnect multiple sub-modules laid out according to a semi-global floor plan. They are usually of lengths between that of local and global wires and are mostly used for signal communications, but may also assist in clock distribution.

Finally, modules are arranged according to a pre-defined global floor plan to construct the third and final tier entity i.e. the chip itself. **Global wires** interconnect the modules and carry signals, clock and power between them.

Figure 2.2: Three Tier Architectural hierarchy for VLSI circuit design

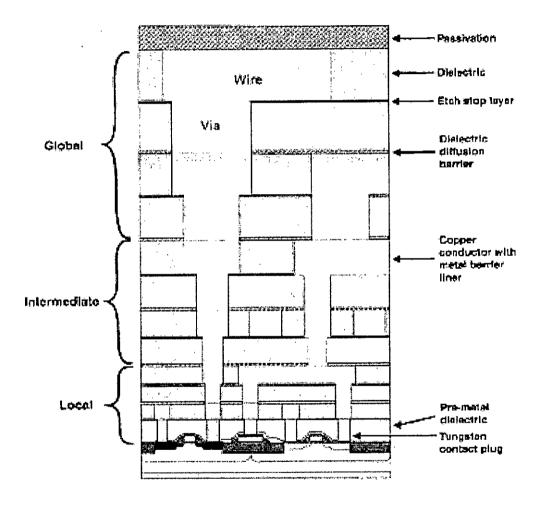

A wiring hierarchy is typically used that places the shorter wires nearer to the silicon surface and increasing longer wires on higher layers. Figure 2.3 shows a cross-section of an advanced hierarchical wiring scheme using copper metallization [44]. The lower levels of interconnect are thinner and are used in local routing. Intermediate layers

are of medium thickness and used for semi-global routing. Finally, the top layers are the thickest and are used for global routing. Alternating levels of interconnect are customarily laid out in orthogonal directions to minimize cross-talk between adjacent levels. Furthermore, this convention helps to simplify routing.

#### **Typical Chip Cross Section**

Figure 2.3: Sample cross-section of hierarchical wire scaling [44]

#### 2.3 Logic and Wire Delays

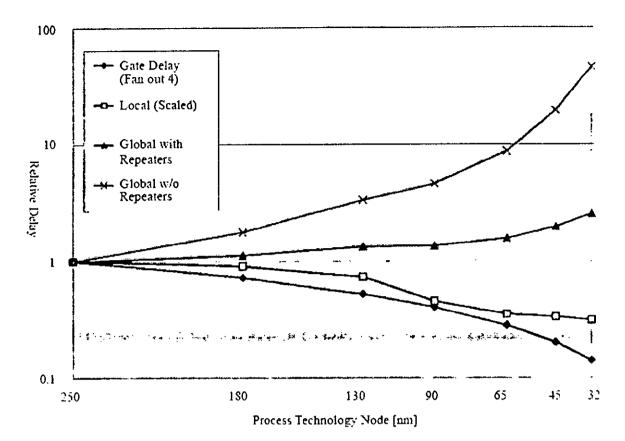

The International Technology Roadmap for Semiconductors (ITRS) illustrates the growing problem of global interconnects delays (Figure 2.4) [44]. As technology continues to scale, the logic delays decrease due to faster transistors. At the same time, local interconnect delays similarly improve because the physical size of circuit blocks decrease, and the local interconnect spans shorter distances. On the other hand, the global interconnect delays rise with technology scaling for one of two different reasons. The first possible reason is that overall chip size increases so that interconnects need to span longer distances. A second, more likely, scenario is, even if chips do not become larger, the increased complexity of circuits requires an increased density of interconnects. This is achieved by reducing the cross-sectional area of wires, which negatively impacts the resistance, and decreasing wire spacing, which adversely impacts the capacitance. The combination of these factors results in global interconnect delays that scale in the wrong direction. Repeaters help alleviate this growing divergence between logic and global interconnect delays, but are not enough to close the performance gap.

Overall circuit performance in the past has depended primarily on device properties. To enhance the circuit and system speed the primary effort had been on improving the device speed through scaling the device dimensions. The parasitic resistance, capacitance and inductance associated with interconnections (Figure 2.5) and contacts are now beginning to influence circuit performance and will be one of the primary factors in the evolution of deep submicron ULSI technology. The results of theoretical modeling indicate that below 1  $\mu$ m minimum feature size the impact of parasitics seriously hurts circuit and system performance [45]. RC time delay, IR voltage drop, CV<sup>2</sup>f power consumption and crosstalk noise due to these parasitics is becoming appreciable.

Figure 2.4: International Technology Roadmap for Semiconductors 2001 predictions for device and wire delays [44]

Figure 2.5: Dense mesh of interconnect typical of modern high-performance integrated circuits, with series resistance and shunt capacitance indicated

. .

#### 2.4 Evolutionary Approaches to Global Interconnect

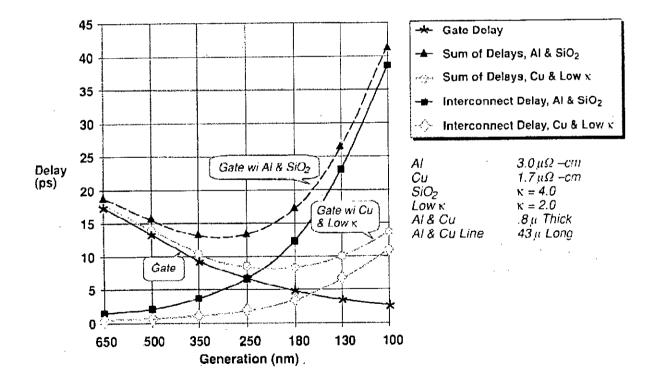

Much of the work related to improving global interconnects is in reducing the resistance and capacitance of the wires. Along these lines, semiconductor fabrication facilities have introduced integration of new materials [46], [47]. Copper metallization provides lower resistance than similarly sized aluminum wires, and lower permittivity dielectrics provide lower capacitance. Introduction of these materials is expensive due to extensive reliability requirements and fabrication tool adaptation. At the circuit level, designers have sought to reduce capacitance by preventing wire switching in opposite directions. These techniques have shown to be effective in reducing the wire delay, but are not enough. Thus even with very fast devices and with copper and low-k dielectrics the overall performance of a large circuit could be seriously affected by the limitations of interconnections and contacts as shown in Figure 2.6 [1].

Figure 2.6: Calculated gate and interconnect delay versus technology generation [1]

### 2.5 Revolutionary Techniques of Interconnection

The evolutionary approaches being used to solve the problems imposed by interconnects eventually encounter fundamental materials limits. Therefore, revolutionary new techniques are needed to provide a paradigm shift to continue the progress in integrated electronics. Examples of such techniques are:

- + Three-dimensional ICs with multiple layers of active devices

- Optical interconnects for on-chip and chip-to-chip interconnects

- **4** RF/wireless interconnect for inter- and intra-chip communications

- These approaches are briefly discussed and compared below.

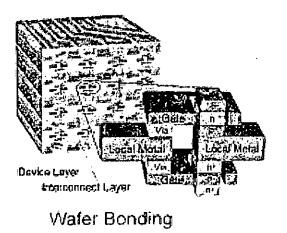

#### 2.5.1 3-D Integration

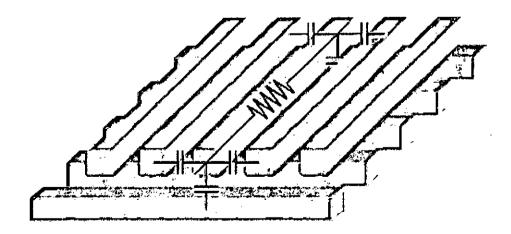

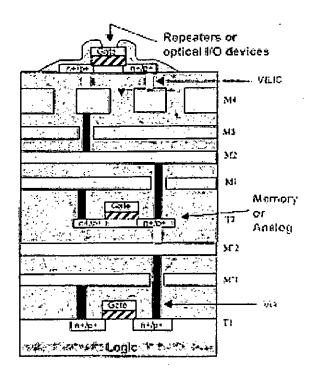

3-D integration of active transistor layers or, as an intermediate step placement of the clock/signal and power/ground wires on opposite sides of a chip, can reduce the number and average length of two-dimensional (2-D) global wires by providing shorter "vertical" paths for connection. A 3-D approach has also been shown to reduce overall chip area when designs are interconnect-limited. Several different schemes have been proposed for implementing 3-D integration for the advanced technology nodes as shown in Figure 2.7 [48].

Seeding crystallization of a-Si

Figure 2.7: Different approaches to fabricate 3-D circuits [48]

3-D integration also offers some attractive advantages related to system performance and enabling of new system architectures. First, it can extend the performance of high-speed transistors to technology nodes where the global wires otherwise are expected to present serious frequency limitations to advanced CMOS. Second, for systems-on-chip (SOC) applications, 3-D integration may provide the means to integrate dissimilar technologies (digital, memory, analog, RF, etc.) in the same cube but on different active layers. For example, power hungry digital circuits could be located on the bottom layer adjacent to the heat sink and lower-power/highervoltage analog circuits on the top active layer. 3-D approaches could also enable integration of huge amounts of cache memory on top of a high performance microprocessor chip.

Complex and difficult challenges remain, however, including management of thermal dissipation from interior stacked active layers, the need for 3-D routing and

placement tools, development of new systems architectures to exploit 3-D integration, etc. Furthermore, there are diminishing returns for adding more than three or four active layers to a 3-D chip. For this reason, including more than four active layers would provide no further savings in active chip area needed to realize a system function or, therefore, in cost per transistor or function.

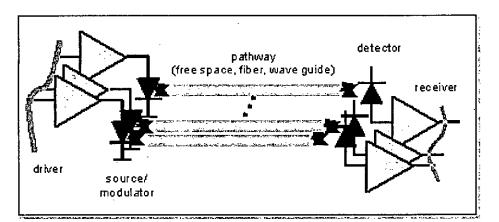

#### 2.5.2 Optical Interconnect

Optical interconnect technologies have long been considered as attractive alternatives to providing both inter-chip and, perhaps eventually, intra-chip replacement technology for metal/dielectric global interconnects [49]. Proposed optical approaches can be grouped into **guided wave** and **free space**. Guided wave optics involves the use of waveguides to contain the optical signals within a board, package, or on a chip. Free-space optics utilizes diffractive optics and conventional lenses or micro lens arrays to guide single or multiple parallel optical beams in free space. Figure 2.8 shows a typical view of an optical interconnect system using optical modulator and detector units.

Figure 2.8: Optical interconnect concept

Compared to electrical wires, optical technology offers fundamental advantages to global interconnects, given that the technology can be realized in a simple, cost effective implementation. The bandwidth of electrical interconnects is  $\sim A/l^2$ , where A is

the cross section area of interconnect and *l* is the length. Optical interconnects, however, are not bandwidth limited in this way, although they are limited by the propagation delays of optoelectronic components such as transmitters, modulators, and receivers. Optical interconnects must overcome some rather difficult fundamental and technological challenges before they will find application as on-chip interconnects. The first issue, particularly for on-chip guided wave optical interconnects, is the relative size of optical components (particularly waveguides and photo-receiver circuits) required. For this reason, guided wave optical interconnect to the functional blocks to support the required optoelectronic components. Power dissipation for receivers, and, to a lesser extent, transmitters can be prohibitively large. Other issues with optical interconnects are the technologies for fabricating III–V devices on silicon. Hetero-epitaxial growth of III–V vertical-cavity surface-emitting lasers (VCSELs) on silicon CMOS circuits is a very difficult technology limited by reliability concerns.

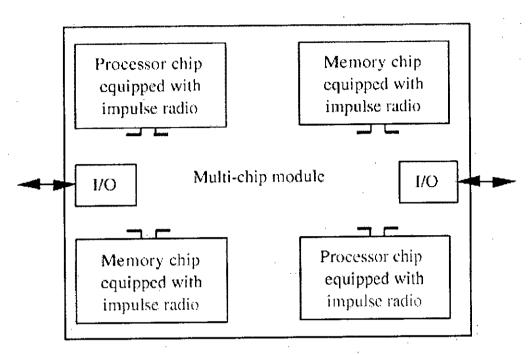

#### 2.5.3 Wireless Interconnect

A wireless interconnect technology uses a radio technology to provide communications between functions on a large integrated circuit chip (intra-chip) as well as communications between functions on separate chips (inter-chip) located on a multichip module or on a motherboard, where distances are measured in a few to tens of centimeters and data rates are gigabits per second. The wireless interconnect technology has become possible due to the confluence of wireless communications algorithms with RF silicon processes. For example, Floyd *et al.* have demonstrated a wireless interconnect technology with integrated antennas, transmitters, and receivers in a 0.18-um CMOS process for intra-chip clock distribution at 15 GHz [5]. Zhang has evaluated the performance of a wireless interconnect technology for intra-chip data transmission at 15 GHz [50]. Chang *et al.* have implemented a wireless interconnect technology for inter-chip data transmission at 15 GHz [50]. Chang *et al.* have implemented a wireless interconnect technology for inter-chip data transmission at 15 GHz [50]. Chang *et al.* have implemented a wireless interconnect technology for inter-chip data transmission at 15 GHz [50]. Chang *et al.* have implemented a wireless interconnect technology for inter-chip data transmission at 15 GHz [50]. Chang *et al.* have implemented a wireless interconnect technology for inter-chip data transmission at 15 GHz [50]. Chang *et al.* have implemented a wireless interconnect technology for inter-chip data transmission at 15 GHz [50]. Chang *et al.* have implemented a wireless interconnect technology for inter-chip data transmission at 15 GHz [50]. Chang *et al.* have implemented a wireless interconnect technology for inter-chip data transmission at 15 GHz [50]. Chang *et al.* have implemented a wireless interconnect technology for inter-chip data transmission at 15 GHz [50].

very new approach, and much work remains to be done before becoming a viable candidate to replace global wires.

Figure 2.9: Wireless interconnect using impulse radio for interchip communication [52]

Figure 2.9 illustrates the wireless interconnect technology within a multichip module that features the use of impulse radio [52]. Conventionally, a processor chip interconnects with a memory chip in the multichip module using a peripheral component interconnect express (PCIe) circuit. The PCIe circuit is a recent industry standard in which a differential driver and a differential receiver reside on the processor chip, and a differential driver and a differential receiver reside on the memory chip. The differential driver on the processor chip is coupled to the differential receiver on the memory chip through a pair of wires. The differential driver on the memory chip is coupled to the differential receiver on the processor chip through another pair of wires. The pair of wires needs to support a high data rate of 2.5 Gbps. The PCIe standard is intended to provide architecture that can extend into the future to accommodate the ever-increasing requirements for communication performance between chips. The wireless interconnect technology employs an impulse radio to realize a wireless PCIe.

Specifically, an impulse transmitter replaces a PCIe driver, an impulse receiver replaces a PCIe receiver, and an antenna replaces a pair of wires. As compared with the conventional PCIe, the wireless interconnect technology has such advantages as scalability and reconfigurability. It can also be used at the system level to attain fault tolerance, because one can reconfigure the multichip module by software commands to debug and then to eliminate the fault chips via reconfiguration. To fully exploit the capabilities of the wireless interconnect technology for inter-chip communications, the assessment of the theoretical performance of the impulse radio over an inter-chip wireless channel appears desirable. Zheng *et al.* evaluated the performance of the binary phase-shift-keying (BPSK) impulse radio over an inter-chip wireless channel of length 20 cm [52]. The impulse radio operates with the radiated power spectral density < -41 dBm/MHz (or the average transmitted power less than -2.85 dBm) to meet the emission regulation over the UWB from 3.1 to 10.6 GHz [8].

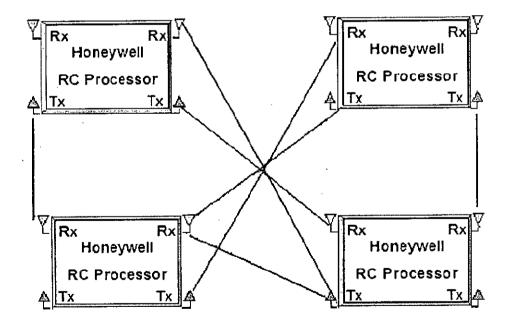

#### Wireless Interconnect

Figure 2.10: Chip-to-chip wireless links [53]

A generic board designed for multiple applications will have to be routed as depicted in Figure 2.10 [53]. Each processor, which is Field Programmable Gate Arrays (FPGAs), now has to communicate through each other if it does not have a direct trace to the device. However, a wireless link will allow the point to point communication link. Mapping new algorithms or systems that have different data rate requirements would be easily achievable with re-configuring the wireless link. With such a configurable wireless link, the data sharing and processing will allow a single device to communicate to multiple devices and vice versa. Distributed process can be easily achieved with the available bandwidth.

Compared to global electrical wires, RF interconnects potentially offer several advantages. First, circuits can be synchronized over much larger areas because wireless approach transmit signals three to ten times' faster compared to global wires. In addition, the bandwidth of the RF approaches, much like optical interconnects, is only limited by the bandwidths of the transmitting and receiving components, and not by the transmission medium, as is the case for global wires. Also, the crosstalk between channels should be much improved, particularly for the approach using FDMA and CDMA communication techniques.

RF interconnect has to overcome some difficult challenges before becoming a viable candidate to replace global wires. First, for package applications, the RF implementation must be cost competitive with conventional interconnect systems. Further, the power dissipated by RF interconnect support circuits must be equal to or less than the power dissipated by the global interconnect wires, and the silicon area consumed by these RF circuits must only be a small fraction of the chip size. Also, the RF power dissipation cannot add a significant amount of heat to an already heavy thermal load. Finally, similar to optical interconnects, RF interconnect systems will likely require adaptation of new system architectures to fully exploit the capabilities of RF interconnects.

21

~°.

Though both optical and wireless interconnect schemes are simultaneously evaluated as a new technology solution for the future ULSI, the later shows a number of promising advantages.

- Optical interconnect requires conversion of electrical signal into optical signal at the transmitter side and optical signal to electrical signal at the receiver end.

Optical devices are fabricated using III V group which are not compatible with existing Si technology and hence costly to implement. On the other hand wireless interconnects provide completely CMOS compatible architecture.

- ✤ The relative size of optical components (particularly waveguides and photoreceiver circuits) compared to chip circuitry is a critical design constraint. That is why, optical interconnects may require separate active layers in the vertical dimension with via interconnect to the functional blocks to support the required optoelectronic components. To the contrary, no special guided wave mechanism is required for on-chip wireless interconnect hence it reduces the electronic overhead on the existing circuit components.

# CHAPTER 3 UWB WIRELESS CHIP-TO-CHIP COMMUNICATION

Ultra-wideband (UWB) is a promising technology for networks requiring a very high data rate at short distances. Chip to chip, board to board, and box to box interconnects can also make use of an UWB based wireless link. In these cases, the distances are even shorter compared to a networking application, and the UWB designer can take advantage of this fact for high speed link. After providing some basic fundamental definitions on UWB techniques, this chapter describes the proposed architecture for UWB transceiver intended to use for on-chip wireless interconnects. The ultimate shape of the transmitting UWB pulse capable of both carrying high data rate and satisfying the FCC regulations is also investigated at the end of this chapter.

#### 3.1 Motivations for Developing UWB System

Modern integrated circuits require high capacity channel to communicate between chips and also within the chips. According to Shannon's channel capacity theorem [54]. channel capacity C is given by

$$C = B \log_2\left(1 + \frac{S}{N}\right) \tag{3.1}$$

where, B is the bandwidth, S is the total signal power, and N is the total noise power. It is clear that the channel capacity (data rate) increases linearly with the bandwidth and logarithmically (and hence weakly) with the signal-to-noise ratio (SNR). For fixed SNR we, therefore, need huge bandwidth for high capacity or bit rate for example, 10-20 Gbps or even more. Since ultra wideband, as its name implies, provides large bandwidth, we

have moved from traditional narrowband system to UWB technology for on-chip wireless interconnects.

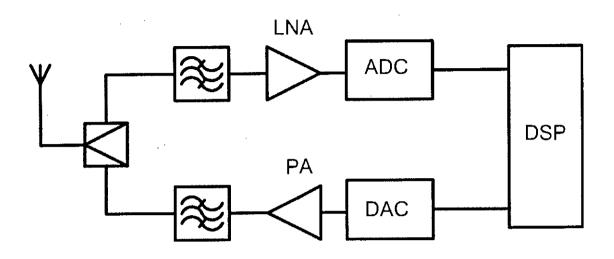

Figure 3.1: Block diagram of the impulse-radio transceiver [55]

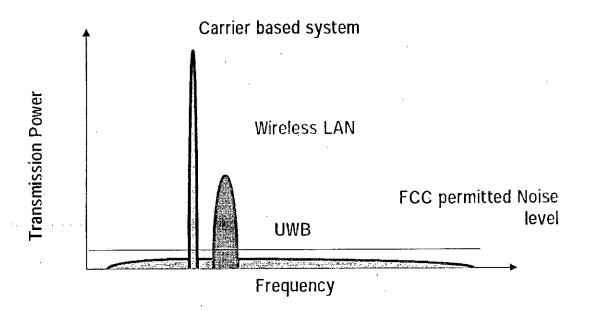

The UWB system not only helps achieve high data rates, but also allows operation at a significantly lower signal power than narrowband systems, with only a minor effect on channel capacity [17]. Figure 3.1 shows an ideal UWB transceiver architecture used in an impulse-radio transceiver [55]. Many components, including frequency synthesizers, down-conversion mixers, up-conversion mixers, image-rejection filters, and channelselection filters, that are used in narrowband transceivers can be eliminated from a UWB transceiver. Signal processing tasks such as modulation, demodulation, channel selection, and filtering that were previously performed by the RF and analog circuits in narrowband transceivers can now be executed in the digital domain by the baseband digital signal processing (DSP) circuits [55]. Many advantages can be achieved by using fewer RF circuits, including reduction in the hardware, power, cost, and number of design cycles, as well as high integration and more flexibility. Also, the low RF signal power of the UWB system further reduces the transceiver's power consumption. The ability of a UWB communication system using modulated short pulses to operate without a carrier signal allows a very efficient use of the signal spectrum [56]. The PSD of UWB systems (Figure 3.2) is so low (lower than -41.3 dBm/MHz) that it does not cause any interference with

24

existing narrowband communication systems in the same frequency band. For instance, a 802.11.a (5 GHz) system would not be affected at all by UWB signals [57]. All these remarkable properties strengthen our choice for employing UWB system.

t

Figure 3.2 PSD of different wireless communication systems

#### 3.2 Fundamentals of Ultra-Wideband System

#### 3.2.1 UWB Definition

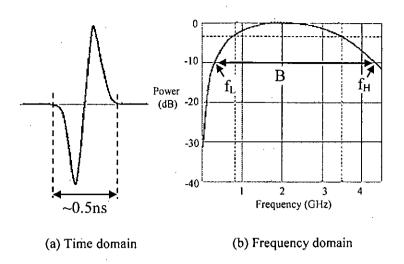

UWB technology is generally defined as any wireless transmission scheme where the fractional bandwidth is greater than 20% or occupies 500MHz or more bandwidth. The fractional bandwidth is defined as  $B/f_c$ , where  $B=f_H - f_L$  denotes the -10 dB bandwidth and center frequency  $f_c = (f_H + f_L) / 2$  with  $f_H$  being the upper frequency of the -10 dB emission point, and  $f_L$  the lower frequency of the -10 dB emission point as depicted in Figure 3.3.

Figure 3.3: Ultra wideband signals

The main core of the technology is the usage of the pulse-code modulation of ultra wide band signals for data transmission. Instead of transmitting a continuous carrier wave modulated with information or with information combined with the spread code, which determines the bandwidth of the signal, a UWB radio system transmits a series of very narrow impulses, typically with the pulse widths of about 0.5 ns.

The intervals between these pulses may vary from 0.1 to 100 ns. These short timedomain impulses take the form of a single cycle, or Gaussian monocycle transformed into the frequency domain result in the ultra wideband spectrum. Indeed, the central frequency  $f_c$  is roughly inverse to the width  $\tau$  of the pulse  $f_c \sim 1/\tau$ , so for the single impulse with the width of 0.5 ns the central frequency is about 2 GHz.

#### 3.2.2 UWB Advantages

UWB is a newly developed carrier less wireless RF technology, and is considered to be a potential solution to a wide range of RF problems. UWB transmitters transmit trains of extremely short pulses at precise time intervals, resulting in a very low power signal that can coexist with other radio systems. Its features can be summarized as:

- Ultra wideband and ultra-low PSD

- Extremely low transmission energy

- 🔸 👘 Very high data rate

- Hase-band communications

- **L** Excellent immunity to interference from other radio systems

- 🔸 👘 Excellent multipath immunity

- Low probability to intercept

- Vearly 'all digital' architecture with simple CMOS circuitry

- Commonality of signal generation and processing architectures

- Here Potentially small size and processing power

- Low cost

Ultra Wideband is a promising technique for wireless communications. In contrast with the conventional communication systems using the "sine wave", UWB information is carried in very short pulse, which covers an extremely wide spectrum bandwidth. So, the RF and analog receiver circuitry is reduced to a wide band low-noise amplifier. a correlator and data converters. No up down conversion is needed, which results in substantial reduction of transceiver area, power, and can be integrated with low price CMOS circuit. UWB is a carrier-free (base-band) technique, which will greatly reduce the complexity and cost of the transceiver.

A very wide bandwidth means better multipath mitigation, interference mitigation by using spread spectrum techniques, more users and high data rate. Short impulse (typically <1ns) prevents destructive interference from multipath and the multipath components can be individually resolved. Carrier-less nature of waveform results in less fading, even when pulses overlap. This reduces fade margin in link budgets.

This ultra wideband signaling scheme is particularly attractive for wireless interconnect systems for several reasons. First, it creates less electrical overhead on the existing circuitry of the chip because of its simplified transceiver architecture. UWB systems can be made nearly "all digital", with minimal RF and microwave electronics. Second, on chip antenna can be effectively utilized to transmit UWB pulse thus avoiding

expensive and power hungry analog components. Third, to achieve a high data rate with low BER using conventional data transmission technique, one needs a substantial amount of transmitted power. Large transmitted power results in increased power consumption, which generates extra heat in the chip. Since UWB systems use ultra short pulses to transmit data, active signal occupies a small fraction of the total transmission time and hence the average power requirement is very low.

Therefore, low power, low cast and very wide bandwidth make carrier less UWB technology an attractive competitor in wireless interconnect system design.

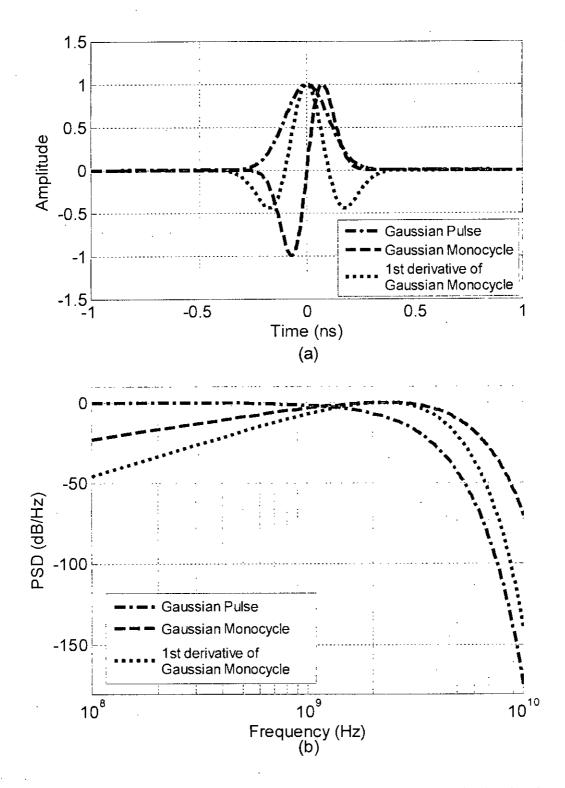

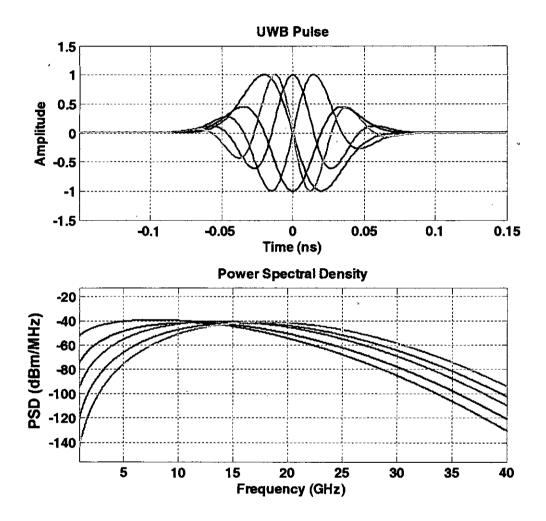

#### 3.2.3 UWB Signaling and Pulse Shapes

UWB is a base-band technology, and thus the choice of the monocycle shape will affect the performance. Several possible monocycles for UWB are listed below [41].

#### i. Gaussian pulse

The Gaussian pulse often used to model UWB signal can be represented by

$$p(t) = Ae^{-\frac{(t-\mu)^2}{2\sigma^2}}$$

(3.2)

where,

A is the pulse amplitude (volts)

t is time (seconds)

$\sigma$  is the standard deviation of the Gaussian pulse (seconds)

$\mu$  is the mean value of the Gaussian pulse (seconds)

#### ii. Gaussian Monocycles

The Gaussian monocycle is similar to the first derivative of the Gaussian pulse and is given by

$$p'(t) = -\frac{A}{\sigma^2} (t - \mu) e^{-\frac{(t - \mu)^2}{2\sigma^2}}$$

(3.3)

#### iii. Scholtz's Monocycles

This monocycle appears in Dr. Scholtz's papers, so we call it Scholtz's monocycle. It is similar to the second derivative of the Gaussian pulse and can be represented by

$$p'(t) = \left[ -\frac{A}{\sigma^2} + \frac{A}{\sigma^4} (t - \mu)^2 \right] e^{-\frac{(t - \mu)^2}{2\sigma^2}}$$

(3.4)

#### iv. Higher Order Gaussian Monocycles

Higher order derivatives of Gaussian monocycles are also widely used in the design of UWB transmitter depending on the system power spectrum requirements.

The time domain waveforms of Gaussian pulse, Gaussian monocycles, Scholtz's monocycles along with their power spectrum densities are illustrated in Figure 3.4. As shown in figure, Gaussian pulse has dc spectral components, which may reduce the antenna radiating efficiency and, therefore, basic Gaussian pulse is normally not used in UWB systems. Moreover, Gaussian and its nth-derivative pulses are favored over other waveforms, e.g. rectangular and sinusoidal, for UWB since their side lobes have the smallest energy.

Figure 3.4 (a) Generally adopted Gaussian pulse shapes in UWB communication ( $\sigma = 0.1$ ns) (b) Fourier transform of the pulse shapes

#### 3.3 Modulation Types

Although numerous modulation techniques are used with impulse-radio UWB, three common schemes are often found in research papers and journals. On-Off Keying (OOK), Bipolar Phase Shift Keying (BPSK), and Pulse Position Modulation (PPM) are popular UWB modulation techniques due to their simplicity and flexibility towards low duty cycle pulsed communication systems. The basic techniques of signal transmission under different modulation schemes are outlined in Figure 3.5.

**Binary Modulation:**

Pulse Position Modulation (PPM)

Pulse Amplitude Modulation (PAM)

On Off Keying (OOK)

Bipolar Phase Shift Keying (BPSK)

#### 3.3.1 On Off Keying (OOK)

On Off Keying is the simplest pulse modulation technique where a pulse is transmitted to represent a binary "1", while no pulse is transmitted for a binary "0", as depicted in Figure 3.5.

One obvious advantage of using OOK is the simplicity of the physical implementation, as one pulse generator is necessary, as opposed to two, as is the case with bi-phase modulation. A single RF switch can control the transmitted pulses by switching on for a "1" data bit and off for a "0" data bit. This effortless transmitter configuration makes OOK popular for less complex UWB systems. Although OOK has a very straightforward implementation, there are some system drawbacks. In either a hardware or software based receiver design, synchronization may be lost if the data contains a steady stream of "0's".

#### 3.3.2 Binary Phase Shift Keying (BPSK)

The most common form of PAM in UWB communications is bipolar phase shift keying (BPSK), where the polarity of a pulse is modulated. In this situation, a positive pulse is transmitted for a "1" and a negative pulse is transmitted for a "0".

One advantage of BPSK modulation is its improvement over OOK in BER performance. Another benefit of bi-phase modulation is its ability to eliminate spectral lines due to the change in pulse polarity. This aspect minimizes the amount of interference with conventional radio systems. A decrease in the overall transmitted power could also be attained, making bi-phase modulation a popular technique in UWB systems when energy efficiency is a priority. A disadvantage of bi-phase modulation is the physical implementation is more complex, as two pulse generators, one of them with the opposite polarity, are normally necessary instead of one, as is the case with OOK. This presents a problem when attempting to transmit a stream of pulses, as the time between pulses can become non-periodic if the pulse generators are not triggered in a timely fashion.

#### 3.3.3 Binary PPM

The last popular UWB modulation scheme to be discussed is PPM, which is a technique where the timing of each pulse is altered to transmit data instead of varying the amplitude. The simplest form of PPM is binary PPM, where a pulse in a uniformly spaced pulse train represents a "0" and a pulse offset in time from the pulse train represents a "1." Conceptually, the binary PPM technique is shown in Figure 3.5.

The most advantageous feature of PPM is the orthogonal signaling present in its data. Each of the pulses in time is independent of one another, meaning the time during the symbol period can be broken up to look for each pulse within a specified time slot. In the case of M-ary modulation schemes, PPM provides better error performance than PAM and also has the advantage of permitting non-coherent reception. One of the disadvantages of PPM is its poor BER performance. Another apparent drawback to PPM is its susceptibility to inter-symbol interference, as multiple positions are required to transmit at a higher data rate. PPM must lower the transmitted pulse rate to account for this effect. Therefore, there is a data rate limitation when using M-ary PPM in impulse-radio UWB applications. Even when the inter-symbol interference is reduced at the transmitter by decreasing the pulse rate, multipath are more likely to overlap with the next data pulse, causing bit errors at the receiver if the reflections are strong. These types of problems lead to a more complex receiver design, which hampers the use of PPM.

#### **3.4 IR-UWB Architecture for Interconnects System**

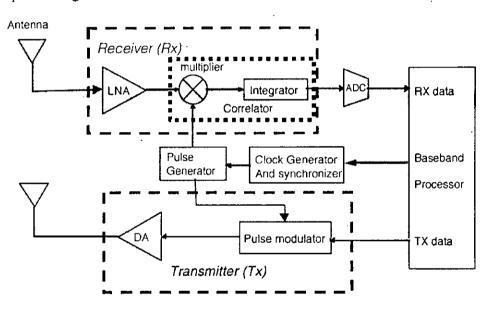

Since UWB wireless interconnects is a new technology, very few system architectures are found in the literature. Zheng *et al.* [52] proposed a block diagram of the UWB impulse-radio transceiver architecture as shown in Figure 3.6. The building blocks of the UWB transmitter comprise a UWB Gaussian pulse generator, modulator, and a UWB driver amplifier (DA). The Gaussian pulse generator generates a UWB Gaussian pulse and the UWB pulse modulator modulates the pulse. The modulated UWB Gaussian pulse is then amplified by the UWB DA. Subsequently, the UWB antenna transmits the

amplified pulse wirelessly. The receiver consists of a UWB low-noise amplifier (LNA), a correlator (including a multiplier and integrator), an analog-to-digital converter (ADC), and clock generation and synchronization circuits. The UWB LNA is matched to the UWB antenna by means of a matching network. The purpose of the UWB LNA is to amplify the received pulses to a suitable level for signal processing as well as to provide enough gain so as to overcome noise in subsequent stages. The data is subsequently recovered by the correlator. The ADC is used to convert the analog demodulated signal into the digital signal. The digital baseband provides control for the clock generation, synchronization, and data processing.

Figure 3.6: Conventional Architecture of UWB wireless transceiver [52]

A similar architecture was also proposed by Jin *et al.* for wireless interconnects [14]. Although these architectures serve the purpose, they have some basic limitations which will be prominent in future high speed communications. First, a reliable technique should be built in order to synchronize the pulses used in the correlator. None of them has mentioned this technique. On the other hand, for coherent demodulation, we need to distribute the same clock among all the chips and also within the chip. This introduces another issue of clock distribution whether it is wired or wireless.

Secondly, the template pulse used for the correlator block is shown the same as the transmitted pulse. But, in general, the received pulses are the derivatives of the transmitted

34 -

pulses. Therefore, the effect of antenna on signal transmission is not considered which is clearly discussed in the later sections.

Thirdly, integrator and analog to digital converter (ADC) are used at the receiver. To facilitate the A/D conversion, the integrator should be made as lossless as possible. Also the integration response time should be short so that the ADC would have enough time to perform conversion. This means that the integrator should have a high slew rate and fast settling behavior.

#### 3.5 **Proposed Transceiver Architecture**

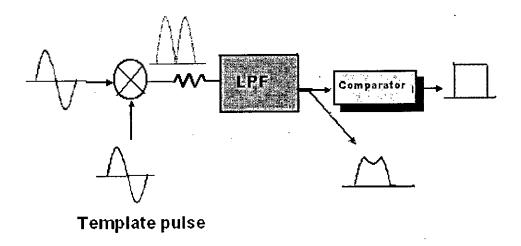

Determining the architecture of UWB transceiver for on-chip wireless interconnects application is a critical issue. Rake, transmitted-reference (TR), differential detector, and energy detector (ED) are the four most popular UWB receiver architectures investigated in the literature. To make a selection among these options, there are several aspects to be taken into account. For instance, UWB Rake receiver provides high data rate (typically up to several Gbps) but with the cost of a highly complex circuitry. On the other hand, the ED receiver architecture provides lower data rate (typically 1-100 Mbps) but with much lower complexity. One of the factors that influence the hardware complexity in a UWB transceiver is the use of either all-digital or mixed analog-digital components. Although all-digital Rake receiver provides reconfigurability, scalability, and a high data rate it is burdensome to implement an all-digital Rake receiver with the current technology. The RF components and digital hardware required to design a Rake receiver are expensive, and designing such components comes with some challenges. Therefore, low-complexity UWB system architecture such as TR transceiver using mixed analog-digital components is considered.

First to solve the last problem mentioned in the previous section, we have replaced the integrator by a low pass filter as shown in Figure 3.7. As shown in the figure, the receiver is based on the correlation between the received pulse and a template pulse. This means that a template signal is to be correlated with the received signal in order to derive