## A Simulation Based Comparative Analysis of Performance Limits of High Mobility MOSFETS of Alternate Structures

Mahmudur Rahman Siddiqui

A thesis submitted in partial fulfillment of the requirements for the degree of MASTER OF SCIENCE IN ELECTRICAL AND ELECTRONIC ENGINEERING

DEPARTMENT OF ELECTRICAL AND ELECTRONIC ENGINEERING BANGLADESH UNIVERSITY OF ENGINEERING AND TECHNOLOGY July 2011 The thesis titled "A Simulation Based Comparative Analysis of Performance Limits of High Mobility MOSFETS of Alternate Structures" submitted by Mahmudur Rahman Siddiqui, Student no: 0409062255 P, Session: April, 2009 has been accepted satisfactory in partial fulfillment of the requirement for the degree of Master of Science in Electrical and Electronic Engineering on July 27, 2011.

#### **Board of Examiners**

1.

Dr. Quazi Deen Mohd Khosru Professor Department of EEE, BUET, Dhaka - 1000 2.

Dr. Md. Saifur Rahman Professor Department of EEE, BUET, Dhaka - 1000

3.

Dr. Md. Shafiqul Islam Professor Department of EEE, BUET, Dhaka - 1000

4.

Dr. M. Rezwan Khan Professor and Vice - Chancellor United International University, Dhaka - 1209 Chairperson (Supervisor)

Member (Ex - officio)

Member

Member (External)

# Declaration

It is hereby declared that this dissertation is the result of my own work except where explicit reference is made to the work of others, and has not been submitted elsewhere for the award of any degree or diploma.

(Mahmudur Rahman Siddiqui)

To my beloved parents.

## Acknowledgment

I would like to express my sincere gratitude to my supervisor, Dr. Quazi Deen Mohd Khosru, Professor, Department of Electrical and Electronic Engineering, Bangladesh University of Engineering and Technology, for his generous help, warm encouragement and support throughout my graduate thesis. Throughout my life I will benefit from the experience and knowledge I have gained working with him.

I also wish to thank Dr. Saifur Rahman, Head and Professor, Department of Electrical and Electronic Engineering, Bangladesh University of Engineering and Technology, for providing perfect atmosphere for carrying out my thesis work.

I am also indebted to my friends and colleagues with whom I have shared many fruitful discussions.

Finally, I owe more than words can describe to my family. This work is dedicated to them.

# Contents

| D        | Declaration<br>Dedication |              |                                      |      |

|----------|---------------------------|--------------|--------------------------------------|------|

| D        |                           |              |                                      |      |

| 1        | Intr                      | Introduction |                                      |      |

|          | 1.1                       | Introd       | luction                              | . 1  |

|          | 1.2                       | Literat      | ture Review                          | . 2  |

|          | 1.3                       | Object       | tive of The Thesis                   | . 4  |

| <b>2</b> | Bal                       | listic C     | Current                              | 7    |

|          | 2.1                       | Physic       | es of the Over-the-barrier model     | . 8  |

|          | 2.2                       | Mathe        | ematical formulation and algorithm   | . 11 |

| 3        | Equ                       | ilibriu      | m Electrostatics                     | 14   |

|          | 3.1                       | Algori       | thm of the self-consistent simulator | . 14 |

|          |                           | 3.1.1        | Initialization                       | . 15 |

|          |                           | 3.1.2        | Solving Poisson's Equation           | . 17 |

|          |                           | 3.1.3        | Solving Schrödinger's Equation       | . 20 |

|          |                           | 3.1.4        | Charge Calculation                   | . 20 |

|          |                           | 3.1.5        | Updating and error check             | . 22 |

|          | 3.2                       | Poisso       | n's Equation Solver                  | . 23 |

|          | 3.3                       | Schröd       | linger's Equation Solver             | . 25 |

| 4        | Material Parameters |                                       |    |  |

|----------|---------------------|---------------------------------------|----|--|

|          | 4.1                 | Variation With Material Composition   | 29 |  |

|          | 4.2                 | Effects of Strain                     | 33 |  |

| <b>5</b> | Res                 | ults and Discussions                  | 37 |  |

|          | 5.1                 | Bulk MOSFETs                          | 38 |  |

|          | 5.2                 | Surface Channel MOSFETs               | 44 |  |

|          | 5.3                 | Double Gate MOSFETs                   | 52 |  |

|          | 5.4                 | SOI MOSFETs                           | 57 |  |

|          | 5.5                 | Comparison Among Different Structures | 61 |  |

| 6        | Con                 | clusion                               | 64 |  |

|          | 6.1                 | Result Summary                        | 64 |  |

|          | 6.2                 | Future Scope of the Work              | 65 |  |

# List of Figures

| 2.1 | Schematic diagram showing bottom of the conduction band variation with                 |    |

|-----|----------------------------------------------------------------------------------------|----|

|     | increasing drain bias under a fixed gate bias                                          | 8  |

| 2.2 | Schematic diagram shows over-the-barrier transport in an n-MOSFET under                |    |

|     | drain bias                                                                             | 9  |

| 2.3 | Schematic diagram showing bottom of the conduction band variation with                 |    |

|     | increasing gate bias under a fixed drain bias                                          | 10 |

| 2.4 | Algorithm for calculating the ballistic current for a given gate voltage               | 12 |

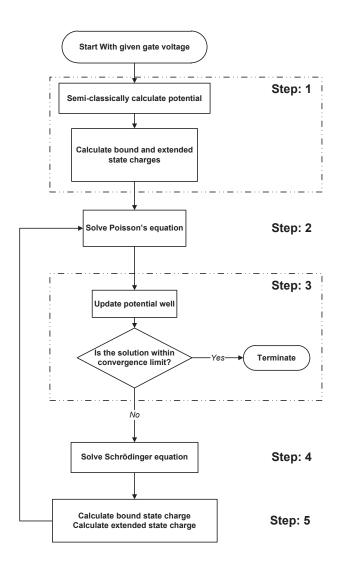

| 3.1 | Flow diagram of self-consistent simulator                                              | 16 |

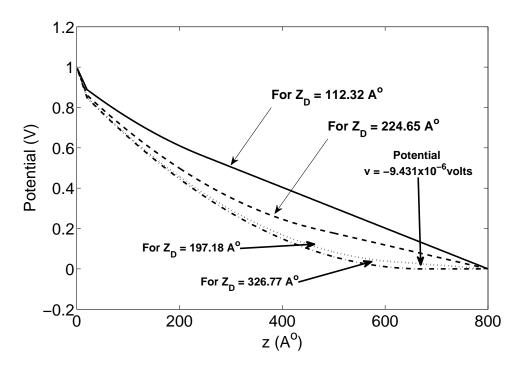

| 3.2 | Potential profile obtained from Poisson solver for different $Z_D$ for $V_{GS} = 1$ V. | 18 |

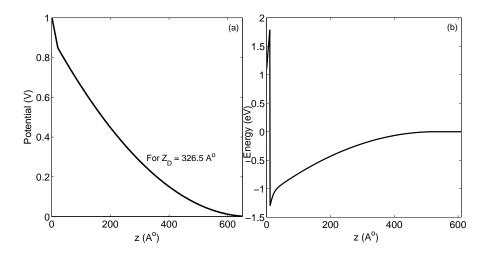

| 3.3 | (a)<br>Solution of the Poisson equation for $V_{GS} = 1$ V. (b) Calculated energy band |    |

|     | profile from the potential profile.                                                    | 18 |

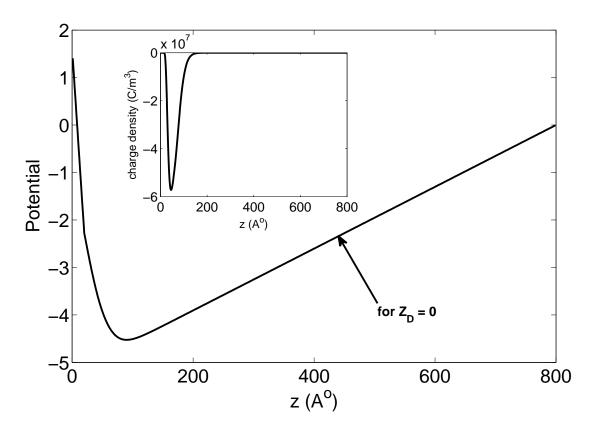

| 3.4 | Solution obtained from Poisson solver for heavily overestimated inversion              |    |

|     | charge density.                                                                        | 19 |

| 3.5 | Erroneous $ \psi_n ^2$ obtained from Schrödinger equation solver for Eigen energy      |    |

|     | of $-0.0043eV$                                                                         | 21 |

| 3.6 | Maximum error for different iterations for different updating coefficients             | 22 |

| 4.1 | Band diagram for a typical heterostructures.                                           | 31 |

| 5.1 | Schematic diagram of a bulk MOSFET used for the simulation                             | 38 |

| 5.2 | Energy band diagram portraying the conduction band minima (CBM) energy                 |    |

|     | for InAs bulk MOSFET at $V_{GS} = 2.0$ V                                               | 38 |

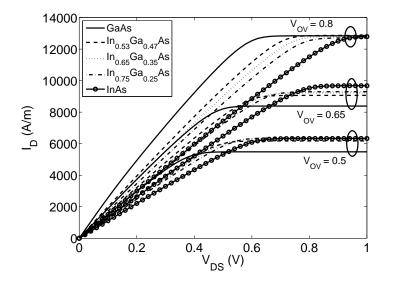

| 5.3  | Simulated ballistic drain current for bulk MOSFETs at $V_{OV} = 0.5, 0.65$ and                               |    |

|------|--------------------------------------------------------------------------------------------------------------|----|

|      | 0.8 V                                                                                                        | 40 |

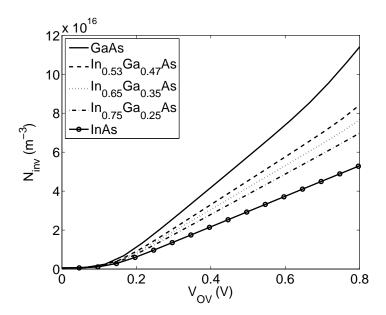

| 5.4  | Number of inversion carriers $N_{inv}$ for different bulk MOSFETs                                            | 40 |

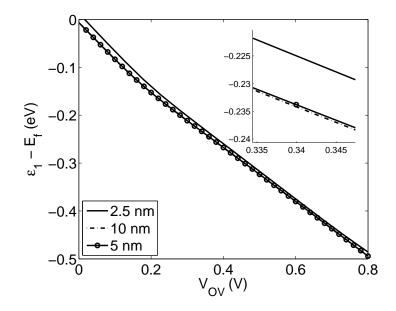

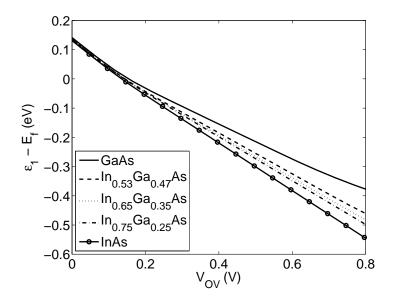

| 5.5  | Position of first Eigen state $\varepsilon_1$ with respect to the equilibrium source Fermi                   |    |

|      | level for different bulk MOSFETs                                                                             | 41 |

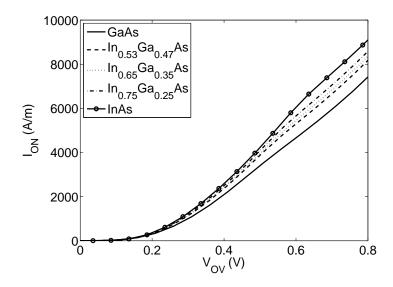

| 5.6  | Simulated ballistic on current for bulk MOSFETs at $V_{DS} = 1.5 V$                                          | 41 |

| 5.7  | Change in simulated ballistic on current for bulk MOSFETs with respect to                                    |    |

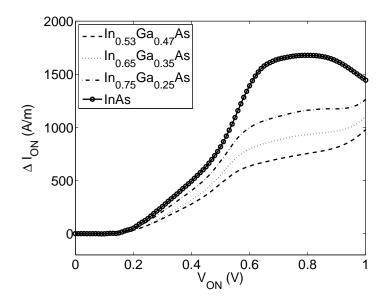

|      | GaAs bulk MOSFET at $V_{DS} = 1.5$ V                                                                         | 42 |

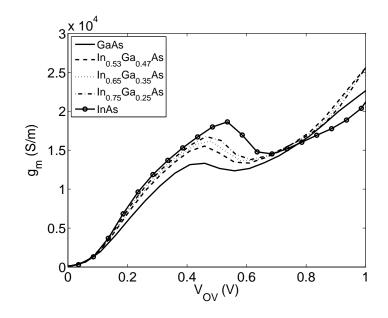

| 5.8  | Simulated transconductance for bulk MOSFETs at $V_{DS} = 1.5 \text{ V.} \dots \dots$                         | 42 |

| 5.9  | Schematic diagram of a surface channel MOSFET used for the simulation                                        | 44 |

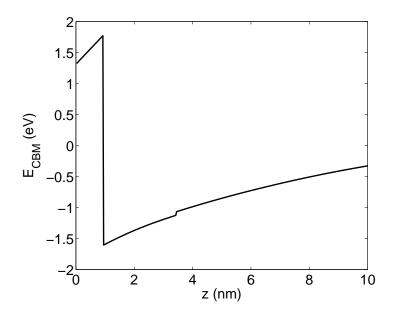

| 5.10 | Energy band diagram portraying the conduction band minima (CBM) energy                                       |    |

|      | for $In_{0.65}Ga_{0.35}As$ surface channel MOSFET at $V_{GS} = 2.0$ V                                        | 44 |

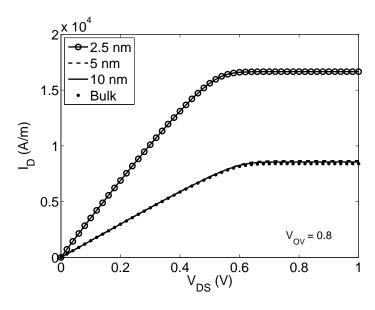

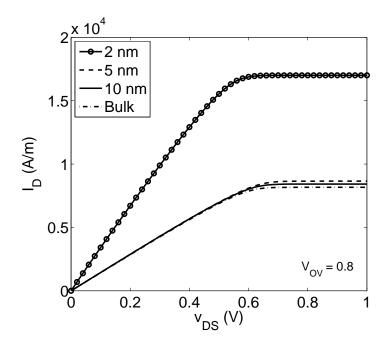

| 5.11 | Ballistic drain current for $In_{0.65}Ga_{0.35}As$ surface channel MOSFETs for $V_{OV}$                      |    |

|      | = 0.8 V for different surface layer thickness. $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$         | 45 |

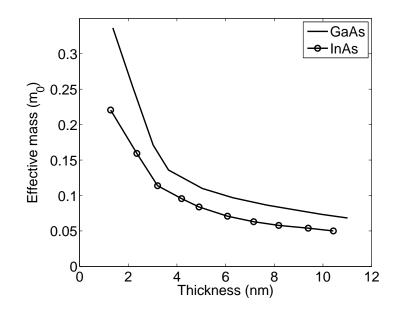

| 5.12 | Change in value of effective mass with the thickness of semiconductor layer [38].                            | 46 |

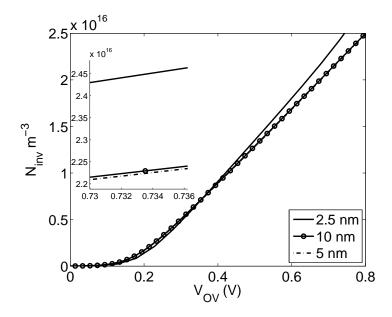

| 5.13 | Number of inversion carriers $N_{inv}$ for $In_{0.65}Ga_{0.35}As$ surface channel MOSFETs                    |    |

|      | of different channel thickness. Inset shows a magnified vision. $\ldots$                                     | 47 |

| 5.14 | Position of first Eigen state $\varepsilon_1$ with respect to the equilibrium source Fermi                   |    |

|      | level for $In_{0.65}Ga_{0.35}As$ surface channel MOSFETs of different channel thick-                         |    |

|      | ness. Inset shows a magnified vision.                                                                        | 47 |

| 5.15 | Ballistic drain current for $In_{0.75}Ga_{0.25}As$ surface channel MOSFETs for $V_{OV}$                      |    |

|      | = 0.5 V for different surface layer thickness. $\dots \dots \dots \dots \dots \dots \dots \dots \dots \dots$ | 48 |

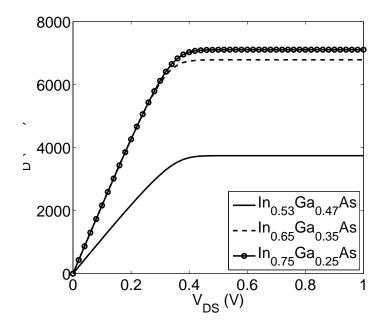

| 5.16 | Ballistic drain current for different surface channel MOSFETs for $V_{OV} = 0.5$                             |    |

|      | V and surface layer thickness of 2.5 nm.                                                                     | 49 |

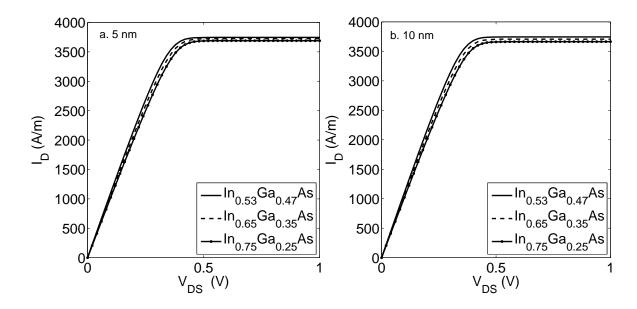

| 5.17 | Ballistic drain current for different surface channel MOSFETs for $V_{OV} = 0.5$                             |    |

|      | V and surface layer thickness a. 5 nm and b. 10 nm                                                           | 50 |

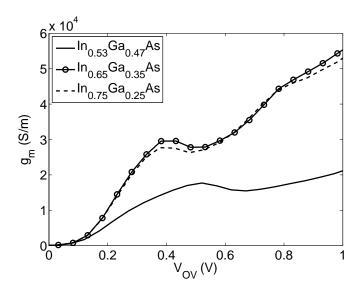

| 5.18 | Transconductance for different surface channel MOSFETs for surface layer                                     |    |

|      | thickness of 2.5 nm                                                                                          | 50 |

| 5.19 | Transconductance for different surface channel MOSFETs for surface layer                   |    |

|------|--------------------------------------------------------------------------------------------|----|

|      | thickness a. 5 nm and b. 10 nm                                                             | 51 |

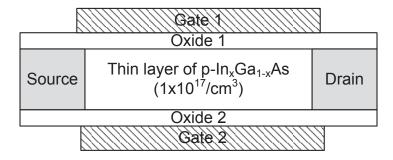

| 5.20 | Schematic diagram of a Double Gate MOSFET used for the simulation                          | 52 |

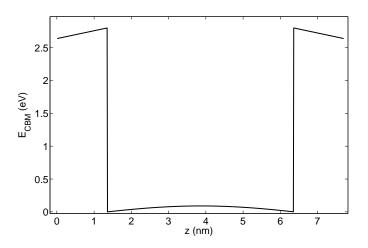

| 5.21 | Energy band diagram portraying the conduction band minima (CBM) energy                     |    |

|      | for GaAs double gate MOSFET at $V_{GS} = 2.0$ V at both gates                              | 52 |

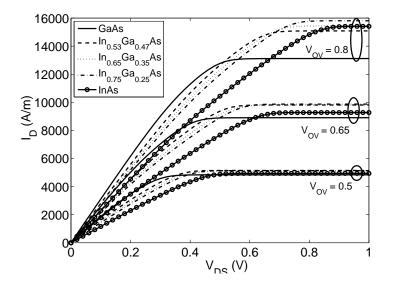

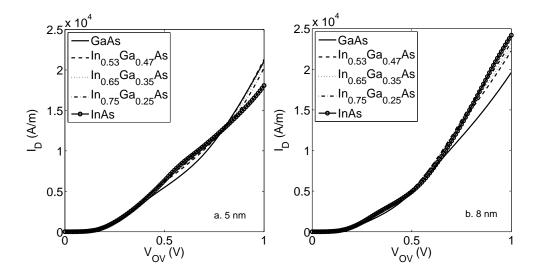

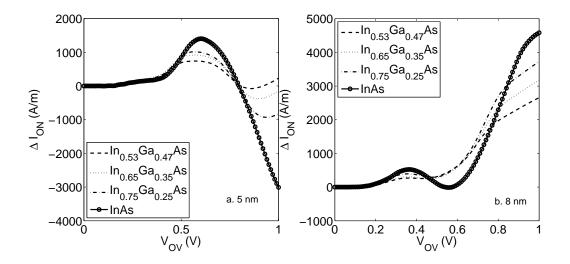

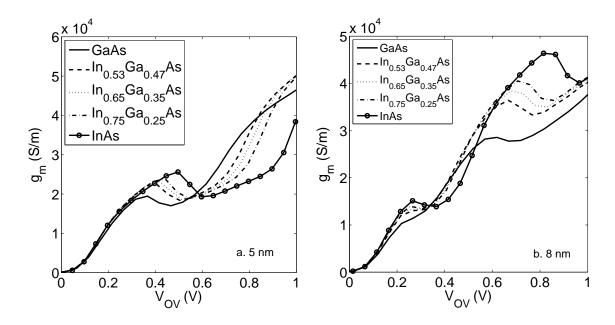

| 5.22 | Simulated ballistic drain current for different Double Gate MOSFETs with $5$               |    |

|      | nm thin channel layer for $V_{OV} = 0.5, 0.65$ and 0.8 V simulation.                       | 53 |

| 5.23 | Number of inversion carriers $N_{inv}$ for different DG MOSFETs                            | 54 |

| 5.24 | Position of first Eigen state $\varepsilon_1$ with respect to the equilibrium source Fermi |    |

|      | level for different DG MOSFETs                                                             | 54 |

| 5.25 | Simulated ballistic drain current for different Double Gate MOSFETs with 8                 |    |

|      | nm thin channel layer for $V_{OV} = 0.5, 0.65$ and 0.8 V simulation                        | 55 |

| 5.26 | Simulated ballistic on current for DG MOSFETs at $V_{DS} = 1.5$ V for a. 5 nm              |    |

|      | and b. 8 nm thin channel.                                                                  | 56 |

| 5.27 | Change in simulated ballistic on current for DG MOSFETs with respect to                    |    |

|      | GaAs DG MOSFET at $V_{DS} = 1.5$ V for a. 5 nm and b. 8 nm thin channel.                   | 56 |

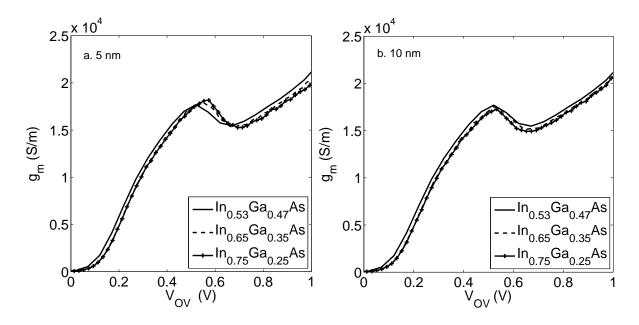

| 5.28 | Transconductance for different DG MOSFETs for channel layer thickness a.                   |    |

|      | 5 nm and b. 8 nm                                                                           | 57 |

| 5.29 | Schematic diagram of a SOI MOSFET used for the simulation                                  | 58 |

| 5.30 | Energy band diagram portraying the conduction band minima (CBM) energy                     |    |

|      | for GaAs SOI MOSFET at $V_{GS} = 2.0$ V                                                    | 58 |

| 5.31 | Simulated ballistic drain current for different SOI MOSFETs with $5.5 \text{ nm}$ thin     |    |

|      | channel layer for $V_{OV} = 0.5, 0.65$ and 0.8 V simulation                                | 59 |

| 5.32 | Number of inversion carriers $N_{inv}$ for different SOI MOSFETs                           | 60 |

| 5.33 | Position of first Eigen state $\varepsilon_1$ with respect to the equilibrium source Fermi |    |

|      | level for different SOI MOSFETs                                                            | 60 |

| 5.34 | Simulated ballistic on current for SOI MOSFETs at $V_{DS} = 1.5 \text{ V.} \dots \dots$    | 61 |

| 5.35 | Change in simulated ballistic on current for SOI MOSFETs with respect to |    |

|------|--------------------------------------------------------------------------|----|

|      | GaAs SOI MOSFET at $V_{DS} = 1.5 V$                                      | 61 |

| 5.36 | Transconductance for different SOI MOSFETs.                              | 62 |

# List of Tables

| 4.1 | Required material parameters for $In_x Ga_{1-x} As$ material system                         | 35 |

|-----|---------------------------------------------------------------------------------------------|----|

| 4.2 | Bowing parameters for $In_xGa_{1-x}As$ material system                                      | 36 |

| 5.1 | Parameters for the devices used for simulation in this study                                | 37 |

| 5.2 | Change in inversion charge ( $V_{OV} = 0.5 \text{ V}$ ), transport effective mass and drain |    |

|     | current (V <sub>OV</sub> = 0.5 V, V <sub>DS</sub> = 1.5 V) for bulk MOSFETs                 | 43 |

| 5.3 | On current $(I_{ON})$ for $V_{OV} = 0.5$ V for for different surface channel MOSFETs.       | 51 |

| 5.4 | Comparison of On current of different device structures utilizing different III-            |    |

|     | V compound semiconductors at $V_{OV} = 0.5$ V                                               | 62 |

#### Abstract

After dominating the semiconductor logic industry for decades the reign of Si is coming to an end. Aggressive scaling of MOSFETs have pushed Si towards its physical performance limits. By the end of this decade the Si MOSFETs will reach their theoretical limits. To continue the scaling of logic devices and improve performance of integrated circuits researchers must find a suitable replacement for Si. To meet the high current demands the replacement must have high carrier mobility. III-V semiconductors appear as perfect candidates for nMOS materials as they have very high electron mobility. But there are many possible III-V materials. Also the aggressive scaling of Si has given birth to some very innovative structures which solves very critical problems of nano-scale fabrication. Few of such innovative structures are Double gate MOSFETs, Semiconductor On Insulator MOSFETs, FinFETs etc. These structures might be utilized to achieve further performance enhancement of the III-V based MOSFETs. Researchers all around the world are searching for the best possible alternative using III-V materials. But fabrication of III-V materials pose some difficult challenges. One such challenge is the gate dielectric. The III-V materials do not have aa natural oxide dielectric like Si and thus growth of a dielectric with acceptable interface quality is very difficult and perfecting one process is time and resource consuming. A theoretical study of all the possible options of III-V MOSFETs will shed some light on how to choose the most optimum path of device development and ensure perfect utilization of resources and time. Thus theoretical evaluation of different performance markers of a MOSFET using III-V material has become very important. There are several performance markers for a MOSFET. The On current denotes the current driving capability of a MOSFET which in turn decides the speed of a logic circuit. The subthreshold swing decides the power loss of a MOSFET. The on/off current ratio also is a performance parameter of a MOSFET. As integrated circuits are being shrunk down the speed of a transistor needs to increase while the power consumption must decrease. Thus a systemic study of the On current of a MOSFET will provide the engineers with one basis of selection or even lead to early elimination of some device structure that will not be able to sustain performance improvement in the long run without wasting valuable time and resources. In this study a comparative picture of the transistor On current for four different structures utilizing five different III-V semiconductor is presented. The calculation has taken into account the quantum mechanical effects active at the operating device dimensions. Only the limiting current is considered here and all imperfections are ignored as the objective is to draw a comparative picture of the ultimate performances of these devices.

# Chapter 1

## Introduction

## **1.1** Introduction

Silicon (Si) has dominated the semiconductor industries for decades. The performance of Si Metal Oxide Semiconductor Field Effect Transistors (MOSFET) have been improving with the gradual scaling of the devices as per Moor's Law. With scaling of MOSFETs the oxide thickness has gone down to facilitate lower operating voltage but at the same time increasing gate leakage current. Also the channel lengths have been reduced thus increasing the drain current. But gradually this scaling is pushing Si MOSFETs to their performance limits. SiO<sub>2</sub> was the preferred gate dielectric material for Si based MOS devices as SiO<sub>2</sub> is the natural oxide of Si and the fabrication process is very simple. Also the interface quality is very good. But due to the high tunneling current at nano-scale the gate dielectrics of current Si MOSFETs are high- $\kappa$  materials. Also current carrying capability of Si is approaching the target drain current [1]. The limiting performance of Si MOSFETs is presented in [2]. The typical bulk Si MOSFET has already reached its best performance and to achieve further improvement Si MOSFETs with different structures is being considered.

Different device architectures have been explored utilizing Si to improve performance and achieve continuous scaling. Multiple gate structures stirred the most attractions. Different multiple gate structures have been investigated such as Double Gate (DG) and triple gate MOSFETs [3, 4, 5]. Other structures using Si for high performance nano- MOSFETs that have undergone extensive research are Si On Insulator (SOI) MOSFETs and FINFETs [6, 7]. These alternate structures have brought certain improvement to the characteristics of the MOSFET compared to the bulk MOSFET. But the current carrying capability of Si is limited due to the low electron mobility and also high electron effective mass. As a result, Si will not be able to provide the required drain current in future technology nodes. To meet the drain current requirements materials with higher electron mobilities are essential [8, 9].

Research community is searching for high mobility alternative materials for the future high speed logic devices to continue the predicted performance enhancement [10]. Carbon nanotubes [11], Si nanowires [12], Graphene [13], Ge [14] and III-V compound semiconductors such as InSb [15, 16] and InGaAs [17, 18] are among the materials studied as they have high electron and hole mobility. As the mobility becomes higher the maximum drain current also increase as well as the speed of the device.

III-V compound semiconductors shows good promise as the building block of the future high speed and low power nMOSFETs as they have very high electron mobility. But there are many different possibilities both in material composition and device structures. As research community improves the fabrication process of compound semiconductor devices, effects of imperfections such as interface traps and oxide traps are reducing. These impurities have to be reduced to an acceptable value before these devices are ready for industrial production. Under these conditions the performances of these devices will approach their limiting values. A comparative study of the limiting performance of these devices can shed some light on the most preferable path of evolution of compound semiconductor based devices.

### 1.2 Literature Review

III-V compound semiconductors have very high electron mobility compared to Si. As a result the drain currents in III-V material based n-MOSFETs are much higher compared to Si. From transport viewpoint, ternary InGaAs has its advantages over binary materials (GaAs, InAs etc.) as its larger inter-valley separation (0.5 eV for  $In_{0.53}Ga_{0.47}As$ ) ensures lower degradation of electron transport under high drain bias. One of the major challenges in the development of III-V semiconductor MOSFETs is the development of suitable gate

dielectrics. Ren et al. have fabricated enhancement-mode n-channel InGaAs MOSFETs for the first time using  $Ga_2O_3$  and  $Gd_2O_3$  as gate dielectrics [19]. Passlack et al. also reported enhancement mode nMOSFETs with high mobility channel material [21]. Researchers have also reported other different MOSFETs using III-V compound semiconductors that provide enhanced drain current and high speed.

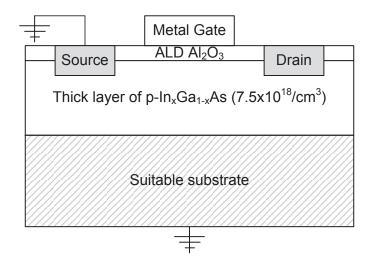

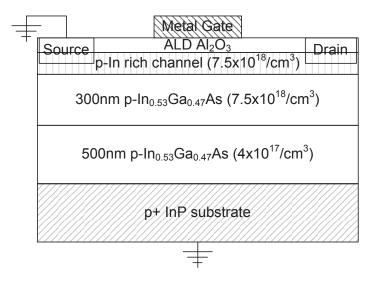

Structural change can further improve the performances of the MOSFETs. Xuan et al. have reported increased drain current in surface channel InGaAs MOSFETs with surface layer enriched with In [20]. These surface channel MOSFETs have relatively long channel. They use atomic layer deposited (ALD)  $Al_2O_3$  as gate dielectric. The interface quality of this dielectric is very poor [22]. The performance enhancement under ideal condition is still unexplored.

In case of Si based devices, the Semiconductor On Insulator structure has shown better performance. Thus similar structure also caught the interest of researchers. The III-V on insulator structure has already found important use in photonic circuits and LASERs. But their application as high performance MOS devices also shows promise [23]. Researchers are also investigating the possibilities of double gate and SOI MOSFETs using III-V materials as channel [25]. The impact of variation in material composition of the constituting III-V semiconductor is yet to be explored. Also the impact of the channel width on the drain current is still under study. The fabrication of III-V material based devices are complicated by oxide growth and appropriate substrate fabrication. As a result nano scale device fabrication is quite complicated. Thus theoretical studies are required until fabrication techniques are perfected.

The FinFET structure has achieved very good success for Si based MOSFETs. The FinFET structure is an evolved from of the double gate structure but it provides better performance than double gate MOSFETs and also provides easier fabrication options. The use of FinFET structure for III-V based nano MOSFETs might also avail the same advantages that have been observed for Si. Wu et al. have successfully fabricated III-V based FinFET [24]. The possible improvements of performance with change of material and with scaling is still under research.

Another innovative structure that has caught attention of the research community is the Quantum Well FET (QWFET). The QWFET is inspired by the High Electron Mobility Transistor structure (HEMT). These devices are still under fabrication research statge. In-GaAs and InSb based quantum well FETs have been reported for ultra-high speed and low power operation [15, 16, 17, 18]. These QWFETs show very promising results for future high performance applications.

## 1.3 Objective of The Thesis

The interest of research community in high mobility semiconductors has intensified due to the limitations of Si devices at sub 16 nm nodes [1]. Researchers are investigating the prospects of MOSFETs of different structures using compound semiconductors. As mentioned in the previous section the fabrication process of III-V based transistors are complicated due to the oxide interface quality and substrate growth. Thus significant efforts are necessary to perfect the fabrication procedure of these devices. A theoretical study of performance limits of each structure and the variation of performance with the constituting material composition will give a direction to focus all our efforts on perfecting the fabrication process of the most attractive III-V based MOS structure.

The most important performance indicators of a transistor are the On current, subthreshold swing and the on-off current ratio. The determination of On current requires the analysis of the device under strong inversion. For determination of the off current and sub-threshold swing the device has to be analyzed under low bias. For different structures different boundary set ups are required for the theoretical study. The two analysis require different algorithms. In this thesis the On current is determined and compared for different material and structure combinations. This study portrays a comparative picture of the On current of these devices and provides a basis of selection. The subthreshold characteristics will also play a role in making the most optimized selection but the sub-threshold region is outside the scope of this work.

The bulk MOSFET structure has been taken as the basis of comparison for this study. The on current of the bulk MOSFETs will be calculated for different III-V materials. Then the drain currents for DG MOSFETs, SOI MOSFETS and Surface Channel MOSFETs will be compared with the bulk device to investigate the impact of the structural change on the device performance. Also the currents will be compared among each device to understand the impact of change in material on the drain current. Here, the FinFET structure and the QWFET structure is excluded. Because the FinFET structure requires a 2D analysis environment while bulk, surface channel, DG and SOI MOSFETs can be analyzed in a 1D environment. While the QWFET structure uses very thin quantum well layer as channel. The thin layer changes the energy-momentum relationship of electron in the channel. As a result, the effective mass approximation is not valid for QWFETs. The analysis of such devices requires eight band k-p method for determination of effective mass of electrons of different energies. Thus the QWFET structure does not comply with the simulator used for the other four structures.

In this thesis, performance limits of MOSFETs of several different structures will be determined using numerical simulation. The simulation involves using the electrostatic solutions of the devices to determine the ballistic currents. Electrostatic solutions for different biases will be acquired by solving the coupled Schrdinger's and Poisson's equations self-consistently [26]. The Poisson's equation will be solved using finite difference method and the Schrdinger's equation will be solved using Hamiltonian matrix formalism [34]. The obtained electrostatic solution will be used to determine the ballistic current of the device using the over-the-barrier model [27, 28]. The equation system will be modified according to the physical structure of the device with appropriate boundary conditions. As compound semiconductors will be used for the devices under study, an appropriate determination of material parameters according to the composition of the semiconductor is required. All the

necessary material parameters will be adjusted according to the material compositions using appropriate equations.

This thesis will shade light on the impact of change in material parameters such as electron effective masses, band gap etc. on the drain current of a device. Also, we will gain insight on the impacts of changing in device structures on drain current which will provide a better understanding of the impacts of quantization and strain.

# Chapter 2 Ballistic Current

The carrier transport in long channel devices can be accurately modeled by using carrier mobility as the channel length is much larger than the scattering length or mean free path. Thus an electron or a hole experiences many collisions before reaching its destination. As a result the statistical parameter mobility gives an accurate picture of the carrier transport. But as the device is scaled down, the number of collisions experienced by carriers while moving from source to drain reduces. As a result the assumption of mobility becomes less effective. A Monte Carlo simulation done by a IBM group [29] showed that near ballistic transport is reached for Si Semiconductor On Insulator (SOI) MOSFETs for a channel length of 30 nm. III-V materials such as GaAs and InAs has much higher mean free path for electrons compared to that of Si. Thus it is expected that the electron transport in III-V MOSFETs will be ballistic in future devices where physical channel length is expected to be in the sub 15 nm range [1].

The ballistic current for different devices has been determined using the Over-the-barrier model. The Over-the-barrier model was first proposed by Kenji Natori in [27]. The same model was adopted by Asad et al. [28] with slight modification. The model used by Asad has been adopted in this work. In this chapter the Over-the-barrier model is discussed at length. The algorithm for calculating the current is also discussed.

### 2.1 Physics of the Over-the-barrier model

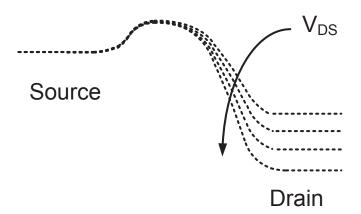

In ballistic transport no scattering occurs while the carrier travels from the source to the drain. The current is given by the net charge flow from the source to the drain that is the difference between carriers flowing from source to drain and those flowing from drain to source. The potential energy for electron from the source to the drain forms a barrier. When no voltage is applied across the the source and drain the potential at both the source and the drain is same. But due to difference in dopant types between the source and drain diffusions and the channel region, the channel potential forms the barrier. When a positive voltage is applied between the drain and the source the potential of the drain goes down. Thus the drain end of the barrier goes lower. Thus the potential rises sharply from the source end to a maximum value and from the top of the barrier the potential gradually decreases towards the drain end. This is depicted in Fig. 2.1. The picture shows that the top of the barrier energy does not change with the drain voltage.

Figure 2.1: Schematic diagram showing bottom of the conduction band variation with increasing drain bias under a fixed gate bias.

The maximum energy of the potential barrier plays a significant role in Over-the-barrier model. This point is denotes as Top-of-the-barrier. In Over-the-barrier model it is assumed that all the carriers injected from the source that have lower energy than the Top-of-thebarrier energy is reflected back towards the source by the barrier. The carriers contributing in the drain current are those that have energy equal or higher than the Top-of-the-barrier energy. Thus the carrier concentration at the position of Top-of-the-barrier is required to determine the ballistic drain current.

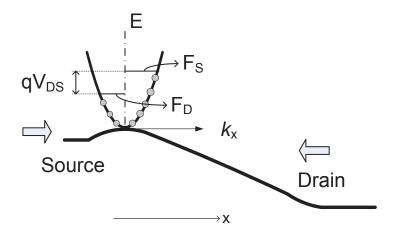

The states at the Top-of-the-barrier are filled according to the source and drain fermi levels depending on the momentum of the state. This is shown in Fig. 2.2. The positive k states are filled according to the source Fermi level and the negative k states are filled according to the drain Fermi level. When no voltage is applied across the drain and source the Fermi levels are at the same energy for both the source and the drain. As a result the carrier distribution around the k-space is symmetric. Thus the numbers of carriers traveling along the +x direction and the -x direction are equal resulting in a zero current. When a voltage is applied between the drain and the source the drain Fermi level becomes lower compared to the source Fermi level. Thus the number of carriers traveling towards the source (-x direction) becomes lower compared to the carrier traveling between the drain distribution changes. The number of carriers traveling towards the drain (+x direction).

Figure 2.2: Schematic diagram shows over-the-barrier transport in an n-MOSFET under drain bias.

As the drain voltage increase and the drain Fermi level goes down the number of -k state carriers decrease. To maintain the gate voltage the total number of inversion carriers needs to stay constant. This is an important assumption of the Over-the-barrier model. To keep the total inversion charge constant the source Fermi level has to be adjusted accordingly. Thus the carrier concentration remains the same as the equilibrium concentration but the distribution of the carriers around the k-axis changes as the drain voltage is increased. Once the drain voltage reaches a high enough value all the carriers occupy the +k states. As a result the current reaches a maximum value at this drain voltage. If the drain voltage is further increased the current stays constant.

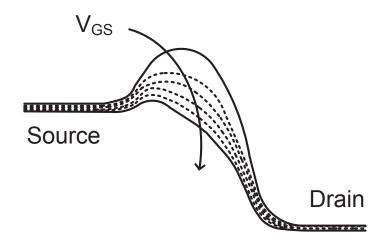

The total number of carriers is controlled by the applied gate voltage. As the gate voltage is increased the barrier height reduces that is the Top-of-the-barrier energy reduces. This is shown in Fig. 2.3. The increase in gate voltage results is an overall increase in carrier concentration. The number of carriers for a given gate voltage can be calculated by solving the equilibrium electrostatic of the device. The determination of the equilibrium electrostatics of the device is discussed in the next chapter.

Figure 2.3: Schematic diagram showing bottom of the conduction band variation with increasing gate bias under a fixed drain bias.

It is apparent from the discussion that the Top-of-the-barrier plays a significant role in the Over-the-barrier model. The electron potential energy reaches a maximum value a small distance away from the source. To determine the Eigen states at the Top-of-the-barrier the gate voltage at this position is required. The distance of the Top-of-the-barrier from the source is very small and it is neglected for this study. This assumption does not affect the ballistic current as the ballistic current only considers the carriers flowing above the Top-of-the-barrier energy. Thus the gate voltage at the source end can be used to determine the equilibrium carrier concentration for the device which is equal to  $V_{GS}$ . The current due to carriers tunneling trough the barrier is ignored in this study. This component of the current is ignored as it does not contribute to the limiting current of the device.

## 2.2 Mathematical formulation and algorithm

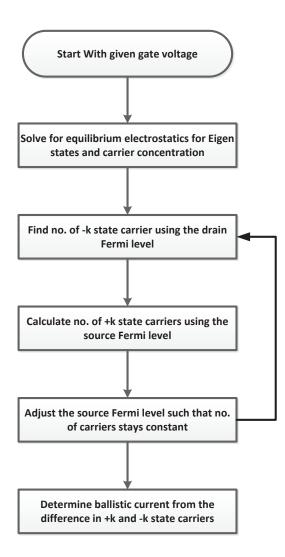

As discussed in the previous section the ballistic current is determined from the difference between carriers flowing in the +x direction and -x direction. To find the carrier distribution in the k-space, first the total carrier concentration must be determined for the equilibrium condition at the Top-of-the-barrier. This is done by solving the coupled one dimensional Poisson-Schrödinger equations for the applied  $V_{GS}$ . This solution process is discussed in the next chapter. The solution of the coupled Poisson-Schrödinger equations gives the equilibrium carrier concentration  $N_{inv}$  and the Eigen energies  $\varepsilon$ .

From the Eigen energies and the drain Fermi level for a given drain to source voltage  $V_{DS}$  the number of -k state carriers can be determined. From the total number of inversion carriers obtained from the electrostatic solution and the number of -k state carriers the position of the source Fermi can be adjusted. The adjusted source Fermi level gives the total number of carriers in the +k states. The number of carriers in *i*-th sub band  $N_{inv}^i$  can be calculated using the source and the drain Fermi levels with Eq. 2.1 and the total number of carriers can be calculated by summing  $N_{inv}^i$  for all the sub bands (Eq. 2.2)

$$N_{inv}^{i} = \left[\frac{m_{Di}}{\pi\hbar^{2}}\frac{K_{B}T}{2}\right] \left\{\ln\left(1 + exp\left(\frac{E_{F} - \varepsilon_{i}}{K_{B}T}\right)\right) + \ln\left(1 + exp\left(\frac{E_{F} - \varepsilon_{i} - qV_{DS}}{K_{B}T}\right)\right)\right\}$$

(2.1)

Figure 2.4: Algorithm for calculating the ballistic current for a given gate voltage.

$$N_{inv} = \sum N_{inv}^i \tag{2.2}$$

Here,  $m_{Di}$  is the density of states effective mass and  $E_F$  is the Fermi level at the source end and  $E_F - V_{DS}$  gives the drain Fermi level.  $E_F$  is adjusted so that the total number of carriers  $N_{inv}$  is equal to the carrier concentration obtained from the electrostatics solution. The adjusted source Fermi level and the calculated Eigen states are used in Eq. 2.3 to calculate the current for the i-th sub band. The total current is then determined by summing the sub band currents for all the sub band.

$$\frac{I_D^i}{W} = \left[ \frac{q}{\hbar^2} \sqrt{\frac{m_{Ci}}{2}} \left( \frac{K_B T}{\pi} \right)^{3/2} \right] \{F_{1/2} \left[ \frac{(E_F - \varepsilon_i)}{K_B T} \right]

-F_{1/2} \left[ \frac{(E_F - \varepsilon_i - qV_D)}{K_B T} \right] \}$$

(2.3)

# Chapter 3 Equilibrium Electrostatics

The Top-of-the-barrier plays a significant role in the Over-the-barrier model. It has been assumed in this work that the Top-of-the-barrier is at the source end of the device thus assuming an abrupt increment of the CBM at the source. This assumption plays little role in determination of the ballistic current of the device as the ballistic current is not dependent on the channel length. But this assumption will result in an under estimation of the short channel effect. This study only focuses on the limiting ballistic currents of MOSFETs with different structures and materials. Thus this assumption will not incur any significant errors in this study. The equilibrium charge concentration at the source end might be determined from the equilibrium electrostatic solution of the device. This solution can be obtained by a self-consistent simulator. In this chapter the self-consistent simulator has been discussed. The boundary conditions for this simulator has to be adjusted according to the different device structures used for study here. The required adjustments are discussed in later chapter.

### **3.1** Algorithm of the self-consistent simulator

The the electrostatic solution of a MOSFET consists of a potential well and its corresponding charge distribution for a given gate voltage. Self-consistent modeling is a tool that finds the equilibrium electrostatic solution of a MOSFET by iterative methods. The MOSFET is described by two coupled differential equations: Poisson's Equation and Schrödinger's equation. There are two different ways of acquiring the self-consistent solution depending on the starting point:

- Gate Voltage.

- Number of Inversion Carriers.

The process described here uses the gate voltage as a starting point. The following sections present the solution process for a bulk nMOS in inversion region. Only the inversion region is discussed here as this objective of this study includes the determination of the On current of MOSFETs.

A flow diagram given in figure 3.1 shows the basic steps of a self-consistent model. The model starts with a given gate voltage which is used to calculate the potential profile inside the semiconductor with the aid of an assumed charge density. This assumption might be obtained from the solution for a lower gate voltage or it might also be guessed as the ionized impurity concentration. For the later assumption the simulator will take higher number of iterations to converge. The potential profile obtained is then converted into an energy band diagram by using the physical parameters of the device. This energy band profile is used in the Schrödinger equation to obtain Eigen functions. These Eigen functions and corresponding Eigen energies are used to calculate the charge density. The charge density obtained is used in place of the assumed charge density of the first iteration to obtain a new potential profile and the process continues until two successive iterations produce results within the tolerance limit. The whole process in explained elaborately in the following sections with the aid of necessary figures. A typical bulk Si nMOS with 1nm thick  $SiO_2$  gate and an uniform  $10^{18} \ cm^{-3}$  impurity concentration is used for this discussion. The algorithm stays the same for different materials and structures.

#### 3.1.1 Initialization

Initialization provides the data required for solving the Poisson's equation for the  $1_{st}$  iteration. Poisson's equation requires two parameters: gate voltage and distribution of charge

Figure 3.1: Flow diagram of self-consistent simulator

density with space. The process starts with a given gate voltage. The overall charge density can be divided into two parts: Depletion Charge and Inversion Charge. A zero inversion charge density is assumed for the  $1_{st}$  iteration or the inversion charge determined by the self-consistent simulator for a closer gate voltage. Any initial condition should be alright theoretically. But an absurd initial condition might lead to slow convergence or even cause failure to converge. So it is advised to use the inversion charge profile obtained for a lower gate voltage as an initial condition. The gate voltage and the inversion charge density profile are used to solve the Poisson solver.

#### 3.1.2 Solving Poisson's Equation

To solve Poisson's equation distribution of the total charge density is required which consists of both inversion charge and depletion charge. The mathematical process is discussed in Section 3.2. The depletion charge changes with the gate voltage for lower gate voltages. When the device reaches deep inversion the depletion charge distribution becomes constant. To obtain the appropriate depletion charge for a given inversion charge, a depletion width is assumed and total charge density is calculated as follows

$$\rho_{dep}(z) = -e(N_A - N_D); \qquad 0 < z < z_d$$

= 0;  $z > z_d$  (3.1)

where  $z_d$  is the depletion layer thickness.

$$\rho_{total}(z) = \rho_{dep}(z) + \rho_{inv}(z) \tag{3.2}$$

Using the total distribution of charge density the Poisson's equation is solved to obtain a potential profile. The objective is to find the maximum depletion width for which the potential does not go below the bulk potential for an nMOS for a given inversion charge density. That is the potential should not have any local maxima or minima inside the semiconductor. Depletion width is varied until an acceptable solution is obtained. Different potential profiles for different  $Z_D$  is shown in Fig. 3.2. Through iterative method the appropriate  $Z_D$  is determined which gives the solution of the Poisson's equation.

From the solution of the Poisson equation we obtain a depletion width and a potential profile. Depletion charge can be calculated by multiplying the depletion width with impurity concentration and electrons charge. Figure 3.3 shows the potential profile and the corresponding depletion width obtained from the solution of the Poisson equation for a gate voltage of 1 volt. The potential profile is used to determine the energy band profile for the device. The energy band profile is calculated by multiplying the potential profile with the charge of electron and then offsetting the oxide and semiconductor part of the profile by the

Figure 3.2: Potential profile obtained from Poisson solver for different  $Z_D$  for  $V_{GS} = 1$  V.

Figure 3.3: (a)Solution of the Poisson equation for  $V_{GS} = 1$  V. (b) Calculated energy band profile from the potential profile.

appropriate differences in their work functions (Fig. 3.3). This energy band profile is used in the Schrödinger's equation solver. The solution obtained from the Poisson solver might require some post processing under some specific circumstances. It is evident that if inversion charge is underestimated then depletion width is overestimated and vice versa. So, if the self-consistent loop is initialized with a low assumption for inversion charge the first iteration will result in a high overestimation of depletion width. A higher depletion width means a broader potential well. The resulting inversion charge density becomes highly overestimated due to the broad potential well. For the second iteration, the inversion charge is heavily overestimated. Hence even a zero depletion width provides a unacceptable solution. The situation is portrayed in figure 3.4.

Figure 3.4: Solution obtained from Poisson solver for heavily overestimated inversion charge density.

The potential profile obtained here is not physically possible. This situation is very common if an iteration is initialized with zero inversion charge density for a gate voltage high enough to push the device into deep inversion. For such situations the negative values of the potential profile are replaced by zeros.

#### 3.1.3 Solving Schrödinger's Equation

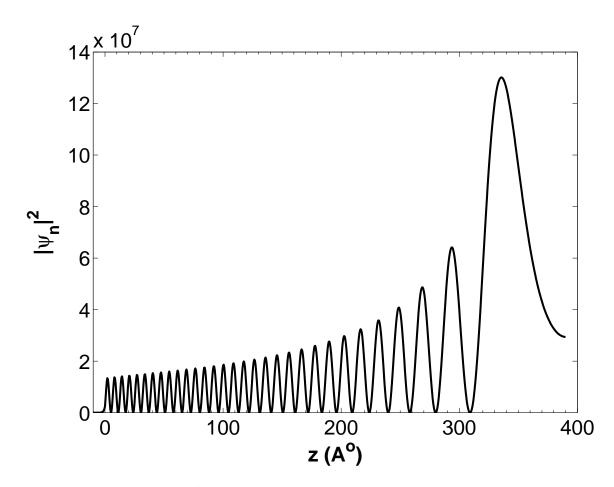

The Schrödinger equation is solved following the precess discussed in Section 3.3. The solution of the Schrödinger equation provides us with some Eigen energies and corresponding normalized wave function  $(|\Psi|_n^2)$  or Eigen functions. These Eigen energies and Eigen functions are used to calculate the inversion charge density. There is a small probability of obtaining an erroneous solution from the Schrödinger solver. The matrix based solver that is used in this study has an accuracy that is dependent upon the step size of the mesh. As the frequency of the wave function becomes higher the accuracy of the solver goes down. That is the solver can calculate lower Eigen energies and their corresponding Eigen functions accurately but the higher Eigen energies will require a finer mesh which compromises computational efficiency. At energies very near to the bulk energy level an Eigen energy might reside which is difficult to obtain accurately while keeping acceptable computational efficiency. The normalized wave function obtained for these Eigen energies does not decay down to a zero value in the bulk due to the error introduced by the computational inaccuracy. Such a wave function is shown in figure 3.5.

The impact of this error is negligible while calculating for an inverting gate voltage as the contribution of the first few Eigen energies heavily dominate the proceedings and the higher Eigen energy being further away from the Fermi level contributes little to the inversion charge. But this erroneous wave function can have a profound impact in the accumulation region. These erroneous states are neglected completely.

#### 3.1.4 Charge Calculation

The inversion charge density is calculated using the Eigen energies and their corresponding normalized wave functions with the aid of the following formulas.

Figure 3.5: Erroneous  $|\psi_n|^2$  obtained from Schrödinger equation solver for Eigen energy of -0.0043 eV

$$N_{ij} = \frac{n_{vi}m_{di}kT}{\pi\hbar^2} \ln\left[1 + exp\left(\frac{E_F - E_{ij}}{kT}\right)\right]$$

(3.3)

Here  $N_{ij}$  denotes carrier concentration in the *j*th subband in the *i*th valley,  $n_{vi}$  is the valley degeneracy,  $m_{di}$  is the density of states effective mass of the *i*th valley,  $E_F$  is the fermi energy level and  $E_{ij}$  is the Eigen energy.

$$\rho_{inv}(z) = -e \sum_{ij} N_{ij} |\psi_{ij}(z)|^2$$

(3.4)

here  $\rho_{inv}$  is the inversion charge density.

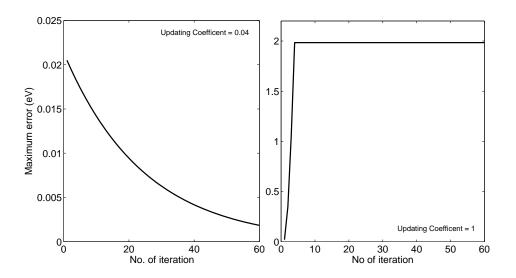

#### 3.1.5 Updating and error check

At higher gate biases when deep inversion is achieved, the inversion charge calculated from the Eigen energies and the Eigen functions become very sensitive to small changes in the potential profile. As a result the self-consistent simulator becomes divergent if the potential profile is changed significantly after each iterations. This gives rise to the necessity of containing the change in the potential profile to ensure small change in every iteration. To contain the change in inversion charge the potential profile is controlled by updating the previous potential profile rather using the newly obtained potential profile. The update equation is given below where u denotes potential.

$$u_{new} = u_{old} + update \ coeff \times (Poisson \ solution \ - \ u_{old}) \tag{3.5}$$

The value of the update coefficient might vary from 0.06 to 0.03 depending on the impurity concentration.

Figure 3.6: Maximum error for different iterations for different updating coefficients

Figure 3.6 shows maximum difference between two consecutive energy band profile in electron volts where gate voltage is 2 volts for two self-consistent solutions one adapting an update coefficient and another without any updating. It is obvious that use of appropriate update coefficient is essential for successful and fast convergence. The newly obtained inversion charge profile is compared with the previous one. If the difference lies within the tolerance limit then the self-consistent solution is obtained and the loop is terminated.

#### 3.2 Poisson's Equation Solver

In this section we discuss discuss the use of finite difference method to solve Poisson equation. In this method the derivatives in the partial differential equation are approximated by combinations linear equations by using the discrete differentiation methods. There are several discrete differentiation processes.

Three discrete differentiation forms are commonly considered for approximation of first order derivatives.

#### Forward difference

$$\left(\frac{\partial u}{\partial x}\right)_i \approx \frac{u_{i+1} - u_i}{\Delta x} \tag{3.6}$$

**Backward difference**

$$\left(\frac{\partial u}{\partial x}\right)_i \approx \frac{u_i - u_{i-1}}{\Delta x} \tag{3.7}$$

#### Central difference

$$\left(\frac{\partial u}{\partial x}\right)_i \approx \frac{u_{i+1} - u_{i-1}}{2\Delta x} \tag{3.8}$$

A second order derivative can be approximated with the aid of first order derivatives. Using the discrete approximations discussed before a second order derivative may be approximated by the following equation.

$$\left(\frac{\partial^2 u}{\partial x^2}\right)_i \approx \frac{u_{i+1} - 2u_i + u_{i-1}}{(\Delta x)^2} \tag{3.9}$$

Generalized Poisson's equation can be written as

$$\frac{\partial^2 V(z)}{\partial z^2} = f \tag{3.10}$$

where,

$$f = -\rho_{inv}(z)/\epsilon_0 \epsilon_{ox}$$

,  $-t_{ox} < z < 0$  (3.11)

$$= -(\rho_{inv}(z) + \rho_{dep}(z))/\epsilon_0\epsilon_{si}, \qquad z > 0$$

(3.12)

Now, the value of the voltage at the metal end of the gate is the applied voltage  $V_GS$ . This is used as a boundary condition for solving the Poisson equation. The other boundary is taken at the other physical end of the device. This boundary is deep in the semiconductor body for a bulk MOSFET or the second gate metal for a double gate MOSFET. Here, we are using a bulk MOSFET. Thus the potential will be zero deep inside the bulk.

$$V_1 = V_G S \tag{3.13}$$

and

$$V_{end} = 0 \tag{3.14}$$

Open boundary condition at material interfaces are necessary to relate their Electric fields. For a bulk MOSFET with the oxide field  $F_{ox}$  and semiconductor field should be related as shown in the equation below. This relationship is held at every material boundaries.

$$\epsilon_{ox} F_{ox} = \epsilon_{semiconductor} F_s \tag{3.15}$$

So, using the discrete differentiation technique the Poisson equation can be approximated as the set of following linear equations.

$$i = 1 V_1 = V_g$$

$$V_1 - 2V_2 + V_2$$

$$i = 2 \qquad \qquad \frac{\sqrt{1 - 2\sqrt{2} + \sqrt{3}}}{(\Delta z)^2} \qquad \qquad = f_2$$

$$i = 3$$

$\frac{V_2 - 2V_3 + V_4}{(\Delta z)^2} = f_3$

$$At \ SiO_2/Si \ interface \qquad -\epsilon_{ox}V_{i-1} + (\epsilon_{ox} + \epsilon_{si})V_i - \epsilon_{si}V_{i+1} \qquad = 0$$

$$i = N - 1$$

$i = N$

$i = N$

$\frac{V_{N-2} - 2V_{N-1} + V_N}{(\Delta z)^2}$

$V_N$

$= f_{N-1}$

$= 0$

Solving this set of linear equations we can obtain the solution of the poisson's equation for the MOSFET.

#### 3.3 Schrödinger's Equation Solver

The Schrödinger equation can be solved utilizing two different methods which are

- Retarded Green's function formalism using transmission line analogy.

- Hamiltonian matrix formalism

. .

A detailed comparison of these two methods has been presented in [33]. The model used in this study uses the Hamiltonian Matrix formalism. This method has been chosen because of the faster execution of matrix based algorithm while maintaining the required level of accuracy with the use of larger matrices. The Hamiltonian Matrix formation is discussed at length here for a bulk MOSFET. The Hamiltonian matrix is the energy matrix for any system. The energy band levels around the conduction band minimum can be described by [34]

$$h(\vec{k}) = E_c + \frac{\hbar^2 k^2}{2m^*}$$

(3.16)

where  $E_c$  is the conduction band minimum energy and  $m^*$  is the effective mass. A differential equation can be formed that will yield energy eigenvalues replacing  $\vec{k}$  with  $-i\vec{\nabla}$  in the Eq. 3.16.

$$\left[E_c - \frac{\hbar^2}{2m^*}\nabla^2\right]\psi(\vec{r}) = E\psi(\vec{r})$$

(3.17)

For one dimension Eq. 3.17 can be written as

$$\left[E_c - \frac{\hbar^2}{2m^*} \frac{d^2}{dx^2}\right] \psi(x) = E\psi(x)$$

(3.18)

Finite difference method is used to convert Eq. 3.18 into a Hamiltonian matrix. This conversion is done by choosing a discrete lattice. We can represent the wave function  $\psi(x)$  by a column vector("T" denotes transpose)

$$\{\psi(x_1) \ \psi(x_2) \ \dots \ \psi(x_{i-1}) \ \psi(x_i) \ \psi(x_{i+1}) \ \dots \ \dots\}^T$$

Then the matrix representing the hamiltonian operator  $(H_{op})$  is obtained.

$$H_{op} \equiv E_c - \frac{\hbar^2}{2m^*} \frac{d^2}{dx^2}$$

Using finite difference method it can be written

$$\left(\frac{d^2}{dx^2}\psi\right)_{x=x_i} = 2\frac{(x_i - x_{i-1})\psi_{i+1} - (x_{i+1} - x_{i-1})\psi_i + (x_{i+1} - x_i)\psi_{i-1}}{(x_{i+1} - x_{i-1})(x_{i+1} - x_i)(x_i - x_{i-1})}$$

For uniform mesh size of  $\triangle x = a$  which reduces to

$$\left(\frac{d^2}{dx^2}\psi\right)_{x=x_i} = \frac{\psi_{i+1} - 2\psi_i + \psi_{i-1}}{a^2}$$

(3.19)

and

$$(E_c\psi)_{x=x_i} \to E_c(x_i)\psi_i \tag{3.20}$$

If we assume

$$t_o = \frac{\hbar}{2m^*a^2}$$

then

$$[H_{op}\psi]_{x=x_i} = -t_o\psi_{i-1} + (E_c(x_i) + 2t_o)\psi_i - t_o\psi_{i+1}$$

(3.21)

and the matrix,

$$[H_{op}] = \begin{bmatrix} E_c(x_1) + 2t_o & -t_o & 0 & 0 & 0 & 0 \\ -t_o & E_c(x_2) + 2t_o & -t_o & 0 & 0 & 0 \\ \vdots & \vdots & \vdots & \vdots & \vdots & \vdots & \vdots \\ \cdots & \cdots & \cdots & \cdots & \cdots & \cdots & \cdots \\ \vdots & \vdots & \vdots & \vdots & \vdots & \vdots & \vdots \\ 0 & 0 & 0 & -t_o & E_c(x_{n-1}) + 2t_o & -t_o \\ 0 & 0 & 0 & 0 & -t_o & E_c(x_n) + 2t_o \end{bmatrix}$$

(3.22)

For spatially varying effective mass the correct/modified version of Eq. 3.18, 3.21 and 3.22 are Eq. 3.23,3.24 and 3.25 respectively.

$$\left[E_c - \frac{\hbar^2}{2} \frac{d}{dx} \left(\frac{1}{m^*(x)} \frac{d}{dx}\right)\right] \psi(x) = E\psi(x)$$

(3.23)

$$[H_{op}\psi]_{x=x_i} = -t_{i-1}\psi_{i-1} + (E_c(x_i) + t_{i-1} + t_i)\psi_i - t_i\psi_{i+1}$$

(3.24)

where

$$t_{i} = \frac{\hbar^{2}}{2m_{i}^{*}}$$

$$[H_{op}] = \begin{bmatrix} E_{c}(x_{1}) + 2t_{1} & -t_{1} & 0 & 0 & 0 & 0 \\ -t_{1} & E_{c}(x_{2}) + t_{1} + t_{2} & -t_{2} & 0 & 0 & 0 \\ \vdots & \vdots & \vdots & \vdots & \vdots & \vdots & \vdots \\ \cdots & \cdots & \cdots & \cdots & \cdots & \cdots \\ \vdots & \vdots & \vdots & \vdots & \vdots & \vdots & \vdots \\ 0 & 0 & 0 & -t_{n-2} & E_{c}(x_{n-1}) + t_{n-1} + t_{n-2} & -t_{n-1} \\ 0 & 0 & 0 & 0 & -t_{n-1} & E_{c}(x_{n}) + 2t_{n-1} \end{bmatrix}$$

$$(3.25)$$

To solve the Schrödinger's equation the following steps should be followed to calculate Eigen energies and normalized wave function.

- 1. The potential well was approximated with multi step function.

- 2. The hamiltonian matrix is formed using Eq. 3.22 or 3.25

- 3. Eigenvalues and eigenvectors are determined of that matrix.

- 4. Eigen energies are calculated from eigenvalues.

- 5. Eigenvector are normalized to determine normalized wave function.

# Chapter 4

## **Material Parameters**

The devices under study here have III-V compound semiconductor materials. The material parameters vary with composition of the material. The parameters also vary under the effect of strain. In this chapter we discuss the variation of material parameters with composition and strain.

#### 4.1 Variation With Material Composition

The variation of different material parameters such as electron effective, hole effective mass, band gap etc. with material composition have to be calculated appropriately. All the material parameters associated with this studies is discussed in this section. The exact calculation of a variation of a material parameter with its composition is impossible due to the large uncertainty. Thus the value of the required parameter in calculated using interpolation technique. Thus the parameter for the new material is determined from the corresponding known values of the parameter for the end semiconductors. For this study the ternary material  $\ln_x Ga_{1-x}As$  has been used. The required material parameters of  $\ln_x Ga_{1-x}As$  can be calculated from the known values of InAs and GaAs. If  $A_x B_{1-x}C$  is the ternary material of interest and the material parameters of binary material AC and BC are known then we can calculate the value for  $A_x B_{1-x}C$  using Equation 4.1.

$$T_{ABC(x)} = xB_{AC} + (1-x)B_{BC} - x(1-x)W_{ABC}$$

(4.1)

Here, T is the parameter for the ternary material while B is the same parameter for binary materials. W is the bowing parameters. The value of W changes for different material parameters. All the parameters of interest have been calculated using Equation 4.1.

If the bowing parameter W becomes zero then this interpolation becomes linear. According to Vegrad's Law the bowing parameter for calculating lattice constant is zero. Thus calculation of lattice constant is necessarily a linear interpolation between the lattice constants of InAs and GaAs. The lattice constants of InAs and GaAs are given in Table 4.1. Several parameters can be calculated using the linear interpolation that is assuming their bowing parameters as zero. These parameters are density of states effective masses, quantization effective masses and transport effective masses for both electrons and holes, elastic stiffness constants C11 and C12, deformation potential b,  $a_v$  and  $a_c$ , relative permittivity, Luttinger parameter. All these parameters for the material  $In_xGa_{1-x}As$  system have been listed in in Table 4.1.

One of the device parameters that depends on a bowing parameter is band gap. Also, parameters related to spin orbit splitting and electron affinity also depend on a bowing parameters. These values of these parameters along with their bowing parameters are also mentioned in Table 4.1 and 4.2.

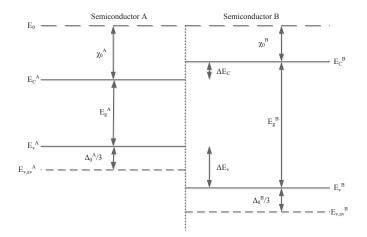

To describe the physics of the device with different compound semiconducting material the band alignment of the layers of semiconductors have to be calculated according to the material composition and the resulting strain from mismatch between two different semiconductor materials if any. Fig. 4.1 shows a typical heterogenous band structure.

Here the effects of material composition on band alignment is discussed. The effects of strain is discussed in the next section. There are two band offsets associated with band alignment: the conduction band offset and the valance band offset. Both these offset changes with the material composition. The model-solid theory is employed here to estimate the band edge offsets of cubic semiconductors [31]. The model lines up the band structure of different semiconductors by introducing an average valence band energy  $E_{v,av}^0$ .  $E_{v,av}^0$  can be expressed with Equation 4.2 for unstrained semiconductors.

Figure 4.1: Band diagram for a typical heterostructures.

$$E_{v,av}^{0} = E_{v}^{0} - \frac{\Delta_{0}}{3} \tag{4.2}$$

Here  $E_v^0$  denotes valence band edge and  $\Delta_0$  denotes spin orbit splitting. Values for  $E_{v,av}^0$  are given in Table 4.1. These values are obtained by calculating the average electrostatic potential for model-solids of neutral atoms and are taken from [32]. The conduction band edge can be calculated from these data as shown in Equation 4.3.

$$E_c^0 = E_v^0 + E_g = E_{v,av}^0 + \frac{\Delta_0}{3} + E_g$$

(4.3)

Here,  $E_c^0$  denotes conduction band edge and  $E_g$  denotes the band gap of the material. For interpolating  $E_{v,av}^0$  for a ternary material  $A_x B_{1-x}C$  it has to be taken into account that the lattice parameter  $a_{ABC}$  is different form the binary lattice constants  $a_{AC}$  and  $a_{BC}$ . The bowing parameter for  $E_{v,av}^0$  can be calculated from the binary deformation potential  $a_v$  and binary lattice parameters using Equation 4.4

$$C_{ABC}(E_{v,av}^{0}) = 3[a_v(AC) - a_v(BC)]\frac{a_{AC} - a_{BC}}{a_{ABC}}$$

(4.4)

The binary deformation potential  $a_v$  is also dependent on the composition but as mentioned before the bowing parameter for it is zero. Under strain, the average energy  $E_{v,av}$  is shifted from its unstrained value  $E_{v,av}^0$  as shown in Equation 4.5

$$E_{v,av} = E_{v,av}^{0} - P_{\epsilon} = E_{v}^{0} - \frac{\Delta_{0}}{3} - P_{\epsilon}$$

(4.5)

Here,  $P_{\epsilon}$  is an energy associated with strain which is required to include strain in the two band Hamiltonian matrix. More on  $P_{\epsilon}$  has been discussed in the following section.

By comparison with fully self-consistent interface calculations, the error bar on band offsets determined from the model-solid theory extends up to 0.1 eV [36]. Many other theoretical and experimental investigations of heterostructure band offsets have been published, leading to a list of typical values for the valence band edge  $E_v^0$  in unstrained bulk material (4.1). The absolute energy scale is arbitrary, here the InSb valence band edge is used as origin. Known bowing parameters are listed in Table 4.2. The implementation of the effects of strain are discussed in the next section.

An alternate way to determine the band offset is to take vacuum level as the reference and using the electron affinity ( $\chi_0$ ) as shown in Equation 4.6.

$$E_c^0 = E_0 - \chi_0 \tag{4.6}$$

Bowing parameters for the affinity can be calculated by weighting the band gap bowing parameter  $C(E_g)$  with the average conduction band offset ratio  $\Delta E_c/\Delta E_g$  of the binary endpoint materials for the same symmetry point (Equation 4.7).

$$C(\chi_0) = -C(E_g) \frac{\Delta E_c}{\Delta E_g} \tag{4.7}$$

This study uses the valence band edge method for band edge alignment.

#### 4.2 Effects of Strain

The fabrication of materials with different lattice parameters on each other results in a strained layer at the top of the device. The strain changes material parameters like electron affinity, transport effective mass etc. The variation of parameters with strain is discussed here. Strain deforms the crystal lattice. However, it is assumed to be still periodic such that Bloch functions are still applicable. Since the elementary crystal cell is deformed, potential and Bloch lattice functions now have a period equal to the strained elementary cell. The relative change of the lattice period gives the strain.

$$\epsilon_{ij} = \frac{\Delta a_i}{a_j} \tag{4.8}$$

This strain can be different in different directions. With small strain, the strained Hamiltonian can be given as perturbation of the unstrained Hamiltonian [37]. Only bi-axial strain is considered in this work. For mismatched super lattice grown along the z-axis the strain components can be calculated as

$$\epsilon_{xx} = \epsilon_{yy} \neq \epsilon zz$$

$$\epsilon_{ij} = 0 fori \neq j$$

(4.9)

The two strain components are related by the elastic stiffness coefficient  $C_{11}$  and  $C_{12}$  as sown in equation below:

$$\epsilon_{zz} = -2 \frac{C_{12}}{C_{11}} \epsilon_{xx}$$

$$\epsilon_{xx} = \epsilon_{yy} = \frac{a_{st} - a_0}{a_0}$$

(4.10)

where  $a_{st}$  and  $a_0$  are the lattice constant of the strained and unstrained crystal, respectively. For compressive strain,  $a_{st} < a_0$ ,  $\epsilon_{xx} = \epsilon_{yy} < 0$ , and  $\epsilon_{zz} > 0$ .

Additions of  $P_{\epsilon}$  and  $Q_{\epsilon}$  are required to the diagonal elements of the two-band Hamiltonian matrix to incorporate the effects of crystal deformations on the Bloch functions.  $P_{\epsilon}$  and  $Q_{\epsilon}$ is given below.

$$P_{\epsilon} = -a_v(\epsilon_{xx} + \epsilon_{yy} + \epsilon_{zz})$$

$$Q_{\epsilon} = -\frac{b}{2}(\epsilon_{xx} + \epsilon_{yy} - 2\epsilon_{zz})$$

(4.11)

As a result of this modification, the strain is found to cause the following shifts of the band edges at the  $\Lambda$  point. According to the two band model which assumes that the interaction with the spin orbit can be neglected the band edge shifts can be expressed as:

$$E_{hh}(0) = E_{hh}^{0} = E_{v}^{0} - P_{\epsilon} - Q_{\epsilon}$$

$$E_{lh}(0) = E_{lh}^{0} = E_{v}^{0} - P_{\epsilon} + Q_{\epsilon}$$

(4.12)

The conduction band edge is given by

$$E_{c}(0) = E_{c}^{0} = E_{v}^{0} + E_{g} + a_{c}(\epsilon_{xx} + \epsilon_{yy} + \epsilon_{zz})$$

(4.13)

The factors  $a_c$  and  $a_v$  are hydrostatic deformation potentials; b is the shear deformation potential. The separation of the total hydrostatic deformation potential in conduction  $(a_c)$ and valence band  $(a_v)$  contributions is important at heterointerfaces.

Due to the deformation of crystal structures under strain, the E-k relationship changes. Thus the effective mass changes with strain. To calculate the change is effective mass the two band model can be used which assumes that there are no coupling with the spin orbit band or the three band model which includes the spin orbit but neglects the effects of the coupling with conduction band. According to the two band model the bands along the z-axis remains parabolic thus the effective mass stays the same along the z direction. But the x-y E-k relationship deforms from the parabolic band thus resulting in a k dependent effective mass. Near the  $\Lambda$  point which is the point of interest in simulation studies the transverse effective masses can be expressed as:

$$m^t_{hh} = \frac{m_0}{\gamma_1 + \gamma_2}$$

$$m_{lh}^t = \frac{m_0}{\gamma_1 - \gamma_2} \tag{4.14}$$

Here,  $\gamma_1$  and  $\gamma_2$  are Luttinger parameters for cubic solids. The two band model is discussed here. A more detailed discussion along with the three band model can be found in [32]. All the related data for determination of change in material parameters due the composition and strain is given in Table 4.1 and 4.2.

| Parameter               | InAs           | GaAs           |

|-------------------------|----------------|----------------|

| $E_g$                   | 0.36  eV       | 1.42  eV       |

| $m_c^{\Gamma}$          | $0.023m_0$     | $0.063m_0$     |

| $m_c^X(t/l)$            | $0.16/1.13m_0$ | $0.23/1.3m_0$  |

| $m_c^L(t/l)$            | $0.05/0.64m_0$ | $0.075/1.9m_0$ |

| $m_{hh}$                | $0.57m_{0}$    | $0.50m_{0}$    |

| $m_{lh}$                | $0.025m_0$     | $0.076m_0$     |

| $m_{so}$                | $0.14m_0$      | $0.14m_0$      |

| $\gamma_1$              | 20.0           | 6.98           |

| $\gamma_2$              | 8.5            | 2.06           |

| $\gamma_3$              | 9.2            | 2.93           |

| $a_0$                   | 6.0583         | 5.65325        |

| C <sub>11</sub>         | 832.9          | 1221           |

| C <sub>12</sub>         | 452.6          | 566            |

| b                       | -1.8           | -2.0           |

| $\mathbf{a}_v$          | 1.0            | 1.16           |

| $a_c$                   | -5.08          | -7.17          |

| $\mathrm{E}_v^0$        | -0.59          | -0.8           |

| $\Delta_0$              | 0.39           | 0.341          |

| $\mathrm{E}_{v,av}^{0}$ | -6.67          | -6.92          |

| $\chi_0$                | 4.90           | 4.07           |

Table 4.1: Required material parameters for  $In_x Ga_{1-x}As$  material system.

| Bowing Parameter   | (In,Ga)As    |  |

|--------------------|--------------|--|

| $C(E_g^{\Lambda})$ | -0.127+1.31x |  |

| $C(E_g^X)$         | 0.055        |  |

| $C(E_g^L)$         | 0            |  |

| $C(E_v^0)$         |              |  |

| $C(\Delta_0)$      | 0            |  |

Table 4.2: Bowing parameters for  $In_x Ga_{1-x}As$  material system.

# Chapter 5

## **Results and Discussions**

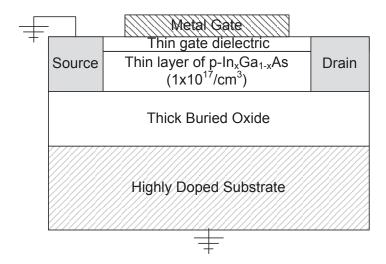

III-V semiconductors have shown promise to become the material of choice for future high performance devices. As discussed before number of different structures with different III-V semiconductors have come under consideration. In this study bulk MOSFETs, Surface Channel MOSFETs, Double Gate MOSFETs and SOI MOSFETs have been taken for theoretical evaluation of their limiting performance. The devices fabricated to this day suffer from different processing issues such as oxide-semiconductor interface traps. Thus the experimentally reported drain currents does not provide a clear picture of the limiting performance of each devices and their variation with material compositions.  $In_xGa_{1-x}As$  was taken as the material of choice for this study. The obtained results are presented here. Also the device parameters are presented in Table 5.1

| Device Type     | EOT  | <b>Doping Concentration</b> | Thickness              |  |

|-----------------|------|-----------------------------|------------------------|--|

|                 | (nm) | ${f cm}^{-3}$               | $\mathbf{n}\mathbf{m}$ |  |

| Bulk            | 0.53 | $7.5 \times 10^{18}$        |                        |  |

| Surface Channel | 0.53 | $7.5 \times 10^{18}$        | 5-20                   |  |

| Double Gate     | 0.77 | $1 \times 10^{17}$          | $5,\!8$                |  |

| SOI             | 0.6  | $1 \times 10^{17}$          | 5.5                    |  |

Table 5.1: Parameters for the devices used for simulation in this study.

### 5.1 Bulk MOSFETs

Bulk MOSFETs are typical Si MOSFET like structures only the semiconductor material is III-V.

Figure 5.1: Schematic diagram of a bulk MOSFET used for the simulation.

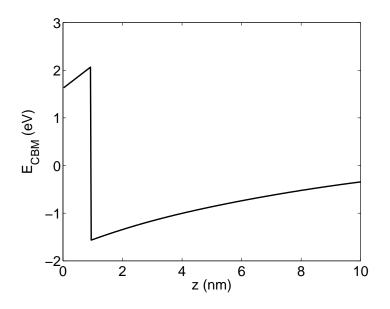

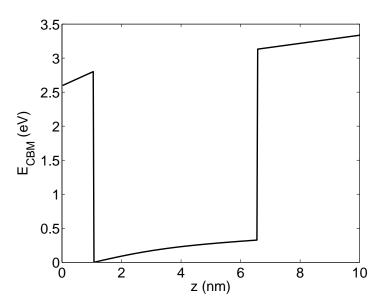

Figure 5.2: Energy band diagram portraying the conduction band minima (CBM) energy for InAs bulk MOSFET at  $V_{GS} = 2.0$  V.

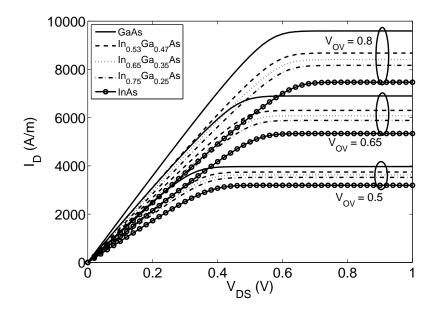

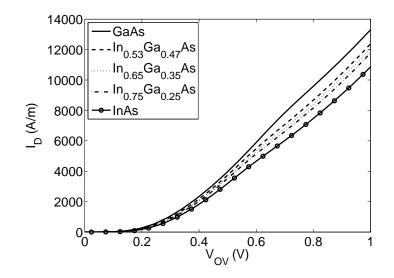

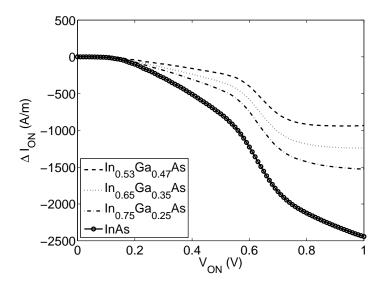

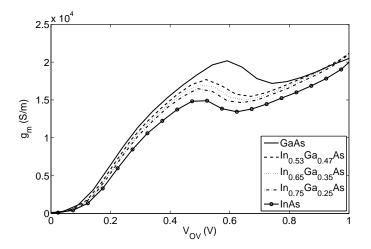

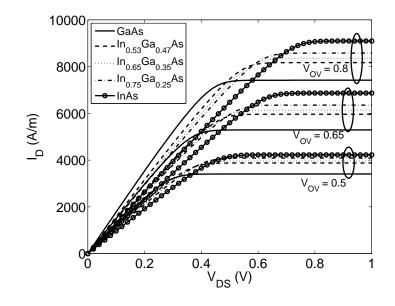

But III-V MOS fabrication rises some issues. InP is the material of choice as the substrate for the fabrication of  $In_xGa_{1-x}As$  MOSFETs. Thus a buffer layer of  $In_{0.53}Ga_{0.47}As$  has to be fabricated to reduce strain on the active layer. This buffer layer is not suitable for the end binary semiconductors that is GaAs and InAs. To provide a comparative picture for this study a hypothetical substrate is assumed which does not cause any strain on the active material. Also the active layer is taken to be thick such that the substrate does not play any role on the device performance. This is shown in the schematic diagram of a bulk III-V MOSFET in Fig. 5.1. The EOT of the oxide is 0.53 nm and the doping concentration is  $7.5 \times 10^{18} cm^{-3}$  according to [1]. The device parameters are also summarized in Table 5.1. The energy band diagram for an InAs bulk MOSFET under applied gate to source voltage  $V_{GS} = 2.0$  V is shown in Fig. 5.2. Here, the oxide-semiconductor conduction band offset will change with material composition. The oxide offsets for GaAs, In<sub>0.53</sub>Ga<sub>0.47</sub>As,  $In_{0.65}Ga_{0.35}As$ ,  $In_{0.75}Ga_{0.25}As$  and InAs for  $Al_2O_3$  are 2.80 eV, 3.34 eV, 3.42 eV, 3.5 eV and 4.23 eV respectively. The ballistic currents for devices with different material composition have been calculated using the methods discussed in Chapter 2. As a comparison between different materials is presented the comparison over the over drive voltage  $(V_{OV})$  is more appropriate. Here  $V_{OV} = V_{GS} - V_{th}$ . The threshold voltage  $(V_{th})$  is defined such that the drain current is 1 ( $\mu$ A/m). Fig. 5.3 shows the currents for five different materials for V<sub>OV</sub> 0.5 V, 0.65 V and 0.8 V respectively.

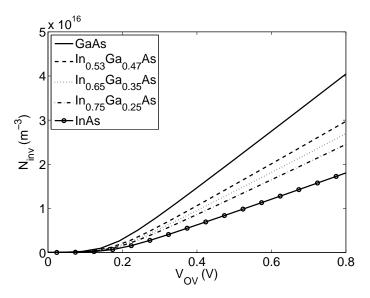

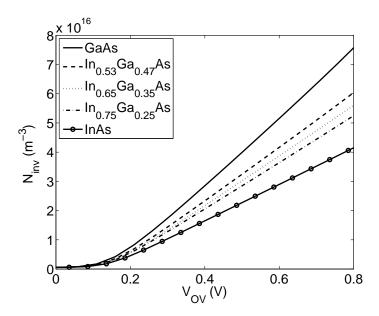

These results may present themselves as counter intuitive as we know that InAs has much higher electron mobility compared to GaAs. Thus it is expected that the drain currents will increase as the In composition in the material increases. Similar conclusion can be reached if the transport effective masses are taken into account for ballistic transport. The effective masses are shown in Table 4.1. The effective mass decreases as In composition increases in the material thus increasing the injection velocity. But the ballistic currents also depend on the inversion charge density. The number of inversion carriers are shown in Fig. 5.4

As the density of states effective mass reduces from GaAs towards InAs the inversion charge density is expected to reduce. Fig. 5.4 shows the inversion charge density for five

Figure 5.3: Simulated ballistic drain current for bulk MOSFETs at  $V_{OV} = 0.5$ , 0.65 and 0.8 V.

Figure 5.4: Number of inversion carriers  $N_{inv}$  for different bulk MOSFETs.

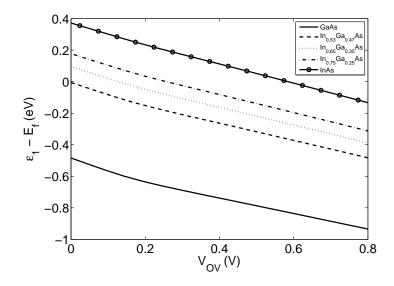

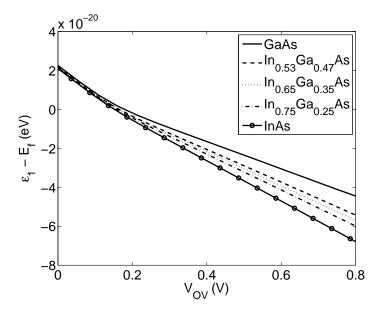

different materials. The figure shows a significant decrease in inversion charge density. Another factor in determining the ballistic current is the position of the Eigen energies  $\varepsilon_i$ . From Chapter 2 we observe that as  $\varepsilon_i$  goes closer to the source Fermi level the number of +k carriers increase. Fig. 5.5 shows the position of first Eigen energies with respect to the equilibrium source Fermi level.

Figure 5.5: Position of first Eigen state  $\varepsilon_1$  with respect to the equilibrium source Fermi level for different bulk MOSFETs.

Figure 5.6: Simulated ballistic on current for bulk MOSFETs at  $V_{DS} = 1.5$  V.

As GaAs has higher quantization effective mass the Eigen energy is lower than that of InAs. Also the potential well formed in the GaAs device will be narrower as the Eigen

Figure 5.7: Change in simulated ballistic on current for bulk MOSFETs with respect to GaAs bulk MOSFET at  $V_{DS} = 1.5$  V.

Figure 5.8: Simulated transconductance for bulk MOSFETs at  $V_{DS} = 1.5$  V.

energy is low. Due to the low Eigen energy the number of +k state carriers are higher for GaAs. This argument is also applicable to the -k states. As the Eigen energies are lower the energy state will be closer to the drain Fermi level thus resulting in a comparatively higher number of -k state carriers. But the drain Fermi level resides much lower than the Eigen states and slight variation of the Eigen states does not change the number of -k state carriers significantly as the drain Fermi is further away. But due to the close proximity of the source

Fermi a slight variation in the position of the Eigen states results in significant change in the number of +k state carriers and thus is the drain current. Fig. 5.6 shows the On current  $I_{ON}$  for different bulk MOSFETs at different  $V_{OV}$ . Also, the change in  $I_{ON}$  is depicted in Fig. 5.27 which shows the change is  $I_{ON}$  with respect to GaAs bulk MOSFET. A negative value denotes that current is decreasing from GaAs to InAs.

Table 5.2: Change in inversion charge ( $V_{OV} = 0.5 \text{ V}$ ), transport effective mass and drain current ( $V_{OV} = 0.5 \text{ V}$ ,  $V_{DS} = 1.5 \text{ V}$ ) for bulk MOSFETs.

| Parameter                                  | GaAs   | $\mathbf{In}_{0.53}\mathbf{Ga}_{0.47}\mathbf{As}$ | $\mathbf{In}_{0.65}\mathbf{Ga}_{0.35}\mathbf{As}$ | $\mathbf{In}_{0.75}\mathbf{Ga}_{0.25}\mathbf{As}$ | InAs    |

|--------------------------------------------|--------|---------------------------------------------------|---------------------------------------------------|---------------------------------------------------|---------|