# DESIGN AND OPTIMIZATION OF A FULLY INTEGRATED HIGH DATA RATE TRANCEIVER IN 90nm CMOS TECHNOLOGY FOR ON-CHIP UWB WIRELESS INTERCONNECT SYSTEM

A Thesis Submitted to the

Department of Electrical and Electronic Engineering

of

Bangladesh University of Engineering and Technology

Bangladesh University of Engineering and Technology in Partial Fulfillment of the Requirement For the Degree of

#### MASTER OF SCIENCE IN ELECTRICAL AND ELECTRONIC ENGINEERING

by

#### S. M. Shahriar Rashid

Student ID: 0409062238

DEPARTMENT OF ELECTRICAL AND ELECTRONIC ENGINEERING BANGLADESH UNIVERSITY OF ENGINEERING AND TECHNOLOGY (BUET)

OCTOBER, 2011

The thesis titled "DESIGN AND OPTIMIZATION OF A FULLY INTEGRATED HIGH DATA RATE TRANCEIVER IN 90nm CMOS TECHNOLOGY FOR ON-CHIP UWB WIRELESS INTERCONNECT SYSTEM" submitted by S. M. Shahriar Rashid, Student ID.: 0409062238 P, Session: April 2009 has been accepted as satisfactory in partial fulfillment of the requirement for the degree of MASTER OF SCIENCE IN ELECTRICAL AND ELECTRONIC ENGINEERING on October 30, 2011.

#### **BOARD OF EXAMINERS**

| Dr. A. B. M. Harun -Ur-Rashid<br>Professor<br>Department of Electrical and Electronic Engineering<br>BUET, Dhaka-1000, Bangladesh. | Chairman<br>(Supervisor)      |

|------------------------------------------------------------------------------------------------------------------------------------|-------------------------------|

| Dr. Md. Saifur Rahman Professor and Head Department of Electrical and Electronic Engineering BUET, Dhaka-1000, Bangladesh.         | <b>Member</b><br>(Ex-officio) |

| Dr. Pran Kanai Saha Professor Department of Electrical and Electronic Engineering BUET, Dhaka-1000, Bangladesh.                    | Member                        |

| Dr. M. Rezwan Khan Professor and Vice-Chancellor United International University (UIU) Dhanmondi, Dhaka-1209, Bangladesh           | <b>Member</b><br>(External)   |

### **Declaration**

| (S. M. Shahriar Rashid)                                                                        |

|------------------------------------------------------------------------------------------------|

|                                                                                                |

| Signature of the Student                                                                       |

|                                                                                                |

| for the award of any degree or diploma.                                                        |

| It is hereby declared that neither this thesis nor any part of it has been submitted elsewhere |

Student ID.: 0409062238 P

# **Dedication**

To my parents

## **CONTENTS**

| Appr   | oval Certific | cate    | •••         | •••    | •••     | •••    | •••    | •••    | •••    | •••  | •••  | •••  |     | ii  |

|--------|---------------|---------|-------------|--------|---------|--------|--------|--------|--------|------|------|------|-----|-----|

| Decla  | aration       | •••     | •••         | •••    | •••     | •••    | •••    | •••    | •••    | •••  | •••  | •••  |     | iii |

| Dedi   | cation        | •••     | •••         | •••    | •••     | •••    | •••    | •••    | •••    | •••  | •••  | •••  |     | iv  |

| List o | of Figures    | •••     | •••         | •••    | •••     | •••    | •••    |        | •••    | •••  | •••  | •••  |     | ix  |

| List o | of Tables     | •••     | •••         | •••    | •••     | •••    | •••    | •••    | •••    | •••  | •••  | •••  | 2   | XV  |

| Ackn   | owledgeme     | nt      | •••         | •••    | •••     | •••    | •••    | •••    | •••    | •••  | •••  | •••  | X   | vi  |

| Abstı  | ract          | •••     | •••         | •••    | •••     | •••    | •••    | •••    | •••    | •••  | •••  | •••  | X   | vii |

| СНА    | APTER 1       | Ι       | NTR         | ODU    | JCTI    | ON     | •••    | •••    | •••    | •••  | •••  | •••  | ••• | 1   |

| 1.1    | Motivatio     | on      | •••         | •••    | •••     | •••    | •••    | •••    | •••    | •••  | •••  | •••  | ••• | 1   |

| 1.2    | Overview      | of th   | ne Inte     | rconn  | ects    | •••    | •••    | •••    | •••    | •••  | •••  | •••  | ••• | 2   |

|        | 1.2.1 T       | hree I  | Dimen       | sional | (3D)    | Integr | ation  | •••    | •••    | •••  | •••  | •••  | ••• | 3   |

|        | 1.2.2 O       | ptical  | Interd      | connec | ct      | •••    | •••    | •••    | •••    | •••  | •••  | •••  | ••• | 3   |

|        | 1.2.3 R       | F/Wi    | reless      | Interc | onnec   | t      | •••    | •••    | •••    | •••  | •••  | •••  | ••• | 4   |

| 1.3    | Why do v      | we pro  | efer Rl     | F/Wir  | eless l | nterco | nnect  | •••    | •••    | •••  | •••  | •••  | ••• | 5   |

| 1.4    | Current S     | tate o  | of the I    | Proble | em      | •••    | •••    |        | •••    | •••  | •••  |      | ••• | 6   |

| 1.5    | Thesis O      | vervie  | ew          | •••    | •••     | •••    | •••    | •••    | •••    | •••  | •••  | •••  | ••• | 7   |

| 1.6    | Layout of     | f the T | Γhesis      |        | •••     | •••    | •••    | •••    | •••    | •••  | •••  | •••  | ••• | 8   |

| CHA    | APTER 2       | _       | J <b>WB</b> |        |         | CHIP   | V      | VIRI   | ELES   | SS   | TR   | ANC  | EIV |     |

|        |               | A       | ARCI        | HTE    | CTU     | JRE    | • •    | •      | •• •   | •• • | •• • | •• • | ••  | 11  |

| 2.1    | Bright Si     | des o   | f the U     | WB (   | Comm    | unicat | ion    | • •    |        | ••   | ••   | ••   | ••  | 1   |

| 2.2    | The On-C      | Chip I  | JWB Y       | Wirele | ess Tra | anscei | ver Ar | chitec | ture . |      |      |      |     | 12  |

| CHA         | APTER     | 3 DESIGN OF A DO             | GN OF A DOUBLE |          |         |          | E BALANCED SQUA |         |       |     |  |  |

|-------------|-----------|------------------------------|----------------|----------|---------|----------|-----------------|---------|-------|-----|--|--|

|             |           | CMOS FREQUI                  | ENC            | Y U      | P-C     | ONV      | ERS             | ION     | MI    | XER |  |  |

|             |           | FOR THE TRAN                 | SMI'           | TTEF     | 2       | •••      | •••             | •••     | •••   | 17  |  |  |

| 3.1         | Design    | Objectives of the Frequency  | Up-C           | Conver   | sion N  | Aixer    | •••             | •••     | •••   | 17  |  |  |

| 3.2         | Selection | on of the Mixer Topology     | •••            | •••      | •••     | •••      | •••             | •••     | •••   | 19  |  |  |

| 3.3         | Descrip   | tion of the Circuit          | •••            | •••      | •••     | •••      | •••             | •••     | •••   | 20  |  |  |

| 3.4         | Other S   | imulated Responses           | •••            | •••      | •••     | •••      | •••             | •••     | •••   | 27  |  |  |

| <b>CH</b> A | APTER     | 4 DESIGN OF A 20             | GH             | z DIF    | FER     | ENT      | IAL             | LOV     | V NO  | ISE |  |  |

|             |           | AMPLIFIER                    | •••            | •••      | •••     | •••      | •••             | •••     | •••   | 35  |  |  |

| 4.1         | Descrip   | tion of A 21 GHz Source-De   | egene          | rated I  | Differe | ential I | Low N           | Noise A | mplif | ier |  |  |

|             | •••       |                              | •••            | •••      |         | •••      | •••             | •••     | •••   | 35  |  |  |

|             | 4.1.1     | Design of the Source-Degen   | erated         | l Diffe  | rentia  | l LNA    | •••             | •••     | •••   | 36  |  |  |

|             | 4.1.2     | Simulated Responses of the   | Sourc          | e-Deg    | enerat  | ed Dif   | ferent          | tial LN | ΙA    | 42  |  |  |

| 4.2         | Design    | of A 20 GHz Differential Lo  | w No           | oise An  | nplifie | er       |                 | •••     | •••   | 44  |  |  |

|             | 4.2.1     | Description of the 20 GHz I  | Differe        | ntial L  | NA      | •••      | •••             | •••     | •••   | 44  |  |  |

|             | 4.2.2     | Frequency Response and Lin   | nearity        | y of the | e 20 C  | Hz Di    | ifferer         | ntial L | NA    | 55  |  |  |

|             | 4.2.3     | Transient Response of the 20 | ) GHz          | z Diffe  | rentia  | l LNA    | •••             | •••     | •••   | 60  |  |  |

|             | 4.2.4     | Area and Power Requirement   | nts of         | the 20   | GHz     | Differ   | ential          | LNA     | •••   | 62  |  |  |

| <b>CH</b> A | APTER     | 5 UNIFYING LNA               | AND            | MIX      | KER     | FOR      | THI             | E RE    | CEIV  | ER  |  |  |

|             |           | FRONT-END                    | •••            | •••      | •••     | •••      | •••             | •••     | •••   | 64  |  |  |

| 5.1         | Choosi    | ng a Suitable Mixer Topolog  | У              | •••      | •••     | •••      | •••             | •••     | •••   | 65  |  |  |

| 5.2         | Analys    | s of Gilbert's Mixer         | •••            | •••      |         | •••      |                 | •••     | •••   | 67  |  |  |

|             | 5.2.1     | Gilbert's Mixer as Freque    | ency (         | Conver   | ter     | •••      | •••             | •••     | •••   | 68  |  |  |

|             | 5.2.2     | Gilbert's Mixer as a Sma     | ll Sigi        | nal Mu   | ltiplie | er       | •••             | •••     | •••   | 70  |  |  |

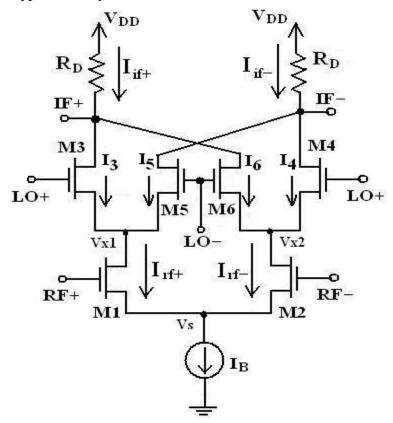

| 5.3 | Design of | of the Receiver Front-End      | •••      | •••     | •••    | •••     | •••    | •••     | •••  | 72  |

|-----|-----------|--------------------------------|----------|---------|--------|---------|--------|---------|------|-----|

|     | 5.3.1     | Design Issues                  | •••      | •••     | •••    | •••     | •••    | •••     | •••  | 73  |

|     | 5.3.2     | Unification of LNA and         | Mixer    | •••     | •••    | •••     | •••    | •••     |      | 77  |

|     | 5.3.3     | Limitation of this Unification | ation T  | Technic | que    | •••     | •••    |         | •••  | 82  |

|     | 5.3.4     | Frequency Responses an         | d Line   | arity o | f the  | Receiv  | er Fro | ont-End | d    | 83  |

| 5.4 | Detection | n of Traditional Digital Sig   | gnals b  | y this  | Recei  | ver Fro | ont-Ei | nd      | •••  | 89  |

|     | 5.4.1     | Synchronous Detection of       | of the S | Signal  | •••    | •••     | •••    | •••     | •••  | 91  |

|     | 5.4.2     | Asynchronous Detection         | of the   | Signa   | 1      | •••     | •••    | •••     | •••  | 93  |

| CHA | APTER 6   | OPTIMIZING TI<br>DETECT HIGH   |          |         |        |         |        |         |      | INC |

|     |           | UWB TRANSMI                    |          |         |        |         |        |         |      | 98  |

| 6.1 | Design (  | Objectives of the Receiver     | Front-   | End     | •••    | •••     | •••    | •••     | •••  | 99  |

| 6.2 | Optimizi  | ing the Receiver Front-End     | l        | •••     | •••    | •••     | •••    | •••     | •••  | 101 |

|     | 6.2.1     | Extension of Bandwidth         | •••      | •••     | •••    | •••     | •••    |         | •••  | 101 |

|     | 6.2.2     | Inter-Stage Matching           | •••      | •••     | •••    | •••     | •••    | •••     |      | 102 |

|     | 6.2.3     | Matching of LO Input Po        | ort      | •••     | •••    | •••     | •••    |         | •••  | 108 |

|     | 6.2.4     | Matching of RF Input Po        | ort      | •••     | •••    | •••     | •••    | •••     |      | 110 |

|     | 6.2.5     | Justification of the Narro     | w Bar    | nd Inpu | ıt Mat | tching  | •••    | •••     | •••  | 112 |

|     | 6.2.6     | Noise Issues of the Rece       | iver Fr  | ont-Ei  | nd     | •••     | •••    | •••     |      | 117 |

| 6.3 | Detection | n of TR-UWB Pulse Stream       | n by tl  | his Red | ceiver | Front-  | -End   | •••     |      | 117 |

| 6.4 | Modified  | d TR-UWB Communicatio          | n Sche   | eme     | •••    | •••     | •••    | •••     | •••  | 119 |

| CHA | APTER 7   | DESIGN OF A H                  | IGH      | SPEI    | ED C   | COME    | PAR    | АТОБ    | R FO | R   |

|     |           | THE RECEIVER                   |          | •••     | •••    | •••     | •••    | •••     | •••  | 123 |

| 7.1 | Design o  | of the Comparator              | •••      | •••     | •••    | •••     | •••    | •••     | •••  | 124 |

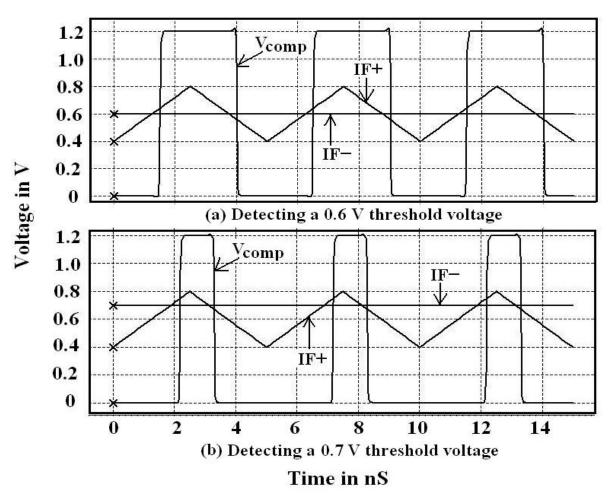

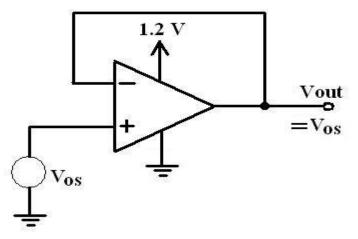

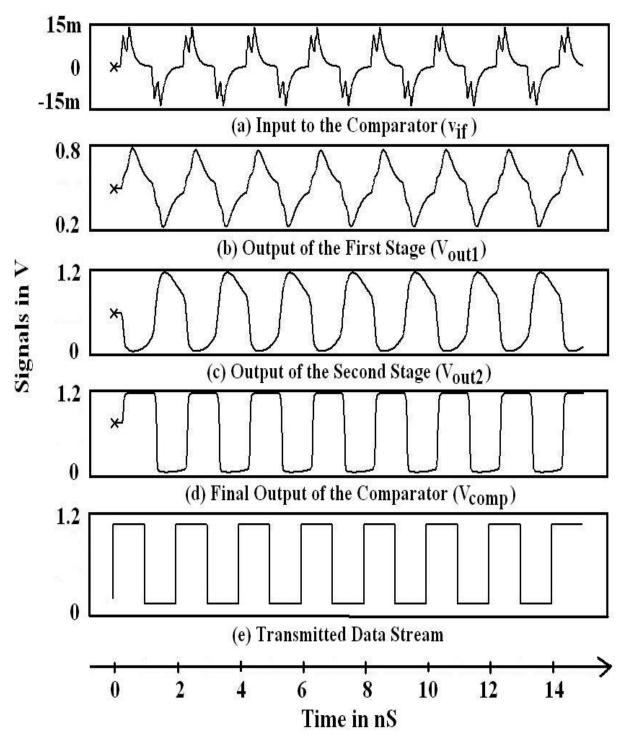

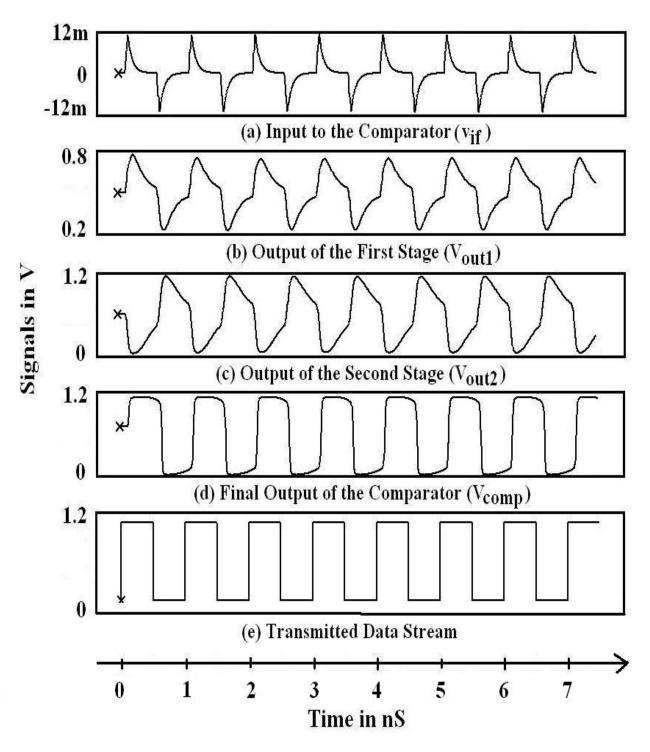

| 7.2 | Detection | n of High Speed Digital Da     | ata      | •••     | •••    | •••     | •••    | •••     | •••  | 136 |

| 7.3 | Commit    | ments of this Comparator       | •••      | •••     | •••    | •••     | •••    | •••     | •••  | 139 |

| CHA   | APTER 8   | CO      | NCL     | USI    | ON     | •••     | ••• | •••   | •••   | •••     | ••• | ••• | 144 |

|-------|-----------|---------|---------|--------|--------|---------|-----|-------|-------|---------|-----|-----|-----|

| 8.1   | Summary o | of Cont | ributio | ons of | this V | Work    | ••• | •••   | •••   | •••     | ••• |     | 144 |

| 8.2   | Future Wo | rks     | •••     | •••    | •••    | •••     | ••• | •••   | •••   | •••     | ••• | ••• | 148 |

| Appe  | endix A   | Photog  | graph   | of the | e Fab  | ricated | Low | Noise | e Amj | plifier | ••• | ••• | 150 |

| Refer | ences     |         |         | •••    |        |         |     |       |       |         |     |     | 151 |

# List of Figures

| Figure 1.1:  | Transceiver architecture of the Optical Interconnect            | 4  |

|--------------|-----------------------------------------------------------------|----|

| Figure 1.2:  | Block diagram of a typical RF/Wireless Interconnect             | 4  |

| Figure 2.1:  | Block diagram of the on-chip UWB wireless transceiver           | 12 |

| Figure 2.2:  | Transmitted TR-UWB Signal                                       | 13 |

| Figure 2.3:  | Internal block diagram of the TR-UWB pulse generator            | 13 |

| Figure 2.4:  | Signals at nodes of Fig. 2.3                                    | 14 |

| Figure 2.5:  | Block diagram of a typical receiver                             | 15 |

| Figure 2.6:  | Signals at the nodes of the receiver of Fig. 2.1                | 16 |

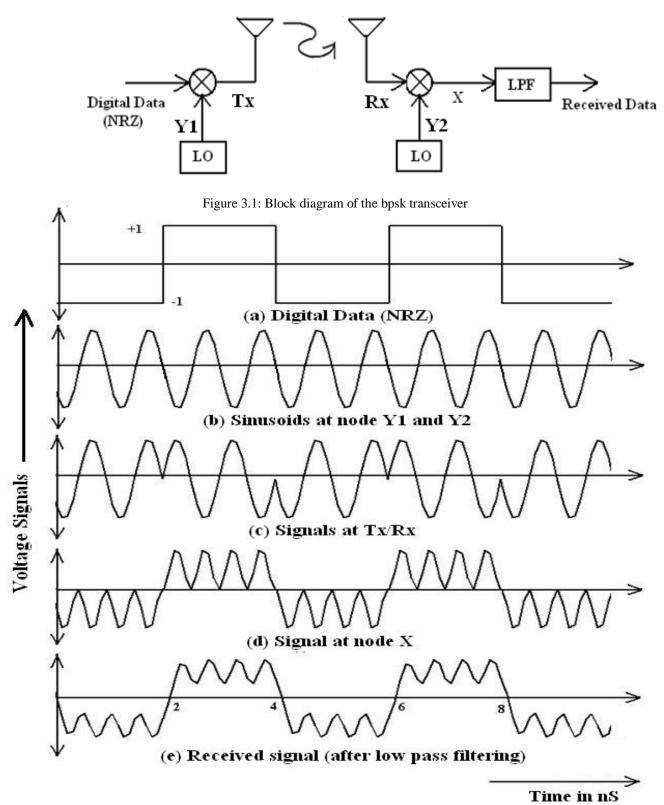

| Figure 3.1:  | Block diagram of the bpsk transceiver                           | 18 |

| Figure 3.2:  | Signals at the nodes of Fig. 3.1                                | 18 |

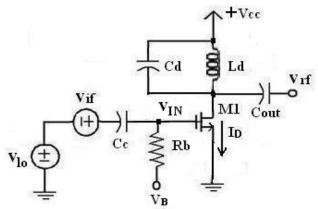

| Figure 3.3:  | A simple square law mixer                                       | 21 |

| Figure 3.4:  | Modified circuit of a square law mixer                          | 22 |

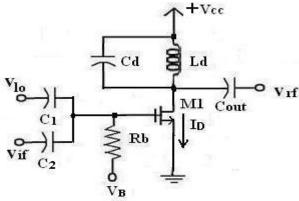

| Figure 3.5:  | Square Law Mixer with improved input isolation technique        | 22 |

| Figure 3.6:  | Voltage Gain of the circuit of Fig. 3                           | 23 |

| Figure 3.7:  | Normalized FFT of vrf of the mixer in Fig. 3.5                  | 23 |

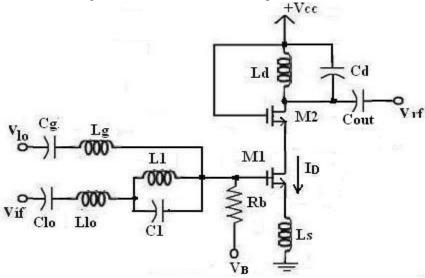

| Figure 3.8:  | The double balanced square law CMOS up-conversion mixer         | 24 |

| Figure 3.9:  | Normalized Frequency Constituents of the Double Balanced Output | 25 |

| Figure 3.10: | Double Balanced Output Vs Time                                  | 26 |

| Figure 3.11: | Normalized Frequency Constituents of the Single Balanced Output | 26 |

| Figure 3.12: | Single Balanced Output Vs Time                                  | 27 |

| Figure 3.13: | S21 and S12 Vs Frequency                                        | 28 |

| Figure 3.14: | S11 and S22 Vs Frequency                                        | 28 |

| Figure 3.15: | Input Isolation Vs Frequency                                    | 29 |

| Figure 3.16: | Noise Figure and Minimum Noise Figure Vs Frequency              | 29 |

| Figure 3.17: | Input referred 1dB Compression Point                            | 30 |

| Figure 3.18: | Input referred IP3 (IIP3)                                       | 30 |

| Figure 3.19: | Group Delay Vs Frequency                                        | 31 |

| Figure 3.20: | RF Output for the three tone input signal                       | 32 |

| Figure 3.21: | Ideal RF Output from (3.6) Vs Time                                                          | 32 |

|--------------|---------------------------------------------------------------------------------------------|----|

| Figure 3.22  | (a): Transmitted signal of Fig. 3.10                                                        | 33 |

| Figure 3.22  | (b): Received signal                                                                        | 33 |

| Figure 4.1:  | A 21GHz source-degenerated differential low noise amplifier                                 | 36 |

| Figure 4.2:  | Half circuit of the differential LNA of Figure 4.1                                          | 36 |

| Figure 4.3:  | Core amplifier for SNIM matching                                                            | 37 |

| Figure 4.4:  | Core amplifier for PCSNIM matching                                                          | 37 |

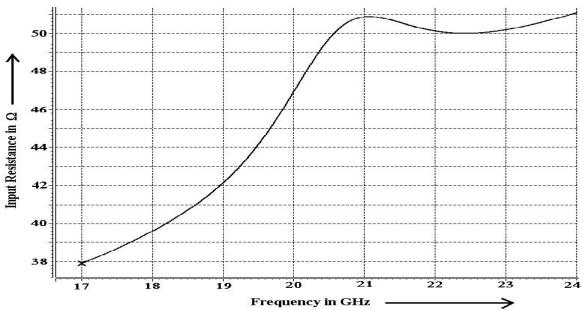

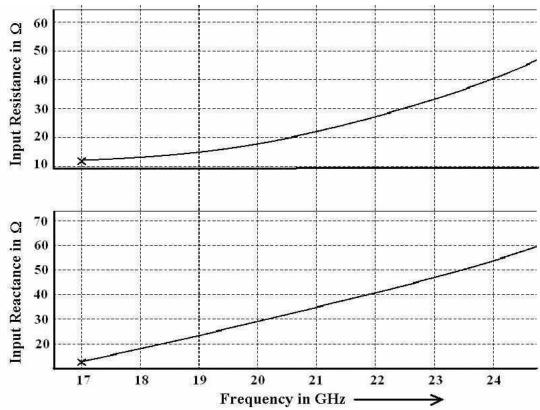

| Figure 4.5:  | Input resistance versus frequency for the circuit of Fig. 4.1                               | 41 |

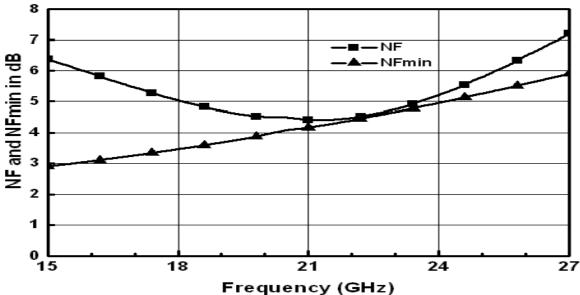

| Figure 4.6:  | NF and NFmin versus frequency for the circuit of Fig. 4.1                                   | 41 |

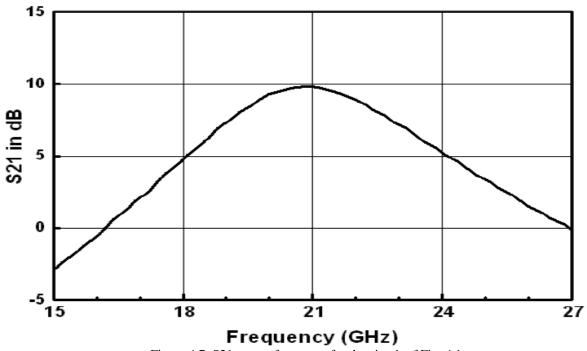

| Figure 4.7:  | S21 versus frequency for the circuit of Fig. 4.1                                            | 42 |

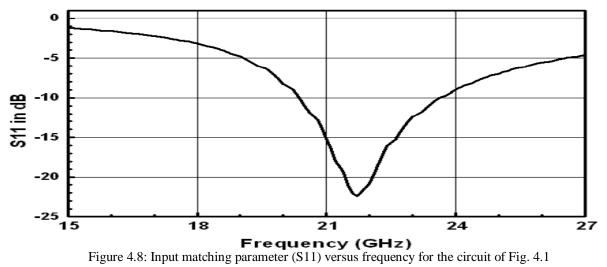

| Figure 4.8:  | Input matching parameter (S11) versus frequency for the circuit of Fig. 4.1                 | 43 |

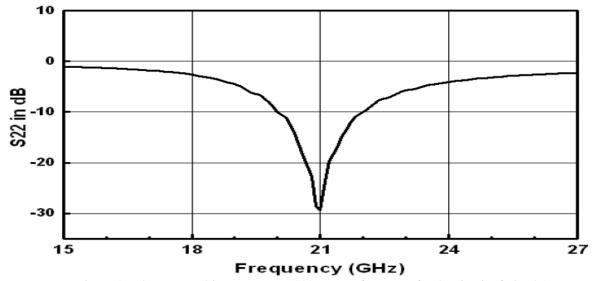

| Figure 4.9:  | Output matching parameter (S22) versus frequency for the circuit of Fig. 4.1                | 43 |

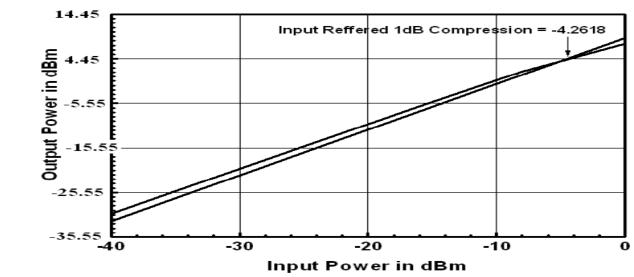

| Figure 4.10: | Output versus input power for the circuit of Fig. 4.1                                       | 43 |

| Figure 4.11: | Half circuit of the 20 GHz differential LNA                                                 | 44 |

| Figure 4.12: | Half Circuit of the 20 GHz differential LNA without input-output Matching                   | 45 |

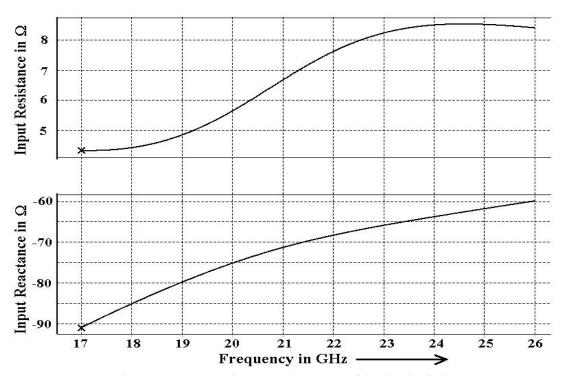

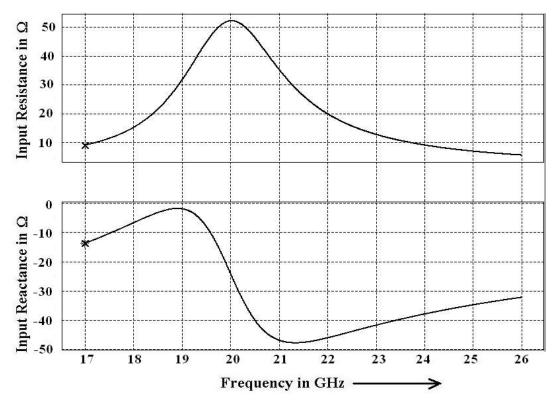

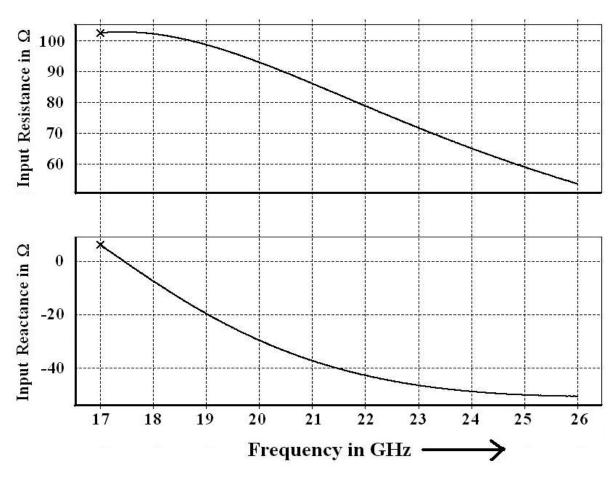

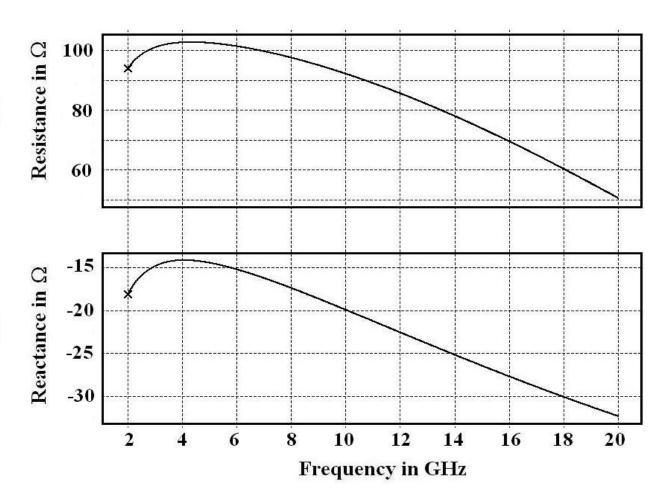

| Figure 4.13: | Input resistance and reactance of the circuit of Fig. 4.12                                  | 45 |

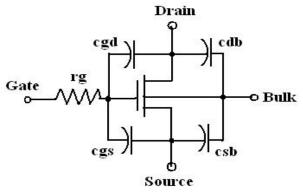

| Figure 4.14: | High frequency model of the NMOS Transistor                                                 | 46 |

| Figure 4.15: | Schematic diagram of a parallel resonator                                                   | 46 |

| Figure 4.16: | Half Circuit of the 20 GHz differential LNA with a gate inductor                            | 47 |

| Figure 4.17: | Input resistance and reactance of the circuit of Fig. 4.16                                  | 47 |

| Figure 4.18: | Half Circuit of the 20 GHz differential LNA with input matching                             | 48 |

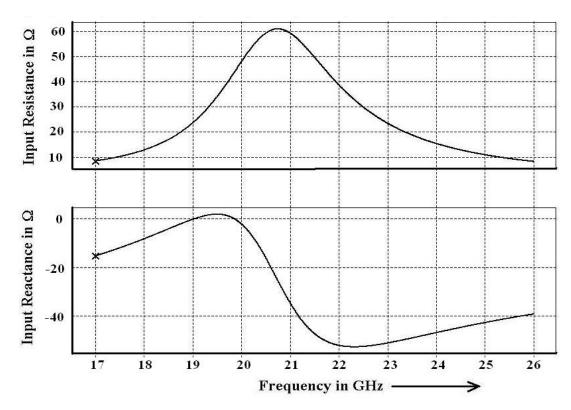

| Figure 4.19: | Input resistance and reactance of the circuit of Fig. 4.18                                  | 49 |

| Figure 4.20: | Input resistance and reactance of the circuit of Fig. 4.18 after the adjustment of $C_{RF}$ | 49 |

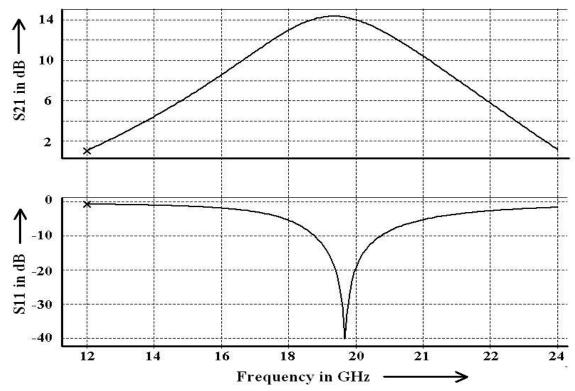

| Figure 4.21: | S21 versus frequency of the circuit of Fig. 4.18                                            | 50 |

| Figure 4.22: | NF and NFmin versus frequency of the circuit of Fig. 4.18                                   | 51 |

| Figure 4.23: | Input reactance of the circuit of Fig. 4.18 versus frequency                                | 52 |

| Figure 4.24: | NF and NFmin of the circuit of Fig. 4.18 versus frequency after noise matching              | 52 |

| Figure 4.25: | S21 and S11 of the circuit of Fig. 4.18 versus frequency after noise matching               | 53 |

| Figure 4.26: | Complete 20 GHz differential low noise amplifier                                            | 54 |

| Figure 4.27: | S21 versus frequency of the 20 GHz differential LNA                                         | 55 |

| Figure 4.28: | S12 versus frequency of the 20 GHz differential LNA                                | 56 |

|--------------|------------------------------------------------------------------------------------|----|

| Figure 4.29: | S11 and S22 versus frequency of the 20 GHz differential LNA                        | 56 |

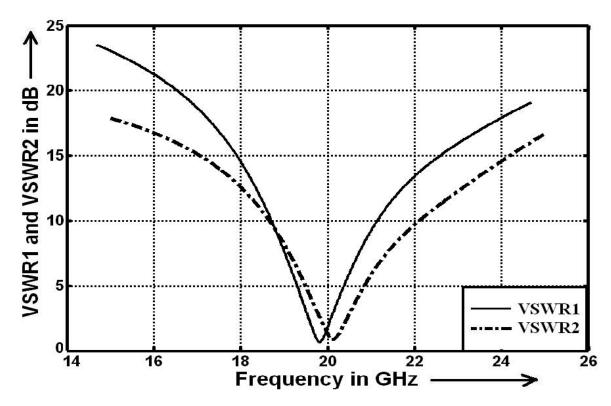

| Figure 4.30: | VSWR1 and VSWR2 versus frequency of the 20 GHz differential LNA                    | 57 |

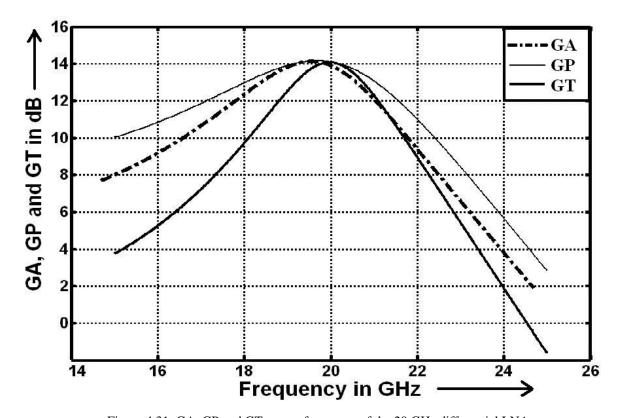

| Figure 4.31: | GA, GP and GT versus frequency of the 20 GHz differential LNA                      | 57 |

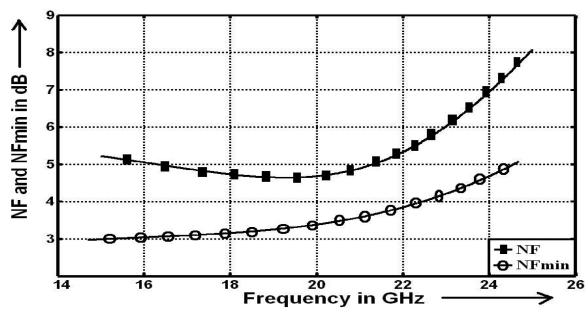

| Figure 4.32: | Noise Figure (NF) and Minimum Noise Figure (NFmin) versus frequency of the         |    |

|              | 20 GHz differential LNA                                                            | 58 |

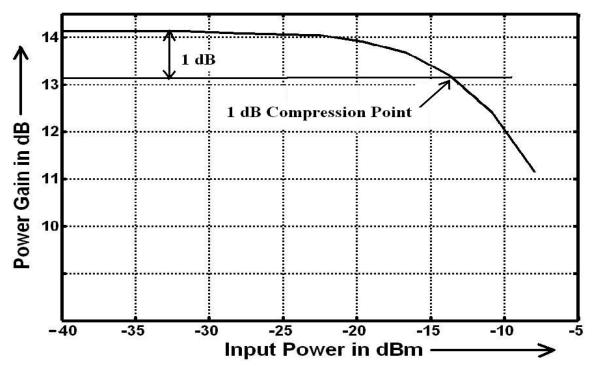

| Figure 4.33: | Gain versus input power of the 20 GHz differential LNA                             | 59 |

| Figure 4.34: | Illustration of the 3rd order intercept point (IP3) of the 20 GHz differential LNA | 59 |

| Figure 4.35: | Rollet stability factor (Kf) of the 20 GHz differential LNA                        | 60 |

| Figure 4.36: | System for observing Transmitted (Tx), Received (Rx) and Amplified signals in      |    |

|              | time domain                                                                        | 61 |

| Figure 4.37: | Signals at the nodes of Fig. 4.36                                                  | 61 |

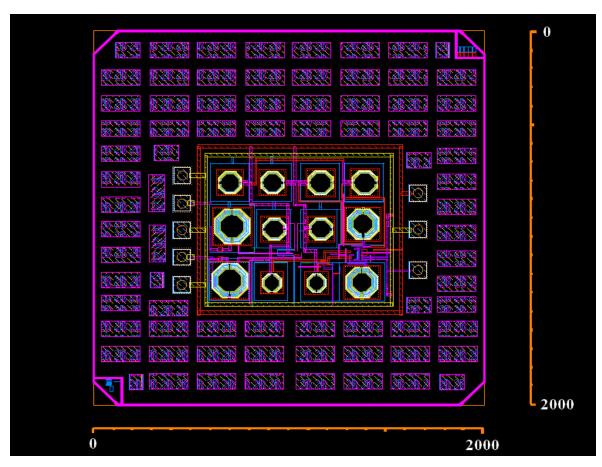

| Figure 4.38: | Layout of the 20 GHz differential low noise amplifier                              | 62 |

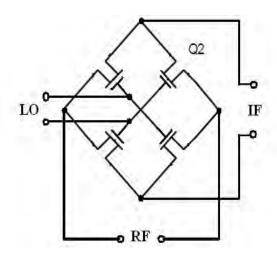

| Figure 5.1:  | Core of a passive mixer                                                            | 66 |

| Figure 5.2:  | A basic bulk-driven mixer                                                          | 66 |

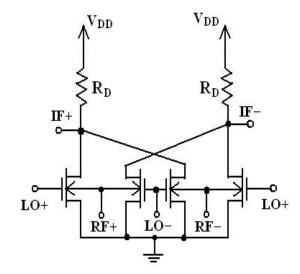

| Figure 5.3:  | A basic Gilbert's mixer                                                            | 67 |

| Figure 5.4:  | Input-Output signals of a Gilbert's mixer when working as frequency up-converter   | 69 |

| Figure 5.5:  | Frequency constituents of the output signal of Fig. 5.4(c)                         | 70 |

| Figure 5.6:  | An example of a receiver front end                                                 | 72 |

| Figure 5.7:  | Gilbert's mixer for high frequency applications                                    | 73 |

| Figure 5.8:  | A folded Gilbert's mixer                                                           | 74 |

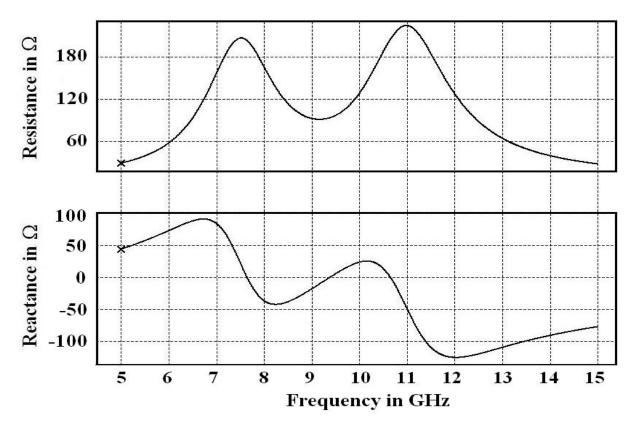

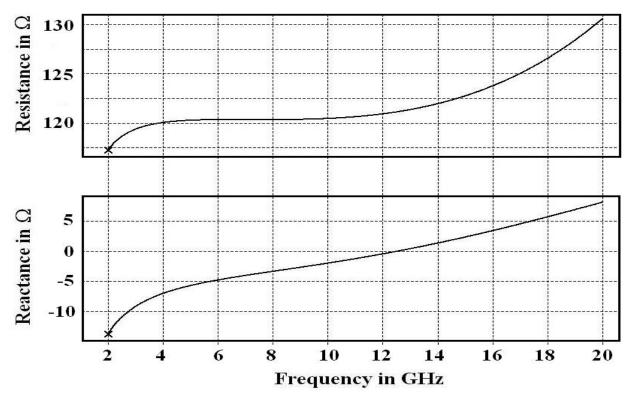

| Figure 5.9:  | Input resistance and reactance versus frequency of the mixer stage                 | 75 |

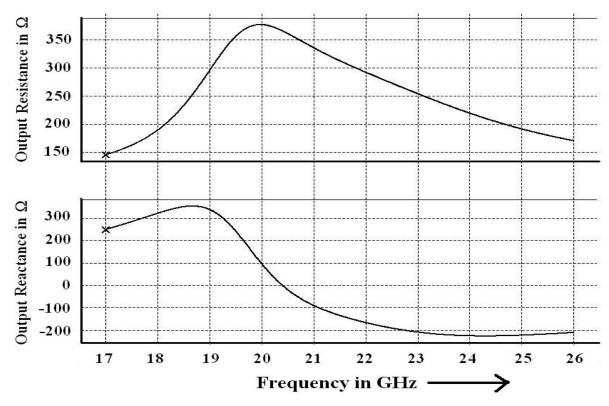

| Figure 5.10: | Output resistance and reactance versus frequency of the first stage                | 76 |

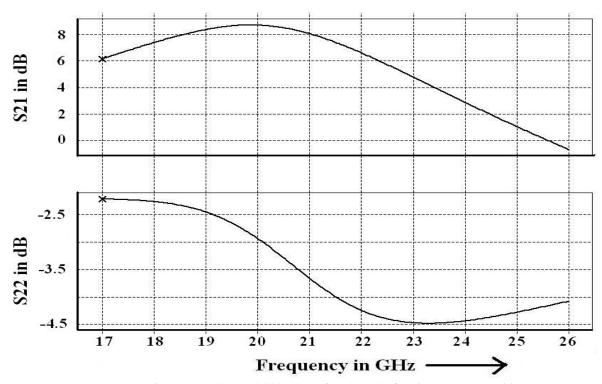

| Figure 5.11: | S21 and S22 versus frequency before inter-stage matching                           | 76 |

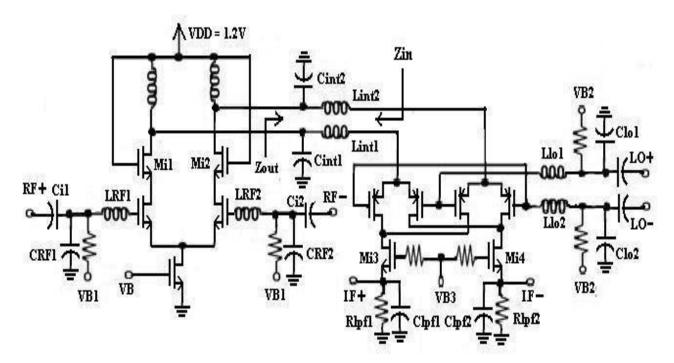

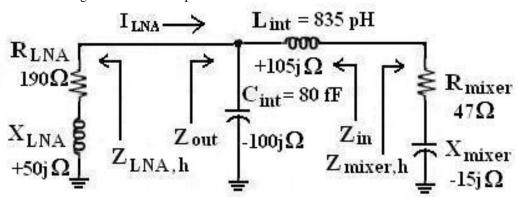

| Figure 5.12: | The complete circuit of unified LNA and mixer                                      | 78 |

| Figure 5.13: | Model of inter-stage matching                                                      | 78 |

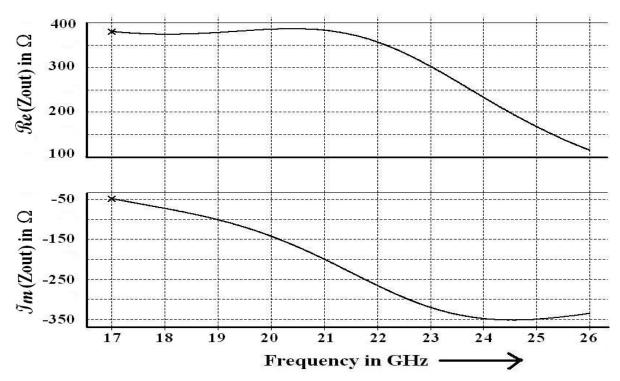

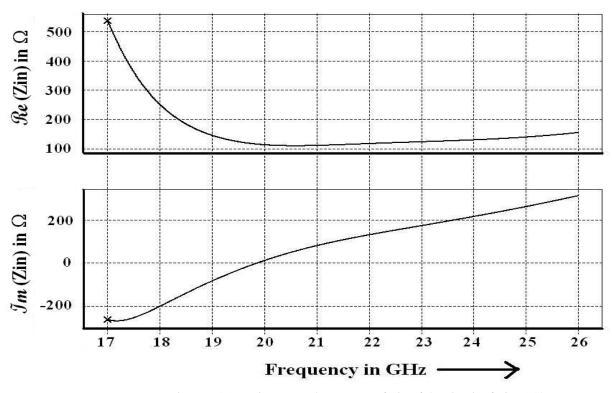

| Figure 5.14: | Resistance and reactance of Zout of the circuit of Fig. 5.12                       | 80 |

| Figure 5.15: | Resistance and reactance of Zin of the circuit of Fig. 5.12                        | 80 |

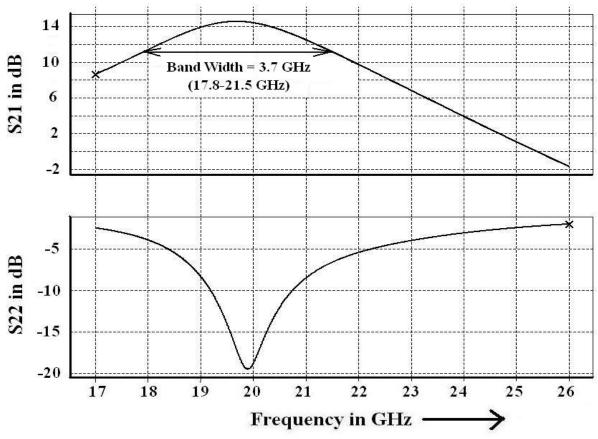

| Figure 5.16: | Gain (S21) and the output matching parameter (S22) of the first stage of Fig. 5.12 |    |

|              | after the inter-stage matching employed                                            | 81 |

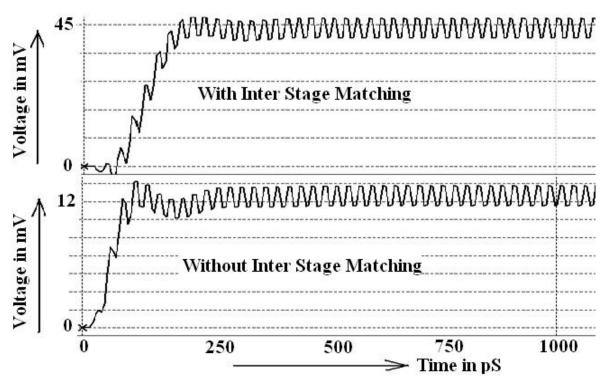

| Figure 5.17: | Transient response of the receiver front-end when detecting a dc signal    | 83  |

|--------------|----------------------------------------------------------------------------|-----|

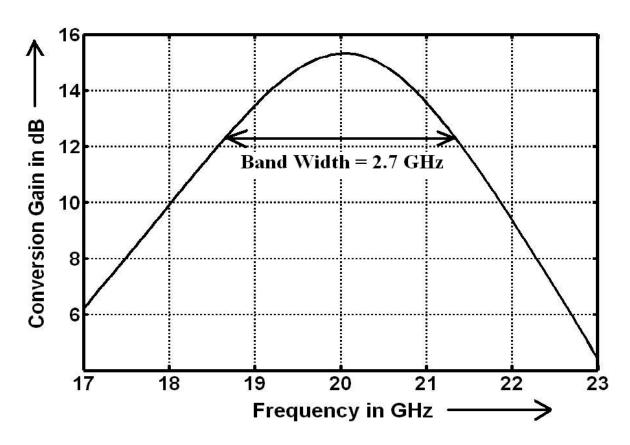

| Figure 5.18: | Conversion gain of the receiver front-end versus frequency                 | 84  |

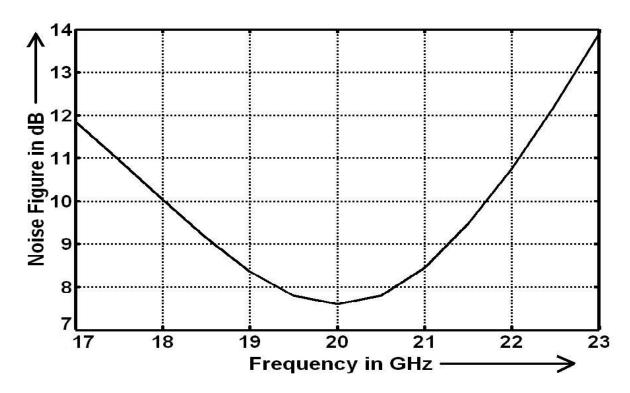

| Figure 5.19: | Noise Figure (NF) versus frequency                                         | 85  |

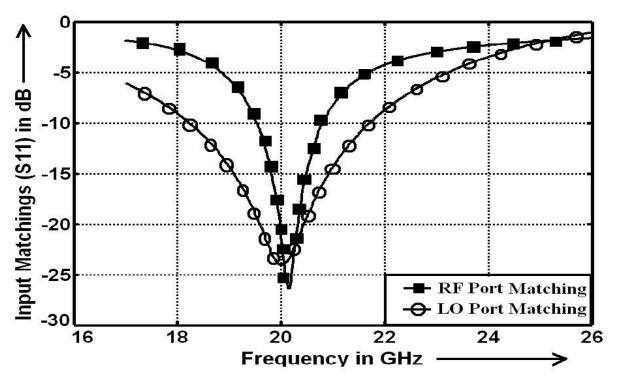

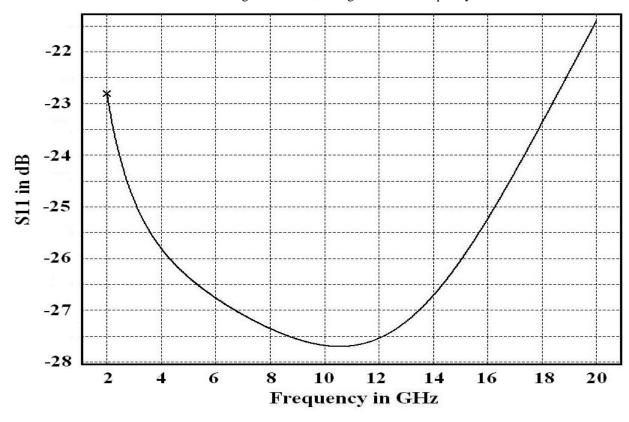

| Figure 5.20: | Input port matching parameters (S11) versus frequency                      | 86  |

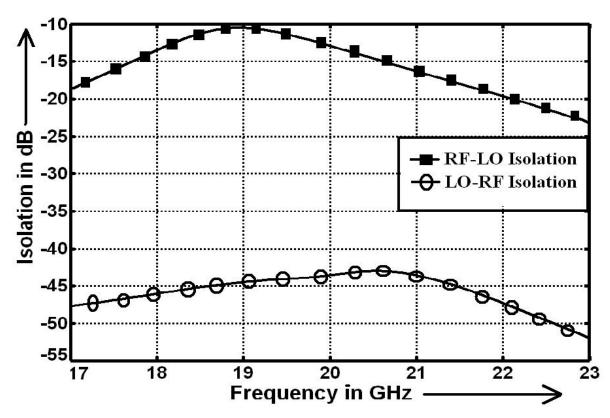

| Figure 5.21: | Input port isolations versus frequency                                     | 86  |

| Figure 5.22: | Input to output feed-through versus frequency                              | 87  |

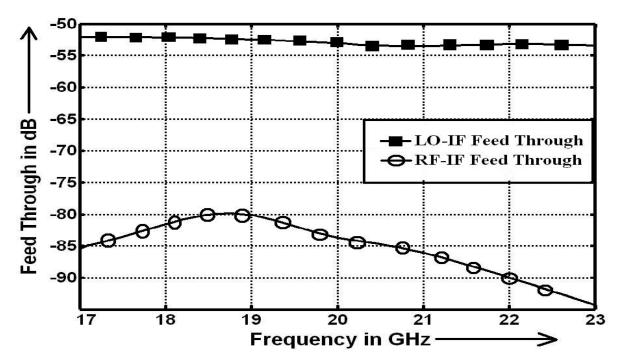

| Figure 5.23: | Conversion gain versus input power                                         | 88  |

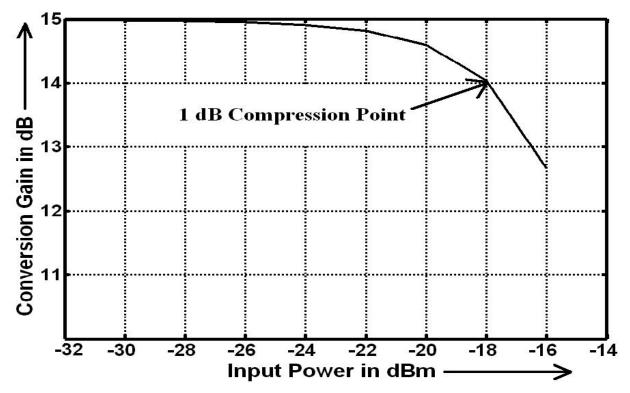

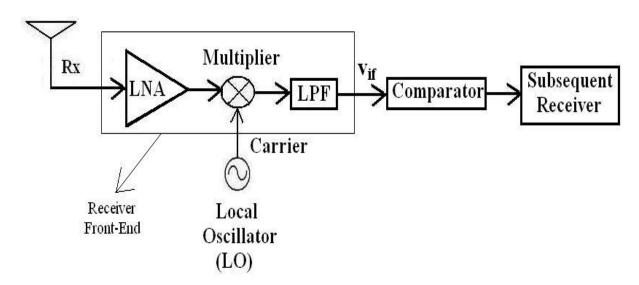

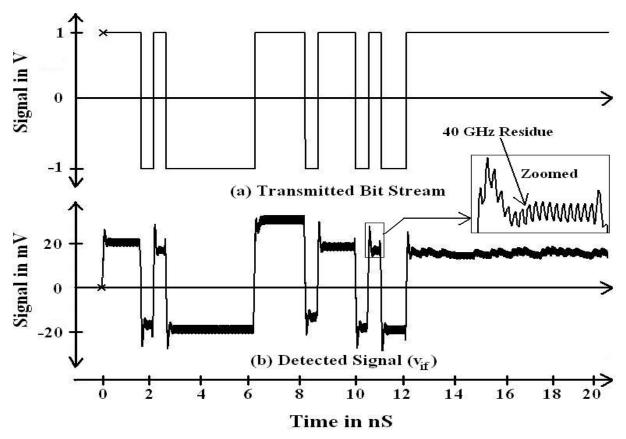

| Figure 5.24: | The basic block diagram of the transceiver                                 | 90  |

| Figure 5.25: | Signals at different nodes of the system of Fig. 5.24                      | 90  |

| Figure 5.26: | Receiver diagram for synchronous detection of the signal                   | 91  |

| Figure 5.27: | Transmitted and detected digital bit streams                               | 92  |

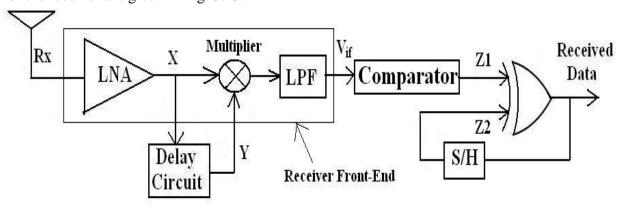

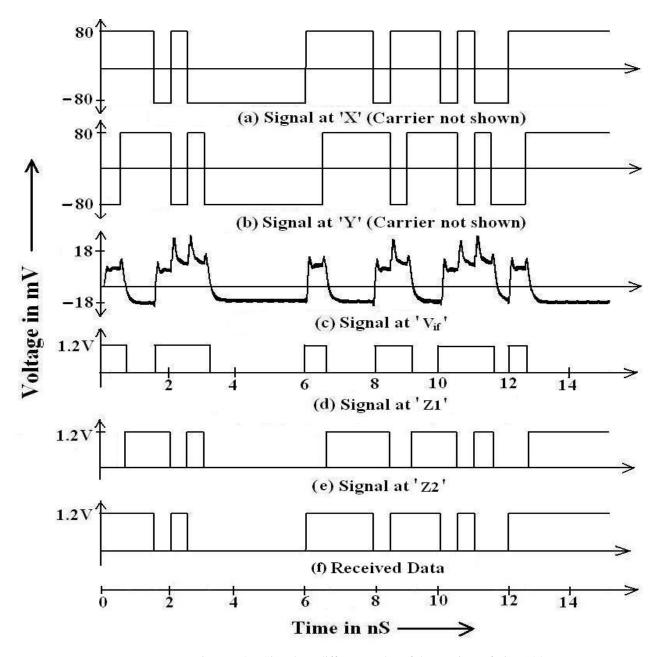

| Figure 5.28: | Receiver diagram for asynchronous detection of the signal                  | 93  |

| Figure 5.29: | Signals at different nodes of the receiver of Fig. 5.28                    | 94  |

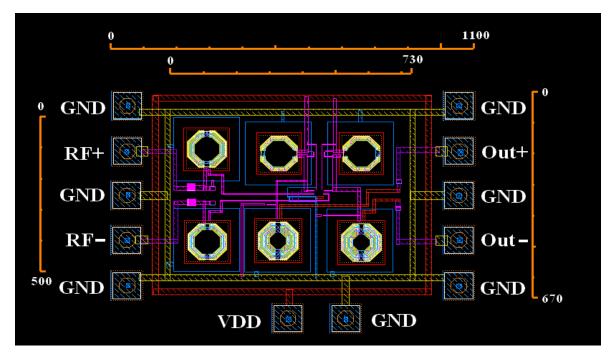

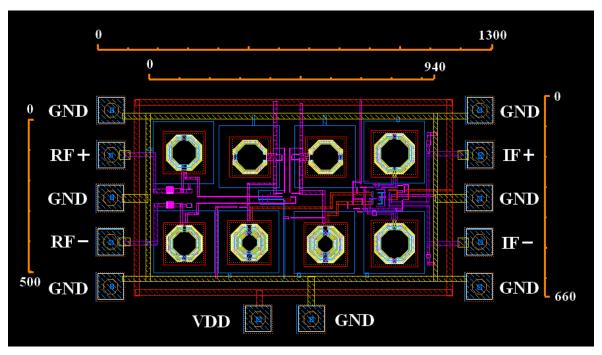

| Figure 5.30: | Layout of the receiver front-end of Fig. 5.12                              | 96  |

| Figure 5.31: | Layout of the whole chip                                                   | 96  |

| Figure 6.1:  | Block diagram of the on-chip UWB wireless transceiver                      | 98  |

| Figure 6.2:  | Signals at the nodes of the receiver of Fig. 6.1                           | 99  |

| Figure 6.3:  | Received signal at node 'Rx' of the block diagram of Fig. 6.1              | 100 |

| Figure 6.4:  | Frequency constituents of the signal of Fig. 6.3                           | 100 |

| Figure 6.5:  | Receiver front-end to work with TR-UWB signal                              | 103 |

| Figure 6.6:  | Voltage gain of the first stage of the receiver front-end                  | 103 |

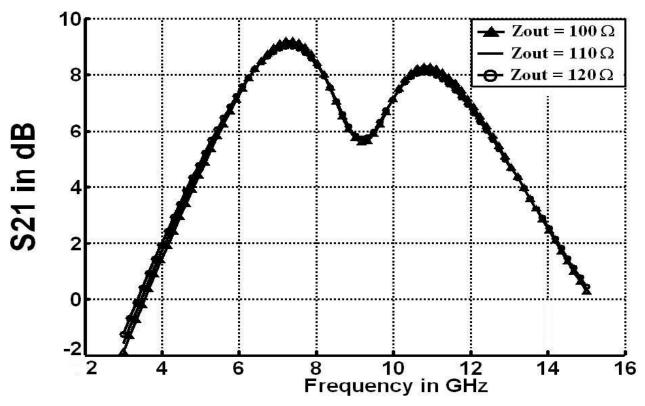

| Figure 6.7:  | $Z_{LNA}$ of Fig. 6.5 versus frequency                                     | 104 |

| Figure 6.8:  | Gain (S21) of the LNA versus frequency for three different load impedances | 105 |

| Figure 6.9:  | Output matching (S22) of the LNA versus frequency for three different      |     |

|              | load impedances                                                            | 105 |

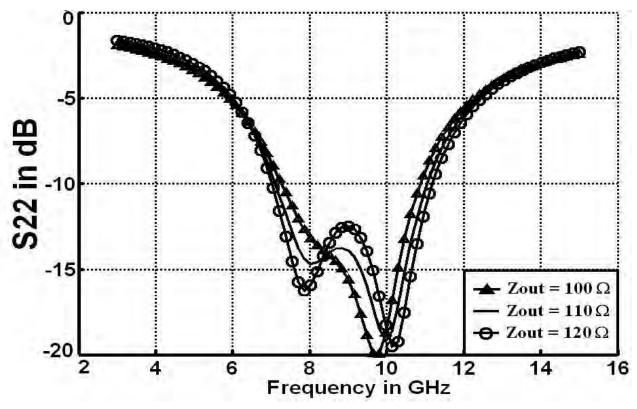

| Figure 6.10: | $Z_{mixer}$ of Fig. 6.5 versus frequency                                   | 106 |

| Figure 6.11: | $Z_{out}$ of Fig. 6.5 versus frequency                                     | 107 |

| Figure 6.12: | S11 of the second stage of Fig. 6.5 versus frequency                       | 107 |

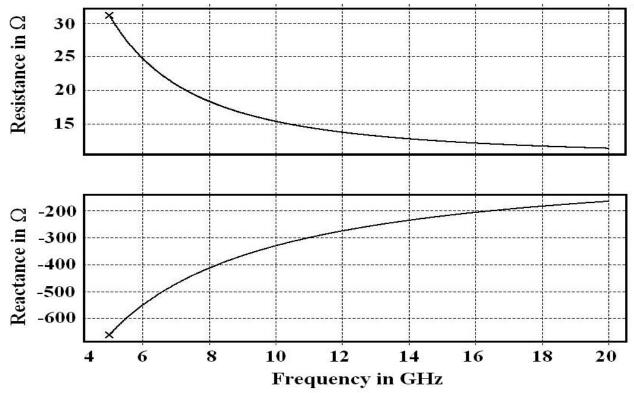

| Figure 6.13: | Z <sub>LO</sub> of Fig. 6.5 versus frequency (Before matching)             | 109 |

| Figure 6.14: | $Z_{LO}$ of Fig. 6.5 versus frequency (After matching)                     | 109 |

| Figure 6.15: | Input matching parameter (S11) of the LO port versus frequency                       | 110 |

|--------------|--------------------------------------------------------------------------------------|-----|

| Figure 6.16: | $Z_{RF}$ of Fig. 6.5 versus frequency (Before matching)                              | 111 |

| Figure 6.17: | Z <sub>RF</sub> of Fig. 6.5 versus frequency (After matching)                        | 111 |

| Figure 6.18: | Input matching parameter (S11) of the RF port versus frequency                       | 112 |

| Figure 6.19: | S21 and S12 of the first stage of Fig. 6.5 (LNA) versus frequency                    | 113 |

| Figure 6.20: | S11 and S22 of the first stage of Fig. 6.5 (LNA) versus frequency                    | 113 |

| Figure 6.21: | Signals at three different nodes of the circuit of Fig. 6.5                          | 114 |

| Figure 6.22: | Frequency components of the signal of Fig. 6.21(a) and (b)                           | 115 |

| Figure 6.23: | Signals at different nodes of the circuit of Fig. 6.5                                | 116 |

| Figure 6.24: | Noise figure of the receiver front end versus frequency                              | 116 |

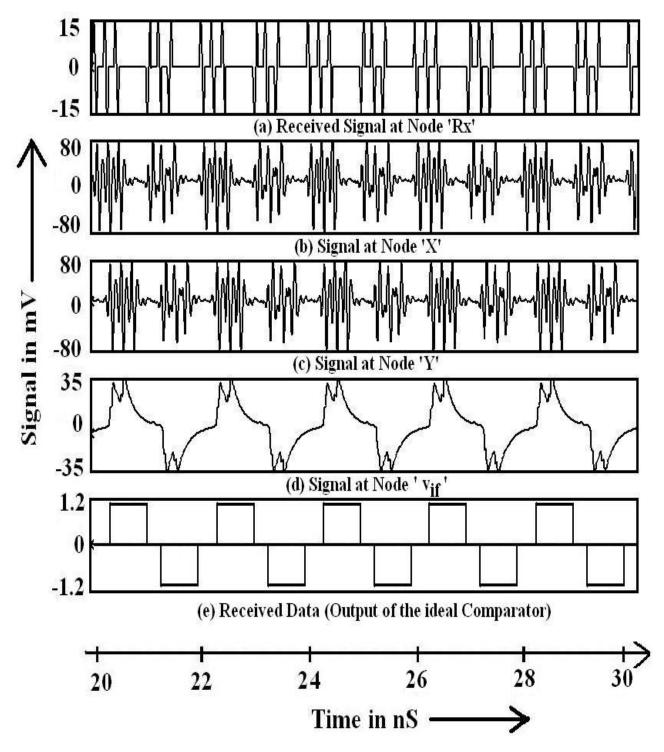

| Figure 6.25: | Signals at different nodes of the UWB receiver of Fig. 6.1 when detecting 2 gbps     |     |

|              | digital data with real receiver front-end of Fig. 6.5 employed                       | 118 |

| Figure 6.26: | Proposed three pulse TR-UWB signal for on-chip wireless interconnect                 | 119 |

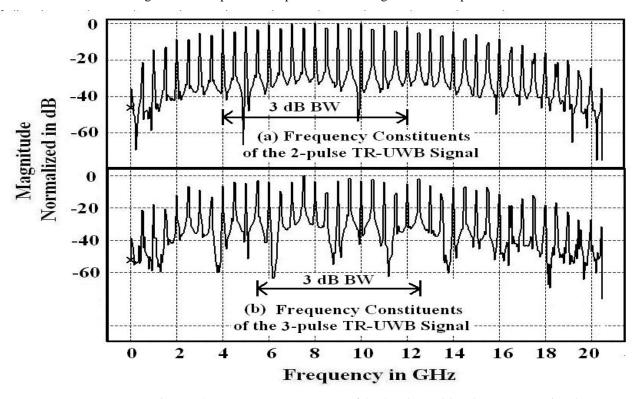

| Figure 6.27: | Frequency components of the 2-pulse and 3-pulse TR-UWB signal                        | 119 |

| Figure 6.28: | Detection of the 1 gbps digital data using 3-pulse TR-UWB transmission scheme        | 120 |

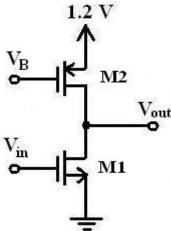

| Figure 7.1:  | A real active loaded common source amplifier                                         | 124 |

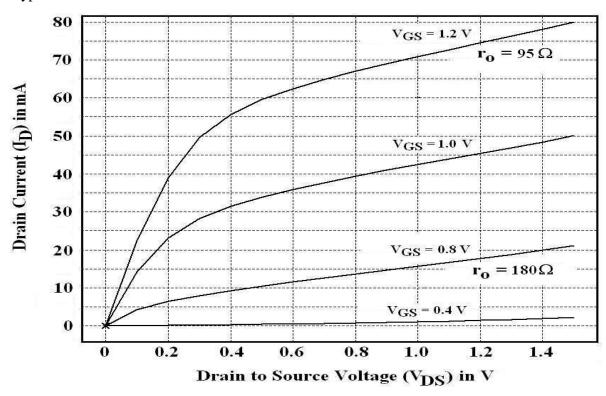

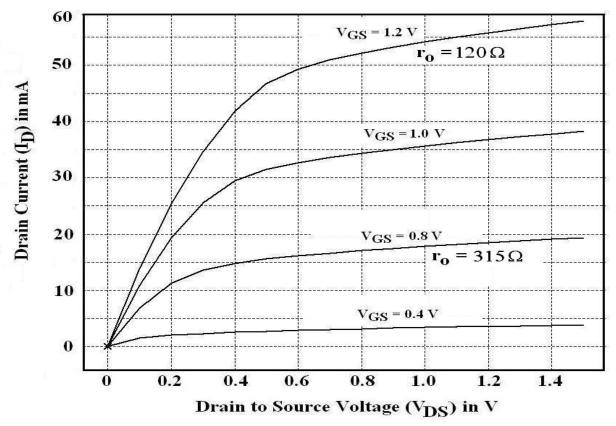

| Figure 7.2:  | I-V curve of NMOS transistors with W=100 $\mu m$ and L=100 nm                        | 125 |

| Figure 7.3:  | I-V curve of NMOS transistors with W=100 μm and L=200 nm                             | 126 |

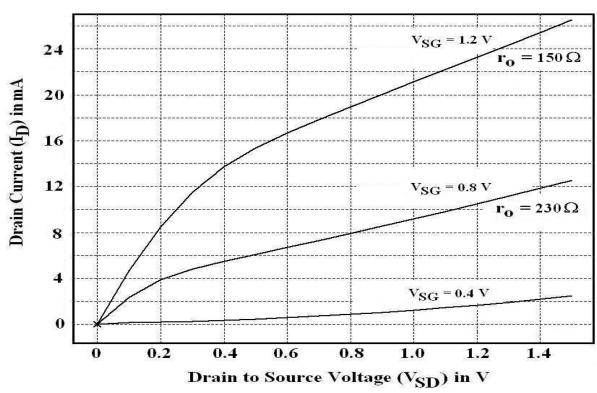

| Figure 7.4:  | I-V curve of PMOS transistors with W=100 $\mu m$ and L=100 $nm$                      | 126 |

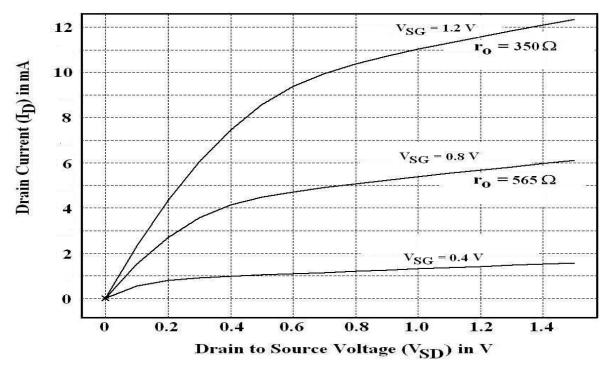

| Figure 7.5:  | I-V curve of PMOS transistors with W=100 $\mu m$ and L=200 nm                        | 127 |

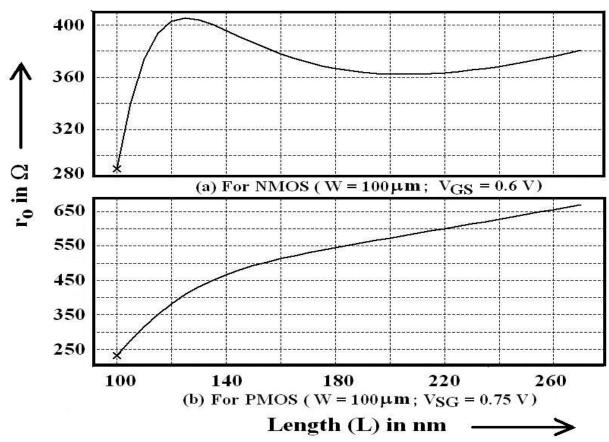

| Figure 7.6:  | ro of NMOS and PMOS transistors versus channel length                                | 127 |

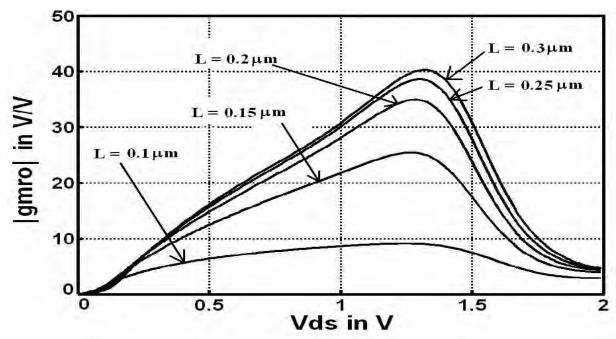

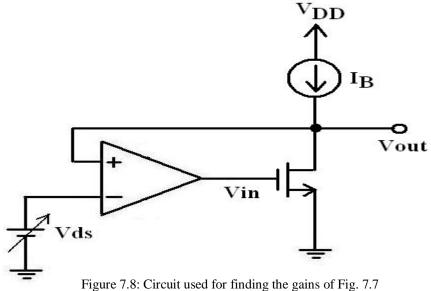

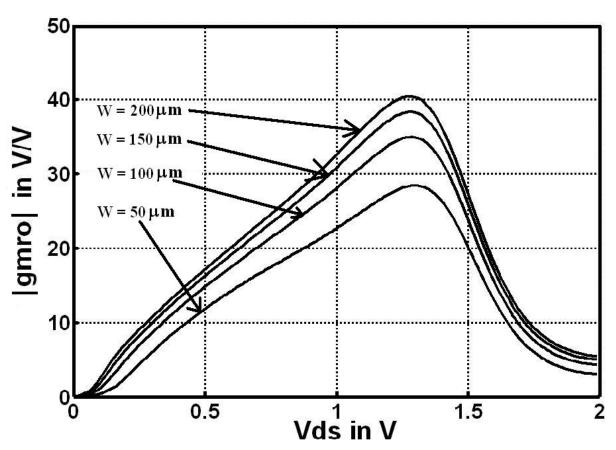

| Figure 7.7:  | Gain of an ideal current source loaded common source amplifier for various L $\dots$ | 128 |

| Figure 7.8:  | Circuit used for finding the gains of Fig. 7.7                                       | 128 |

| Figure 7.9:  | Gain of the ideal current source loaded common source amplifier for various W        | 129 |

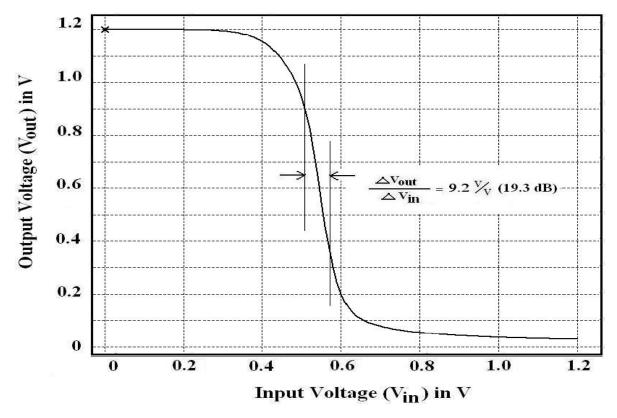

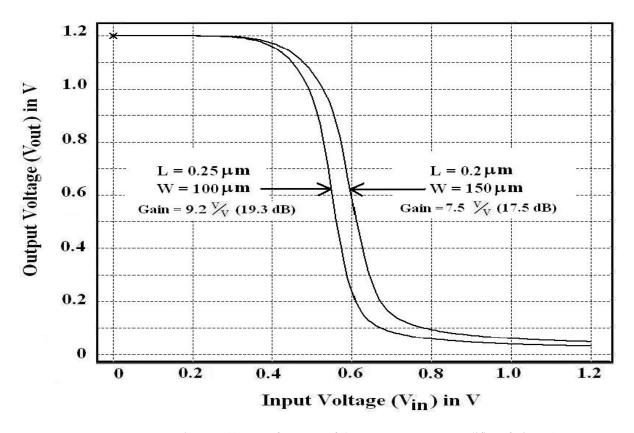

| Figure 7.10: | Transfer curve of the active loaded common source amplifier of Fig. 7.1              | 130 |

| Figure 7.11: | Transfer curve of the common source amplifier of Fig. 7.1 for two different sizes    |     |

|              | of the load                                                                          | 131 |

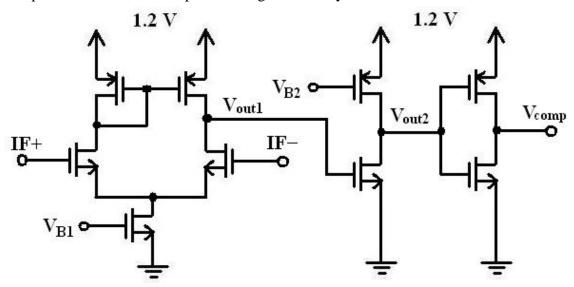

| Figure 7.12: | Schematic diagram of the three stage comparator                                      | 132 |

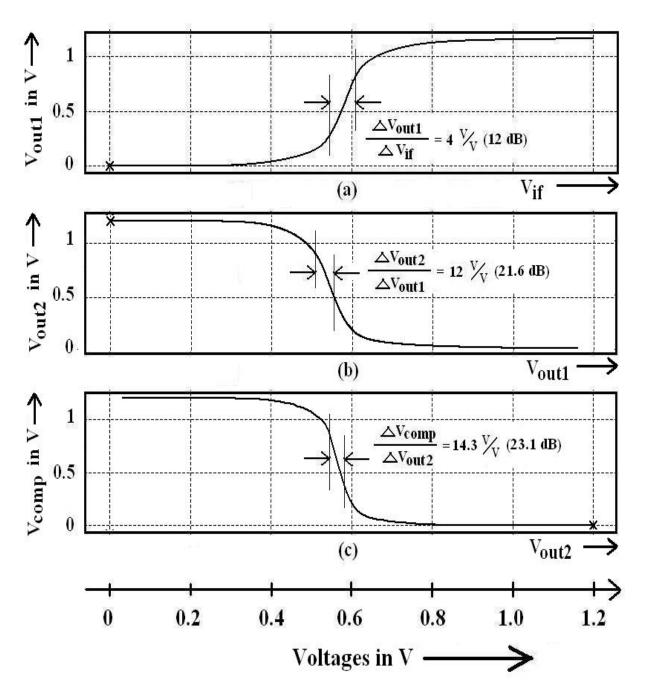

| Figure 7.13: | Transfer curves of all three individual stages of the comparator of Fig. 7.12        | 133 |

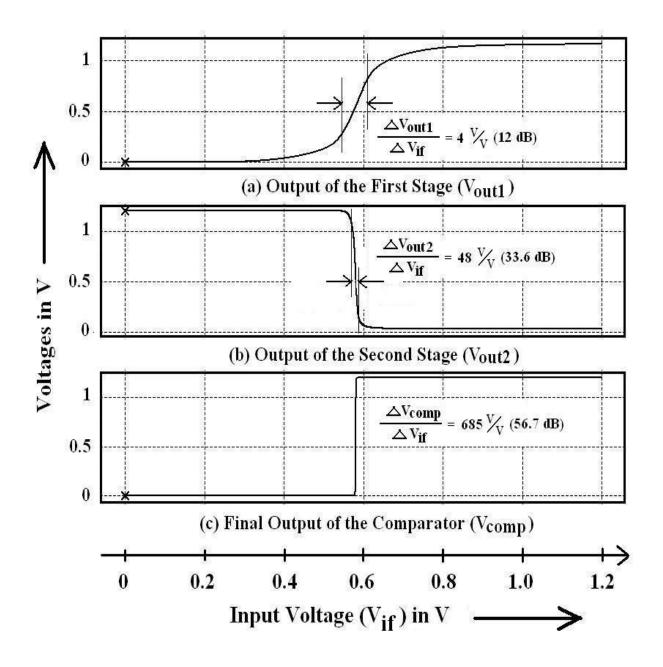

| Figure 7 14. | Overall transfer curves of all stages of the comparator of Fig. 7.12                 | 134 |

| Figure 7.15: | Performance of the comparator as a threshold detector                        | 135 |

|--------------|------------------------------------------------------------------------------|-----|

| Figure 7.16: | Circuit used for finding offset voltage                                      | 136 |

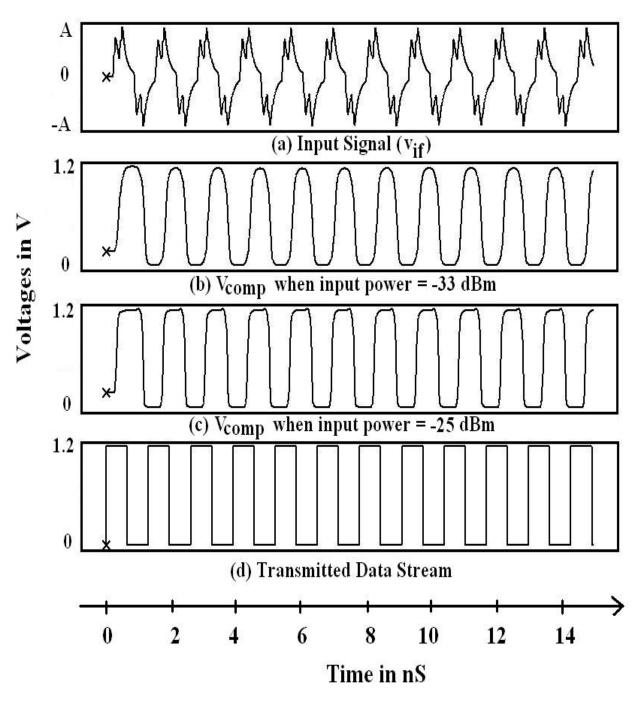

| Figure 7.17: | Regeneration of 1 gbps digital data in 3-pulse TR-UWB transmission scheme    | 137 |

| Figure 7.18: | Regeneration of 2 gbps digital data in 2-pulse TR-UWB transmission scheme    | 138 |

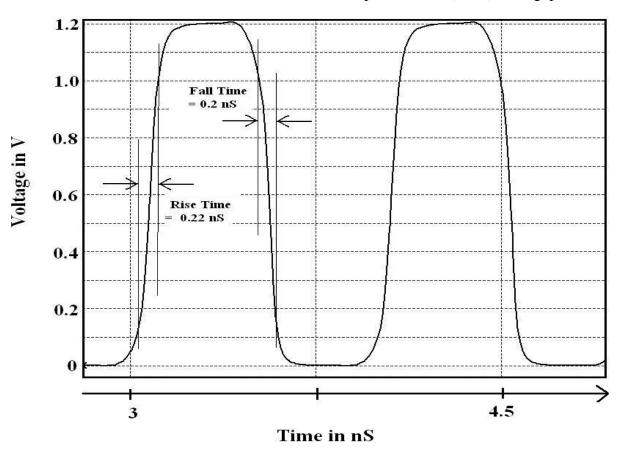

| Figure 7.19: | Finding maximum operating speed of the comparator                            | 139 |

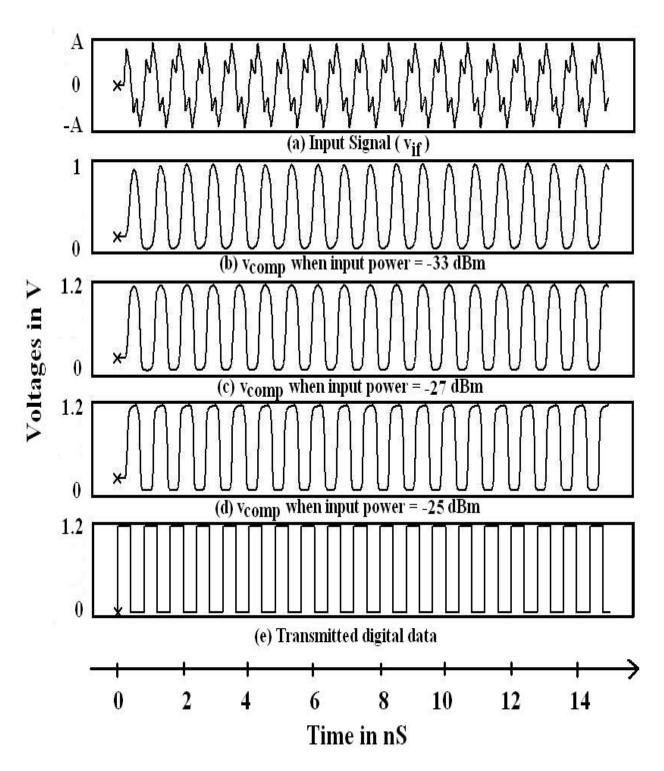

| Figure 7.20: | Finding minimum detectable received power level for 3-pulse signaling at the |     |

|              | maximum data speed of 1.5 gbps                                               | 140 |

| Figure 7.21: | Finding minimum detectable received power level for 2-pulse signaling at the |     |

|              | maximum data speed of 2.5 gbps                                               | 141 |

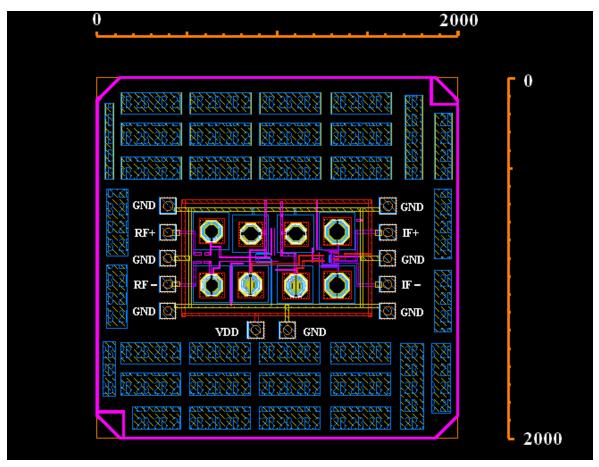

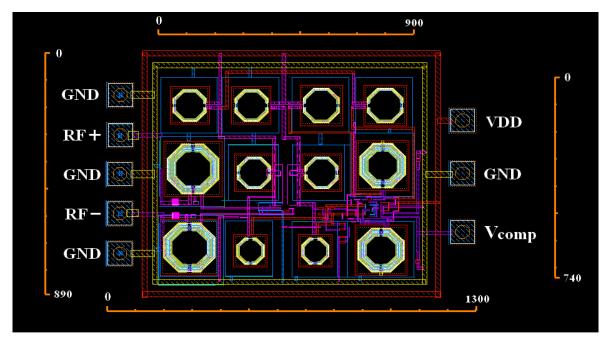

| Figure 8.1:  | Layout of the whole receiver                                                 | 147 |

| Figure 8.2:  | Layout of the full chip                                                      | 147 |

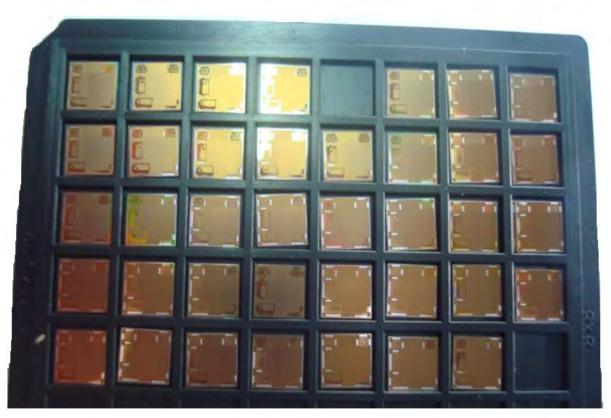

| Figure A.1:  | Photograph of the lot of 40 chips of 21 GHz source degenerated LNA           | 150 |

### List of Tables

| Table 4.1: | Comparison of the 20 GHz differential LNA with state of the art LNAs | 63  |

|------------|----------------------------------------------------------------------|-----|

| Table 5.1: | Comparison of the folded mixer with state of the art                 | 97  |

| Table 7.1: | Comparison of the high speed comparator with state of the art        | 143 |

#### Acknowledgement

All praises and gratitude belong to almighty Allah, without whose consent nothing is achievable. This is He, who gave me enough physical and mental strength to invest in this thesis that was of prime importance for completing this work.

I am very grateful to my supervisor, Dr. A. B. M. Harun-Ur-Rashid for his whole hearted support and friendly attitude which helped me a lot in moving onward with this thesis. His prudent suggestions and guidance illuminated my way innumerable times. He always extended his helping hand towards me for any kind of research materials or for any other help. He also had a lot of valuable suggestions for me, even besides official formalities. I shall be very glad to thank him for trusting throughout the progress of this work.

I am also grateful to Dr. Md. Saifur Rahman, Professor and Head, Department of Electrical and Electronic Engineering, BUET for his cordial helps and consents whenever I needed.

Last but not the least; I must remember my parents for their life long unconditional supports and inspirations which motivated me for all sorts of successes of my life.

#### **Abstract**

Modern submicron transistors are capable of offering unity gain bandwidths as high as hundred GHz. Still, circuit modules of next generation integrated circuits will not be able to utilize this high speed, if the parasitic issues associated with the interconnecting copper wires continue to increase as technology shrinks down. That is why; forthcoming ultra high speed ICs have to come up with a whole new interconnect systems replacing traditional copper interconnects. One of the approaches to overcome this limitation could be the use of on-chip wireless interconnection with integrated antenna. However, being sensitive to interference and multipath fading, this kind of short distance wireless data transmission necessitates the communication scheme to be carefully chosen. UWB topology, offering low power spectral density, has proved itself as one of the wise choices for this application. It has a lot more bright sides. Large bandwidth available for high speed data transmission, multiplexing capabilities, interference tolerances etc. are to name a few. TR-UWB (Transmitted Reference- Ultra Wide Band) version of this topology is gaining much interest in literature, especially for its simple transceiver architecture.

It this thesis, a number of RF circuits were designed, they are- square law up-conversion mixer, low noise amplifier, direct conversion folded mixer, low pass filter and comparator. The circuits were fully integrated i.e. no off chip circuit elements, in IBM 90 nm CMOS technology and were simulated both in Cadence Spectre & HSPICE. They were optimized in terms of speed, power, area etc. and were characterized thoroughly so as to investigate their viability of incorporating in the intended TR-UWB on-chip wireless interconnects systems. Finally, the circuits were assembled to form a complete system, included with on-chip integrated antenna pair to transmit and eventually to recover digital data where the system worked very successfully. A system level investigation was also carried on at the end to identify its overall performance limits. The maximum achievable speed of the system was found as 2.5 gbps with a minimum detectable receiving power level of -27 dBm. A new signaling scheme is also proposed to reduce the minimum

detectable power level to -33 dBm sacrificing about 1 gbps speed. The receiver burns only 40 mW power from a 1.2 V power supply and occupies 0.67 mm<sup>2</sup> area on silicon chip.

Therefore, overall performance of the system is outstanding and its commitment for being a viable replacement of traditional wired interconnects is really appreciating. In literature, there are only handful of circuit level designs of such intra-chip interconnects systems, which are capable of communicating random digital data wirelessly.

#### CHAPTER 1

#### INTRODUCTION

#### 1.1 Motivation

The unity gain frequency (f<sub>T</sub>) of modern submicron CMOS transistors are in around 100 GHz. But, this benefit is yet to be utilized in high speed ICs, because the parasitic issues associated with the traditional interconnects i.e. copper wire, limits the speed of their internal data transmission. This problem aggravates as the technology shrinks, because as the process scales down, the width of the metal wires also follow giving rise to an increase in wiring resistance. Moreover, smaller transistors need less space to create circuits that need more number of metal layers to account wiring difficulties. In other words, metal wires are coming closer ending up to larger parasitic capacitances. Thus, RC delay is waxing for both reasons and the consequence is the data transmission speed limitation to severe extent [1-2].

The delay of interconnecting wires can be quantified in terms of time of flight (TOF), which is defined as the delay experienced by a signal as it propagates through a wire of unit length. This TOF can be as high as 8 ps/mm. In comparison, gate delay of a NAND Gate of fan out 3 is about 30 and 12 ps in 130 nm and 50 nm technologies respectively [3].

Now, consider the edge dimension of modern microprocessors, which is in between 20 mm to 30 mm. These ICs need long interconnections between their arithmetic logic units (ALU), registers, cache storages etc. So, TOF of those long interconnect would range from 125 to 250 ps, meaning- speed of those microprocessors has to be less than 8 GHz. And this delay is 2 to 20 times of the gate delay of modern submicron technologies [4].

More alarming, limitation of interconnecting speed will be the bottleneck in the emerging age of nano-transistors, when several hundreds of GHz bandwidth will be available, if this issue is not addressed properly. So, fending off the interconnecting delays will be one of the major challenges in future ULSI technologies. That is why; this problem invokes a lot of research in parallel with technological advancement and a corner edge solution is to be invented.

#### 1.2 Overview of the Interconnects:

History of interconnects in ICs started with aluminum wire. Almost all the transistors and modules of the ICs in 1950s, when the technology was in it's infancies, were connected by aluminum wires. Later, as the process advanced, increased resistances of those wires due to scaling down began to bother. Peoples tried to overcome the problem by using wider wires or by using repeaters to connect modules. But, the first technique increased capacitance in long wires and second one yielded when the total delay of large number of repeaters over long distance summed up to be inconvenient. These factors put engineers in quest of alternative connecting metal like copper.

Copper wires were lucrative because of it's lower resistivity (60% of Aluminum). However, what factors took it so long to come in to ICs includes- difficulties of fabrication, diffusion through silicon, formation of silicon dioxides and it's toxicity. Fortunately, most of those problems could be avoided after the incorporation of complicated and costly copper damascene process.

Today, 40% improvement of resistivity of copper wires over aluminum is no longer sufficient for large modern ICs in submicron technologies, especially which aspire for operation in a speed of tens of GHz. So, this is the time to invent next generation interconnect techniques, that will not only reduce the interconnection delay considerably, but also will be simple, will occupy less space, will be usable both in intra-chip and interchip applications and will be cheap as well.

In response to this urge, the approaches proposed so far include:

- 1. Three Dimensional (3D) Integration

- 2. Optical Interconnect

- 3. RF/Wireless Interconnect

Let us put some light on their pros and cons.

#### **1.2.1** Three Dimensional (3D) Integration

Usually, in ICs, transistors are created in a single layer i.e. in 2D. Three dimensional integration proposes that, transistors will be formed in two or more layers, so that, more number of modules can be accommodated in small space and thus, long lateral interconnect could be avoided [5].

This technique in effect implies a whole new fabrication process, that will be difficult to implement since the foundry will be complicated and costly. Again, incorporation of more than four layers would be impractical. Finally, transistors of upper layers will find difficulties in heat dissipation process. For these reasons, this scheme has not received much attention yet.

#### **1.2.2** Optical Interconnect

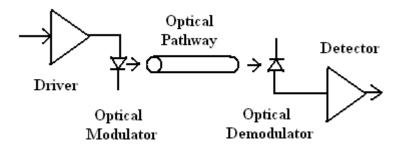

Optical interconnect could be one of the possible solutions [6]. Concept of this technique is depicted in Fig. 1.1. Merits of this approach are- several THz of bandwidth will be available in optical carrier signal and optical propagation velocity is much higher than the signal propagation velocity of electrical interconnects. In fact, optical interconnect could be the next generation interconnects unanimously, if was not for the following demerits:

Figure 1.1: Transceiver architecture of the Optical Interconnect

Although, the optical bandwidth is enormous, but the limitation would be imposed by the slower transmitter, modulator, demodulator and receiver circuitry. Next, incorporation of active pathway in chip is difficult, transceiver circuits would be power hungry and space consuming, above all, it could not be fabricated without complex and costly III-V foundry. Still, peoples are working to make the process feasible [6].

#### 1.2.3 RF/Wireless Interconnect

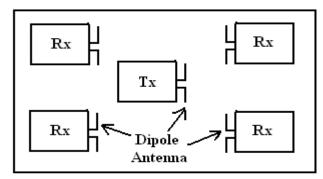

RF and wireless interconnect is relatively a latest idea that is getting attention in literature as one of the promising savior of speed limitation problem of the interconnects in future generation high speed ICs [7]. This technique will be using on-chip integrated antennas for intra-chip and inter-chip wireless data transmission at high speed [8-9]. A block diagram is shown in Fig. 1.2, where a transmitter (Tx) is transmitting clock signal and four receiver (Rx) modules are receiving. [7] used this scheme for high speed clock distribution.

Tx: Transmitter & Rx: Receiver

Figure 1.2: Block diagram of a typical RF/Wireless Interconnect

In this work, we chose this method of data transmission because of several other advantages those will be discussed in the next section.

#### 1.3 Why do we prefer RF/Wireless Interconnect

RF/Wireless interconnect will exchange data wirelessly by means of RF signal. That is why, unlike optical interconnect, it will not require complex fabrication process like those for active guiding medium or for III-V device on silicon chip. This will make the transceiver compact and cheaper. Power dissipation will be within reasonable limit as well.

Next, similar to optical interconnect; bandwidth of this scheme is limited only by the delays associated with the transceiver circuits, not by the channel itself. So, it has inherent capability of supporting multiplexing and multiple access topologies like FDMA and CDMA, which might enhance its data transmission ability by manifolds. Interference, crosstalk etc. will also reduce dramatically.

Several other achievements, such as, low power spectral density i.e. low interference, wider bandwidth, simple transceiver architecture, thus viable to be fully integrated on silicon chip and so on, will be annexed if UWB (Ultra Wide Band) communication technique is adopted [10-11].

Therefore, to us, this simpler methodology could be the future generation high speed interconnects for ICs, if it gets proper attention and research.

#### 1.4 Current State of the Problem

First of the challenges in this arena was to design fully integrated on-chip transmitter-receiver antenna pair for RF/Wireless interconnect system, when the proposition was in its embryonic state in 1990's. Design of some good antenna pairs can be found in [8-9]. They also demonstrated the feasibility and competence of those integrated antennas on silicon chip. There were other works like [5], [13] who studied the merits and demerits of this technique.

Later, peoples were interested in UWB transceiver architecture for these kind of short distance communication due to its innate advantages discussed earlier. [10-11] and [14-16] studied the signal and system in depth. They also proposed a few feasible communication and transceiver topologies. [17-21] are the recent works in this field who investigated signal propagation loss, leakage loss, interference, fading, scattering, BER etc.

But, complete integrated RF/Wireless interconnects or UWB RF circuits designed especially for these kinds of on-chip wireless interconnect system are yet to appear in literature. The best that can be found is- distribution of periodic signal like monolithic clock within ICs, such as that in [7]. Those designs are inapplicable for random data streams. Apparently, incorporation of RF circuitry in those systems is still to be. Receiver front ends for such wireless applications are designed in [22-23], but are partial. In fact, a complete on-chip wireless interconnects system with UWB transmission has not showed up yet. Therefore, this is our opportunity to design them to help the system incarnate.

#### 1.5 Thesis Overview

Designing a series of high frequency circuits with short channel devices is very difficult because of low trans-conductance per unit current of the transistors, low quality factors of the energy storage elements, short channel effects, parasitic elements, matching issues to name a few. In this thesis, a few RF circuits will be designed in IBM 90 nm CMOS process. So, being involved with short channel devices, all the aforementioned difficulties can be expected to be present.

At first, a square law up-conversion mixer will be designed for the transmitter with improved matching technique which will elevate the lower frequency signal, to K-frequency band (above 20GHz). This frequency up-lifted TR-UWB signal will be transmitted and subsequently will be received by a pair of on-chip integrated antenna. The system will be optimized so that the signal strength at the receiving antenna is well above the minimum detection level.

Then a low noise amplifier (LNA) will be designed and will be optimized in terms of power gain, noise figure, power consumption and at the same time in terms of area by reducing the number of on-chip inductors- those are major area occupying elements in silicon chips.

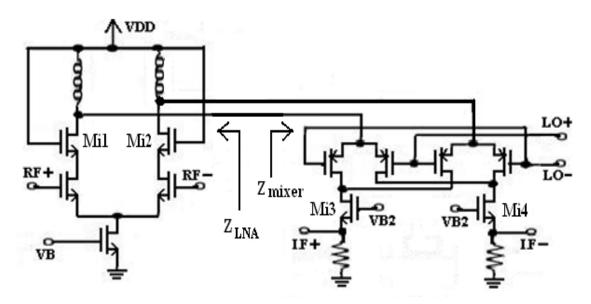

Next, A direct conversion folded mixer will be annexed to the LNA. Both the current pushed and voltage fed folded mixers will be simulated and their features will be evaluated. An inter-stage matching will be incorporated to merge the LNA with mixer that will help warding off using separate LNA and mixer. Fruition of this clever technique will be less power, low noise, reduced number of on-chip inductors e.g. saving of chip area, simpler architecture, thus better reliability and so forth. The system will be characterized in frequency domain, as well as from linearity standpoint and then time domain simulation will be invoked to confirm the successful detection of transmitted 5gbps bit streams by BPSK and DPSK.

The system will be re-designed to detect TR-UWB pulses. A new TR-UWB modulation technique will be proposed for the case when the digital circuits of transmitter and receiver will be slow to process excessive high speed data streams. A comparator will be designed as well to enrich the detected binary signals and thus for retrieving the transmitted information bits.

Circuits will be designed in HSPICE, fully integrated in IBM 90nm CMOS technology e.g. no external circuit elements and then will be assembled in Cadence Spectre for complete chip level simulation. After optimizing the system up to satisfactory level, layout will be drawn for estimating the area budget of the system on chip.

#### 1.6 Layout of the Thesis

This thesis will consist of **Eight** chapters. **Chapter 1** introduced the topic, mentioning the challenges and problems of the next generation ULSI technology, what are the techniques under research to remain in the technology roadmap, what are their pros and cons etc. This chapter also discussed what was the motivations in preferring on-chip wireless interconnect with UWB communication technique. An overview of the literature was presented to give an idea about the current state of the art. And lastly, the objective and methodology of this thesis work was outlined.

Chapter 2 will present the transceiver architecture which is to be implemented. This chapter will discuss on how the UWB signals will be generated, how the digital signal will be modulated, what are the issues involved in transmitting those signals through the silicon channel, how the received signal will be amplified, how they will be demodulated etc. The benefits and shortcomings of the scheme will also be included in this chapter.

Chapter 3 will explain the design of a square law up-conversion mixer after mentioning why it is needed in the transmitter. This chapter will show the design steps in detail that will include an improved input-matching technique which makes this circuit superior comparing to the other mixers of same topology of literature. Time domain response of the circuit will be demonstrated after characterizing the circuit thoroughly.

**Chapter 4** will discuss on designing the low noise amplifier (LNA) for the receiver. After mentioning the design objectives, this chapter will describe how the LNA could be optimized in terms of gain, power dissipation, input-output matching and space requirement. What features had to sacrifice in return will also be noted in this chapter. Layout of the LNA will be included to find out the area requirement.

Chapter 5 will describe the design of fully integrated direct conversion mixer. This chapter will mention what types of mixers are available in the literature, why they need to be optimized before being used in this application and then, will explain how those limitations were addressed in this work. After that, two types of feeding technique to the mixer, namely- current pushed and voltage fed, will be analyzed, their relative merits will be compared and then the mixer will be merged with the LNA designed in chapter 4. Thus the receiver front end will consist of a single circuit, which will perform the functions of both LNA and Mixer. This circuit will be optimized in frequency domain as well as in time domain. Finally, the circuit will be used to detect 2gbps bpsk and dpsk signals. Layout of the circuit will also be given.

**Chapter 6** will demonstrate how the receiver front end of chapter 5 was redesigned to detect the UWB signal successfully. A new technique will be incorporated in the circuit that will help avoiding otherwise bulky and power hungry circuits of the state of the art. This circuit will be used to detect the UWB transmitted signal and will be compared with the ideal scenario depicted in chapter 2. Then, a new TR-UWB modulation method will be introduced in response to a practical difficulty. Merits and demerits of the

circuit and the modulation technique will be investigated. At last, area budget of this receiver front end will be estimated from the layout.

**Chapter 7** will be comprised of the design of a CMOS comparator for the regeneration of high speed digital bit streams, detected in chapter 6. The circuit will be explained and its performance will be evaluated. This chapter will discuss on a basic limitation of designing such circuits in modern sub-micron CMOS technologies like IBM 90 nm Process- that was the foundry used throughout this work.

**Chapter 8** will conclude the thesis work summarizing and evaluating them judiciously. Suggestions for the future works required to finish the design of complete UWB on-chip wireless transceiver will also be included in this chapter.

#### CHAPTER 2

# UWB ON-CHIP WIRELESS TRANCEIVER ARCHITECTURE

#### 2.1 Bright Sides of the UWB Communication

Merits of the UWB communication was mentioned briefly in previous chapter. First, its large bandwidth can support data transmission in very high speed. From time domain standpoint-larger the bandwidth, shorter the pulse duration. That means, more data can be transmitted over the same period of time using these sharper pulses. This represents the main idea of the high speed communication, since pulse width has to be briefest possible if highest possible communication speed is to attain. However, excessively large bandwidth can not be obtained because of the practical issues related to the transceiver circuits.

Secondly, power spectral density (psd) of a signal reduces as its bandwidth increases, because the signal power is distributed over the whole bandwidth. That is why; psd of the UWB signal is very low and so is less likely to interfere with other communication channels. Thus provision for multiplexing and multiple access such as FDMA or CDMA is ensured. Also, the effect of multipath fading, colored noise etc. can be expected to be minimum. Moreover, this scheme is especially suitable for these kinds of short distance communication, because the low psd signal will not be able to travel much longer out of the chip and will not interfere with the regular terrestrial communication signal, which would violate the FCC (Federal Communications Commission) rules.

Third, as the UWB signals themselves are of high frequency, they do not need the assistance of any other high frequency carrier for modulation. So, modulation techniques of the UWB signals are easier. In fact, UWB communication is sometimes referred as carrier less communication. These short duration pulses can be modulated using simpler

techniques like PAM (Pulse Amplitude Modulation), PPM (Pulse Position Modulation), OOK (On Off Keying) etc [10-11], [14], [16]. However, in our application, we would prefer TR-UWB (Transmitted Reference- UWB) modulation method, where at least a couple of pulses will be transmitted for each bit- one will serve as the reference pulse for synchronization, no other information, while the other will carry the information about the bit i.e. '1' or '0'. So, no bulky and power hungry synchronizing circuits like PLL (Phase Locked Loop) will be needed. In other words, the system will be self synchronized [15].

Lastly, the transceiver architecture will be simplest possible, as there is no need for synchronization, carrier generation i.e. local oscillator, frequency up or down conversion etc. Again, simple modulator in turn implies a simple de-modulator. All that will be needed in the receiver is a simple correlator, consisting of only a few circuitries. There will be a number of achievements in return- reliability, easy design, less power, limited footprint etc. are a few of them. In fact, design of high frequency circuits is always troublesome and this simple architecture will save us from designing too much of them. Next section presents such a transceiver system which enjoys almost all the benefits mentioned above.

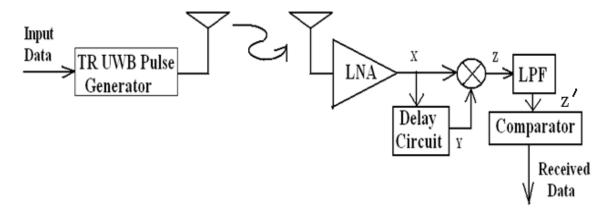

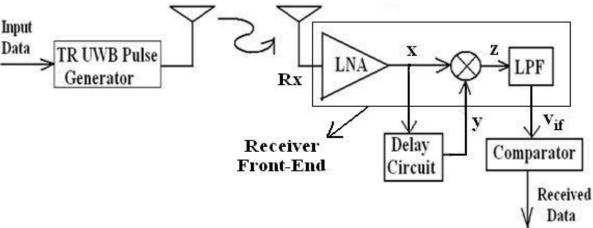

#### 2.2 The On-Chip UWB Wireless Transceiver Architecture

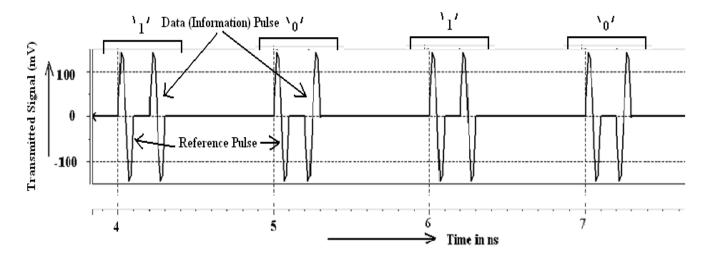

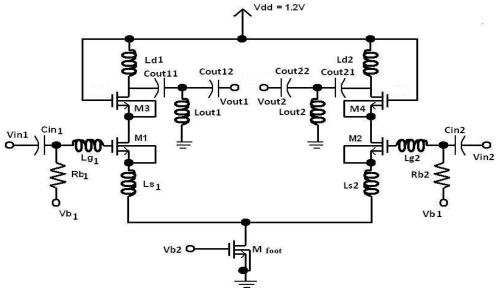

Block diagram of the on-chip UWB wireless transceiver is given in Fig. 2.1 and the transmitted TR-UWB signal is shown in Fig. 2.2.

Figure 2.1: Block diagram of the on-chip UWB wireless transceiver

Figure 2.2: Transmitted TR-UWB Signal

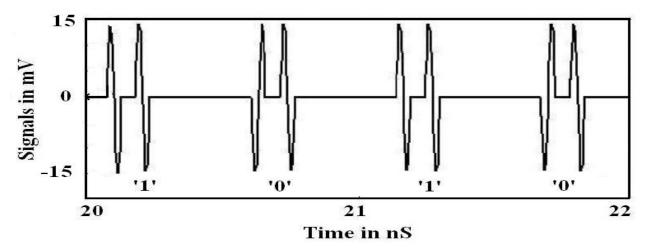

In Fig. 2.2, the transmitted TR-UWB signal consists of a couple of pulses for each bit. The leading pulses are always in the same phase, known as reference pulse that is required for synchronization, will be described later. The trailing pulse is the information signal, because it is in the same phase or out of phase with respect to the reference pulse, denoting '1' and 'o' respectively.

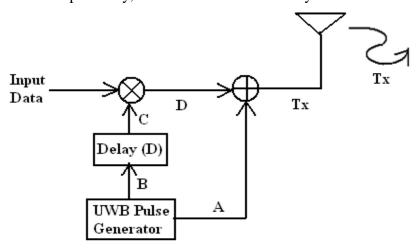

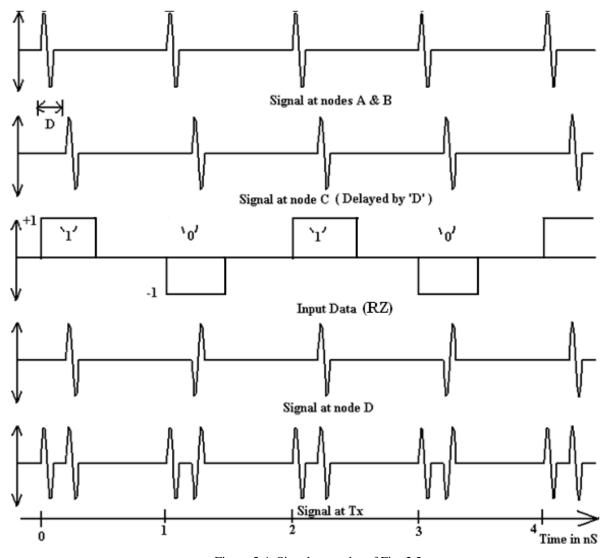

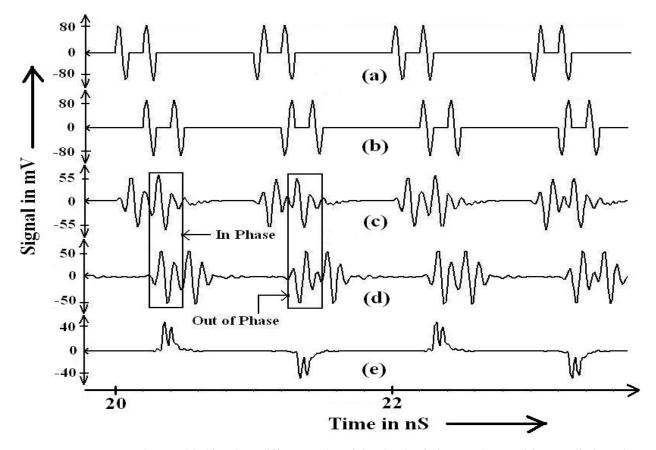

Now, in Fig. 2.1, the transmitter is necessarily a TR-UWB pulse generator, that will generate streams of TR-UWB pulses depending on the input data. Its internal structure can be shown like that in Fig. 2.3 and the corresponding signals at all the nodes are given in Fig. 2.4. Those figures are self explanatory, so let us avoid unnecessary details.

Figure 2.3: Internal block diagram of the TR-UWB pulse generator

Figure 2.4: Signals at nodes of Fig. 2.3

However, instead of using separate pulse generator, delay element, multiplier and adder as can be found in Fig. 2.3, the whole transmitter circuit can be designed only by a single mixed signal circuit, where the input will be digital bit streams and the output will be TR-UWB pulses of Fig. 2.2. Such one can be found in [24].

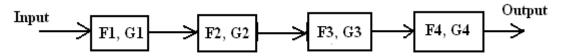

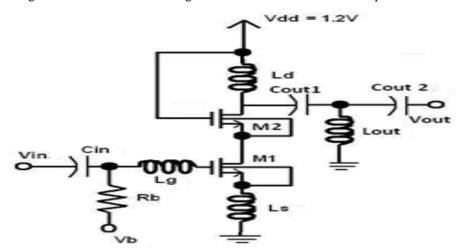

Now, the signal received by the receiving antenna will have to be amplified, because it will experience much attenuation on its way through the silicon channel. This is the job of the low noise amplifier (LNA). LNA, being the first element of the receiver,

plays a very important role on the overall performance of the receiver, because according to Frii's formula, overall noise figure of any receiver like that of Fig. 2.5 is given by:

$$F_{total} = F_1 + \frac{F_2 - 1}{G_1} + \frac{F_3 - 1}{G_1 G_2} + \frac{F_4 - 1}{G_1 G_2 G_3} + \dots$$

2.1

Where, 'F' and 'G' are the noise factor and the gain of the corresponding blocks.

Figure 2.5: Block diagram of a typical receiver.

Usually, the first blocks of the receivers are an LNA. So,  $F_1$ = $F_{LNA}$  and  $G_1$ = $G_{LNA}$  are the noise factor and the gain of the LNA. In that case, (2.1) reduces to:

$$F_{receiver} = F_{LNA} + \frac{(F_{rest} - 1)}{G_{LNA}}$$

2.2

Where,  $F_{rest}$  is the overall noise factor of the rest of the receiver after the LNA. Both from (2.1) and (2.2), it is clear that, total noise factor of the receiver will be minimum if  $F_{LNA}$  is minimum and  $G_{LNA}$  is maximum. This is the main reason, why LNA is one of the most vital elements in the receiver. However, designing such LNAs for high frequency UWB applications is very complicated because of other constrains such as- low transconductance per unit current of the transistors of the sub micron technologies, low quality factors of the energy storage elements, necessity of wide band input-output matching, area and power budget etc. Therefore, careful design and judicious optimization is obvious for getting a satisfactory overall performance of the receiver.

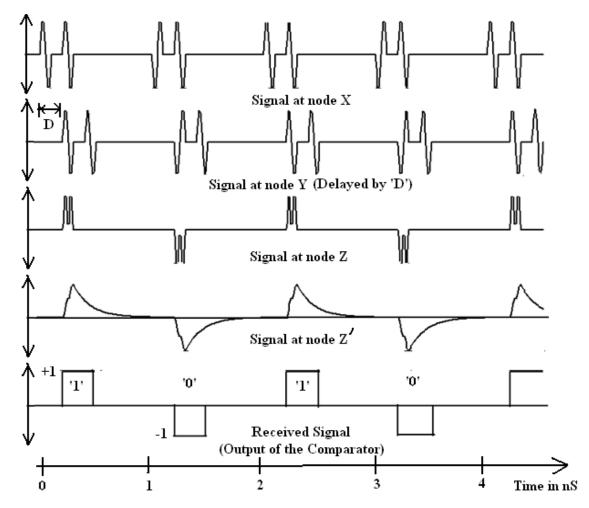

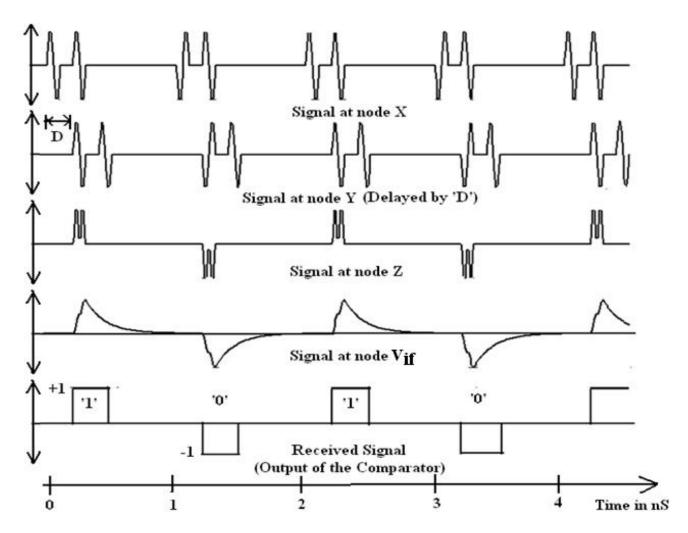

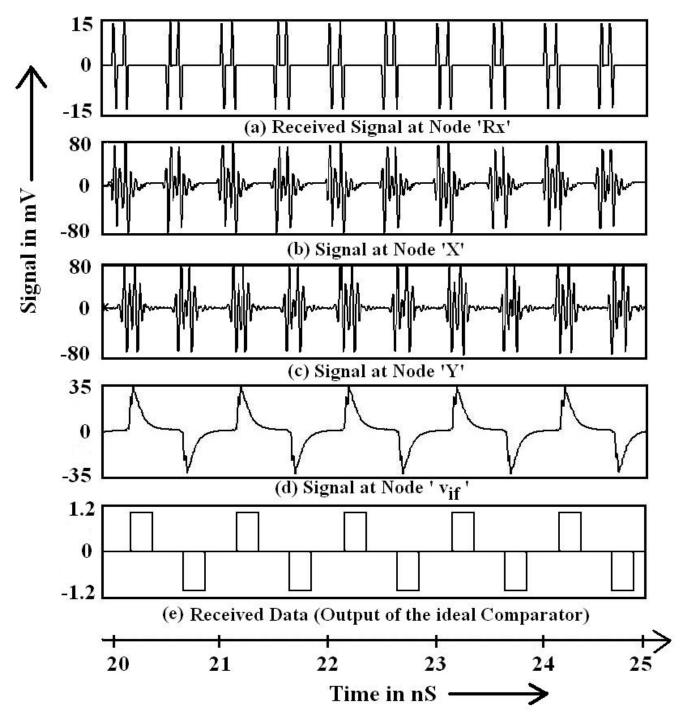

The detection of the received signal by the receiver of Fig. 2.1 is depicted in Fig. 2.6. The amplified signal of node X is delayed by 'D' in node Y and then is multiplied to get the signal like that in node Z. Signal at node Z 'is obtained after removing the high frequency components by the LPF (Low Pass Filter) i.e. after integration. Finally, the comparator regenerates the transmitted RZ bit streams and thus the input data (RZ) of Fig.

2.4 are retrieved. This is how this UWB wireless transceiver will work without the assistance of any explicit carrier or synchronizing circuit. Note that, a sample and hold circuit could be incorporated in between the LPF and comparator if the data were NRZ instead; that would sample the signal at node Z once in every bit.

Figure 2.6: Signals at the nodes of the receiver of Fig. 2.1

In this transceiver architecture, one should expect that, the high frequency UWB signal will not appear after the LPF. Knowing that, designing RF circuits is a tedious job; this system would appear especially attractive, because only a few circuits (LNA, Delay Block, Mixer and LPF) have to work with those RF signals. Nevertheless, as mentioned earlier, a complete receiver like that of Fig. 2.1 is not yet reported. In subsequent chapters, we would like to explain how we tried to design the system in circuit level to detect the transmitted data conveniently.

#### CHAPTER 3

# DESIGN OF A DOUBLE BALANCED SQUARE LAW CMOS FREQUENCY UP-CONVERSION MIXER FOR THE TRANSMITTER

When the TR-UWB pulse generator of the transmitter of Fig. 2.1 was being designed, it appeared that, involved with digital signal, more than a few GHz speed in this 90 nm technology would not be available due to the signal integrity constraints and compounded by the non-ideal effects of the devices. On the other hand, the antenna pair works in around 20 GHz that necessitated the incorporation of a frequency up-conversion mixer in between the pulse generator and the transmitting antenna.

This chapter will mention the design objectives of the up-conversion mixer for the transmitter. Then, the reason of choosing square law topology will be discussed, together with its limitations. A square law up-conversion mixer will be designed next with a new input isolation technique which will eliminate the problem of this topology in high frequency applications. The circuit will be analyzed thoroughly in frequency domain as well as in time domain. At last a transient simulation will be carried on to up-convert a 1 GHz sinusoidal signal to 20 GHz and then the signal will be transmitted and will be received to observe the performance of this part of the system.

#### 3.1 Design Objectives of the Frequency Up-Conversion Mixer

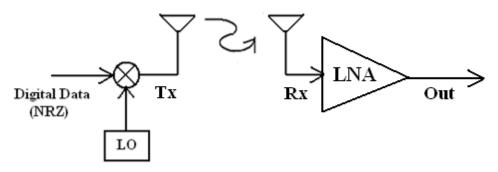

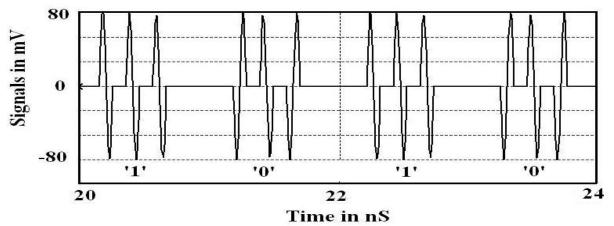

Detection of short duration pulses like TR-UWB signals introduced in previous chapter is very complicated. So let us start the design with traditional digital signal like BPSK (Binary Phase Shift Keying) or DPSK (Differential Phase Shift Keying). A BPSK transceiver is given in Fig. 3.1 and the corresponding signals are shown in Fig. 3.2, where the LO (Local Oscillator) signal is a 1 GHz Sinusoid. These figures are self explanatory.

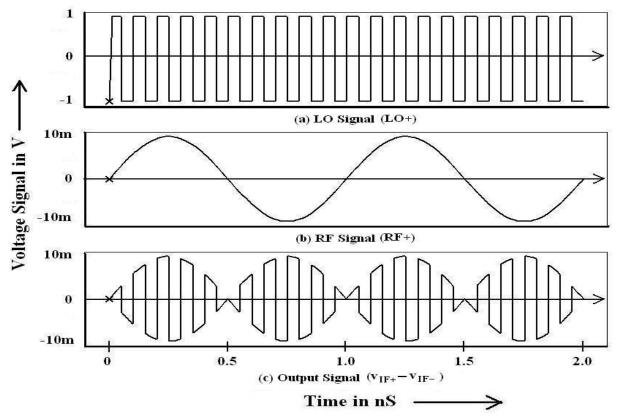

Figure 3.2: Signals at the nodes of Fig. 3.1

Since, eventually the transmitter of Fig. 3.1 will be replaced by the TR-UWB pulse generator, so the bpsk generator will be modeled as ideal whenever needed. But now, let us work with continuous '1' or '0' for further simplification at this starting level. Note that, in this case continuous '1' or '0' will be 1 GHz sinusoidal signals, but in phase with respect to the carrier for '1' or out of phase otherwise.

In summary, the frequency up-conversion mixer will up-lift the 1 GHz sinusoidal signal to about 20 GHz i.e. in K-frequency band, so that the signal frequency falls within the pass band of the on-chip integrated antenna. The mixer has to be simple, compact, low power, it should have good input and output matching, lowest possible harmonic distortion, good port to port isolation etc. Next sections will explain what the constraints in choosing proper mixer topology were and how the circuit was designed to satisfy all the design objectives mentioned.

## 3.2 Selection of the Mixer Topology

Choice of the mixer topology is very important for designing transceivers, especially for high frequency conditions. Compromises among the conversion gain, noise figure, power consumption and the linearity are involved. Though, CMOS low noise amplifiers operating in K-frequency band have received good attention, but the upconversion mixers have not got that much [25]. In fact, a design whose features match exactly to this system could not be found in literature. That is why, a fresh one was to design.

Passive mixer like that of [26] is one of the choices, but is subject to high conversion losses. Gilbert mixer is probably the most popular choice, but is usually power hungry. For example, 40.5mW and 93mW power consumptions are reported in [22] and [27] respectively. Folded mixers are familiar for their better linearity, but are noisy. 12.9 NF of such one is reported in [28].

On the other hand, square law mixers are simple, consists of least number of transistors. So, low power, less noisy and are less susceptible to harmonic problems [29], but are criticized for their poor input port isolation, which makes it less appropriate for high speed transceivers. The square law mixer designed in this thesis work incorporated a new input isolation technique that suppressed the leakage problem satisfactorily. The circuit was designed in IBM 90 nm CMOS process, whereas most of the modern MMwave circuits are implemented in costly technologies like SiGe, SOI etc. Therefore, the mixer will be cheap as well. After all, this mixer could up-convert a 1 GHz sinusoidal signal to K-frequency band successfully.

# 3.3 Description of the Circuit

If principle of superposition is applied to the square law mixer of Fig. 3.3, then it can be shown that,  $v_{IN}=V_B+v_{lo}+v_{if}$ , where  $v_{lo}$  and  $v_{if}$  are the ac components of  $v_{IN}$ . Their frequencies are same as those of  $v_{lo}$  and  $v_{if}$  respectively, but the amplitude is scaled by the corresponding impedance of the coupling capacitor, Cc. Again, when the transistor is in saturation, then

$$I_{D} = \frac{1}{2} \beta (v_{IN} - V_{t})^{2}$$

3.1

Where,  $\beta = \mu_n C_{ox} \frac{W}{L}$ ,  $\mu_n =$  mobility of the electron,  $C_{ox} =$  oxide capacitance per unit area, W and L are the width and the length of the transistor respectively,  $V_t$  it the threshold voltage.

From (3.1),

$$I_{D} = \frac{1}{2} \beta (V_{B} + v_{lo} + v_{if} - V_{t})^{2},$$

$$= \frac{1}{2} \beta (V_{B} - V_{t})^{2} + \frac{1}{2} \beta v_{lo}^{2} + \frac{1}{2} \beta v_{if}^{2}$$

$$+ \beta (V_{B} - V_{t}) v_{lo} + \beta (V_{B} - V_{t}) v_{if} + \beta v_{if} v_{lo}$$

('\(^{\frac{1}{2}}\), are dropped for simplicity)

Figure 3.3: A simple square law mixer

Now, in Fig. 3.3,  $v_{rf}$ = -I<sub>D</sub>R<sub>load</sub>, where R<sub>load</sub> is the equivalent impedance at the output of the circuit. Apparently, the circuit will work as a balanced mixer if the I<sub>D</sub> can be made equal to  $\beta v_{if}v_{lo}$  filtering other frequency components of (3.2). Advantages of the circuit would be the simplicity, low power consumption, low noise and less area requirement. However, this circuit is criticized for its lack of isolation between the input ports. Another limitation is, only one input source can have a ground reference in this circuit.

The later problem can be addressed in the circuit of Fig. 3.4, where the principle of superposition can be used again to show that, the circuit works in the similar way to that of Fig. 3.3. Still, low input isolation is the critical issue of this circuit, which makes it unattractive especially in high frequency applications.

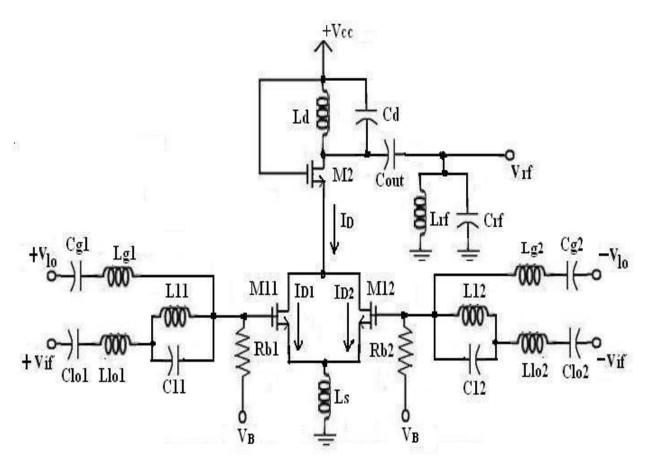

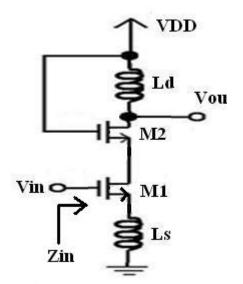

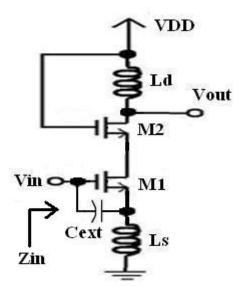

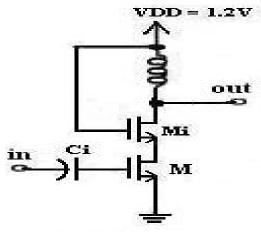

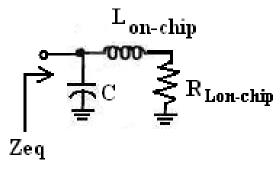

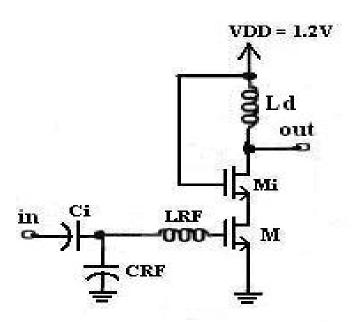

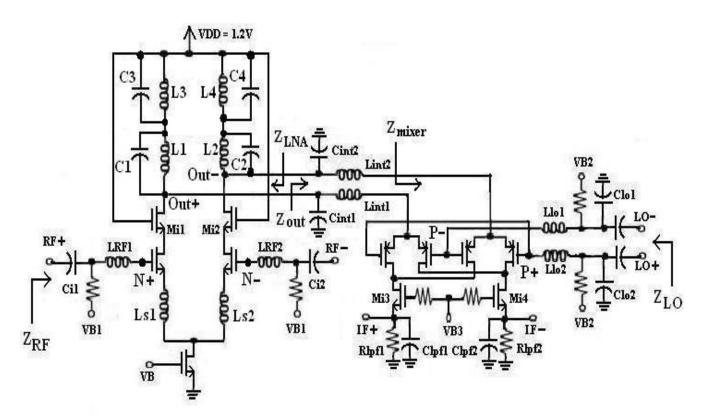

In this work, the circuit is modified further and is drawn in Fig. 3.5. This circuit was derived from the popular cascode low noise amplifier topology, where M2 improves the gain and input-output isolation. The resonant tank, consisting of L1 and C1 is designed to resonate at  $f_{lo}$ , where  $f_{lo}$  is the frequency of  $v_{lo}$ . So, it will block  $v_{lo}$  on its way to the IF input port. On the other hand,  $v_{if}$  will see different impedance through this parallel combination as long as  $f_{if} \neq f_{lo}$ , where  $f_{if}$  is the frequency of  $v_{if}$ . It will reach the gate of the transistor conveniently, but will be blocked by the series combination of Lg and Cg as they are matched for  $f_{lo}$  i.e. series resonance only at the frequency  $f_{lo}$ . In this way, the isolation between the input ports was improved. Note that, the resonant tank could be placed in the LO input path as well, with necessary modifications.

Figure 3.4: Modified circuit of a square law mixer

Figure 3.5: Square Law Mixer with improved input isolation technique

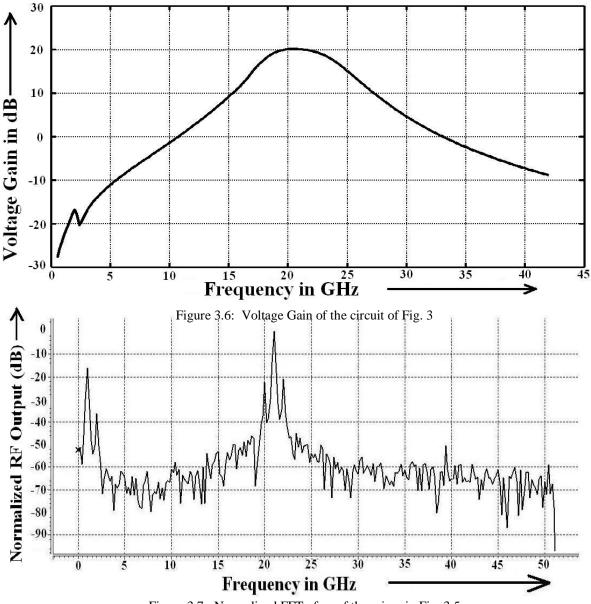

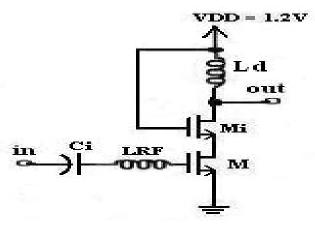

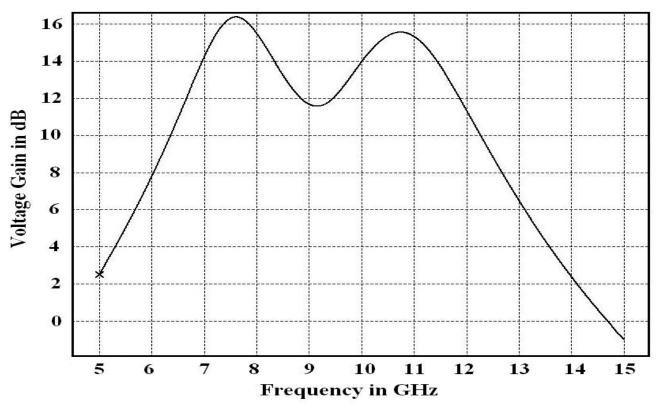

To demonstrate the performance of the mixer as a frequency up-converter, the  $f_{if}$  and  $f_{lo}$  was chosen as 1GHz and 19GHz respectively. Now, the impedance of the resonant tank is theoretically infinite for  $f_{lo}$  if L1=1nH and C1=70.2fF. But, it is about 6.3j  $\Omega$  for the  $f_{if}$ . Similarly,  $v_{lo}$  encounters zero impedance on its way to the gate of the transistor if Lg and Cg are 1.2nH and 58.5fF respectively, whereas, the  $v_{if}$  sees this series path as -2700j  $\Omega$ . In this way, a good isolation could be ensured. Rb is a large resistor, used for preventing both  $v_{if}$  and  $v_{lo}$  from bypassing the transistor gate. Clo is the dc blocking capacitor, while Llo and Ls match the input side like LNA. Input matching of LNA will be discussed in detail in next chapter. Anyways, Cd and Ld are chosen so that, the centre frequency of the gain is 19GHz, since the USB and the LSB of the  $v_{rf}$  would be 20GHz and 18GHz respectively. Voltage gain is plotted in Fig. 3.6.

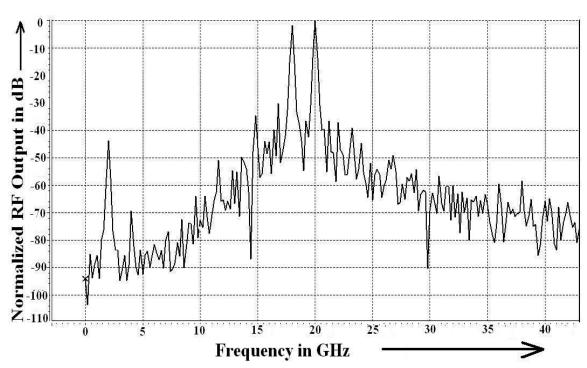

Though, all the frequency components of (3.2) except  $f_{lo}$  and  $f_{lo}\pm f_{if}$  are expected to be attenuated much because of falling out of the band, still  $v_{if}$  ( $f_{if}$ =1GHz) manifests itself significant, as seen in Fig. 3.7, because of its much higher magnitude than the  $v_{if}v_{lo}$ . For example, if the magnitude of  $v_{lo}$  and  $v_{if}$  are 1mV and 10mV respectively, then those of the USB and LSB of  $v_{if}v_{lo}$  would be  $5\mu V$  and a gain of about 1000 would be required to bring up this term in the range of mV for making it comparable to  $v_{rf}$ , which is infeasible in this high frequency. That is why;  $v_{if}$  will be quite large comparing to  $v_{if}v_{lo}$  even after experiencing out of band attenuation.

Figure 3.7: Normalized FFT of  $v_{rf}$  of the mixer in Fig. 3.5

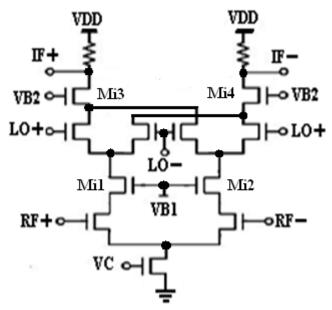

To mitigate the issue, further modification was obvious. The circuit of Fig. 3.8 is the complete double balanced square law up-conversion mixer, where the inputs were fed differentially. In this case, (3.2) can be used to show:

$$\begin{split} I_{D1} &= \frac{1}{2}\beta(V_B - V_t)^2 + \frac{1}{2}\beta{v_{lo}}^2 + \frac{1}{2}\beta{v_{if}}^2 + \beta(V_B - V_t)v_{lo} \\ &+ \beta(V_B - V_t)v_{if} + \beta{v_{if}}v_{lo} & 3.3 \\ I_{D2} &= \frac{1}{2}\beta(V_B - V_t)^2 + \frac{1}{2}\beta{v_{lo}}^2 + \frac{1}{2}\beta{v_{if}}^2 - \beta(V_B - V_t)v_{lo} \\ &- \beta(V_B - V_t)v_{if} + \beta{v_{if}}v_{lo} & 3.4 & and \\ I_D &= I_{D1} + I_{D2} \\ &= \beta(V_B - V_t)^2 + \beta{v_{lo}}^2 + \beta{v_{if}}^2 + 2\beta{v_{if}}v_{lo} & 3.5 \end{split}$$

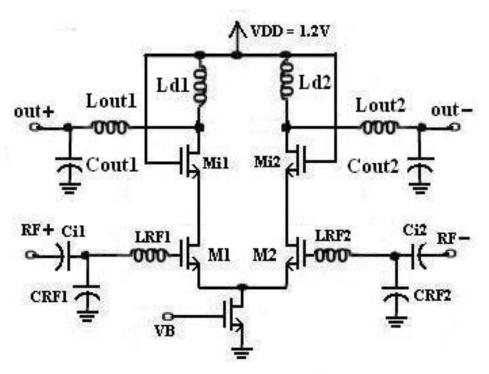

Figure 3.8: The double balanced square law CMOS up-conversion mixer

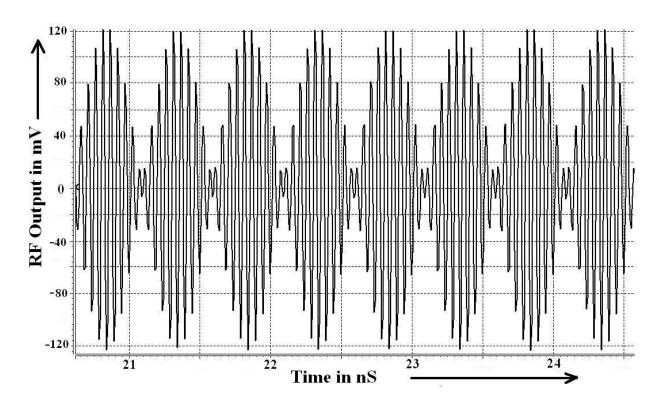

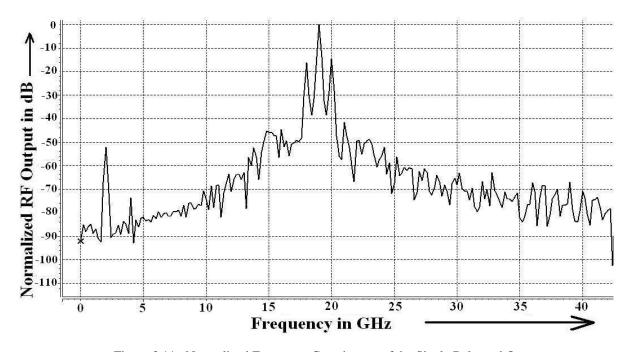

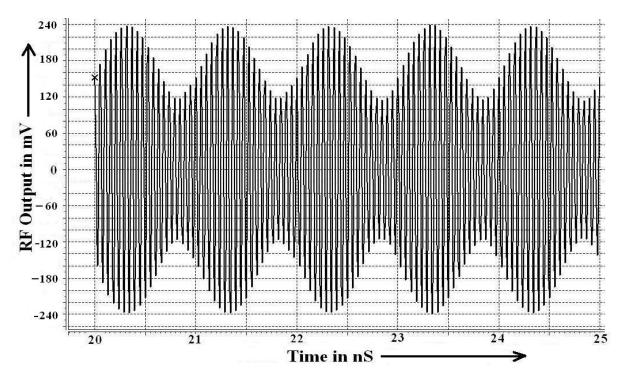

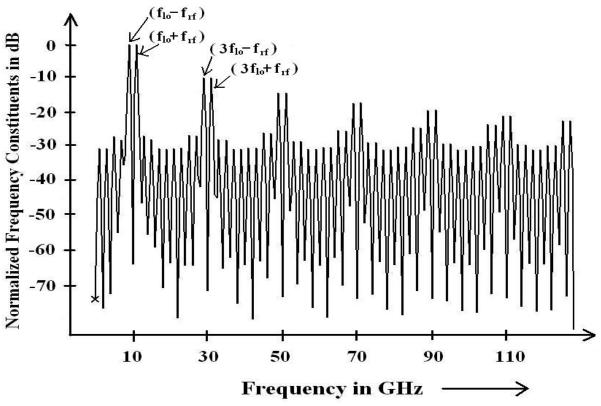

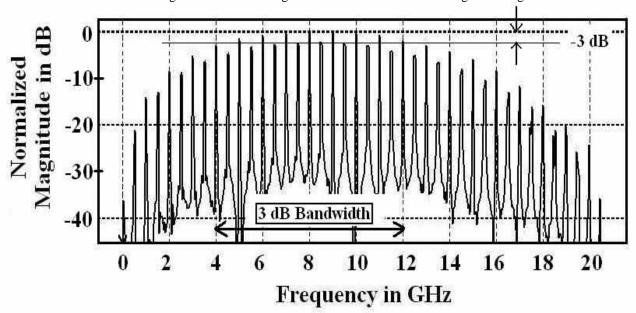

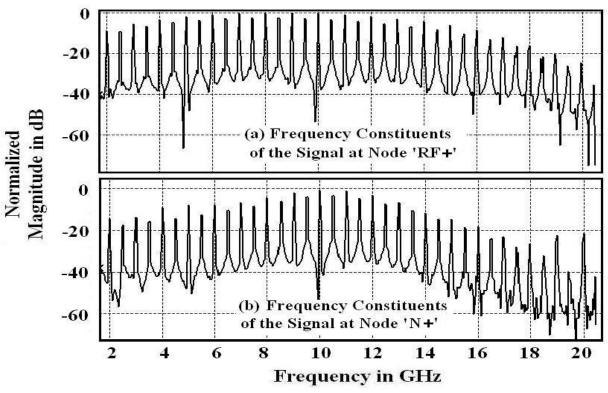

Now, in (3.5), magnitudes of  $v_{lo}^2$ ,  $v_{if}^2$  and  $v_{if}v_{lo}$  are comparable. Still all the frequency components of (3.5) except  $v_{if}v_{lo}$  falls out of the band and suffers sufficient attenuation. This is how, the circuit works as a double balanced mixer i.e no carrier signal at the output. Lrf and Crf forms the RF band pass filter and improves the SNR of  $v_{rf}$ . However, this filter could be designed to pass only the USB or the LSB to the output if desired. But, both were used in this system because, that will make the detection of binary bits easier. FFT of  $v_{rf}$  and corresponding time domain signal are shown in Fig. 3.9 and Fig. 3.10 respectively.

Use of only three transistors makes the circuit less noisy and power starved. Another advantage is, the circuit can work in single balanced mode i.e. carrier is one of the constituents of the output signal, simply when the  $-v_{lo}$  input port is grounded, because  $\beta(V_B - V_t)v_{lo}$  augments (3.5) in that case. Therefore, this square law mixer can work as well in applications where the carrier is needed. FFT and the time domain signal of the single balanced configuration are given in Fig. 3.11 and Fig. 3.12 respectively.

Figure 3.9: Normalized Frequency Constituents of the Double Balanced Output

Figure 3.10: Double Balanced Output Vs Time

Figure 3.11: Normalized Frequency Constituents of the Single Balanced Output

Figure 3.12: Single Balanced Output Vs Time

# 3.4 Other Simulated Responses

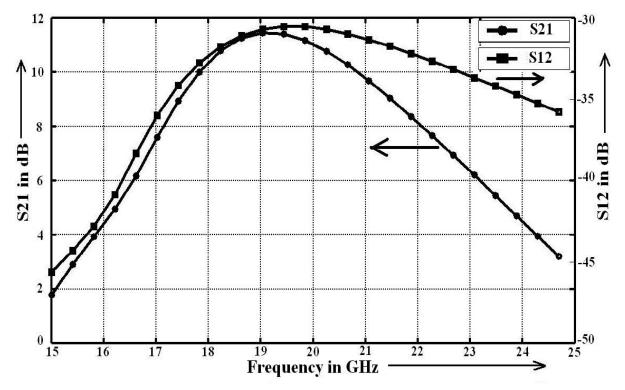

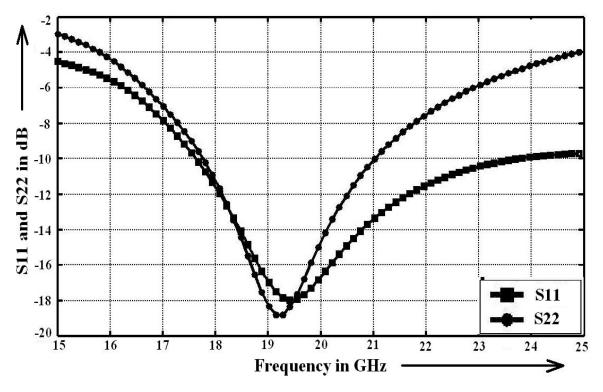

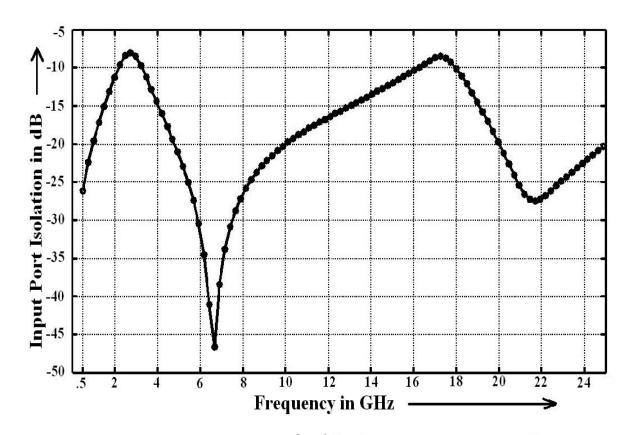

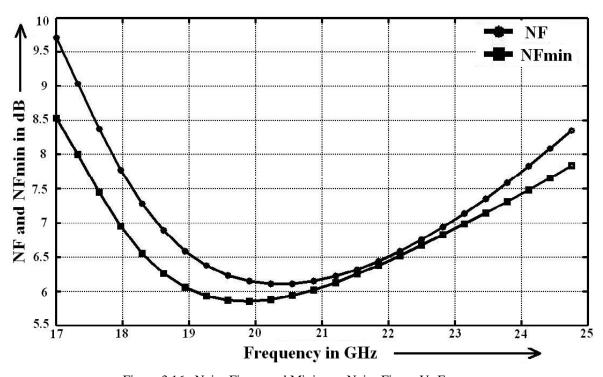

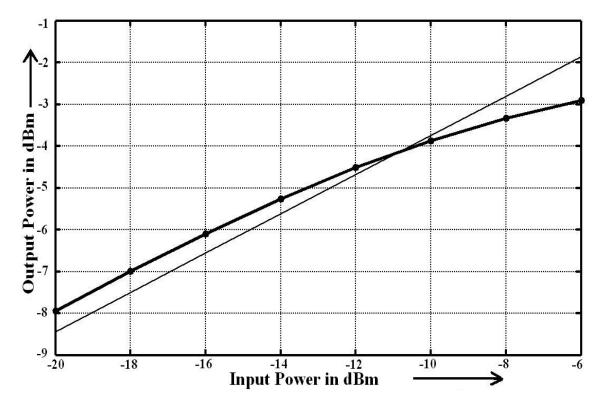

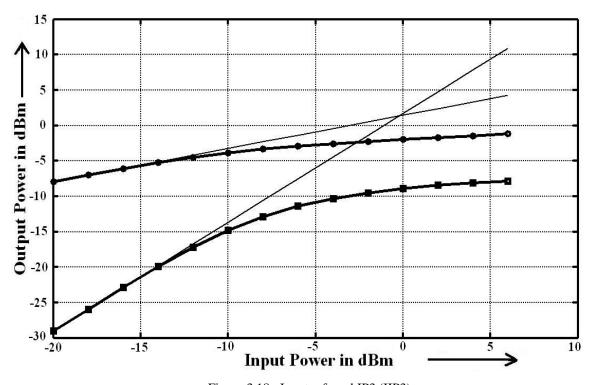

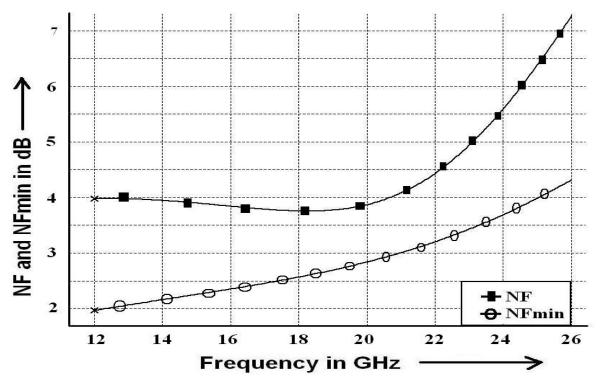

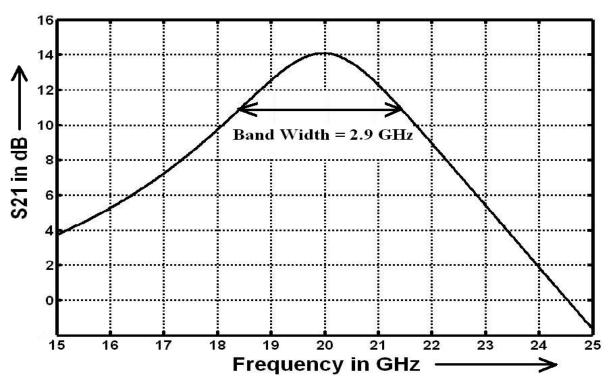

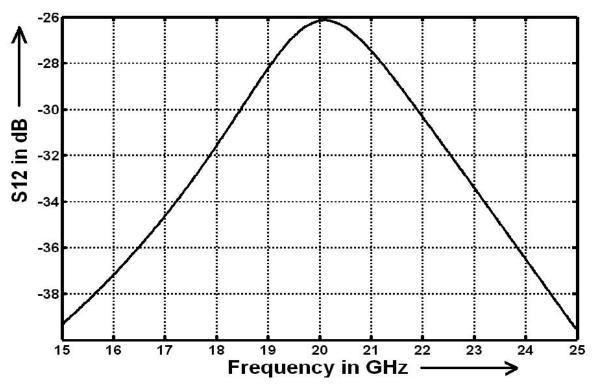

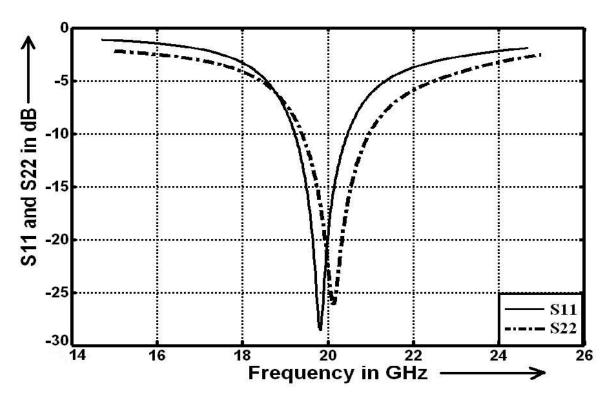

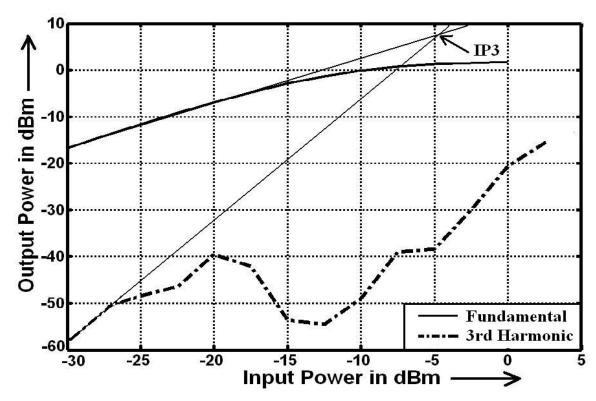

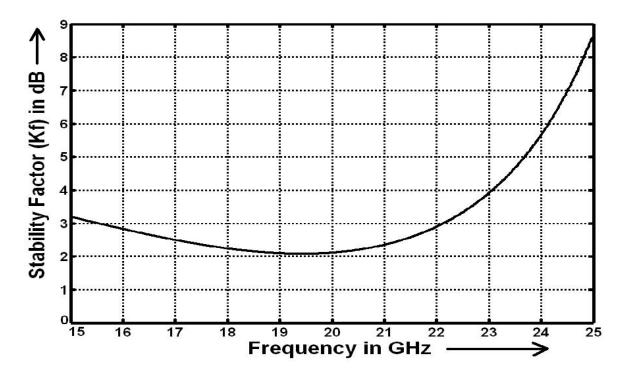

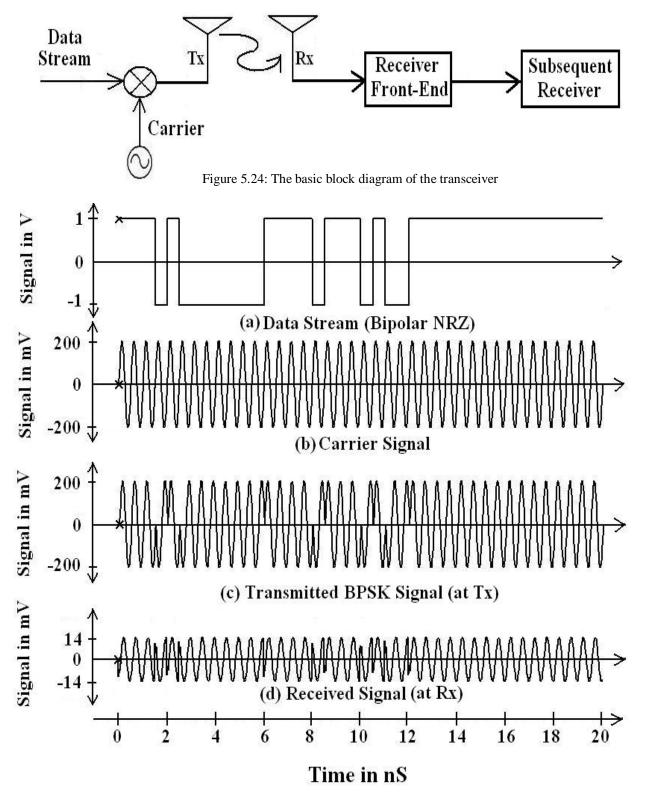

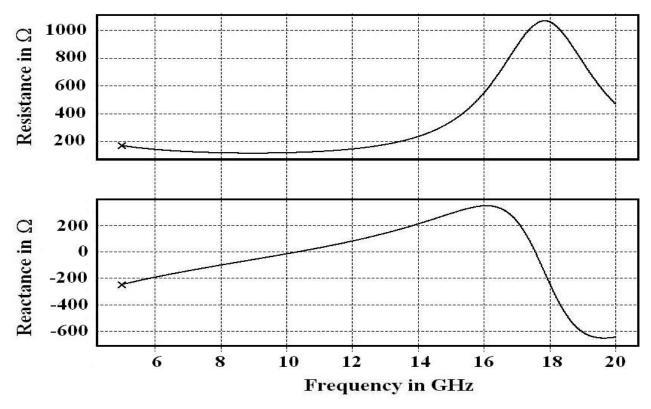

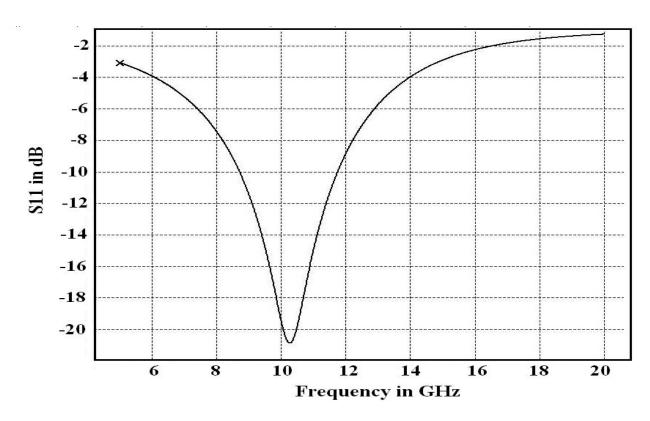

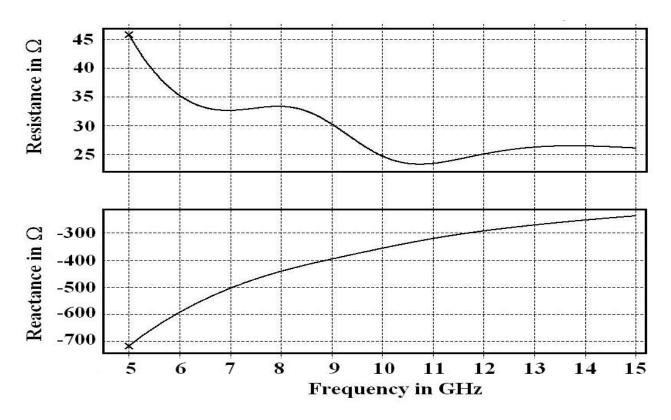

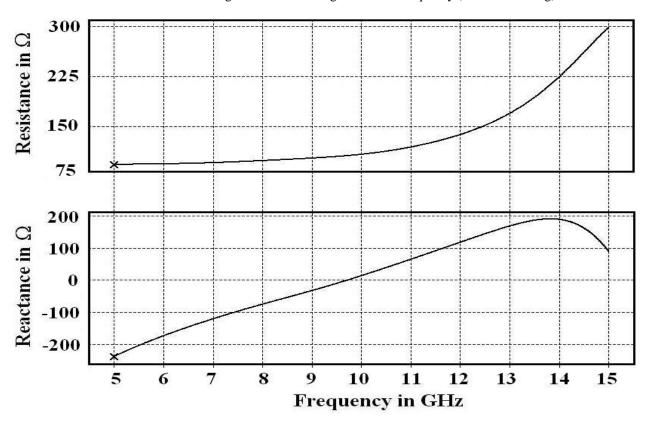

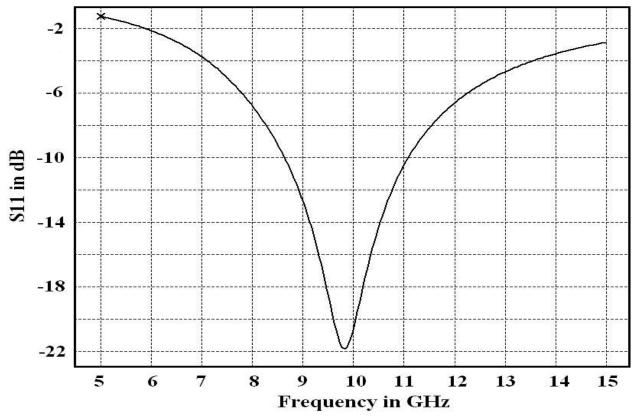

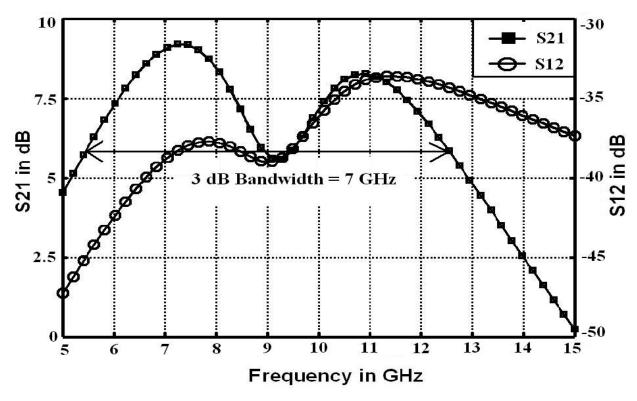

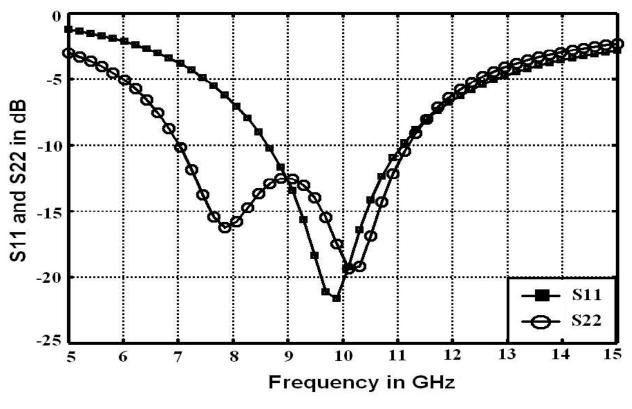

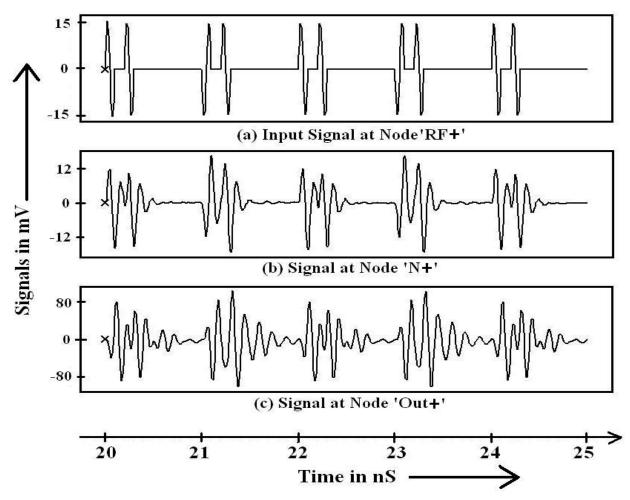

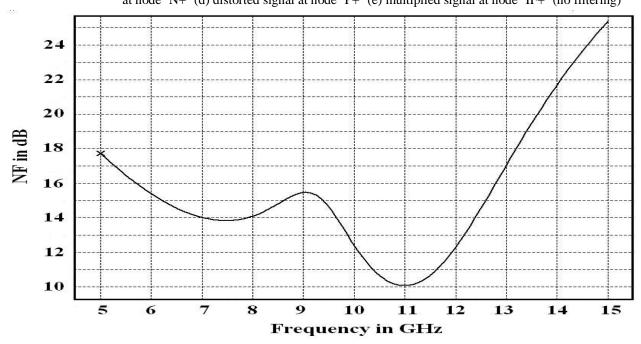

The mixer was designed in IBM 90nm CMOS process, fully integrated i.e. no off-chip circuit component, and was simulated in HSPICE. A 1GHz signal was up converted by a 19GHz carrier. This RF circuit was matched for  $50\Omega$  system. The RF filter at the output was designed to pass both the sidebands. The simulated responses exhibit a conversion gain (S21) of 11.4dB from the LO to the RF port and the reverse isolation (S12) is -30.5dB. They are plotted in Fig. 3.13. Input-Output matching parameters (S11 and S22) are depicted in Fig. 3.14 and are -18dB and -18.8dB respectively. LO to IF port isolation is shown in Fig. 3.15 and is less than -15dB in the input frequencies of interest ( $f_{if}$  and  $f_{lo}$  in this case), which is quite high for a square law mixer. Noise figure of the mixer is 6.1dB and is plotted in Fig. 3.16 together with the minimum noise figure. Input referred 1dB compression point and the IIP3 are -10.8dBm and about 0dBm respectively. They are respectively in Fig. 3.17 and in Fig. 3.18.

Figure 3.13: S21 and S12 Vs Frequency

Figure 3.14: S11 and S22 Vs Frequency

Figure 3.15: Input Isolation Vs Frequency

Figure 3.16: Noise Figure and Minimum Noise Figure Vs Frequency

Figure 3.17: Input referred 1dB Compression Point

Figure 3.18: Input referred IP3 (IIP3)

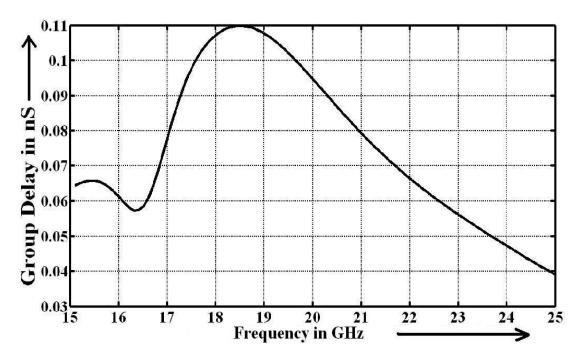

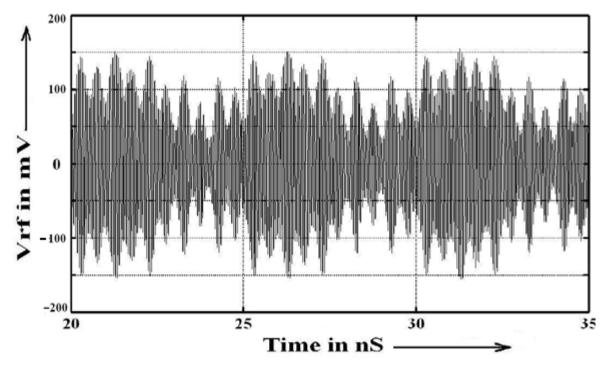

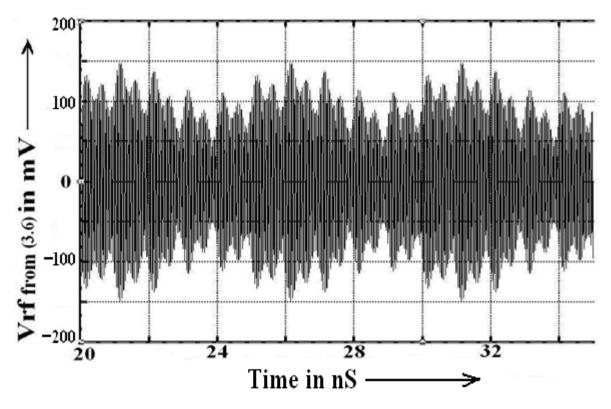

Group delay of the mixer is shown in Fig. 3.19 and it varies from .07 nS to .11 nS within the operating band. Time period relative to the centre frequency (19GHz) is .053 nS. So, group delay variation is about 75.5% ( $\frac{0.11-0.07}{0.053}$ X100%) with respect to the centre frequency. This <100% group delay ensures that, there will be no Inter Symbol Interference due to the dispersion if the mixer is employed in digital applications. Moreover, the variation of the group delay, as can be seen in Fig. 3.19, is almost symmetric with respect to the centre frequency. That is why  $f_{lo}$ +  $f_{if}$  and  $f_{lo}$ -  $f_{if}$  can be expected to experience almost same delay on their way to the output, resulting in very low distortion. To demonstrate this issue, the mixer was fed by a three tones IF input, i.e.  $v_{if}$  = $A_1 \sin(2\pi f_1 t) + A_2 \sin(2\pi f_2 t) + A_3 \sin(2\pi f_3 t)$ , where  $f_1$ ,  $f_2$  and  $f_3$  are 1, 2 and 0.2 GHz respectively. The corresponding RF output can be found in Fig. 3.20, where the mixer was in single balanced mode. To compare with, Fig. 3.21 plots:

$$V_{rf} = Ac[1 + A_1 \sin(2\pi f_1 t) + A_2 \sin(2\pi f_2 t) + A_3 \sin(2\pi f_3 t)] \sin(2\pi f_1 t)$$

3.6

using MATLAB, where,  $f_{lo}$ =19GHz. As, there is no group delay variation, thus no distortion in (3.6), so the resemblance between Fig. 3.20 and Fig. 3.21 justifies the aforementioned argument.

Figure 3.19: Group Delay Vs Frequency

Figure 3.20: RF Output for the three tone input signal

Figure 3.21: Ideal RF Output from (3.6) Vs Time

The circuit consumes only 9.25mW power from a 1.2V power supply. Therefore, commitments of this simple square law mixer are quite lucrative comparing to the state of the art. The design was accepted in 17 th IEEE International Conference on Electronics, Circuits and Systems (ICECS 2010), Athens, Greece, December 12-15, 2010 [30].

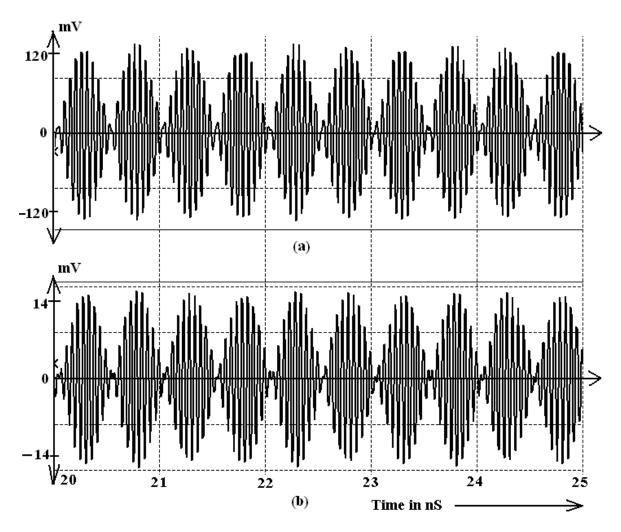

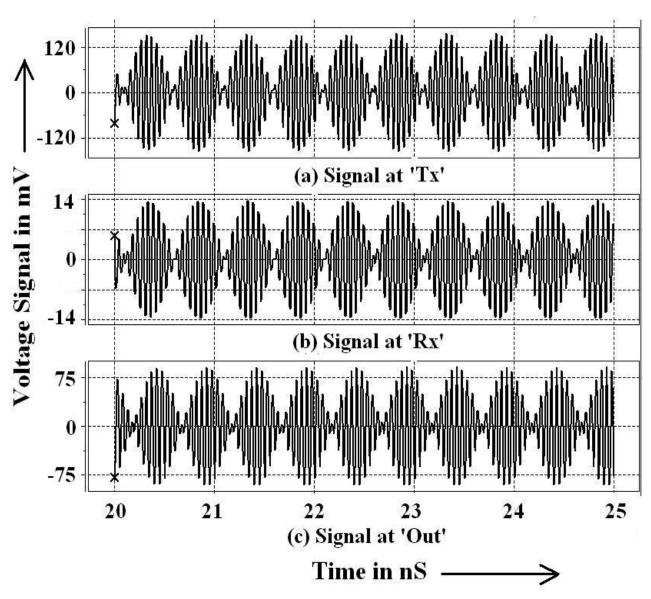

Lastly, the double balanced signal of Fig. 3.10 was transmitted and received by the on-chip antenna pair. The simulated responses can be found in Fig. 3.22. The signal experienced about -18 dB attenuation on its way through the wireless channel. Negligible distortion of the received signal indicates that, the signal frequencies matched well with the transmission bandwidth of the antenna and thus, optimum performance was obtained.

Figure 3.22: (a) Transmitted signal of Fig. 3.10 (b) Received signal

A suitable mixer topology was chosen in this chapter considering the design requirements and also its limitations were identified. The needs for employing an upconversion mixer were mentioned as well. Then, a 1 to 20 GHz square law CMOS upconversion mixer was designed with new input isolation technique to get rid of its problem of signal leakage in the input ports. No off-chip circuit components were used in designing this circuit i.e. the mixer was fully integrated. The circuit was analysed thoroughly and was showed that, it can work both as balanced and un-balanced mixer. Its simulated response appeared lucrative. At last, a 20 GHz DSB signal was created up-converting a 1 GHz sinusoidal signal by this mixer. That signal was transmitted and was received successfully by an on-chip integrated antenna pair. Thus, the performance of this section of the system was verified.

However, this circuit was matched for sinusoidal signal. So, wideband matching would be needed for using it in UWB applications. But, at the end no up-converter was required in the system, because high frequency UWB pulse generator appeared afterward that made frequency up-conversion unnecessary.

### CHAPTER 4

# DESIGN OF A 20 GHz DIFFERENTIAL LOW NOISE AMPLIFIER

Since a differential dipole antenna pair will be used in this wireless interconnect system, so the following LNA has to be differential as well. Differential circuits usually perform better than their single ended counterpart. They are more immune to power supply and environmental noises. They also have high common mode rejection ratio (CMRR) that makes them robust against common mode noise. But differential circuits are criticized for their power and space requirement.

In this chapter, at first the design of a 21 GHz source degenerated differential LNA will be described. This circuit was designed in our BSc thesis [31]. Its limitations will be discussed after a through analysis of the circuit. Then a 20 GHz differential LNA will be designed without any source degeneration. The merits and demerits of the circuit will be analyzed in detail. The circuit will be optimized for this particular application. Simulated responses of the circuit will be presented together with the layout. Lastly, the time domain performance of the LNA will be verified by observing how the received DSB signal of previous chapter, shown in Fig. 3.22, is handled by this amplifier.

# **4.1** Description of A 21 GHz Source-Degenerated Differential Low Noise Amplifier

Schematic diagram of a 21 GHz source degenerated differential low noise amplifier is given in Fig. 4.1. The reason of choosing a common source structure was to achieve a better noise performance, because in this structure the input is fed to the gate of a MOSFET. So the input side is free from substrate noise that would have picked up if it was fed to any diffusion body e.g. to the source of the driving transistor if it were a common gate structure.

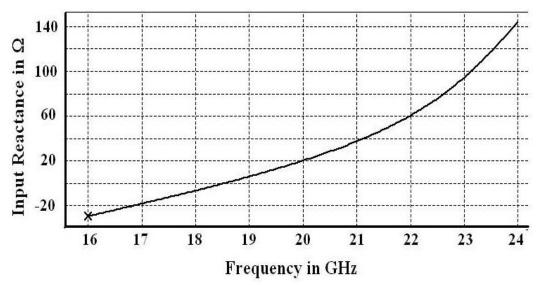

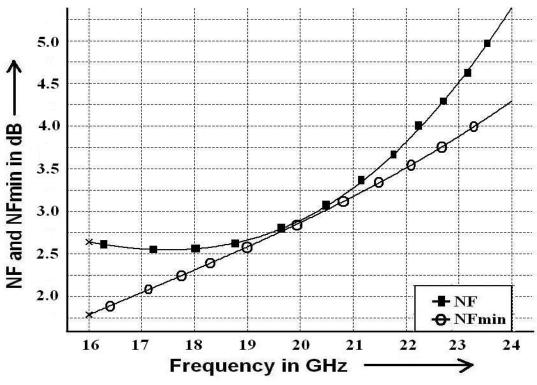

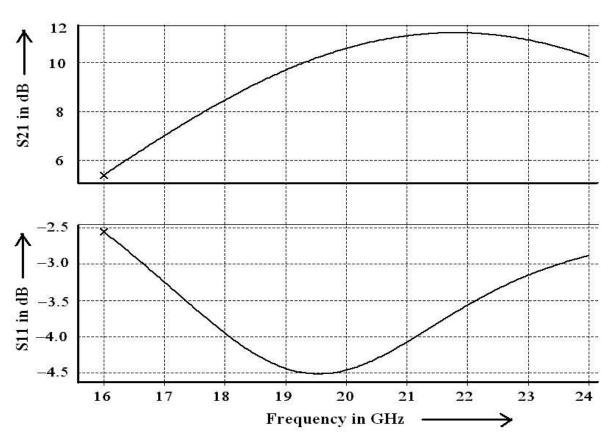

### 4.1.1 Design of the Source-Degenerated Differential LNA