### COMPACT MODELING OF DIRECT TUNNELING GATE-CURRENT CONSIDERING QUANTUM MECHANICAL CORRECTIONS IN NANO-SCALE MOSFETS

A thesis submitted for the partial fulfillment of the requirement of the degree of Master of Science in Electrical and Electronic Engineering

By

Muhammed Ahosan-ul-Karim

Department of Electrical and Electronic Engineering

Bangladesh University of Engineering and Technology

Dhaka-1000

February, 2010

# **Contents**

| Ce       | ertification                                                                                                                                                                                                                                                                                                                                                                                                    | v                                                             |  |  |

|----------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------|--|--|

| De       | vi                                                                                                                                                                                                                                                                                                                                                                                                              |                                                               |  |  |

| Ac       | vii                                                                                                                                                                                                                                                                                                                                                                                                             |                                                               |  |  |

| De       | viii                                                                                                                                                                                                                                                                                                                                                                                                            |                                                               |  |  |

| Abstract |                                                                                                                                                                                                                                                                                                                                                                                                                 |                                                               |  |  |

| 1        | Introduction 1.1 Literature Review 1.2 Objective of This Work 1.3 Organization of The Thesis                                                                                                                                                                                                                                                                                                                    | 1<br>2<br>6<br>6                                              |  |  |

| 2        | Direct Tunneling Gate Current and Compact Model  2.1 MOS Structure  2.2 Direct Tunneling Gate Current  2.3 Self Consistent Simulator  2.3.1 Basic Model  2.3.2 Green's Function Formalism  2.3.3 Coupling Schrödinger and Poisson's Equati  2.3.4 Calculation of DT Gate Current  2.4 Compact Model  2.4.1 Calculation of $N_{ij}$ 2.4.2 Calculation of $\Gamma_{ij}$ 2.4.3 Calculation of DT Gate Current, $J$ | 7<br>7<br>8<br>9<br>10<br>11<br>on 17<br>18<br>19<br>20<br>23 |  |  |

| 3        | Results and Discussions 3.1 Eigen States, $E_{ij}$ 3.2 Concentration of the Inversion Electrons, $N_{ij}$ 3.3 Imaginary Part of Eigen Energy, $\Gamma_{ij}$ 3.4 Direct Tunneling Gate Current, $J$                                                                                                                                                                                                              | 29<br>29<br>34<br>40<br>44                                    |  |  |

| 4        | Conclusion 4.1 Summary 4.2 Suggestion for Future Works                                                                                                                                                                                                                                                                                                                                                          | <b>50</b><br>50<br>51                                         |  |  |

# **List of Figures**

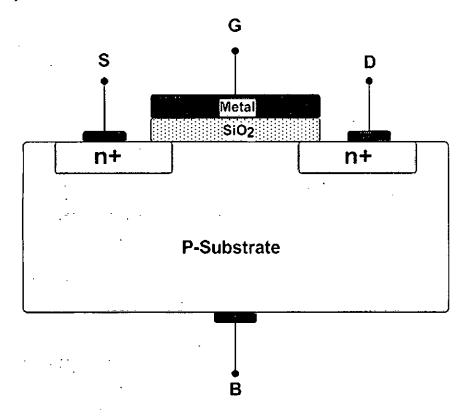

| 2.1 | Cross section of an enhancement-type n-MOSFE1.                                                 | ð  |

|-----|------------------------------------------------------------------------------------------------|----|

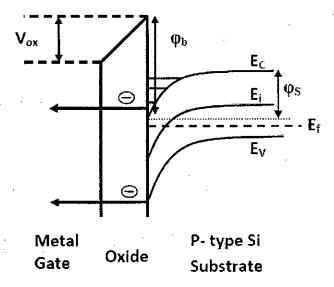

| 2.2 | A schematic of the band diagram of a Metal/oxide/p-Si                                          |    |

|     | MOS structure showing the electron quantization effect in                                      |    |

|     | the substrate and direct electron tunneling from the substrate                                 |    |

|     | inversion layer to the gate.                                                                   | 9  |

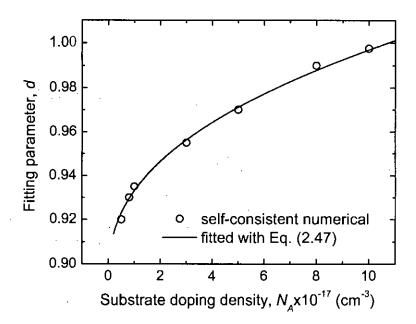

| 2.3 | Fitting of parameter $d$ with variation of $N_A$                                               | 23 |

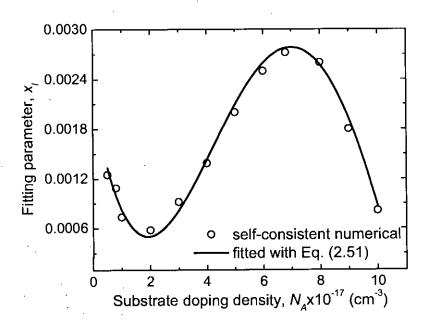

| 2.4 | Fitting of parameter $x_l$ with variation of $N_A$                                             | 25 |

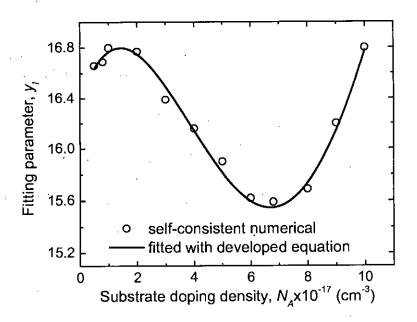

| 2.5 | Fitting of parameter $y_i$ with variation of $N_A$                                             | 25 |

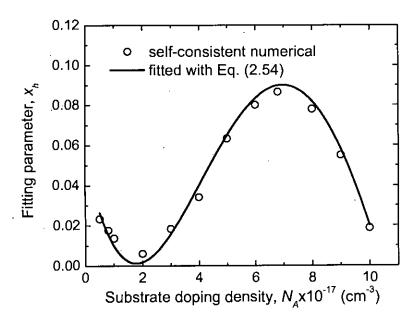

| 2.6 | Fitting of parameter $x_h$ with variation of $N_A$                                             | 27 |

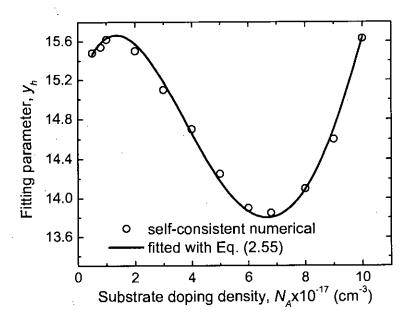

| 2.7 | Fitting of parameter $y_h$ with variation of $N_A$                                             | 27 |

| ۷., | Titling of parameter yn with variation of the                                                  |    |

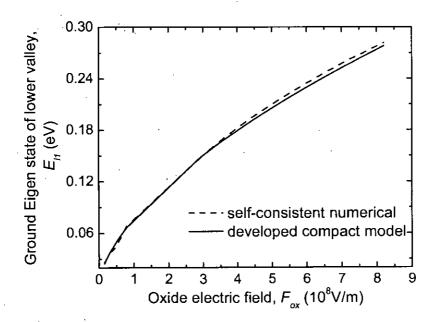

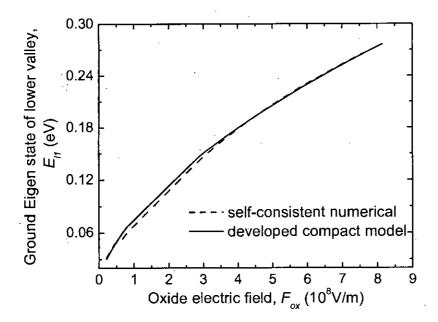

| 3.1 | Ground Eigen state of lower valley vs. Oxide electric field for                                |    |

| ·   | MOSFET with Al/SiO <sub>2</sub> /Si structure. Here, $N_A = 5 \times 10^{16}$ cm <sup>-3</sup> |    |

|     | and $T_{ox} = 1.46 \text{ nm}$ .                                                               | 30 |

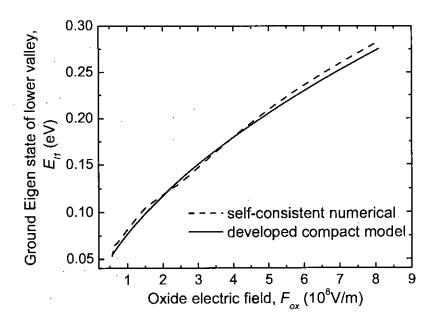

| 3.2 | Ground Eigen state of lower valley vs. Oxide electric field for                                |    |

|     | MOSFET with Al/SiO <sub>2</sub> /Si structure. Here, $N_A = 10^{17}$ cm <sup>-3</sup> and      |    |

|     | $T_{ox} = 1.46 \text{ nm}.$                                                                    | 30 |

| 3.3 | Ground Eigen state of lower valley vs. Oxide electric field for                                |    |

|     | MOSFET with Al/SiO <sub>2</sub> /Si structure. Here, $N_A = 10^{18}$ cm <sup>-3</sup> and      |    |

|     | $T_{ox} = 1.46 \text{ nm}.$                                                                    | 31 |

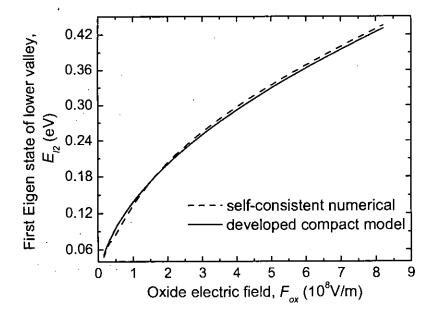

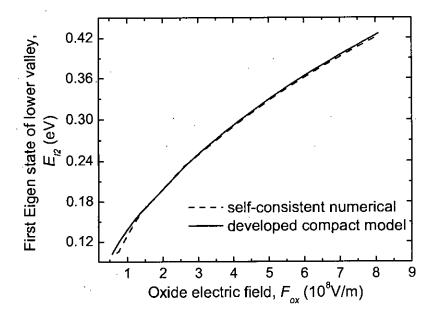

| 3.4 | First Eigen state of lower valley vs. Oxide electric field for                                 |    |

|     | MOSFET with Al/SiO <sub>2</sub> /Si structure. Here, $N_A = 5 \times 10^{16}$ cm <sup>-3</sup> |    |

|     | and $T_{ox} = 1.46$ nm.                                                                        | 31 |

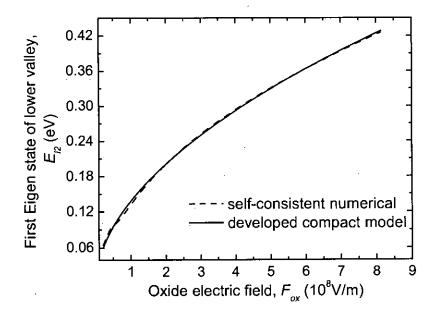

| 3.5 | First Eigen state of lower valley vs. Oxide electric field for                                 |    |

|     | MOSFET with Al/SiO <sub>2</sub> /Si structure. Here, $N_A = 10^{17}$ cm <sup>-3</sup> and      |    |

|     | $T_{ox} = 1.46 \text{ nm}.$                                                                    | 32 |

| 3.6 | First Eigen state of lower valley vs. Oxide electric field for                                 |    |

|     | MOSFET with Al/SiO <sub>2</sub> /Si structure. Here, $N_A = 10^{18}$ cm <sup>-3</sup> and      |    |

|     | $T_{ox} = 1.46 \text{ nm}.$                                                                    | 32 |

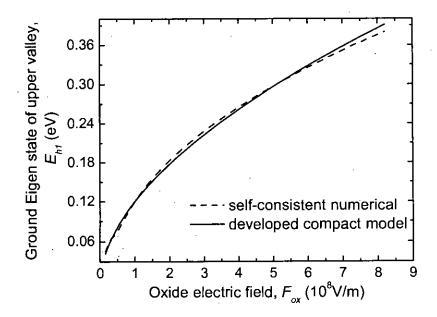

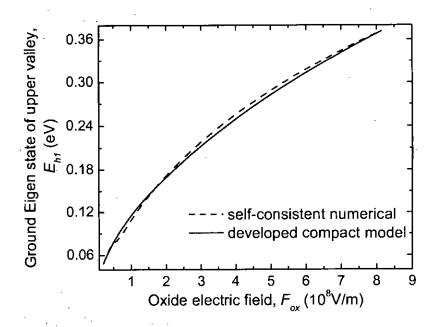

| 3.7 | Ground Eigen state of upper valley vs. Oxide electric field for                                |    |

|     | MOSFET with Al/SiO <sub>2</sub> /Si structure. Here, $N_A = 5 \times 10^{16}$ cm <sup>-3</sup> |    |

|     | and $T_{ox} = 1.46 \text{ nm}$ .                                                               | 33 |

| 3.8 | Ground Eigen state of upper valley vs. Oxide electric field for                                |    |

|     | MOSFET with Al/SiO <sub>2</sub> /Si structure. Here, $N_A = 10^{17}$ cm <sup>-3</sup> and      |    |

|     | $T_{ox} = 1.46 \text{ nm}.$                                                                    | 33 |

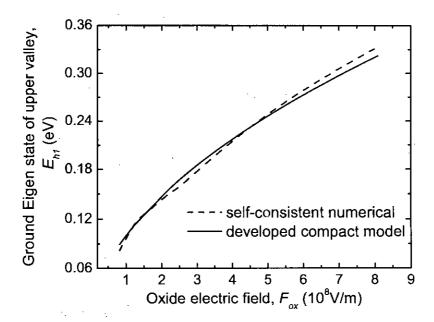

| 3.9 | Ground Eigen state of upper valley vs. Oxide electric field for                                |    |

|     | MOSFET with Al/SiO <sub>2</sub> /Si structure. Here, $N_A = 10^{18}$ cm <sup>-3</sup> and      |    |

|     | $T_{ox} = 1.46 \text{ nm}.$                                                                    | 34 |

|     | - or                                                                                           |    |

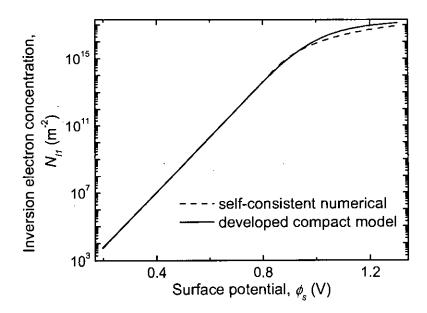

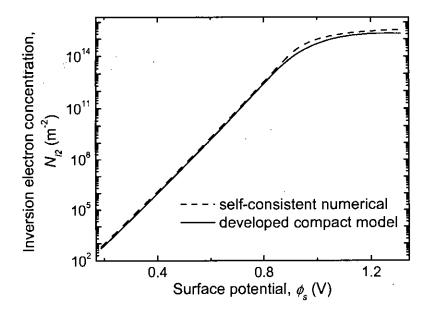

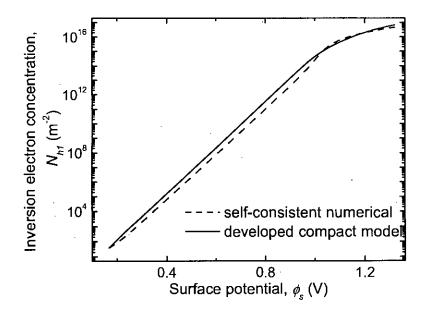

| 3.10  | Inversion electron concentration of ground state of lower valley vs. surface potential for MOSFET with Al/SiO <sub>2</sub> /Si structure.                                     | 35       |

|-------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------|

| 2 1 1 | Here, $N_A = 5 \times 10^{16} \text{ cm}^{-3}$ and $T_{ox} = 1.46 \text{ nm}$ .<br>Inversion electron concentration of ground state of lower valley                           | <b>J</b> |

| 3.11  | vs. surface potential for MOSFET with Al/SiO <sub>2</sub> /Si structure.                                                                                                      | 35       |

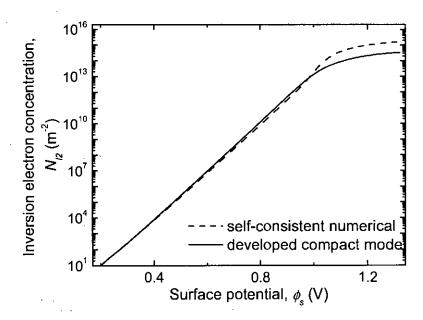

| 3.12  | Inversion electron concentration of ground state of lower valley                                                                                                              |          |

|       | vs. surface potential for MOSFET with Al/SiO <sub>2</sub> /Si structure.                                                                                                      | 26       |

|       | TIEIE. IV $\lambda = 10$ CIII WIGHTON = 1.10 MIN.                                                                                                                             | 36       |

| 3.13  | Inversion electron concentration of first eigen state of lower                                                                                                                |          |

|       | valley vs. surface potential for MOSFET with Al/SiO <sub>2</sub> /Si structure. Here, $N_A = 5 \times 10^{16}$ cm <sup>-3</sup> and $T_{ox} = 1.46$ nm.                       | 36       |

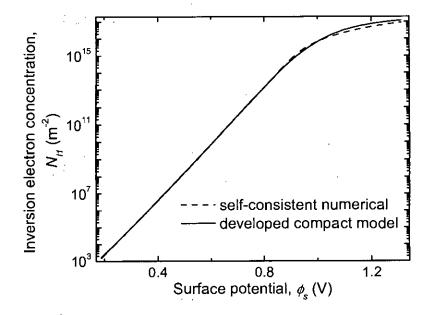

| 214   | Inversion electron concentration of first eigen state of lower                                                                                                                |          |

| 3.14  | valley vs. surface potential for MOSFET with Al/SiO <sub>2</sub> /Si                                                                                                          |          |

|       | structure. Here, $N_A = 10^{17}$ cm <sup>-3</sup> and $T_{ox} = 1.46$ nm.                                                                                                     | 37       |

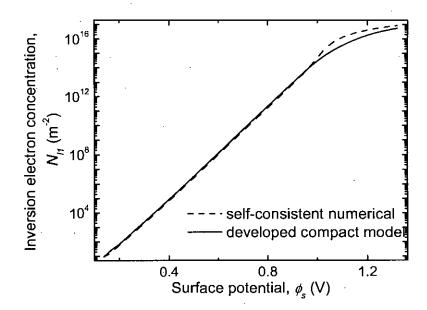

| 3 15  | Inversion electron concentration of first eigen state of lower                                                                                                                |          |

| 0.10  | valley vs. surface potential for MOSFET with Al/SiO <sub>2</sub> /Si                                                                                                          |          |

|       | structure. Here, $N_A = 10^{18} \text{ cm}^{-3}$ and $T_{ox} = 1.46 \text{ nm}$ .                                                                                             | 38       |

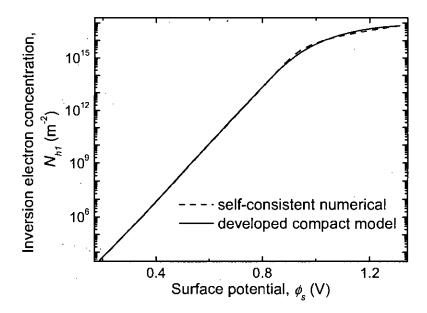

| 3.16  | Inversion electron concentration of ground state of upper valley                                                                                                              |          |

|       | vs. surface potential for MOSFET with Al/SiO <sub>2</sub> /Si structure.                                                                                                      | 38       |

|       | Here, $N_A = 5 \times 10^{16} \text{ cm}^{-3}$ and $T_{ox} = 1.46 \text{ nm}$ .                                                                                               | 30       |

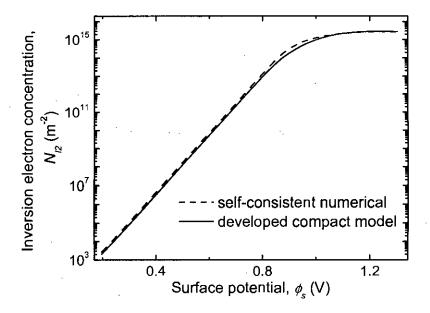

| 3.17  | Inversion electron concentration of ground state of upper valley                                                                                                              |          |

|       | vs. surface potential for MOSFET with Al/SiO <sub>2</sub> /Si structure.<br>Here, $N_A = 10^{17}$ cm <sup>-3</sup> and $T_{ox} = 1.46$ nm.                                    | 39       |

| 2 10  | Inversion electron concentration of ground state of upper valley                                                                                                              | 0,       |

| 3.10  | vs. surface potential for MOSFET with Al/SiO <sub>2</sub> /Si structure.                                                                                                      |          |

|       | Here, $N_A = 10^{18} \text{ cm}^{-3}$ and $T_{ox} = 1.46 \text{ nm}$ .                                                                                                        | 40       |

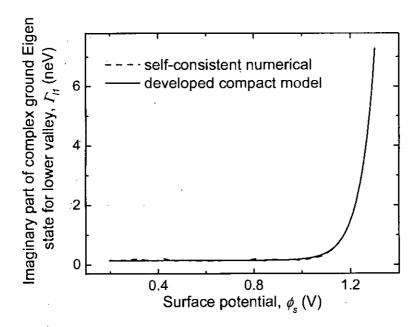

| 3.19  | Imaginary part of complex ground eigen state of lower valley vs.                                                                                                              |          |

| 0,17  | surface potential for MOSFET with Al/SiO <sub>2</sub> /Si structure. Here,                                                                                                    |          |

|       | $N_A = 5 \times 10^{16} \text{ cm}^{-3} \text{ and } T_{ox} = 1.46 \text{ nm}.$                                                                                               | 41       |

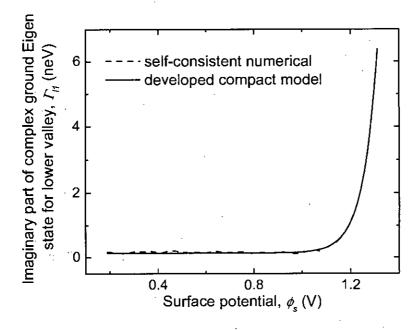

| 3.20  | Imaginary part of complex ground eigen state of lower valley vs.                                                                                                              |          |

|       | surface potential for MOSFET with Al/SiO <sub>2</sub> /Si structure. Here,                                                                                                    | 41       |

|       | $N_A = 10^{17}$ cm <sup>-3</sup> and $T_{ox} = 1.46$ nm.                                                                                                                      | 41       |

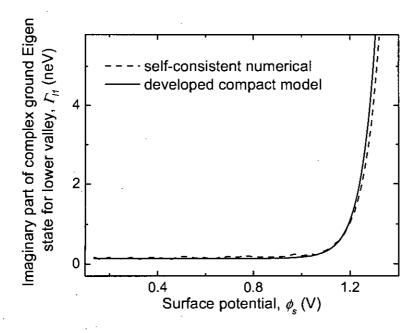

| 3.21  | Imaginary part of complex ground eigen state of lower valley vs. surface potential for MOSFET with Al/SiO <sub>2</sub> /Si structure. Here,                                   |          |

|       | surface potential for MOSPET with All SiO27 Structure. Therefore $N_A = 10^{18} \text{ cm}^{-3}$ and $T_{ox} = 1.46 \text{ nm}$ .                                             | 42       |

| 2 22  | Imaginary part of complex ground eigen state of upper valley vs.                                                                                                              |          |

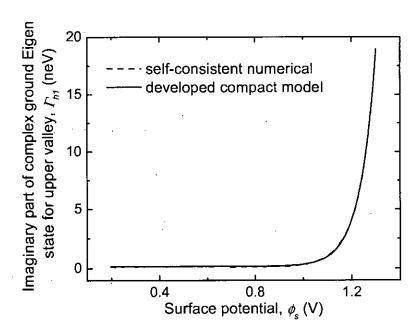

| 0.22  | surface potential for MOSFET with Al/SiO <sub>2</sub> /Si structure. Here,                                                                                                    |          |

|       | $N_A = 5 \times 10^{16} \text{ cm}^{-3}$ and $T_{ox} = 1.46 \text{ nm}$ .                                                                                                     | 43       |

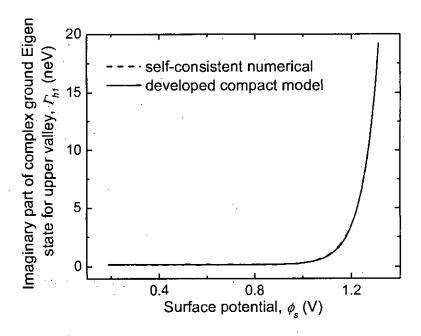

| 3.23  | Imaginary part of complex ground eigen state of upper valley vs.                                                                                                              |          |

|       | surface potential for MOSFET with Al/SiO <sub>2</sub> /Si structure. Here,                                                                                                    |          |

|       | $N_A = 10^{17} \text{ cm}^{-3} \text{ and } T_{ox} = 1.46 \text{ nm}.$                                                                                                        | 43       |

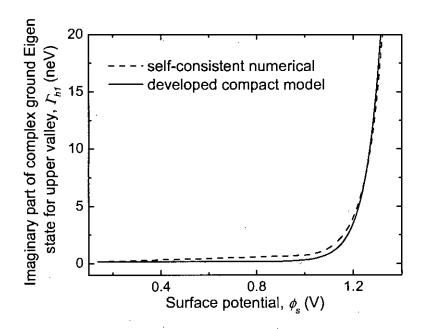

| 3.24  | Imaginary part of complex ground eigen state of upper valley vs.                                                                                                              |          |

|       | surface potential for MOSFET with Al/SiO <sub>2</sub> /Si structure. Here,                                                                                                    | 44       |

|       | $N_A = 10^{18} \text{ cm}^{-3} \text{ and } T_{ox} = 1.46 \text{ nm}.$                                                                                                        | 44       |

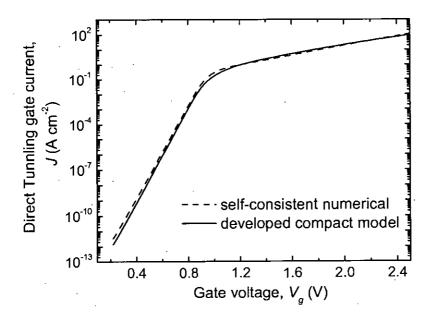

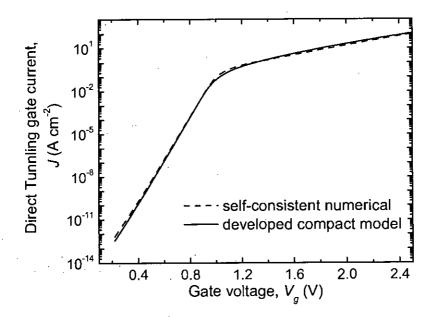

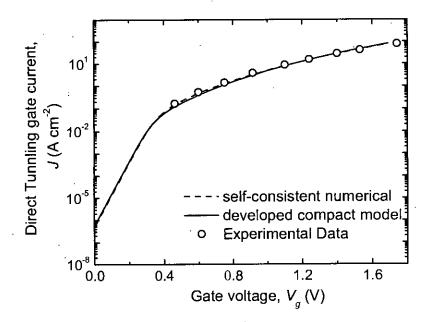

| 3.2   | Direct Tunneling gate current vs. Gate voltage for MOSFET with Al/SiO <sub>2</sub> /Si structure. Here, $N_A = 5 \times 10^{16}$ cm <sup>-3</sup> and $T_{ox} = 1.46$ nm.     | 45       |

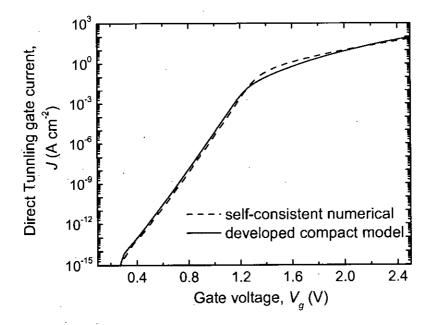

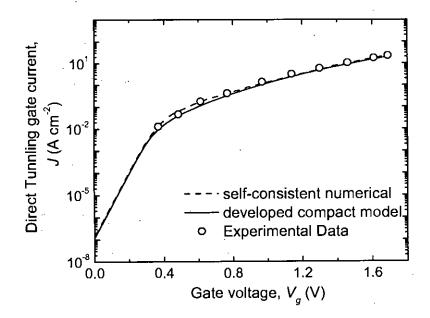

| 2.0   | Al/SiO <sub>2</sub> /Si structure. Here, $N_A = 3 \times 10^{-4}$ cm <sup>-2</sup> and $T_{ox} = 1.40$ min.  6 Direct Tunneling gate current vs. Gate voltage for MOSFET with |          |

| 3.20  | b Direct lunneling gate current vs. Gate voltage for MOSI ET With                                                                                                             | 45       |

Main of

LIST OF FIGURES

| 3.27 | Direct Tunneling gate current vs. Gate voltage for MOSFET with                                             |    |

|------|------------------------------------------------------------------------------------------------------------|----|

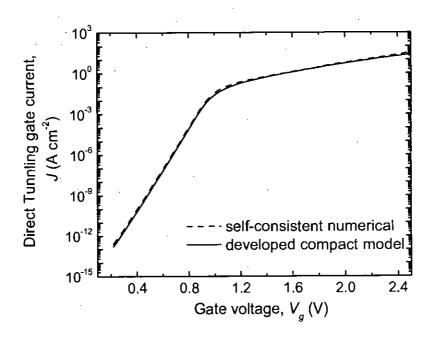

|      | Al/SiO <sub>2</sub> /Si structure. Here, $N_A = 10^{18}$ cm <sup>-3</sup> and $T_{ox} = 1.46$ nm.          | 46 |

| 3.28 | Direct Tunneling gate current vs. Gate voltage for MOSFET with                                             |    |

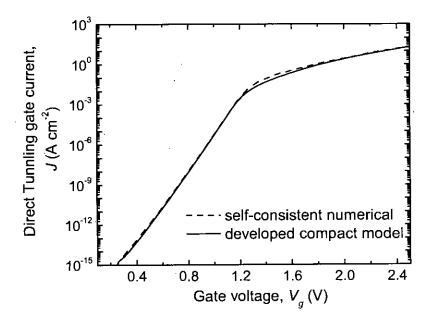

|      | Al/SiO <sub>2</sub> /Si structure. Here, $N_A = 8 \times 10^{16}$ cm <sup>-3</sup> and $T_{ox} = 1.55$ nm. | 46 |

| 3.29 | Direct Tunneling gate current vs. Gate voltage for MOSFET with                                             |    |

|      | Al/SiO <sub>2</sub> /Si structure. Here, $N_A = 8 \times 10^{17}$ cm <sup>-3</sup> and $T_{ox} = 1.55$ nm. | 47 |

| 3.30 | Direct Tunneling gate current vs. Gate voltage for MOSFET with                                             |    |

|      | Al/SiO <sub>2</sub> /Si structure. Here, $N_A = 5 \times 10^{17}$ cm <sup>-3</sup> and $T_{ox} = 1.46$ nm. | 47 |

| 3.31 | Direct Tunneling gate current vs. Gate voltage for MOSFET with                                             |    |

|      | Al/SiO <sub>2</sub> /Si structure. Here, $N_A = 5 \times 10^{17}$ cm <sup>-3</sup> and $T_{ox} = 1.55$ nm. | 48 |

| 3.32 | Direct Tunneling gate current vs. Gate voltage for MOSFET with                                             |    |

| -    | Al/SiO <sub>2</sub> /Si structure. Here, $N_A = 5 \times 10^{17}$ cm <sup>-3</sup> and $T_{ox} = 1.79$ nm. | 48 |

| 3.33 | Direct Tunneling gate current vs. Gate voltage for MOSFET with                                             |    |

|      | Al/SiO <sub>2</sub> /Si structure. Here, $N_A = 5 \times 10^{17}$ cm <sup>-3</sup> and $T_{ox} = 2$ nm.    | 49 |

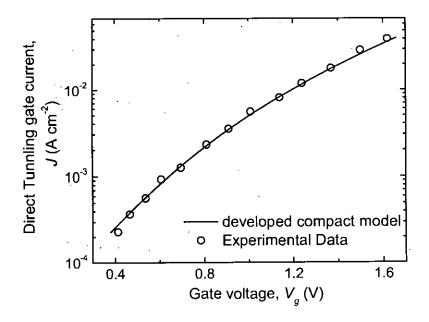

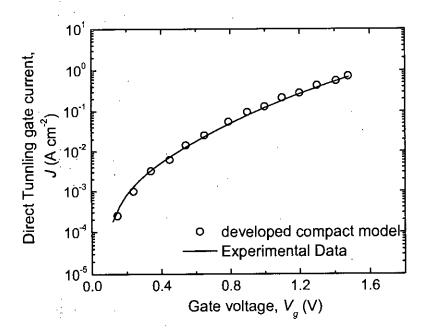

| 3.34 | Direct Tunneling gate current vs. Gate voltage for MOSFET with                                             |    |

|      | Al/SiO <sub>2</sub> /Si structure. Here, $N_A = 4.1 \times 10^{17}$ cm <sup>-3</sup> and $T_{ox}$ is taken |    |

|      | as 1.78 nm.                                                                                                | 49 |

## Certification

The thesis titled "Compact Modeling of Direct Tunneling Gate Current Considering Quantum Mechanical Corrections in Nano-Scale MOSFETs" submitted by Muhammed Ahosan-ul-Karim, Roll No.: 100706220P, Session: October, 2007, has been accepted satisfactory in partial fulfillment of the requirement for the degree of Master of Science in Electrical and Electronic Engineering on February 06, 2010.

#### **Board of Examiners**

Dr. Quazi Deen Mohd Khosru

Professor,

Department of Electrical and Electronic Engineering, Bangladesh University of Engineering and Technology, Dhaka-1000, Bangladesh.

Dr. Aminul Hoque Professor and Head,

Department of Electrical and Electronic Engineering, Bangladesh University of Engineering and Technology, Dhaka-1000, Bangladesh.

Dr. Md. Ziaur Rahman Khan

Associate Professor,

Department of Electrical and Electronic Engineering, Bangladesh University of Engineering and Technology, Dhaka-1000, Bangladesh.

Dr. M. Rezwan Khan Professor and Vice Chancellor, United International University, Dhaka-1209, Bangladesh. Chairman

Member (Ex-officio)

Member

Member (External)

# **Declaration**

It is hereby declared that this thesis or any part of it has not been submitted elsewhere for the award of any degree or diploma.

200

Muhammed Ahosan-ul-Karim

# Acknowledgements

The author would like to thank Dr. Quazi Deen Mohd Khosru, Professor, Department of Electrical and Electronic Engineering (EEE), Bangladesh University of Engineering and Technology (BUET), Dhaka, for his many fruitful suggestions and constant support during this research.

The author is also thankful to Dr. Aminul Hoque, Professor and Head, Department of Electrical and Electronic Engineering, Bangladesh University of Engineering and Technology (BUET), Dhaka, for providing his valuable time in this thesis work.

The author is grateful to all the members of the Board of Examiners for their valuable and fruitful suggestions.

The author is also thankful to all teachers, colleagues and friends for providing encouragement to complete this research work.

Dhaka, Author February, 2010

# Dedication

To My Parents

## **Abstract**

A physically based, accurate model for the direct tunneling (DT) gate current of nano-scale MOS devices considering quantum mechanical (QM) effects is developed. Effect of wave function penetration into the gate-dielectric is also taken into account. When electrons tunnel from the MOS inversion layer to the gate, the system becomes quantized with finite lifetimes of the inversion carriers. In such a system, the Eigen energies are complex quantities. The imaginary part of these complex Eigen energies,  $\Gamma$  is required to estimate the lifetimes of these states.  $\Gamma$  follows an exponential relationship with the thickness of the gate-dielectric layer even in the sub-1-nm-thickness regime. In this work, an empirical equation of  $\Gamma$  is developed as a function of surface potential,  $\phi_s$ , from a developed self-consistent numerical simulator (Schrödinger-Poisson solver) considering open boundary condition. Inversion layer electron concentration is determined using Eigen energy, calculated by modified Airy function approximation that considers wave function penetration effect. Good agreement of the developed compact model with self-consistent numerical simulator and experimental data for a wide range of substrate doping densities and oxide thicknesses states the accuracy and robustness of the developed model. Though the developed model holds good for only SiO<sub>2</sub> used as gate oxide, following the same methodology compact model of DT gate current for MOS devices with high-k gate dielectric can also 🖖 be developed.

# Chapter 1

## Introduction

Aggressive scaling of MOS devices in past decades has introduced the feature size to nanometer regime. A methodology has been given in [1] to show the scaling nature of MOS devices. As guided by the ITRS (International Technology Roadmap for Semiconductors), the scaling down has been accomplished by a decrease in gate-oxide thickness and increase in doping density. A complete scenario of scaling features of device size, oxide thickness and enhancement in doping concentration are given in ITRS [1].

Oxide current due to direct tunneling of carriers is increasingly becoming an important component of the operation of devices in nanometer scale MOS technologies [2]. The dielectric is now being scaled into a regime (<2 nm) where leakage through the gate dielectric due to direct tunneling is becoming an inevitable feature of device operation even at low operating voltages. Because of this, there is a requirement to include gate current in compact MOS models for circuit simulation. The most significant effect of gate current on the design of digital circuits is the influence that it will have on off-state power consumption [3]. In the on-state at high switching speeds, the contribution of the gate current is probably going to be small. Analog circuits however, typically use longer channel length devices and ratios of device geometries are used to achieve performance targets. As a result, compact models, which include gate current due to direct tunneling, will become of increasing importance for analog circuit design in the immediate future.

1.1 Literature Review 2

Ideally a compact model should be physically based. It should be based on technologically relevant and measurable parameters and it should include the main physical effects. In this way, it is hoped that such a model will have some predictive capability for small process changes and also give some diagnostic capability. A physical basis also helps to ensure a clear path to physical parameter extraction strategy.

However, in compact modeling the requirement for a physical basis must be traded off against the sometimes conflicting requirement of speed and simplicity. The goal of circuit simulation is to simulate large and relatively complex circuits in a reasonable time. In order to reduce computation time in compact models explicit equations in terms of the applied terminal voltages are usually used and iterative or numerical calculations are generally avoided.

Wave function penetration and quantization are the two most important phenomena for modeling ultrathin MOS devices. In this work a physically based, accurate compact model for Direct Tunneling (DT) gate current is developed considering quantum mechanical effect and incorporating wave function penetration effect.

### 1.1 Literature Review

Current scaling of metal-oxide-semiconductor field effect transistors (MOSFET) has led to the fabrication of devices in the sub-100-nm regime. In such devices, a large gate current flows due to direct tunneling (DT) of inversion carriers. This DT current is important from both device performance and characterization points of view. However, even though there are many reports concerning the effects of the gate leakage current to MOS transistor operations and numerical modeling [4–8], fewer studies have been made regarding impacts of the gate current to real circuit operations due to absence of an accurate circuit simulation model for gate tunneling current.

Hakim et al. [5] proposed an accurate and numerically stable quantum-mechanical technique with open boundary conditions to calculate the direct tunneling (DT) gate current in metal-oxide-semiconductor (MOS) structures exploiting the numerically obtained exponential dependence of imaginary part of complex eigen state,  $\Gamma$ , on the thickness of the gate-dielectric layer. They have simplified the determination of  $\Gamma$  in devices where it is too small to be calculated directly. They also showed that the MOS electrostatics, calculated self-consistently with open boundary conditions, is independent of the dielectric layer thickness provided that the other parameters remain unchanged. Utilizing these findings, a computationally efficient and numerically stable method is developed for calculating the tunneling currentgate voltage characteristics.

Using both quantum mechanical calculations for the silicon substrate and a modified WKB approximation for the transmission probability, Yang et al. [6] have presented a model for direct tunneling currents across ultra-thin gate oxides of MOS structures for electrons from the inversion layers in p-type Si substrates.

Tunneling current from MOS inversion layer was studied by Lo et al. [4]. They have showed that for the purpose of modeling tunneling characteristics of electrons exhibiting quasi two-dimensional character, the transmission probability applicable to an incident Fermi gas of free electrons is no more an acceptable concept and the well known WKB (Wentzel-Krammer-Brioullion) approximation or the numerical integration of Airy function is not valid. In their work an accurate determination of the physical oxide thickness was achieved by fitting experimentally measured capacitance-versus-voltage curves to quantum-mechanically simulated capacitance-versus-voltage results. The lifetimes of quasi-bound states and the direct tunneling current was calculated using a transverse resonant method, applicable for electromagnetic waves in a non-uniform waveguide for solving the Schrödingers equation.

1.1 Literature Review 4

Shih et al. [9] have shown the viability of WKB approximation at low biases. Tunneling rate calculations invoking the WKB approximation and the numerical solution to the effective-mass Schrodinger equation have been independently carried out in a post-processing fashion following a self-consistent Schrdinger-Poisson solver. The direct-tunneling currents calculated by these two distinct approaches have been compared with oxide thickness ranging from 1.5 to 4 nm.

Vogel et al. [10] modeled the tunneling currents for insulators with an effective oxide thickness of 2.0 nm using a numerical calculation of the WKB tunneling current. Their model was shown to agree with previously determined analytical WKB formulations of tunneling current for SiO2.

A modified WKB approximation has been proposed by Register et al. [11]. It modifies the usual tunneling probability predicted by WKB, by accounting the reflections from potential discontinuity. In this model, the barrier height to tunneling is taken to be a function only of the total electron energy and the Si bandgap dispersion relation is modeled as a two band Franz-type.

Hou et al. [12] have presented a physical model to calculate the direct tunneling hole current through ultrathin gate oxides from the inversion layer of metaloxidesemiconductor field-effect transistors. A parametric self-consistency method utilizing the triangular well approximation is used for the electrostatics of the inversion layer and tunneling probability is calculated by a modified WKB approximation.

A number of surface potential based compact model have been reported in the literature [13–15]. Most of these models incorporate Quantum mechanical effect without considering wave function penetration effect and utilize WKB [16] approximation to obtain a simple analytical expression for the transparency. In these models Quantum mechanical correction to the surface potential also does not consider wave function penetration effect.

Gu et al. [13] have reported a physics-based compact model of gate current in the n-MOSFET. They presented a simplified version of the Esaki-Tsu formula Introduction 5

to calculate the tunneling current density, in which the original integral is approximated to retain the essential physics. The channel component of the gate current is physically partitioned into the source and drain parts using a symmetrically linearized version of the charge-sheet model. This model is surface potential-based and requires rigorous mathematical manipulation. Register et al. [11] proposed a model for tunneling with the modified WKB transparency.

Choi et al. [14] presented a compact direct tunneling current model for circuit simulation to predict ultra-thin gate oxide CMOS circuit performance by introducing the explicit surface potential model and quantum-mechanical corrections. For quantum-mechanical corrections, they utilized the bandgap widening approach of van Dort et al. [17].

Clerc et al. [15] presented a physically based, analytical, circuit simulation model for direct tunneling from NMOS inversion layers in a MOS structure. This model takes account of the effect of quantization on surface potential in the silicon, the supply of carriers for tunneling and the oxide transmission probability. The inclusion of quantum effects is based on a variational approach to the solution of the Poisson and Schrödinger equations in the silicon inversion layer.

Li et al. [18] presented a physics-based compact modeling tool for tunneling current through ultra-thin gate dielectrics utilizing the concept of impact frequency. Sullivan et al. [19] have reported a comprehensive study on the compact modeling of gate tunneling current.

Physically based compact modeling of DT gate current of MOS devices for a large range of oxide thicknesses considering quantum correction and wave function penetration effect is yet to be reported in the literature.

### 1.2 Objective of This Work

In this work, a physically based and accurate compact model to simulate DT gate current for MOS devices considering quantum mechanical correction and wave function penetration effect is developed. DT gate current will be calculated using an equation reported by Kalam et. al [8]. An empirical equation of  $\Gamma$  will be developed as a function of Quantum mechanically corrected surface potential considering wave function penetration effect. Concentration of the inversion electron will be determined using Eigen energy, calculated by modified Airy function approximation considering wave function penetration effect [20], and the equation proposed by Stern [21]. To benchmark the proposed compact model for DT gate current, a self-consistent numerical simulator will be developed by solving the coupled Schrödinger-Poisson equations. For incorporating wave function penetration effect, open boundary condition will be applied in the gate-gate oxide interface. Results obtained from the developed compact model will also be compared with the published experimental data to show the validity of the model.

## 1.3 Organization of The Thesis

In chapter 2 necessary theories to develop self-consistent model and compact model for Direct Tunneling gate current are discussed. In chapter 3 different device parameters, calculated by the developed compact model are compared with numerical simulation results. Finally, Direct Tunneling gate current for a wide range of doping densities and oxide thicknesses are compared with the self-consistent numerical simulator and published experimental data to show the accuracy and robustness of the developed model.

## **Chapter 2**

# Direct Tunneling Gate Current and Compact Model

This section describes Direct Tunneling (DT) Gate Current and its Compact Modeling. Mechanism behind DT gate current of MOS devices is given. The compact model of DT gate current considering Quantum Mechanical (QM) effect and wave function penetration is also been presented.

### 2.1 MOS Structure

Metal-insulator-semiconductor (MIS) transistor is one of the most widely used electronic devices, particularly in digital integrated circuits. These types of devices are made using silicon as the semiconductor, SiO<sub>2</sub> as the insulator and metal or polysilicon as the gate electrode. The term metal oxide semiconductor field-effect transistor (MOSFET) or MOS devices is used to refer these devices.

Fig. 2.1 shows an n-channel enhancement-type MOS device. This device is fabricated on a p-type substrate which is a single-crystal silicon wafer that provides physical support for the device. Two heavily doped n-type regions termed as source and drain regions are created in the substrate. A thin layer of silicon dioxide (SiO<sub>2</sub>) or any other material that is an excellent electrical insulator is grown on the surface of the substrate, covering the area between the source and drain regions. Metal acts as the electrode for the device. Metal

contacts are also brought out the source region, the drain region and the substrate also known as the body. Thus four terminals are brought out: the gate terminal (G), the source terminal (S), the drain terminal (D), and the substrate or body terminal (B).

Fig. 2.1: Cross section of an enhancement-type n-MOSFET.

## 2.2 Direct Tunneling Gate Current

Two components of gate current from the inversion layer of a n-MOSFET is illustrated in Fig. 2.2. The main component of the gate current is due to tunneling of electrons from the conduction band of the silicon substrate into the gate. In the valance band of the silicon, tunneling occurs by generation of electron-hole pairs. Electron tunnels towards the positively biased gate and hole form the substrate current in the device. However this current is usually several orders of magnitude smaller than the conduction band component because of the increased barrier height for tunneling from the valance band. This work will therefore focus on model for tunneling from silicon conduction

band.

Fig. 2.2: A schematic of the band diagram of a Metal/oxide/p-Si MOS structure showing the electron quantization effect in the substrate and direct electron tunneling from the substrate inversion layer to the gate.

In Fig. 2.2, a schematic band diagram is shown for a n-MOSFET in inversion condition.  $E_C$  and  $E_V$  at the substrate side are the Si conduction and valence band edges.  $E_f$  is the Fermi level in the Si substrate.  $E_C$  and  $E_V$  are the n<sup>+</sup> polysilicon conduction and valence band edges. ECB and EVB are the electron tunneling from conduction and valence band.  $\phi_b$  is the barrier height and  $\phi_s$  is the surface potential.  $V_{OX}$  is the oxide voltage drop.

### 2.3 Self Consistent Simulator

In this work, a self-consistent Schrödinger-Poisson solver is developed to benchmark the compact model of DT gate current against it. This simulator is also very much necessary to formulate empirical equation for the compact model, explained in the next section. The self consistent simulator used is based on Green's function formalization [22]. Shams [23] presented a detail algorithm of this simulator.

### 2.3.1 Basic Model

### Schrödinger solver

Stern [21] and Moglestue [24] described a self-consistent solution approach for the first time. Three major assumptions by Stern were,

- (1) Effective mass approximation is valid. So periodic potential need not be taken into account.

- (2) At the silicon surface envelop wavefunction vanishes.

- (3) Surface states are neglected and any charge in the oxide near semiconductor body can be replaced by an electric field.

By the effective mass approximation, Schrödinger's equation for the wave function  $\psi_{0_{ij}}$  can be written as,

$$[-\frac{1}{2}\hbar^{2}\nabla m^{*-1}\nabla + eV(z)]\psi_{0ij} = E'_{ij}\psi_{0ij}$$

(2.1)

Here,  $m^{*-1}$  is the effective mass tensor, V(z) the electrostatic potential, e is electron charge magnitude and  $E'_{ij}$  is the energy. z is the direction in the MOSFET from gate to the bulk body.

Stern [21] showed that the electronic wavefunction  $\psi_{0_{ij}}$  for the jth subband in the ith valley can be expressed in terms of Bloch function traveling parallel to the interface, constrained by an envelope function normal to it. This is represented as,

$$\psi_{0_{ij}}(x,y,z) = \psi_{ij}(z)e^{i\theta z}e^{ik_{x}x + ik_{y}y}$$

(2.2)

where,  $k_x$  and  $k_y$  represents the component of the wave vector k in x and y direction.  $\theta$  depends on  $k_x$  and  $k_y$ .  $\psi_{ij}(z)$  can be obtained from,

$$\left[-\frac{\hbar^2}{2m_{zi}}\frac{d^2}{dz^2} + eV(z)\right]\psi_{ij}(z) = E_{ij}\psi_{ij}(z)$$

(2.3)

where,  $m_{zi}$  is the quantization effective mass and  $E_{ij}$  is the eigenenergy of the jth subband in the ith valley in the perpendicular direction.

Here two boundary conditions are used for the solution of (2.3). They are,

- $\psi_{ij}(\infty) = 0$  deep inside the semiconductor

- $\psi_{ij}(0) = 0$  at the metal oxide interface.

Each eigenvalue  $E_{ij}$  found from the solution of Eq. (2.3) is the bottom of subband, with energy levels given by,

$$E'_{ij} = E_{ij} + \hbar^2 k_x^2 / 2m_x + \hbar^2 k_y^2 / 2m_y \tag{2.4}$$

here  $m_x$  and  $m_y$  are the effective masses in the transport plane. The conduction band of silicon has six ellipsoidal valleys along the 100 direction of the Brillouin zone. As a result there can be as many as three values of  $m_z$  depending on the surface orientation. From the effective mass approximation, the valleys are degenerated in pairs. So the solution of Eq. (2.3) gives the eigenenergy  $E_{ij}$  and the envelope function  $\psi_{ij}(z)$ .

### 2.3.2 Green's Function Formalism

The process of Schrödinger's equation solution as stated above is based on Green's function [25]. Green's function is a technique for calculating an effect at a certain point due to disturbance at any other point. In MOS devices retarded Green's function for the i'th valley at a distance z is given by,

$$[E + \frac{\hbar^{2}}{2m_{zi}}\frac{\partial^{2}}{\partial z^{2}} - eV(z) + i\epsilon]G_{i}^{R}(z, z'; E) = \delta(z - z')$$

(2.5)

Here  $\epsilon$  is an infinitesimally small positive energy. Its value is in  $10^{-12}$  range. Retarded Green's function  $G_i^R(z,z';E)$  is a wave function at z originated by an excitation at z'. An important fact here is this that Green's function is continuous at z=z' and the derivative is discontinuous at z' by,  $2m_{zi}/\hbar^2$ .

One dimensional density of states,  $N_{1D}$ , eigenenergies  $E_{ij}$  and normalized wavefunctions,  $\psi_{ij}$  are calculated using the retarded Green's function. The logarithmic derivative of the retarded Green's function  $G^R$  is defined by,

$$Z_{i}(z, z'; E) = \frac{2\hbar}{im_{zi}} \left[ \frac{\partial G_{i}^{R}(z, z'; E)}{\partial z} / G_{i}^{R}(z, z'; E) \right]$$

(2.6)

Two boundary conditions are needed to estimate  $Z_i(z,z';E)$  as  $Z_i(z,z';E)$  has a discontinuity at z=z'. Here we assume that potential profile is flat inside the semiconductor and inside the metal at a distance far from the oxide semiconductor interface. So if we have  $V(\infty)$  is the constant potential at  $z=\infty$  (deep inside the semiconductor) and if  $V(-\infty)$  is the constant potential at  $z=-\infty$  (deep inside the gate metal), Green's function may be expressed as,

$$G_i^R(z \longrightarrow \infty, z'; E) \sim e^{\gamma_i(\infty)(z-z')}$$

(2.7)

and

$$G_i^R(z \longrightarrow -\infty, z'; E) \sim e^{-\gamma_i(-\infty)(z-z')}$$

(2.8)

where,  $\gamma_i(\pm \infty) = i\sqrt{(2m_{zi}/\hbar^2)(E - eV(\pm \infty) + i\epsilon)}$ . The boundary conditions to estimate  $Z_i$  are determined from Eq. (2.7) and (2.8). These are,

$$Z_i(z \longrightarrow \infty, z'; E) = Z_{oi}(\infty), z > z'$$

(2.9)

and

$$Z_i(z \longrightarrow -\infty, z'; E) = Z_{oi}(-\infty), z < z'$$

(2.10)

where,  $Z_{oi}(\pm \infty) = (2\hbar/im_{zi})\gamma_i(\pm \infty)$ . From the properties of 1D Green's functions, it can be shown [26], for all z > z':

$$Z_i(z, z'; E) = Z_i^+(z; E)$$

(2.11)

for all z < z',

$$Z_i(z, z'; E) = Z_i^-(z; E)$$

(2.12)

here,  $Z_i^+(Z_i^-)$  does not depend on z' as long as z > z' (z < z'). To calculate,  $Z_i^\pm$  method described by [27] is followed. Here microwave transmission line analogy is used to find the eigenenergies for any quantum well. Use of this technique in MOS quantum wells is given in [28].

The normalized wave function is calculated from retarded Green's function. We have  $G_i^R$  expressed as a function of complete set of eigenfunctions,

$$G_i^R(z, z'; E) = \sum_j \frac{\psi_{ij}(z)\psi_{ij}^*(z')}{E - E_{ij} + i\epsilon}$$

(2.13)

If  $E_{i(j+1)} - E_{ij} >> \epsilon$  for all j, only one term dominates when  $E \to E_{ij}$ , as the discrete eigenenergies are degenerate. For the diagonal elements of  $G_i^R$ , we obtain

$$G_i^R(z, z'; E \to E_{ij}) \cong \frac{|\psi_{ij}(z)|^2}{E - E_{ij} + i\epsilon}$$

(2.14)

Equating imaginary parts of (2.14) and putting  $E = E_{ij}$ ,

$$|\psi_{ij}(z)|^2 = -\epsilon Im[G_i^R(z, z'; E_{ij})]$$

(2.15)

It has been shown in [26] that,

$$-Im[G_i^R(z,z';E_{ij})] = \frac{4}{\hbar}Im(\frac{i}{Z_i^+(E_{ij}) - Z_i^-(z;E_{ij})})$$

(2.16)

From (2.16) in (2.15),

$$|\psi_{ij}(z)|^2 = \frac{4\epsilon}{\hbar} Im(\frac{i}{Z_i^+(z; E_{ij}) - Z_i^-(z; E_{ij})})$$

(2.17)

Again 1D state of density  $N_{1D}$  is related to the diagonal part of  $G^R$ .  $N_{1D_i}(z; E)$ , in terms of retarded Green's function,  $G_i^R$  is given by,

$$N_{1D_i}(z;E) = -\frac{1}{\pi} Im[G_i^R(z,z';E)]$$

(2.18)

When  $\epsilon \to 0^+$ , the density-of-states (DOS),  $N_{1D_i}(z; E)$ , becomes a delta function at the eigenenrgies,  $E = E_{ij}$  in a bound system with the amplitude equal to the probability density at that energy, i.e.,

$$N_{1D_i}(z;E) = \sum_{i} |\psi_{ij}(z)|^2 \delta(E - E_{ij})$$

(2.19)

Final expression of  $\mathcal{N}_{1D_i}$  is given by,

$$N_{1D_i}(z;E) = \frac{V_i}{\pi} \frac{|\psi_{ij}(z)|^2}{(E - E_{ij})^2 + V_i^2}$$

(2.20)

Using Eq. (2.18),  $N_{1D}$  can be expressed in terms of the logarithmic  $Z_i^{\pm}$  [26]:

$$N_{1D_i}(z;E) = \frac{4}{\pi\hbar} Im(\frac{i}{Z^+(z;E) - Z^-(z;E)})$$

(2.21)

### Poisson solver

Poisson solver is needed to obtain the potential profile V(z). This is the starting phase of the self-consistent simulator. Here Poisson's equation is solved by finite difference method considering nonuniform grid spacing. Grid spacing is finer near oxide semiconductor interface.

$$\frac{d^2V(z)}{dz^2} = -\frac{\left[\rho_{depl}(z) + \rho_{inv}(z)\right]}{\epsilon_{si}\epsilon_0}, \quad for \quad z > Tox$$

(2.22)

$$\frac{d^2V(z)}{dz^2} = -\frac{[\rho_{inv}(z)]}{\epsilon_{ox}\epsilon_0}, \quad for \quad z \le Tox$$

(2.23)

Here,  $\epsilon_{si}$  is the dielectric constant of semiconductor,  $\epsilon_{ox}$  is the dielectric constant of oxide,  $\rho_{depl}(z)$  is the depletion charge and  $\rho_{inv}(z)$  is the inversion charge distribution along z. Inversion charge is calculated with wave-function penetration effect consideration. Once proper charge distributions are known accurate determination of the potential profile is done.  $\rho_{inv}(z)$  is calculated from eigenenergies and wave-function values. It is given by,

$$\rho_{inv} = \sum_{ij} N_{ij} |\psi_{ij}(z)|^2 \tag{2.24}$$

$$N_{ij} = \frac{n_{vi} m_{di} kT}{\pi \hbar^2} \ln[1 + \exp(\frac{E_F - E_{ij}}{kT})]$$

(2.25)

Here,  $n_{vi}$  is the valley degeneracy and  $m_{di}$  is the density of states effective mass of the ith valley as shown in the previous section.  $E_F$  is the Fermi level.

Depletion charge density  $\rho_{depl}(z)$  is given by,

$$\rho_{depl}(z) = \begin{cases} -e(N_A - N_D), & 0 < z < z_d \\ 0, & z > z_d \end{cases}$$

(2.26)

here,  $z_d$  is the depletion layer thickness which is given by,

$$z_d = \sqrt{\frac{2\epsilon_{si}\epsilon_0\Phi_d}{e(N_A - N_D)}}$$

(2.27)

where  $\Phi_d$  is the depletion charge band bending.  $\Phi_d$  is given by,

$$\Phi_d = \Phi_s - \frac{kT}{e} - \frac{eN_{inv}z_{avg}}{\epsilon_{si}\epsilon_0}$$

(2.28)

Here,  $\Phi_s$  is the total band bending of the semiconductor.  $N_{inv}$  is the total inversion charges per unit area in the inversion layer. It is expressed as,

$$N_{inv} = \sum_{ij} N_{ij} \tag{2.29}$$

Again  $z_{avg}$  is the average distance of the inversion charge from the silicon-oxide interface and it is given by,

$$z_{avg} = (1/N_{inv}) \sum_{ij} N_{ij} \int z |\psi_{ij}|^2 dz$$

(2.30)

Boundary conditions are used for the solution of Eq. (2.22). These are,

- $V(z_d) = 0$

- $V(0) = V_g$ , at the metal oxide interface. Here  $V_g$  acts as the gate voltage input.

- At the oxide semiconductor interface  $F_s = F_{ox}$ , where,

$$F_s = \frac{e(N_{inv} + N_{depl})}{\epsilon_{si}\epsilon_0} F_{ox} = \frac{e(N_{inv} + N_{depl})}{\epsilon_{ox}\epsilon_0}$$

(2.31)

are the surface electric fields and,

$$N_{depl} = z_d(N_A - N_D) (2.32)$$

is the number of charge per unit area in the depletion layer.

### 2.3.3 Coupling Schrödinger and Poisson's Equation

Self-consistent simulation is done for each gate bias for a MOS device. Here gate bias acts as the input. First for a particular gate bias Poisson's equation 2.22 is solved by finite difference method. According to finite difference method,

$$\frac{d^2V}{dz^2} = \frac{V_{n+2} - 2V_{n+1} + V_n}{\delta z^2} = -\rho_n/\epsilon \tag{2.33}$$

Here, n+2, n+1 and n are different grid space points.  $\rho_n$  is the value of total charge in space point n and  $\epsilon$  is the dielectric constant for oxide or the semiconductor. Solving the Poisson's equation, voltage profile for a particular gate bias is gained. From it potential profile is estimated. Schrödinger's equation is solved by retarded Green's function to get the eigen states and from that inversion charges are calculated for each state and for each valley (2.36). From these charges  $\rho_{inv}$  is estimated. Taking the full charge profile,  $(\rho_{inv}, \rho_{depl})$  Poisson's equation is solved again. A new potential profile is generated by taking 96% percent of the older profile and 4% of the newer profile. Whole calculation is done again. This procedure is repeated until error between the two successive profiles is less than 0.01%.

For higher gate voltages starting potential profile for the calculation is taken as the last converged profile of previous gate voltage.

### 2.3.4 Calculation of DT Gate Current

### Calculation of $\Gamma_{ij}$

Many different models have been proposed to calculate  $\Gamma_{ij}$ . In [7], Schrödingers equation has been discretized using a finite difference technique. consequence of using open boundary conditions, the Hamiltonian matrix, defined over a finite region of interest, becomes non-Hermitian. Numerical determination of the complex eigenvalues of the non-Hermitian matrix provides an estimation of  $\Gamma_{ij}$ . Gildenblat et. al [29] has shown that the energy derivative of the phase of the reflection coefficient (determined using the transfer matrix formalism) around the energies of each quasi-bound state has a Lorentzian form and its full width at half-maximum (FWHM) is equal to  $\Gamma_{ij}$ . This method has been applied in [30] and [31] to calculate the lifetimes. However, from a numerical standpoint, direct calculation of such a derivative is difficult [31]. Therefore, a suggestion has been made in [31] to calculate  $\Gamma_{ij}$  from the diagonal element of the transfer matrix. But the transfer matrix method itself suffers from numerical instability. In a truly bound system, the 1D local DOS,  $N_{1D}$ , is given by a series of delta functions at the eigenenergies. When leakage occurs,  $N_{1D}$  broadens in energy and becomes a Lorentzian function.  $\Gamma_{ij}$ can be estimated from the FWHM of the energy broadened  $N_{1D}$ . The Greens function formalism is applied to estimate  $N_{1D}$ . The 1D local DOS, by definition, is related to the diagonal element of the retarded Greens function  $G^R$  [26] which is shown in Eq. (2.16).

The diagonal element of  $G^R$  can easily be calculated with open boundary conditions using the logarithmic derivative technique, which has been described in detail in [26]. An advantage of this technique is that it is free from any matrix manipulation, and consequently, it is computationally

efficient and numerically stable. Although  $\Gamma_{ij}$  and  $\tau_{ij}$  can be calculated in a straightforward way using Eq. (2.16), it requires  $N_{1D}$  to be resolved in energy with sufficient accuracy to calculate the FWHM. Normally, in devices with gate-oxide thickness ( $T_{ox}$ ) equal or less than 2.5 nm, this poses no serious limitation. However, in structures with  $T_{ox} \geq 3$  nm,  $\Gamma_{ij}$  is very small and its determination demands precisions which are much higher than usual thus requiring very high computational time. Hakim et. al [5] presented an alternate way to perform this calculation which is utilized in this work to produce a compact model of DT gate current, described in the next section.

### 2.4 Compact Model

When tunneling occurs in the MOS inversion layer, the system becomes quasibound with finite lifetimes of the inversion carriers. In such a system, the eigenenergies are complex quantities:  $E_{ij} \Rightarrow E_{ij} + j\Gamma_{ij}$ . Here, the real part  $E_{ij}$  is the energy of the jth quasi-bound state in the ith valley and the imaginary part  $\Gamma_{ij}$  is related to the lifetime  $\tau_{ij}$  of the corresponding state following the relationship

$$\tau_{ij} = \hbar/2\Gamma_{ij}.\tag{2.34}$$

According to the QM methods, the DT current is calculated from the known values of  $\tau_{ij}$  using Eq. (2.35):

$$J = \sum_{ij} \frac{qN_{ij}}{\tau_{ij}}. (2.35)$$

Here,  $N_{ij}$ , the concentration of the inversion electrons in the jth state of the ith valley.

### 2.4.1 Calculation of $N_{ij}$

The concentration of the inversion electrons in the *jth* state of the *ith* valley is given by

$$N_{ij} = \frac{n_{vi} m_{di} kT}{\pi \hbar^2} \ln[1 + \exp(\frac{E_F - E_{ij}}{kT})]$$

(2.36)

Here,  $n_{vi}$  is the valley degeneracy and  $m_{di}$  is the density of states effective mass of the *ith* valley. For lower valley  $n_{vl}=2$ ,  $m_{dl}=0.190m_0$  and for higher valley  $n_{vh}=4$ ,  $m_{dh}=0.417m_0$  where  $m_0=9.1^{-31}{\rm kg}$  is the electron rest mass.  $E_F$  is the Fermi level and k is the Boltzman constant.

In this work inversion electron concentration of first two states of the lower valley and only first state of the upper valley is considered. To calculate the energy separation between fermi level and eigen states, modified Airy function approach is used. According to the Airy function approximation, the energies of the quantized states are proportional to  $(F_{ox})^{2/3}$ , where  $F_{ox}$  is the oxide electric field. However, for the state-of-the-art nano-scale MOSFETs, the 2/3 power law is not accurate. It has been shown recently that the quantized energies of the quasi-bound states, as functions of  $F_{ox}$ , follow a power-law relationship (even though different from 2/3, as predicted by the Airy function approximation) even when wave function penetration effect into the gate dielectric is considered [32].

According to [32], The energy of the quasi-bound states  $E_{ij}$ , measured from the respective band edge, is expressed as

$$E_{ij} \cong \pm \zeta_{ij} \left( \frac{\mid F_{ox} \mid \text{cm}}{\text{MV}} \right)^{\lambda_{ij}}. \tag{2.37}$$

Here,  $\zeta_{ij}$  and  $\lambda_{ij}$  are the empirically fitted parameters. According to [32],  $\zeta_{l1} = 77$  meV,  $\lambda_{l1} = 0.61$  for electrons and  $\zeta_{l1} = 88$  meV,  $\lambda_{l1} = 0.64$  for holes incorporating wave function penetration effect where suffix l1 represents the

ground state of lower valley. Here (+) sign is for electrons and (-) sign is for holes.  $F_{ox} = -Q_s/\epsilon_0\epsilon_{ox}$ , where  $Q_s$  is the total charge density in Si.  $\epsilon_0$  is the absolute permittivity and  $\epsilon_{ox}$  is the relative permittivity of oxide.

$Q_s$  can be calculated by Eq. (2.38)

$$Q_s = -C_{ox}(V_g - V_{fb} - \phi_s), (2.38)$$

here  $C_{ox} = \epsilon_0 \epsilon_{ox}/T_{ox}$  is the oxide capacitance and  $T_{ox}$  is the oxide thickness.  $V_g$  is the gate voltage and  $V_{fb}$  is the flatband voltage. Surface potential  $(\phi_s)$  is a very important parameter.  $\phi_s$ , considering Quantum Mechanical (QM) correction, can be calculated as

$$\phi_{s[qm]} = \phi_{s[sc]} + \delta\phi_s. \tag{2.39}$$

Here  $\phi_{s[sc]}$  is the semiclassical surface potential neglecting QM effects.  $\phi_{s[sc]}$  can be estimated from the well known Pao-Sah equation [33].  $\delta\phi_s$  can be calculated from the second order solution of an implicit equation of  $\delta\phi_s$  as

$$\delta\phi_s = \frac{C_{ox} \left[ V_g - V_{fb} - \left( \phi_{s[sc]} + \delta\phi_s^1 + \gamma \sqrt{|\phi_{s[sc]} + \delta\phi_s^1|} \right) \right] E_{l1}^1}{q\epsilon_0 \epsilon_{ox} F_{ox}^1}, \tag{2.40}$$

where  $\gamma = \sqrt{2q\epsilon_0\epsilon_{si}N_A}/C_{ox}$  is the body factor.Here,  $\delta\phi_s^1$ , the first order solution is

$$\delta\phi_s^1 = \frac{C_{ox} \left[ V_g - V_{fb} - \left( \phi_{s[sc]} + \gamma \sqrt{|\phi_{s[sc]}|} \right) \right] E_{l1}^0}{q \epsilon_0 \epsilon_{ox} F_{ox}^0}. \tag{2.41}$$

$E_{l1}^0$ ,  $F_{ox}^0$  are the zeroth order terms and  $E_{l1}^1$ ,  $F_{ox}^1$  are the first order terms, respectively. These are given by

$$E_{l1}^{0} = \zeta_{l1} \left( \frac{|F_{ox}^{0}| \text{ cm}}{\text{MV}} \right)^{\lambda_{l1}}, \tag{2.42}$$

$$E_{l1}^{1} = \zeta_{l1} \left( \frac{|F_{ox}^{1}| \text{ cm}}{\text{MV}} \right)^{\lambda_{l1}}, \tag{2.43}$$

$$F_{ox}^{0} = \frac{C_{ox}(V_g - V_{fb} - \phi_{s[sc]})}{\epsilon_0 \epsilon_{ox}}, \tag{2.44}$$

$$F_{ox}^{1} = \frac{C_{ox}[V_g - V_{fb} - (\phi_{s[sc]} + \delta\phi_s^1)]}{\epsilon_0 \epsilon_{ox}}.$$

(2.45)

By the above formulas, a quantum mechanically correct, accurate  $\phi_s-V_g$  characteristics can be determined

In this work a self-consistent numerical method incorporating wave function penetration effect (explained in previous section) is used to find the values of  $\zeta_{ij}$  and  $\lambda_{ij}$  for first eigen state of the lower valley ( $\zeta_{l2}$  and  $\lambda_{l2}$ ) and ground state of the higher valley ( $\zeta_{h1}$  and  $\lambda_{h1}$ ). For ground eigen state of the lower valley, values given in [32] kept unchanged.

For first eigen state of lower valley  $\zeta_{l2}=10^{-0.86} {\rm eV}$  and  $\lambda_{l2}=0.54$  are two empirical constants.

For ground eigen state of the higher valley, if a constant value of  $\zeta_{h1}$  is considered then while calculating  $E_{h1}$  from Eq. (2.37) does not match well with the self-consistent numerical solution. It is observed that  $\zeta_{h1}$  varies with  $N_A$ . So, an empirical equation of  $\zeta_{h1}$  is formulated based on the results obtained from the self-consistent numerical solution as

$$\zeta_{h1} = 10^{-d} \text{eV},$$

(2.46)

where,

$$d = aN^b + c. (2.47)$$

00

Here, a=0.04086, b=0.4087, c=0.8923 are empirical constants and  $N=N_A(\text{cm}^{-3})/10^{17}$  where  $N_A$  is the substrate doping density. Fig. 2.3 shows the fitting of the parameter d with data set obtained using self-consistent numerical solution.  $\lambda_{h1}$  is treated as a constant parameter with value 0.56.

Fig. 2.3: Fitting of parameter d with variation of  $N_A$

Energy separation between eigen energy and fermi energy can be calculated as

$$E_F - E_{ij} = -[(E_g/2) + q\phi_f - q\phi_s + E_{ij}]. \tag{2.48}$$

Here,  $E_g$  is the band gap energy and  $\phi_f = (kT/q) \ln(N_A/N_i)$  is the quasi fermi potential where  $N_i$  is the intrinsic carrier concentration.

### 2.4.2 Calculation of $\Gamma_{ij}$

Hakim and Haque [5] presents an efficient way to calculate  $\Gamma_{ij}$ , which can be applied for MOS devices with very small oxide thicknesses to large oxide thicknesses, as

$$\Gamma_{ij} = \Gamma_{0ij} \exp(-T_{ox}/L_{ij}). \tag{2.49}$$

Here,  $\Gamma_{0ij}$  and  $L_{ij}$  are fitting parameters. In this work  $\Gamma_{0ij}$  and  $L_{ij}$  are formulated empirically using the self-consistent numerical simulation presented in the previous section.

For ground eigen state of lower valley

$$\Gamma_{0l1} = [(x_l \exp(y_l \phi_s)) + 6.5 \times 10^4] \times 10^{-25} \text{J},$$

(2.50)

where

$$x_l = P_{xl1}N^4 + P_{xl2}N^3 + P_{xl3}N^2 + P_{xl4}N + P_{xl5}, (2.51)$$

and

$$y_l = P_{ul1}N^4 + P_{ul2}N^3 + P_{ul3}N^2 + P_{ul4}N + P_{ul5}.$$

(2.52)

Неге

$$P_{xl1} = 2.386 \times 10^{-6}$$

$$P_{xl2} = -7.723 \times 10^{-5}$$

$$P_{xl3} = 0.0007175$$

$$P_{xl4} = -0.001965$$

$$P_{xl5} = 0.002143$$

$$P_{yl1} = -0.001066$$

$$P_{yl2} = 0.03436$$

$$P_{yl3} = -0.2982$$

$$P_{yl4} = 0.6519$$

$$P_{yl5} = 16.38$$

Fig. 2.4: Fitting of parameter  $x_l$  with variation of  $N_A$

Fig. 2.5: Fitting of parameter  $y_l$  with variation of  $N_A$

Fig. 2.4 shows the best possible fitting of parameter  $x_l$  and Fig. 2.5 shows the best possible fitting of parameter  $y_l$  for different values of  $N_A$  and these empirical fittings hold good for substrate doping densities beyond  $10^{18}$  cm<sup>-3</sup>, which may be considered as practical substrate doping density range.

For first eigen state of lower valley  $\Gamma_{0l2}=5.5\times 10^{-19}$  J. For ground eigen state of higher valley

$$\Gamma_{0h1} = [(x_h \exp(y_h \phi_s)) + 8 \times 10^4] \times 10^{-25} \text{J},$$

(2.53)

where

$$x_h = P_{xh1}N^4 + P_{xh2}N^3 + P_{xh3}N^2 + P_{xh4}N + P_{xh5}, (2.54)$$

and

$$y_h = P_{yh1}N^4 + P_{yh2}N^3 + P_{yh3}N^2 + P_{yh4}N + P_{yh5}. (2.55)$$

Here

$P_{xh1} = 9.056 \times 10^{-5}$

$P_{xh2} = -0.002857$

$P_{xh3} = 0.02588$

$P_{xh4} = -0.06703$

$P_{xh5} = 0.04967$

$P_{yh1} = -0.001541$

$P_{yh2} = 0.04952$

$P_{yh3} = -0.4249$

$P_{yh4} = 0.8905$

$P_{yh5} = 15.12$

Fig. 2.6 shows the best possible fitting of parameter  $x_h$  and Fig. 2.7 shows the best possible fitting of parameter  $y_h$  for different values of  $N_A$  and these empirical fittings hold good for substrate doping densities beyond  $10^{18}$  cm<sup>-3</sup>, which may be considered as practical substrate doping density range.

Fig. 2.6: Fitting of parameter  $x_h$  with variation of  $N_A$

Fig. 2.7: Fitting of parameter  $y_h$  with variation of  $N_A$

The value of  $L_{ij}$  is very little sensitive to the change in substrate doping density and remains constant for all the cases. Empirically calculated constant value of  $L_{ij}$  is  $7.5 \times 10^{-11}$  m.

#### 2.4.3 Calculation of DT Gate Current, J

Direct Tunneling gate current contributed by the first two eigen states of the lower valley and lowest eigen state of higher can be almost accurately approximated as the total DT gate current.  $\tau_{l1}$ ,  $\tau_{l2}$  and  $\tau_{h1}$  is calculated using already calculated values of  $\Gamma_{l1}$ ,  $\Gamma_{l2}$  and  $\Gamma_{h1}$ . The values of  $J_{l1}$ ,  $J_{l2}$  and  $J_{h1}$  is calculated using Eq. (2.35) from the values of  $N_{l1}$ ,  $N_{l2}$ ,  $N_{h1}$ ,  $\tau_{l1}$ ,  $\tau_{l2}$  and  $\tau_{h1}$ . Finally DT gate current is calculated by adding the currents that tunnel from the considered eigen states as

$$J = J_{l1} + J_{l2} + J_{h1}. (2.56)$$

Developed compact model is surface potential  $(\phi_s)$  based i.e. the input parameter is  $\phi_s$ . Using the  $\phi_s-V_g$  characteristics and Eq. (2.56),  $J-V_g$  characteristics can be determined.

## Chapter 3

# **Results and Discussions**

In this chapter various device parameters, calculated from both self-consistent Schrödinger-Poisson solver and developed compact model, are shown. Results obtained from these two methods of calculations show very good agreement. Finally, the direct tunneling gate current, calculated using developed compact model, is compared with self-consistent numerical solution and experimental data taken from published sources. To show the robustness of the compact model a large range of substrate doping densities are considered. For low, moderate and high doping density, values  $5 \times 10^{16}$  cm<sup>-3</sup>,  $10^{17}$  cm<sup>-3</sup> and  $10^{18}$  cm<sup>-3</sup> are considered respectively.

### 3.1 Eigen States, $E_{ij}$

Ground eigen state of lower valley is calculated using Eq. (2.37) with the same parameters values proposed in [32]. Figs. 3.1, 3.2 and 3.3 show ground eigen state  $E_{l1}$  as a function of oxide electric field  $F_{ox}$ , calculated by Eq. (2.37) and self-consistent numerical simulator for three different substrate doping densities. Results shows a good agreement between these two forms of calculations for all the cases considering low, moderate and high substrate doping densities.

Fig. 3.1: Ground Eigen state of lower valley vs. Oxide electric field for MOSFET with Al/SiO<sub>2</sub>/Si structure. Here,  $N_A = 5 \times 10^{16}$  cm<sup>-3</sup> and  $T_{ox} = 1.46$  nm.

Fig. 3.2: Ground Eigen state of lower valley vs. Oxide electric field for MOSFET with Al/SiO<sub>2</sub>/Si structure. Here,  $N_A=10^{17}~{\rm cm}^{-3}$  and  $T_{ox}=1.46~{\rm nm}$ .

First eigen state of lower valley is calculated using Eq. (2.37) with empirical constants  $\zeta_{l2}=10^{-0.86} {\rm eV}$  and  $\lambda_{l2}=0.54$ . Figs. 3.4, 3.5 and 3.6 show first eigen state  $E_{l2}$  as a function of oxide electric field  $F_{ox}$ , calculated by Eq. (2.37) and self-consistent numerical simulator for low, moderate and high substrate

Fig. 3.3: Ground Eigen state of lower valley vs. Oxide electric field for MOSFET with Al/SiO<sub>2</sub>/Si structure. Here,  $N_A=10^{18}~{\rm cm}^{-3}$  and  $T_{ox}=1.46~{\rm nm}$ .

doping densities respectively. Results shows a good agreement between these two forms of calculations for all the cases.

Fig. 3.4: First Eigen state of lower valley vs. Oxide electric field for MOSFET with Al/SiO<sub>2</sub>/Si structure. Here,  $N_A = 5 \times 10^{16}$  cm<sup>-3</sup> and  $T_{ox} = 1.46$  nm.

Winds

Fig. 3.5: First Eigen state of lower valley vs. Oxide electric field for MOSFET with Al/SiO<sub>2</sub>/Si structure. Here,  $N_A = 10^{17}$  cm<sup>-3</sup> and  $T_{ox} = 1.46$  nm.

Fig. 3.6: First Eigen state of lower valley vs. Oxide electric field for MOSFET with Al/SiO<sub>2</sub>/Si structure. Here,  $N_A = 10^{18}$  cm<sup>-3</sup> and  $T_{ox} = 1.46$  nm.

Ground eigen state of higher valley is calculated using Eq. (2.37) where empirical parameter  $\zeta_{h1}$  is calculated using Eq. (2.46) and  $\lambda_{h1}$  is an empirical constant with value 0.56. Figs. 3.7, 3.8 and 3.9 show ground eigen state  $E_{h1}$  as a function of oxide electric field  $F_{ox}$ , calculated by Eq. (2.37) and self-consistent

numerical simulator for low, moderate and high substrate doping densities respectively and results shows a good agreement between these two forms of calculations for all the cases.

Fig. 3.7: Ground Eigen state of upper valley vs. Oxide electric field for MOSFET with Al/SiO<sub>2</sub>/Si structure. Here,  $N_A=5\times 10^{16}~\rm cm^{-3}$  and  $T_{ox}=1.46~\rm nm$ .

Fig. 3.8: Ground Eigen state of upper valley vs. Oxide electric field for MOSFET with Al/SiO<sub>2</sub>/Si structure. Here,  $N_A=10^{17}~{\rm cm}^{-3}$  and  $T_{ox}=1.46~{\rm nm}$ .

Fig. 3.9: Ground Eigen state of upper valley vs. Oxide electric field for MOSFET with Al/SiO<sub>2</sub>/Si structure. Here,  $N_A = 10^{18}$  cm<sup>-3</sup> and  $T_{ox} = 1.46$  nm.

### 3.2 Concentration of the Inversion Electrons, $N_{ij}$

Inversion layer electron concentration for the ground eigen state of lower valley,  $N_{l1}$  is calculated from Eq. (2.36). Figs. 3.10, 3.11 and 3.12 show inversion layer electron concentration of ground eigen state of lower valley  $N_{l1}$  as a function of quantum mechanically corrected surface potential  $\phi_s$ , calculated by Eq. (2.36) and self-consistent numerical simulator as well for low, moderate and high substrate doping densities respectively and results show a good agreement between these two forms of calculations for all the cases. For high substrate doping densities, two results show little discrepancies in moderate and strong inversion region. But it does not considerably affect the end result.

Fig. 3.10: Inversion electron concentration of ground state of lower valley vs. surface potential for MOSFET with Al/SiO<sub>2</sub>/Si structure. Here,  $N_A = 5 \times 10^{16}$  cm<sup>-3</sup> and  $T_{ox} = 1.46$  nm.

Fig. 3.11: Inversion electron concentration of ground state of lower valley vs. surface potential for MOSFET with Al/SiO<sub>2</sub>/Si structure. Here,  $N_A=10^{17}~{\rm cm}^{-3}$  and  $T_{ox}=1.46$  nm.

Inversion layer electron concentration for the first eigen state of lower valley,  $N_{l2}$  is calculated from Eq. (2.36). Figs. 3.13, 3.14 and 3.15 show inversion layer electron concentration of first eigen state of lower valley  $N_{l2}$  as a function of

Fig. 3.12: Inversion electron concentration of ground state of lower valley vs. surface potential for MOSFET with Al/SiO<sub>2</sub>/Si structure. Here,  $N_A=10^{18}~{\rm cm}^{-3}$  and  $T_{ox}=1.46$  nm.

Fig. 3.13: Inversion electron concentration of first eigen state of lower valley vs. surface potential for MOSFET with Al/SiO<sub>2</sub>/Si structure. Here,  $N_A$  = 5 × 10<sup>16</sup> cm<sup>-3</sup> and  $T_{ox}$  = 1.46 nm.

quantum mechanically corrected surface potential  $\phi_s$ , calculated by Eq. (2.36) and self-consistent numerical simulator as well for low, moderate and high substrate doping densities respectively and results show a good agreement

1 29

between these two forms of calculations for all the cases. In this case also, for high substrate doping densities, two results show little discrepancies in moderate and strong inversion region and it has very little effect on the end result i.e. DT gate current.

Fig. 3.14: Inversion electron concentration of first eigen state of lower valley vs. surface potential for MOSFET with Al/SiO<sub>2</sub>/Si structure. Here,  $N_A=10^{17}~{\rm cm}^{-3}$  and  $T_{ox}=1.46$  nm.

Fig. 3.15: Inversion electron concentration of first eigen state of lower valley vs. surface potential for MOSFET with Al/SiO<sub>2</sub>/Si structure. Here,  $N_A = 10^{18}$  cm<sup>-3</sup> and  $T_{ox} = 1.46$  nm.

Fig. 3.16: Inversion electron concentration of ground state of upper valley vs. surface potential for MOSFET with Al/SiO<sub>2</sub>/Si structure. Here,  $N_A = 5 \times 10^{16}$  cm<sup>-3</sup> and  $T_{ox} = 1.46$  nm.

Inversion layer electron concentration for the ground eigen state of higher valley,  $N_{h1}$  is calculated from Eq. (2.36). Figs. 3.16, 3.17 and 3.18 show inversion layer electron concentration of ground eigen state of higher valley  $N_{h1}$  as a

function of quantum mechanically corrected surface potential  $\phi_s$ , calculated by Eq. (2.36) and self-consistent numerical simulator as well for low, moderate and high substrate doping densities respectively and results show a good agreement between these two forms of calculations for all the cases. For high substrate doping densities, two results show little discrepancies in depletion and weak inversion region.

Fig. 3.17: Inversion electron concentration of ground state of upper valley vs. surface potential for MOSFET with Al/SiO<sub>2</sub>/Si structure. Here,  $N_A = 10^{17}$  cm<sup>-3</sup> and  $T_{ox} = 1.46$  nm.

Fig. 3.18: Inversion electron concentration of ground state of upper valley vs. surface potential for MOSFET with Al/SiO<sub>2</sub>/Si structure. Here,  $N_A = 10^{18}$  cm<sup>-3</sup> and  $T_{ox} = 1.46$  nm.

### 3.3 Imaginary Part of Eigen Energy, $\Gamma_{ij}$

Imaginary Part of eigen Energy for the ground eigen state of lower valley,  $\Gamma_{l1}$  is calculated by Eq. (2.49) and with the help of Eq. (2.50)-(2.52). Figs. 3.19, 3.20 and 3.21 show imaginary Part of eigen Energy of ground eigen state of lower valley  $\Gamma_{l1}$  as a function of quantum mechanically corrected surface potential  $\phi_s$ , calculated by developed equations and self-consistent numerical simulator as well for low, moderate and high substrate doping densities respectively and results show a good agreement between these two forms of calculations for all the cases.

Fig. 3.19: Imaginary part of complex ground eigen state of lower valley vs. surface potential for MOSFET with Al/SiO<sub>2</sub>/Si structure. Here,  $N_A = 5 \times 10^{16}$  cm<sup>-3</sup> and  $T_{ox} = 1.46$  nm.

Fig. 3.20: Imaginary part of complex ground eigen state of lower valley vs. surface potential for MOSFET with Al/SiO<sub>2</sub>/Si structure. Here,  $N_A = 10^{17}$  cm<sup>-3</sup> and  $T_{ox} = 1.46$  nm.

Imaginary Part of eigen Energy for the first eigen state of lower valley,  $\Gamma_{l2}$  is calculated by Eq. (2.49) and using constant fitting parameter  $\Gamma_{0l2} = 5.5 \times 10^{-19}$  J and imaginary Part of eigen Energy for the ground eigen state of higher valley,

Fig. 3.21: Imaginary part of complex ground eigen state of lower valley vs. surface potential for MOSFET with Al/SiO<sub>2</sub>/Si structure. Here,  $N_A = 10^{18}$  cm<sup>-3</sup> and  $T_{ox} = 1.46$  nm.

$\Gamma_{h1}$  is calculated by Eq. (2.49) and with the help of Eqs. (2.53)-(2.55). Figs. 3.22, 3.23 and 3.24 show imaginary Part of eigen Energy of ground eigen state of higher valley  $\Gamma_{h1}$  as a function of quantum mechanically corrected surface potential  $\phi_s$ , calculated by Eq. (2.49) and self-consistent numerical simulator as well for low, moderate and high substrate doping densities respectively and results show a good agreement between these two forms of calculations for all the cases.

Fig. 3.22: Imaginary part of complex ground eigen state of upper valley vs. surface potential for MOSFET with Al/SiO<sub>2</sub>/Si structure. Here,  $N_A$  = 5 × 10<sup>16</sup> cm<sup>-3</sup> and  $T_{ox}$  = 1.46 nm.

Fig. 3.23: Imaginary part of complex ground eigen state of upper valley vs. surface potential for MOSFET with Al/SiO<sub>2</sub>/Si structure. Here,  $N_A=10^{17}~{\rm cm}^{-3}$  and  $T_{ox}=1.46~{\rm nm}$ .

Fig. 3.24: Imaginary part of complex ground eigen state of upper valley vs. surface potential for MOSFET with Al/SiO<sub>2</sub>/Si structure. Here,  $N_A = 10^{18}$  cm<sup>-3</sup> and  $T_{ox} = 1.46$  nm.

#### 3.4 Direct Tunneling Gate Current, J

Finally, Direct Tunneling Gate Current, J is calculated by adding the currents that tunnel from the considered eigen states using Eq. (2.56). Figs. 3.25, 3.26 and 3.27 show Direct Tunneling gate current as a function of gate voltage  $V_g$ , calculated by developed compact model and self-consistent numerical simulator as well for low, moderate and high substrate doping densities respectively and results show very good agreement between these two forms of calculations for all the cases.

Fig. 3.25: Direct Tunneling gate current vs. Gate voltage for MOSFET with Al/SiO<sub>2</sub>/Si structure. Here,  $N_A = 5 \times 10^{16}$  cm<sup>-3</sup> and  $T_{ox} = 1.46$  nm.

Fig. 3.26: Direct Tunneling gate current vs. Gate voltage for MOSFET with Al/SiO<sub>2</sub>/Si structure. Here,  $N_A=10^{17}~{\rm cm}^{-3}$  and  $T_{ox}=1.46~{\rm nm}$ .

Figs. 3.28 and 3.29 show Direct Tunneling gate current as a function of gate voltage  $V_g$ , calculated by developed compact model and self-consistent numerical simulator for low and high substrate doping densities respectively with oxide thickness  $T_{ox}=1.55$  nm. Results show very good agreement

Fig. 3.27: Direct Tunneling gate current vs. Gate voltage for MOSFET with Al/SiO<sub>2</sub>/Si structure. Here,  $N_A = 10^{18}$  cm<sup>-3</sup> and  $T_{ox} = 1.46$  nm.

between these two forms of calculations in both figures.

Fig. 3.28: Direct Tunneling gate current vs. Gate voltage for MOSFET with Al/SiO<sub>2</sub>/Si structure. Here,  $N_A=8\times10^{16}$  cm<sup>-3</sup> and  $T_{ox}=1.55$  nm.

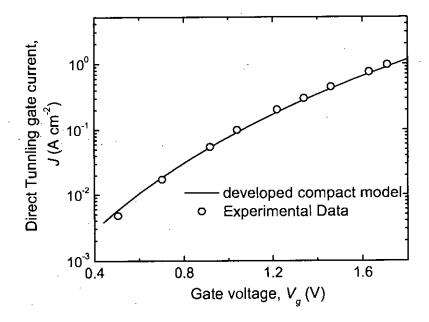

Figs. 3.30 and 3.31 compares Direct Tunneling gate current as a function of gate voltage  $V_g$ , calculated by developed compact model and self-consistent

Fig. 3.29: Direct Tunneling gate current vs. Gate voltage for MOSFET with Al/SiO $_2$ /Si structure. Here,  $N_A=8\times10^{17}~{\rm cm}^{-3}$  and  $T_{ox}=1.55~{\rm nm}$ .

numerical simulator, with experimental data taken from [6] for two different oxide thickness. Results show very good agreement between these two forms of calculations and with experimental data as well in both figures.

Fig. 3.30: Direct Tunneling gate current vs. Gate voltage for MOSFET with Al/SiO<sub>2</sub>/Si structure. Here,  $N_A$  = 5 × 10<sup>17</sup> cm<sup>-3</sup> and  $T_{ox}$  = 1.46 nm.

Fig. 3.31: Direct Tunneling gate current vs. Gate voltage for MOSFET with Al/SiO<sub>2</sub>/Si structure. Here,  $N_A=5\times 10^{17}~{\rm cm^{-3}}$  and  $T_{ox}=1.55~{\rm nm}$ .

Fig. 3.32: Direct Tunneling gate current vs. Gate voltage for MOSFET with Al/SiO<sub>2</sub>/Si structure. Here,  $N_A$  = 5 × 10<sup>17</sup> cm<sup>-3</sup> and  $T_{ox}$  = 1.79 nm.

To validate the robustness of the developed compact model, Figs. 3.32, 3.33 and 3.34 compare Direct Tunneling gate current J, as a function of gate voltage  $V_g$ , calculated by developed compact model with experimental data for different oxide thicknesses and substrate doping densities. In Figs. 3.32 and 3.33

experimental data is taken from [6] and in Figs. 3.34 experimental data is taken from [13]. Here also the results show very good agreement with experimental data in both figures.