## **Analytical Modeling of the Pocket Implanted Nano Scale n-MOSFET**

by Muhibul Haque Bhuyan

# DOCTOR OF PHILOSOPHY IN ELECTRICAL AND ELECTRONIC ENGINEERING

Department of Electrical and Electronic Engineering

BANGLADESH UNIVERSITY OF ENGINEERING AND TECHNOLOGY

**CANDIDATE'S DECLARATION**

It is hereby declared that this thesis titled "Analytical Modeling of the Pocket

Implanted Nano Scale n-MOSFET" or any part of it has not been submitted

elsewhere for the award of any degree or diploma.

Signature of the candidate

**Muhibul Haque Bhuyan**

Roll No: P04030604P Registration #: 91182

prolitical

i

The thesis titled "Analytical Modeling of the Pocket Implanted Nano Scale n-MOSFET" submitted by Muhibul Haque Bhuyan, Roll No: P04030604P, Registration No: 91182, Session: April 2003 has been accepted as satisfactory in partial fulfillment of the requirement for the degree of Doctor of Philosophy in Electrical and Electronic Engineering on 30 July 2011

**BOARD OF EXAMINERS** Dr. Quazi Deen Mohd Khosru Chairman Professor (Supervisor) Department of EEE, BUET, Dhaka Member Dr. Md. Saifur Rahman (Ex-officio) Professor and Head Department of EEE, BUET, Dhaka Dr. M. M. Shahidul Hassan Member Professor Department of EEE, BUET, Dhaka Dr. Md. Shafiqul Islam Member Professor Department of EEE, BUET, Dhaka Member Dr. A. B. M. Harun-Ur-Rashid Professor Department of EEE, BUET, Dhaka Dr. Md. Ziaur Rahman Khan Member Associate Professor Department of EEE, BUET, Dhaka Dr. Syed Kamrul Islam Member Professor (External) Department of Electrical Engineering and Computer Science The University of Tennessee, Knoxville, TN, USA

### **Dedication**

#### **Dedicated to**

# My Parents, My Wife, My Daughter and the Other Family Members

who have always inspired and supported me and also sacrificed many things for me to carry on my research work smoothly

# **Contents**

| Ack   | nowledgments                              | xvii |

|-------|-------------------------------------------|------|

| Abst  | tract                                     | xix  |

| Ch    | apter 1                                   |      |

| Intr  | roduction                                 | 1    |

| 1.1   | Introduction                              | 1    |

| 1.2   | Moore's Law                               | 1    |

| 1.3   | Device Scaling                            | 4    |

| 1.4   | Literature Review                         | 7    |

| 1.4.1 | Present RSCE Models                       | 7    |

| 1.4.2 | Surface Potential                         | 8    |

| 1.4.3 | Threshold Voltage                         | 9    |

| 1.4.4 | Temperature Effects                       | 9    |

| 1.4.5 | Inversion Layer Effective Mobility        | 10   |

| 1.4.6 | Subthreshold Drain Current                | 10   |

| 1.4.7 | Low Frequency Drain Current Flicker Noise | 11   |

| 1.5   | Objectives                                | 12   |

| 1.6   | Methodology                               | 12   |

| 1.7   | Organization of the Thesis                | 14   |

# **Chapter 2**

| Poc   | ket Implanted n-MOSFET                                 | 15 |

|-------|--------------------------------------------------------|----|

| 2.1   | Introduction                                           | 15 |

| 2.2   | Threshold voltage control                              | 16 |

| 2.3   | Short Channel Effects                                  | 19 |

| 2.3.1 | Threshold voltage roll-off in linear region            | 20 |

| 2.3.2 | Combating Short Channel Effects                        | 23 |

| 2.4   | Formation of the Pocket Implanted n-MOSFET             | 25 |

| 2.5   | Characterization and Modeling of Pocket Doping Profile | 29 |

| 2.5.1 | Characterization of Pocket Doping Profile              | 30 |

| 2.5.2 | Modeling of Pocket Doping Profile                      | 32 |

| 2.6   | Summary                                                | 36 |

|       |                                                        |    |

| Ch    | apter 3                                                |    |

| Mo    | deling Pocket Implanted n-MOSFET                       | 37 |

| 3.1   | Introduction                                           | 37 |

| 3.2   | Model Derivation                                       | 38 |

| 3.2.1 | Surface Potential Model                                | 39 |

| 3.2.2 | Threshold Voltage Model                                | 44 |

| 3.2.3 | Inversion Layer Effective Mobility Model               | 47 |

| 3.2.4 | Subthreshold Drain Current Model                       | 55 |

| 3.2.5 | Low Frequency Drain Current Flicker Noise Model        | 58 |

| 3.3   | Summary                                                | 62 |

# **Chapter 4**

| Sim   | ulation Results and Discussions                 | 63  |

|-------|-------------------------------------------------|-----|

| 4.1   | Introduction                                    | 63  |

| 4.2   | Surface Potential Model                         | 64  |

| 4.3   | Threshold Voltage Model                         | 70  |

| 4.3.1 | Bias Effects                                    | 70  |

| 4.3.2 | Temperature Effects                             | 78  |

| 4.4   | Inversion Layer Effective Mobility Model        | 84  |

| 4.5   | Subthreshold Drain Current Model                | 89  |

| 4.6   | Low Frequency Drain Current Flicker Noise Model | 96  |

| 4.7   | Summary                                         | 101 |

|       |                                                 |     |

| Ch    | apter 5                                         |     |

| Con   | nclusions                                       | 102 |

| 5.1   | Conclusion                                      | 102 |

| 5.2   | Limitations of the Work                         | 103 |

| 5.3   | Future Scopes                                   | 103 |

|       |                                                 |     |

| List  | t of Publications                               | 105 |

| Bib   | liography                                       | 107 |

| Арр   | pendix                                          | 116 |

# **List of Tables**

| Table<br>Number | Title of the Tables                                                                                             | Page Number |  |  |

|-----------------|-----------------------------------------------------------------------------------------------------------------|-------------|--|--|

| 1.1             | Road map of MOSFET minimum feature size 2010 update [5]                                                         | 4           |  |  |

| 4.1             | Minimum surface potential and its position along the channel from the source side for different channel lengths | 66          |  |  |

# **List of Figures**

| Figure<br>Number | Captions of the Figures                                                                                                                                                                                                                                                                                 | Page<br>Number |

|------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------|

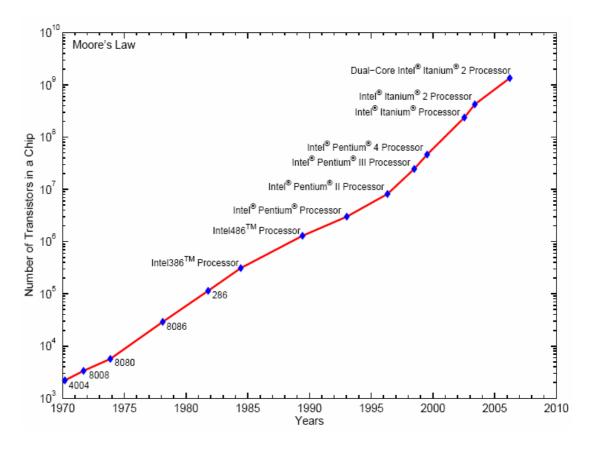

| 1.1              | Moore's Law [5]                                                                                                                                                                                                                                                                                         | 2              |

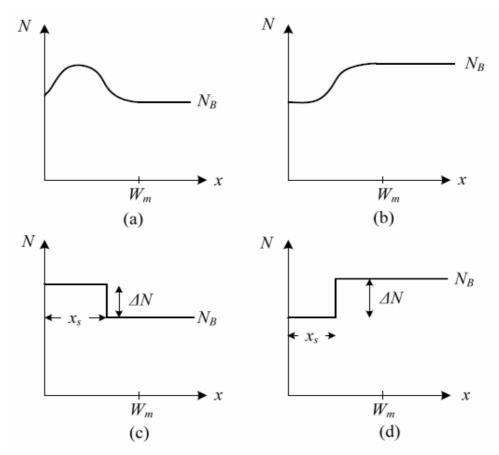

| 2.1              | Non-uniform channel doping profiles. (a) high-low profile. (b) low-high profile. (c) step-profile approximation of high-low profile (d) step-profile approximation of low-high profile [1]                                                                                                              | 17             |

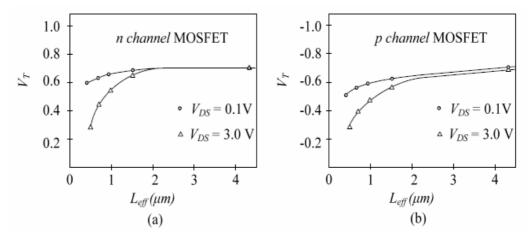

| 2.2              | Dependence of threshold voltage on effective channel length $(L_{\it eff})$ and drain bias [82]                                                                                                                                                                                                         | 21             |

| 2.3              | Schematic of the charge-sharing model [1]                                                                                                                                                                                                                                                               | 21             |

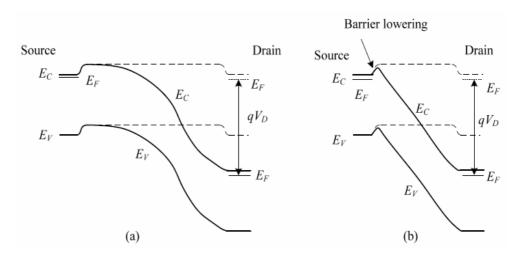

| 2.4              | Energy-band diagram at the semiconductor surface from source to drain, for (a) long-channel MOSFET and (b) short-channel MOSFET showing DIBL effect. Dash line is for zero drain bias and solid line is for energy-band diagram at the semiconductor surface from source to drain for $V_D\!>\!0\ [81]$ | 23             |

| 2.5              | Short Channel Effects in conventional bulk n-MOSFET                                                                                                                                                                                                                                                     | 24             |

| 2.6              | Reduction of Short Channel Effects in conventional bulk n-MOSFET                                                                                                                                                                                                                                        | 25             |

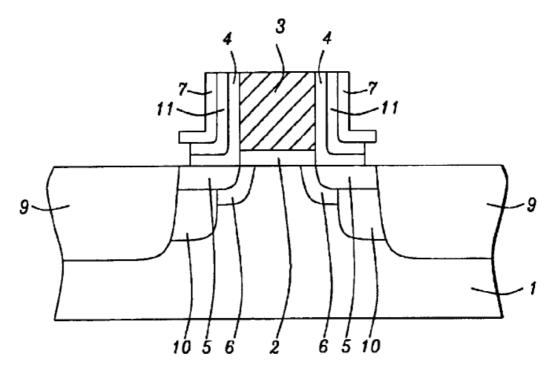

|                  | Pocket implanted n-MOSFET with composite insulator spacers [84], various regions numbers are shown in the texts in parenthesis                                                                                                                                                                          | 27             |

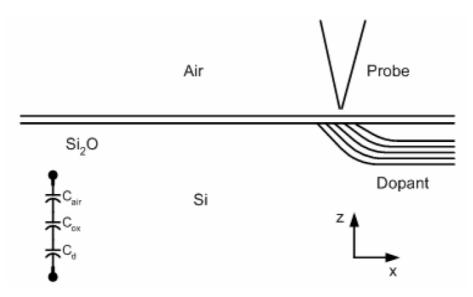

| 2.8              | Illustration of the basic concept of scanning capacitance microscopy                                                                                                                                                                                                                                    | 31             |

| 2.9              | Block diagram of the SCM apparatus with sample at bias voltage, $\it V$                                                                                                                                                                                                                                 | 31             |

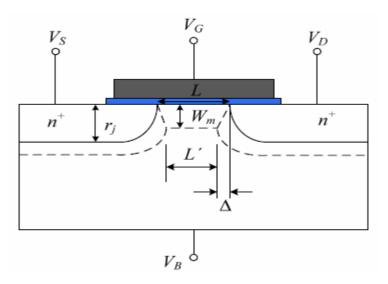

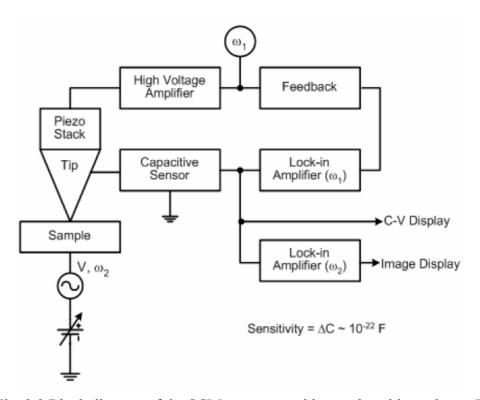

| 2.10             | Pocket Implanted n-MOSFET Structure                                                                                                                                                                                                                                                                     | 32             |

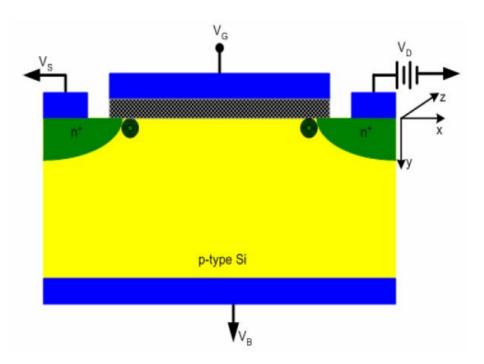

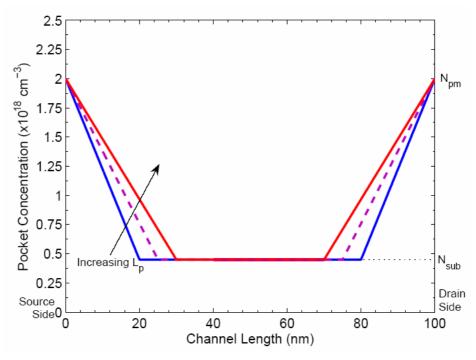

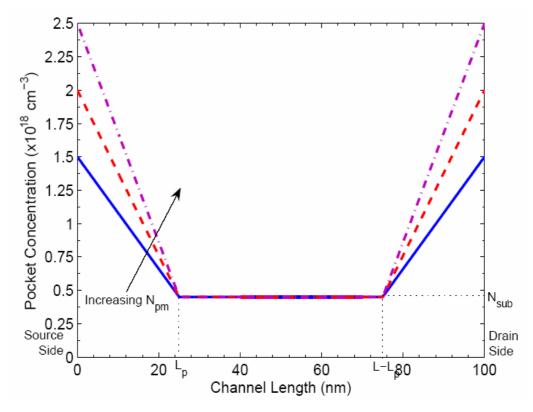

| 2.11             | Simulated pocket profiles at the surface for different pocket lengths, $L_p = 20$ , 25 and 30 nm; peak pocket concentration, $N_{pm} = 1.75 \times 10^{18} \text{ cm}^{-3}$                                                                                                                             | 34             |

| 2.12             | Simulated pocket profiles at the surface for various peak pocket concentrations, $N_{pm} = 1.25 \times 10^{18}$ , $1.5 \times 10^{18}$ and $1.75 \times 10^{18}$ cm <sup>-3</sup> and pocket length, $L_p = 25$ nm                                                                                      | 35             |

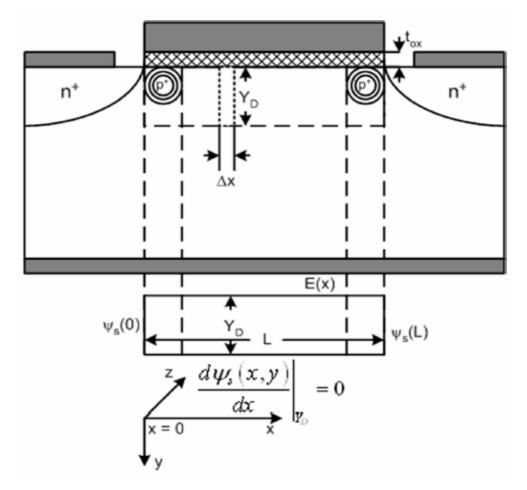

| 3.1              | Schematic diagram showing n-MOSFET with p+ pocket implant regions (upper figure) and Gaussian box; detailed Gaussian box with boundary conditions (lower figure) to get the surface potential model                                                                                                     | 40             |

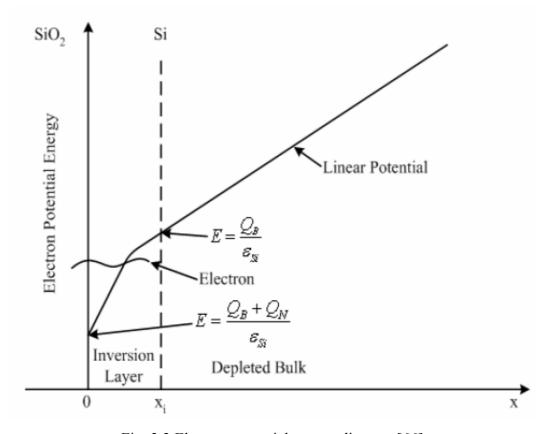

| 3.2              | Band diagram of metal oxide semiconductor structure [108]                                                                                                                                                                                                                                               | 47             |

| 3.3              | Electron potential energy diagram [66]                                                                                                                                                                                                                                                                  | 48             |

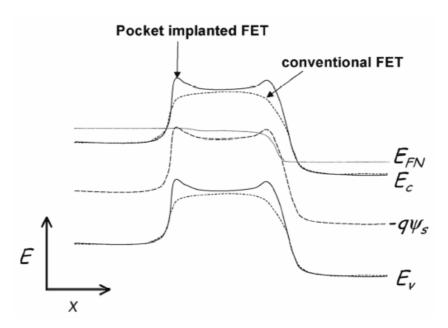

| 3.4  | Schematic energy band diagram in the channel region of the pocket implanted n-MOSFET. It is to be noted that the potential barriers caused by the pocket implants that also affect the surface potential $\psi_s$ [72]                 | 56 |

|------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

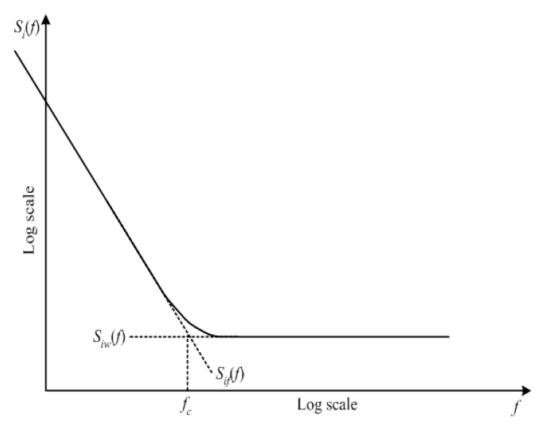

| 3.5  | A typical plot of the drain-noise current power spectral density vs. frequency in log-log axes                                                                                                                                         | 59 |

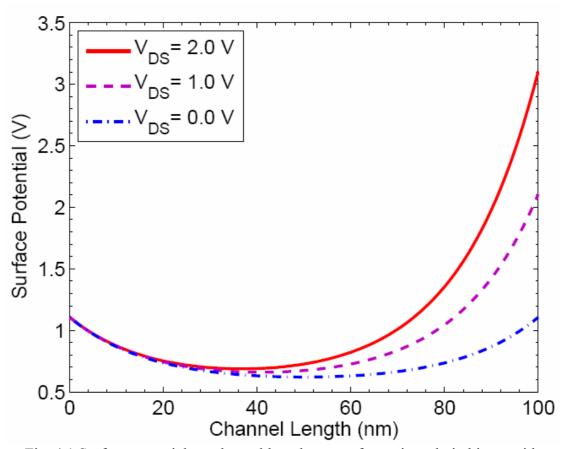

| 4.1  | Surface potential vs. channel length curves for various drain biases with channel length, $L=100$ nm and substrate bias, $V_{BS}=0.0 \text{ V}$                                                                                        | 64 |

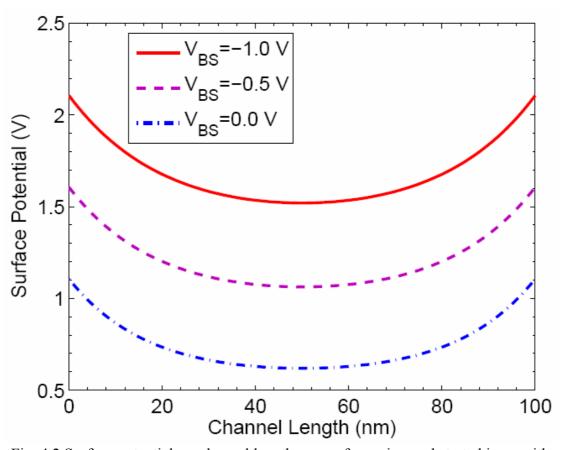

| 4.2  | Surface potential vs. channel length curves for various substrate biases with channel length, $L=100$ nm and drain bias, $V_{DS}=0.0$ V                                                                                                | 65 |

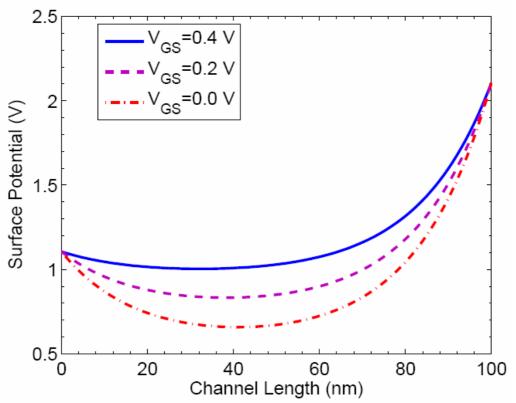

| 4.3  | Surface potential curves along the channel for various gate biases below the threshold voltage with channel length, $L = 100$ nm, substrate bias, $V_{BS} = 0.0$ V and drain bias, $V_{DS} = 1.0$ V                                    | 66 |

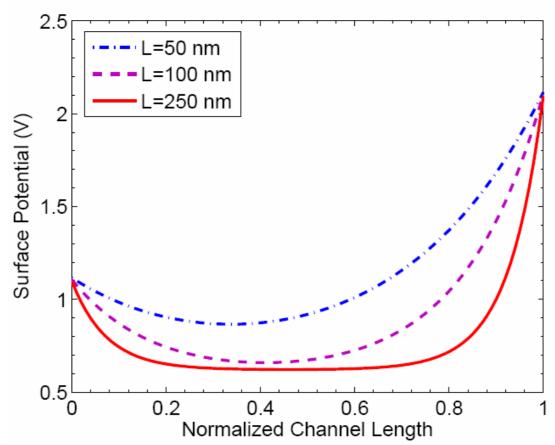

| 4.4  | Surface potential curves along the channel for various channel lengths with substrate bias, $V_{BS} = 0.0 \text{ V}$ and drain bias, $V_{DS} = 1.0 \text{ V}$                                                                          | 67 |

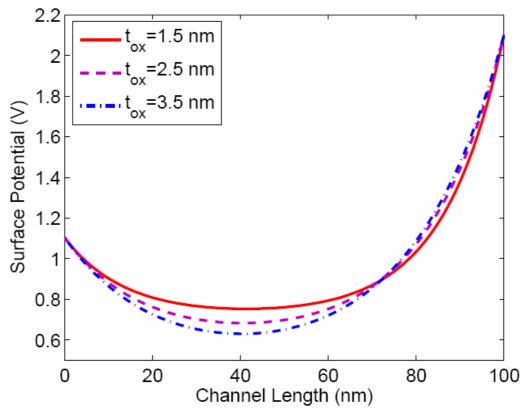

| 4.5  | Surface potential curves along the channel for various oxide thicknesses with channel length, $L = 100$ nm, substrate bias, $V_{BS} = 0.0 \text{ V}$ and drain bias, $V_{DS} = 1.0 \text{ V}$                                          | 68 |

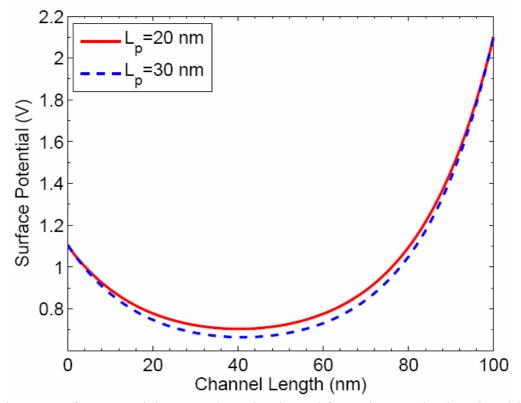

| 4.6  | Surface potential curves along the channel for various pocket lengths with channel length, $L = 100$ nm, substrate bias, $V_{BS} = 0.0 \text{ V}$ and drain bias, $V_{DS} = 1.0 \text{ V}$                                             | 68 |

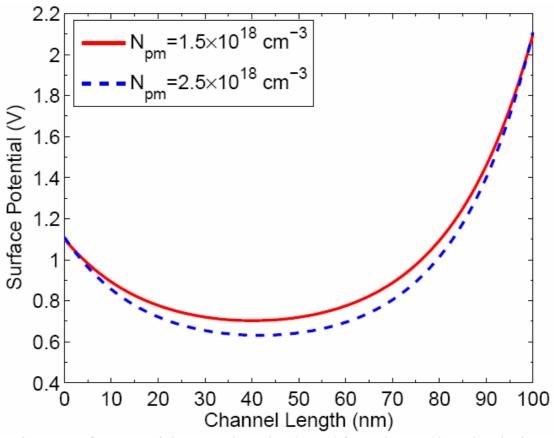

| 4.7  | Surface potential curves along the channel for various peak pocket doping concentration with channel length, $L = 100$ nm, substrate bias, $V_{BS} = 0.0$ V and drain bias, $V_{DS} = 1.0$ V                                           | 69 |

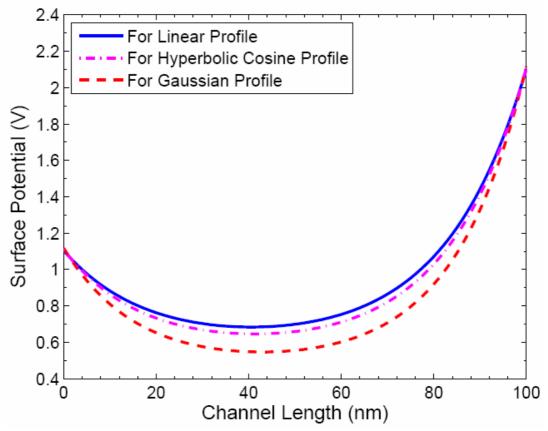

| 4.8  | Surface potential curves along the channel for various pocket profiles found in the literatures with channel length, $L = 100$ nm, substrate bias, $V_{BS} = 0.0$ V, drain bias and $V_{DS} = 1.0$ V                                   | 70 |

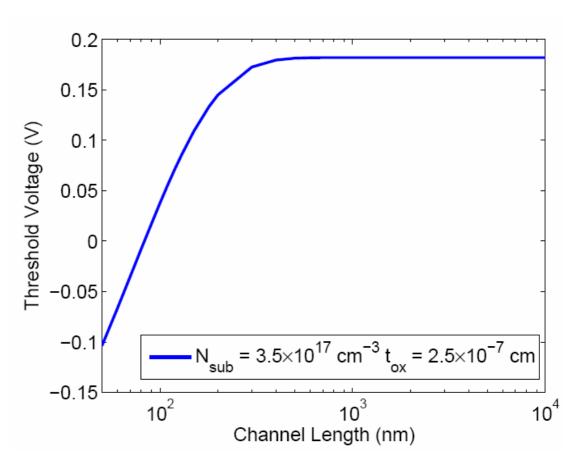

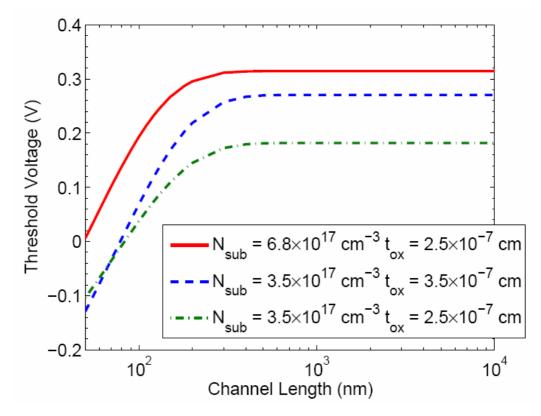

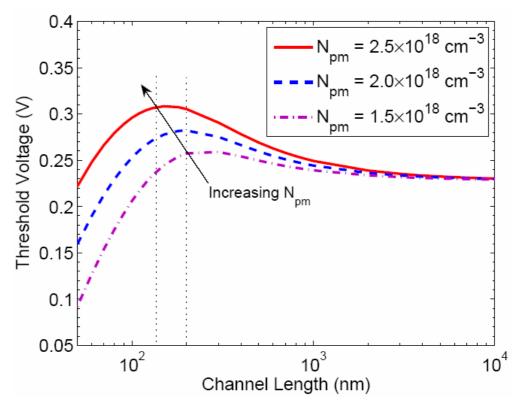

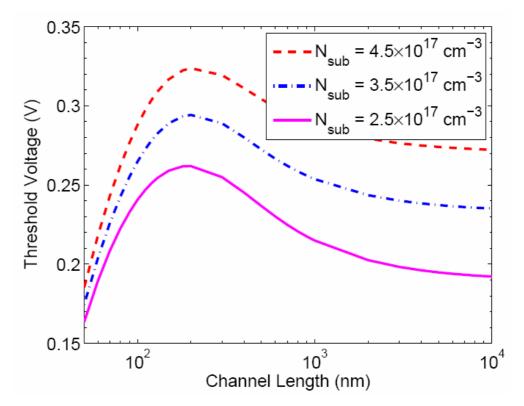

| 4.9  | Threshold voltage vs. channel length curves along the channel for various peak pocket doping concentration with $V_{BS} = 0.0 \text{ V}$ , $V_{DS} = 0.0 \text{ V}$ and pocket length, $L_p = 25 \text{ nm}$                           | 71 |

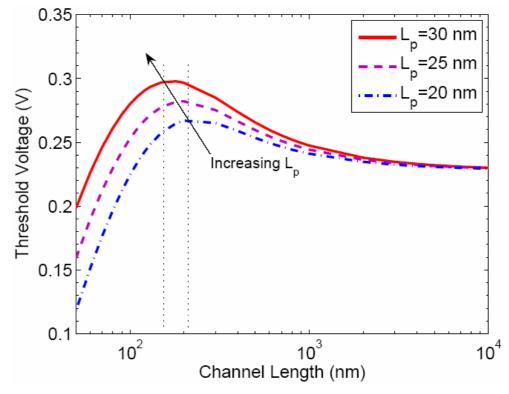

| 4.10 | Threshold voltage vs. channel length curves along the channel for various pocket lengths with $V_{BS} = 0.0 \text{ V}$ , $V_{DS} = 0.0 \text{ V}$ and peak pocket doping concentration, $N_{pm} = 1.75 \times 10^{18} \text{ cm}^{-3}$ | 71 |

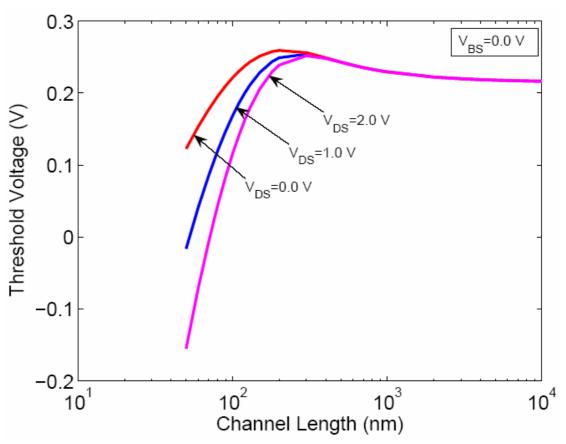

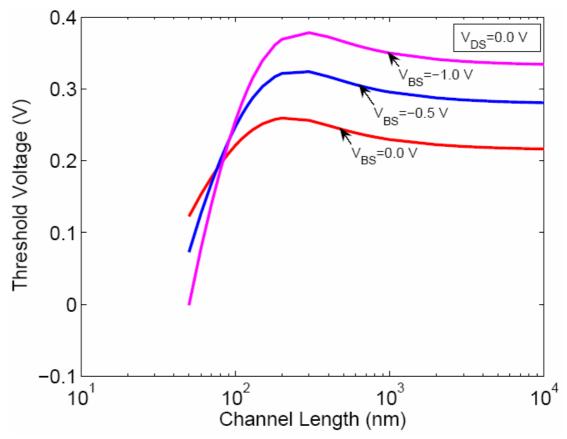

| 4.11 | Threshold voltage vs. gate length curves for various drain biases at zero substrate bias                                                                                                                                               | 72 |

| 4.12 | Threshold voltage vs. gate length curves for various substrate biases at zero drain bias                                                                                                                                               | 73 |

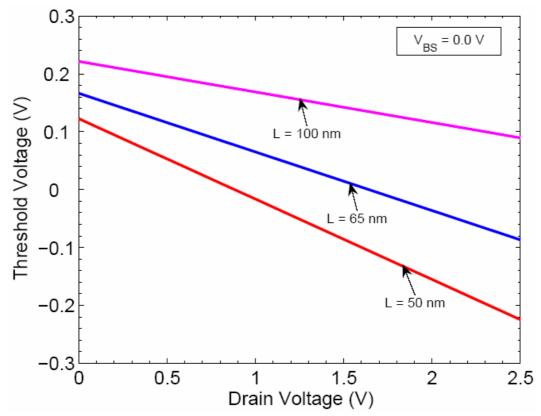

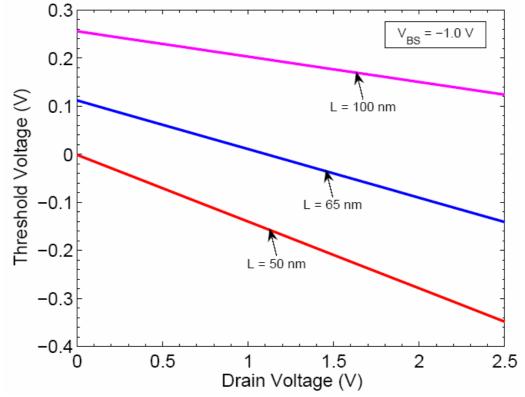

| 4.13 | Threshold voltage vs. drain voltage curves for various gate lengths with substrate bias, $V_{BS} = 0.0 \ V$                                                                                                                            | 74 |

| 4.14 | Threshold voltage vs. drain voltage curves for various gate lengths with substrate bias, $V_{\rm BS}$ = -1.0 V                                                                                                                         | 74 |

|      |                                                                                                                                                                                                                                        |    |

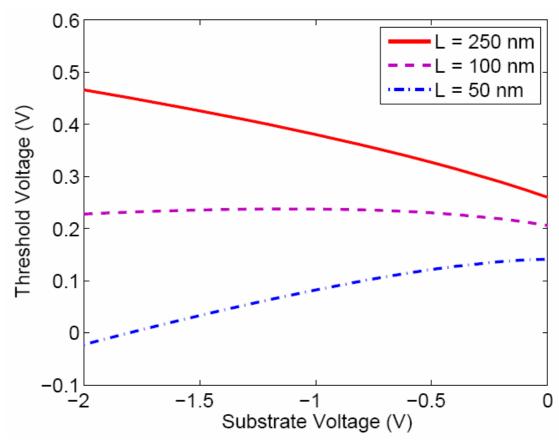

| 4.15 | Threshold voltage vs. substrate voltage curves for various gate lengths with $V_{DS} = 0.0 \text{ V}$                                                                                                                                                                | 75 |

|------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

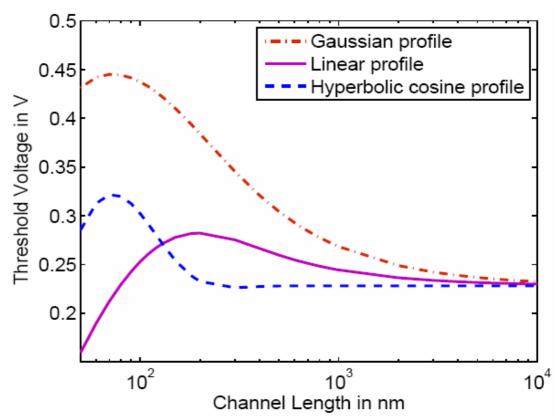

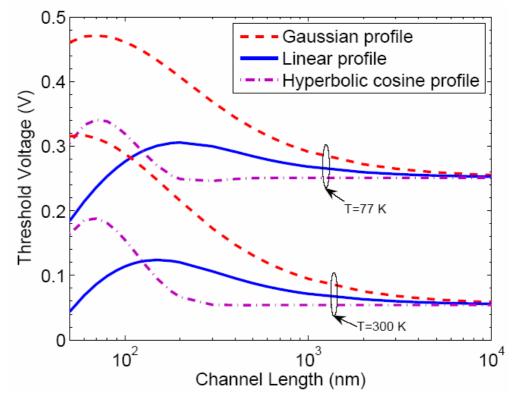

| 4.16 | Threshold voltage vs. gate length curves for three different pocket profiles based on linear, Gaussian and hyperbolic cosine functions for $N_{pm} = 1.75 \times 10^{18}$ cm <sup>-3</sup> , $L_p = 25$ nm and $N_{sub} = 4.2 \times 10^{17}$ cm <sup>-3</sup>       | 76 |

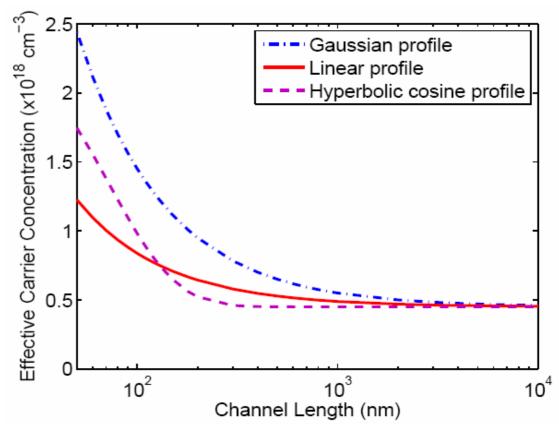

| 4.17 | Effective carrier concentration with channel lengths for three different pocket profiles based on linear, Gaussian and hyperbolic cosine functions for $N_{pm}=1.75\times10^{18}~cm^{-3}$ , $L_p=25~nm$ and $N_{sub}=4.2\times10^{17}~cm^{-3}$                       | 77 |

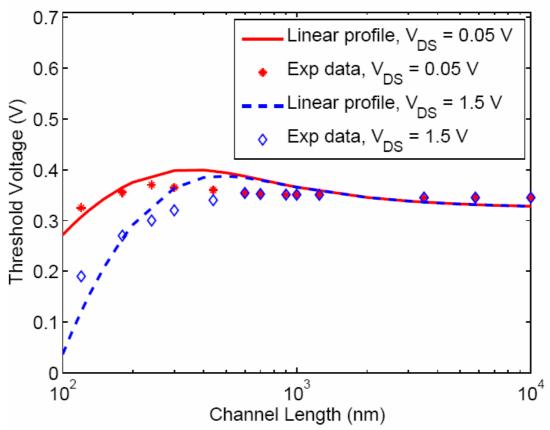

| 4.18 | Fitting experimental data of reference [33] to the simulated results of the proposed linear pocket profile based threshold voltage model                                                                                                                             | 78 |

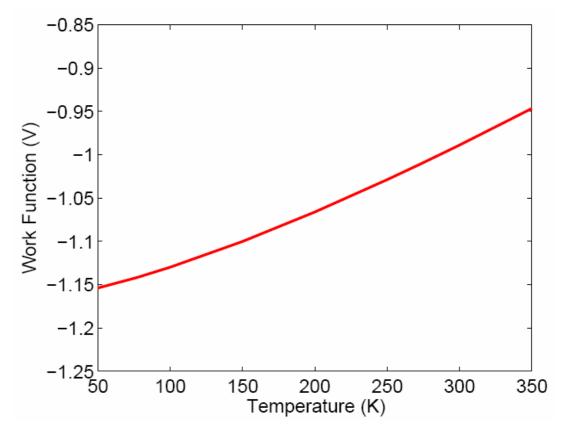

| 4.19 | Metal-Semiconductor work function difference variation with temperature                                                                                                                                                                                              | 79 |

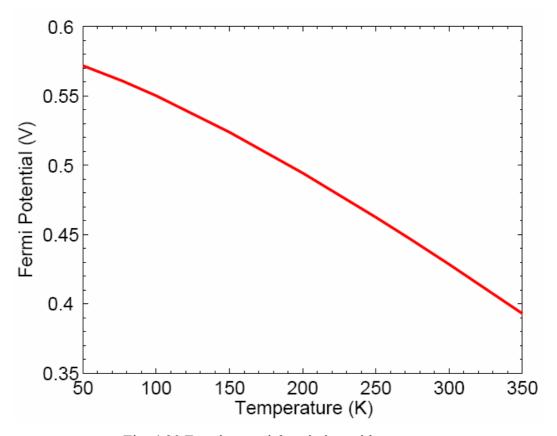

| 4.20 | Fermi potential variation with temperature                                                                                                                                                                                                                           | 79 |

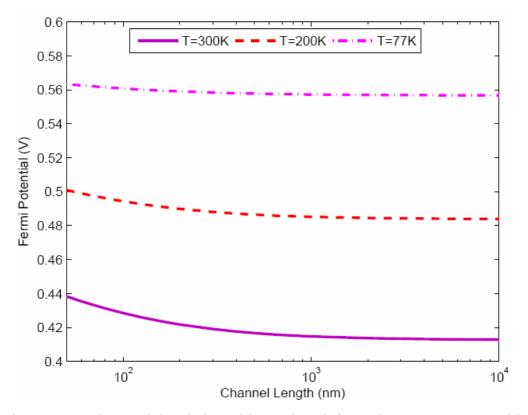

| 4.21 | Fermi potential variation with gate length for various temperatures with drain bias, $V_{DS} = 0.1 \text{ V}$ and substrate bias, $V_{BS} = 0.0 \text{ V}$                                                                                                           | 80 |

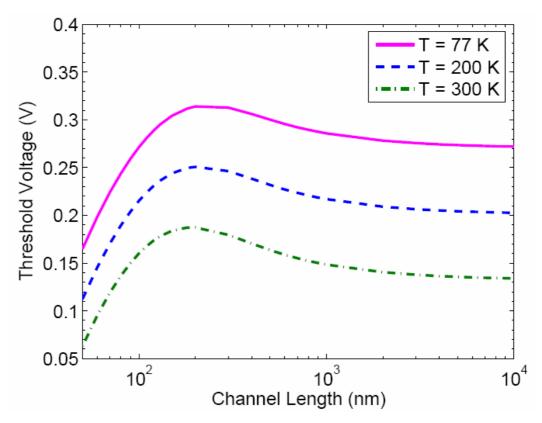

| 4.22 | Threshold voltage variation with gate length for various temperatures with drain bias, $V_{DS} = 0.05$ V and substrate bias, $V_{BS} = 0.0$ V                                                                                                                        | 81 |

| 4.23 | Comparison of threshold voltage variation vs. gate length for various substrate concentrations at temperature of 77 K                                                                                                                                                | 82 |

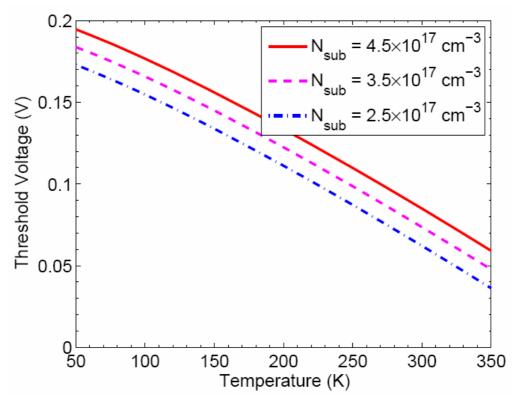

| 4.24 | Comparison of threshold voltage variation vs. temperature for various substrate concentrations at gate length, $L = 50 \text{ nm}$                                                                                                                                   | 82 |

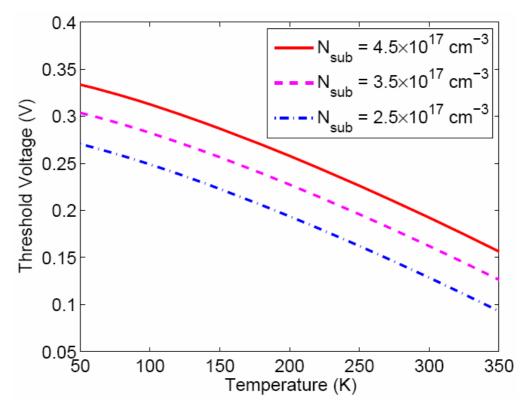

| 4.25 | Comparison of threshold voltage variation vs. temperature for various substrate concentrations at gate length, $L = 0.25 \mu m$                                                                                                                                      | 83 |

| 4.26 | Comparison of threshold voltage variation with gate length for various temperatures                                                                                                                                                                                  | 83 |

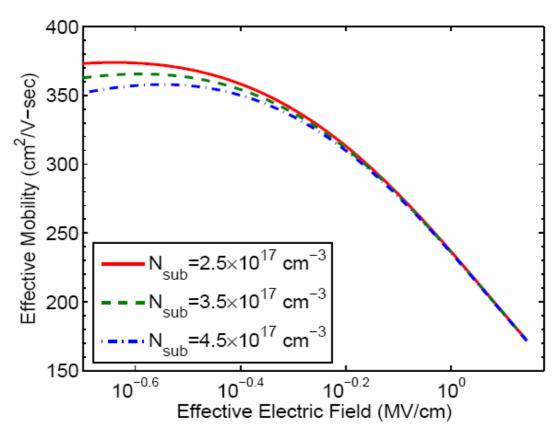

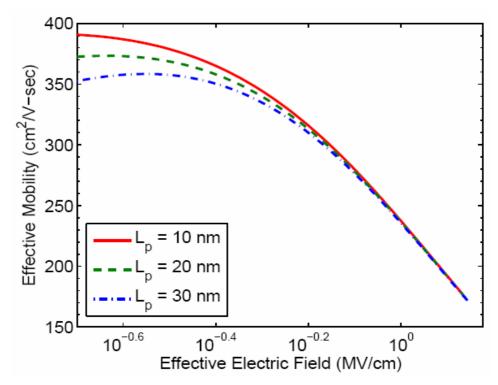

| 4.27 | Effective mobility vs. effective electric field for different substrate concentrations ( $N_{sub}$ ) with $L = 0.1  \mu m$ , $L_p = 25  nm$ , $N_{pm} = 1.75 \times 10^{18}  cm^{-3}$ , $V_{DS} = 0.05  V$ and $T = 300  K$                                          | 84 |

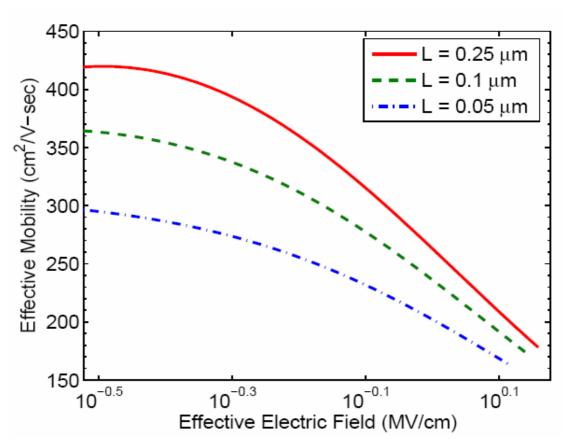

| 4.28 | Effective mobility vs. effective electric field for different channel lengths ( <i>L</i> ) with $N_{sub} = 3.5 \times 10^{17}$ cm <sup>-3</sup> , $L_p = 25$ nm, $N_{pm} = 1.75 \times 10^{18}$ cm <sup>-3</sup> , $V_{DS} = 0.05$ V and $T = 300$ K                 | 85 |

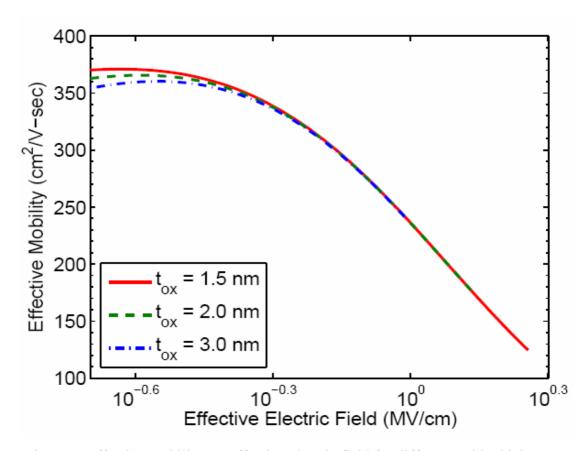

| 4.29 | Effective mobility vs. effective electric field for different oxide thicknesses ( $t_{ox}$ ) with $L_p = 25$ nm, $L = 0.1$ µm, $N_{sub} = 3.5 \times 10^{17}$ cm <sup>-3</sup> , $N_{pm} = 1.75 \times 10^{18}$ cm <sup>-3</sup> , $V_{DS} = 0.05$ V and $T = 300$ K | 86 |

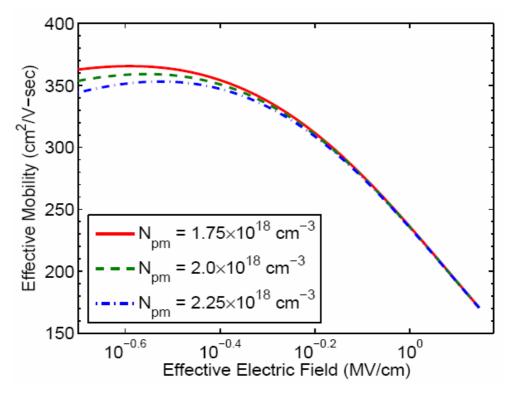

| 4.30 | Effective mobility vs. effective electric field for different peak pocket doping concentrations ( $N_{pm}$ ) with $L = 0.1$ µm, $L_p = 25$ nm, $N_{sub} = 3.5 \times 10^{17}$ cm <sup>-3</sup> , $V_{DS} = 0.05$ V and $T = 300$ K                                   | 87 |

| 4.31 | Effective mobility vs. effective electric field for different pocket lengths $(L_p)$ with $L=0.1$ µm, $N_{sub}=3.5\times10^{17}$ cm <sup>-3</sup> , $N_{pm}=1.75\times10^{18}$ cm <sup>-3</sup> , $V_{DS}=0.05$ V and $T=300$ K                                      | 87 |

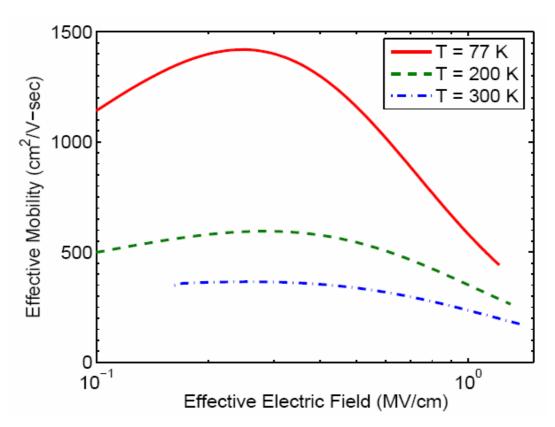

| 4.32 | Effective mobility vs. effective electric field for different temperatures ( $T$ ) with $L = 0.1 \mu m$ , $N_{sub} = 4.5 \times 10^{17} \text{ cm}^{-3}$ , $L_p = 25 \text{ nm}$ , $N_{pm} = 1.75 \times 10^{18} \text{ cm}^{-3}$ and $V_{DS} = 0.05 \text{ V}$ | 88 |

|------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

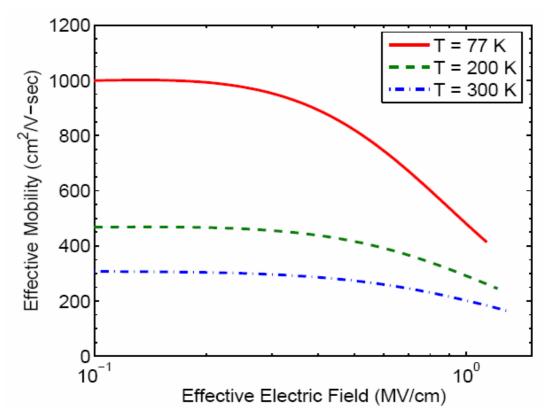

| 4.33 | Effective mobility vs. effective electric field for different temperatures ( <i>T</i> ) with $L = 50$ nm, $L_p = 25$ nm, $N_{sub} = 4.5 \times 10^{17}$ cm <sup>-3</sup> , $N_{pm} = 1.75 \times 10^{18}$ cm <sup>-3</sup> and $V_{DS} = 0.05$ V                | 89 |

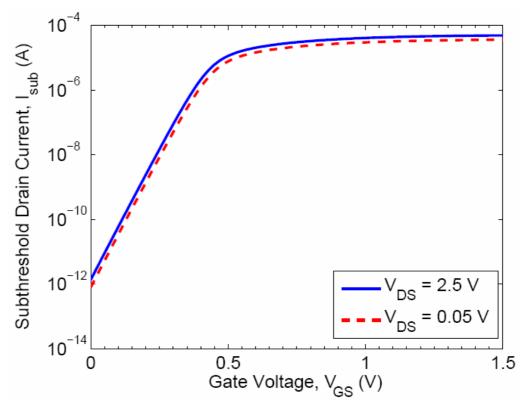

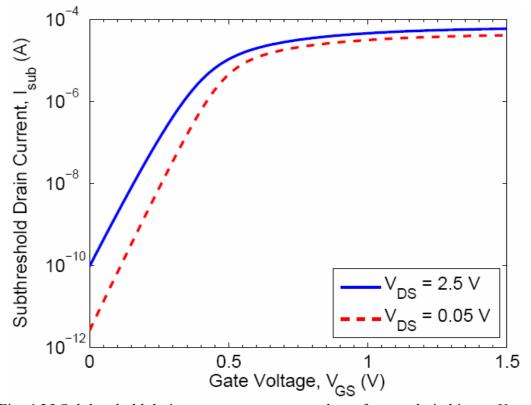

| 4.34 | Subthreshold drain current versus gate voltage for two drain biases, $V_{DS} = 0.05$ V and $V_{DS} = 2.5$ V with channel length, $L = 0.25 \mu \text{m}$                                                                                                        | 90 |

| 4.35 | Subthreshold drain current versus gate voltage for two drain biases, $V_{DS} = 0.05$ V and $V_{DS} = 2.5$ V with channel length, $L = 100$ nm                                                                                                                   | 90 |

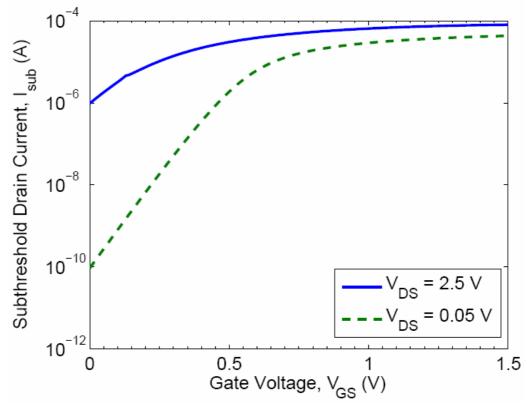

| 4.36 | Subthreshold drain current versus gate voltage for two drain biases, $V_{DS}$ = 0.05 V and $V_{DS}$ = 2.5 V with channel length, $L$ = 50 nm                                                                                                                    | 91 |

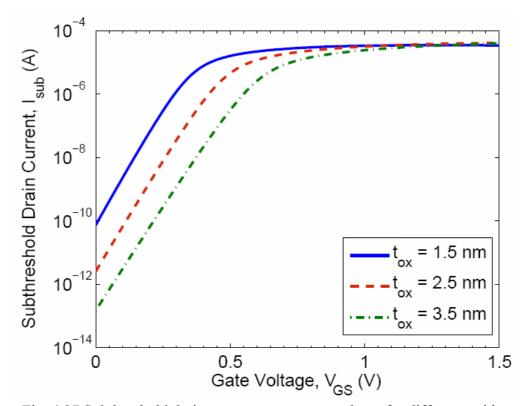

| 4.37 | Subthreshold drain current versus gate voltage for different oxide thicknesses with drain bias, $V_{DS} = 0.05$ V and channel length, $L = 100$ nm                                                                                                              | 91 |

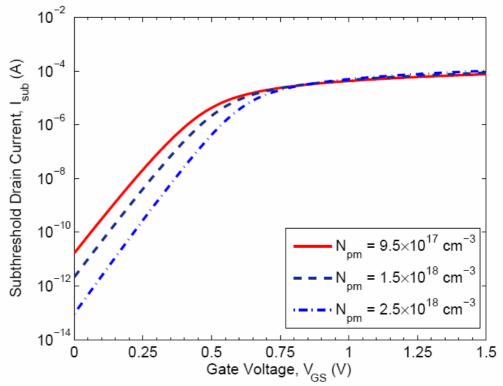

| 4.38 | Subthreshold drain current versus gate voltage for three different peak pocket implant concentrations, drain bias, $V_{DS} = 0.05 \text{ V}$ with $L = 100 \text{ nm}$                                                                                          | 92 |

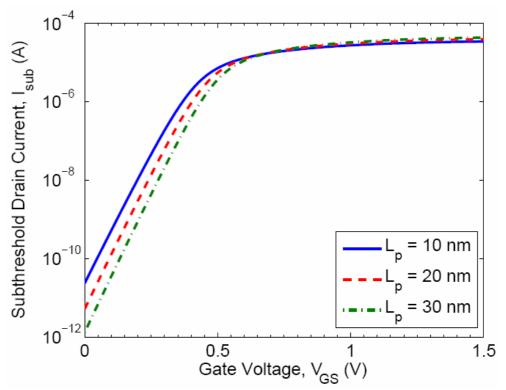

| 4.39 | Subthreshold drain current versus gate voltage for three different pocket lengths and drain bias, $V_{DS} = 0.05$ V with channel length, $L = 100$ nm                                                                                                           | 93 |

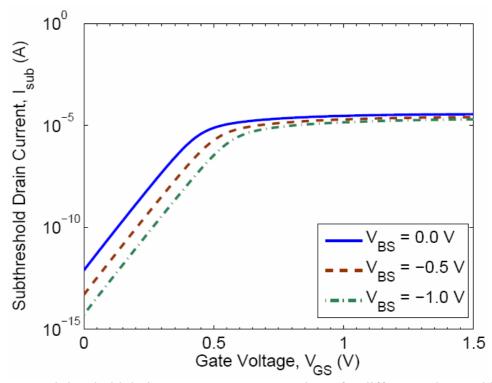

| 4.40 | Subthreshold drain current versus gate voltage for different substrate biases with $V_{DS} = 0.05$ V and $L = 0.25$ $\mu m$                                                                                                                                     | 94 |

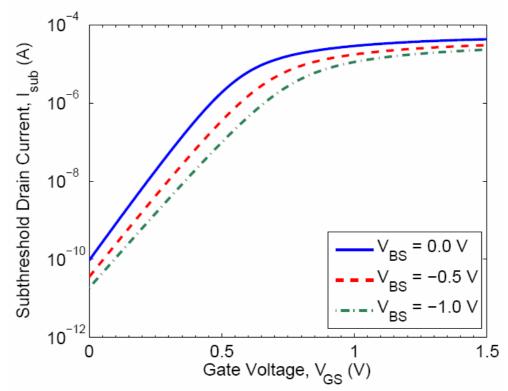

| 4.41 | Subthreshold drain current versus gate voltage for different substrate biases with $V_{DS} = 0.05$ V and $L = 100$ nm                                                                                                                                           | 94 |

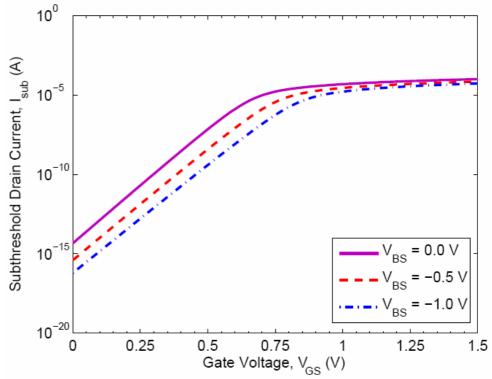

| 4.42 | Subthreshold drain current versus gate voltage for different substrate biases, $V_{BS} = 0.0 \text{ V}$ , -0.5 V and -1.0 V with drain bias, $V_{DS} = 0.1 \text{ V}$ and channel length, $L = 50 \text{ nm}$                                                   | 95 |

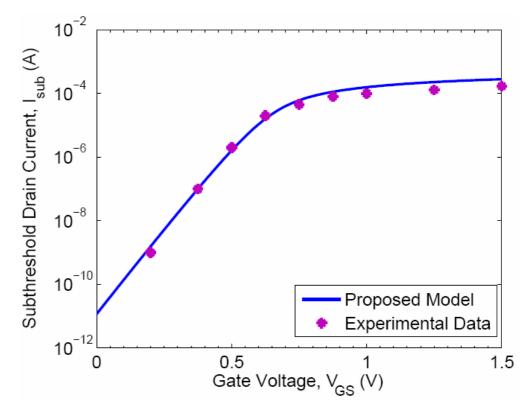

| 4.43 | Fitting experimental data already published in the literature [70] with the simulated results of the proposed subthreshold drain current model                                                                                                                  | 95 |

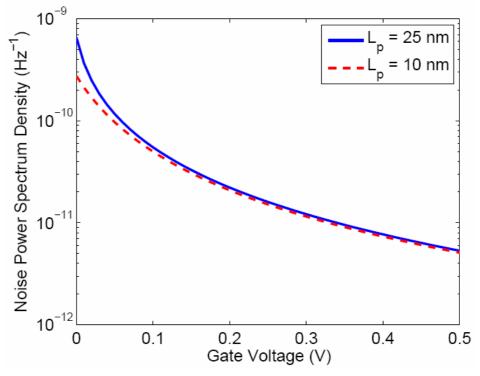

|      | Noise power spectrum density vs. gate voltage for different pocket lengths with $L = 50$ nm, $N_{pm} = 1.25 \times 10^{18}$ cm <sup>-3</sup> , $V_{DS} = 0.2$ V and $f = 100$ Hz                                                                                | 96 |

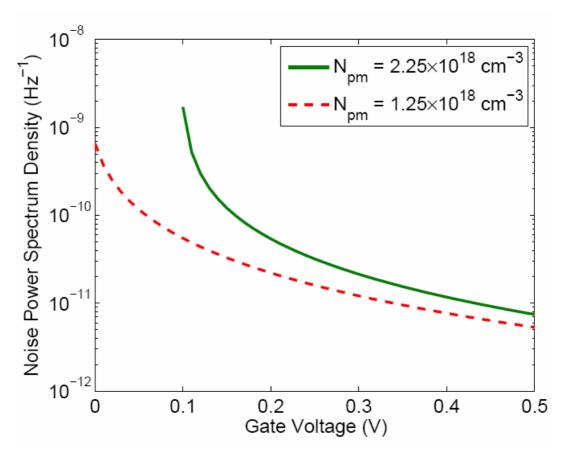

| 4.45 | Noise power spectrum density vs. gate voltage for two pocket doses with $L = 50$ nm, $L_p = 25$ nm, $V_{DS} = 0.2$ V and $f = 100$ Hz                                                                                                                           | 97 |

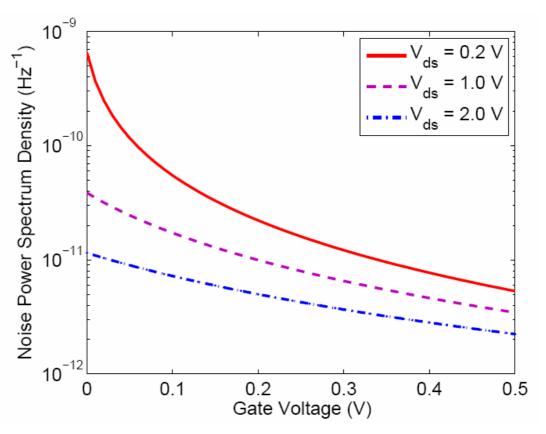

| 4.46 | Noise power spectrum density vs. gate voltage for different drain biases with $L = 50$ nm, $N_{pm} = 1.25 \times 10^{18}$ cm <sup>-3</sup> , $L_p = 25$ nm and $f = 100$ Hz                                                                                     | 98 |

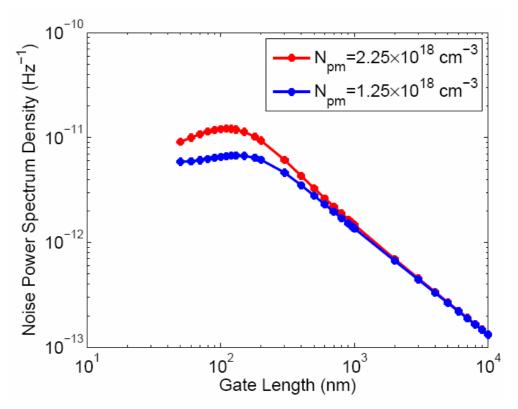

| 4.47 | Noise power spectrum density vs. gate length for two pocket doses with $L_p = 25$ nm, $V_{GS} = 0.5$ V, $V_{DS} = 0.2$ V and $f = 100$ Hz                                                                                                                       | 99 |

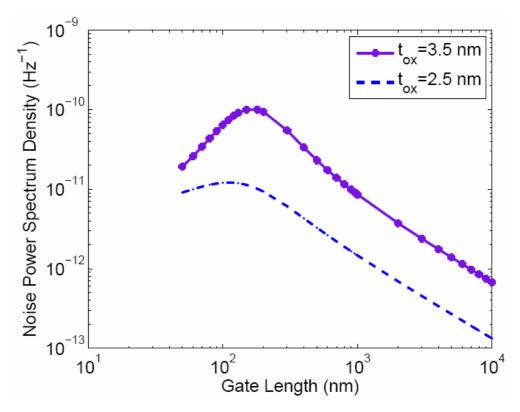

|      | Noise power spectrum density vs. gate length for different oxide                                                                                                                                     | 99  |

|------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

| 4.48 | thicknesses with $N_{pm} = 2.25 \times 10^{18}$ cm <sup>-3</sup> , $L_p = 25$ nm, $V_{GS} = 0.5$ V, $V_{DS} = 0.2$ V and $f = 100$ Hz                                                                |     |

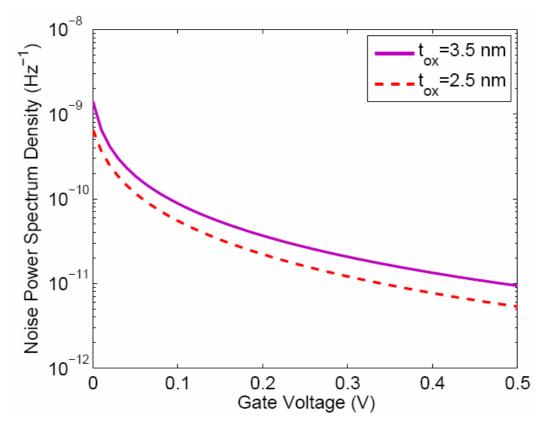

| 4.49 | Noise power spectrum density vs. gate bias for different oxide thicknesses with $N_{pm} = 1.25 \times 10^{18}$ cm <sup>-3</sup> , $L_p = 25$ nm, $V_{GS} = 0.5$ V, $V_{DS} = 0.2$ V and $f = 100$ Hz | 100 |

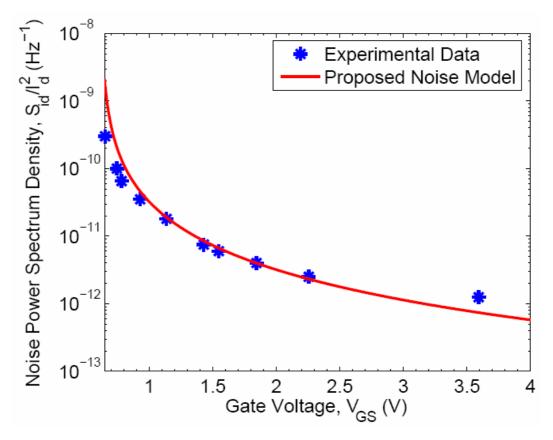

| 4.50 | Fitting experimental data already published in the literature [78] with the simulated results of the proposed low frequency drain current flicker poise model                                        | 101 |

#### **List of Abbreviations**

**Abbreviated Full Meaning**

Word

**AFM** Atomic Force Microscopy **APCVD** Atmospheric Pressure CVD **BPSG** Borophosphorus Silicate Glass **CLM** Channel Length Modulation

**CMOS** Complimentary Metal Oxide Semiconductor Field Effect Transistor

C-V Capacitance Voltage

**CVD** Chemical Vapor Deposition **DIBL Drain Induced Barrier Lowering**

**FET** Field Effect Transistor HCI Hot Carrier Injection HDPCVD

High Density Plasma CVD

**HFET** Heterojunction Field Effect Transistor

**ICP** Inductively Coupled Plasma

**IGFET** Insulated-Gate Field-Effect Transistor

**ILD** Inter Layer Dielectric

**ITRS** International Technology Roadmap for Semiconductors

**JFET** Junction Field Effect Transistor LATI Large-Angle-Tilt-Implanted

**LDD** Lightly Doped Drain LPCVD Low Pressure CVD

**MESFET** Metal Semiconductor Field Effect Transistor

Metal Insulator Semiconductor **MIS**

**MISFET** Metal Insulator Semiconductor Field Effect Transistor Metal Oxide Semiconductor Field Effect Transistor **MOSFET**

Plasma Enhanced CVD **PECVD** Potential Effect Transistor **PET PSG** Phosphorus Silicate Glass **Quantum Mechanical Effects QME**

RF Radio Frequency **RIE** Reactive Ion Etching

**RSCE** Reverse Short Channel Effect

**RTA** Rapid Thermal Anneal **RTP** Rapid Thermal Processor **SCE** Short Channel Effect

**SCM** Scanning Capacitance Microscopy

| Abbreviated Word | Full Meaning                     |

|------------------|----------------------------------|

| SIMS             | Secondary Ion Mass Spectroscopy  |

| SOI              | Silicon On Insulator             |

| STM              | Scanning Tunneling Microscopy    |

| TCAD             | Technology Computer Aided Design |

| TEOS             | Tetra Ethyle Ortho Silicate      |

| ULSI             | Ultra Large Scale Integration    |

| VLSI             | Very Large Scale Integration     |

# **List of Symbols**

| Symbols        | Name of the Symbols                                |

|----------------|----------------------------------------------------|

| $D_n$          | Diffusion Coefficient for Electron                 |

| $E_{e\!f\!f}$  | Effective Electric Field                           |

| $E_{fn}$       | Electron Fermi Level                               |

| $I_{D,sat}$    | Drain Saturation Current                           |

| $I_{DS}$       | Drain Current                                      |

| $I_{dsub}$     | Subthreshold drain current                         |

| $I_{sub}$      | Subthreshold Drain Current                         |

| $J_n$          | Electron Current Density                           |

| L              | Channel Length                                     |

| $L_{DH}$       | Debye-Huckel Value                                 |

| $L_p$          | Pocket Length                                      |

| $L_s$          | Screening Length                                   |

| $L_{TF}$       | Thomas-Fermi Value                                 |

| $L_{th}$       | Thermal Length                                     |

| $N_C$          | Effective Density Of States in the Conduction Band |

| $N_{ch}(x)$    | Lateral Non-Uniform Channel Doping                 |

| $N_{e\!f\!f}$  | Effective Doping Concentration                     |

| $n_i$          | Intrinsic carrier concentration of Si              |

| $N_{inv}$      | Number of Channel Carriers per unit Area           |

| $N_{pm}$       | Peak Pocket Doping Concentration                   |

| $N_{sd}$       | Source or drain doping concentration               |

| $N_{sub}$      | Substrate Doping Concentration                     |

| $N_V$          | Effective Density Of States in the Valence Band    |

| q              | Electronic Charge                                  |

| $Q_0$          | Oxide Charge per unit Area                         |

| $Q_{dep}$      | Depletion Region Charge per unit Area              |

| $Q_{inv}$      | Inversion Layer Charge                             |

| $Q_{it}$       | Interface Trap Density per unit Area               |

| $r_j$          | Junction Depth                                     |

| $S_{id}/I_d^2$ | Normalized Noise Power Spectrum Density            |

| T              | Absolute Temperature                               |

| $t_{ch}$       | Channel Thickness                                  |

| $t_{ox}$       | Oxide thickness                                    |

| v              | Carrier Velocity                                   |

| $V_{BS}$       | Substrate Voltage                                  |

| $V_{D,sat}$    | Drain Saturation Voltage                           |

| $V_{DS}$       | Drain Voltage                                      |

#### **Symbols** Name of the Symbols Fermi Velocity $v_F$ Flat Band Voltage $V_{FR}$ $V_{GS}$ Gate Voltage Thermal Velocity $v_{th}$ $V_{th}$ Threshold Voltage $V_{th L}$ Long Channel Threshold Voltage $V_{thp}$ Threshold Voltage in the Pocket Region $W_m$ Maximum Width of the Surface Depletion Region $X_D$ Depletion Width ZChannel Width **Electrostatic Potential** Ψ Electrostatic Potential in the Bulk $\psi_B$ **Electron Mobility** $\mu_n$ Hole Mobility $\mu_p$ Charge Density per unit Volume $\rho_s$ $\Phi m$ Work Function of Metal Work Function of Semiconductor $\Phi_{S}$ Electron Affinity of the Semiconductor χ **Dimensional Scaling Factor** $\alpha$ **Electric Field Scaling Factors** β Dielectric Permittivity of Oxide $\mathcal{E}_{ox}$ Dielectric Permittivity of Si $\mathcal{E}_{Si}$ Thermal Voltage $\phi_{th}$ Attenuation Coefficient of the Electron Wave Function γ Threshold sensitivity due to back bias for effective doping $\gamma_A$ concentration along the channel Body factor corresponding to bulk doping respectively $\gamma_B$ Built-in potential at the source or drain to channel junction $\varphi_{bi}$ Fermi potential due to pocket implantation $\varphi_F$ Work Function between Metal and Semiconductor $\varphi_{MS}$ **Ballistic Mobility** $\mu_{bal}$ Coulomb Scattering Mobility $\mu_{cb}$ **Effective Mobility** $\mu_{eff}$ **Phonon Scattering Mobility** $\mu_{ph}$ Surface Roughness Scattering Mobility $\mu_{sr}$ Subthreshold Ideality Factor $\theta$ Surface Potential $\psi_s$

Surface Potential at the onset of Strong Inversion

$\psi_{s,inv}$

## Acknowledgements

In the name of the Allah, the most Beneficent, the most Merciful, the most Compassionate. It is by the grace of the Almighty Allah that I was able to complete this thesis successfully. This thesis would not have been possible without the support of many people.

The author expresses his profound gratitude and a deep sense of respect to his supervisor Dr. Quazi Deen Mohd Khosru, Professor of the Department of Electrical and Electronic Engineering (EEE), Bangladesh University of Engineering and Technology (BUET), for his erudite suggestions, helpful discussions, invaluable assistance and great encouragement in the process of completing this work. His attention to detail, quest for excellence and love for perfection has inspired me to give my best efforts in this stupendous task. He has always been keen to cross his roles as a supervisor and played the role of a very helpful mentor. I am deeply indebted to him for making this research experience a memorable and successful one. Without his wholehearted supervision, it would have been impossible to finish the work in time. Not only that he always did all the official procedures and formalities very quickly.

Then the author would like to be grateful to all the examiners of the doctoral committee of EEE Department, BUET and to the external examiner Dr. Syed Kamrul Islam, Professor of the Department of Electrical Engineering and Computer Science, The University of Tennessee, Knoxville, TN, USA for their invaluable suggestions and corrections made to improve this thesis.

After that the author would like to pay his thanks and humble respects to all the Heads of various tenures during the progress of his thesis works, such as, Dr. M. M. Shahidul Hassan, Dr. Mohammad Ali Choudhury, Dr. S. Shahnawaz Ahmed, Dr. Satya Prasad Majumder, Dr. Aminul Hoque and Dr. Md. Saifur Rahman, Professors of the Department of Electrical and Electronic Engineering (EEE), Bangladesh University of Engineering and Technology (BUET) for their help, support and co-operation.

The author would like to convey his thanks and gratefulness to the Committee of Advanced Studies and Research (CASR) of BUET for the financial support in this research work.

The author would also like to express his thanks and respects to all the members of the Board of Post Graduate Studies (BPGS) for their unanimous decisions for which this research has come into reality.

The author then extends his thanks to the Departmental and Central Library staffs who helped to collect various journal and conference papers as well as various undergraduate and postgraduate thesis from the Library.

Sincerest thanks are also due to my friend Dr. Mohammed Imamul Hassan Bhuiyan, Associate Professor and my M.Sc. Engg. supervisor Dr. Kazi Mujibur Rahman, Professor, Department of EEE, BUET for their encouragement, suggestions and co-operation, and also for helping me to work with LaTeX during this thesis work. Dr. Bhuiyan also supplied me numerous research articles while he was doing his PhD in Canada. My special thanks go to Dr. Md. Ziaur Rahman Khan, Associate Professor, Department of EEE, BUET for giving me his PhD thesis (degree obtained from Cambridge University, UK) to get few important articles and references. I would also like to thank Dr. Mohammad Arfiul Haque, Assistant Professor, Department of EEE, BUET (who did his PhD from Department of EEE, BUET) for supplying me the LaTeX templates and few official documents regarding PhD degree. It gives me much pleasure to express my deep feeling of gratitude to all my respected teachers who always encouraged me to complete this task. I would also like to thank all the staffs in EEE Department and other departments/sections of BUET for extending their helping hands and co-operation.

I would also like to pay attention to numerous BUETians in the e-mail group to express my gratefulness and respect for their contribution towards my research works by supplying promptly a large number of research articles of various journals and conferences upon my e-mail request and also helping me by providing the LaTeX manuals and documents.

Finally, the author expresses his heartfelt appreciation and cordial thanks to his parents, wife, daughter and other family members, friends as well as well-wishers for their inspiration, sacrifice and extension of their co-operative hands during the progress of this work.

### **ABSTRACT**

As MOSFET device dimensions are shrinking to get optimum device performance, device structure is being modified. Additional atoms have been doped laterally by ion implantation at the source and drain sides. These additional doping atoms are known as pocket atoms that cause threshold voltage to rise when the gate length is reduced. This effect is known as reverse short channel effect or RSCE. This thesis presents the analytical models of the pocket implanted n-MOSFET. Two linear equations are used to simulate the pocket profiles along the channel at the surface from the source and drain edges towards the center of the n-MOSFET. Then the effective doping concentration is derived by integrating the pocket profiles from source to drain side and is used in the Poisson's equation in the depletion region at the surface. From this Poisson's equation, an analytical surface potential model of the pocket implanted n-MOSFET is derived using the appropriate boundary conditions. This model is used to find the threshold voltage model incorporating the bias and temperature effects. Then the inversion layer effective mobility model is also derived based on linear pocket profiles. These models are used to derive the subthreshold drain current model of the same device. Finally, low frequency drain current flicker noise model for the pocket implanted nano scale n-MOSFET has been derived using the proposed threshold voltage model.

After the model development, surface potential, threshold voltage, inversion layer effective mobility, subthreshold drain current and low frequency drain current flicker noise models are simulated by developing various MATLAB programs for different device and pocket profile parameters as well as various bias conditions. The simulated results of the proposed models are compared with the two other pocket profile models found in the literatures. The comparison shows that the models obtained using the linear pocket doping profile also produce similar results without hampering the accuracy level. Besides, the threshold voltages for various gate lengths fit well with the experimental data already published in the literatures. Not only that subthreshold drain current as well as low frequency drain current flicker noise models also fit well with the experimental data published in the literatures for the similar device and pocket profile parameters as well as bias conditions. In fact, these models possess a simple compact form that can be utilized to study and characterize the pocket implanted n-MOSFET in the nano scale regime.

# Chapter 1

### Introduction

#### 1.1 Introduction

The MOS transistor, also known as the Metal Oxide Semiconductor Field Effect Transistor (MOSFET) or Insulated-Gate Field Effect Transistor (IGFET) is by far the most common field-effect transistor in both digital and analog circuits' applications [1]. The MOSFET is the basic building block of the computer industry, digital telecommunication systems, pocket calculators and digital wristwatches [2]. The MOSFET is also used in applications like switched capacitor circuits, analog-to digital converters and filters.

This thesis is focused on investigating a pocket implanted n-MOSFET structure and developing different types of analytical models by proposing a pocket profile model. Method of pocket profile characterization is also presented. MATLAB programs and function files are developed for simulations of the models.

In this chapter, historical perspective of Complimentary Metal Oxide Semiconductor Field Effect Transistor (CMOS) technology evolution will be described. Then extensive literatures will be reviewed for these parameters. Objectives and methodology of this work will also be discussed. Finally, this chapter ends with summarizing the organization of this thesis.

#### 1.2 Moore's Law

In 1965, Gordon Moore, co-founder of Intel Corporation, predicted that the computer industry would double the density of components every year [3]. He speculated that this trend would continue and the chip density of 50 components per circuit in 1965

might reach 65,000 components per circuit by 1975. This speculation became known as Moore's Law and has served as the operational standard for the semiconductor industry. Other attributes of digital electronic devices like processing speed, memory capacity, even the number and size of pixels in digital cameras are linked to Moore's law as they are also improving at (roughly) exponential rates. Although originally calculated as doubling every year, Moore later refined the period to two years [4], [5]. Fig. 1.1 illustrates Moore's Law and current trends [5]. The semiconductor industry follows Moore's law by shrinking transistor dimensions. CMOS technology has been proven as one of the most important achievements in modern engineering history and has become the primary engine driving the world economy. The secret to the success is simply to keep delivering more functionality with fewer resources and device scaling, and thus to follow the Moore's Law. But transistors cannot be scaled-down infinitely. There is couple of issues that needs to be addressed when the transistor size is reduced.

Figure 1.1: Moore's Law [5]

For digital applications, a transistor is operated as a switch. For high speed operation, it must deliver a large on-current that rapidly charges and discharges the stray capacitance of the wires connecting it to the other transistors in the circuit. In the circuit, the switching power is directly proportional to the operating frequency and to the square of the supply voltage. However, device scaling increases the number of gates on a chip and their operating frequency. Thus, in order to limit power dissipation and prevent the chip from overheating, the power supply voltage must therefore decrease when scaling the device down while maintaining the on-current. A transistor should have a very little off-current to reduce the static power loss. Because of scaling the device size, the distance between the source and drain shrinks, and it becomes increasingly difficult to turn a MOSFET off. Consequently, off-current increases exponentially with device scaling such that the off state power consumption become substantial [6].

In an interview with Techworld, Gordon Moore told that that the law cannot be sustained indefinitely. According to him "It can't continue forever. The nature of exponentials is that you push them out and eventually disaster happens" [7]

One of the limits to Moore's law is often believed to be in lithography and in the availability to pattern the minimum feature size. But materials are now also an important constraint. Cu has replaced Al as the interconnect material between the transistors because of current densities. In order to reduce the RC time delays of the ICs, lower dielectric constant materials, such as, SiO<sub>2</sub>F<sub>x</sub> or SiOCH alloys are used instead of the SiO<sub>2</sub> as the inter layer dielectric [8]. The excellent material and electrical properties of SiO<sub>2</sub> used as the gate dielectric is one of the key elements that allowed the successful scaling of silicon based MOSFETs. Amorphous SiO<sub>2</sub> can be thermally grown on silicon with excellent control in thickness and uniformity. It naturally forms a very stable interface with the silicon substrate with a low density of intrinsic interface defects. SiO<sub>2</sub> has an excellent thermal and chemical stability, which is required for the fabrication of transistors that includes annealing steps at high temperatures (up to  $1000^{0}$  C). Furthermore, the band gap of  $SiO_{2}$  (9 eV) is large enough for excellent electrical isolation. It has large energy band offsets with the conduction and valence bands of Si and high breakdown fields, of the order of 13 MV/cm [9].

| Year          | 1999 | 2001 | 2002 | 2004 | 2006                   | 2009 | 2010 | 2011 | 2014 |

|---------------|------|------|------|------|------------------------|------|------|------|------|

| L (nm)        | 180  | 130  | 90   | 65   | 45                     | 38   | 32   | 22   | 20   |

| $t_{ox}$ (nm) | ~4   | ~3   | ~2   | ~1.5 | ~1.5                   | ~1.5 | ~1.1 | ~1.0 | -    |

|               |      |      |      |      | with High-k/Metal gate |      |      |      |      |

|               |      |      |      |      |                        |      |      |      |      |

Table 1.1 Road map of MOSFET minimum feature size 2010 update [5]

All these superior properties allowed the fabrication of commercial devices with SiO<sub>2</sub> gate layers as thin as 2 nm [10]. Studies indicated that bulk SiO<sub>2</sub> electronic structure is not achieved in a thermal oxide until the thickness reaches ~0.7 nm [11]. According to the International Technology Roadmap for Semiconductors (ITRS), the next generations of Si-based MOSFETs will require oxide thicknesses below 1 nm, both for high performance logic applications (e.g. microprocessors for personal computers and workstations) and low operating power logic applications (like wireless applications) [5]. The minimum dimension size of a single device for present day technology is in the nano scale regime. Continued success in device scaling is necessary for further development of the semiconductor industry in the years to come. A group of leading companies publishes their projections for the next decade in the most recent International Technology Roadmap for Semiconductors (ITRS 2010) [5]. The roadmap projects a device gate-length down to ~20 nm around 2014 [5] as shown in Table 1.1. This forecast promises another few years of brightness. Scaling beyond 20 nm, however, can be much more difficult and different. We are quite close to the fundamental limits of semiconductor physics. How much further down can we go? It is hard to answer. Nevertheless, without doubt, we are facing numerous challenges, both practically and theoretically. Device simulation requires new theory and approaches to understand device physics and to design devices in the nano scale regime. Efforts have been put forth in recent years [12]-[16], but much more is needed. For these purposes, different types of MOSFET models are found in the literatures [17].

#### 1.3 Device Scaling

There are two primary device structures that have being widely studied and used in CMOS technology. One is the bulk structure, where a transistor is directly fabricated on the semiconductor substrate. The other is called SOI (silicon-on-insulator), where a

transistor is built on a thin silicon layer, which is separated from the substrate by an insulator layer. The bulk structure is relatively simple from a device process point of view and still the standard structure in almost all CMOS based products until today.

For device scaling, basically it is tried to balance two things: device functionality and device reliability. Both of them have to be maintained at a smaller dimensional size. As the channel length of MOSFETs is scaled down to deep-submicrometer or nano scale regime, it is observed the reduction of threshold voltage with the reduction of channel length due to the charge sharing between the drain/source region and the channel and also due to high electric fields in the channel [1]. This effect is known as short channel effect (SCE). This effect is usually accompanied by degraded subthreshold swing (S), which causes difficulty in turning off a device. Primarily, there are two kinds of leakages, gate tunneling current and junction tunneling current. Both of them result from extremely scaled dimensions and high electric fields. Unwanted leakage currents can make the device fail to function properly. SCEs also include the drain induced barrier lowering (DIBL) effect. DIBL results in a drain voltage dependent on  $V_{th}$ , which complicates CMOS design at a circuit level. This effect arises as a result of two dimensional potential distribution and high electric fields in the channel region [18]. Therefore, to accomplish device scaling, it is needed to suppress any dimension related effects as much as possible. As a transistor scales, reliability concerns become more pronounced.

According to device scaling physics, increasing channel doping concentration can effectively suppress SCEs. Frank et al. recently published their work quantifying the dependence of the scale length on channel doping concentration [19].

Device scaling has come a long way. In the early days, gate length (L) is relatively long; a low uniform substrate concentration can be used providing satisfactory immunity of SCEs. A low substrate concentration gives a small body effect coefficient, which improves the subthreshold swing [20].

The emergence of MOS device in the sub-100 nm regime has led to the development of source/drain engineering procedures. Such procedures used to form pocket or halo regions. As the channel length decreases, a retrograde or ground plane doping profile can be introduced [21]-[22]. This doping profile has a low doping region near the Si/Oxide interface, but a high doping region underneath. The top region provides better body effect, while the bottom region suppresses SCEs. To achieve even shorter channel lengths, a ground plane profile is not enough, a more complicated doping

profile has to be added, namely the super halo [23]. In this case, high gradient halo dopings are formed next to the source/drain junction region. These heavily doped regions can effectively protect the source end of the channel region from the influence due to the electric fields from the drain diffusion region. As the channel length varies around the nominal gate length, a shorter length causes the halo regions to merge, ending up with higher substrate doping concentration, which resists  $V_{th}$  roll off. By using the ground plane and halo doping profiles, simulations show that the bulk structure can be scaled down to ~25 nm regime [23]. Also, due to the pocket implantation,  $V_{th}$  roll off is reversed with the reduction of gate length. This effect is known as Reverse Short Channel Effect (RSCE). There are many causes to originate the RSCE. Different sensitivities of pocket implant and SCE onto the channel length may constitute one of the main reasons for the threshold voltage roll-up shortly after an L longer than the shortest length of that technology. Another source of RSCE, originally in MOSFETs, is the channel concentration build-up resulting from the oxidation-enhanced-diffusion [24] or implant-damage-enhanced diffusion [25], which are very difficult to control, the electrical deactivation of arsenic [26] or boron penetration from poly-gate and oxide [27]. There are still other factors, such as, annealing [28] and salicide [29] within front end processes affecting the RSCE. By raising the doping concentration locally in the channel has been implemented via lateral channel engineering utilizing halo [30] or pocket implant [31], [32]-[36] surrounding drain/source regions is effective in suppressing SCE. The two terms are used interchangeably here although a halo may connote a pocket that is deeper than the drain. The halo or pocket implant can be either symmetrical [37] or asymmetrical [38] with respect to source or drain. Reported circuit applications include a 256 M-bit DRAM [39] and mixed-signal processor [40].

Recently, very excellent short-channel performance was demonstrated in 0.1 µm n-channel and buried p-channel MOSFET's using Large-Angle-Tilt-Implanted (LATI) pocket [37]. In fact, this pocket implant technology is found to be very promising in the effort to tailor the short-channel performances of deep-submicron as well as nano scale MOSFETs although careful tradeoffs need to be made between minimum channel length and other device electrical parameters [33]. It could be shown that with an optimized pocket implant process the saturation current is up to 10% higher

compared to a conventional optimized junction technology without increasing the leakage current of the devices minimum channel length.

#### 1.4 Literature Review

In pocket or halo doped regions, the doping concentration is higher and gradually it decrease down to substrate region concentration in the lateral direction. Therefore, an understanding of the effects of a lateral doping profile in the channel is necessary. This thesis explores the effects of a laterally non-uniform doping distribution on the threshold voltage of a device by focusing on the Reverse Short Channel Effect (RSCE). This effect causes the threshold voltage ( $V_{th}$ ) to rise as the gate length (L) shrinks because of the presence of laterally non-uniform channel doping. This thesis explores the analytical modeling areas of pocket implanted n-channel MOSFETs, such as, surface potential, threshold voltage incorporating bias and temperature effects, mobility modeling, subthreshold drain current modeling and low frequency drain current flicker noise modeling. But before start of the modeling, literatures have been reviewed extensively on different operational parameters of the pocket implanted n-MOSFET. These are provided in the next sub-sections.

#### 1.4.1 Present RSCE Models

Various analytic models currently exist in the literature specifically for calculating the threshold voltage of devices exhibiting RSCE. Of these, two are aimed at providing models that allow a length-independent description of such devices for compact modeling. Another paper examines the effects of RSCE on the drain current and output conductance, modeling it as a potential barrier at the source and drain.

Brut et al. picture the RSCE as caused by extra doping of a Gaussian-like shape at the edge of the channel [41]. They then find an average doping of the channel ( $N_{b,eff}$ ), integrating its doping from source to drain and dividing by the channel length. This gives an effective channel doping dependent upon the channel length. Using the definition of threshold voltage in [1], they replace the  $N_b$  with this  $N_{b,eff}$  and add short channel effects (SCE) via a charge sharing description, which reduces  $Q_B$  by a multiplicative factor. Their model tracks actual  $V_{th}$  data closely for both channel length and back bias. They used five fitting parameters in the model of which three

are physically based and the other two are purely experimental parameters that allow them to fit the roll-off of the threshold voltage due to short channel effects.

Arora et al. take a similar approach but use negative fixed oxide charge as the cause of the RSCE [42], [43]. Assuming an exponentially decreasing distribution of fixed oxide charge near the source and drain, they also take an average by integrating the oxide charge from source to drain and then dividing by L. They then use this effective  $Q_{ox}$  to adjust the flat band voltage implementing the SCE differently. The final model has four fitting parameters. Similarly to Brut, the two parameters that are physically based are the magnitude  $(Q_{ox})$  and characteristic decay length  $(x_o)$  of the extra  $Q_{ox}$ . The other two parameters allow them to fit the roll-off of the threshold voltage due to short channel effects.

Looking in general at the effect of a potential barrier at the source or drain, Hsu et al. use RSCE as an example to create their model [44]. Taking the standard equation for current over a barrier, they linearize its dependence on the voltage applied across it, giving an effective conductance modulated by the gate voltage. His equation shows that the output current is reduced by the source/drain resistance and a resistance due to the barrier. Interestingly, the feature that differentiates the barrier resistance from the source/drain resistance is that it depends upon gate voltage. Empirically coming up with an equation for the relationship between the gate voltage and barrier height, Hsu shows a nice fit to an experimental current-voltage curve with the model. They conclude that a potential barrier at the source and drain can severely degrade a MOSFET's performance. Each of these models accurately describes the Reverse Short Channel Effects in terms of threshold voltage vs. channel length characteristics.

#### 1.4.2 Surface Potential

Solution of the Poisson's equation in the depletion region of the MOSFETs is an important step in order to determine the surface potential. Numerical device simulators like MEDICI [45] can produce most accurate solutions of the Poisson's equation. But analytical models that have been used for MOSFET device design, take less time for device simulation. It also provides device physics insight [46]. Analytical model shown in [33] does not satisfy the boundary conditions and device simulation results of MEDICI. Analytical model in [46] assume a step profile of pocket doping. Besides, Gaussian profile [47] and hyperbolic cosine function [48] were assumed for

the pocket profile to derive the threshold voltage equations. But it has been observed that linear profile of pocket doping produce better results for threshold voltage [49]. The previous works [46]-[49] are on the threshold voltage and surface potential modeling of pocket implanted MOS devices.

#### 1.4.3 Threshold Voltage

The conventional threshold voltage model is derived for the homogeneous doping concentration [1]. An extension of the homogeneous model to the non-homogeneous impurity pileup in the vertical direction has been reported previously [18], [32], [50]. However, the reported model cannot be extended further to the pocket implantation, where inhomogeneity along the channel is the main cause for the Reverse Short Channel Effect (RSCE) [51]. Previous attempts for including the strong RSCE due to the pocket implantation in to a circuit simulation model were done by introducing model parameters without connection to the pocket profile [35]. A strong reverse short channel effect suppresses the short channel effect on threshold voltage of the MOSFET [52]. Threshold voltage model for pocket implanted MOSFETs for circuit simulation does not describe the sub-100 nm case [52].

#### 1.4.4 Temperature Effects

It is well known that a change in the operating temperature of a device affects its characteristics and hence the circuit performance [1]. Accurate description of the temperature effects in devices is necessary to predict circuit behavior over a range of temperatures. A number of important model parameters such as mobility, threshold voltage, saturation velocity, parasitic series resistance, and source/drain junctions characteristics are temperature dependent. All of these temperature dependencies need to be modeled correctly. Since the threshold voltage of MOSFET is an important parameter its effect on temperature should be studied, especially in lower temperature operation. There are many benefits for MOSFET operating in lower temperatures, such as, improvement of subthreshold swing, increase of carrier mobility, higher saturation velocity and operation speed, lower voltage swing and reduced leakage current, improved latch up immunity, reduction of short channel effects and improved electro-migration and device power dissipation etc. Temperature dependent conventional and SOI MOS device physics and characteristics have already been

discussed in the literatures [1], [53]-[59]. Comprehensive analysis of pocket implanted MOSFETs from low-temperature operation has been described in [60]. But here model is developed using an exponential profile of pocket doping.

#### 1.4.5 Inversion Layer Effective Mobility

The inversion layer mobility in Si MOSFET's has been a very important physical quantity as a parameter to describe the drain current and a probe to study the electric properties of a two-dimensional carrier system. Therefore, much study [61] since the 1960's has revealed dominant scattering mechanisms determining the mobility.

On the other hand, it has already been reported that the electron and hole mobilities in the inversion layer on a (100) surface follow the universal curves at room temperature independent of the substrate impurity concentration or the substrate bias when plotted as a function of effective normal fields,  $E_{eff}$  [62]. Pocket implant causes a strong nonuniform lateral doping profile. With the reduction of the channel length or with the increase of the pocket profile parameters there is a pronounced increase of the effective the channel doping concentration, the effective mobility is supposed to be degraded further due to Coulomb scattering with the ionized dopants and charged interface traps at low vertical electric fields, i.e., at low gate bias. This is called "rolloff" region. As the effective vertical field increases, the mobility becomes independent of the channel doping and all the samples approach the so-called universal curve. In this region, the main scattering processes are phonon and surface roughness scattering that do not depend on channel doping. In most circuit models [63]-[65], simple mobility models [17], [66] are used to describe the effective surface mobility neither accounting for the degradation by Coulomb scattering in heavily doped MOSFET's (only the 'universal curve' [67] is modeled) nor accounting for the lateral non-uniform doping profile. This neglect can cause simulation errors in the transconductance of short n-MOS pocket implanted devices of up to 50% which can not be tolerated in today's circuit simulations [68].

#### 1.4.6 Subthreshold Drain Current

When the gate voltage is below the threshold voltage and the semiconductor surface is in weak inversion, the corresponding drain current is called the subthreshold current. The subthreshold region is particularly important for low-voltage, low-power applications, such as, when the MOSFET is used as a switch in digital logic and memory applications, because the subthreshold region describes how the switch turns on and off. Already few papers have been published focusing on the subthreshold behavior of pocket implanted n-MOSFET [69]-[72]. In [36], models for subthreshold and above subthreshold currents in 0.1 µm pocket n-MOSFETs for low-voltage applications have been derived based on the diffusion current transport equation. But this model characterizes the localized pile-up of channel dopants as step profile. The influences of halo implant dose and tilt angle on the off-state current have been investigated by technology computer aided design (TCAD) simulation in [69]. A channel length independent subthreshold characteristic in submicron MOSFETs has been reported by Shin et al in [70] due to the presence of localized pileup of channel dopants near the source and drain ends of the channel. An analytical subthreshold current model for pocket-implanted n-MOSFETs has been presented in [71]. But this model characterizes the localized channel dopants as step profile. In [72], the authors presented an analytical model for the subthreshold current applicable for any type of FET and showed that the subthreshold current of nMOSFETs, which is mainly due to diffusion, is determined by the internal two-dimensional hole distribution across the device.

#### 1.4.7 Low Frequency Drain Current Flicker Noise Model

In the low frequency region, flicker noise is dominant. Flicker noise affects the signal-to-noise ratio in operational amplifiers and in analog-to-digital-converters and digital-to-analog converters. Phase noise of voltage controlled oscillators originating from flicker noise is another concern for radio frequency applications. In order to reduce the low-frequency noise in MOS devices, the physical origin of flicker noise in the MOS devices should be studied and modeled properly. Already few papers have been published focusing on the degradation of drain current flicker noise due to pocket implantation in MOSFETs [73]-[79]. New pocket structures, such as, single pocket, asymmetric channel structure, [73], [75] and epitaxial channel MOSFETs [76], [77], were proposed to reduce the drain current flicker noise by elimination of pocket implantation. The low frequency noise in pocket implanted MOSFETs may result from additional oxide trap creation due to pocket implantation [77], but this was also not supported by the experiment [78]. In [78], it was shown that the non-uniform

distribution of threshold voltage along the channel resulting from the pocket implantation is responsible for the low frequency drain current flicker noise degradation, but there step doping profiles are used in the pocket implanted region to model the drain current flicker noise.

#### 1.5 Objectives

The objectives of the thesis are to develop various analytical models of the pocket implanted nano scale n-MOSFET based on linear pocket profiles.

The specific aims of this thesis are:

- 1. To study the characterization of the lateral doping profiles at the source and drain edges of the pocket implanted n-MOSFET and hence to develop the doping profile models of the pocket implanted nano scale n-MOSFET.

- 2. To develop the surface potential model of the pocket implanted nano scale n-MOSFET assuming linear pocket doping profiles.

- 3. To incorporate the effective doping profiles in the threshold voltage model of the same device including substrate and drain bias effects.

- 4. To incorporate the temperature effects in the threshold voltage model.

- 5. To develop an inversion layer effective mobility model for the same device.

- 6. To develop a subthreshold drain current model of the pocket implanted nano scale n-MOSFET using the developed pocket doping profiles and incorporating the inversion layer effective mobility model.

- 7. To develop low frequency drain current flicker noise model.

The outcome of the thesis will be several models of the pocket implanted n-MOSFET, such as, doping profile, surface potential, threshold voltage incorporating bias and temperature effects, inversion layer effective mobility, subthreshold drain current and low frequency drain current flicker noise models. Fabrication and doping profile characterization technique of the pocket implanted n-MOSFET will also be discussed. Experimental verifications will also be made.

#### 1.6 Methodology

The model derived in this work aims to be more exact in modeling the effects of a non-uniform lateral channel doping profile by taking an effective channel doping concentration. At first, pocket implantation technology, pocket profile characterization and various types of pocket doping profiles in the literature will be studied. Then a linear pocket doping profile at the source and drain edges at the surface of the pocket implanted n-MOSFET will be established for this work. After that various operational parameters will be studied and then suitable models for these parameters of the pocket implanted n-MOSFET will be developed. One developed model will be used to develop the other models. Effects of various parameters will be incorporated in the model.

After that an analytical model that can predict the surface potential of the nano scale pocket implanted n-MOSFET will be derived incorporating the linear pocket doping profile. Here the 1-D pocket doping profile across the channel will be transformed to an effective doping concentration expression ( $N_{eff}$ ), which is used in the Gauss's law to derive the model applying the appropriate boundary conditions.

Then a model capable of describing the threshold voltage of the pocket implanted nano scale n-MOSFET incorporating  $N_{eff}$  and threshold voltage shift,  $\Delta V_{th}$ incorporating drain and substrate bias effects. Here a short channel threshold voltage equation is used for the case of pocket implanted n-MOSFET where exponential dependence on channel length and a linear dependence on drain and substrate biases have been observed [80]. Effects of temperature variation will be studied using threshold voltage model by incorporating various temperature dependent parameters. Besides, an analytical inversion layer effective mobility model will be developed taking into account the pocket doping as well as temperature effects for the nano scale pocket implanted n-MOSFET. The total number of inversion layer charges will be calculated numerically using the threshold voltage and the surface potential models obtained. The pocket profile and device parameters as well as bias voltages will be varied to investigate the pocket implantation effect on effective mobility. Then a subthreshold drain current model will be developed incorporating this effective mobility model and using the conventional drift-diffusion equation. The surface potential model derived earlier will also be used. Finally, an analytical drain current flicker noise model will be developed taking into account the pocket doping effect and using the developed threshold voltage model.

After the model development, simulation results will be obtained by developing the several MATLAB programs and all the necessary function files. The simulated results

will be analyzed to evaluate the device performance and characterize the pocket implanted nao scale n-MOSFET. The simulated results will also be compared with the results obtained using the other pocket doping profiles found in the literature. Besides, experimental data already published in the different literatures will be fitted with the simulated data of the proposed analytical models.

#### 1.7 Organization of the Thesis

This Thesis is organized as follows:

Chapter 2 reviews the threshold voltage control and the Short Channel Effects (SCE) in conventional bulk n-MOSFET. Then it describes the how the structure of the pocket implanted n-MOSFET is formed. After that, it elucidates how Reverse Short Channel Effect (RSCE) arises due to pocket implantation and the other causes of RSCE. Then it explains the lateral doping profile characterization techniques followed by the review of the existing models for the doping profiles that cause RSCE and finally, proposes the modeling of the lateral doping profile of the pocket implanted n-MOSFET.

Chapter 3 describes model derivation techniques and then presents various models of the pocket implanted nano scale n-MOSFET using the lateral doping profile model proposed in chapter 2.

Chapter 4 provides MATLAB simulation results of the developed models and explores the effects of the variation of the different device and pocket profile parameters of the pocket implanted n-MOSFET as well as of the various bias conditions. It also explains the simulated results and shows the comparisons of the proposed model with the other pocket doping profiles found in the literatures. Experimental verifications are also made for few models.

Finally, Chapter 5 concludes the thesis with a summary, limitations of the proposed models and few suggestions for the future scopes of this work.

# Chapter 2

# **Pocket Implanted n-MOSFET**

#### 2.1 Introduction

The Metal Oxide Semiconductor Field Effect Transistor (MOSFET) is a very important device for very large scale and ultra large scale integrated circuits, such as, microprocessors and semiconductor memories. It is also used in power electric circuits. CMOS device dimensions are continuously being shrinking to enhance the circuit speed and density and this has become possible due to the nonstop progress of the semiconductor device process technology. But this reduction of device dimensions reduces the threshold voltage ( $V_{th}$ ). This adverse  $V_{th}$  roll-off effect is perhaps the most daunting road block in future MOSFET design and modeling [33]. The minimum acceptable channel length,  $L_{min}$ , is primarily determined by the threshold voltage roll-off, which is known as Short Channel Effect (SCE). So,  $V_{th}$  is an important parameter in MOS device design and fabrication.

The pocket implant technology has been developed to combat SCE and enables gate length reduction in to the nano scale regime [23]. Using this technology  $V_{th}$  roll off can be reduced, i.e., SCE can be improved without increasing substrate concentration and/or oxide thickness [33]. This can be achieved by locally raising the channel doping next to the drain or drain/source junctions. This improvement can be observed as a delayed onset of  $V_{th}$  roll-off or an increased  $V_{th}$ , which consequently reduces the subthreshold leakage current. Furthermore, the driving capability of pocket-implanted device is enhanced due to the minimum channel length deviation. The phenomenon in which the threshold voltage of a device increases as the channel length decreases is known as the Reverse Short Channel Effect (RSCE). This behavior is the opposite of what is expected from SCE.

In the first part of this chapter, threshold voltage control and combating the SCE will be discussed. Then in the second part of this chapter, the structure and formation processes of the pocket implanted n-MOSFET will be discussed. Then the characterization and modeling of the pocket doping profile will be discussed.

#### 2.2 Threshold Voltage Control

The threshold voltage is one of the most important parameters of the MOSFET and it is given by (2.1). Flat band voltage incorporates the effects of the fixed-oxide charge and the difference in work function. Substrate bias effect on the threshold voltage is also incorporated in to this model. Because, a reverse bias between the substrate and the source widens the depletion region and results an increase in the threshold voltage to accommodate larger inversion charge.

$$V_T = V_{FB} + 2\psi_B + \frac{\sqrt{2q\varepsilon_s N_{sub} (2\psi_B + V_{BS})}}{C_{ox}}$$

(2.1)

,where  $V_{FB}$  is the flat band voltage,  $\psi_B$  is the electrostatic potential in the bulk of the semiconductor, q is the electronic charge,  $\varepsilon_{Si}$  is the dielectric permittivity of Si,  $N_{sub}$  is the substrate doping concentration,  $V_{BS}$  is the reverse substrate to source bias and  $C_{ox}$  is the oxide capacitance per unit area.

Precise control of threshold voltage of a MOSFET is essential for a reliable circuit operation when the device is used in an integrated circuit. It is generally adjusted vertically through ion implantation into the channel region. The threshold voltage of an n-channel MOSFET is adjusted by boron implantation through surface oxide. V<sub>BS</sub> is the reverse substrate to source bias. Precise control of threshold voltage of a MOSFET is essential for a reliable circuit operation when the device is used in an integrated circuit. It is generally adjusted through ion implantation into the channel region. The threshold voltage of an n-channel MOSFET is adjusted by a boron implantation through a surface oxide.

#### 2.2.1 Non-uniform doping