#### Modeling of direct tunneling gate current and gate capacitance in deep submicron MOSFETs with high-K dielectric.

#### A thesis submitted to the department of Electrical and Electronic Engineering of Bangladesh University of Engineering and Technology in partial fulfillment of the requirement for the degree of MASTER OF SCIENCE IN ELECTRICAL AND ELECTRONIC ENGINEERING

by Mohammad Mojammel Al Hakim

#### DEPARTMENT OF ELECTRICAL AND ELECTRONIC ENGINEERING BANGLADESH UNIVERSITY OF ENGINEERING AND TECHNOLOGY 2002

i

The thesis titled "Modeling of direct tunneling gate current and gate capacitance in deep submicron MOSFETs with high-K dielectric" submitted by Mohammad Mojammel Al Hakim, Roll No.: 040006216P, Session: April 2000 has been accepted as satisfactory in partial fulfillment of the requirement for the degree of MASTER OF SCIENCE IN ELECTRICAL AND ELECTRONIC ENGINEERING on March 03, 2002.

#### **BOARD OF EXAMINERS**

- Abril 13,2002

**Dr. Anisul Haque** Associate Professor Department of Electrical and Electronic Engineering BUET, Dhaka-1000, Bangladesh.

(Supervisor)

Member

Chairman

2.

1.

**Dr. M. Rezwan Khan** Professor Department of Electrical and Electronic Engineering BUET, Dhaka-1000, Bangladesh.

3.

12000

**Dr. M. Jahangir Alam** Assistant Professor Department of Electrical and Electronic Engineering BUET, Dhaka-1000, Bangladesh.

**Dr. M. M. Shahidul Hassan** Professor and Head Department of Electrical and Electronic Engineering BUET, Dhaka-1000, Bangladesh.

A. Hanaci

5.

4.

**Dr. A. K. M. Akhter Hossain** Assistant Professor Department of Physics BUET, Dhaka-1000, Bangladesh. Member

**Member** (Ex-officio)

Member (External)

#### Declaration

I hereby declare that this thesis or any part of it has not been submitted elsewhere for the award of any degree or diploma.

Signature of the candidate

W Alkalin

(Mohammad Mojammel Al Hakim)

### Dedication

To My Parents

# Contents

| D  | eclaration                                                                                                                                          | iii                       |

|----|-----------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------|

| Ð  | edication                                                                                                                                           | iv                        |

| A  | cknowledgement                                                                                                                                      | ix                        |

| A  | bstract                                                                                                                                             | x                         |

| 1  | Introduction<br>1.1 Literature review<br>1.2 Objective of the work<br>1.3 Organization of the thesis                                                | 1<br>2<br>7<br>8          |

| 2  | Quantum Mechanical theory of MOS inversion layer<br>2.1 Self-consistent solution<br>2.2 Transmission line analogy<br>2.3 Green's function formalism | <b>9</b><br>9<br>11<br>14 |

| 3  | <b>Properties of high-K dielectrics</b><br>3.1 Properties of available dielectrics                                                                  | <b>17</b><br>17           |

| 4  | Modeling of direct tunneling gate current<br>4.1 Theory of gate current<br>4.2 Results and discussion                                               | <b>20</b><br>20<br>21     |

| 5  | Modeling of gate capacitance<br>5.1 Theory of gate capacitance<br>5.2 Results                                                                       | <b>32</b><br>32<br>33     |

| 6  | <b>Conclusion</b><br>6.1 Summary<br>6.2 Suggestion for further work                                                                                 | <b>49</b><br>49<br>49     |

| Re | eference                                                                                                                                            | ÷ 51                      |

# **List of Figures**

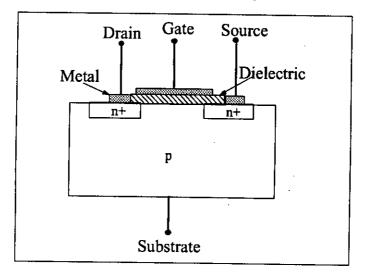

| 2.1 | A typical nMOS structure.                                                                                                                                                                                                                                                           | 9  |

|-----|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

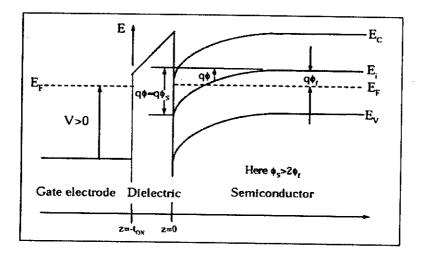

| 2.2 | A typical conduction band profile of an NMOS structure.                                                                                                                                                                                                                             | 10 |

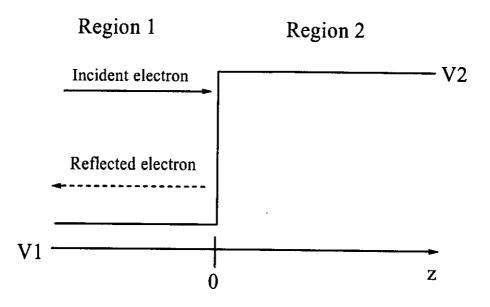

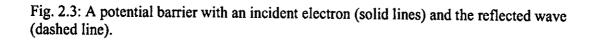

| 2.3 | A potential barrier with an incident electron (solid lines) and the reflected wave (dashed line).                                                                                                                                                                                   | 12 |

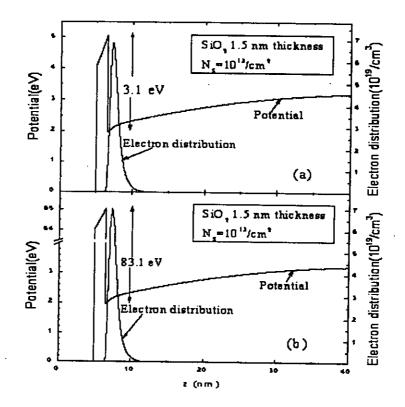

| 4.1 | Potential profile obtained self-consistently with SiO <sub>2</sub> gate dielectric of 1.5 nm thickness at inversion charge density of $N_S = 10^{13}/\text{cm}^2$ a) open boundary conditions b) closed boundary conditions.                                                        | 22 |

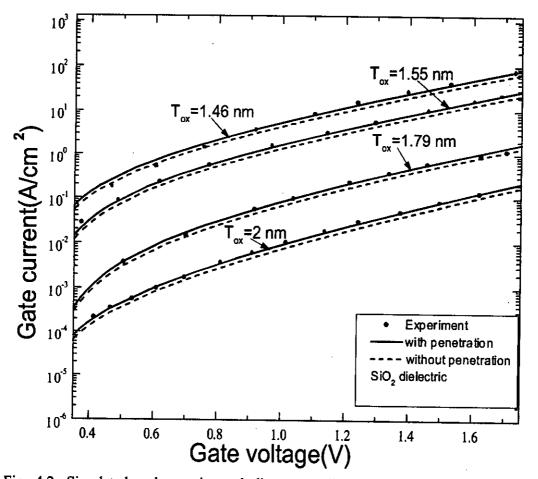

| 4.2 | Simulated and experimental direct tunneling currents in nMOSFET's both considering and without considering carrier tunneling effects within the self-consistent loop. Experimental data are taken from Ref. [17]. The poly-silicon doping level is $N_{poly}=10^{20}/\text{cm}^3$ . | 23 |

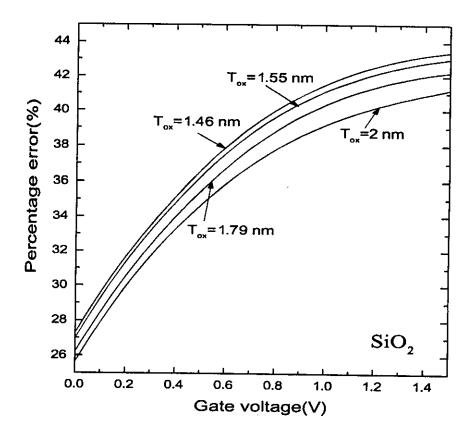

| 4.3 | Relative error in direct tunneling gate current shown in Fig. 4.2 due to neglect of tunneling effects within self-consistent loop.                                                                                                                                                  | 24 |

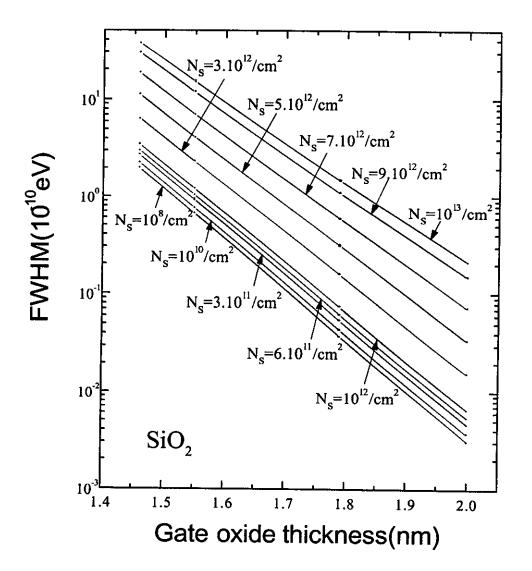

| 4.4 | FWHM variation with oxide thickness for different inversion condition for $SiO_2$ dielectric.                                                                                                                                                                                       | 26 |

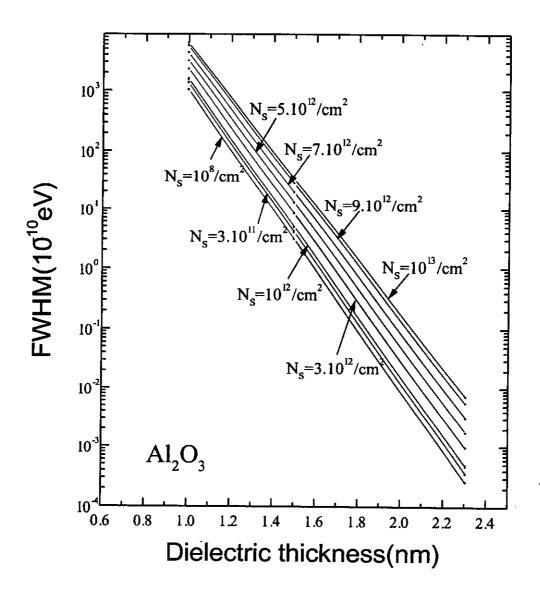

| 4.5 | FWHM variation with oxide thickness for different inversion condition for $Al_2O_3$ dielectric.                                                                                                                                                                                     | 27 |

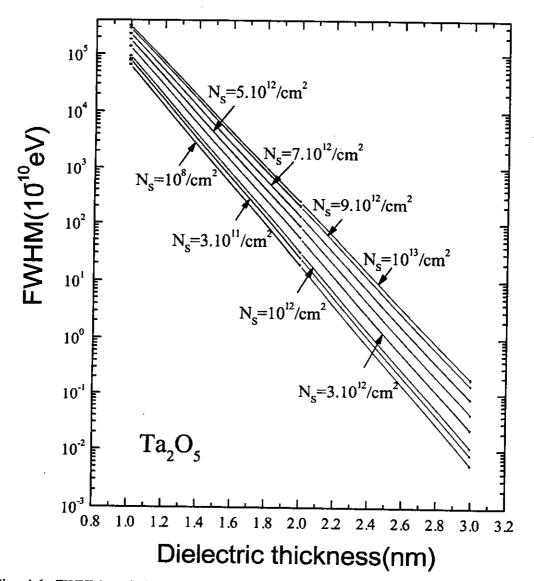

| 4.6 | FWHM variation with oxide thickness for different inversion condition for Ta <sub>2</sub> O <sub>5</sub> dielectric.                                                                                                                                                                | 28 |

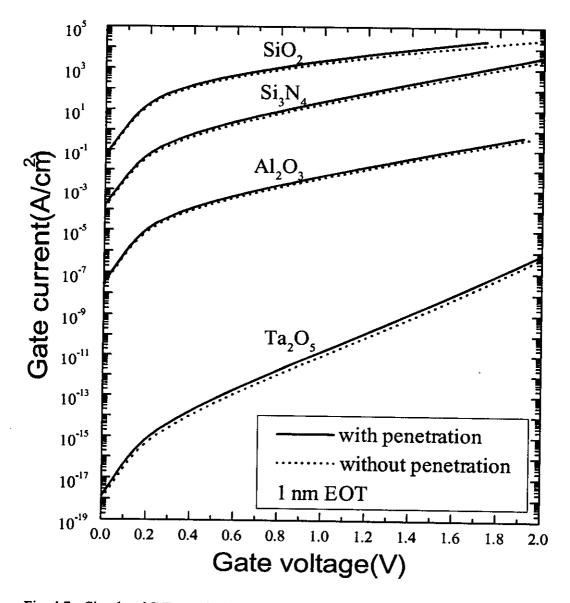

| 4.7 | Simulated DT gate leakage current vs gate voltage for different dielectrics for EOT of 1 nm.                                                                                                                                                                                        | 29 |

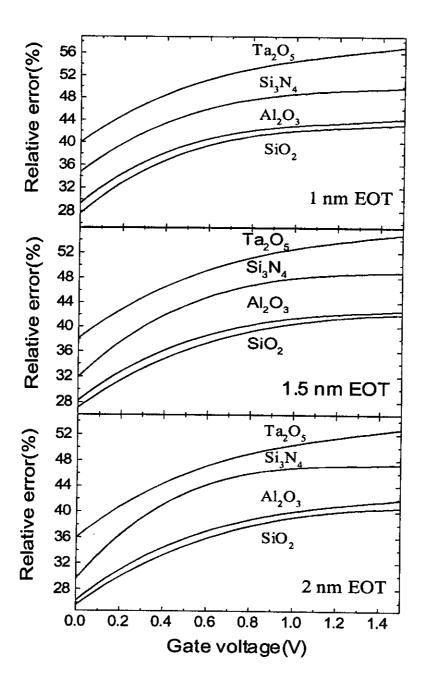

| 4.8 | Relative error in DT gate current due to neglect of tunneling effects within self-consistent loop for different dielectrics.                                                                                                                                                        | 31 |

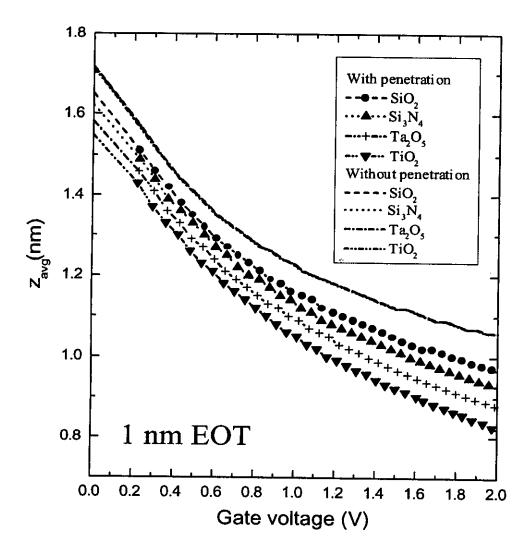

| 5.1 | $Z_{avg}$ variation with gate voltage for different dielectrics of 1 nm EOT both considering and without considering penetration.                                                                                                                                                   | 34 |

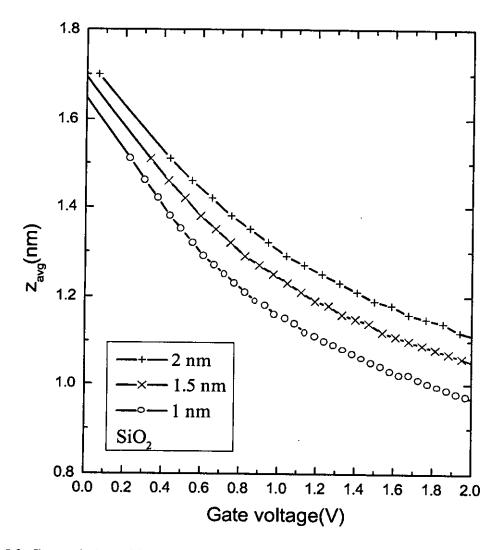

| 5.2 | $Z_{avg}$ variation with gate voltage for different dielectric thickness for SiO <sub>2</sub> when penetration is considered.                                                                                                                                                       | 36 |

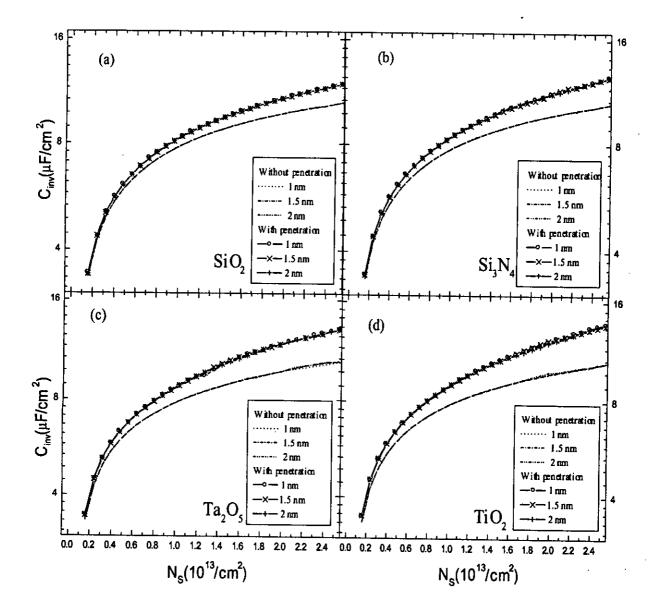

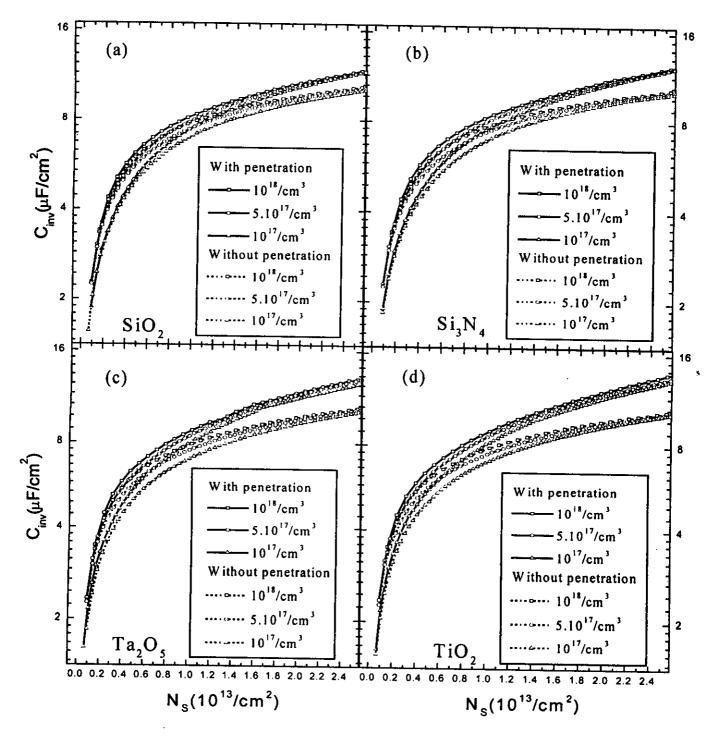

| 5.3 | $C_{inv}$ vs $N_S$ for different gate dielectrics of 1 nm EOT both considering and without considering penetration.                                                                                                                                                                 | 38 |

alan Salata Salata

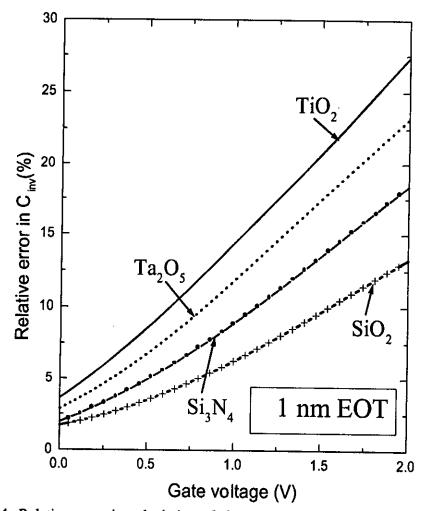

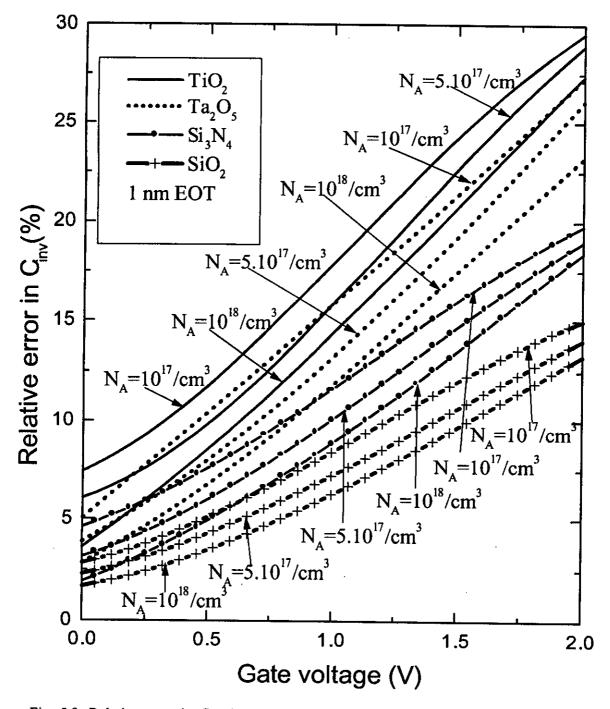

| 5.4  | Relative error in calculation of $C_{inv}$ due to neglect of penetration at various voltages for different dielectrics.                                           | 39 |

|------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

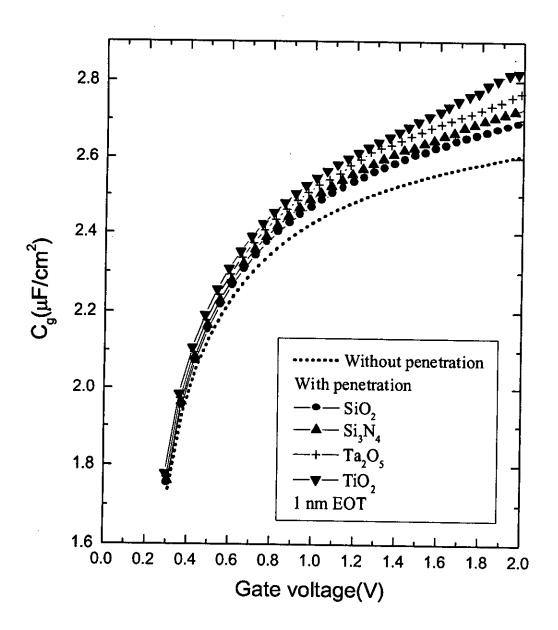

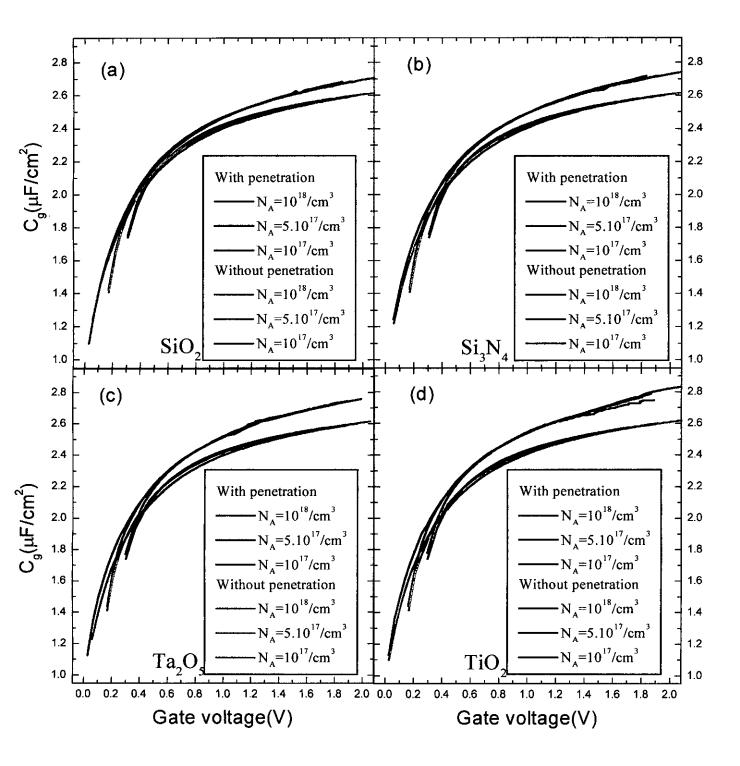

| 5.5  | $C_g$ as a function of gate voltage for different dielectrics at 1 nm EOT both considering and without considering penetration.                                   | 40 |

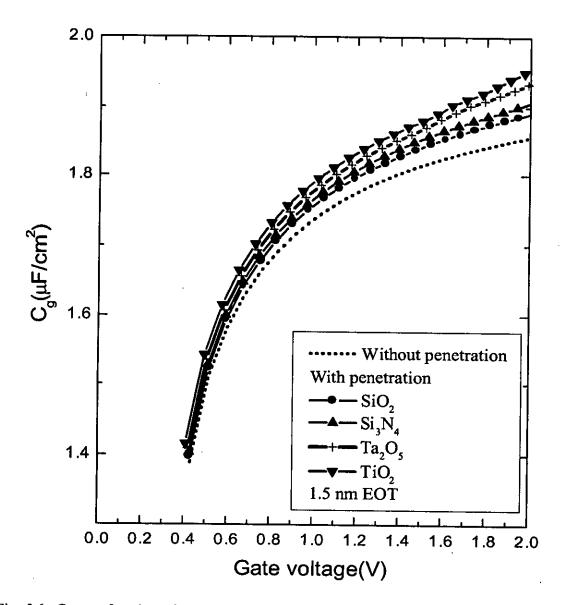

| 5.6  | $C_g$ as a function of gate voltage for different dielectrics at 1.5 nm EOT both considering and without considering penetration.                                 | 41 |

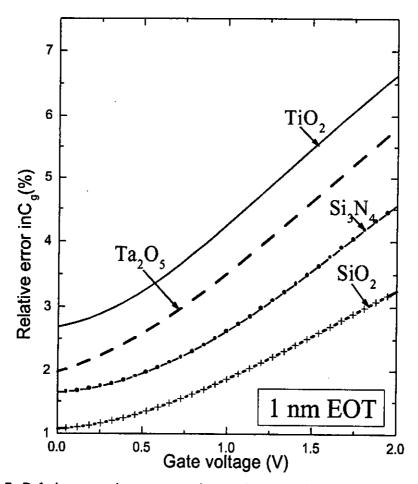

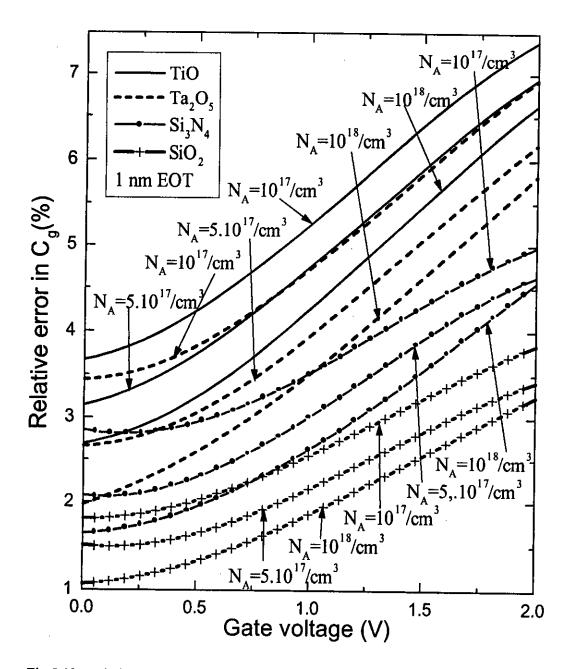

| 5.7  | Relative error in gate capacitance due to neglect of penetration for different dielectrics of 1 nm EOT.                                                           | 42 |

| 5.8  | $C_{inv}$ -N <sub>S</sub> curves with different substrate doping concentrations both considering and without considering penetration.                             | 43 |

| 5.9  | Relative error in $C_{inv}$ due to neglect of penetration for different dielectrics at different $N_{SUB}$ for 1 nm EOT.                                          | 44 |

| 5.10 | $C_g$ variation with voltage at different $N_{SUB}$ for different gate dielectric materials of 1 nm EOT.                                                          | 46 |

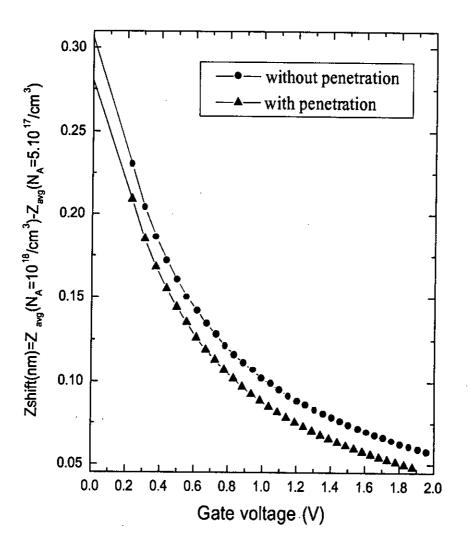

| 5.11 | $Z_{avg}$ shift due to change of $N_{SUB}$ at various voltages both considering penetration and without considering penetration for SiO <sub>2</sub> of 1 nm EOT. | 47 |

| 5.12 | Relative error in $C_g$ due to neglect of penetration at different $N_{SUB}$ for various dielectrics of 1 nm EOT.                                                 | 48 |

*.*/v

# List of tables

| 3.1 | Comparison of relevant properties of high-K dielectrics.                                                | 18 |

|-----|---------------------------------------------------------------------------------------------------------|----|

| 4.1 | Parameters of {100} orientation.                                                                        | 22 |

| 5.1 | $Z_{avg}$ (nm) of different dielectric for inversion condition of $1.5 \times 10^{13}$ /cm <sup>2</sup> | 35 |

## Acknowledgement

I wish to convey my heartiest gratitude and profound respect to my supervisor Dr. Anisul Haque, Associate Professor, Department of Electrical and Electronic Engineering (EEE), Bangladesh University of Engineering and Technology (BUET), Bangladesh, for his continuous guidance, suggestions and wholehearted supervision throughout the progress of this work, without which this thesis never be materialized. I am grateful to him for acquainting me with the world of advanced research.

I am grateful to Dr. M. M. Shahidul Hassan, Professor and Head, Dept. of EEE, Bangladesh University of Engineering and Technology (BUET), who provided with the computing facilities of the department and cooperation to complete the work. I want to thank M. Zahed Kauser, former Lecturer, Dept. of EEE, BUET for his continuous suggestions, inspiration, encouragement and many fruitful discussions.

I want to thank my friends Khairul, Yunus and many others, who were directly or indirectly related to this work, for their support and encouragement. I also thank all the personnel at the departmental library, BUET reference library and xerox section for providing me with the valuable journals and thesis papers to complete this work.

## Abstract

Scaling down of MOS device dimensions is accompanied by a decrease in gate-oxide thickness and an increase in substrate doping density. When gate oxide thickness becomes less than 2 nm, a subtantial current follows through gate-oxide due to direct tunneling. In order to reduce this current, International Technology Roadmap for Semiconductors (ITRS) has suggested replacement of SiO<sub>2</sub> gate insulator layer by high-K dielectrics. For a given equivalent oxide thickness (EOT), high-K dielectrics offer greater physical thickness. The direct tunneling (DT) current and the gate capacitance for an inverted n-MOS device with different dielectrics used as gate insulator is studied. Coupled Schrodinger's and Poisson's equations are solved self-consistently. Open boundary conditions, taking account the wavefunction tail inside the gate dielectric within the self-consistent loop are used to solve Schrodinger's equation. DT current increases exponentially with the decrease of conduction band offset for electrons travelling from silicon substrate to dielectric. As general trend of dielectrics is to decrease of conduction band offset with the increase of dielectric constant, use of high-K material as gate insulator results in prominent influence of direct tunneling of carriers on potential profile. Therefore in DT current calculation effect of wavefunction penetration on potential profile is incorporated within self-consistent loop. Results of this simulation is compared with published experimental results and also with the results of the simulation where penetration effect on potential profile is neglected. Results show that neglect of wavefunction penetration effect on potential profile causes underestimation of DT current. A comprehensive analysis of the effect of wavefunction penetration on the gate capacitance of the MOSFETs with high-K dielectrics is also done. Gate capacitance from conventional modeling is found to be independent of dielectric materials for a given EOT. The study reveals that accounting for wavefunction penetration into the gate dielectric causes gate capacitance to vary from material to material for a given EOT. Consequently wavefunction penetration effects must be considered to determine properties of future generation devices where high-K dielectrics will be employed as gate insulator.

Х

# मा शाको मल ति जि मा 96712 २ वार 30/4/02 म लाइंख्यी, 5141

$\square c$

# **Chapter 1**

#### Introduction

Due to the rapid advancement of the semiconductor device fabrication technology, metaloxide-semiconductor (MOS) devices recently approached the deep submicron regime [1] and aggressive scaling of gate dielectric thickness has continued. According to the International Technology Roadmap for Semiconductors (ITRS) 2001, in sub-100 nm generation devices, an equivalent gate oxide thickness of less than 2 nm will be required [2]. Different dimensions ( gate length, oxide thickness etc) are scaled down and the substrate doping concentration is increased. This results in large surface electric fields and steep potential wells even near threshold leading to significant quantization of carriers in the direction perpendicular to the channel. Due to quantization of energies of the inversion layer carriers in quantum well, the distribution of carriers can no longer be represented by semi-classical models [3,4], rather quantum mechanical (QM) models must be used. QM approach is essential for the calculation of several parameters; such as gate capacitance, carrier concentration, effective oxide thickness, drive current, on-state series resistance, polysilicon work function, gate leakage current etc. Since carriers in the inversion layer, localized near Si/SiO2 interface, are quantized into two dimensional (2-D) subband structure, the finite thickness of the wave function of 2-D carriers results in the inversion-layer capacitance,  $C_{inv}$ , which acts as a series capacitance with the oxide capacitance. As a consequence,  $C_{inv}$  degrades the gate capacitance and the gate oxide thickness determined from the gate capacitance becomes thicker than the physical thickness.

As potential barrier and thickness of oxide layer is finite, inversion electrons may tunnel through the oxide barrier and reach gate electrode. In deep sub-micron MOSFETs, the tunneling probability is high and a dc gate leakage current due to the quantum mechanical tunneling flows in these devices. As the thickness of the oxide layer decreases, the tunneling current increases in a nearly exponential manner. The increased current not only adversely affects the MOS device performance but also greatly increases the standby power consumption of a highly integrated chip. Therefore, there has been much interest in finding a high-permittivity gate insulator with equivalent SiO<sub>2</sub> thickness and sufficient barrier height as a replacement for SiO<sub>2</sub>. Physical thickness of such an insulating layer will be much higher than that of the corresponding SiO<sub>2</sub> layer, thereby reducing direct tunneling current considerably. But reducing oxide thickness down to less than 2 nm or using high-K dielectrics make the increase of the gate-oxide capacitance indispensable. In MOSFETs with such high capacitance, inversion layer thickness or inversion layer capacitance can have a significant influence on the electrical characteristics. However, since the barrier height of a dielectric material tends to decrease with increasing dielectric constant [5], strong tradeoffs exist between various alternative dielectrics.

#### **1.1 Literature Review**

The rapid progress of complementary metal-oxide-semiconductor (CMOS) integrated circuit technology since the late 1980's has enabled the silicon based microelectronics industry to simultaneously meet several technological requirements to fuel market expansion. These requirements include performance (speed), low static (off-state) power, and a wide range of power supply and output voltages. This has been accomplished by developing the ability to perform a calculated reduction of the dimensions of the fundamental active device in the circuit: the field effect transistor (FET)-a practice termed 'scaling'. The key element enabling the scaling of the silicon based metal-oxidesemiconductor field effect transistor (MOSFET) is the materials (and resultant electrical) properties associated with the dielectric employed to isolate the transistor gate from the Si channel in CMOS devices for decades: silicon dioxide. Since its use as gate insulator in 1957, many research works have been devoted to the conduction through silicon dioxide [6]. In the last three decades two approaches are taken in explaining the physical origin of the experimental gate current. One explains with band to band tunneling and the other is with trap assisted tunneling. In 1969 Lezlinger and Snow [7] showed that the current through thermally grown silicon dioxide is 'electrode limited'. Like other similar works done at that time, they overlooked quantum mechanical effects in the silicon inversion layer and their model under estimated the measured current. Stern and Howard [8] first considered QM treatment and solved Schrödinger's equation mostly concerning with the lowest levels of subbands split up from the conduction band. They assumed the potential profile near the interface as triangular and calculated wave functions from the variational principle. Later Stern [9] solved the self-consistent solution of Schrödinger's and Poisson's equations. Self consistent results for energy levels, populations and charge distributions were given for n-type inversion layer on p-type silicon. QM effects were taken into account in the effective mass approximation and the envelope wave function was assumed to vanish at the oxide-semiconductor interface. This assumption is equivalent to assuming an infinite potential barrier at the interface. It is considered to be justified since the barrier height at the interface is high enough (~ 3.1 eV) and hence, the contribution of the wave function tail inside the oxide is extremely small. Moglestue [10] extended the self-consistent calculations to hole inversion charges in the same way as Stern did. The charge distribution for holes and electrons was calculated for the {100} oriented Si-SiO<sub>2</sub> interface, both for weak and strong inversion, by solving Schrodinger's and Poisson's equations for particles obeying Fermi-Dirac statistics. It was shown that for weak inversion, the self consistent result did not deviate significantly from those obtained assuming a triangular potential well, but for strong inversion region carriers tend to move closer to the oxide.

Ohkura [11] studied the dependence of self-consistent solution on the substrate doping concentration. In his results he found shift of subthreshold curves with the increase in doping level, especially for impurity concentration greater than  $10^{17}$  /cm<sup>3</sup>. He also proposed a method for transferring the QM effects into the semi-classical calculation through the modification of gate oxide thickness and flat band voltage. Quantization of

electrons in inversion layer modifies the electron density. Therefore gate voltage dependency of surface potential at the interface must be calculated considering the QM effects. Actually it is found that, due to this dependence, both the non-degenerate and degenerate approximations have deviated increasingly from the actual quantum case with increasing gate voltage. This deviation also increases with decreasing oxide thickness.

Dort *et al.* proposed a simple model for explaining measurements in the high doping level regime where the conventional model fails to reproduce the experimental results [12]. The model proposed by them uses the same drift-diffusion approximation used by semi-classical model [3]. This model modifies the intrinsic carrier concentration for the silicon bandgap inversion conditions. They showed that their model agreed with the results given by self-consistent QM calculation.

Rana *et al.* [13] modeled gate current including the accumulation regime selfconsistently and showed good agreements with measured tunneling current. In their work they also explained why classical calculations were successful in predicting the tunneling currents. Self consistent solutions give a greater substrate potential drop and classical calculations give larger electric field in the oxide. The tunneling rate is dependent exponentially on both oxide electric field and the energy of incident electron. With increased gate voltage the difference in oxide electric fields predicted by the classical and self consistent models increases but at the same time the energies of electrons increase in self consistent models making the predicted tunneling currents similar in both models. They used finite element method for the purpose. To include wave function penetration into gate-oxide, they assumed that the wave function goes zero at gate-electrode-gatemetal interface instead of Si/SiO<sub>2</sub> interface.

Tunneling current from MOS inversion layer was studied by Lo *et al.* [14]. They have showed that for the purpose of modeling tunneling characteristics of electrons exhibiting quasi two-dimensional character, the transmission probability applicable to an incident Fermi gas of free electrons is no more an acceptable concept and the well known WKB (Wentzel-Krammer-Brioullion) approximation or the numerical integration of Airy function is not valid. In their work an accurate determination of the physical oxide thickness was achieved by fitting experimentally measured capacitance-versus-voltage curves to quantum-mechanically simulated capacitance-versus-voltage results. The lifetimes of quasi-bound states and the direct tunneling current was calculated using a transverse resonant method, applicable for electromagnetic waves in a non-uniform waveguide for solving the Schrödinger's equation.

Shih and others [15] have shown the viability of WKB approximation at low biases. Tunneling rate calculations invoking the WKB approximation and the numerical solution to the effective-mass Schrodinger equation have been independently carried out in a post-processing fashion following a self-consistent Schrödinger-Poisson solver. The direct-tunneling currents calculated by these two distinct approaches have been compared with oxide thickness ranging from 1.5 to 4 nm. Their findings suggest that the WKB approximation, in spite of its simplicity, remains a viable approach for predicting the gate leakage current in the direct tunneling regime. However, in the Fowler-Nordheim (FN) tunneling regime, the WKB approximation fails to capture the interference effects near the SiO<sub>2</sub>-metal interface, and the results obtained from the fully numerical approach are more consistent with experimental findings.

A modified WKB approximation has been proposed by Register et *al.* [16]. It modifies the usual tunneling probability predicted by WKB, by accounting the reflections

from potential discontinuity. In this model, the barrier height to tunneling is taken to be a function only of the total electron energy and the Si bandgap dispersion relation is modeled as a two band Franz-type.

Using the QM calculations and a modified WKB method, Yang *et al.*[17] have demonstrated an efficient model for direct tunneling current for ultra thin gate oxides. They have used it in conjunction with the C-V measurements as a complementary characterization technique for estimating physical oxide thickness. The combined C-V and tunneling current technique has been shown to provide an efficient and reasonably accurate method for characterizing ultra-thin oxides in the direct tunneling regime. The doping effects on the tunneling currents have been studied in this work, where quantum mechanical calculations of the substrate have been used to obtain accurate information about the substrate inversion layers. It was shown that higher levels of substrate doping help to reduce the direct tunneling currents at the same applied gate voltage. However, for the self-consistent loop, they have neglected effects of wave function tail in oxide on electrostatic potential by assuming the barrier at the Si/SiO<sub>2</sub> interface to be infinite. As the tunneling current across ultra thin silicon dioxide becomes too large for devices to function, they have suggested that alternative dielectric materials (such as high-K materials) will be required for the replacement of silicon dioxide

Recently Ghetti and others [18] have investigated different components of gate current using self consistent potential profile. They have calculated transmission probability through an exact solution of Schrödinger equation. Effective mass approximation was used in terms of Airy's function following the transfer matrix method.

Eric M. Vogel and others [19] modeled the tunneling currents for insulators with an effective oxide thickness of 2.0 nm using a numerical calculation of the WKB tunneling current. Their model was shown to agree with previously determined analytical WKB formulations of tunneling current for SiO<sub>2</sub>. Their tunneling model was applied to alternative dielectrics having different barrier heights and dielectric constants. Their results indicated that alternative dielectrics with higher dielectric constants resulted in lower currents at low biases. They also mentioned that if an alternative high dielectric constant material is to replace SiO<sub>2</sub>, then it will be necessary to find one with a barrier height greater than the applied voltage and one that can he fabricated with a few atomic layers (or less) of SiO<sub>2</sub> at the interface. This may prove to be a difficult challenge for future IC manufacturing.

In search of suitable high-K material, Yeo and others [20] calculated direct tunneling gate currents through  $Si_3N_4$  in both n-and pMOSFETs using an analytical model. Agreement between model and experimental data was shown. Important differences between  $Si_3N_4$  and  $SiO_2$  parameters were highlighted. It was projected that the equivalent oxide thickness of  $Si_3N_4$  gate dielectric fabricated by jet-vapor deposition (JVD) technique can be scaled down to 0.65 nm and 1.13 nm for high-performance and low-power applications, respectively before it is limited by excessive tunneling gate leakage current. In both the previous work nothing was told about the effect of penetration wheather on  $SiO_2$  or high-K dielectrics.

Later J. Zhang and others [21] gave an effective analytical model to evaluate the leakage currents for different dielectric stacked gate deep sub micron MOSFETs. They showed that for a given equivalent oxide thickness of a stacked gate, the gate leakage current decreases with an increase of high-K dielectric thickness or a decrease of interlayer thickness. Turning points at high gate biases of the *I-V* curves are observed for

$Si_3N_4/SiO_2$ ,  $Ta_2O_5/SiO_2$ ,  $Ta_2O_5/SiO_{2-y}N_y$ ,  $Ta_2O_5/Si_3N_4$  and  $TiO_2/SiO_2$  stacked gates except for  $Al_2O_3/SiO_2$  structure. Design optimization for the stacked gate architecture to obtain the minimum gate leakage current was evaluated.

Most recently Mudanai and others [22] calculated the direct tunneling current from an inverted p-substrate through different gate dielectrics by numerically solving Schrodinger's equation and allowing for wave-function penetration into the gatedielectric stack. Their numerical solution adopted a first-order perturbation approach to calculate the lifetime of the quasi-bound states. This approach was been verified to be valid even for extremely thin dielectrics (0.5 nm). They showed that for the same effective oxide thickness (EOT) the direct tunneling current decreases with increasing dielectric constant, as expected. But they did not consider effect of wave function penetration on the potential profile. For the self-consistent loop, the Schrodinger's equation was solved assuming that the wave function goes to zero at the dielectric-silicon substrate boundary on one side and at some point deep in the substrate on the other side. Once they found the self-consistent potential, the Schrodinger's equation was again solved assuming that the wave function now penetrates the gate dielectric and gate electrode. Thus, the effect of the wave function penetration into the oxide on the electrostatic potential has been ignored in this work and tunneling current was calculated in post processing fashion.

The inversion layer capacitance  $(C_{inv})$  inherent to MOS structure, plays a significant role in the gate capacitance of ultra-thin MOSFETs. The total gate capacitance  $(C_g)$  is the series combination of the oxide capacitance  $(C_{ox})$  and  $C_{inv}$ . Since device scaling rule demands thinner gate oxide and the resultant larger  $C_{ox}$ , the degradation of  $C_g$  due to  $C_{inv}$  becomes larger with the shrinkage of devices. As a result transconductance of MOSFET's which is determined by  $C_g$ , is reduced. There are two physical origins of  $C_{inv}$ , one origin is the finite band bending required to increase inversion charge density  $(N_S)$ , due to finite effective density-of-states in the band and the other due to the finite inversion layer thickness.

In the paper of Takagi et al. [23] the inversion-layer capacitance in n-channel MOSFET's was studied experimentally and theoretically with emphasis on the surface carrier concentration dependence of  $C_{inv}$  which is important in the quantitative description of the inversion layer capacitance. Based on the experimental  $N_S$  and temperature dependencies, the physical origin  $C_{inv}$  was discussed. It was shown that, at lower  $N_S$ , the  $C_{inv}$  is determined by the finite effective density of states, while, at higher  $N_S$ ,  $C_{inv}$  is determined quantum mechanically by the finite inversion-layer thickness. Also, the results of the surface orientation dependence of  $C_{inv}$  were presented as the first direct evidence for the fact that surface quantization plays a significant role in  $C_{inv}$  even at room temperature. They also studied the effect of substrate doping and verified that  $C_{inv}$  increases with substrate doping. But their work did not take account of inversion electron penetration into the gate dielectric.

Later Takagi et al. [24] compared the amount of  $C_{inv}$  and its influence on the gate capacitance between electron and hole inversion layers. It was experimentally verified that, under same physical thickness of gate oxides, the electrical gate oxide thickness, determined from the gate capacitance, is larger for inversion layer holes than that for inversion-layer electrons, because of smaller values of  $C_{inv}$  for inversion-layer holes.

In another paper of Takagi et al. [25] the influence of inversion-layer capacitance on supply voltage  $(V_{dd})$  of n- and p-MOSFET's was quantitatively examined. The physical origin of the effect of  $C_{inv}$  on  $V_{dd}$  consists in the band bending of a Si substrate in the inversion condition due to  $C_{inv}$ , which is not scaled with a reduction in gate oxide thickness. The amount and the impact of the band bending is accurately evaluated on a basis of one-dimensional (1-D) self-consistent calculations including two-dimensional (2-D) subband structure of inversion electrons and holes.

Jallepalli et al.[26] have presented the effects of hole quantization on p-MOS device characteristics and improvement on earlier results for electron quantization. A compact analytical model has been provided to quantitatively describe the threshold voltage shifts due to quantum effects as a function of the doping concentration and oxide thickness. The temperature dependence of the threshold shifts was also illustrated. The increase in the "effective" oxide thickness due to quantization has been presented as a function of the oxide field for a range of doping concentrations. To describe the quantization effects in a simple fashion, constant quantization and density of states effective-mass have also been presented. This simplified description has then been used to study the significance of quantization for buried channel p-MOS structures.

Ritcher, Hefner and Vogel have very recently compared the results of an extensive ensemble of the most advanced available QM capacitance-voltage simulators and analysis packages for a range of MOS device parameters [27]. They found that, for different simulators, in the accumulation capacitance region, extracted equivalent oxide thickness (EOT) shows on the order of 0.2 nm variations for total SiO<sub>2</sub> thickness in the range of 1.0 to 3.0 nm. Their study emphasizes on the fact that, when reporting experimentally derived electrical thickness results, it is essential to describe fully how these values were obtained. The same experimental curve can lead to different extracted EOT depending upon which quantum mechanical software is used for the analysis.

In Ref. [28], an empirical model for the DC charge centroid in terms of the gate voltage, threshold voltage and oxide thickness was developed. This model developed a one dimensional simulator using a self-consistent method by solving Schrödinger's and Poisson's equations iteratively along with Fermi-Dirac Statistics. Employing this model, a universal expression for this DC charge centroid from the accumulation to depletion region was later derived by Liu et.al. [29]. They considered the finite charge layer thickness due to quantization effects in all operating regions and thereby proposed an accurate model for C-V characterization.

Fiegna and Abramo have analyzed the QM effects on gate capacitance, threshold voltages and effective mobility of electrons in nonuniformly doped MOS structures [30]. Their results show that, with the introduction of a low doped region at the device surface, it is possible to manipulate the threshold voltage according to the circuit application. Also for a given charge sheet density, the introduction of low doped epitaxial region produces a reduction of the electron effective field, resulting in the improvement of electron effective mobility. But it leaves the total gate capacitance unaffected.

In the study of QM effects in MOS inversion layer, conventionally the wavefunction penetration inside oxide region is neglected. Since present MOS devices approach the deep submicron dimensions, this boundary condition is no longer justified. In ref [22] though wavefunction penetration was allowed but they did not consider wavefunction penetration within self-consistent loop. In ref [31] a new boundary condition encountering wavefunction penetration was introduced. In that work both conventional and the proposed boundary condition were employed in calculation of  $N_{S_3}$ , DC charge centroid shift from the oxide semiconductor interface ( $Z_{avg}$ ) and effective gate

oxide capacitance ( $C_{EFF}$ ). A comparative study of the effects of these boundary conditions made in this work suggested that the choice of boundary condition for deep submicron devices is significant and the choice becomes increasingly more important as the devices are scaled down.

Most recently, Mudanai et al. [32] have performed a comprehensive analysis of the effects of wavefunction penetration on the capacitance of NMOS capacitors for the first time, using a self-consistent Schrodinger-Poisson solver. Their study revealed that accounting for wave function penetration into the gate dielectric causes carrier profile to be shifted closer to the gate dielectric reducing the electrical oxide thickness. They observed that this shift increases with increasing gate voltage and results in an increased gate capacitance. In this work the increase in capacitance observed in the inversion region was relatively insignificant when a poly gate electrode with a doping of less than  $1 \times 10^{20}$  cm<sup>-3</sup> was used due to the poly-depletion effect. A physical picture of the effect of physical thickness on the tunneling current was also presented.

#### **1.2 Objective of the work**

We already know in deep sub-micron MOSFET, quantum effects of inversion carriers become prominent which has two important adverse effects 1) a high gate current flow due to the direct tunneling (DT) of inversion carriers and 2) inversion-layer capacitance. It has been suggested that in order to reduce direct tunneling current, the gate dielectric in devices with sub-2 nm should be a high-K dielectric instead of SiO<sub>2</sub>. The thickness of high-K dielectric should be such that the physical thickness must increase, while equivalent oxide thickness must continue to scale down. A number of studies have been reported in the literature on the modeling of gate capacitance, which is the series combination of the oxide capacitance and inversion layer capacitance, of MOS structures [23-27] and on the modeling of direct tunneling gate current [13-21]. The electrostatic potential in silicon near silicon-gate-oxide interface is typically determined from the selfconsistent solution of Schrödinger's and Poisson's equations. Closed boundary conditions commonly used for the solution of Schrödinger's equation are that the wave function goes to zero at silicon-gate-oxide interface and at some point deep inside the bulk [9]. However, due to the finite potential barrier height, some penetration of the wave function into the gate-oxide occurs [22,31,32]. This penetration is actually responsible for the DT gate current. Because of the computational involvement associated with the common solution techniques of Schrödinger's equation with open boundary conditions, in many studies, the potential profile is determined self-consistently neglecting the DT of the carriers, and the tunneling current[13-21] and gate capacitance[23-27] is calculated in a postprocessor outside the self-consistent loop. Effect of wave function penetration into the gate dielectric was considered during calculation of the gate current and gate capacitance in ref [22] and ref [32] respectively. But effect of DT of inversion electron on potential profile was neglected in these works as mentioned in review section. Also a comparison between closed and open boundary models for gate current calculation has been performed in Ref. [33], but in this study too, while using open boundary conditions, the effects of tunneling within the self-consistent loop are neglected. It is already known that the effects of carrier tunneling on potential profile is non-trivial [34, 35]. This raises questions on the accuracy of calculation of the tunneling current in a post-processor.

Providing high-K dielectric material as gate insulator is taken as alternate solution of the problem of high off state leakage current. The fabrication rule dictated by ITRS roadmap is that the width of high-K material should be such that would provide same gate capacitance of their SiO<sub>2</sub> counterpart. As general trend of high-K dielectric is to decrease of conduction band offset with the increase of dielectric constant strong trade off exists various alternate dielectrics. We will investigate the validity of the assumption of neglecting carrier tunneling effects on self-consistent electrostatic potential in calculating direct tunneling gate current and gate capacitance in deep sub-micron MOSFETs with both SiO<sub>2</sub> and high-K dielectrics as the gate insulator. Comparison between simulated and experimental results will be shown. A numerically efficient technique, proposed recently [36], will be applied in the calculation of the DT current considering tunneling within the self-consistent loop. The relative error in gate current and gate capacitance due to neglect of carrier tunneling will be calculated to find out penetration pattern with gate voltages and with oxide thickness. The results will shed light on the accurate modeling of direct tunneling current and gate capacitance of MOSFETs with high-K dielectric materials used as gate insulator. We will also study the substrate doping effect on the modeling of gate capacitance considering wave function penetration in the gate dielectric.

#### **1.3 Organization of the Thesis**

Chapter 2 reviews quantum effect in MOS devices and discusses transmission line analogy and Green's function formalism. Chapter 3 deals with the available high-k materials, their properties, interface quality etc. Chapter 4 narrates calculation of gate leakage current from density of states and results of direct tunneling current for various gate dielectrics. Chapter 5 narrates results of gate capacitance and inversion capacitance using high-k gate dielectric materials. Concluding remarks of this work will be presented in chapter 6.

# **Chapter 2**

### **Quantum Mechanical Analysis of MOS Devices**

Quantum mechanical effects in MOSFETs arise when the quantization of the inversion layer carriers occur due to the presence of a high electric field  $(F_S)$  at the surface of the semiconductor. In this chapter the theory of the quantum mechanical analysis of MOS structures are discussed. The Structure of an n channel enhancement type MOS is shown in the Fig. 2.1. It is doped p type and the gate is in contact with positively biased metal electrode. The positive potential of the metal causes the depletion of holes at the surface. If the bias is sufficiently strong, the bands will bent enough to make the conduction band come below the Fermi level, in which case an inversion layer of electrons forms near the interface. Even when the Fermi level is just below the conduction band edge, there will be a thermally induced inversion layer of electrons. The following analysis also applicable to an n-type semiconductor with a negatively biased insulator, in which case holes collect near the interface. In that case it is assumed that holes behave like particles.

#### 2.1 Self-consistent Solution

The self consistent solution of coupled Schrödinger's and Poisson's equations as proposed by Stern [9] is presented in this section which is based on three major approximations. It is assumed 1) that the effective mass approximation is valid, so that the periodic potential can be neglected. The effective masses and the dielectric constant of the perfect crystal can be used. 2) that the envelope wavefunction vanishes at the surface. Neither approximation is likely to be valid at high electric field. The third major

Fig 2.1: A typical nMOS structure.

Fig. 2.2: A typical conduction band profile of an NMOS structure.

approximation 3) is that surface states can be neglected and the effect of charges in the oxide or insulator adjacent to semiconductor can be replaced by an equivalent electric field. A typical conduction band profile for an nMOS structure is shown in Fig. 2.2

The band bending of a semiconductor can be characterized by a potential  $\phi(z)$ . In the effective mass approximation, the electronic wavefunction for the *i*th subband is the product of the Bloch function at the bottom of the conduction band and envelope function. Envelope function  $G_i(z)$  is the solution of

$$\frac{d^2 \varsigma_i}{dz^2} + \frac{2m_3}{\hbar^2} [E_i + e\phi(z)] \varsigma_i(z) = 0$$

(2.1)

Here  $m_3$  is the effective mass in the direction perpendicular to the interface and  $E_i$  is the energy of the *i*th bound state in the same direction. Boundary conditions commonly used for the solution of Eq. (2.1) are  $\varsigma_i(\infty) = 0$  and at the semiconductor-oxide interface,  $\zeta_i(0) = 0$ . Each solution of Eq. (2.1) gives the bottom of a continuum of levels called a subband. There can be as many as three values of  $m_3$  depending on the surface orientation because the conduction band of Si has six ellipsoid valleys along the (100) family of direction. In the effective mass approximation, the valleys are degenerate in pairs. Solution of Eq. (2.1) gives the eigenenergy  $E_i$  and the envelope function  $\zeta_i(z)$ .

The potential  $\phi(z)$  is found from the solution of Poisson's equation, which is as follows.

$$\frac{d^2\phi(z)}{dz^2} = -\left[\rho_{depl}(z) - e\sum_i N_i \zeta_i^2(z)\right] / \varepsilon_{sl}\varepsilon_o$$

(2.2)

here,  $\varepsilon_{si}$  is the dielectric constant of the semiconductor,  $N_i$  is the carrier concentration in the *i*th subband  $N_i$  is given by the following equation,

$$N_{i} = \frac{n_{vi}m_{di}kT}{\pi\hbar^{2}} In \left[ 1 + \exp\left(\frac{E_{F} - E_{i}}{kT}\right) \right]$$

(2.3)

where,  $n_{vi}$  is the valley degeneracy of *i*th valley,  $m_{di}$  is the density of states effective mass per valley and  $E_F$  is the Fermi energy.

$\rho_{depl}(z)$  is the charge density in the depletion layer, which is taken to be.

$$\rho_{depl}(z) = -e(N_{A} - N_{D}), \quad 0 < z < z_{d}$$

$$\rho_{depl}(z) = 0, \quad z > z_{d}$$

(2.4)

here,  $z_d$  is the depletion layer thickness given by [9] as following,

$$z_{d} = \sqrt{\frac{2\varepsilon_{si}\varepsilon_{o}\phi_{d}}{e(N_{A} - N_{D})}}$$

(2.5)

$\phi_d$  is the band bending due to depletion charge only.  $\phi_d$  can be calculated from [4] as following,

$$\phi_d = \phi_s - \frac{kT}{e} - \frac{eN_{inv}Z_{av}}{\varepsilon_{si}\varepsilon_0}$$

(2.6)

Where  $N_{inv} = \sum_i N_i$  is the total number of charge per unit area in the inversion layer and  $z_{av}$  is the average penetration of inversion charge density into Si. The two boundary conditions for solution of Eq. (2.2) are  $d\phi/dz=0$  for large z and at the surface, its value is  $F_s$ . From [9],  $F_s$  is given by,

$$F_{s} = \frac{e(N_{inv} + N_{depl})}{\varepsilon_{si}\varepsilon_{a}}$$

(2.7)

$N_{depl} = z_d(N_A - N_D)$  is the number of charge per unit area in the depletion layer. In a selfconsistent formulation, Eqs. (2.1)-(2.6) are solved iteratively for a given  $F_S$  until results converge.

#### **2.2 Transmission Line Analogy**

After Stern's publication [9] it is evident that QM effects can no longer be neglected to make a balance between the theoretical model and the experimental results with the increasing trend of scaling down the MOS feature size. To accurately model the QM effects, it is a must to solve Schrödinger's equation. But this generally requires lengthy matrix manipulation. Hence, some assumptions are made to reduce the complicacy of the problem. Various researchers worked on to derive a simple solver to reduce the computational hazards in solving the QM approach. Of those, some are mentioned in chapter 1. In this chapter, a quite simple approach is presented. This approach first uses the well-known transmission line concept used in microwave engineering. Realizing the power of this approach to solve QM problems, later Green's function is introduced to calculate eigenenergies and wave functions. When these are known, other quantities of interest can be calculated easily.

Transmission line analogy to solve Schrödinger's equation is described briefly as follows [42]. The well known equations for voltage (V) and current (I) used in transmission line theory are, with time variation assumed as  $e^{-jwt}$  instead of usual  $e^{iwt}$

$$I(z) = I_{+}^{+} (e^{\gamma_{r} z} - \Gamma_{r} e^{-\gamma_{r} z})$$

$$V(z) = I^{+} Z_{o} (e^{\gamma_{r} z} + \Gamma_{r} e^{-\gamma_{r} z})$$

(2.8)

where,  $\gamma_i$  is the propagation constant and  $\Gamma_i$  is the wave amplitude reflection coefficient given by

$$\Gamma_{t} = \frac{Z_{tt} - Z_{ot}}{Z_{tt} + Z_{ot}}$$

(2.9)

where  $Z_{it}$  and  $Z_{ot}$  are the load and the characteristics impedance of the transmission line, respectively.

If an electron with an energy E is incident on the potential barrier, then the corresponding wave function can be expressed as

$$\Psi(z) = A^{+}(e^{\gamma z} - \rho e^{\gamma z})$$

(2.10)

where time-variation is implicitly assumed as  $e^{-iEt/\hbar}$  and

$$\gamma = \alpha + i\beta = i\sqrt{\frac{2m^*}{\hbar^2}(E - V)}$$

(2.11)

is the propagation constant,  $m^*$  is the effective mass, V is the potential and  $\rho$  is the wave amplitude reflection coefficient. For the two regions shown in figure 2.3 Eq. 2.10 is rewritten as

$$\psi_{1}(z) = A_{1}^{+}(e^{\gamma_{1}z} - \rho e^{-\gamma_{2}z}) \qquad z < 0$$

$$\psi_{2}(z) = A_{2}^{+}e^{\gamma_{2}z} \qquad z > 0$$

(2.12)

Here  $\gamma_j = \alpha_j + i\beta_j = i\sqrt{\frac{2m^*}{\hbar^2}(E - V_j)}$ ,  $m_j$  and  $V_j$  (j = 1,2), are the effective mass and the potential respectively for the *i*th project Since for  $\lambda = 0$  does not set  $z_i$ .

the potential, respectively, for the *j*th region. Since, for z > 0 the region is of infinite extent, it is evident that there is no reflection. The boundary conditions for this problem, with regard to the continuity of wave function, are

$$\frac{\psi_1(0) = \psi_2(0)}{\frac{\psi_1'}{m_1^*} = \frac{\psi_2'}{m_2^*}}$$

(2.13)

Using these boundary conditions an expression for  $\rho$  is found as

$$\rho = \frac{\frac{\gamma_2}{m_2^*} - \frac{\gamma_1}{m_1^*}}{\frac{\gamma_1}{m_1^*} + \frac{\gamma_2}{m_2^*}}$$

(2.14)

If a function,  $\psi^{TM}(z)$  is defined as

$$\psi^{TM}(z) = \frac{2\hbar}{im^*} \frac{d\psi}{dx}$$

(2.15)

then,

$$\Psi^{TM}(z) = A^{+}Z_{o}(e^{\gamma z} + \rho e^{-\gamma z})$$

(2.16)

where,

$$Z_o = \frac{2\gamma \hbar}{im^*} \tag{2.17}$$

Using the value of  $Z_o$  in Eq. 2.14, it is found that

$$\rho = \frac{Z_{o,2} - Z_{o,1}}{Z_{o,2} + Z_{o,1}} \tag{2.18}$$

where  $Z_{0,1}$  and  $Z_{0,1}$  are defined for region 1 and region 2, respectively.

From the above discussion, an analogy is found between voltage and current expressed by Eqs. 2.8 with  $\psi^{TM}$  and  $\psi$  expressed by Eqs. 2.16 and 2.10, respectively. Since, the transmission line impedance is the ratio of V and I, so the ratio of  $\psi^{TM}$  and  $\psi$

is called as wave impedance by using this analogy. This fact can be verified by using another analogy found between the equation of wave amplitude reflection coefficient for electron wave ( $\rho$ ) and the equation of wave amplitude reflection coefficient for transmission line ( $\Gamma_{\nu}$ ), as seen in Eqs 2.18 and 2.9, with  $Z_{lt}$  replaced by  $Z_{0,2}$  and  $Z_{ot}$ replaced by  $Z_{0,1}$  Moreover,  $\psi^{TM}$  and  $\psi$  are continuous across the boundary between the two regions, which directly corresponds to the continuity conditions for voltage and current at the junction between two transmission lines. All these lead to a conclusion that a quantum mechanical wave impedance concept can be introduced analogous to transmission line impedance as given by at any plane z

$$Z(z) = \frac{\psi^{TM}(z)}{\psi(z)}$$

(2.19)

Thus, transmission line concept can be applied for QM calculations. For example, the input impedance,  $Z_i$  at z = -l may be expressed in terms of load impedance,  $Z_l$  at z = 0 as in transmission line

$$Z_{i} = Z_{o} \frac{Z_{i} \cosh(\gamma i) - Z_{o} \sinh(\gamma i)}{Z_{o} \cosh(\gamma i) - Z_{i} \sinh(\gamma i)}$$

(2.20)

An important feature of using transmission line concept in QM calculations is its ability to calculate the eigenenergy of any arbitrary potential well. Becasue, from Eq. 2.19, at any eigenenergy, the wave impedances looking to the right (positive direction) and to the left (negative direction), at any plane z must be equal, i.e.

$$Z_{iR} = Z_{iL} \tag{2.21}$$

#### 2.3 Green's Function Formalism

Green's function formalism is used along with the transmission line analogy to include the effects of energy broadening of the density-of-states due to either finite particle lifetime in a well (i.e. when particles leak out from a quantum well) or the presence of inelastic scattering processes. Although this formalism is based on a complicated Green's function approach, it allows one to calculate easily the normalized wave functions in arbitrary 1-D quantum well structures [36].

In this formalism the QM wave impedance is redefined in terms of the logarithmic derivative of the retarded Green's function,  $G^{R}$  as

$$Z(z,z';E) = \frac{2\hbar}{im_z^*} \left[ \frac{\partial G^R(z,z';E)}{\partial z} / G^R(z,z';E) \right]$$

(2.22)

where  $G^{R}$  satisfies the equation,

Э

$$\left[E + \frac{\hbar^2}{2m_z^*} \frac{\partial^2}{\partial z^2} - V(z) + i\varepsilon\right] G^R(z, z'; E) = \delta(z - z')$$

(2.23)

where  $\varepsilon$  is an infinitesimally small positive energy. The Green's function in this context is discussed in detail in Ref. [37]. Owing to the property of  $G^R$ , Z(z, z'; E) has a discontinuity at z = z', and one needs two boundary conditions to determine Z(z, z'; E). To obtain these boundary conditions, the potential profile is assumed flat sufficiently far from z = z' in both directions. If  $V_R$  is the constant potential at  $z = \infty$  and if  $V_L$  is the constant potential at  $z = -\infty$  the Green's function in these regions can be expressed as [36]:

$$G^{R}(z \to \infty, z'; E) \approx e^{\gamma R(z-z')}$$

$$G^{R}(z \to -\infty, z'; E) \approx e^{-\gamma L(z-z')}$$

(2.24)

where

è.

$$\gamma_{R(L)} = i \sqrt{\frac{2m_z^*}{\hbar^2} (E - V_{R(L)})}$$

(2.25)

$\gamma_{R(L)}$  is imaginary if  $E > V_{R(L)}$ , else this is real. From the above relationships, the boundary conditions are found as

$$Z(z \to \infty, z'; E) = Z_o(\infty)$$

$$Z(z \to -\infty, z'; E) = -Z_o(-\infty)$$

(2.26)

where

$$Z_o(\pm\infty) = \frac{2\hbar}{im_z^*} \gamma_{R(L)}$$

(2.27)

From the properties of the Green's functions it can be shown that [37]

$$Z(z, z'; E) = Z_{iR}(z; E) \text{ for all } z' < z$$

$$Z(z, z'; E) = Z_{iL}(z; E) \text{ for all } z' > z$$

(2.28)

It is noteworthy that  $Z_{iR}$  ( $Z_{iL}$ ) does not depend on z' as long as z > z' (z < z). Using transmission line analogy,  $Z_{iR}$  ( $Z_{iL}$ ) can be calculated. The eigenenergies of an arbitrary quantum well can be determined using following condition:

$$Z_{iR}(z; E) = Z_{iL}(z; E)$$

(2.29)

as from tranmission line analogy, at any eigenenergy and for all values of z inside the quantum well the above equation must be satisfied. Once an eigenenergy is found, the corresponding normalized wavefunction can be calculated using the following relationship:

$$\left|\varphi_{n}(z)\right|^{2} = \frac{4\varepsilon}{\hbar} \Im\left[\frac{i}{Z_{iR}(z;E_{n}) - Z_{iL}(z;E_{n})}\right]$$

(2.30)

By definition, the one dimensional (1D) DOS is given by the imaginary part of the diagonal term of 1D retarded Green's function  $G^{R}$ ,

$$N(z;E) = -\frac{1}{\pi} \Im m \Big[ G^{R}(z,z;E) \Big]$$

(2.31)

Relating diagonal part of  $G^{R}$  to quantum mechanical impedence, equation (2.31) reduces to,

$$N(z;E) = \frac{4}{\pi\hbar} \Im m \left[ \frac{j}{Z_{iR}(z;E_n) - Z_{iL}(z;E_n)} \right]$$

(2.32)

Equations 2.29 and 2.30 are used to find the eigenenergies and wavefunctions in MOS inversion layers. Note that in calculating the wavefunctions the conventional boundary conditions that the wave function is zero at the oxide-semiconductor interface and inside the bulk are not used. Rather, the boundary conditions used (Equation 2.26) assume that the potential profile is flat sufficiently far from the interface in both directions. These boundary conditions, known as the asymptotic boundary conditions, are definitely physically more acceptable boundary conditions and allow one to include the exponentially decreasing tail of the wave function inside the oxide in the calculation.

# **Chapter 3**

#### **Properties of high-K dielectrics**

The key element enabling the scaling of the Si-based MOSFET is the material (and resultant electrical) properties associated with the dielectric employed to isolate the transistor gate from the Si channel in CMOS devices. For decades, silicon dioxide has been the material of choice. The use of amorphous, thermally grown SiO<sub>2</sub>, as a gate dielectric offers several key advantages in CMOS processing including a stable (thermodynamically and electrically), high-quality Si-SiO<sub>2</sub> interface as well as superior electrical isolation properties. These outstanding electrical properties clearly present a significant challenge for any alternative gate dielectric candidate. Many dielectrics appear favorable and show the most promise toward successful integration into the expected processing conditions for future CMOS technologies, especially due to their tendency to form at interfaces with Si (e.g. silicates). A list of these available dielectrics and material properties is shown in Table 3.1 [38].

#### **3.1 Properties of available dielectrics**

In SiO<sub>2</sub> the density of states transition from the substrate into the SiO<sub>2</sub> layer indicates that the full band gap of SiO<sub>2</sub> is obtained after only about two mono layers of SiO<sub>2</sub>. Within two mono layers of the Si channel interface, oxygen atoms do not have the full arrangement of oxygen neighbors and therefore cannot form the full band gap that exists within the "bulk" of the SiO<sub>2</sub> film. These results set an absolute physical thickness limit of SiO<sub>2</sub> to 0.7 nm. Below this thickness, the Si rich interfacial regions from the channel and polycrystalline Si gate interfaces used in MOSFETs overlap, causing an effective "short" through the dielectric, rendering it useless as an insulator. And it is already mentioned that in sub-2 nm dielectric thickness leakage current is very high. Therefore below 2 nm regime high-K dielectrics are favorable.

In addition to leakage current increasing with scaled oxide thickness, the issue of boron penetration through the oxide is a significant concern. The large boron concentration gradient between the heavily doped poly-Si gate electrode, the undoped oxide and lightly doped Si channel causes boron to diffuse rapidly through a sub-2 nm oxide upon thermal annealing, which results in a higher concentration of boron in the channel region. A change in channel doping then causes a shift in threshold voltage, which clearly alters the intended device properties in an unacceptable way.

The concerns regarding high leakage currents and boron penetration have led to materials structures such as oxy-nitrides and oxide/nitride stacks for near-term gate dielectric alternatives. These structures provide a slightly higher K value than SiO<sub>2</sub> (pure Si<sub>3</sub>N<sub>4</sub> has K = 7) for reduced leakage (since the film is physically slightly thicker), reduced boron penetration and better reliability characteristics. The addition of N<sub>2</sub> to SiO<sub>2</sub>

| Material                       | Dielectric<br>constant<br>(k) | Band gap<br>(E <sub>G</sub> ) | $\Delta E_{C}$ to Si |

|--------------------------------|-------------------------------|-------------------------------|----------------------|

| SiO <sub>2</sub>               | 3.9                           | 8.9                           | 3.2                  |

| Si <sub>3</sub> N <sub>4</sub> | 7                             | 5.1                           | 2                    |

| Al <sub>2</sub> O <sub>3</sub> | 9                             | 8.7                           | 2.8                  |

| Y <sub>2</sub> O <sub>3</sub>  | 15                            | 5.6                           | 2.3                  |

| La <sub>2</sub> O <sub>3</sub> | 30                            | 4.3                           | 2.3                  |

| Ta <sub>2</sub> O <sub>5</sub> | 26                            | 4.5                           | 1-1.5                |

| TiO <sub>2</sub>               | 80                            | 3.5                           | 1.2                  |

| HfO <sub>2</sub>               | 25                            | 5.7                           | 1.5                  |

| ZrO <sub>2</sub>               | 25                            | 7.8                           | 1.4                  |

TABLE 3.1. Comparison of relevant properties of high-K dielectrics.

greatly reduces boron diffusion through the dielectric, and has been shown to result from the particular Si-O-N network bonding formed in silicon nitride and oxy-nitride. Furthermore, small amounts of  $N_2$  (0.1 at. %) at or near the Si channel interface have been shown to improve device performance.

Scaling with oxy-nitrides/nitrides appears are limited to 1.3 nm. Below this, the effects of gate leakage, reliability or electron channel mobility degradation will most likely prevent further improvements in device performance. According to the most recent industry roadmaps,  $SiO_xN_y$ , and  $Si_xN_y$ /SiO<sub>2</sub> dielectrics represent current three year near-term solutions for scaling the CMOS transistor.

The most commonly studied high-K gate dielectric candidates have been materials systems such as  $Ta_2O_5$ , which have dielectric constants ranging from 10 to 80,  $\Delta E_C=1-1.5$  eV and have been employed mainly due to their maturity in memory capacitor applications. Interfacial reaction has been observed for the case of  $Ta_2O_5$  on Si, therefore its high permittivity could not be fully utilized.

Alumina (Al<sub>2</sub>O<sub>3</sub>) with  $\Delta E_C = 2.3 - 2.8$  eV is a very stable and robust material, and has been extensively studied for many applications. Al<sub>2</sub>O<sub>3</sub> has many favorable properties, as shown in Table 3.1, including a high band gap, thermodynamic stability on Si up to high temperatures, and is amorphous under the conditions of interest. The drawback is that  $A1_2O_3$  only has K = 8-10, and would therefore make it a relatively short-term solution for industry's needs (1-2 generations).

$Y_2O_3$  and  $La_2O_3$  with  $\Delta E_C = 2.3$  eV, are also studied for the purposes of high-K gate dielectrics. The dielectric constant of the  $Y_2O_3$  grown on SiO<sub>2</sub> was found to be 17 to 20 but for  $Y_2O_3$  grown directly on Si, it was found that K= 12. This lower measured permittivity value may have resulted from growth of interfacial SiO<sub>2</sub>, during the thermal oxidation step.  $La_2O_3$  has a high dielectric constant 30. Pure La is well known to be very volatile and reactive in air, and  $La_2O_3$  will absorb water vapor from air. These characteristics signify that any *ex situ* exposure of these films to air will certainly result in an uncontrolled reaction

A substantial amount of investigation has gone into  $\text{TiO}_2 (\Delta E_C = 1.2 \text{eV})$ ,  $ZrO_2 (\Delta E_C = 1.4 \text{eV})$  and  $HfO_2 (\Delta E_C = 1.5 \text{eV})$ , as these systems have shown much promise in overall materials properties as candidates to replace SiO<sub>2</sub>. The TiO<sub>2</sub>, system has been heavily studied for high-K applications both for memory capacitors and in transistors. It is attractive because it has a high permittivity of K=80-110, depending on the crystal structure and method of deposition. This anomalously high permittivity, which arises through a strong contribution from soft phonons involving Ti ions, is not exhibited by the other metal oxides.

HfO<sub>2</sub> films in A1/HfO<sub>2</sub>/Si structures show K= 22-25 and ZrO<sub>2</sub> films in Al/ZrO<sub>2</sub> /Si structures show K= 17-18. Pure ZrO<sub>2</sub> anf HfO<sub>2</sub> show mobile ion transport and crystallization of the metal oxides either during the deposition process or upon moderate post-annealing conditions. The interface quality of these systems remains a critical issue, however, since the materials in particular are extremely susceptible to O<sub>2</sub> diffusion and reaction at the channel interface. It was observed that processing in inert ambient reduces mobile ion transport. This indicates the possible application of these materials as high-K candidate.

To select a gate dielectric with a higher permittivity than that of SiO<sub>2</sub>, the required permittivity must be balanced, however, against the barrier height for the tunneling process. For electrons traveling from the Si substrate to the gate, this is the conduction band offset, for electrons traveling from the gate to the Si substrate, this is work function of gate material. This is because leakage current increases exponentially with decreasing barrier height (and thickness) for electron direct tunneling transport. In order to obtain low leakage currents, it is desirable to find a gate dielectric that has a large  $\Delta E_C$  value to Si . If the experimental  $\Delta E_C$  values for various oxides are much less than 1.0 eV, it will likely preclude using these oxides in gate dielectric applications, since electron transport (either by thermal emission or tunneling) would lead to unacceptably high leakage currents.

In contrast to the general trend of increasing permittivity with increasing atomic number for a given cation in a metal oxide, the band gap  $E_G$  of the metal oxides tends to decrease with increasing atomic number, particularly within a particular group in the periodic table. In the cases of Ta<sub>2</sub>O<sub>5</sub> and TiO<sub>2</sub>, both materials have small  $E_G$  values and correspondingly small  $\Delta E_C$  values. These small  $\Delta E_C$  values directly correlate with high leakage currents for both materials, making pure Ta<sub>2</sub>O<sub>5</sub> and TiO<sub>2</sub> unlikely choices for gate dielectrics. Table 3.1 also shows, however, that La<sub>2</sub>O<sub>3</sub>, HfO<sub>2</sub>, and ZrO<sub>2</sub> offer relatively high values for both K and  $E_G$ .

# **Chapter 4**

### Modeling of Direct Tunneling gate current

Due to finite potential barrier height and width of gate dielectric material, inversion electrons can tunnel into the gate electrode from the inversion layer. As a consequence of this tunneling, a leakage current flows in the gate which increases standby power consumption. To restrict this current we have to replace SiO<sub>2</sub> gate dielectric by suitable high-K material in deep sub-micron MOSFET's as predicted by ITRS roadmap [2]. In such leaky quantum well, the lifetime of inversion carriers is finite and the 1D DOS broadens in energy around each eigenvalue. When open boundary conditions are used, the Hamiltonian for a finite system becomes non-Hermitian and the eigenenergies become complex. The real parts give the energies of the quasi-bound states and the imaginary parts are related to lifetime. Since the calculation of complex eigenenergies is numerically complicated, typically Schrodinger's and Poisson's equations are solved self consistently neglecting tunneling of carriers into the gate dielectric and gate current is calculated in a post processing fashion assuming effect of wave function penetration on potential profile to be negligible [13-17, 22]. Therefore, we adopt an alternate technique using the theory developed in chapter 2, and the direct tunneling current is calculated considering effects of wavefunction penetration self-consistent potential. The consequences of neglecting this effect are also investigated.

#### 4.1 Theory of current calculation

In self-consistent solution, Eqs. 2.1 to 2.6 are solved iteratively for a fixed inversion electron density  $N_S$  with the help of Green's function. Wave functions are calculated from the logarithmic derivative of the retarded Green's function (Eq. 2.30).

It may be mentioned that once self-consistent potential profile for any fixed inversion condition is obtained, gate voltage required to obtain the inversion condition can be calculated from the following equation:

$$V_G = \phi_S + T_{OX} F_{OX} + \phi_{ms} + \phi_{poly} \tag{4.1}$$

Where  $\phi_S$  is the total band bending,  $\phi_{ms}$  the difference between the metal and semiconductor work functions,  $\varphi_{poly}$  is the voltage drop in the poly-silicon depletion region. Here  $T_{OX}$  and  $F_{OX}$  are oxide width and electric field in the oxide respectively.

The Gate current due to quantum mechanical tunneling is calculated from the carrier concentration and the lifetimes of the carriers of all eigenstates using following relationship,

$$J = \sum_{i} \frac{qN_i}{\tau_i} \tag{4.2}$$

Here,  $N_i$  is the concentration of the electrons in the *i*th eigenstate (Eq. 2.3),  $\tau_i$  is the lifetime of the electrons in the *i*th eigenstate and J is the total gate leakage current. The peaks of the energy broadened 1D DOS occur at the eigenenergies of the quasi-bound states and the lifetimes of the inversion layer electrons are related to the energy broadening of DOS according to,

$$\tau_{i} = \frac{\hbar}{2\Gamma_{i}} \tag{4.3}$$

Here,  $\Gamma_i$  is the Full-Width at Half-Maximum (FWHM) of the energy broadening around the *i*th eigenenergy. The position dependent DOS as a function of energy around each eigenenergy is calculated using Eq. (2.31). The FWHM of the DOS can be evaluated anywhere inside the well since it has been shown that the energy broadening of the DOS is the same at all positions [39].

Inclusion of carrier tunneling within self consistent loop can easily be done by incorporating open boundary condition (Eq. 2.26) while calculating normalized wave functions during solving Schrodinger's equation. The problem of dealing with non Hermitian matrices during calculation of eigenenergies are avoided here as eigenenergies are found by searching peaks of DOS (Eq. 2.31). Once self-consistent potential profile is obtained considering DT effect on potential profile, gate leakage current can easily be determined from Eqn. (4.2) and Eqn. (4.3) by searching FWHM broadening of DOS. Values of conduction band offset used for various dielectrics are shown in the Table 3.1 of chapter 3. Figure 4.1(a) shows typical self-consistent potential profile found for inversion condition of  $N_S = 10^{13}$ /cm<sup>2</sup> for 1.5 nm thickness of SiO<sub>2</sub> gate material with open boundary condition.

Closed boundary conditions are simulated by using theoretically infinite conduction band offset for electrons tunneling from silicon to gate dielectric. In practice, we have used a barrier height of 83.1 eV to represent closed boundary condition. Figure 4.1 (b) shows the potential profile found for inversion condition of  $N_S=10^{13}/\text{cm}^2$  for 1.5 nm thickness of SiO<sub>2</sub> gate material using closed boundary conditions.

#### 4.2 Result and Discussion

All simulations are performed for {100} Si substarte. For high-K dielectrics, Ta<sub>2</sub>O<sub>5</sub>, Si<sub>3</sub>N<sub>4</sub> and Al<sub>2</sub>O<sub>3</sub> are chosen. Values of conduction band offset and dielectric constant are taken from Ref. [38] as mentioned in Table 3.1. Table 4.1 shows values of effective masses for {100} surface orientation which are taken from Ref. [9]. Effective mass of electrons in gate dielectric region are taken to be  $0.50m_0$  for all the dielectric materials [21]. All calculations are done for room temperature (T=300K). Substrate doping density  $N_A=10^{18}/\text{cm}^3$  is used and n<sup>+</sup>-ploysilicon with doping density equal to  $10^{20}/\text{cm}^3$  is used as the gate electrode.

Fig. 4.1: Potential profile obtained self-consistently with SiO<sub>2</sub> gate dielectric of 1.5 nm thickness at inversion charge density of  $N_S = 10^{13}/\text{cm}^2$  a) open boundary conditions b) closed boundary conditions.

| Surface           | {100} |        |          |

|-------------------|-------|--------|----------|

| Valleys           | Lower | Higher |          |

| Degeneracy        | 2     | 4      | <u> </u> |

| Normal mass       | 0.916 | 0.190  | ·        |

| Density-of-states | 0.190 | 0.417  |          |

| mass per valley   |       |        |          |

Table 4.1: Parameters of {100} orientation.

All effective masses are in unit of free electron mass.

Figure 4.2 shows modeled direct tunneling currents from the inversion layer for oxide thickness between 1.4 nm to 2 nm as a function of applied gate voltage both considering and without considering carrier tunneling effects on electrostatic potential. Results are also compared with experimental data obtained from Ref. [17]. From Figure 4.2 one can see that excellent agreement between measured and modeled currents are found when we consider carrier tunneling within the self-consistent loop. It is evident that neglect of wavefunction penetration causes under estimation of direct tunneling current. For these devices, good agreement between the modeled and experimental direct tunneling currents is achieved for gate voltages greater than 0.35V. Below this value of gate voltage, experimental current is much higher than the simulated current (results not shown). The discrepancy below 0.35 V is shown to be due to inelastic trap scattering of electrons in gate oxide region [41].

Fig. 4.2: Simulated and experimental direct tunneling currents in nMOSFET's both considering and without considering carrier tunneling effects within the self-consistent loop. Experimental data are taken from Ref. [17]. The poly-silicon doping level is  $N_{poly}=10^{20}/\text{cm}^3$ .

Fig. 4.3 shows the relative error in direct tunneling gate current as a function of gate voltage. We see that the relative error increases with the increase of gate voltage for a given oxide thickness and decreases with the increase of the gate oxide thickness at a fixed gate voltage. This agrees with the fact that DT of inversion electrons increases with the increase of gate voltage for a fixed oxide thickness and for a fixed gate voltage decreases with the increase of gate oxide thickness. We see that this error is well above 40% at high gate voltage in thin gate-oxide devices. The error is found to be significant over the whole voltage regime. In Ref. [22] it is claimed without adequate justification that neglect of penetration effect on potential profile does not have any significant influence on modeling of DT currents. This allows calculation of the gate current in a post processor. But our results show that the neglect of the penetration effects causes under-estimation of the measured current. As the error is non-trivial over the entire gate voltage range, we conclude that for accurate modeling of DT gate current, tunneling or penetration effect on potential profile should be considered within the self-consistent loop. The good agreement between our simulation and experiment also shows the usefulness of our model.

£

Fig. 4.3: Relative error in direct tunneling gate current shown in Fig. 4.2 due to neglect of tunneling effects within self-consistent loop.

We have already mentioned that as the gate lengths of CMOS devices continue to scale down to the sub-100 nm regime, the device requirements dictate that the gate oxide thickness be scaled down to below 2 nm. However, as the thickness decreases below 2 nm, the direct tunneling current increases rapidly. In order to decrease the leakage current caused by tunneling, the physical thickness of the dielectric layer must increase, while the equivalent oxide thickness must continue to scale down. This is only possible with the introduction of suitable high-dielectric constant (high-K) materials. Hence, ITRS has called for the introduction of high-K materials for MOSFET's below 100-nm channel length due to direct tunneling problems in SiO<sub>2</sub>. For this reason we have performed simulation of DT gate current at various EOT with high-K dielectric materials. Materials chosen for simulation are Ta<sub>2</sub>O<sub>5</sub>, Si<sub>3</sub>N<sub>4</sub> and Al<sub>2</sub>O<sub>3</sub>. This simulation is done taking Al as gate electrode material and dielectric thickness is taken to provide same gate capacitance of SiO<sub>2</sub> counter part (EOT) as dictated by ITRS [2].