### IMPACT OF UNIAXIAL STRAIN ON THE CAPACITANCE-VOLTAGE CHARACTERISTICS OF HIGH-k DOUBLE GATE MOSFET

A thesis submitted for the partial fulfillment of the requirement of the degree

of

Master of Science in Electrical and Electronic Engineering

By

Khadija Abul Khair

**Department of Electrical and Electronic Engineering**

Bangladesh University of Engineering and Technology

Dhaka-1000

December, 2011

## Declaration

It is hereby declared that this thesis or any part of it has not been submitted elsewhere for the award of any degree or diploma.

Khadija Abul Khair

## Acknowledgements

The author would like to thank Dr. Quazi Deen Mohd Khosru, Professor, Department of Electrical and Electronic Engineering (EEE), Bangladesh University of Engineering and Technology (BUET), Dhaka, for his many fruitful suggestions and constant support during this research.

The author is also grateful to Dr. Saifur Rahman, Professor and Head, Department of Electrical and Electronic Engineering, Bangladesh University of Engineering and Technology (BUET), Dhaka, for providing all the necessary helps and his valuable time in this thesis work. Dr. Md. Ziaur Rahman Khan had given many suggestions and creative ideas and the author is grateful to him.

The author would also like to express her sincere gratitude to A. T. M. Golam Sarwar and Mahmudur Rahman Siddiqui for their part.

Finally the author would like to thank Dr. Md. Anwarul Abedin, Associate Professor, Department of EEE, DUET, Gazipur, for providing solutions and fruitful discussions.

BUET, Dhaka,

Author

December, 2011

## Dedication

To My Mother

### Abstract

Suppression of short-channel effects (SCE) will be key challenges for transistor scaling. High-k Double-Gate MOSFET may eventually be needed to meet performance requirements in the sub-20nm gate length regime because SCE can be effectively suppressed without the need for high channel doping concentrations, resulting in enhanced carrier mobilities. Strained-Si has also been considered as a key technology for enhancing carrier mobilities via modification of the electronic band structure of the channel material and effective masses of the electron. In this work, to accurately simulate the DG MOSFET self-consistent fully-coupled1D Schrodinger and Poisson's equation model has been used. Quantum mechanical effects have been considered by incorporating wave function penetration effect and open boundary conditions at the Si/HfO<sub>2</sub> interfaces. It has been found that, the uniaxial strain increases the gate capacitance as it reduces eigen energy levels of longitudinal valleys of Si, thereby increasing the total charge. Moreover, the uniaxial strain reduces the threshold voltage, shifts the inversion channel towards the Si/HfO<sub>2</sub> interfaces and reduces the gate leakage current.

## Contents

|     | Certification                                                             | V                                                                                                                                                                                                                                                                                                                                                                            |

|-----|---------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|     | Declaration                                                               | vi                                                                                                                                                                                                                                                                                                                                                                           |

|     | Acknowledgements                                                          | vii                                                                                                                                                                                                                                                                                                                                                                          |

|     | Dedication                                                                | viii                                                                                                                                                                                                                                                                                                                                                                         |

|     | Abstract                                                                  | ix                                                                                                                                                                                                                                                                                                                                                                           |

|     | Introduction                                                              | 1                                                                                                                                                                                                                                                                                                                                                                            |

| 1.1 | Mobility Scaling                                                          | 1                                                                                                                                                                                                                                                                                                                                                                            |

| 1.2 | Multiple Gate Devices                                                     | 2                                                                                                                                                                                                                                                                                                                                                                            |

| 1.3 | Literature Review                                                         | 2                                                                                                                                                                                                                                                                                                                                                                            |

| 1.4 | Objective of The Thesis                                                   | 3                                                                                                                                                                                                                                                                                                                                                                            |

| 1.5 | Organization of The Thesis                                                | 4                                                                                                                                                                                                                                                                                                                                                                            |

|     | Double-Gate MOSFET                                                        | 5                                                                                                                                                                                                                                                                                                                                                                            |

| 2.1 | Device Structure and Physics                                              | 5                                                                                                                                                                                                                                                                                                                                                                            |

| 2.2 | Short Channel Effects                                                     | 10                                                                                                                                                                                                                                                                                                                                                                           |

| 2.3 | Volume Inversion                                                          | 13                                                                                                                                                                                                                                                                                                                                                                           |

| 2.4 | High-k Dielectrics                                                        | 13                                                                                                                                                                                                                                                                                                                                                                           |

| 2.5 | Gate Capacitance                                                          | 15                                                                                                                                                                                                                                                                                                                                                                           |

| 2.6 | Gate leakage Current                                                      | 16                                                                                                                                                                                                                                                                                                                                                                           |

| 2.7 | Strained-Si Technology                                                    | 18                                                                                                                                                                                                                                                                                                                                                                           |

|     | 2.7.1 Physics of Strained Si                                              | 22                                                                                                                                                                                                                                                                                                                                                                           |

|     | Simulation Technique                                                      | 29                                                                                                                                                                                                                                                                                                                                                                           |

| 3.1 | Poisson's Equation Solver                                                 | 29                                                                                                                                                                                                                                                                                                                                                                           |

|     | 1.2<br>1.3<br>1.4<br>1.5<br>2.1<br>2.2<br>2.3<br>2.4<br>2.5<br>2.6<br>2.7 | DeclarationAcknowledgementsDedicationAbstractIntroduction1.1Mobility Scaling1.2Multiple Gate Devices1.3Literature Review1.4Objective of The Thesis1.5Organization of The ThesisDouble-Gate MOSFET2.12.2Short Channel Effects2.3Volume Inversion2.4High-k Dielectrics2.5Gate Leakage Current2.7Strained-Si Technology<br>2.7.1 Physics of Strained Si<br>Simulation Technique |

|   | 3.2 | Poisson's Equation Solver for DG MOS     | 30 |

|---|-----|------------------------------------------|----|

|   | 3.3 | Schrodinger's Equation Solver            | 32 |

|   | 3.4 | Schrodinger's Equation Solver for DG MOS | 33 |

| 4 |     | Simulations and Results                  | 40 |

|   | 4.1 | Charge Calculation                       | 40 |

|   | 4.2 | The Effects on Gate Capacitances         | 47 |

|   | 4.3 | The Effects on Gate Leakage Current      | 52 |

| 5 |     | Conclusion                               | 55 |

|   | 5.1 | Conclusion                               | 55 |

|   | 5.2 | Future Works                             | 55 |

|   |     | References                               | 56 |

## **List of Figures**

| Figure 2.1<br>Figure 2.2<br>Figure 2.3<br>Figure 2.4<br>Figure 2.5<br>Figure 2.6<br>Figure 2.7 | Different structure of DG MOSFET<br>Planar Device Structure<br>FinFET Structure<br>Vertical Device Structure<br>The two operation modes for DG MOSFETs<br>Symmetric DG MOSFET<br>Decomposition of a DG MOSFET into the ideal core and the parasitic                                                                                                                                                                                                                                                                      | 5<br>6<br>7<br>8<br>8<br>9<br>10 |

|------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------|

| Figure 2.8                                                                                     | components<br>Definition of coordinate system in a multiple-gate device. Gate-induced<br>fields are in the x and z directions. Drain penetration field is in the y<br>direction                                                                                                                                                                                                                                                                                                                                          | 11                               |

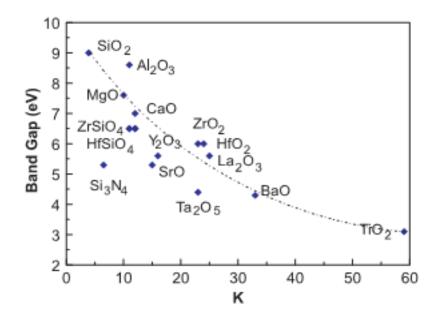

| Figure 2.9                                                                                     | Band gap vs. dielectric constant plot of various high-k materials studied forgateinsulator                                                                                                                                                                                                                                                                                                                                                                                                                               | 14                               |

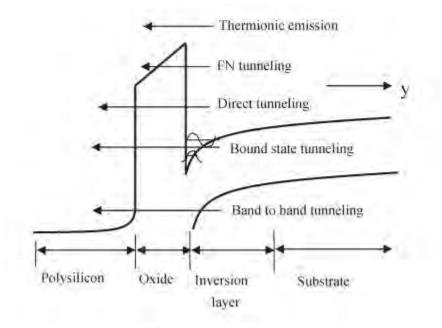

| Figure 2.10                                                                                    | Schematic gate-current components between the polysilicon gate and semiconductor substrate in nanoscale MOSFETs                                                                                                                                                                                                                                                                                                                                                                                                          | 16                               |

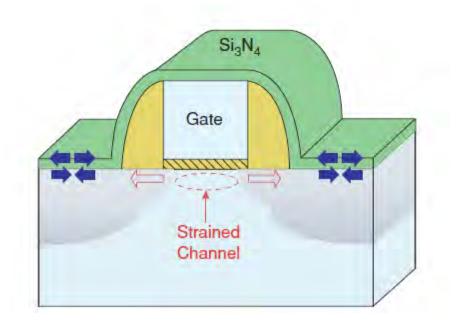

| Figure 2.11                                                                                    | Silicon nitride capping layer to create tensile strain innMOS                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 19                               |

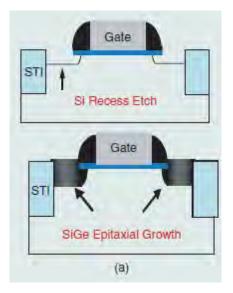

| Figure 2.12                                                                                    | Strained-Si p-channel MOSFET process flow                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 20                               |

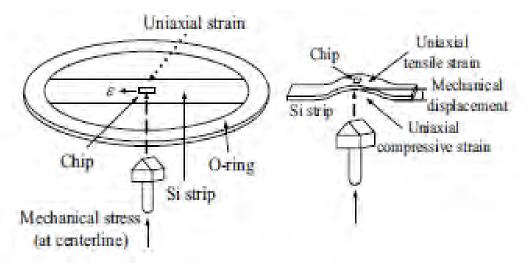

| Figure 2.13                                                                                    | The schematc diagram of externally applied uniaxial package strain                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 21                               |

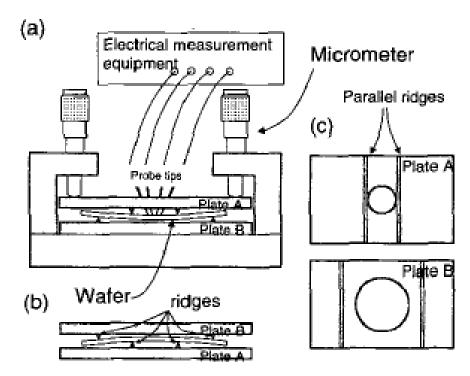

| Figure 2.14                                                                                    | The schematic diagram of bending apparatus to introduce uniaxial strain                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 22                               |

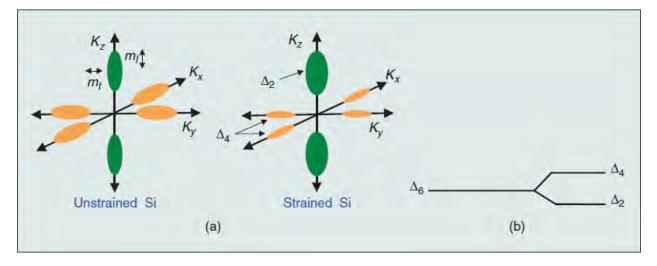

| Figure 2.15                                                                                    | (a) Ellipsoids of constant electron energy in reciprocal ("k") space, each correspondingto one of the degenerate conduction band valleys. For this case, the four orange-colored valleysare in the plane of the Si and the two greencolored valleys are out of the plane (b) Energy levelat the bottom of the six conduction band valleys. Application of advantageous strain splits the energy level as shown, removing the degeneracy (i.e., the equivalence in energy) between the $\Delta_2$ and $\Delta_4$ valleys. | 23                               |

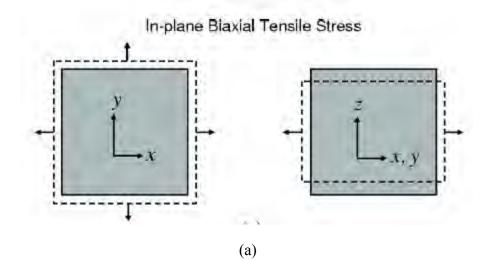

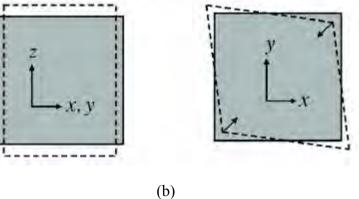

| Figure 2.16                                                                                    | (a) Cubic crystals under in-plane biaxial tensile stress. Under thistype of stress, the <i>x</i> -yplane is still a square, but the <i>x</i> , <i>y</i> - <i>z</i> plane becomes arectangle.<br>(b) Cubic crystals under uniaxial<110> compressive stress. Underthis type of stress, the <i>x</i> - <i>y</i> plane becomes a rhombus, and the <i>x</i> , <i>y</i> - <i>z</i> planebecomes a rectangle                                                                                                                    | 24                               |

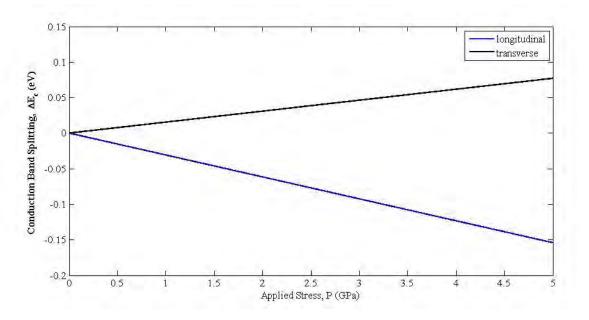

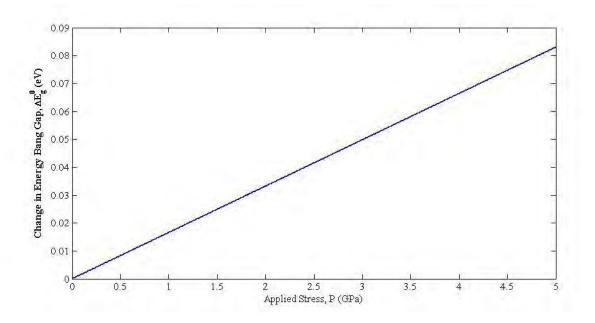

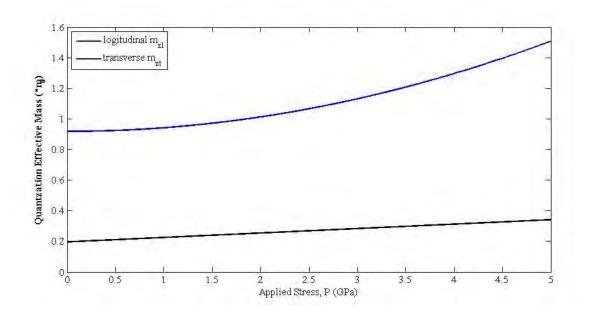

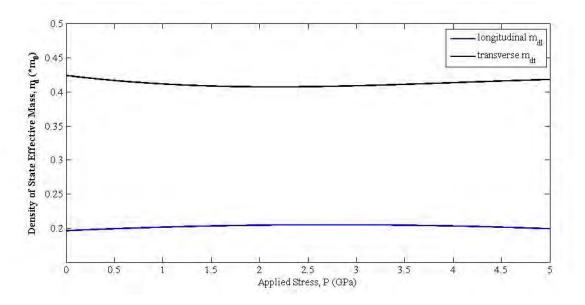

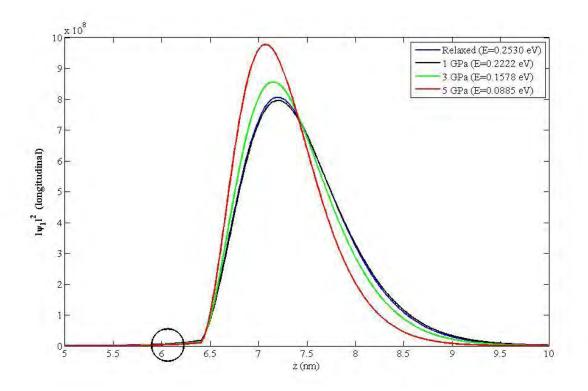

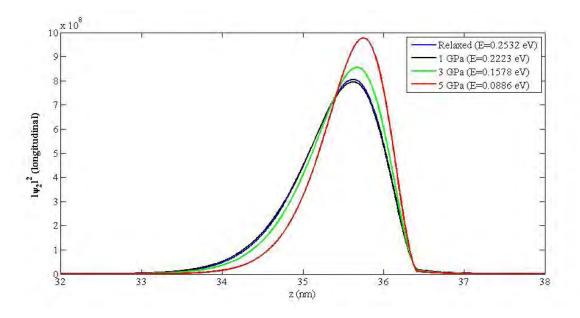

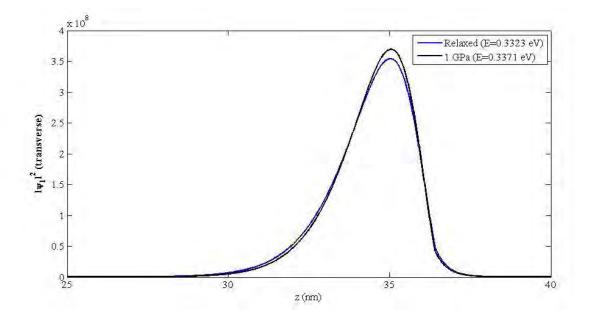

| Figure 2.17<br>Figure 2.18<br>Figure 2.19<br>Figure 2.20<br>Figure 3.1<br>Figure 3.2           | Band splitting in conduction valleys<br>Change in Energy band gap<br>Changes in quantization effective masses<br>Changes in density of state effective masses<br>Normalized Wave function for 1 <sup>st</sup> eigen energy of longitudinal valleys (HfO <sub>2</sub> )<br>Normalized wave function for 2 <sup>nd</sup> eigen energy of longitudinal valley (HfO <sub>2</sub> )                                                                                                                                           | 26<br>27<br>28<br>28<br>33<br>34 |

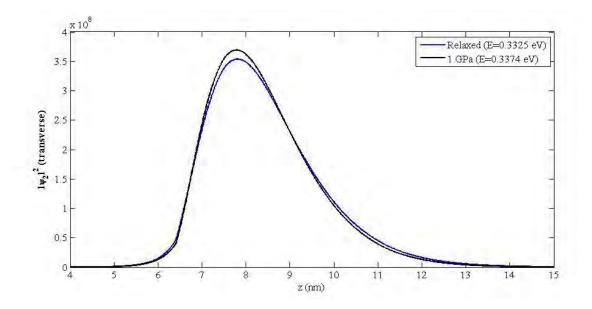

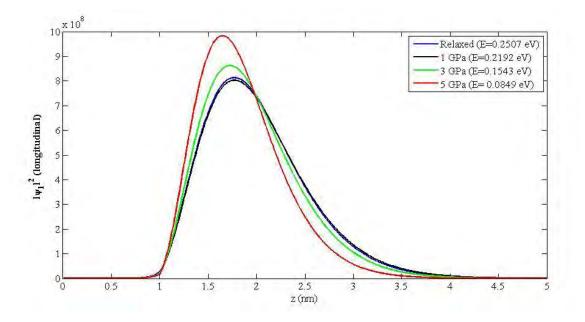

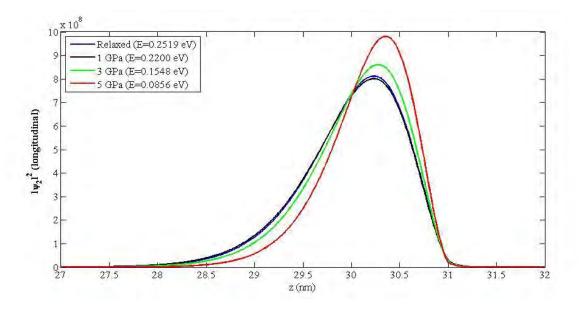

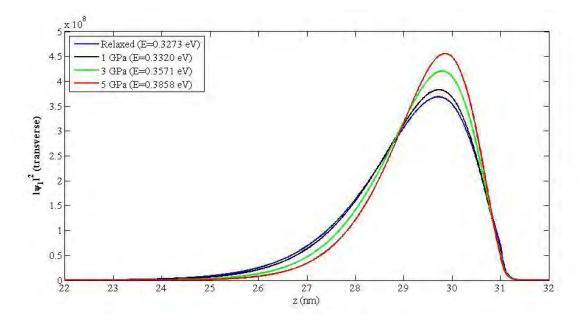

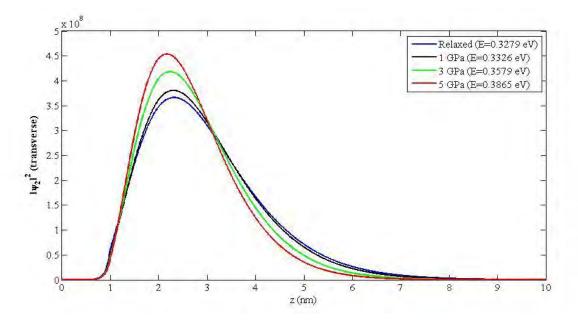

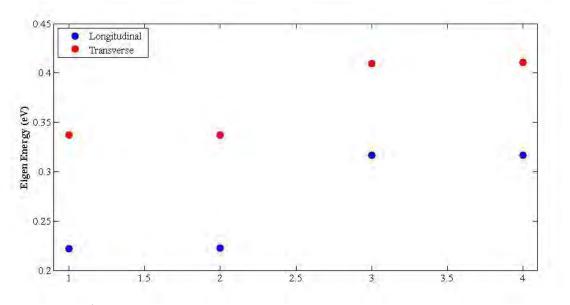

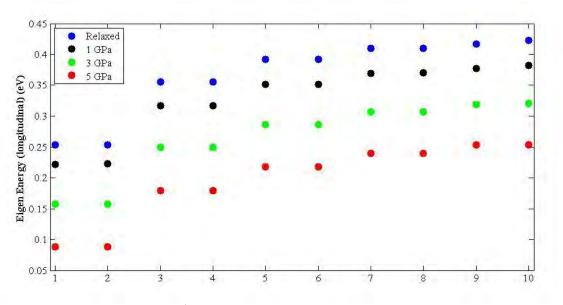

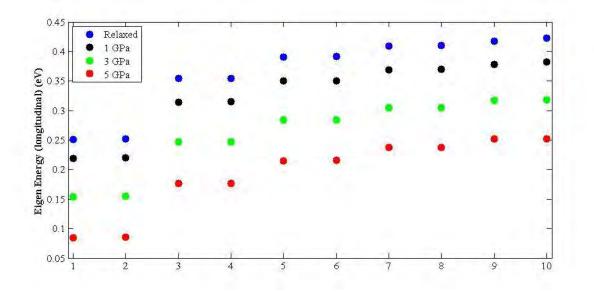

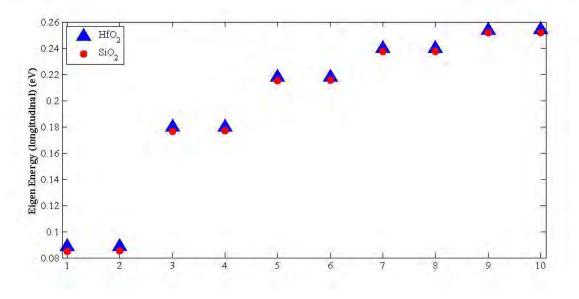

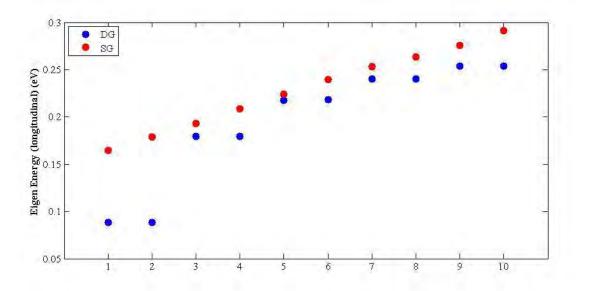

| Figure 3.3<br>Figure 3.4<br>Figure 3.5<br>Figure 3.6<br>Figure 3.7<br>Figure 3.8<br>Figure 3.9<br>Figure 3.10<br>Figure 3.11<br>Figure 3.12<br>Figure 3.13 | Normalized wave function for 1 <sup>st</sup> eigen energy of transverse valley (HfO <sub>2</sub> )<br>Normalized wave function for 2 <sup>nd</sup> eigen energy of longitudinal valleys (SiO <sub>2</sub> )<br>Normalized Wave function for 1 <sup>st</sup> eigen energy of longitudinal valleys (SiO <sub>2</sub> )<br>Normalized wave function for 2 <sup>nd</sup> eigen energy of longitudinal valley (SiO <sub>2</sub> )<br>Normalized wave function for 1 <sup>st</sup> eigen energy of transverse valley (SiO <sub>2</sub> )<br>Normalized wave function for 2 <sup>nd</sup> eigen energy of transverse valley (SiO <sub>2</sub> )<br>Normalized wave function for 2 <sup>nd</sup> eigen energy of transverse valley (SiO <sub>2</sub> )<br>1 <sup>st</sup> four eigen energies of longitudinal and transverse valleys (HfO <sub>2</sub> , 1 GPa)<br>1 <sup>st</sup> ten eigen energies for various strain (HfO <sub>2</sub> )<br>1 <sup>st</sup> ten eigen energies for various strain (SiO <sub>2</sub> )<br>1 <sup>st</sup> ten eigen energies both for HfO <sub>2</sub> and SiO <sub>2</sub> as dielectrics (P= 5GPa)<br>The eigen energies for SG and DG MOSFET with HfO <sub>2</sub> as dielectric (P=<br>5GPa) | 34<br>35<br>36<br>36<br>37<br>37<br>38<br>38<br>39<br>39 |

|------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------|

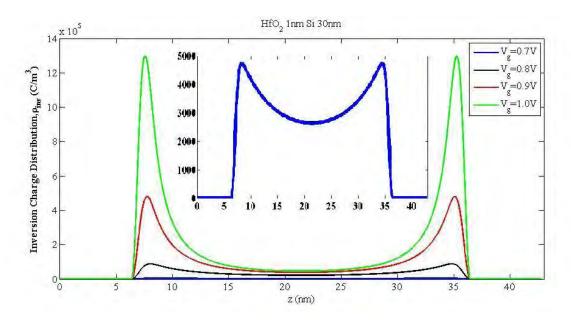

| Figure 4.1                                                                                                                                                 | Inversion charge distribution for various gate voltages (HfO <sub>2</sub> )                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 41                                                       |

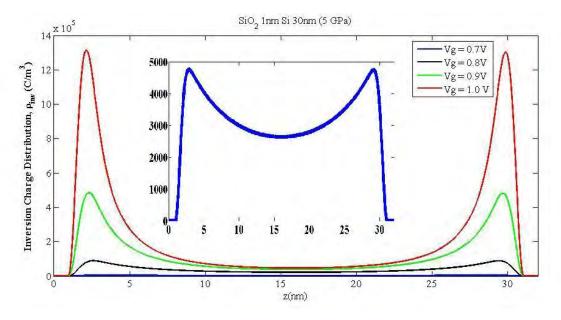

| Figure 4.2                                                                                                                                                 | Inversion charge distribution for various gate voltages (SiO <sub>2</sub> )                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 41                                                       |

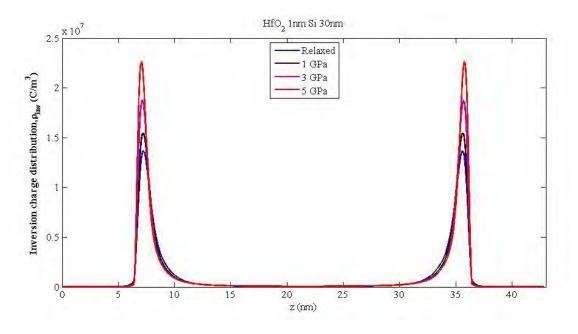

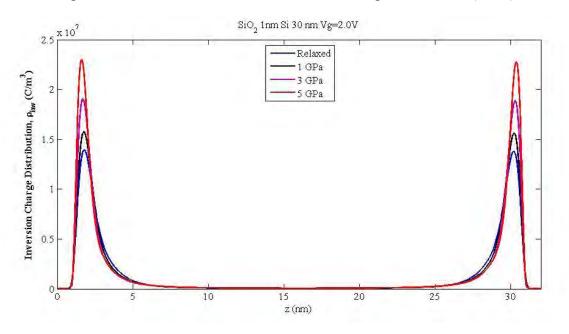

| Figure 4.3                                                                                                                                                 | The effects of strain on inversion charge distribution $(HfO_2)$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 42                                                       |

| Figure 4.4                                                                                                                                                 | The effects of strain on inversion charge distribution (SiO <sub>2</sub> )                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 42                                                       |

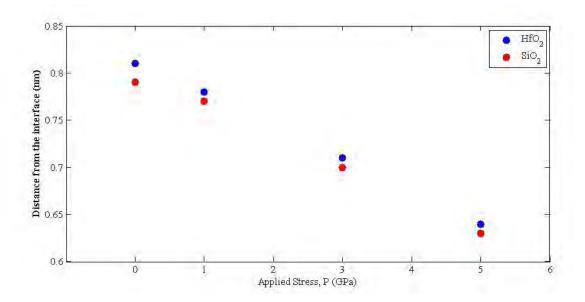

| Figure 4.5                                                                                                                                                 | The distance from the interface of the peak position of inversion charge distribution                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 43                                                       |

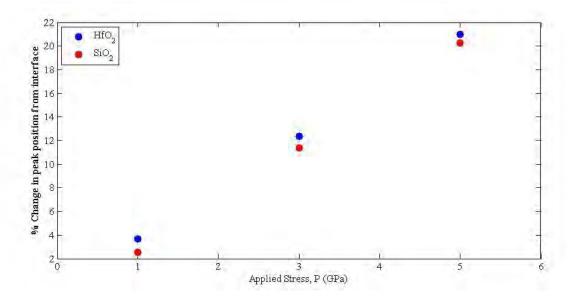

| Figure 4.6                                                                                                                                                 | Percentage change of the distances with respect to the relaxed condition                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 43                                                       |

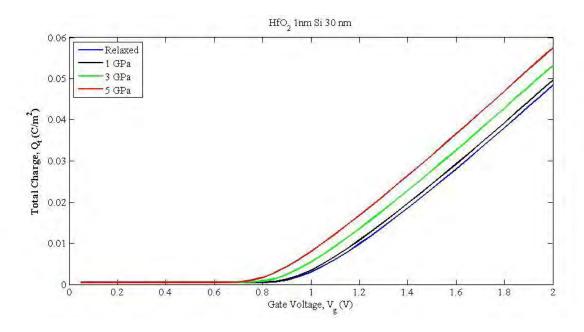

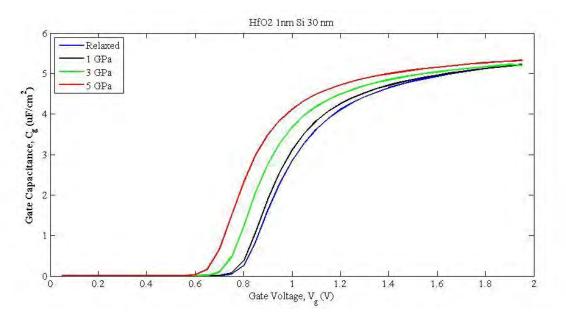

| Figure 4.7                                                                                                                                                 | Increase of total charge with applied stress (HfO <sub>2</sub> )                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 44                                                       |

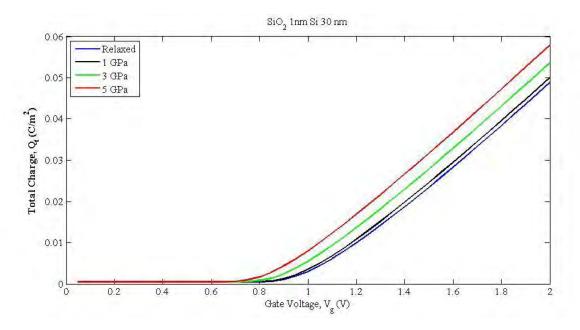

| Figure 4.8                                                                                                                                                 | Increase of total charge with applied stress (SiO <sub>2</sub> )                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 44                                                       |

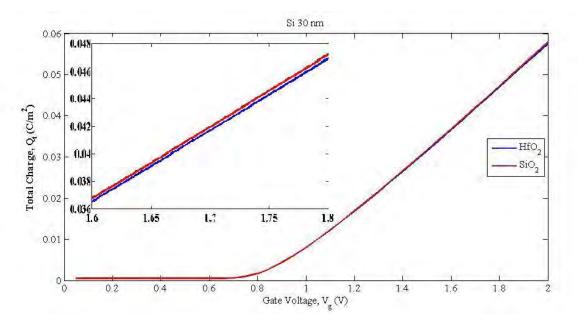

| Figure 4.9                                                                                                                                                 | Comparison of total charges of HfO <sub>2</sub> and SiO <sub>2</sub> at 5 GPa                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 45                                                       |

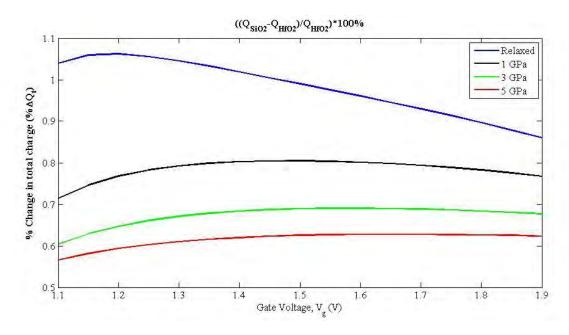

| Figure 4.10                                                                                                                                                | Percentage change in total charge for various stresses                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 45                                                       |

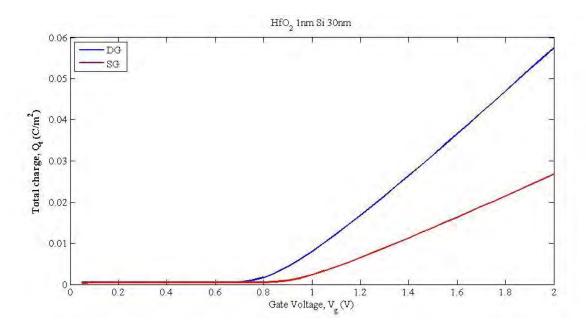

| Figure 4.11                                                                                                                                                | Total charge of DG and SG MOS at 5 GPa                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 46                                                       |

| Figure 4.12                                                                                                                                                | The percentage change between the DG and SG MOS with respect to the DG MOS                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 46                                                       |

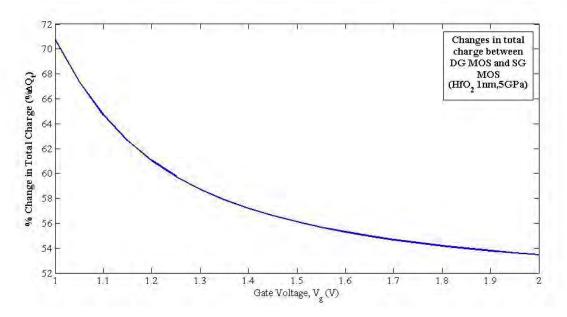

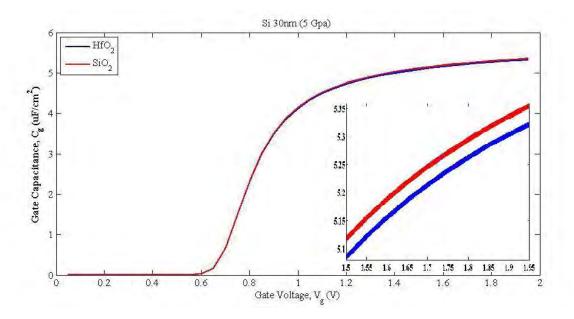

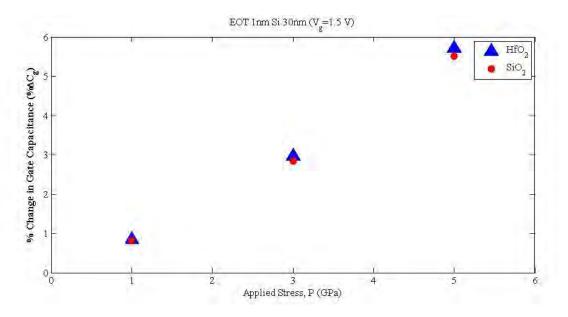

| Figure 4.13                                                                                                                                                | The variation of gate capacitances with applied stress $(HfO_2)$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 47                                                       |

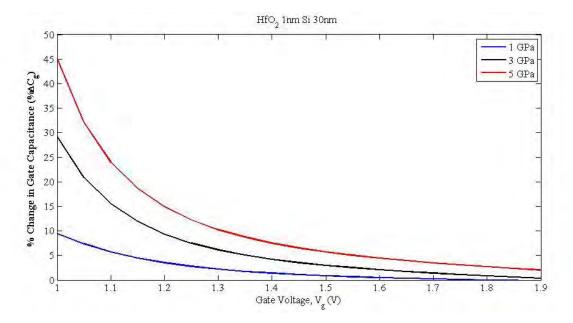

| Figure 4.14                                                                                                                                                | The percentage change in Gate Capacitances (HfO <sub>2</sub> )                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 47                                                       |

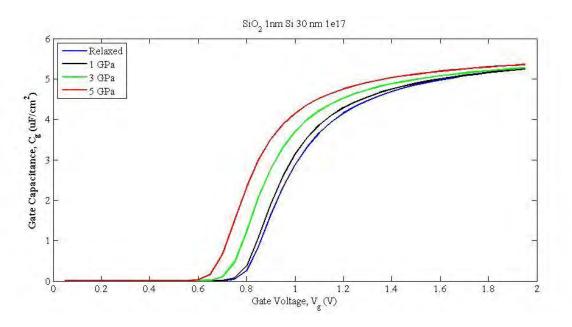

| Figure 4.15                                                                                                                                                | The variation of gate capacitances with applied stress (SiO <sub>2</sub> )                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 48                                                       |

| Figure 4.16                                                                                                                                                | The percentage change in Gate Capacitances (SiO <sub>2</sub> )                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 48                                                       |

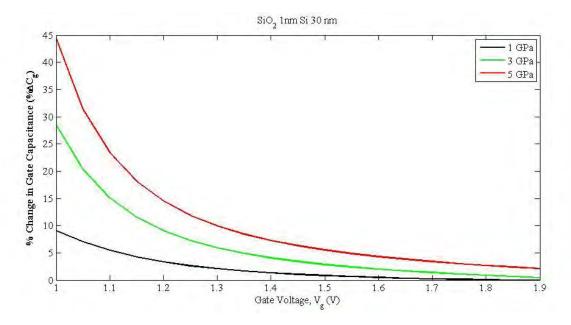

| Figure 4.17                                                                                                                                                | The comparison of gate capacitances between $HfO_2$ and $SiO_2$ at 5GPa                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 49                                                       |

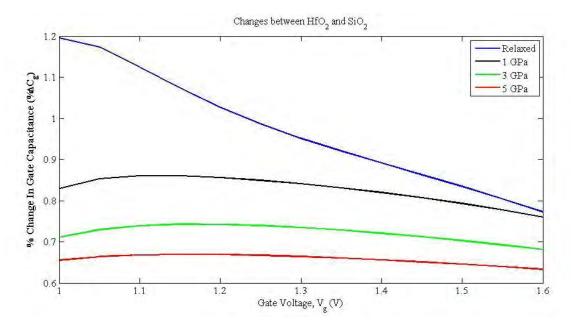

| Figure4.18                                                                                                                                                 | The percentage change in gate capacitances at various gate voltages                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 49                                                       |

| Figure 4.19                                                                                                                                                | The percentage change in gate capacitances at various stresses                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 50                                                       |

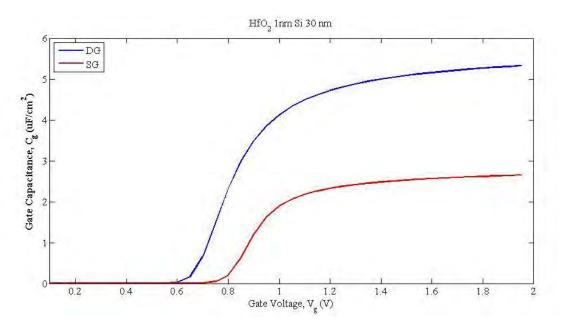

| Figure 4.20                                                                                                                                                | The comparison of gate voltages between DG and SG MOSFET at 5 GPa                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 50                                                       |

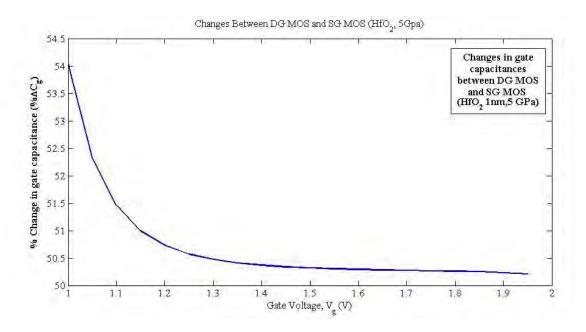

| Figure 4.21                                                                                                                                                | The percentage change of gate capacitance in SG MOS with respect to DG MOS                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 51                                                       |

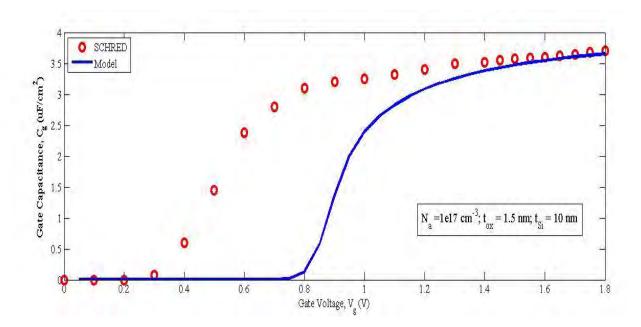

| Figure 4.22                                                                                                                                                | The comparison with SCHRED-predicted total Gate Capacitance                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 51                                                       |

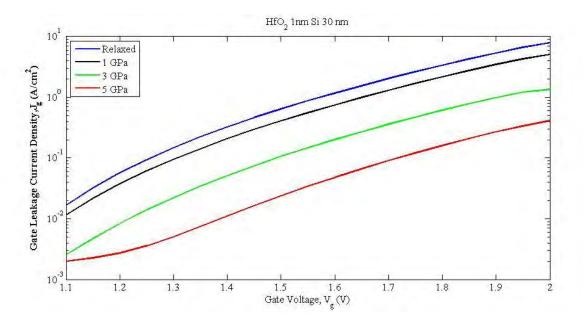

| Figure 4.23                                                                                                                                                | Gate leakage current density at various stresses (HfO <sub>2</sub> )                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 52                                                       |

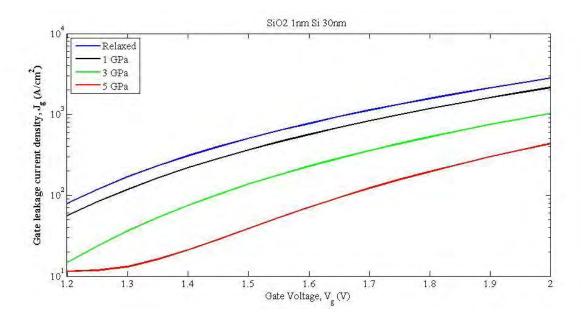

| Figure 4.24                                                                                                                                                | Gate leakage current density at various stresses (SiO <sub>2</sub> )                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 53                                                       |

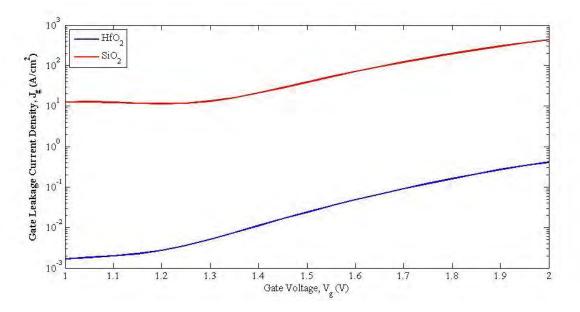

| Figure 4.25                                                                                                                                                | Comparison of Gate leakage Current density between HfO <sub>2</sub> and SiO <sub>2</sub>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 53                                                       |

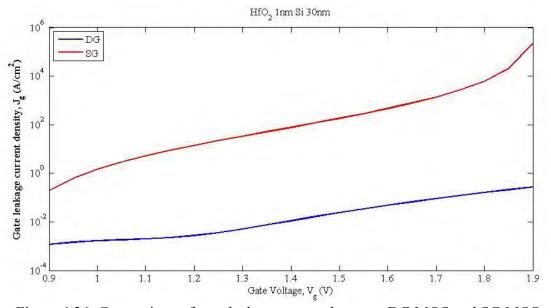

| Figure 4.26                                                                                                                                                | Comparison of gate leakage current between DG MOS and SG MOS                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 54                                                       |

|                                                                                                                                                            |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |                                                          |

# Chapter 1 Introduction

#### **1.1 Mobility Scaling**

In 1947 the bipolar transistor had been invented and the semiconductor industry grew rapidly. In 1958 the concept of an integrated circuit (IC) was invented by J. Kilby and the geometric scaling had been introduced to reduce the cost-per-function with enhanced performance. Aggressive geometric scaling has been accomplished as guided by the ITRS (International Technology Roadmap for Semiconductors) [1].

Geometric scaling is done by reducing the gate length  $L_g$  which introduces several Short Channel Effects (SCE) such as increased off-state leakage current, threshold voltage roll-off and Drain Induced Barrier Lowering (DIBL). To suppress SCE, gate oxide thickness ( $t_{ox}$ ), channel depletion width ( $x_d$ ) and source/drain junction depth ( $x_j$ ) should be scaled down with  $L_g$ . But thin gate oxide increases band-to-band tunneling and thus increases gate leakage current.

To scale down the depletion width, increased channel doping concentration is necessary which reduces the off-state leakage current. But the high channel dopingconcentration degrades carrier mobility, increases band-to-band tunneling across the reverse-biased drain junction and gate-induced drain leakage (GIDL). Shallow source/drain junctions decrease the capacitive coupling of the source/drain to the channel and degrade on-state drive current by increasing parasitic series resistance.

Therefore, the geometric scaling should be replaced with a new scaling vector and this is the mobility scaling [2-4]. Strained-Si technology has been widely used to improve mobility and thus increasing the on-state current without increasing the off-state current [5-11]. Many works incorporated biaxial strain [12-13] but uniaxial strain results in highest drive current enhancement and smaller stress-induced n-channel MOSFET threshold voltage shift. The process induced uniaxial stress offers largeperformance improvement at low cost and minimally

increased manufacturing complexity and is scalable to future technology nodes [14]. Process induced strain can be incorporated by using silicon nitride cap, silicide, and SiGe source/drain. Strain enhances the mobility by splitting the conduction band edge (lowering the longitudinal valleys and increasing the transverse valleys of Si).

#### **1.2 Multiple Gate Devices**

To fulfill the ITRS requirements, multiple gate devices are promising architectures for their improved electrostatic control of the channel. The dominant leakage path for off-state leakage current is located far from the gate, which is least effectively controlled by the gate. Therefore, advanced SOI MOSFETs and Double-Gate MOSFET can suppress the leakage current by eliminating the part of the channel that is not effectively modulated by the gate. SOI MOSFET requires thinner body than DG MOSFET because its body is controlled by one gate, on the other hand the DG MOSFET controls the body with two gates therefore it can use thicker body.

In addition, the DG device does not require high channel doping which eliminates mobility degradation and statistical dopant fluctuation. DG MOSFET has higher transconductance and hence high current driving ability [15]. The drain-induced barrier lowering is also minimized by the shielding effect of the double gate [16]. The lightly doped DG MOS reduces gate leakage current. It can be reduced further if high-k dielectric material is used which will also helpful for scaling down the oxide thickness. Among the high-k dielectrics being studied, HfO<sub>2</sub> appears promising due to its relatively high dielectric constant (25) as compared to Si<sub>3</sub>N<sub>4</sub> (7.5) and Al<sub>2</sub>O<sub>3</sub>(9.1) [17] and its relatively large band gap (5.8 eV) as compared to TiO<sub>2</sub> (3.03 eV) and Ta<sub>2</sub>O<sub>5</sub> (4 eV) [18].

#### **1.3 Literature review**

In 1984 the concept of double-gate SOI MOSFET known as XMOS was invented [19] depicting good short channel characteristics. Since then to model Double-Gate MOSFET, various types of approaches have been used. R. F. Pierret et al. uses two-dimensional device simulations and one dimensional analytical computation to analyze the dual-gate operation in the strong inversion region [20]. K. Suzuki et al. developed a model for short channel  $n^+-p^+$  double gate SOI MOSFET by solving a 2D Poisson's equation [21]. Y. Taur has derived a 1D analytical solution for an undoped or lightly doped DG MOSFET by incorporating only the mobile charge [22].

The complete carrier based non charge sheet analytical model is based on the Poisson's equation to solve for the carrier concentration directly rather than relying on the surface potential alone [23]. This model covers all three regions of CV characteristics and it does not depend on any fitting parameter, auxiliary functions or variables. The mobile carrier concentration is calculated from Boltzmann statistics for the Poisson's equation. The electric field in the center of the Si film has been assumed to be zero and then an exact closed-form expression for the carrier concentration-electron concentration at the center of the channel Si has been derived as a function of gate voltage, channel voltage and Si film. SCE are incorporated in 2D Poisson's equation and to calculate the capacitance, the spatial distribution of the carrier charge across the MOSFET channel is found considering the drain current continuity characteristics.

In explicit continuous model, implicit equations for intermediate parameters by numerical iteration or the table lookup method are solved to avoid computational inefficiency and sporadic exceptions [24]. This model is continuous through the all operation regions, i.e., linear, saturation and subthreshold without using charge sheet approximation and ad hoc fitting parameters. Here, at first the Poisson's equation is solved under the gradual channel approximation. The solution is an implicit equation which is solved using the following general method:

- (1) Compose a continuous starting function as the initial approximation.

- (2) Modify the starting function with high-order correction.

- (3) Make another correction to improve accuracy.

In this way an accurate explicit model DG MOSFET has been derived.

In [25] an analytical solution of gate capacitance for DG and FD/SOI MOSFETs has been derived. To incorporate the symmetric nature, the front and back gates are tied together. The expression of the surface potential referenced to the hypothetical neutral body is obtained by integrating the Poisson's equation. This expression is used in Gauss's law, where it is related to inversion charge and gate voltage. Then this equation is differentiated to obtain the gate capacitance.

Self-consistent numerical model using fully-coupled 1D Schrodinger's and Poisson's equation is very popular for modeling DG MOSFET [26]. A complete model of DG MOSFET which accurately incorporates the QM effects is very important for future circuit simulators.

#### **1.4 Objective of the thesis**

In this thesis, a 1D coupled Schrodinger–Poisson self-consistent simulator has been developed for symmetric double gate MOSFET with silicon as substrate and silicon dioxide or halfnium oxide as insulator material. Poisson's equation has been solved using Finite Difference Method and Schrodinger's equation has been solved using the Hamiltonian Matrix Formalism. As wavefunction penetration into the gate dielectric plays an importantrole in the state-of-the-art nanoscale devices, effect of wave function penetration into the front gate and back gate has been incorporated in the simulator. The accurate value of Quasi Fermi level has been calculated. The effect of uniaxial strain has been incorporated in the simulator by changing the value of effective masses. Due to uniaxial strain the conduction band goes up for transverse valleys and goes down for longitudinal valleys of silicon. These changes have been included. Once the electrostatics of the devices is calculated at different gate voltages, gate capacitance – gate voltage characteristics can be modeled. Transmission coefficients of electrons will be calculated which depends on height and barrier of the potential barrier. Then tunneling lifetime obtained from eigen energies and transmission probability of electrons is multiplied with charge density to calculate the gate tunneling current. Summation of the current components over each carrier subband and valley yields the total gate current.

#### **1.5 Organization of the thesis**

In chapter two the structure and device physics of Double-Gate MOSFET will be discussed. Then the advantages of high-k DG MOS will be presented. Also the necessary theories to include strain effect on band structure and effective mass will be explained from literature.

In chapter three, the method to solve gate capacitance and gate leakage current by the coupled Poisson's equation and the Schrodinger's equation will be discussed. Then the fully coupled 1D Schrodinger and Poisson's equation will be presented for the purpose of simulation.

In chapter four, results obtained from the simulation will be given and the comparisons between different level of applied stress, between  $HfO_2$  and  $SiO_2$  and between the DG MOS and SG MOS will be presented.

# Chapter 2 Double Gate MOSFET

The double-gate MOSFET can be scaled promisinglydue to its inherent robustness to shortchannel effects, high current driving capability and the 60 mV/decade slope of the turn-on characteristic at room temperature [16]. Although the manufacturability of DG MOSFET is still challenging, this extremely interesting device concept is very advantageous for semiconductor device industry.

#### 2.1 Device Structure and physics

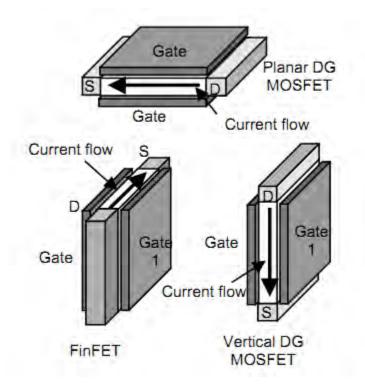

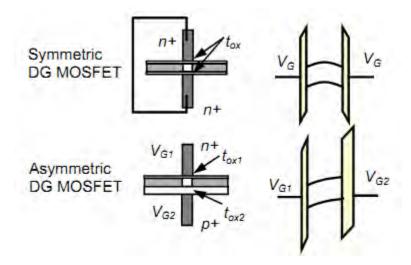

As a result of different fabrication processes, DG MOSFETs can be grouped into

- i. Planer DG MOSFET

- ii. FinFET

- iii. Vertical DG MOSFET.

Figure 2.1: Different structure of DG MOSFET [28]

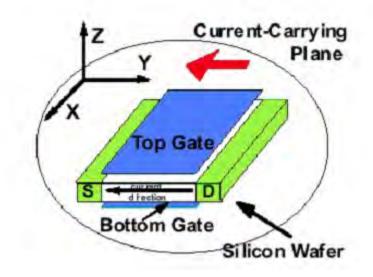

The first type of structure is close to the planar MOSFET in geometry except that it has a bottom gate. An advantage of this topology is the good control of the silicon channel thickness but the fabrication of the self-aligned bottom gate in this structure has been very challenging and the another problem is that the gate length must be controlled by lithography.

Figure 2.2: Planar Device Structure

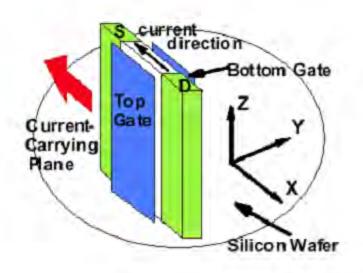

The current flows parallel to the wafer in the second type of structure. However, the Si/SiO2 interface is formed on the sidewalls of an etched silicon fin. Both the gate length and the channel thickness are defined by the lithography in this structure. Also, the width of the transistor is fixed by the fin height, and thus multiple fins have to be used to obtain higher drive current.

Figure 2.3: FinFET Structure

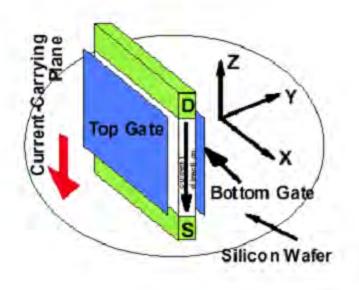

In the third type of device structure, the current flow is perpendicular to the wafer and the gate lengthis defined by non-lithographic methods such as a timed etch or a thin filmdeposition. Gate length is decoupled from the packing density but the fullydepletedoperation is challenging since the silicon channel thicknesshas to be defined by lithography.

Figure 2.4: Vertical Device Structure

The operation modes of DG MOSFET can be classified into symmetric DG (SDG) MOSFET and Asymmetric DG (ADG) MOSFET. The both gates of symmetric type has identical work functions so that the two surface channels turn on at the same gate voltage and the asymmetric type has different work functions for the gates and only one channel turns on at the threshold voltage.

Figure 2.5: The two operation modes for DG MOSFETs [28]

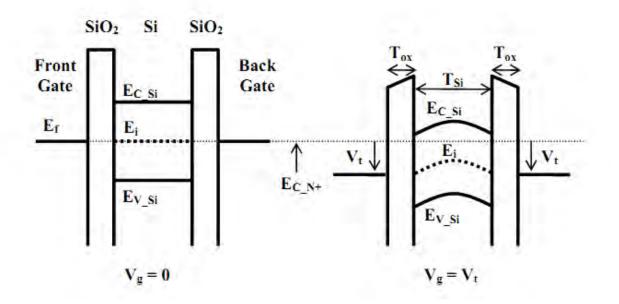

TheSDG device shows higher carrier mobility due to its lower transverseelectric field as compared to the ADG device. Figure 2.6 shows the energy band diagram along the vertical direction (across the front and back gates) of the SDG structure. It describes how conductive channels are formed for the lightly doped n-channel SDG MOSFETs.

Figure 2.6: Symmetric DG MOSFET [4]

Here,  $E_f$  is the fermi level,  $E_i$  is the intrinsic Fermi level,  $E_{C_si}$  is the conduction band of the silicon body and  $E_{C_si}$  is the conduction band edge of the N+source/drain. The same voltage is applied to the two gates having the same work function. At zero gate voltage, the position of the silicon bands is largely determined by the gate work function, because as long as the thin silicon is lightly doped and the depletion charge is negligible, the bands remain essentially flat throughout the thickness of the film. Since there is no contact to the silicon body, the energy levels are referenced to the electron quasi-Fermi level or the conduction band of the n<sup>+</sup> source-drain (not shown), represented by the long dotted line in Fig. 2.6. As the gate voltage increases toward the threshold voltage, mobile charge or electron density becomes appreciable when the conduction band of the silicon body moves to near the conduction band of the source-drain.Since the work functions of two gates are identical, the conduction bands in bothsurfaces (under the front and back gates) are bent by the exactly same amount. As a result, at on-state, two conductive channels are formed for the SDG device, unless the siliconbody thickness is not very

thin (e.g., <5nm). In that case, as the gate voltage approaches V<sub>t</sub>, the bands of the whole silicon body including the center follow Vg, thus volume inversion takes place [27].

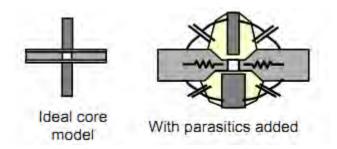

To account for process varieties, a DG MOSFET can be decomposed into an intrinsic core part together with a number of parasitic components as shown in Figure 2.7. The core part of the DG MOSFET remains more or less the same for different processes and can be accurately described by the device physics. The parasitic part, however, is strongly structural dependent and more empirical approach has to be used to include their effects. This allows the initial modeling work to focus on the core structure. A modular approach allows the empirical part to be replaced by a physical formulation once the more definite device structure becomes available [28].

Figure 2.7: Decomposition of a DG MOSFET into the ideal core and the parasitic components [28]

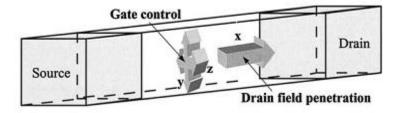

#### 2.2 Short Channel Effects (SCE)

The short-channel effects are attributed to two physical phenomena:

- 1. Thelimitation imposed on electron drift characteristics in the channel,

- 2. The modification of the threshold voltage due to the shortening channel length.

In particular five different short-channel effects can be distinguished:

- 1. Drain-induced barrier lowering

- 2. Surface scattering

- 3. Velocity saturation

- 4. Increased off-state leakage current

- 5. Threshold voltage roll-off

Subthreshold swing degradation and other short-channel effects are caused by the encroachment of electric field line from the drain on the channel region, thereby competing for the available depletion charge, and reducing the threshold voltage. In small-geometry MOSFETs, the potential barrier is controlled by both thegate-to-source voltage and the drain-to-source voltage. If the drain voltage is increased, thepotential barrier in the channel decreases, leading to drain-induced barrier lowering (DIBL). The reduction of the potential barrier eventually allows electron flow between the source and the drain, even if the gate-to-source voltage is lower than the threshold voltage. The channel current that flows under these conditions called the sub-threshold current. Figure 2.8 shows how the gates and the drain compete for the depletion charge. Gate control is exerted in the yand z directions and competes with the variation of electric field in the xdirection due to the drain voltage.

Figure 2.8: Definition of coordinate system in a multiple-gate device. Gate-induced fields are in the x and z directions. Drain penetration field is in the y direction.