# STUDY OF THRESHOLD VOLTAGE AND SUBTHRESHOLD CURRENT BEHAVIOR OF SILICON-ON-INSULATOR (SOI) MOSFETS

A thesis submitted to the Department of Electrical & Electronic Engineering, BUET, Dhaka in partial fulfillment of the requirements for the degree of Master of Science in Engineering (Electrical & Electronic)

# MOHAMMAD FAIZUL MOMEN

October 1998

. .

# **DEDICATED TO MY PARENTS**

ii

## **APPROVAL**

This thesis titled "Study of threshold voltage and subthreshold current behavior of silicon-on-insulator (SOI) MOSFETs" submitted by Mohammad Faizul Momen, Roll No. 9406209P, session 1993-94-95 to the Department of Electrical & Electronic Engineering, BUET, Dhaka has been accepted as satisfactory for the partial fulfillment of the requirements for the degree of Master of Science in Engineering (Electrical and Electronic).

**Board of Examiners**

#### 1. Dr. A.H.M. Zahirul Alam

Associate Professor Department of EEE BUET, Dhaka-1000.

#### 2. Dr. Enamul Basher

Professor and Head Department of EEE BUET, Dhaka-1000

#### 3. Dr. A.B.M. Harunur Rashid

Assistant Professor Department of EEE BUET, Dhaka-1000

#### 4. Dr. Farruk Ahmed

Professor Department of Applied Physics & Electronics Dhaka University, Dhaka-1000

Chairman 0.98 (Supervisor)

Member (Ex-officio)

Member Hannak 21.10.98

Hhmed 21.10.98 Member (External)

# **DECLARATION**

I hereby declare that this work has not been submitted elsewhere for the award of any degree or diploma.

**Countersigned**

(Dr. A.H.M. Zahirul Alam)

نو ہ

(Mohammad Faizul Momen)

iv

# CONTENTS

| ACKNO   | WLEDG    | EMENT          | S          | •••        |       | •    | •     |       | -     | •          | •    | •   | •  | •  | vii     |

|---------|----------|----------------|------------|------------|-------|------|-------|-------|-------|------------|------|-----|----|----|---------|

| ABSTRA  | CT .     |                |            |            |       |      | •     | • •   | •     |            |      |     |    | •  | viii    |

| LIST OF | FIGUR    | ES             |            | • •        |       | -    | •     | •     | • •   | . <b>-</b> | •    | ٠   |    | •  | ix      |

| LIST OF | PRINC    | IPAL SY        | MBOL       | <i>S</i> . |       |      | •     | •     | •••   | •          | •    | •   |    | •  | xii     |

| CHAPTE  | ER – 1   | INTRO          | DUCTI      | ON         |       |      |       | •     |       | •          | -    |     | •  |    | 1       |

| 1.1     | Prologu  | e              | · • •      |            |       |      | •     | •     |       | •          | •    | •   |    | •  | 1       |

| 1.2     | Limitati | ons of scal    | ling dow   | n the      | SOI   | МС   | )SFJ  | ΞT    |       | •          | •    | -   | •  | •  | 5       |

| 1.3     | Review   | of previou     | ıs works   |            |       | •    | •     | •     | • •   |            | •    |     | •  | •  | 6       |

| 1.4     | Objectiv | ve of the p    | resent stu | udy        | •     | •    |       | •     |       |            |      | ٠   | •  |    | 8       |

| 1.5     | Brief in | troduction     | to this tl | hesis      |       |      | •     |       |       |            | •    | •   |    | •  | 9       |

| CHAPTE  | ER –2    | THEOR<br>VOLTA |            |            |       |      |       |       |       |            |      |     |    |    |         |

|         |          | OF A FU        |            |            |       |      |       |       |       |            |      |     |    |    | 10<br>( |

| 2.1     | Overvie  | w              |            |            |       |      | •     | -     | •••   | •          | •    | ٠   | •  |    | 10      |

| 2.2     | Front su | irface pote    | ntial of a | a SOI      | MO    | SFE  | T     |       |       |            |      |     |    |    | 19      |

| 2.3     | The sho  | ort-channel    | thresho    | ld vol     | tage  | moo  | del f | for a | ın FI | oso        | DI N | ٨O  | SF | ЕŢ | 25      |

| 2.4     | Static c | haracterist    | ic model   | for a      | sub   | micr | on/o  | deep  | o sut | omi        | сго  | n S | OI | M  | OS      |

|         | 2.4.1    | Inversior      | h charge   | per u      | nit a | rea  |       | •     |       | ٠          |      | •   | •  | •  | 29      |

|         | 2.4.2    | Drain cu       | rrent mo   | del .      |       | • •  | •     |       | • •   |            |      | •   |    | •  | 36      |

v

| 2.4.2.1 The effective mobility of electrons in the channel . | 37         |

|--------------------------------------------------------------|------------|

| 2.4.2.2 Weak inversion and subthreshold current model .      | 39         |

| 2.4.2.3 Strong inversion and drain current model for a       |            |

| normally ON SOI MOSFET                                       | 43         |

|                                                              | 10         |

| CHAPTER – 3 RESULTS AND DISCUSSIONS                          | 46         |

| CHAPTER – 4 CONCLUSIONS AND SUGGESTIONS FOR                  |            |

| FUTURE WORK                                                  | 85         |

| 4.1 Conclusions                                              | 85         |

| 4.2 Future works                                             | 88         |

|                                                              | 90         |

| REFERENCES                                                   | <u>8</u> 7 |

.

.

## ACKNOWLEDGEMENTS

I would like to express my heartfelt deep gratitude to my honorable supervisor Dr. A.H.M. Zahirul Alam, Associate Professor of the Department of Electrical & Electronic Engineering, BUET, Dhaka, for his careful and continuous supervision, encouragement and friendly support throughout the completion of this work. I owe him a lot for his valuable advices, proper guidance and constructive suggestions he patiently gave me time to time.

I would like to take the opportunity to express my sheer thanks to Dr. Enamul Basher, Professor and head of the Department of Electrical & Electronic Engineering, BUET, for providing the Departmental facilities.

Finally, I would like to thank my parents and other family members who inspired me for the completion of the M.Sc. Degree; additional thanks go to all my colleagues, specially Mr. Hasanuzzaman and Mr. Hamidur Rahman for their continuous support and encouragement.

## ABSTRACT

A theoretical analysis has been carried out to develop a model of the threshold voltage,  $V_{th}$  for fully depleted silicon-on-insulator (FDSOI) MOSFET with effective channel lengths down to the deep-submicrometer (below 0.25 micron) range. A simple quasi-two-dimensional approach has been used to describe the front surface potential of a SOI MOSFET. Based on the expression for front-surface electric-potential,  $V_{sf}$ , the model of the threshold voltage roll-off,  $\Delta V_{th}$  of the SOI device has been developed and its response to the variation in parameters like silicon-film thickness, channel doping and drain bias (DIBL or Drain Induced Barrier Lowering effect) has been carefully studied.

With a view to producing a complete static-characteristic model of a short channel SOI MOSFET, we developed the expression for the 'free inversion areal charge density,'  $Q_m$ , solving the equation of one-dimensional effective gate-channel capacitance and a quasi-two-dimensional Poisson's equation. Using the appropriate expression of channel charge density,  $Q_m$  for various inversion conditions, separate drain current models have been developed analytically. These models, one for the weak inversion region (i.e. subthreshold current) and the other for the strong inversion region, have been carefully incorporated with the modified expression for effective channel mobility and the phenomenon of velocity overshoot. Also the effects of channel-shortening, channel length modulation and channel doping on the drain current behavior have been studied.

## LIST OF FIGURES

- Fig. 2.1 An n-channel MOS Transistor.

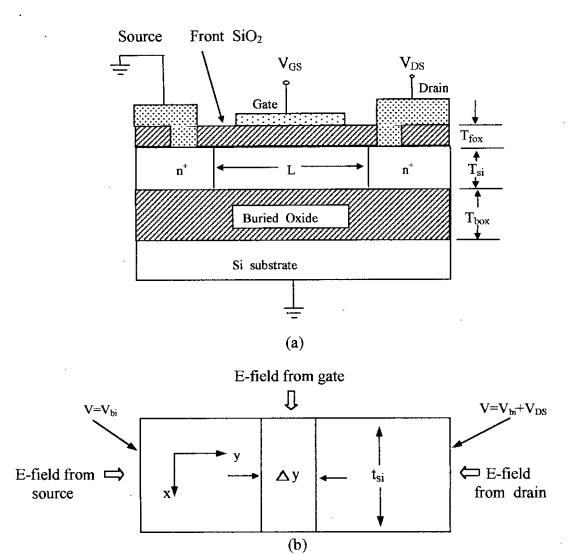

- Fig. 2.2 Cross sectional view of a SOI MOSFET.

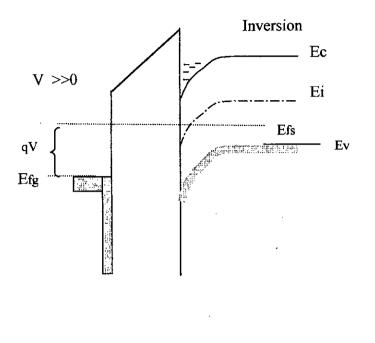

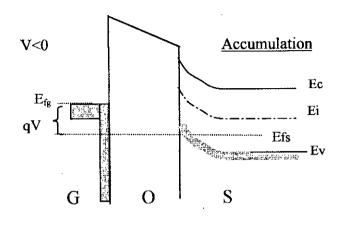

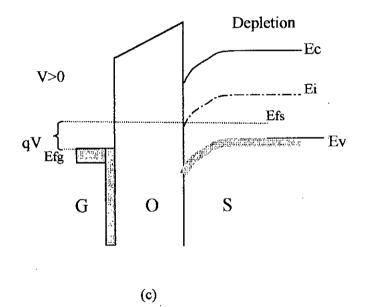

- Fig. 2.3 Effects of applied voltage on the energy band diagram of ideal NMOS capacitor (a) band –diagram at equilibrium, (b) band-diagram for negative gate voltage causing hole accumulation, (c) band-diagram for positive gate voltage causing hole depletion and (d) band-diagram for a larger positive gate voltage causing inversion.

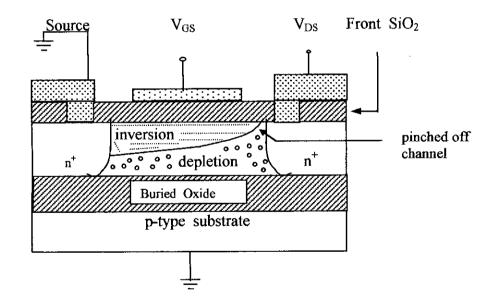

- Fig. 2.4 An n-channel SOI-MOSFET operating in the saturation region.

- Fig. 2.5.a Cross-sectional view of a typical SOI-MOSFET.

- Fig. 2.5.b Gaussian box representation of its channel depletion region with boundary conditions and reference direction.

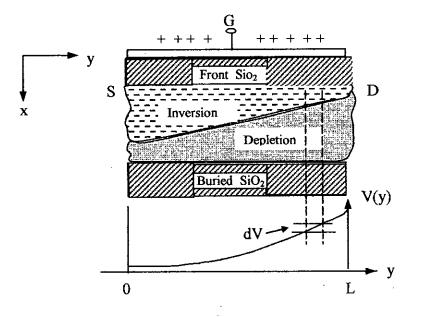

- Fig. 2.6 Schematic view of the n-channel region of a SOI-MOSFET under drain bias and the variation of voltage V(y) along the conducting channel.

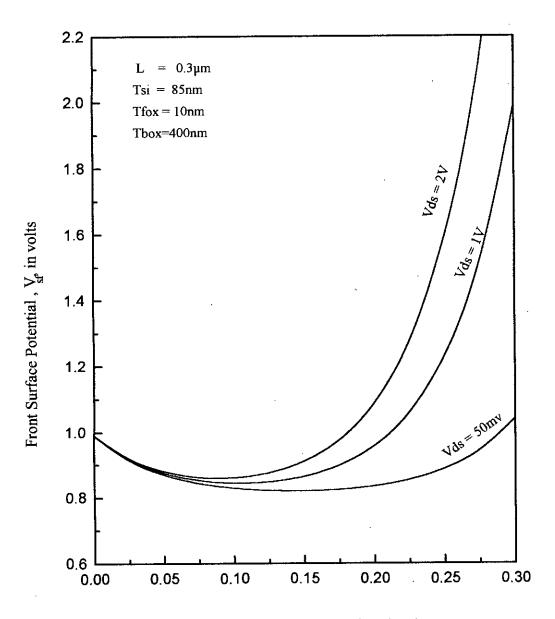

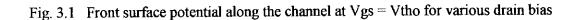

- Fig. 3.1 Front surface potential along the channel at Vgs = Vtho for various drain bias.

- Fig. 3.2 Front surface potential for different channel lengths.

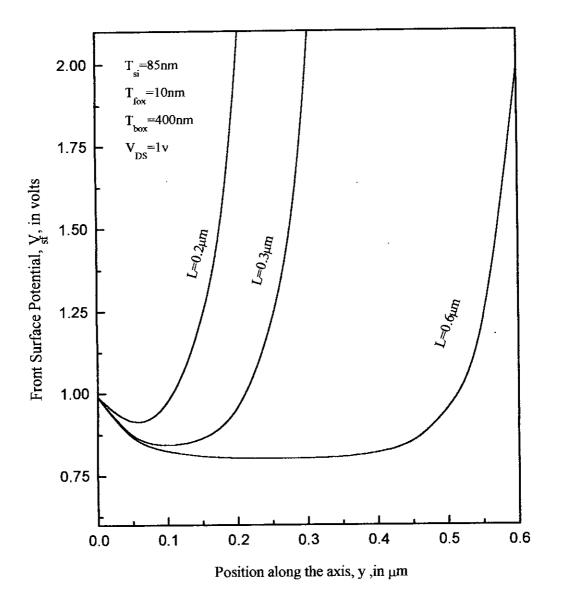

- Fig. 3.3 Definition of channel length modulation.

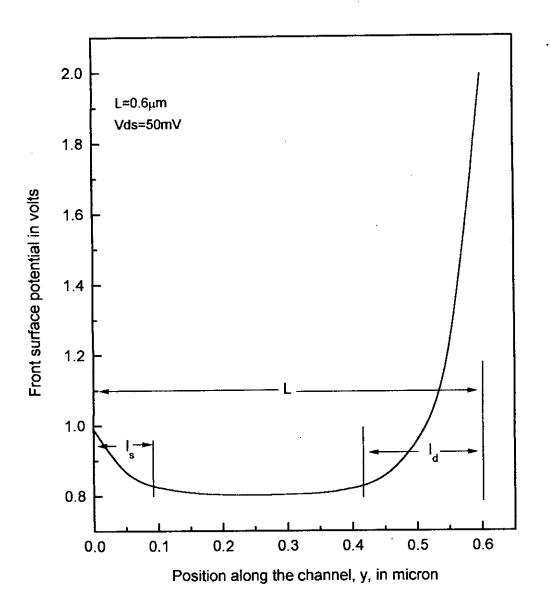

- Fig. 3.4 Effect of channel length modulation on as function of drain voltage.

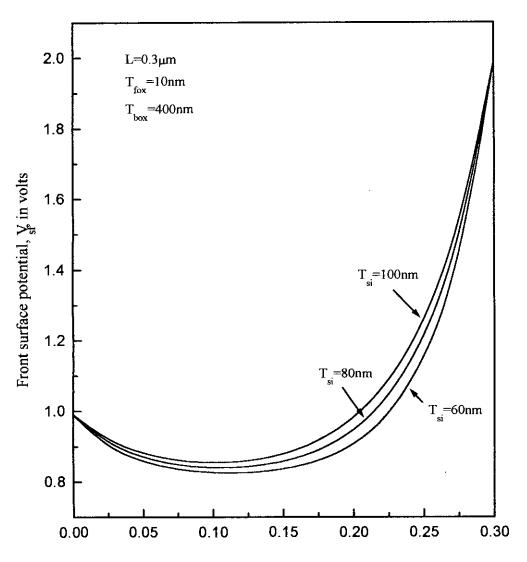

- Fig. 3.5 Front surface potential for different silicon film thickness.

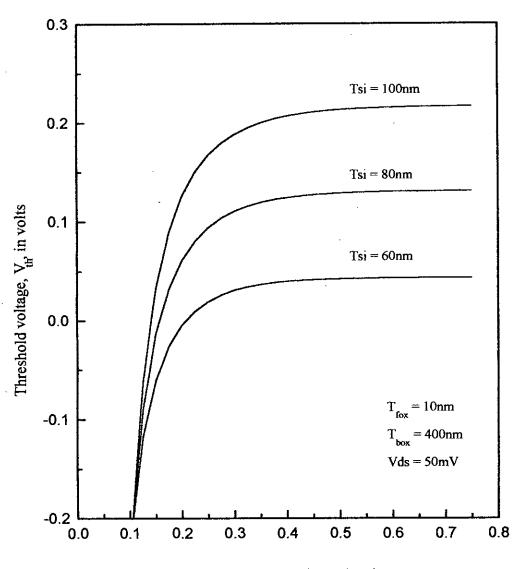

- Fig. 3.6 Threshold voltage vs. channel length for different Si-film thickness.

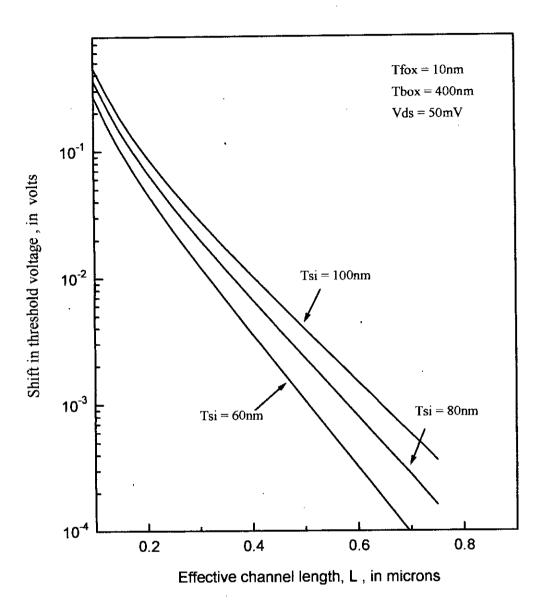

- Fig. 3.7 Shift in threshold voltage vs. channel length for various Si-film thickness.

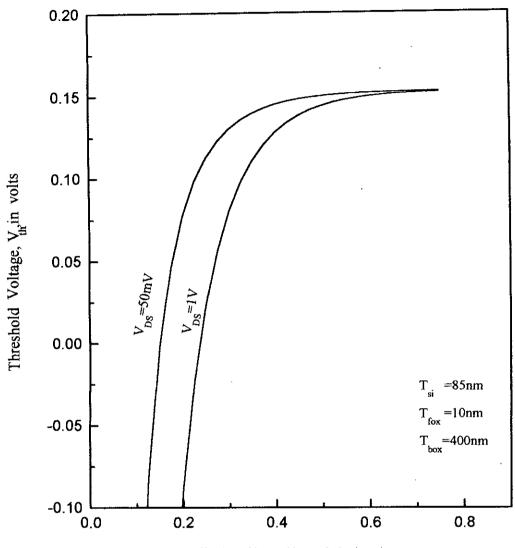

- Fig. 3.8 Threshold Voltage vs. Channel Length for different Drain bias.

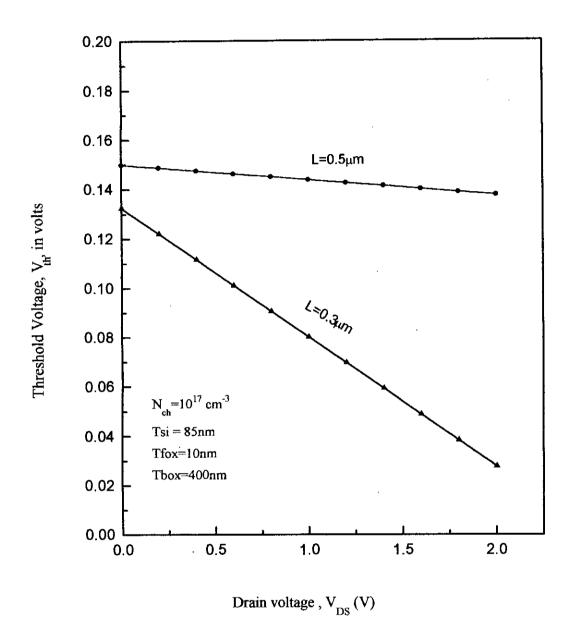

- Fig. 3.9 Dependence of the threshold voltage on the drain voltage for 0.3µm and 0.5µm SOI MOSFETs.

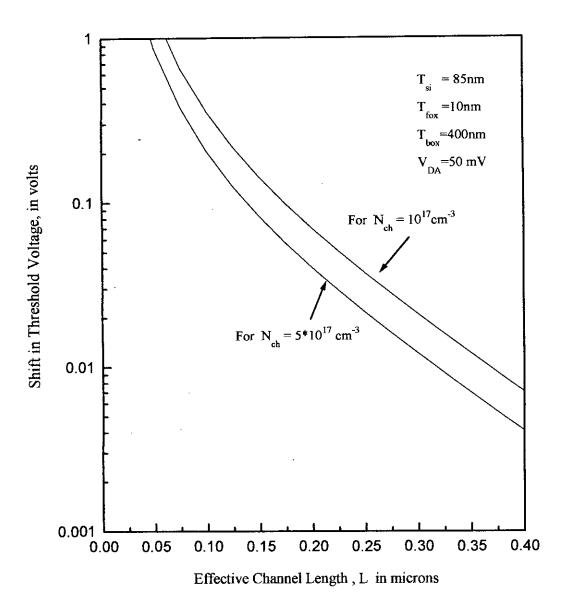

- Fig. 3.10 Shift in Threshold Voltage vs. Channel Length for different channel dopings.

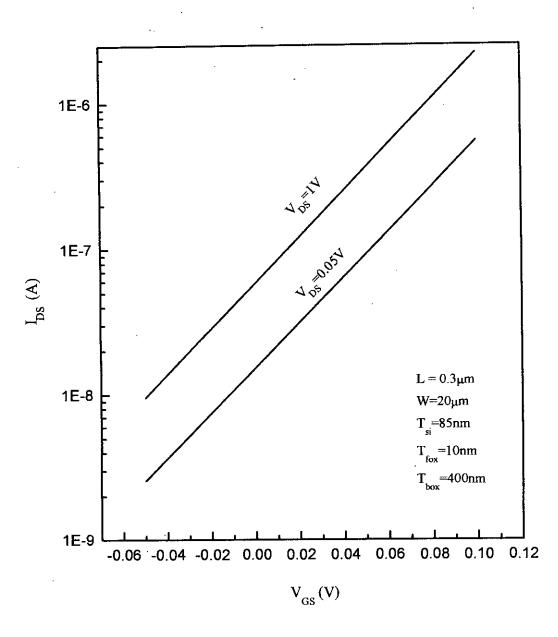

- Fig. 3.11 Subthreshold transfer characteristics of an n-channel SOI MOSFET with  $L=0.3\mu m$ .

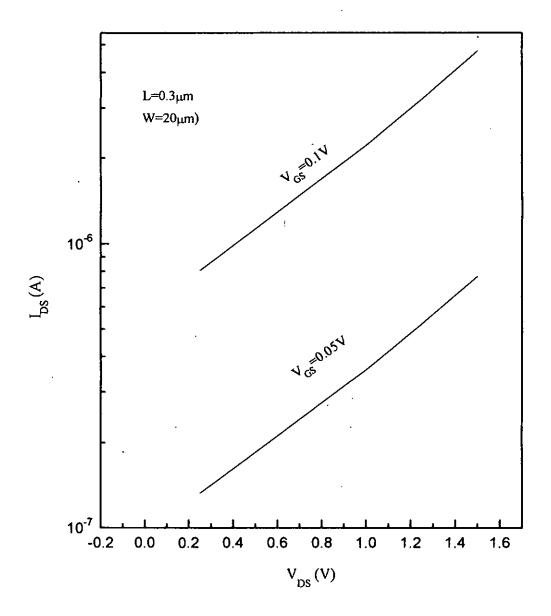

- Fig. 3.12 Subthreshold output characteristics for an n-channel SOI MOSFET with  $L=0.3\mu m$ .

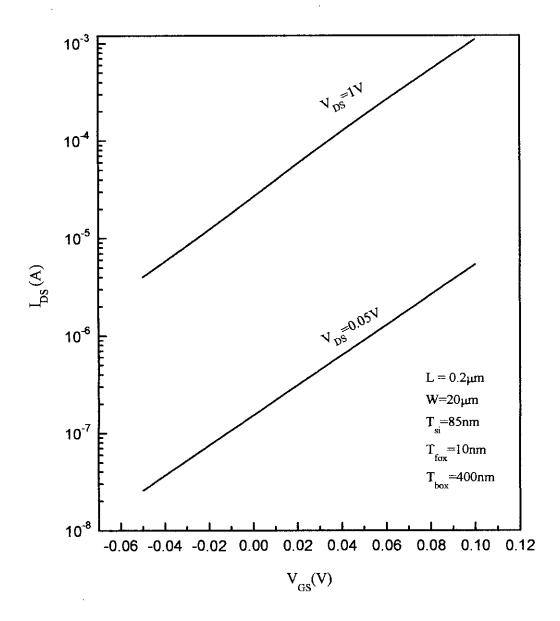

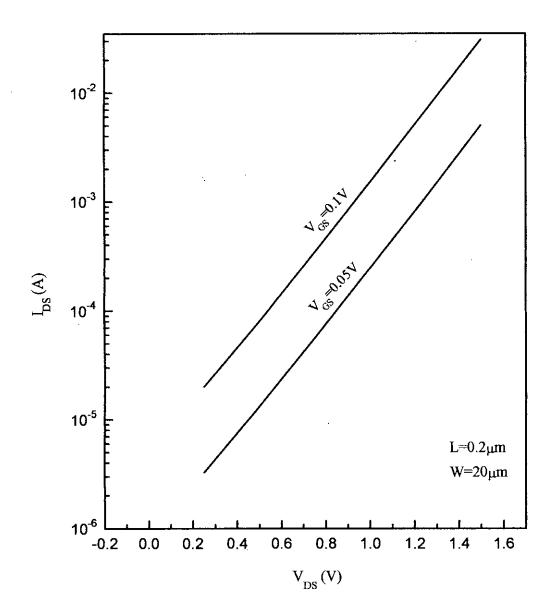

- Fig. 3.13 Subthreshold transfer characteristics of an n-channel SOI MOSFET with L=0.2µm.

- Fig. 3.14 Subthreshold output characteristics of an n-channel SOI MOSFET with  $L=0.2\mu m$ .

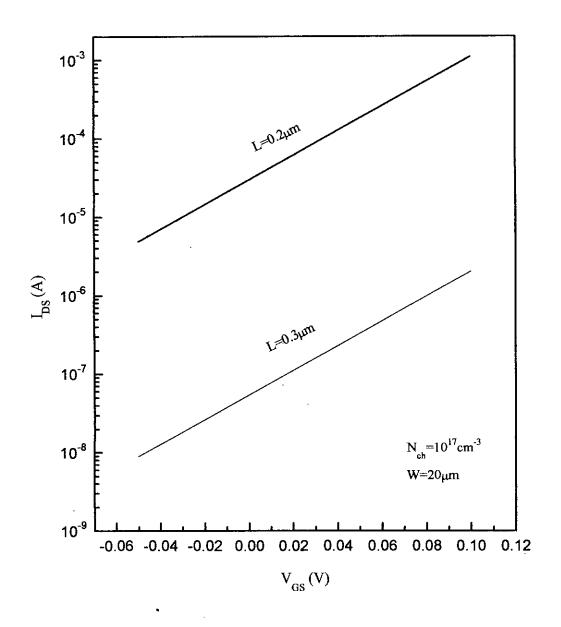

- Fig. 3.15 Subthreshold drain current for two channel lengths.

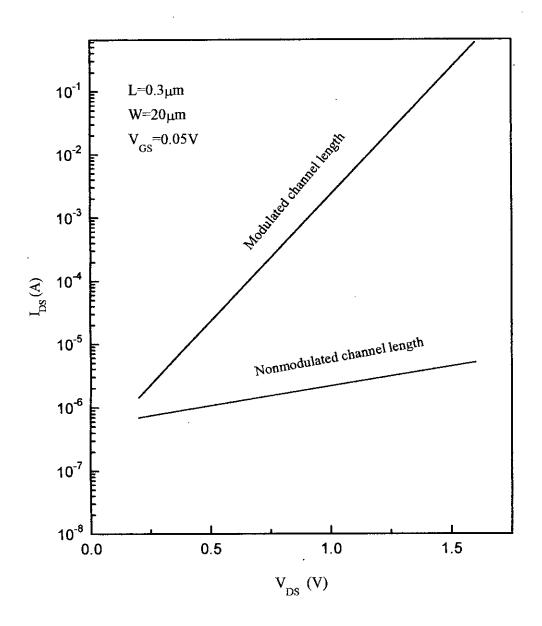

- Fig. 3.16 Effect of channel length modulation on the subthreshold current for a SOI MOSFET with L=0.3μm.

х

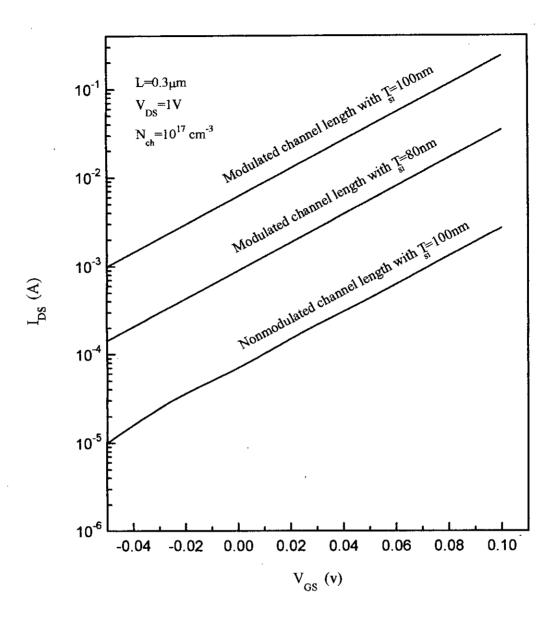

Fig. 3.17 Effects of channel length modulation and silicon film thickness on subthreshold current of a SOI MOSFET.

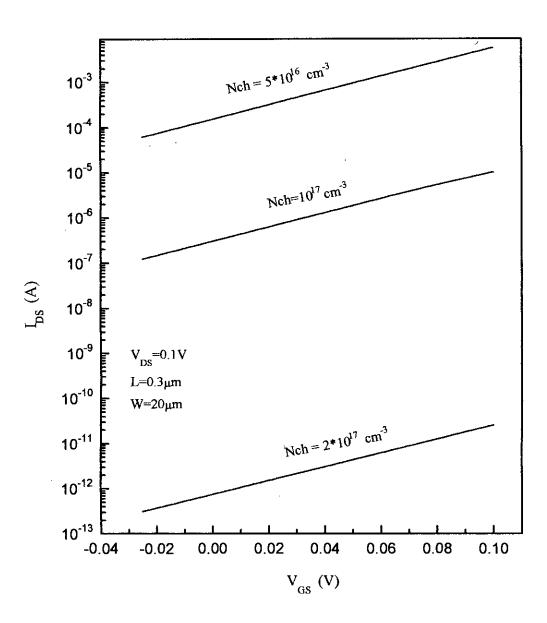

Fig. 3.18 Effect of channel doping concentration on the SOI subthreshold current.

٢

\_2

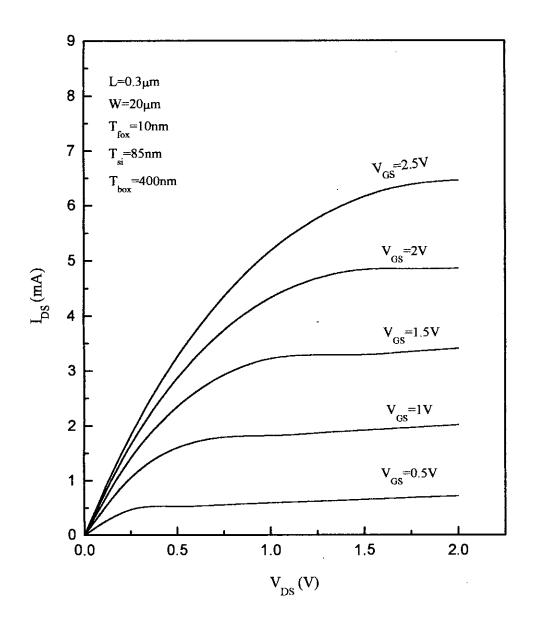

- Fig. 3.19.a Output characteristics of an n-channel SOI MOSFET with  $L=0.3\mu m$ .

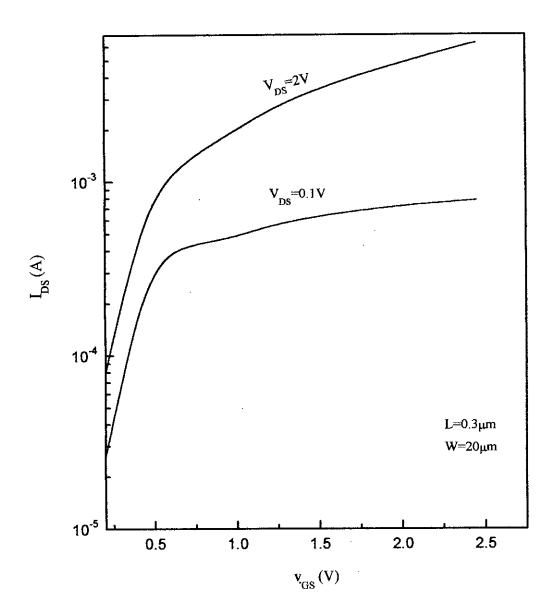

- Fig. 3.19.b Transfer characteristics of an n-channel SOI MOSFET with  $L=0.3\mu m_{\odot}$

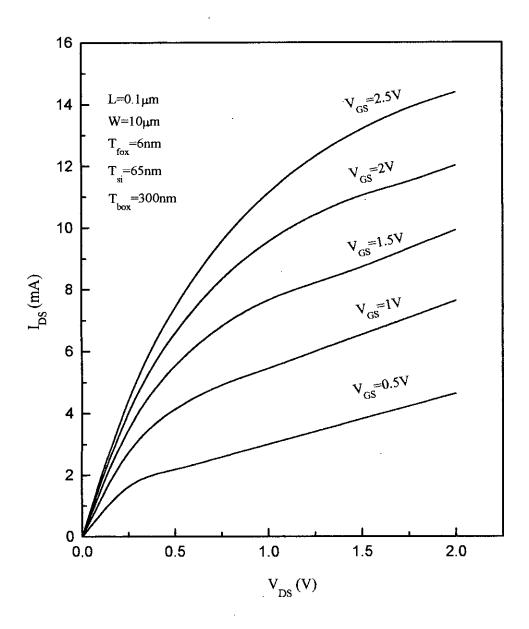

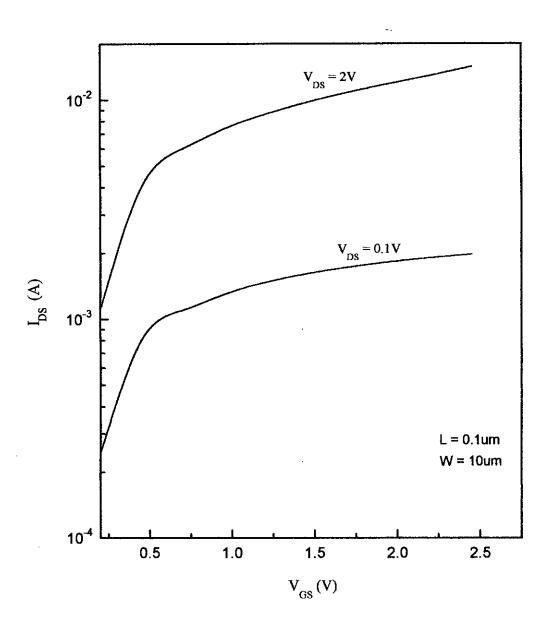

- Fig. 3.20.a Output characteristics of an n-channel SOI MOSFET with  $L=0.1 \mu m$ .

- Fig. 3.20.b Transfer characteristics of an n-channel SOI MOSFET with  $L=0.1 \mu m$ .

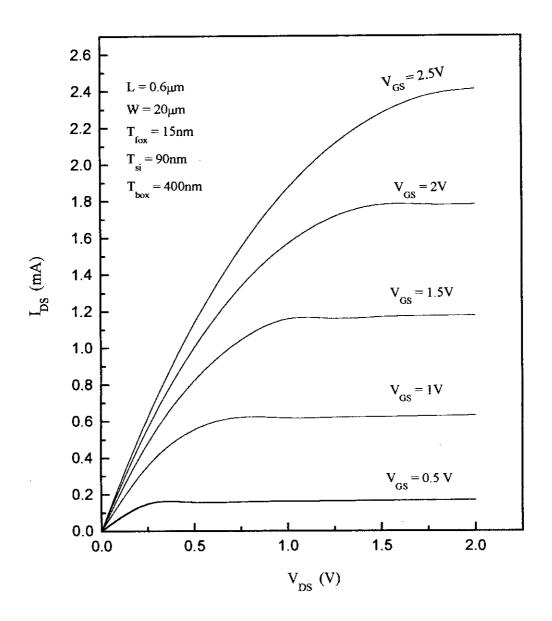

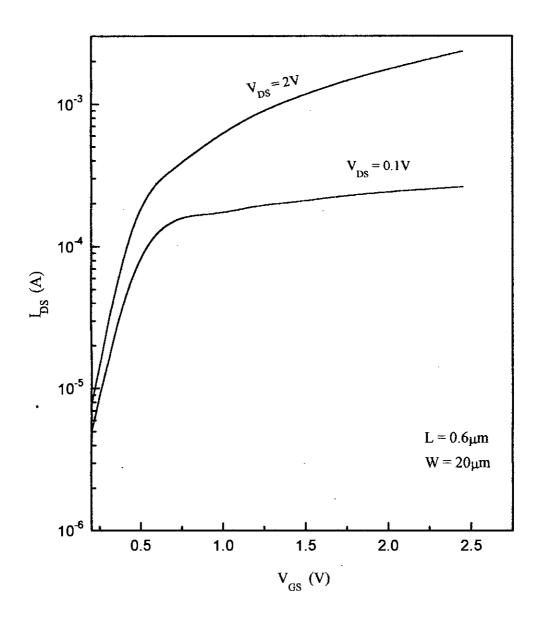

- Fig. 3.21.a Output characteristics of an n-channel SOI MOSFET with  $L=0.6\mu m$ .

- Fig. 3.21.b Transfer characteristics of an n-channel SOI MOSFET with  $L=0.6\mu m$ .

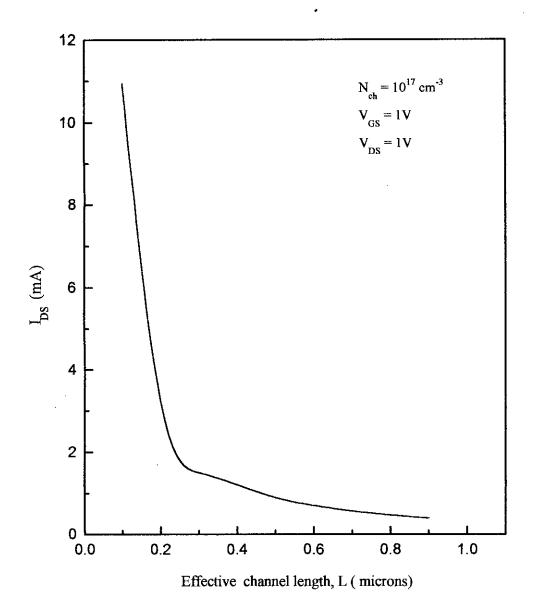

- Fig. 3.22 Drain current vs. channel length for an n-channel SOI MOSFET.

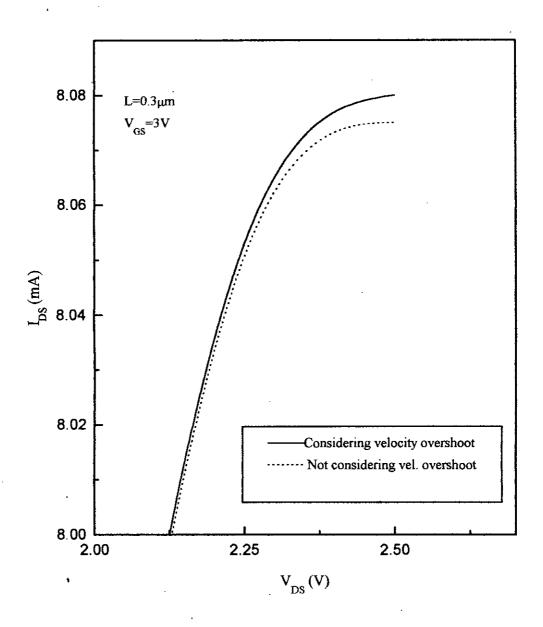

- Fig. 3.23 Effect of velocity overshoot on the drain current of a SOI MOSFET.

# LIST OF PRINCIPAL SYMBOLS

| C <sub>box</sub> | Buried | oxide | capacitance | per unit area |  |

|------------------|--------|-------|-------------|---------------|--|

|                  |        |       |             |               |  |

C<sub>fox</sub> Front oxide capacitance per unit area

C<sub>gc</sub> Effective gate-channel capacitance per unit area

C<sub>i</sub> Inversion capacitance per unit area

C<sub>si</sub> Silicon film capacitance per unit area

E<sub>c</sub> Critical electric field

$E_{sf}(y)$  Front lateral surface electric field at y

I<sub>DS</sub> Drain current

*l* Characteristic length

L Channel length

l<sub>v</sub> Fitting constant

N<sub>ch</sub> Channel doping density

q Electronic charge

Q<sub>m</sub> Free inversion areal charge density

T<sub>box</sub> Buried oxide thickness

T<sub>fox</sub> Front oxide thickness

-1

è

ż.

T<sub>si</sub> Silicon film thickness

V<sub>bi</sub> Built in potential between source-channel or drain-channel

V<sub>cs</sub> Channel – source potential

V<sub>fbf</sub> Flat band voltage at gate

V<sub>fbb</sub> Flat band voltage at substrate

Vsf(y) Surface potential at front oxide -silicon interface

xii

| $V_{sb}(y)$                  | Surface potential at buried oxide-silicon interface |

|------------------------------|-----------------------------------------------------|

| $V_{SL}$                     | Long channel front surface potential                |

| $\mathbf{V}_{t}$             | Thermal voltage, kT/q                               |

| V <sub>th</sub>              | Threshold voltage                                   |

| $V_{th0}$                    | Threshold voltage for a long channel device         |

| V <sub>sat</sub>             | Electron saturation velocity                        |

| W                            | Channel width                                       |

| γ                            | Fitting parameter                                   |

| $\boldsymbol{\epsilon}_{si}$ | Permittivity of silicon                             |

| $\phi_{\rm B}$               | Electron Fermi potential                            |

| φs                           | $2\phi_{\rm B}$                                     |

| η                            | Subthreshold ideality factor                        |

| $\mu_0$                      | Electron low-field mobility                         |

| $\mu_n^{0}$                  | Electron mobility                                   |

| μ <sub>eff</sub>             | Effective electron mobility                         |

| θ                            | Fitting parameter                                   |

| β                            | 2/5U1                                               |

| Uı                           | Equilibrium electron thermal voltage                |

| α                            | $1/E_{\rm C} = \mu_{\rm n}^{0} / 2v_{\rm sat}$      |

. - -

ů,

**"**

Ż

xiii

### **CHAPTER – 1**

#### INTRODUCTION

#### 1.1 **Prologue**

1

)

٦

The modern era of semiconductor electronics was ushered in by the invention of the bipolar transistor in 1948 by Bardeen, Brattain and Shockley at the Bell Telephone Laboratory in the USA. Prior to this invention, valve was the only device to reign in the world of electronics. Valve had many a serious problem, like its bulky size, high cost, short life-time etc. The invention of transistor in 1948 made a complete revolution in the industry of electronics. Since its emergence, the transistor by dint of its multifarious virtues has been replacing the vacuum tubes or valves in almost every field. They began to be used as rectifiers, detectors, amplifiers, oscillators, mixers, modulators etc. Some of the advantages of transistors over vacuum tubes are :

- 1) they are much smaller in size and so are light in weight

- 2) no heater or filament is required ; hence no warm-up time needed

- 3) very low operating voltages can be used

- 4) they consume little power, resulting in greater circuit efficiency

- 5) they are much more reliable because they are solid in construction, extremely rugged and can be made impervious to many severe environmental conditions, so they have longer life with essentially no aging effect.

In recognition of their amazing contribution to physics, the three scientists who invented transistor, were awarded the Noble prize in 1956. Transistors, in fact opened the floodgate to further developments in electronics. Within almost ten years of its discovery, the process of miniaturization of electronic equipments had gained

significant momentum and the first Integrated Circuit (IC) was realized in the year of 1959. Man's desire to conquer the space accelerated this effort even further. The purpose of miniaturization was to increase the packing density (so that many more components could be accommodated on a single chip with the same area) and to improve the circuit performance like speed, response time etc. With the advent of ICs, many circuit functions could be packed into a small place and complex electronic equipments could be employed in many applications where space and weight are critical, such as in aircraft or space vehicles. The use of valves nearly became obsolete during the sixties and newer semiconductor devices were developed day by day with prospective and promising features for various aspects, specially for circuit miniaturization. In this series, the field-effect-transistor or FET was developed in the early 1960s. Like its bipolar counterpart (bipolar transistor), the FET is a threeterminal device in which the current through two terminals is controlled at the third; however the FET device is controlled by a voltage at the third terminal (unlike the bipolar transistor which is controlled by a current). Another difference is that the FET is a unipolar device; that is, its current involves majority carriers only.

रे

7)

With the passage of time, field effect transistors came in several forms, e.g. JFET, MESFET and MOSFET. In a junction FET (called a JFET), the control or gate voltage varies the depletion width of a reverse-biased p-n junction. In a metal-semiconductor FET or MESFET, the junction of a JFET is replaced by a Schottky barrier. The FET that has the greatest commercial importance is the metal-oxide-semiconductor FET or MOSFET (or sometimes called MOST). Also known as insulated-gate FET, a MOSFET uses an oxide layer to separate its gate electrode from the semiconductor. Field effect transistors combine the inherent advantages of solid state devices (e.g. small size, low power consumption and mechanical ruggedness) with a very high input impedance and a square-law transfer characteristic that is specially suitable for use as voltage amplifiers. Since its invention, the field effect transistors (FET) became a superior rival to its counterpart, the bipolar junction transistor or BJT. Some features by which FET excels over BJT are as follows :

- a) it exhibits a high input impedance(typically many megaohms), since the control (or gate ) voltage is applied to a reverse-biased junction or Schottky barrier or across an insulator,

- b) it is simpler to fabricate and occupies less space in integrated form. So it is specially suitable for integration of many devices on a single chip.

- c) it is particularly well suited for controlled switching between an ON state and an OFF state and is therefore useful in digital circuits.

- d) it is less noisy.

Among the members of FET family and other semiconductor devices, metal-oxidesemiconductor FET or MOSFET has gained special significance and prominence over the past two decades. The dominating factor behind such specialty is that the MOS transistor is very well suited to the IC technique, owing to the advantages that it is simpler or easier to fabricate and its size can be reduced with less degree of *smallgeometry effects*. Since 'miniaturization to a further extent' is a never-ending-hunt of the modern researcher, MOSFET, in the last few years has emerged as the most important electronic device, superseding its bipolar counterpart and other devices in both sales volume and applications. MOS transistor has already confirmed its state as a better choice for use in densely packed circuits like ULSI (ultra large scale integration) circuits. Also the fact that digital circuits require only on-off response is an advantage for the MOS device and so MOS transistor is widely used in digital circuits like logic gates, registers or memory arrays.

As said earlier that IC technology was a great advancement of mankind in the world of electronics. Due to the rapid developments in integrated circuit technology starting from small scale integration(SSI), then medium scale integration(MSI), large scale integration(LSI), very large scale integration(VLSI) and now with the

most recent – ultra large scale integration (ULSI) technique – even the use of individual transistors is becoming unnecessary. The vast changes that have taken place during the last 20 years can best be understood by noting the reduction in size and price of modern computers. A small, modern minicomputer is more than 100 times smaller in size and 1/100 th of the price of a computer designed 20 years ago to do the same job. Applications of ICs are now pervasive in such consumer products as watches, calculators, automobiles, telephones, television and other home appliances.

ŧ

ŧ

Now, in the late nineties, the 'hunt-for-further-integration' is not only continuing but is accelerating every day. As earlier said, the metal-oxide-semiconductor FET or MOSFET has been the major device for integrated circuits over the past two decades and this was due to the fact that scaling down of the MOSFET provided high performance gain and smaller die size. The twin benefits of smaller die size ( more chips per wafer and higher fractional yield) exert downward pressure on die cost . As a natural and consequential effort, industrial research has already set sight on MOSFETs of channel length of 0.1 µm and below [1]; the motivations for continued scaling include not only better speed and density but also less power consumption for integrating a complete system on a chip. There have been numerous device structures of submicrometer MOSFET reported in the literature, such as MOSFET with uniformly doped substrate (UD), delta doped MOSFET (DD), partially depleted silicon-on-insulator (SOI) MOSFET and fully depleted silicon-on-insulator (SOI) MOSFET. Among these, fully depleted SOI MOSFET (which has an additional oxide layer just below the Si film) has attracted considerable attention as a potential candidate for future VLSI / ULSI generations, because it offers superior electrical characteristics over bulk MOSFETs, such as, reduced junction - capacitances, attenuated short channel effects, improved subthreshold characteristics, increased channel mobility, reduced hot carrier effects and so on. As a consequence, submicrometer and deep submicrometer SOI circuit design and simulation are becoming increasingly important in VLSI / ULSI technology research.

# 1.2 Limitations of scaling down the SOI MOSFET :

As mentioned in section 1.1 that the purpose of microminiaturization is to increase the packing density and to improve the device performance like speed, response time etc. Ever since the birth of the integrated circuits, researchers have ceaselessly attempted to scale down the size of devices, and silicon-on-insulator (SOI) MOSFET has already proven to be one of the most promising devices for large-scaleintegration. It is expected that the realization of 1 giga bit DRAM (dynamic random access memory) will be achieved in the near future and it will hence require the miniaturization of MOS devices approaching the deep submicron regime (below 0.25  $\mu$ m)[2]. However, as MOS devices are scaled down to submicrometer dimensions, various non ideal characteristics are observed. Since these effects are due to the scaling down of dimensions, these are known as *'small geometry effects.'* These include :

- 1) threshold voltage variation or roll-off

- 2) non saturated drain current

- 3) sharp swing of the subthreshold current

- 4) drain- induced-barrier-lowering (DIBL)

It has been observed experimentally that the threshold voltage does not remain the same if the dimensions are reduced, rather it shifts downward. Moreover, the shift is very sensitive to the drain bias voltage.

As the channel length of a SOI MOS is reduced, its effective channel length becomes comparable to the depletion region near the drain when operated in saturation region; then the drain current does not remain constant with increased drain voltage, unlike that of the long channel device.

The subthreshold current in a SOI MOS (current that flows before applying the threshold voltage or even for zero gate bias) is caused by carrier diffusion from the source to drain. Like a bipolar transistor, this current is very sensitive to the base width i.e. channel length in this case. Subthreshold current is seen to increase as devices are made smaller ; also this current in a short channel device is seen to increase with increasing drain voltage due to channel length modulation.

Another effect that becomes prominent with scaling down of devices is the DIBL or *drain induced barrier lowering effect*. As the channel length continues to decrease, the drain depletion layer starts to interact with the source-channel junction to lower the source-junction potential barrier; which in turn allows electrons to be injected into the channel regardless of the gate voltage and the gate voltage thus loses control of the drain current.

#### **1.3 REVIEW OF THE PREVIOUS WORK**

1

1

The thin-film fully-depleted SOI MOS field-effect-transistor (SOI MOSFET) is considered a promising candidate for future ULSI generations due to its multifarious advantages over the bulk MOSFET. So in the recent years, this device has attracted considerable attention and a sufficient amount of research works have been reported so far which encounters the effect of scaling down on the threshold voltage roll-off, the subthreshold swing, the normal drain current etc. In FDSOI MOSFET, a strong electrical coupling of the two interfaces results in interesting behavior of the threshold voltage. This effect was reported using one-dimensional models [3]-[5]. However, threshold voltage reduction with decreasing channel length and increasing drain-source voltage is a two-dimensional effect in short channel devices. The exact solution of two-dimensional Poisson's equation in the channel

depletion region has already been reported in [6] and [7]. Analytical potential distribution models based on the infinite series methods were developed in [6]. However, such models require iterative calculations, that reduce the physical insight provided by the infinite series models.

Charge sharing approach was reported in [8] for FDSOI MOSFETs. (As the channel length is decreased, the source and drain depletion regions are brought closer together and can intrude into the channel even without bias and this way they can share the charge in the channel; this is known as charge-sharing effect). The concept of charge sharing provides physical insight into the development of the threshold voltage expression and predicts trends almost correctly. Charge sharing models predict a  $1/L_{eff}$  dependent threshold voltage shift. However, the charge- sharing model assumption of constant surface potential is not valid in the range of submicrometer channel length. On the other hand, the exact solution of Poisson's equation with various approximations made for the boundary conditions lacks physical meaning (due to series solution of Poisson's equation) and is computationally inefficient.

Until recently, several analytical I-V characteristic models for SOI MOS had been developed for the purpose of circuit simulation. However, few of these models provide a complete coverage on I-V characteristics including the subthreshold regime. The recently-published models [9]-[10] are mainly restricted to the driftdiffusion model, so the velocity overshoot effect was not taken into account. Velocity overshoot is an energy transport effect; as channel length reduces, the electric field near the source rises in a steep manner which induces non-local transport effect and so enhances carrier velocity in the source end. This phenomenon is known as 'velocity overshoot' effect and it becomes obvious as the feature size is scaled into the deep submicrometer regime [11]. Also the studies published so far, concentrated on intrinsic device behavior without accounting for the source/drain resistance. As device dimensions are scaled down to the submicrometer level, these parasitic resistances become increasingly significant.

# **1.4 OBJECTIVES OF THE PRESENT STUDY**

The main objective of this research is to develop a physics-based simple, complete and analytical submicrometer-SOI-MOSFET model for accurate simulation of digital / analog circuits. The objectives, at large are:

- To develop an accurate expression for surface-potential of a single-gate FDSOI MOSFET by using a quasi-two-dimensional approach.

- To develop an accurate model of threshold voltage for a SOI device, applicable to both submicrometer and deep submicrometer channel lengths

- To obtain the expression for free inversion areal charge density, in terms of gate and drain voltages.

- To derive an effective mobility formula, to be used in the drain current model and modified on the basis of energy-balance equation and considering velocity overshoot.

- To obtain the I-V characteristic models separately in weak inversion (for subthreshold current) and strong inversion (for normal drain current) regions, incorporating the effects of drain/source resistance, velocity overshoot, mobility reduction due to the transverse electric field and DIBL.

# **1.5 BRIEF INTRODUCTION TO THIS THESIS**

A brief introduction to semiconductor electronics and integrated-circuit (IC) technology is presented in chapter 1, with an emphasis on MOSFET devices and a review of the research works currently going on in this field.

Chapter 2 presents sequentially a model for front-surface electric-potential using a quasi-two-dimensional Poisson's equation, then the model for threshold voltage, the model for free-inversion areal charge density, the I-V model for subthreshold regime and the I-V model for above threshold / normal operating conditions.

The results and discussions are presented in chapter 3.

Conclusion and future scope of works are presented in chapter 4.

## **CHAPTER-2**

# THEORETICAL ANALYSIS OF THRESHOLD VOLTAGE AND STATIC CHARACTERISTICS OF A FULLY DEPLETED SOI MOSFET

#### 2.1 Overview

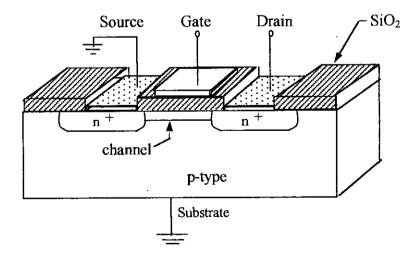

The Metal –Oxide-Semiconductor FET or MOSFET is a four terminal semiconductor device in which the lateral current flow is controlled by an externally applied vertical electric field. A typical MOS transistor is shown in Fig. 2.1 where the four terminals are designated as the source, gate, drain and substrate. (In most simplified analyses the effect of the substrate is neglected or it is often tied to the source and the MOS transistor is considered as a three- terminal device). The transistor shown is an n-channel MOSFET which consists of a lightly doped p-type substrate into which two highly doped  $n^+$  regions (source and drain) are diffused. A thin (100-1000Å) insulating silicon dioxide (SiO<sub>2</sub>) is grown over the surface of the structure and holes are cut into the oxide layer, allowing contact with the source and drain.

Fig. 2.1 An n-channel MOS Transistor

Then the gate electrode is overlaid on the oxide, covering the entire channel region (region between the source and drain). The gate electrode was originally metal, specifically aluminium, but is now more commonly a layer of polycrystalline silicon (referred to as polysilicon).

With no voltage applied to the gate, the two back-to-back p-n junctions between the drain and source prevent current flow in either direction . When a positive voltage is applied to the gate with respect to the substrate, electrons are induced in the semiconductor below the oxide-semiconductor interface. In fact so many electrons are attracted to the surface that an extremely thin conduction channel or inversion layer is formed between the source and drain, where the semiconductor actually changes from p to n type. Now, when a voltage is applied between the source and drain, current can flow between them and the flow (or channel conductivity) can be controlled or modulated by the vertical electric field; this is why the device is called a Field Effect Transistor or FET. For the transistor shown, the induced charge in the channel is ntype and the device is so known as an n-channel MOSFET or simply NMOS. A pchannel transistor is obtained by interchanging the n and p regions. Since the MOS gate is insulated from the channel, no dc current conducts through the oxide layer and so a MOSFET is also known as the insulated-gate field effect transistor (IGFET). The insulating oxide layer results in an extremely high input resistance  $(10^{10} - 10^{15} \text{ ohms})$ for the MOSFET.

The device just described requires a voltage to be applied to the gate before the channel is formed and the drain current is enhanced by the applied gate voltage; this is why the device is called an " enhancement –type MOSFET. Sometimes, charges are deliberately introduced between source and drain by ion implantation or a channel is diffused between source and drain, with the same type of impurity as used for the source and drain diffusion. Such a normally 'ON' transistor is called a depletion-type MOSFET because a gate voltage of reverse polarity (in case of NMOS, negative) is to be applied to deplete the channel of electrons and shut the device off.

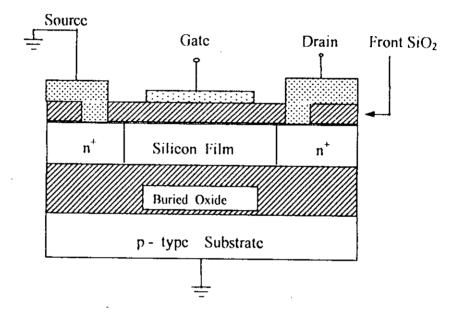

#### SOI MOSFET

An interesting and useful extension of the silicon MOS process can be achieved by growing very thin films of single crystal Si on insulating substrates. The Si films being very thin (100 nm) the source and drain regions can be made to extend entirely through the film to the buried insulator and as a result the junction capacitances are remarkably reduced. Such a device with silicon film sandwiched between two insulating oxide layers is known as Silicon-On --Insulator MOSFET or SOI MOS. The cross sectional view of a SOI MOS is shown in the figure 2.2.

Fig. 2.2 Cross sectional view of a SOI MOSFET.

# THE MECHANISM OF CHANNEL FORMATION AND THE SURFACE CHARGE CONDITIONS IN A SOLMOSFET :

The MOS structure shown in Fig. 2.2 is basically a device containing two capacitors; one is the front capacitor with front  $SiO_2$  as the dielectric material and the other is the buried capacitor with buried  $SiO_2$  as the dielectric material. It is the front capacitor

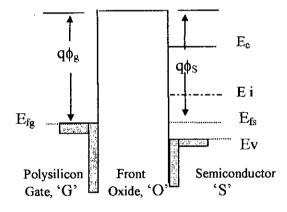

which is significantly prominent and so we limit our concerns here around the conditions of front surface charge of the Si film (i.e. the charge below the interface of front SiO2- Si film). Let us firstly consider the energy –band diagram of an ideal MOS structure, as shown in Fig. 2.3. For simplicity, we have assumed that the work-functions are the same for all three parts of the front capacitor and so their energy-bands at equilibrium are flat. (The work function is defined as the work required to bring an electron from the Fermi level to the vacuum level). As shown in Fig. 2.3.a, the system is at equilibrium and  $q\phi_g = q\phi_S$ , ( $q\phi_g$  is the modified work function for the front SiO<sub>2</sub>-gate interface and  $q\phi_S$  is the modified work function for the front SiO<sub>2</sub>-Si interface). Another useful quantity is the  $q\phi_f$  which indicates how strongly p-type the semiconductor is.

(a)

Fig. 2.3 Effects of applied voltage on the energy band diagram of ideal NMOS capacitor (a) band –diagram at equilibrium

(d)

Fig. 2.3 Effects of applied voltage on the energy band diagram of ideal NMOS capacitor (d) band-diagram for a larger positive gate voltage causing inversion.

If we apply a negative gate voltage (fig. 2.3.b), a negative charge is effectively deposited on the gate and in response, an equal net positive charge or holes is accumulated at the semiconductor surface. This situation, when the hole density just below the Si surface is greater than the equilibrium density in the bulk, is known as carrier accumulation. The energy-bands of the semiconductor bend upward near the interface, leading to a larger  $q\phi_f$  so that the accumulation of holes can be accommodated.

(b)

Fig. 2.3 Effects of applied voltage on the energy band diagram of ideal NMOS capacitor (b)band-diagram for negative gate voltage causing hole accumulation, (c)band-diagram for positive gate voltage causing hole depletion.

When we apply a positive voltage at the gate (fig. 2.3.c), the gate Fermi level is lowered by qV relative to its equilibrium position; as a result holes are depleted from the  $SiO_2 - Si$  interface and the semiconductor energy – bands bend downward near the surface leading to a smaller  $q\phi_f$ .

If we continue to increase the positive gate bias (fig. 2.3.d), the bands at the semiconductor surface bend down more sharply. In fact, a sufficiently large voltage can bend Ei below  $E_{fs}$  (i.e. negative  $q\phi_t$ ), which is particularly an interesting case, since  $E_{fs} >> Ei$  means a large electron concentration in the conduction band. In other words, the silicon surface procures the conduction properties typical of n-type material and this is done not by doping but by the inversion of the originally p-type silicon due to the applied voltage. This inversion layer is the key to MOS transistor operation. Depending on the strength of the positive gate bias, the inversion event is termed as *weak inversion, moderate inversion* and *strong inversion*. As long as the electron density at the surface remains smaller than hole density in the bulk, the condition is called 'weak inversion'. As soon as the two densities become equal, the onset of moderate inversion is reached, the surface potential is then  $2\phi_f$ . In most MOS transistor operation, it is necessary to establish a strong inversion carrier density and the criterion for 'strong inversion is that the surface potential becomes much greater than  $2\phi_f$ .

#### FLAT BAND AND THRESHOLD VOLTAGES

In the previous section, we assumed that the energy-band diagram is flat when the MOS is at equilibrium condition (i.e. zero gate bias). In practice, this condition is not realized because of unavoidable work-function difference and the charges in the oxide and surface states. The modified work-function of the gate-electrode is not generally equal to that of the semiconductor, so a band –bending exists in the semiconductor in order to satisfy the requirement of constant Fermi level under thermal equilibrium.

Also the charges that reside within the oxide contribute to further band – bending. So the gate voltage required to achieve the flat band condition, known as *flat band voltage*, is given by,

$$V_{FB} = V_{G1} + V_{G2} = \phi'_{gs} - Q_0 / C_{fox} = (\phi'_g - \phi'_s) - Q_0 / C_{fox};$$

where,  $\phi'_{g}$  is the modified work-function of gate-electrode

$\phi'_{s}$  is the modified work-function of semiconductor

Q<sub>0</sub> is the sum of induced charges under zero gate bias

$C_{fox}$  is the front oxide capacitance.

In case of a SOI MOSFET, an extra gate voltage is to be applied to take care of the band-bending at buried oxide-Si interface.

## **Threshold Voltage**

Threshold voltage is the critical voltage at which the inversion layer is formed to a significant extent, giving rise to rapid increase of the inverse charge for higher gate voltages. In other words, the threshold voltage specifies the gate voltage at the onset of strong inversion. This voltage takes into account the flat-band voltage, the moderate inversion onset-voltage (i.e.  $2\phi_f$ ) and voltages due to depletion layer and oxide layer charges. Threshold voltage is a very significant parameter of a MOS circuit. Generally a lower threshold voltage is desirable since it allows the use of a small power- supply voltage and so lower power consumption. Lower threshold voltage also allows smaller swing during switching.

# STATIC CHARACTERISTICS OF THE SOI MOSFET

A schematic diagram of an n-channel SOI MOSFET is shown in the Fig.2.4, in which bias voltages are included. To simplify our analysis, the source and the substrate have been grounded. The static characteristics of the SOI MOSFET have two distinct regions of operation. At low drain voltages, the drain to source characteristics are basically ohmic and the drain current is proportional to the drain voltage in a nearly linear fashion. This is the linear region of operation. At high drain voltages the gate voltage is neutralized and the inversion layer disappears at the drain end of the channel. The channel is then called "pinched-off" and further increase of drain voltage would not increase the drain current significantly, i.e. the drain current becomes saturated and the region of operation is called "saturation region".

Fig. 2.4 An n-channel SOI-MOSFET operating in the saturation region

# 2.2 FRONT SURFACE POTENTIAL OF A SOI MOSFET

We firstly represent the channel – depletion – region of a fully depleted n-channel SOI –MOSFET by a rectangular Gaussian box as shown in fig. 2.5. Axes are so chosen that the y-axis is along the channel from source to drain and the x-axis is from the front oxide to the buried oxide. The height of the box is  $T_{si}$  and the length is  $\Delta y$ .

Fig. 2.5 (a) Cross-sectional view of a typical SOI-MOSFET

(b)Gaussian box representation of its channel depletion region with boundary conditions and reference direction.

By applying Gauss's law to this box and neglecting mobile carrier charge in the channel, the following equation can be derived :

$$\frac{\varepsilon_{si}T_{si}}{\gamma} \times \frac{\partial E_{sf}(y)}{\partial y} + C_{fox} \left( V_{GS} - V_{fbf} - V_{sf}(y) \right) + C_{box} \left( -V_{fbb} - V_{sb}(y) \right) = q N_{ch} T_{si}$$

where,

- $\varepsilon_{si}$  is the silicon permittivity

- T<sub>si</sub> is the channel thickness

$E_{sf}(y)$  is the front lateral surface electric field

γ is a fitting parameter

C<sub>fox</sub> is the front oxide capacitance

V<sub>GS</sub> is the gate-source voltage

$V_{\rm fbf}$  is the flat-band voltage at the gate

$V_{sf}(y)$  is the channel potential at the front SiO<sub>2</sub> – Si interface

Cbox is the buried oxide capacitance

$V_{fbb}$  is the flat band voltage at the substrate

$V_{sb}(y)$  is the channel potential at the buried SiO<sub>2</sub> – Si interface

- q is the charge of an electron

- N<sub>ch</sub> is the channel doping

The first term on the left hand side of equation (2.1) refers to the net electric flux entering the Gaussian box along the y – direction, the second term refers to the electric flux entering the top surface of the Gaussian box, the third term refers to the electric flux entering the bottom surface of the Gaussian box. The right hand side of the equation represents the total charge inside the Gaussian box. In deriving equation (1), we have assumed uniform electric field in the buried oxide and neglected fringing fields in the buried oxide due to source and drain.

The back- channel surface potential (Vsb) can be expressed in terms of the front channel surface potential (Vsf) by solving the 1-D Poisson's equation in the thin silicon film as following :

Integrating,

At

$$x = 0$$

,  $(\partial V / \partial x) = -E_{sf}$

$$\therefore C_1 = -E_{sf}$$

Integrating eqn. (2.2.a)

Again at  $x = T_{si}$ ,  $V = V_{sb}$ ;

Now we obtain the following equation by applying Gauss's law at the front SiO<sub>2</sub> - Si interface,

$$E_{sf}(y) \varepsilon_{si} = C_{fox} \left( V_{GS} - V_{fbf} - V_{sf}(y) \right) \qquad (2.3)$$

By substituting (2.2.c) and (2.3) in (2.1) we obtain,

$$\frac{\varepsilon_{si} T_{si}}{\gamma} \times \frac{\partial E_{sf}(y)}{\partial y} + Cfox[(V_{GS} - V_{fbf} - V_{sf}(y)] + C_{box}[-V_{fbb} - V_{fbf}] + \frac{V_{sf}(y)T_{si}}{\varepsilon_{si}}] = qN_{ch}T_{si}$$

$$\{V_{sf} - \frac{C_{fox}(V_{GS} - V_{fbf} - V_{sf}(y))T_{si}}{\varepsilon_{si}}\} + \frac{qN_{ch}T_{si}^{2}}{2\varepsilon_{si}}] = qN_{ch}T_{si}$$

Defining the thin film capacitance  $\epsilon_{si} / t_{si}$  as Csi, we obtain,

$$\frac{\varepsilon_{si}t_{si}}{\gamma} \times \frac{\partial E_{sf}(y)}{\partial y} - V_{sf}(y) \left[ C_{fox} + C_{box} + \frac{C_{box}C_{fox}}{C_{si}} \right] = qN_{ch}t_{si} \left[ 1 + \frac{C_{box}}{2C_{si}} \right]$$

$$- C_{fox} \left( V_{gs} - V_{fbf} \left( 1 + \frac{C_{box}}{C_{si}} \right) + C_{box}V_{fbb} \right] + C_{box}V_{fbb} \right]$$

(2.4.a)

Let ,

$$\frac{1}{\tilde{C}_{ox}} = \frac{1}{C_{fox}} + \frac{1}{C_{box}} + \frac{1}{C_{si}},$$

$$\frac{1}{\tilde{C}_{box}} = \frac{1}{C_{box}} + \frac{1}{C_{si}},$$

$$\frac{1}{\tilde{C}_{fox}} = \frac{1}{C_{fox}} + \frac{1}{C_{si}},$$

$$\frac{1}{\tilde{C}_{fox}} = \frac{1}{C_{fox}} + \frac{1}{C_{si}},$$

$$C_{ox} = \left[C_{fox} + C_{box} + \frac{C_{fox}}{C_{si}}\right] = \frac{C_{fox}}{\tilde{C}_{ox}};$$

Then equation (2.4.a) becomes,

$$\frac{\varepsilon_{si}t_{si}}{\gamma} \times \frac{\partial E_{sf}(y)}{\partial y} - V_{sf}(y)C_{ox} = qN_{ch}t_{si}\left[1 + \frac{C_{box}}{2C_{si}}\right] - C_{fox}\left[1 + C_{box} / C_{si}\right]\left[V_{gs} - V_{fbf}\right] + C_{box}V_{fbb};$$

$$\Rightarrow \frac{\varepsilon_{si} t_{si}}{\gamma C_{ox}} \times \frac{\partial E_{sf}(y)}{\partial y} - V_{sf}(y) = \frac{qN_{ch} t_{si}}{C_{ox}} \left[ 1 + \frac{C_{box}}{2C_{si}} \right] - \frac{C_{fox}}{C_{ox}} \left[ 1 + C_{box} / C_{si} \left[ V_{gs} - V_{fbf} \right] + \frac{C_{box}}{C_{ox}} V_{fbb}; \right]$$

$$\Rightarrow \frac{\varepsilon_{\rm si} t_{\rm si}}{\gamma C_{\rm fox}} \times \frac{\tilde{C}_{\rm ox}}{C_{\rm box}} \times \frac{\partial E_{\rm sf}(y)}{\partial y} - V_{\rm sf}(y) + V_{\rm SL} = 0$$

$$\Rightarrow \ell^2 \frac{\partial E_{sf}(y)}{\partial y} - V_{sf}(y) + V_{SL} = 0 \qquad (2.4.b)$$

where,

$$\ell^2 = \frac{\epsilon_{si} t_{si}}{\gamma C_{fox}} \times \frac{C_{ox}}{C_{box}}$$

and

$$V_{SL} = \frac{C_{fox}}{C_{ox}} \left[ 1 + C_{box} / C_{si} \right] \left( V_{gs} - V_{fbf} \right) - \frac{C_{box} V_{fbb}}{C_{ox}} - \frac{qN_{ch} t_{si}}{C_{ox}} \left[ 1 + \frac{C_{box}}{2C_{si}} \right]$$

$$= \frac{\left[1 + \frac{C_{box}}{C_{si}}\right]}{\left[1 + \frac{C_{box}}{\widetilde{C}_{fox}}\right]} \times \left[V_{gs} - V_{fbf}\right] - \frac{\left[C_{box} / C_{fox}\right]V_{fbb}}{\left[1 + \frac{C_{box}}{\widetilde{C}_{fox}}\right]}$$

$$-\frac{\left[1+\frac{C_{box}}{2C_{si}}\right]}{\left[1+\frac{C_{box}}{\widetilde{C}_{fox}}\right]}\frac{qN_{ch}t_{si}}{C_{fox}}$$

(2.4.c)

The solution of eqn. (2.4.b) with the boundary conditions of  $V_{sf}(0) = V_{bi}$  and  $V_{sf}(L) = V_{bi} + V_{DS}$  is

In the above equation  $V_{SL}$  represents the Long Channel front surface potential, same as that defined in [7],  $V_{bi}$  is the built- in potential between the source-channel and drain-channel p-n junctions and "l" is the characteristic length defined as

$$l = \sqrt{\frac{\varepsilon_{si} t_{si} \tilde{C}_{ox}}{\eta C_{fox} C_{box}}};$$

The front channel surface potential expressed by eqn. (2.5) can be thought of as the long-channel surface potential modified by the source/drain fringing field. The effects of the variation of the lateral field in the depletion layer under the channel are incorporated through the fitting parameter  $\gamma$ .  $E_{sf}(y)/\gamma$  can be thought of as an average lateral electric field in the channel.  $\gamma$  is less than one when  $E_{sf}(y)$  is less than the average field and greater than one otherwise. At  $V_{GS} = V_{th}$ , surface lateral electric field is less than the average lateral electric field in the average lateral electric field in the channel depletion region and so  $\gamma < 1$ . For large drain voltages, the surface lateral electric field near the drain is more than the average lateral field and hence  $\gamma > 1$  as reported in [12] and [13].

# 2.3 <u>THE SHORT-CHANNEL THRESHOLD VOLTAGE</u> <u>MODEL FOR AN FDSOI MOSFET</u>

Here we develop a short-channel threshold voltage model for FDSOI MOSFET using a quasi-two-dimensional approach, similar to those used for modeling threshold voltage, substrate current and other hot electron phenomenons in Bulk MOSFETs[12]-[15].

For a long channel device, i.e. for L  $\rightarrow \infty$ , the surface potential is  $V_{SL}$  and the threshold voltage for such device,  $V_{th0}$  can be obtained from the expression of  $V_{SL}$  (eqn. 2.4.c) by setting it equal to  $2\phi_B$ , where  $\phi_B = (kT/q) \ln (Nch/n_i)$ :

Defining  $2\phi_B$  as  $\phi_S$ ,

$$\varphi_{S} = \frac{\left[1 + \frac{C_{box}}{C_{si}}\right]}{\left[1 + \frac{C_{box}}{\tilde{C}_{fox}}\right]} \times \left[V_{th 0} - V_{fbf}\right] - \frac{\left[C_{box} / C_{fox}\right]V_{fbb}}{\left[1 + \frac{C_{box}}{\tilde{C}_{fox}}\right]}$$

$$- \frac{\left[1 + \frac{C_{box}}{2C_{si}}\right]}{\left[1 + \frac{C_{box}}{\tilde{C}_{fox}}\right]} \frac{qN_{ch} t_{si}}{C_{fox}}$$

$$\Rightarrow V_{\text{th0}} = V_{\text{fbf}} + \frac{\widetilde{C}_{\text{box}}}{\widetilde{C}_{\text{ox}}} \varphi_{\text{S}} + \frac{\widetilde{C}_{\text{box}}}{C_{\text{fox}}} V_{\text{fbb}} + \left[1 - \frac{\widetilde{C}_{\text{box}}}{2C_{\text{si}}}\right] \frac{qN_{\text{ch}}t_{\text{si}}}{C_{\text{fox}}} \dots (2.6)$$

To simplify  $V_{SL}$ , we substitute  $V_{th0}$  in  $V_{SL}$  as follows,

The front channel surface potential  $V_{sf}$  has a minimum value  $V_{sf,min}$ , say at  $y=y_o$ , which can be found by solving the eqn.

$$\left. \frac{dV_{sf}(y)}{dy} \right|_{y = y} = 0$$

and is given by

$$y_{0} = \frac{\ell}{2} \ln \frac{\left[ (V_{bi} - V_{SL})e^{(L/\ell)} - (V_{bi} + V_{DS} - V_{SL}) \right]}{\left[ V_{bi} + V_{DS} - V_{SL} \right] - (V_{bi} - V_{SL})e^{(-L/\ell)}$$

(2.7)

However, when  $V_{DS}\,<<\,(V_{bi}-V_{SL}),\,y_0$  may be approximated as follows  $\,:\,$

$$y_{0} \approx \frac{\ell}{2} \ln \frac{\left[ (V_{bi} - V_{SL}) e^{(L/\ell)} - (V_{bi} - V_{SL}) \right]}{\left[ V_{bi} - V_{SL} \right] - (V_{bi} - V_{SL}) e^{(-L/\ell)} }$$

$$= \frac{\ell}{2} \ln e^{(L/\ell)} = L/2 \quad ; \qquad (2.7.a)$$

So,  $V_{sfmin}$  can be obtained analytically from eqn. (2.5) for  $y = y_0$ :

$$V_{sf min} = V_{SL} + [2(V_{bi} - V_{SL}) + V_{DS}] \frac{\sinh(L/2\ell)}{\sinh(L/\ell)}$$

; ... (2.7.b)

To determine the threshold voltage, we assume that  $V_{sf\,min}$  is equal to  $\phi_S$  or  $2\phi_B$  at  $V_{GS} = V_{th}$  (Threshold voltage).  $V_{th}$  or Threshold voltage is defined as the gate voltage which causes  $V_{sf\,min}$  to equal to  $2\phi_B$  or

$$\left(2 \frac{kT}{q} \ln \frac{N_{ch}}{n_{i}}\right)$$

For  $V_{GS} = V_{th}$ ,

\$

**≡**.

-

$$V_{sf min} = \phi_{S} = V_{SL} + \left[2(V_{bi} - V_{SL}) + V_{DS}\right] \frac{\sinh(L/2\ell)}{\sinh(L/\ell)}$$

$$\Rightarrow \varphi_{S} = \frac{\widetilde{C}_{ox}}{\widetilde{C}_{box}} \left( V_{th} - V_{tho} \right) + \left[ (2V_{bi} + V_{DS}) - 2 \left\{ \varphi_{S} + \frac{\widetilde{C}_{ox}}{\widetilde{C}_{box}} \left( V_{th} - V_{tho} \right) \right\} \right]$$

$$\times \frac{\sinh(L/2\ell)}{\sinh(L/\ell)} + \varphi_{S}$$

Here we can define  $(V_{tho} - V_{th})$  as the Threshold Voltage Shift  $\Delta V_{th}$  and solve for it,

$$\frac{\tilde{C}_{\text{ox}}}{\tilde{C}_{\text{box}}} \Delta V_{\text{th}} \left[ 1 - \frac{2 \sinh(L/2\ell)}{\sinh(L/\ell)} \right] = \left[ 2(V_{\text{bi}} - \varphi_{\text{S}}) + V_{\text{DS}} \right] \frac{\sinh(L/2\ell)}{\sinh(L/\ell)}$$

$$\Rightarrow \Delta V_{\text{th}} = \frac{\tilde{C}_{\text{box}}}{\tilde{C}_{\text{ox}}} \frac{\left[ 2(V_{\text{bi}} - \varphi_{\text{S}}) + V_{\text{DS}} \right] \sinh(L/2\ell)}{\left[ \sinh(L/\ell) - 2 \sinh(L/2\ell) \right]}$$

$$= \eta \frac{\left[ 2(V_{\text{bi}} - \varphi_{\text{S}}) + V_{\text{DS}} \right]}{2 \cosh(L/2\ell) - 2} \qquad (2.8)$$

where ,

$$\eta = \frac{\widetilde{C}_{box}}{\widetilde{C}_{ox}}$$

When  $l \ll L$ , the term  $1/(2\cosh(L/2l)-2)$  can be approximated as  $(\exp^{-L/2l} + 2\exp^{-L/l})$ [14] and threshold voltage shift can be expressed as

$$\Delta V_{\text{th}} = \eta \left[ 2(V_{\text{bi}} - \varphi_{\text{S}}) + V_{\text{DS}} \right] \left( \exp^{-L/2\ell} + 2 \exp^{-L/\ell} \right) \qquad (2.8.a)$$

It is worth noting that in case of a bulk-model MOSFET, the general expression for threshold voltage shift is[14]

$$\Delta V_{\text{th}} = \frac{\left[2(V_{\text{bi}} - \varphi_{\text{S}}) + V_{\text{DS}}\right]}{2\cosh(L/2\ell) - 2} \qquad (2.9)$$

Where, *l* is expressed as

$$\sqrt{\frac{\varepsilon_{\rm si} X_{\rm dep}}{\gamma C_{\rm fox}}}$$

So we see that the threshold voltage shift  $\Delta V_{th}$  of a SOI Mosfet when compared with that of a bulk MOSFET only differs by a multiplication factor  $\eta$  and characteristic length *l*. Since  $t_{si} < x_{dep}$ , ( $x_{dep}$  is the depletion layer thickness) the value of *l* for a SOI MOSFET is less than that of a bulk MOSFET. So it can be easily deduced that the threshold voltage roll-off in FD SOI is less than that in the bulk as predicted by a shorter characteristic length in FDSOI. According to eqn. (2.8.a), a higher channel doping and thinner  $t_{fox}$ ,  $t_{si}$  and  $t_{box}$  will help to suppress the V<sub>th</sub> roll-off.

# 2.4 STATIC CHARACTERISTIC MODEL FOR SUBMICRON/DEEP SUBMICRON SOI MOSFET

#### 2.4.1 INVERSION CHARGE PER UNIT AREA

In order to produce a complete I-V model of a FDSOI-MOSFET, we firstly develop the expression of "free inversion areal charge density"  $Q_m$ , in terms of gate and drain voltages.

The 1-D effective gate-channel capacitance, Cgc can be written as[16],

$$C_{gc} = -\frac{\partial Q_m}{\partial V_{GS}} = -\frac{\partial Q_{GS}}{\partial V_{GS}} \times \frac{\partial Q_m / \partial V_{sf}}{\partial Q_{GS} / \partial V_{sf}}$$

$$\approx \frac{C_{\text{fox}}C_{i}}{\eta C_{\text{fox}} + C_{i}}$$

(2.10)

Where,  $C_i$  is the inversion layer capacitance and is given as  $-\partial Q_m / \partial V$

C<sub>fox</sub> is the front oxide capacitance

$\eta^* = 1 + Csi / Cfox$

**={**-

Csi is the silicon film capacitance

The inversion layer capacitance,  $C_i$  can be found using the charge sheet model, which assumes that all the mobile charges are residing at the oxide-silicon interface as if the inversion layer were a two-dimensional sheet.

From 1-D Poisson's equation, we can obtain

$$\frac{d^2 V}{dx^2} = \frac{q N_{ch}}{\epsilon_{si}} \left[ exp \left( \frac{V - 2\phi_B - V_{CS}}{V_t} \right) + 1 \right] \qquad (2.11)$$

where, V is the potential

$V_{CS}$  is the channel source potential  $V_t$  is thermal voltage, kT/q

By multiplying both sides of eqn. (2.11) with dV/dx and using the identity :

$$\frac{1}{2} \frac{d}{dx} \left( \frac{dV}{dx} \right)^2 = \frac{dV}{dx} \frac{d^2 V}{dx^2}$$

we have,

.

$$\frac{1}{2} \frac{d}{dx} \left( \frac{dV}{dx} \right)^2 = \frac{qN_{ch}}{\epsilon_{si}} \frac{d}{dx} \left\{ V + V_t \exp \left[ (V - 2\varphi_B - V_{CS}) / V_t \right] \right\}$$

.

Integrating the above equation with the boundary conditions  $V(x=0) = V_{sf}$  and  $V(x=t_{si}) = V_{sb}$ , we get the expression for electric field, E(x)

The free inversion charge density is

$$Q_{m} = -q \int_{0}^{tsi} ndx = -q N_{ch} \int_{Vsf}^{Vsb} \frac{exp\left(\frac{V - 2\varphi_{B} - V_{CS}}{V_{t}}\right)}{E} dV$$

$$= q N_{ch} \left[ \frac{exp\left(\frac{V_{sf} - 2\varphi_{B} - V_{CS}}{V_{t}}\right) - exp\left(\frac{V_{sb} - 2\varphi_{B} - V_{CS}}{V_{t}}\right)}{E} \right] \dots (2.13)$$

The inversion capacitance per unit area,  $C_{i} \ \mbox{is defined as}$

$$C_i = \partial Q_m / \partial V_{sf}$$

From eqns. (2.12) and (2.13), we get

۰**۲** -

$$Ci = \frac{qN_{ch} exp\left(\frac{V_{sf} - 2\phi_B - V_{CS}}{V_t}\right)}{\sqrt{\frac{2qN_{ch}}{\epsilon_{si}}} \left[V_t \left\{exp\left(\frac{V_{sf} - 2\phi_B - V_{CS}}{V_t}\right) - exp\left(\frac{V_{sb} - 2\phi_B - V_{CS}}{V_t}\right)\right\} + V_{sf} - V_{sb}\right]}$$

In the weak inversion region,  $V_{sf} < (2\phi_B + V_{CS})$  and  $V_{sb} < (2\phi_B + V_{CS})$ ; therefore eqn.(2.14) can be simplified as,

$$Ci = C'_{d} \exp\left(\frac{V_{sf} - 2\varphi_{B} - V_{CS}}{V_{t}}\right) \qquad (2.15)$$

where,

$$C'_{d} = \frac{qN_{ch}}{\sqrt{2qN_{ch}(V_{sf} - V_{sb}) / \varepsilon_{si}}}$$

In depletion and weak inversion regions, the free inversion areal charge density  $Q_m$  is almost zero and the front surface potential is constant from source to drain so that it can be taken as

$$V_{sf} = 2\varphi_{B} + \frac{\left[V_{GS} - (V_{th0} - \Delta V_{th})\right]}{\eta}$$

With this expression of  $V_{sf}$ , eqn. (2.15) now becomes,

$$Ci = C'_{d} \exp\left(\frac{V_{GS} - (V_{th0} - \Delta V_{th}) - \eta V_{CS}}{\eta V_{t}}\right) \qquad (2.16)$$

Here,  $\eta = \frac{\widetilde{C}_{box}}{\widetilde{C}_{ox}}$

-

While the eqn. (2.16) is valid in the weak inversion region, it can still be substituted in eqn.(2.10) to obtain  $C_{gc}$  in the strong inversion region, because in that region, depletion layer and inversion layer capacitances are larger than the gate oxide capacitance, so that  $C_{gc}$  can be taken as  $C_{fox}$  [17] and so eqn. (2.16) does not effect the accuracy of eqn. (2.10).

Substituting eqn. (2.16) into eqn. (2.10), we get,

$$C_{gc} = -\frac{\partial Q_m}{\partial V_{GS}} = \frac{C_{fox} \tilde{C}_d \exp\left[\frac{V_{GS} - (V_{th0} - \Delta V_{th}) - \eta V_{CS}}{\eta V_t}\right]}{\eta^* C_{fox} + \tilde{C}_d \exp\left[\frac{V_{GS} - (V_{th0} - \Delta V_{th}) - \eta V_{CS}}{\eta V_t}\right]}$$

$$= \frac{\tilde{C}_{d} \exp \left[\frac{V_{GS} - (V_{th0} - \Delta V_{th}) - \eta V_{CS}}{\eta V_{t}}\right]}{\eta^{*} \left[1 + \frac{\tilde{C}_{d}}{\eta^{*} C_{fox}} \exp \left[\frac{V_{GS} - (V_{th0} - \Delta V_{th}) - \eta V_{CS}}{\eta V_{t}}\right]\right]}$$

(2.17)

Now integrating the above equation with respect to  $V_{GS}$  gives,

**.**

$$-Q_{m} = \int \frac{C'_{d} \exp \left[\frac{V_{GS} - (V_{th0} - \Delta V_{th}) - \eta V_{CS}}{\eta V_{t}}\right]}{\frac{1}{\eta^{*} \left[1 + \frac{C'_{d} \exp \left[\frac{V_{GS} - (V_{th0} - \Delta V_{th}) - \eta V_{CS}}{\eta V_{t}}\right]}{\eta^{*} C_{fox}}\right]} dV_{GS}$$

33

$$= \eta C_{\text{fox}} V_{1} \int \frac{C'_{d} \exp \left[\frac{V_{\text{GS}} - (V_{\text{th}0} - \Delta V_{\text{th}}) - \eta V_{\text{CS}}}{\eta V_{t}}\right]}{\sqrt{\frac{1}{\eta \eta^{*}C_{\text{fox}}} V_{t}} \left[1 + \frac{C'_{d} \exp \left[\frac{V_{\text{GS}} - (V_{\text{th}0} - \Delta V_{\text{th}}) - \eta V_{\text{CS}}}{\eta V_{t}}\right]}{\eta^{*}C_{\text{fox}}}\right]^{dV} GS$$

Which is in the form of  $\int f'(x) / f(x) = \ln f(x)$ ; So we get,

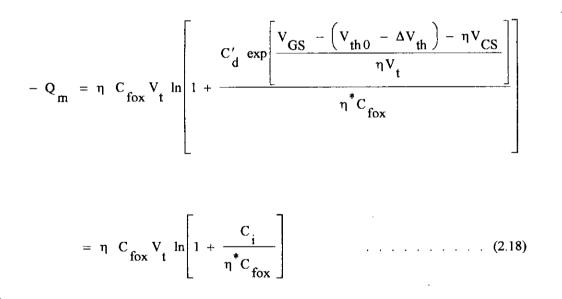

This is the general expression of free inversion areal charge density,  $Q_{m}$ , which is valid in weak, moderate and strong inversions. Derivation of  $Q_{m}$ , of course, involved a drastic approximation which makes the formulation of a comprehensive I-V model possible.

Now in case of strong inversion,  $V_{GS} >> (V_{th0} - \Delta V_{th}) + \eta V_{CS}$  and so we can write,

$$-Q_{m} \approx \eta C_{fox} V_{t} \ln \left[ \frac{C_{i}}{\eta^{*} C_{fox}} \right]$$

$$\approx \eta C_{fox} V_{t} \ln \left[ exp \left\{ \frac{V_{GS} - (V_{th0} - \Delta V_{th}) - \eta V_{CS}}{\eta V_{t}} \right\} \right]$$

$$= C_{fox} \left[ V_{GS} - (V_{th0} - \Delta V_{th}) - \eta V_{CS} \right] \qquad (2.19)$$

In the weak inversion region , where  $V_{GS} \ll (V_{th0} - \Delta V_{th}) + \eta V_{CS}$  , eqn. (2.18) can be approximated as,

$$-Q_{m} \approx \eta C_{fox} V_{t} \times \frac{C_{i}}{\eta C_{fox}}$$

$$= \frac{\eta V_{t}}{\eta} C_{d} \exp\left\{\frac{V_{GS} - (V_{th0} - \Delta V_{th}) - \eta V_{CS}}{\eta V_{t}}\right\} \qquad (2.20)$$

Fig. 2.6 Schematic view of the n-channel region of a SOI-Mosfet under drain bias and the variation of voltage V(y) along the conducting channel.

Since SOI mosfets are a potential candidate for the future ULSI circuitry, it is important to model the current-voltage or I-V characteristics of SOI devices with a view to exploiting their proper application. Here we develop a physics based complete but simple I-V model for an n-channel SOI-Mosfet.

The drain current of any MOS device consists of drift and diffusion components of current as expressed below,

$$I_{DS} = -W\mu Q_m \frac{dV}{dy} - W\mu V_t \frac{dQ_m}{dy} \qquad (2.21)$$

36

٥.

here,

$$W =$$

effective channel width

$\mu =$  mobility of electron

Here we ignored the current component due to the gradient of electron temperature. The first term on the right hand side of eqn. (2.21) is the drift component and the second term is the diffusion component.

# 2.4.2.1 Effective Mobility of Electrons in the Channel

Mobility,  $\mu$  is in fact a complicated function of local electric field and position. The vertical electric field that arises due to the presence of gate voltage, V<sub>GS</sub> can affect the carrier mobility and this effect can be incorporated by the use of  $\mu_n^0$  in place of  $\mu_0^0$ , the maximum low-field mobility where [18]

$$\mu_{n}^{0} = \frac{\mu_{0}}{1 + \theta(V_{GS} - V_{th})}$$

(2.22)

here,  $\theta$  is a fitting parameter, V<sub>th</sub> is the threshold voltage.

An important role that can be played by  $\theta$  is that the effect of source/drain resistance can be lumped into it and so the need for extra elements in circuit simulation can easily be eliminated[19]. Here to mention that as device dimensions are scaled down to the submicrometer regime, the parasitic source/drain series resistances become increasingly significant. They are especially high in fully depleted SOI owing to its thin film nature[20]. Another important modification of carrier-mobility is to be carried out due to the phenomenon of velocity overshoot. As carriers traverse along the conducting channel, they gain energy from the electric field, but their motion is frequently interrupted by collisions with impurities, phonons, crystal defects or other carriers. As the channel length decreases carriers that travel along the channel gain energy while suffer less collisions. Therefore the transient velocity may overshoot its steady-state value. This is the general definition of velocity overshoot phenomenon[18].

At a fixed drain bias, as channel length decreases, the channel electric fields increase and the electric fields in the region near the source also increase. A steep increase of the channel electric field near the source induces the non-local transport effect and so enhances the carrier velocity in the source region. In other words, carriers can gain much more energy in the source-end channel and the velocity overshoot effect becomes apparent. But as the carriers travel a specified distance along the channel, the electron temperature begins to rise and the scattering between mobile electrons and lattice increases, while in turn decreases the carrier velocity, i.e. velocity . overshoot effect gradually vanishes. In fact, carrier velocity overshoot at the drain end does not lead to any observable drain current increase as it only affects the carrier distribution in the post-saturation region [21]. Incorporating the effects at small y (i.e. near the source ) and at large y (i.e. near the drain), the effective mobility in the channel is approximated as,

$$\mu_{\text{eff}} \approx \frac{\mu_{n}^{0}}{1 + \beta E_{y} y \exp(-y / L_{y}) + \alpha E_{y} (1 - \exp(-y / L_{y}))}$$

(2.23)

¢

where,  $E_y = \frac{dV(y)}{dy}$  is the channel electric field  $L_v$  is a fitting constant  $\beta$  is equal to 2/(5U<sub>1</sub>) and U<sub>1</sub> is the equilibrium electron thermal voltage

$$\frac{1}{\alpha} = E_c$$

, the critical field.

#### 2.4.2.2 WEAK INVERSION AND SUBTHRESHOLD CURRENT MODEL :

In weak inversions, a low concentration of electrons are introduced in the channel and the surface potential which has a smaller magnitude, remains constant from source to drain. So the drift component of drain current is negligible in this case and the drain current is dominated by the diffusion current. So from eqns. (2.21) and (2.22) we get,

$$I_{DS} = -W\mu V_t \frac{dQ_m}{dy} \qquad (2.24)$$

For weak inversions,-

$$Q_{m} = -Q'_{m} \exp\left\{\frac{V_{GS} - (V_{th0} - \Delta V_{th}) - \eta V_{CS}}{\eta V_{t}}\right\};$$

here,

$$Q'_m = \frac{\eta V_t}{\eta} C'_d$$

So the above equation becomes,

$$I_{DS} \left[ 1 + \beta E_{y} y \exp(-y / L_{v}) + \alpha E_{y} (1 - \exp(-y / L_{v})) \right] dy = W \mu_{n}^{0} Q'_{m} \exp\left\{ \frac{V_{GS} - (V_{th0} - \Delta V_{th}) - \eta V_{CS}}{\eta V_{t}} \right\} \dots (2.25)$$

Integrating from y=0 to y=L yields,

$$I_{DS} \left[ L + \alpha V_{DS} + E_{y}(0) \left\{ \beta L_{v}^{2} \left( 1 - \exp(-L/L_{v}) \right) - \beta L_{v} L \exp(-L/L_{v}) - \alpha L_{v} \left( 1 - \exp(-L/L_{v}) \right) \right\} \right]$$

=  $W \mu_{n}^{0} Q_{m t}' V_{t} \exp\left\{ \frac{V_{GS} - (V_{th0} - \Delta V_{th})}{\eta V_{t}} \right\} \times \left[ 1 - \exp\left(-\frac{V_{DS}}{V_{t}}\right) \right]$

Since  $L >> L_V$ , the above equation can be approximated as,

$$I_{DS} = \frac{W\mu_n^0 Q'_m V_t \exp\left\{\frac{V_{GS} - (V_{th0} - \Delta V_{th})}{\eta V_t}\right\} \times \left[1 - \exp\left(-\frac{V_{DS}}{V_t}\right)\right]}{L + \alpha V_{DS} + E_y(0)(\beta L_v^2 - \alpha L_v)} \quad \dots \quad (2.27)$$

.

Here,  $E_y(0)$  is the channel electric field as y = 0 and we used it here since at a distance of  $y = L_V$ , the electric field will not deviate very much from the electric field at y = 0.

The factor that accounts for velocity overshoot is  $E_y(0)$  { $\beta L^2_V - \alpha L_V$  } and this being a negative term causes the drain current without overshoot to increase a bit further.

The solution for  $I_{DS}$  considering velocity overshoot is a complicated one. Let us here determine the expression for  $E_y(0)$  in terms of  $I_{DS}$ .

We know from eqn. (2.21), the diffusion current is

$$I_{\rm DS} = -W\mu_{\rm n}^0 V_{\rm t} \frac{dQ_{\rm m}}{dy}$$

$$= -W\mu_n^0 V_t \frac{dQ_m}{dV_{GS}} \cdot \frac{dV_{GS}}{dy}$$

$$= \frac{W\mu_n^0 V_t C'_d}{\eta^*} \exp\left[\frac{V_{GS} - (V_{th0} - \Delta V_{th}) - \eta V_{CS}}{\eta V_t}\right] E_y(y)$$

At y = 0,  $V_{CS} = 0$  and  $E_y(y) = E_y(0)$ ; so that

$$I_{DS} = \frac{W\mu_n^0 V_t C_d'}{\eta^*} \exp\left[\frac{V_{GS} - (V_{th0} - \Delta V_{th})}{\eta V_t}\right] E_y(0)$$

$$\Rightarrow E_{y}(0) = \frac{I_{DS}}{\frac{W\mu_{n}^{0}V_{t}C'_{d}}{\eta^{*}}exp\left[\frac{V_{GS} - (V_{th0} - \Delta V_{th})}{\eta V_{t}}\right]} \qquad (2.28)$$

Solving for  $I_{DS}$  from eqns.(2.27) and (2.28) we get,

$$I_{DS} = \frac{-B + \sqrt{B^2 - 4AC}}{2A}$$

(2.29)

where, A =

$$\frac{\beta L_v^2 - \alpha L_v}{\left[\frac{W\mu_n^0 V_t C_d'}{\eta^*}\right] exp\left\{\frac{V_{GS} - (V_{th0} - \Delta V_{th})}{\eta V_t}\right\}}$$

$$B = L + \alpha V_{DS}$$

$$C = -\left[\frac{W\mu_{n}^{0}\eta V_{t}^{2}C_{d}'}{\eta}\right] \times \exp\left\{\frac{V_{GS} - (V_{th0} - \Delta V_{th})}{\eta V_{t}}\right\} \times \left[1 - \exp\left(-\frac{V_{DS}}{V_{t}}\right)\right]$$

This is the required expression for subthreshold current considering the velocity overshoot phenomenon.

### 2.4.2.3 <u>STRONG INVERSION AND DRAIN CURRENT MODEL FOR A</u> NORMALLY ON SOI MOSFET

In the strong inversion region, the drain current is dominated by the drift current , i.e.

$$I_{\rm DS} \cong -W\mu_{\rm eff}Q_{\rm m}\frac{dV}{dy}$$

....(2.30)

By the use of eqn. (2.19) for expression of  $Q_m$  in strong inversion, we get

$$I_{DS} = \frac{W\mu_n^0 C_{fox} \left[ V_{GS} - (V_{th0} - \Delta V_{th}) - \eta V_{CS} \right] dv / dy}{1 + \beta E_y y \exp(-y / L_v) + \alpha E_y (1 - \exp(-y / L_v))}$$

$$\Rightarrow I_{DS} \left[ 1 + \beta E_y y \exp(-y / L_v) + \alpha E_y + \alpha E_y \exp(-y / L_v) \right] dy = W_{\mu n}^0 C_{fox} \left[ V_{GS} - (V_{th0} - \Delta V_{th}) - \eta V_{CS} \right] dv$$

Integrating the above equation from y = 0 to y = L and simplifying we get,

$$I_{DS} \left[ L + \alpha V_{DS} + E_{y}(0) \left\{ \beta L_{v}^{2} - \alpha L_{v} \right\} \right] = W \mu_{n}^{0} C_{fox} \times \left[ \left\{ V_{GS} - (V_{th0} - \Delta V_{th}) \right\} V_{ds} - \frac{\eta}{2} V_{DS}^{2} \right]$$

$$\Rightarrow I_{DS} = \frac{W\mu_{n}^{0}C_{fox} \left[ \left\{ V_{GS} - (V_{th0} - \Delta V_{th}) \right\} V_{ds} - \frac{\eta}{2} V_{DS}^{2} \right]}{L + \alpha V_{DS} + E_{y}(0) \left\{ \beta L_{v}^{2} - \alpha L_{v} \right\}} \qquad (2.31)$$

Since  $(\beta L_V^2 - \alpha L_V)$  is negative, this equation tells that the drain current increases as channel length decreases due to overshoot effect. For long channel devices, the velocity overshoot effect can be neglected.

Now from eqn. (2.30) for y = 0,

$$I_{DS} = W \mu_n^0 C_{fox} \{ V_{GS} - (V_{th0} - \Delta V_{th}) \} E_y(0) \qquad (2.32)$$

From eqns. (2.31) and (2.32) we can solve for  $I_{DS}$  as

$$I_{DS} = \frac{-A_2 + \sqrt{A_2^2 - 4A_1A_3}}{2A_1} \qquad (2.33)$$

Where,

$$A_{1} = \frac{\beta L_{v}^{2} - \alpha L_{v}}{W \mu_{n}^{0} C_{fox} V_{GST}}$$

$$A_2 = L + \alpha V_{DS}$$

$$A_{3} = -W\mu_{n}^{0}C_{fox} \left[ V_{GST}V_{DS} - \frac{\eta}{2}V_{DS}^{2} \right]$$

$$V_{GST} = V_{GS} - (V_{th0} - \Delta V_{th})$$

When  $V_{DS}$  reaches the saturation voltage  $V_{DSAT}$  and beyond, pinch-off occurs and the device is operated in the saturation mode. Then the saturation drain current becomes,

$$I_{\text{DSAT}} = \frac{-A'_2 + \sqrt{A'_2^2 - 4A'_1A'_3}}{2A'_1} \qquad (2.34)$$

where,

$$A'_{1} = \frac{\beta L_{v}^{2} - \alpha L_{v}}{W \mu_{n}^{0} C_{fox} V_{GST}}$$

$$A'_{2} = L + \alpha V_{DSAT}$$

$$A'_{3} = -W \mu_{n}^{0} C_{fox} \left[ V_{GST} V_{DSAT} - \frac{\eta}{2} V_{DSAT}^{2} \right]$$

$$V_{GST} = V_{GS} - (V_{th0} - \Delta V_{th})$$

The saturation drain voltage,  $V_{\text{DSAT}}\,$  is generally given as,

$V_{DSAT}$  =  $V_{GS}$  - (  $V_{th0}$  -  $\Delta V_{th}$  )

G

#### CHAPTER – 3

#### **RESULTS AND DISCUSSION**

Following the theoretical analysis presented in chapter-2, the models for various significant quantities like front surface potential, threshold voltage and threshold voltage shift, drain current etc. are simulated and tested on a microcomputer by computer programs. These programs written in Borland C<sup>++</sup>, provide a lucid and flexible simulation-environment so that each model can be easily checked and tested from diverse point of view.

Firstly we simulate the expression for front-surface electric-potential  $V_{sf}(y)$ , as presented in equation (2.5). The device used for the study is a fully-depleted nchannel SOI MOSFET with a channel doping of  $10^{17}$  cm<sup>-3</sup>. The silicon-filmthickness of this device is 85nm with front oxide and buried oxide thickness of 10nm and 400nm respectively. The first simulation is set to trace the front surface potential,  $V_{sf}(y)$  along the channel length or in the direction of y; (in this case we have chosen a channel length of 0.3 µm). The variation of surface potential is calculated for three different source- to- drain voltages, e.g.  $V_{DS}=50mv$ ,  $V_{DS}=1V$  and  $V_{DS}=2V$ . As depicted in Fig. 3.1, it is observed that the effective channel length shrinks or contracts as the drain voltage increases. Here we define the 'effective channel length' as the length along the maskchannel where the surface potential is at best 10% higher than the minimum surface potential. This phenomenon i.e. the channel contraction due to increasing drain voltage in a short-channel device is generally termed as *channel length modulation*. This effect has been tested for three different channel lengths (Fig.3.2), e.g. L=0.6 $\mu$ m, L=0.3 $\mu$ m and L=0.2 $\mu$ m, with a particular value of V<sub>DS</sub>. The channel modulation by drain voltage is seen to become prominent in short channel devices. This channel-length-modulation effect has been clearly depicted in the following two Figures, Fig. 3.3 and Fig.3.4. In Fig.3.3, the channel-length-modulation has been defined graphically, where effective channel length is  $(L - l_s - l_d)$ ; here L is the mask channel length,  $l_s$  is the distance to the nearest point from source where the surface potential is down within the range of 110% of the minimum potential and  $l_d$  is the similar distance from drain,(in this connection, we have at first calculated the minimum surface potential V<sub>sfomin</sub> by the use of eqns. (2.5) and (2.7).

As shown in Fig. 3.4, the modulated channel length goes on in the downward direction as the drain voltage is gradually increased (and this was predicted in Fig.3.1). Also observed is that the modulated channel length becomes very short for the shorter channel device; this may cause serious trouble considering punch-through (merging of drain depletion region with source). So the doping concentration of a shorter channel device has to be increased than that of its longer counterpart.

Simulating the surface-potential model against position along the channel with  $T_{si}$  as the parameter reveals an interesting result (Fig. 3.5). A device with larger silicon-film thickness (100nm) has a more contracted or modulated channel length than the one with smaller  $T_{si}$ . This is an important finding about silicon film thickness and more of such findings are revealed later in our research.

Position along the channel length, y, in micron

Fig. 3.2 Surface Potential for different channel lengths

49

Fig. 3.3 Definition of channel length modulation

,

50

Fig. 3.4 Effect of channel length modulation on as function of drain voltage

4

,

Position along the channel length, y, in micron

Fig. 3.5 Front surface potential for different silicon film thickness

The SOI threshold voltage model as expressed by equations (2.6) and (2.8), is simulated to observe its dependence on channel length (L), silicon-filmthickness (Tsi) and drain voltage (VDS). As depicted in Fig. 3.6, threshold voltage, Vth, is seriously affected at reduced channel lengths. For the long channel devices, threshold voltage is a fixed quantity; but as the device is continually scaled down, its threshold voltage tends to shift downward, a phenomenon known as threshold voltage shift or threshold voltage roll-off. A significant relation between threshold voltage of a short-channel device with its silicon-film thickness, Tsi is observed here; as seen in Fig. 3.6, threshold voltage is more seriously affected in case of a device with larger T<sub>si</sub> than the one with smaller T<sub>si</sub>. Here we vary T<sub>si</sub> from 60nm to 100nm in steps of 20nm each. Thicknesses of the front oxide and buried oxide layers are 10nm and 400nm respectively and the channel doping  $N_{ch}$  is  $10^{17}$  cm<sup>-3</sup>. The degree of doping used here is a reasonable one, since higher channel doping (generally  $N_{ch} \ge 5 \times 10^{16} \text{ cm}^{-3}$ ) is an inevitable tool to avoid punch-through in the deep submicrometer device. The drain voltage used is 50mV. An important choice we make here and also for all the devices throughout the research is for the material of the gate; since the flat-band voltage in case of an n<sup>+</sup> polycrystalline silicon (or polysilicon in short) is a deep-negative quantity (about-1.15 volts), it aids in lowering of the long channel threshold voltage,  $V_{th0}$  of the n-channel device (as indicated by equation (2.6)). This is why n<sup>+</sup>- polysilicon is selected as the gate material of our devices.

The effect of silicon-film thickness on the threshold voltage is presented in another way (Fig. 3.7). Using the equation (2.8), we calculate the threshold voltage roll-off,  $\Delta V_{th}$  and plot it against channel length, with  $T_{si}$  as the parameter. The figure 3.7 clearly demonstrates the dependence of the  $\Delta V_{th}$  on  $T_{si}$  as predicted before; the device with larger  $T_{si}$  shows a higher  $\Delta V_{th}$  or threshold voltage shift. Smaller  $T_{si}$  in fact helps to maintain a higher doping concentration in the channel that in turn is necessary to ensure the fullydepleted condition in the subthreshold regime, especially in case of a very short channel device. Silicon films of larger thickness fail to ensure such condition and so are notoriously prominent in sense of threshold voltage roll-off. So we see here that the shift in threshold voltage from device to device include not only Short Channel Effects (SCE), but also contributions due to  $T_{si}$  variations and the thinner the  $T_{si}$ , the better the performance.

Threshold voltage variation against effective channel length with drain voltage as the parameter is also simulated, using the same equations involved in the previous simulation (eqn. (2.6) & eqn. (2.8)). The results are depicted in Fig.3.8; here it is seen that the threshold voltage in the submicron devices is a function of not only the channel length or silicon-film thickness, but also the drain voltage,  $V_{DS}$ . For a device applied with higher drain voltage shows a higher roll-off in its threshold voltage and this is obviously a result of DIBL or drain induced barrier lowering effect. As the channel length is reduced further, the drain depletion region further strengthens its interaction with the source region and the DIBL effect is more pronounced; in turn the subthreshold performance is hampered and  $V_{th}$  is lowered. The same event is simulated in another fashion (Fig. 3.9). Here the threshold voltage-profile is plotted against

drain voltage for two different channel lengths, e.g. L= $0.3\mu$ m and L= $0.5\mu$ m. As predicted above, the lower channel length device is associated with lower threshold voltage and this device suffers more for drain voltage variation than the device with longer channel length.