## DESIGN AND IMPLEMENTATION OF A NEURAL NETWORK BASED REACTIVE POWER CONTROLLER

#### A THESIS SUBMITTED TO THE DEPARTMENT OF ELECTRICAL AND ELECTRONIC ENGINEERING, BUET, IN PARTIAL FULFILLMENT OF THE REQUIREMENT FOR THE DEGREE OF MASTER OF SCIENCE IN ENGINEERING

BY MD. ZIAUR RAHMAN

## DEPARTMENT OF ELECTRICAL AND ELECTRONIC ENGINEERING BANGLADESH UNIVERSITY OF ENGINEERING AND TECHNOLOGY

## DEDICATED TO MY PARENTS THEY GAVE AWAY THEIR TODAYS FOR MY TOMORROWS

## DECLARATION

I hereby declare that this thesis work has not been submitted alsowhere for the award of any degree or diploma or for publication.

Countersigned:

(Dr. S M Lutful Kabir)

Hian f 97 20

(Md. Ziaur Rahman)

The thesis titled, "Design and Implementation of a Neural Network Based Reactive Power Controller", submitted by Md. Ziaur Rahman, Roll No. 930613P, Registration No. 88157 of M. Sc. in Engineering has been accepted as satisfactory in partial fulfillment of the requirements for the degree of Master of science in Electrical Engineering.

Board of Examiners:

Dr. S M Lutful Kabir

Professor

Department of Electrical & Electronic Engg. BUET, Dhaka-1000

20/3/97 Dr. Md. Quamrul Ahsar

Professor and Head Department of Electrical & Electronic Engg. BUET, Dhaka-1000

3.

Dr. Joarder Kamfuzzaman Assistant Professor Department of Electrical & Electronic Engg. BUET, Dhaka-1000

4.

Dr. Abdur Rahim Mollah Professor Department of Electrical & Electronic Engg. BIT, Khulna Chairman (Supervisor)

Member (Ex-Officio)

Member

Member (External)

# CONTENTS

| Ackı | nowledgments                           | i  |  |

|------|----------------------------------------|----|--|

| Abst | ract                                   | ii |  |

| List | of figures                             | iv |  |

| List | of Abbreviations                       | vi |  |

|      |                                        |    |  |

| CHA  | APTER 1: INTRODUCTION                  |    |  |

| 1.1  | Introduction                           | 1  |  |

| 1.2  | Fundamentals on power factor           |    |  |

|      | 1.2.1 Power factor                     | 4  |  |

|      | 1.2.2 Consumption of reactive energy   | 7  |  |

|      | 1.2.3 Necessity of better power factor | 7  |  |

| 1.3  | Conventional PFI plant                 |    |  |

| 1.4  | Thesis objective and layout            | 9  |  |

|      |                                        |    |  |

| СНА  | APTER 2: DESIGN AND TRAINING OF THE    |    |  |

|      | NEURAL NETWORK                         |    |  |

| 2.1  | Introduction                           | 11 |  |

| 2.2  | Back propagation algorithm             |    |  |

|      | 2.2.1 BPN operation                    | 11 |  |

|      | 2.2.2 Mathematical analysis on BPN     | 14 |  |

|      | 2.2.3 BPN features                     | 21 |  |

| 2.3  | BPN for reactive power controller      |    |  |

|      | 2.3.1 Input variables of the network   | 24 |  |

|      | 2.3.2 Output variable of the network   | 25 |  |

|     | 2.3.3 Hidden u    | nits of the network            | 27 |

|-----|-------------------|--------------------------------|----|

| 2.4 | Convergence of    |                                |    |

|     | 2.4.1 Hidden u    | nits                           | 28 |

| 2.5 | BPN with piece    | wise linear activation         |    |

|     | 2.5.1 Segmenti    | ng the sigmoid function        | 32 |

|     | 2.5.2 Training    | of the network                 | 34 |

|     | 2.5.3 Converge    | nce of the network             | 36 |

| 2.6 | Sensitivity analy | rsis of the network            | 40 |

| СНА | PTER 3: IN        | PLEMENTATION OF THE            |    |

|     | NI                | EURAL NETWORK                  |    |

| 3.1 | Introduction      |                                | 42 |

| 3.2 | Control algorith  | n                              | 42 |

| 3.3 | Circuit impleme   |                                |    |

|     | 3.3.1 Input sign  | nal conditioning circuit       |    |

|     | 3.3.1.1           | Current sensing unit           | 44 |

|     | 3.3.1.2           | Power factor sensing unit      | 46 |

|     | 3.3.2 Simulatio   | n of activation function       |    |

|     | 3.3.2.1           | Mathematical Analysis          | 48 |

|     | 3.3.2.2           | Implementation                 | 50 |

|     | 3.3.3 KVAR co     | ntrol circuit                  |    |

|     | 3.3.3.1           | Function of the IC's           | 54 |

|     | 3.3.3.2           | Elimination of low KVAR demand | 58 |

|     | 3.3.4 Capacitor   | switching circuit              | 61 |

|     |                   |                                |    |

.

.

· · · ·

### CHAPTER 4: RESULTS

| 4.1        | Introduction                                                  | 63         |

|------------|---------------------------------------------------------------|------------|

| 4.2        | Performance testing on NN modules                             |            |

|            | 4.2.1 Testing on input signal conditioning unit               | 63         |

|            | 4.2.2 Testing on hidden nodes                                 | 65         |

|            | 4.2.3 Testing on neural network                               | 70         |

|            | 4.2.4 Testing on KVAR control and capacitor switching circuit | 70         |

| 4.3        | Performance test on NN based RPC                              |            |

|            | 4.3.1 Experimental setup                                      | 73         |

|            | 4.3.2 Experimental data                                       | <b>7</b> 6 |

| 4.4        | Results                                                       | 77         |

| 4.5        | Cost analysis                                                 | 80         |

| СНА        | APTER 5: CONCLUSION                                           |            |

| 5.1        | Conclusion                                                    | 81         |

| 5.2        | Further works                                                 | 82         |

| REF        | ERENCES                                                       | 84         |

| APP        | ENDICES                                                       |            |

| Appe       | endix-1                                                       | A-1        |

| Appe       | Appendix-2                                                    |            |

| Appe       | Appendix-3                                                    |            |

| Appe       | Appendix-4                                                    |            |

| Appendix-5 |                                                               | A-19       |

| Appendix-6 |                                                               | A-26       |

| Appendix-7 |                                                               |            |

|            |                                                               |            |

## ACKNOWLEDGMENT

The author reaffirms his indebtedness to Professor S M Lutful Kabir for his continuous supervision and inspiration to carry through this research. Cooperation from all the members of the electrical department is also appreciated.

#### **ABSTRACT**

Neural networks (NN) and their applications are creating immense interest among Electrical Engineers in every fields. Recent researches in this line are concentrated basically within two areas; implementation of NN and successful application of NN in various fields. This research work deals with both of these aspects of NN.

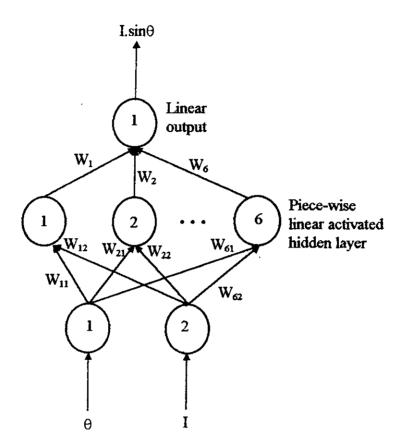

Trends on implementing NN, now a days, are dependent on VLSI technology utilizing the nonlinear operating regions of transistors within very small signal inputs. This research investigates an alternate way to implement analog NN with the simplest of electronic tools like resistors, diodes, buffers and analog adders where VLSI technology can be by-passed. Applications of NN in Power System Engineering has introduced a new dimension. Compared to other electrical fields, power system deals with larger signal sensing and interfacing; also unwanted signal spikes and harmonics in the power line may be vulnerable to small signal sensitive VLSI developed NN. Considering this, an analog NN based Reactive Power Controller (RPC) is designed and implemented in this project. In practice the microprocessor controlled RPC's are widely used. The main function of an RPC is to sense the amount of reactive power required by the system to improve its power factor. An analog NN based RPC has been locally designed and implemented having two input, six hidden and one output node capable of performing nonlinear function mapping;  $X_1$  sin $\theta$  in this particular case, where  $X_1$  and  $\theta$  are the two inputs. The sigmoid function is approximated to piece-wise linear (PWL) and off line training using Back propagation algorithm was used. A unique method has

been developed to implement the weights together with the PWL function with few resistance, diodes, buffers and an analog adder. A technic has been introduced to by-pass the need of amplifiers for constructing the weights. The performance of the developed RPC has been compared with an equivalent microprocessor based RPC. And the developed RPC has been found to be superior than the conventional one. Moreover, the developed RPC based on the implemented NN module approximately reduces the production cost by ten times in comparison to the microprocessor controlled RPC.

# LIST OF FIGURES

| 1.1   | A graphical representation of power factor                            | 5  |

|-------|-----------------------------------------------------------------------|----|

| 2.1   | The general backpropagation network architecture                      | 12 |

| 2.2   | The BPN network with suffix                                           | 15 |

| 2.3   | Hypothetical error surface showing global and local minimum           | 23 |

| 2.4   | A 3-D mapping of the inputs with the output                           | 26 |

| 2.5   | The correlation between output and target values of the test patterns | 29 |

| 2.6   | Response of node (1-4)                                                | 30 |

| 2.7   | BPN module for the reactive power controller                          | 31 |

| 2.8   | Approximating sigmoid to piece-wise linear function                   | 33 |

| 2.9   | The BPN architecture of the neural network module with PWL            | 35 |

| 2.10  | The correlation between output and target values of the test patterns | 37 |

| 2.11  | Response of node (1-6)                                                | 38 |

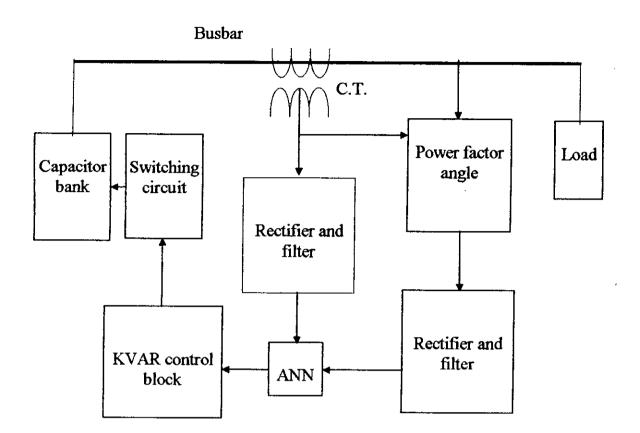

| 3.1   | Line diagram of the neural network based RPC                          | 43 |

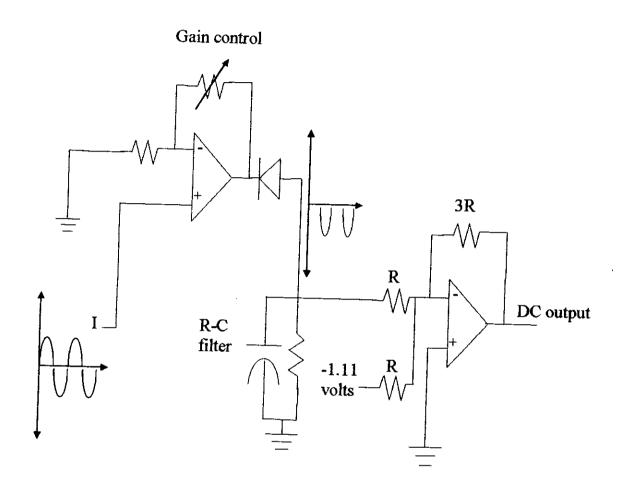

| 3.2   | The rectifier-filter circuit for the current                          | 45 |

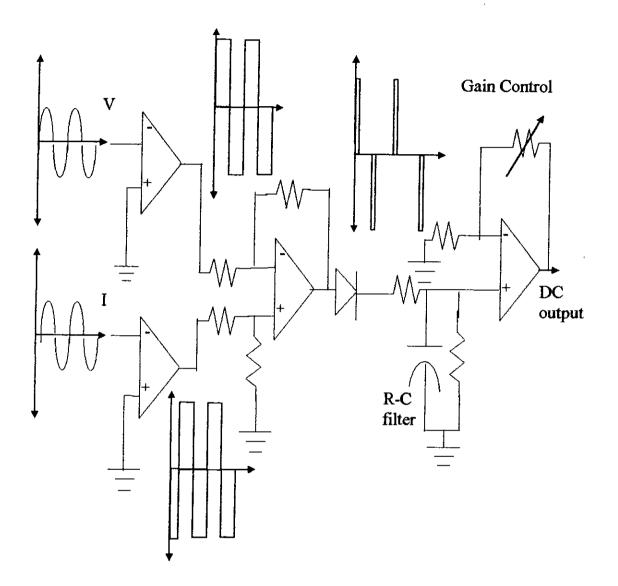

| 3.3   | Rectifier-filter circuit for power factor sensing                     | 47 |

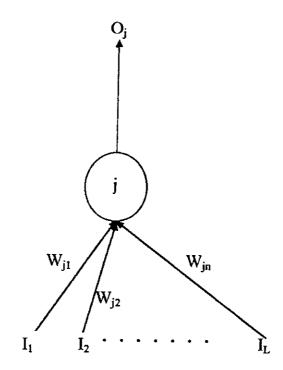

| 3.4.a | j-th node of the hidden layer                                         | 49 |

| 3.4.b | PWL function of the hidden layer                                      | 49 |

| 3.5   | A simple voltage divider circuit                                      | 51 |

| 3.6   | Internal representation of IC LM3914                                  | 55 |

| 3.7   | The pin diagram of 74LS148                                            | 57 |

| 3.8   | The logic block prohibiting the KVAR control circuit to operate       |    |

|       | at very low KVAR demand                                               | 59 |

| 3.9   | The block diagram of KVAR control circuit                             | 60 |

| 3.10  | Capacitor switching circuit                                           | 62 |

| 4.1   | Experimental setup for testing input signal conditioning unit | 64  |  |

|-------|---------------------------------------------------------------|-----|--|

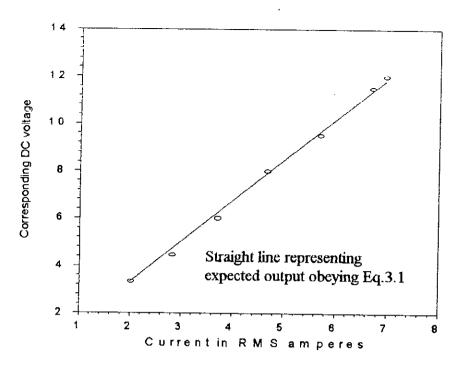

| 4.2.a | Response of current sensing unit                              | 67  |  |

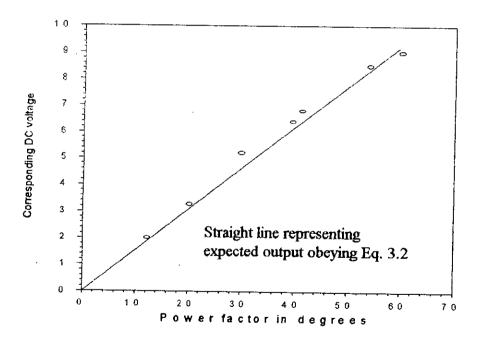

| 4.2.b | Response of power factor sensing unit                         | 67  |  |

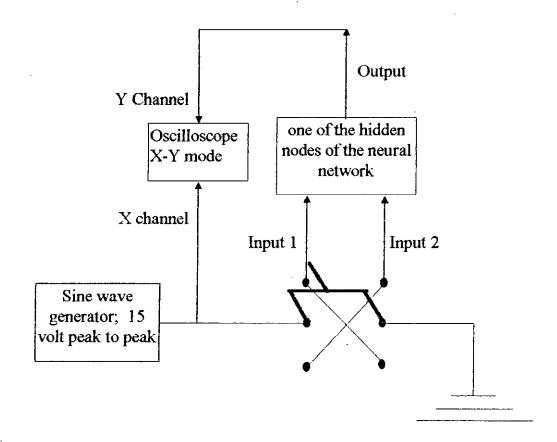

| 4.3   | Test setup for hidden nodes                                   | 68  |  |

| 4.4a  | Response of node 4 with input 2 grounded                      | 69  |  |

| 4.4.b | Response of node 4 with input 1 grounded                      | 69  |  |

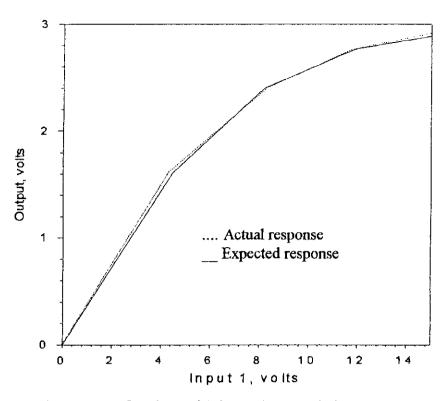

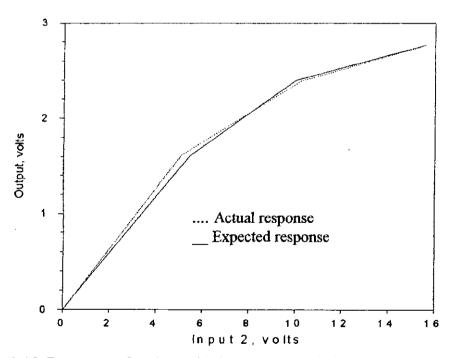

| 4.5   | Comparison between expected and actual output                 | 72  |  |

| 4.6   | Experimental setup for performance test of NN based RPC       | 75  |  |

| 4.7   | The overall response of NN based RPC                          | 79  |  |

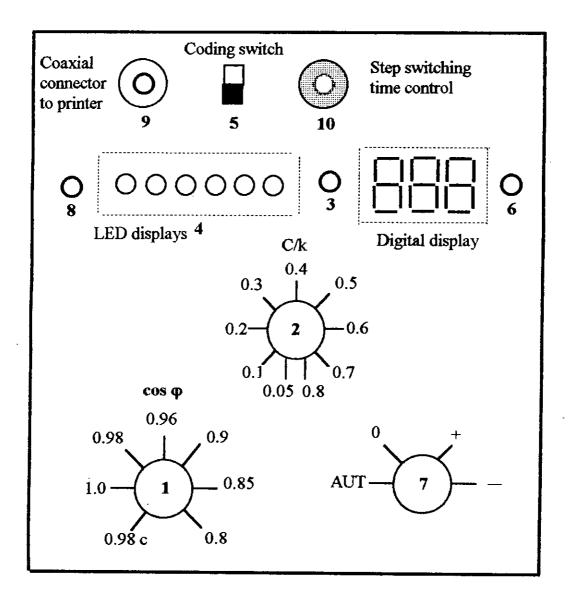

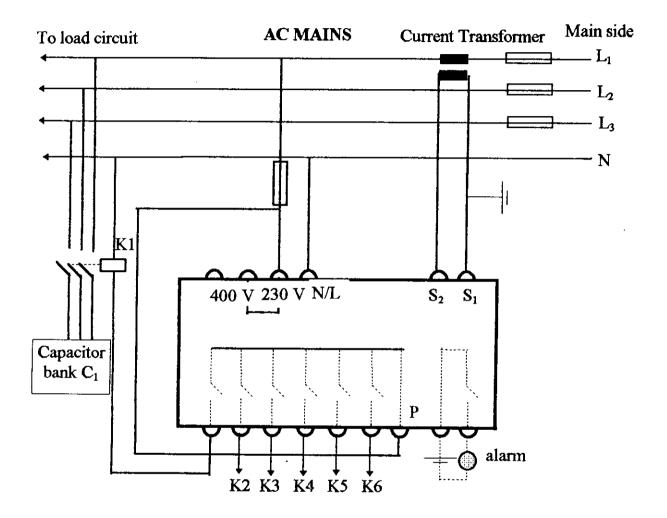

| A.1.1 | Main features of RM 9606 type microprocessor based            |     |  |

|       | RPC controller                                                | A-2 |  |

| A.1.2 | Circuit diagram of RM 9606 connected with the line bus        | A-9 |  |

.

v

.

.

.

.

# LIST OF ABBREVIATIONS

- BPN Back Propagation Network

- C.T. = Current Transformer

- GDR = Generalized Delta Rule

- KVAR = Kilo Volt Ampere Reactive

- LED = Light Emitting Diode

- NN = Neural Network

- PFC = Power Factor Controller

- PFI = Power Factor Improvement

- PWL = Piece-Wise Linear

- RPC = Reactive Power Controller

- VLSI = Very Large Scale Integration

- $\mu P = MicroProcessor$

- $\mu PC = MicroProcessor controller$

# CHAPTER ONE

# INTRODUCTION

.

### **1.1 INTRODUCTION**

Applications of artificial neural network have ushered a new dimension in the field of engineering; especially in industrial control systems. The neural networks try to mimic the nerve system in a mammalian brain into a mathematical model. The brain is a large-scale system connecting many neural cells called neuron. It has many excellent characteristics: parallel processing of information, learning function, self organizing capabilities and so forth [1],[2]. The brain can also provide an associative memory [2] and is good for information processing such as pattern recognition [3]. In artificial neural network, a model of the brain, connects many linear or nonlinear neuron models and process information in a parallel distributed manner [4]. In conventional single processor Von Neumann computers, the speed of computation is limited by the propagation delay of the transistors. Because of their massively parallel nature, neural network can perform computation at much higher speed [1]. In addition, the neural network has many interesting and attractive features. Neural networks have learning and self organization capabilities. Therefore, neural network can adapt to changes in data, learning the characteristics of the input signal. That is, neural network can learn a mapping between an input and output space and synthesize an associative memory that retrieves the appropriate output when presented with the input and generalizes when presented with new inputs [5]. Moreover, because of their nonlinear nature. neural network can perform functional approximation and signal filtering operations that are beyond optimal linear techniques [3]. Recently, many researchers have developed neural networks as new tools in many fields such as pattern recognition, information processing, design, planning, diagnosis, and control. This thesis work develops a hybrid system, a neural network based reactive power controller, as an example of a key technology in the future.

Most of the works done, so far, in industrial control systems are simulated by software programs or fabricated using VLSI technology [6]. The software simulation needs a microprocessor and usually takes a long period of time to execute the huge number of computations involved in the operation of the network. Several researches have adopted hardware implementations to realize such network [7]-[11]. During the past few years, various researchers have begun addressing analog and digital hardware implementations [12]-[21] of certain artificial neural network architecture encompassing a wide variety of applications. Between these two types, analog implementations of artificial neural networks have a number of unique advantages and problems when compared to digital realizations. The primary motivation for implementing a neural network algorithm with analog circuitry is its stand alone capability and capacity to operate on a real time fashion. Countering the above analog advantages is a more extensive list of difficulties and shortcomings. Typically, analog circuits are more complicated to design and more limited in application than digital circuitry [22]. On the other hand, the options that exist for speedy network solutions are digital serial processors known as "neural network coprocessors" [23]-[25]. Using specialized chips that are optimized for matrix multiplication and scaling primitives that underlie most neural models, these digital systems are generally circuit boards that plug onto a host computer bus. Although such systems are capable of simulating networks one or two orders of magnitude faster than the host computer, they remain serial simulators, with network simulation times that grow linearly with interconnection complexity. Hence, analog implementation of neural network seems to be the ultimate choice - at least for the time being.

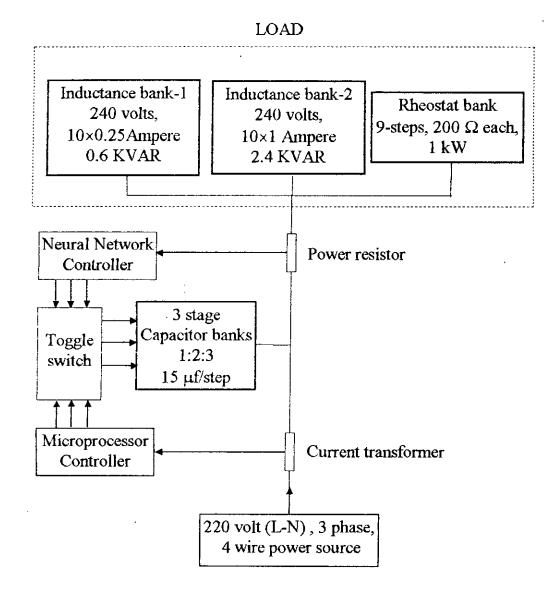

In the proposed research, an analog neural network based reactive power controller will be designed and implemented. Reactive Power Controllers (RPC) are one of the most essential but costly electrical equipment for any industries or production factories. RPC is required in distribution system to improve power factor at a particular bus. It serves as a source of reactive power which is controlled by an automatic power factor controller (PFC) relay. The PFC's are microprocessor [26],[27] based control relay which automatically switches the capacitors in and out of the circuit. Depending on the switching stages of the RPC, its cost varies between one lac Taka for three step switching stages to five lac Taka for twelve step switching stages. This research project implements an RPC based on a feed forward neural network model.

Modeling biological systems presents many challenges to the analog circuit designer. Neural computation is often an emergent property of the system, derived from the way the component elements are organized, and may not be evident in any single element. It is often difficult to separate a neural structure into functional units [28]. Major areas are richly interconnected and computation is intertwined, as a single neural structure subserves a multitude of functions simultaneously [29]. As a result, computational strategies for building collective systems require the development of new architectures and a new design methodology. Mead [30] presented such methodology for implementing biological inspired architectures. This thesis work investigates a new design methodology innovated during the development of the analog neural network for the proposed RPC with the use of simple electronic tools. The neural architecture introduced in this research can be implemented with or without the technical support of VLSI.

### **1.2 FUNDAMENTALS ON POWER FACTOR**

This section will explain some basic terminology on power factor, reactive power and other related topics under three articles.

#### **1.2.1 Power Factor**

Most frequently, an industrial installation is fed from a high-voltage system and comprises :

- a transformer station,

- "resistive" loads, such as ovens, radiators, filament lamps, etc.,

- "inductive" loads, such as transformers, motors, etc.

Let it be assumed that the system is single phase. V will be the voltage in volts at the secondary terminals of the supply transformer that is should to be at full load, and I will be the total absorbed current in amperes.

It should be noted that the Actual or Active Consumed Power  $P_w$ , in watts, is lower than the product: volts × amperes representing the Apparent Power of the installation  $P_a$  in a ratio that is equal to the Power Factor.

$$\frac{P_{w}(watts)}{P_{\bullet}(VA)} = \cos \varphi < 1 \qquad \dots \qquad \dots \qquad \dots \qquad (1.1)$$

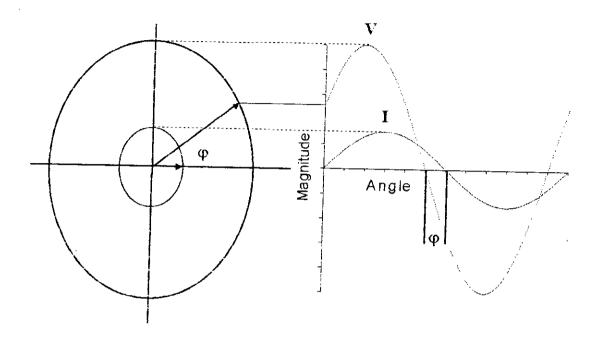

The power factor is graphically represented by the cosines of the angle obtained by the difference in phase between current and voltage; the angle represents the lag between I and V. Figure 1.1 gives a graphical example of power factor.

Figure 1.1  $\Lambda$  graphical representation of Power Factor.

The cos depends only on the characteristics of the load and on their operating conditions (type of motor, speed, load); it is independent of the efficiency of the loads. The loads of the "inductive" type absorb :

- an active power  $P_W = V.I. \cos\varphi$  (watts);

- a reactive power  $P_R = V.I.sin\phi$  (VA react.).

The Apparent Power  $P_{ab}$  equal to the product  $V \times I$ , represents the geometrical sum of the active and reactive powers. The Active Power  $P_W$  is integrally converted into work and heat (losses), being measured with a suitable watt-meter. The active energy  $W_a$  which corresponds to it is recorded by an active energy meter; it is charged to the consumer by the power supply company. The **Reactive Power**  $P_R$  is the power necessary for the magnetic excitation of the said loads. The reactive energy  $W_r$  which corresponds to it can be recorded by a reactive energy meter. The loads of the "resistive" type absorb active power only; the power factor is equal to unity and  $P_a = P_W$ .

The Average Power Factor of an installation, over a long period of time of operation of the workshops is obtained by means of the angle tangent :

When the tangent is known, trigonometric tables give the value of the corresponding cosp.

#### 1.2.2 Consumption of Reactive Energy

- 1. Motors : These are among the loads which consume the greatest amount of reactive energy.

- 2. Transformers : By design, all transformers consume reactive energy used for the magnetization of their cores.

- 3. Transmission lines : Transmission lines, especially overhead lines, have a comparatively high reactance ( $X_L = 0.3$  to 0.5  $\Omega$ -km/phase). The reactive power which they absorb therefore depends upon the load which they carry according to the following formula :

$$P_R = I^2 X_L (I = line current) ... ... (1.3)$$

Since transmission lines have also capacitive characteristic  $X_C$  delivering a reactive power equal to  $V^2.X_C$  (where V is the service voltage), their consumption of reactive voltage depends only on the load, namely when  $I^2.X_L$  becomes higher than  $V^2.X_C$ .

#### 1.2.3 Necessity of Better Power Factor

The advantage of good power factor are multifold and all result in a substantial economy in the operation of electrical installations.

- 1. cutting down penalties for excessive consumption of reactive energy

- reducing line losses : Even when the resistance of conductors is largely calculated, it always causes watt losses which are added to the active consumption of the installation. These losses are proportional to the square of the current carried which for the same active power, decreases as the power factor is increasing.

- 3. increasing line power carrying-capacity with equal losses : If it is considered that an installation which, further to an extension of its activity for instance, has to carry a higher active power, only the improvement of its power factor will allow such an increase without augmenting line losses and, most often, if the initial power factor is small, without modifying the lines p-ower.

- 4. increasing power available at supply transformers : When the power factor increases, the apparent power for the same active power decreases.

- 5. reducing voltage drop : In overloaded low-voltage distribution lines supplying workshops with a small power factor, voltage drops often occur; these are likely to impair the satisfactory operation of motors, even if the voltage at the transformer output is correct. Switching on a capacitor bank at the end of the lines causes a voltage rise  $\Delta V$  defined by the formula :

Where :

- $X_L =$  line reactance in ohms,

- Q = output of the capacitor bank in KVAR,

- V = rated voltage of capacitor in kV.

Switching on a capacitor bank at the terminals of a transformer causes a voltage rise :

$$\Delta V\% = (Q/P).V_{CC}$$

... ... ... (1.5)

Where :

- Q = output of the capacitor bank in KVAR,

- P = power of transformer in KVA,

- V<sub>CC</sub> = transformer impedance voltage (in percentage).

Such a voltage rise, often necessary at full load, could be disastrous at no load. It is therefore necessary to switch off capacitor banks during light-load conditions.

## **1.3 CONVENTIONAL PFI PLANT**

The previous section has explained the advantage of high power factor and the importance of improving power factor in power system. Power Factor Improvement (PFI) plants are used for this purpose. This section will describe the operation and special features of conventionally used PFI plant. Now-a-days, the most widely used PFI plants are microprocessor controlled. The main features of the microprocessor based PFI controller is described in Appendix-1.

### **1.4 THESIS OBJECTIVE AND LAYOUT**

This research work is a combination of theoretical study and practical implementation. A neural network based reactive power controller will be designed and developed, and finally, the performance of the proposed RPC will be compared with the conventional microprocessor controlled RPC in this thesis. The objective of this thesis is classified in two broad view points presented below.

1. There are many methodologies presented by researchers on the implementation of neural networks. One objective of this research work is to introduce a new technology on implementing analog neural networks using simple electronic tools. It is hoped that the invented methodology will make neural network implementation easier and simpler.

2. Conventional microprocessor controlled relays are pretty costly. This research work will show that neural network based controller relays will perform almost as same as the conventional relays, but the cost will be reduced drastically. The second objective of this project is to propose a new way of controlling power factor relays utilizing the emerging techniques of neural systems.

The thesis layout has been confined within three main chapters. Chapter two describes neural network theories and procedures of design a neural network module for the proposed RPC. Chapter three gives an extensive description of the implementation techniques used in the development of the RPC. The final chapter shows the results of the thesis work and presents the performance of the implemented analog neural network based RPC.

## **CHAPTER TWO**

.

.

# DESIGN AND TRAINING OF THE NEURAL NETWORK

.

م. ۲۰۰۰

### 2.1 INTRODUCTION

This chapter explains the back propagation algorithm and utilizes the algorithm to develop an artificial neural network for the reactive power controller. It also assists to form a theoretical back ground on artificial intelligence, learning algorithm and sensitivity of different parameters on convergence of the network. A neural network module for implementing the proposed RPC is presented in this chapter.

# **2.2 BACK PROPAGATION ALGORITHM**

Several methodologies of the artificial neural network have been developed starting from the perceptron idea of Rosenblatt [31]. Among them, the **Backpropagation network** is one of the most effective versatile tool that is readily applied to a number of diverse problem in artificial neural network. To a large extent, its versatility is due to the general nature of the network learning process. This algorithm has established its popularity over other neural network algorithms; specially in the field of power system analysis. In this present project of developing a reactive power controller based on artificial neural system the BPN algorithm, therefore, becomes a natural choice. In this section the theory of back propagation technic is presented.

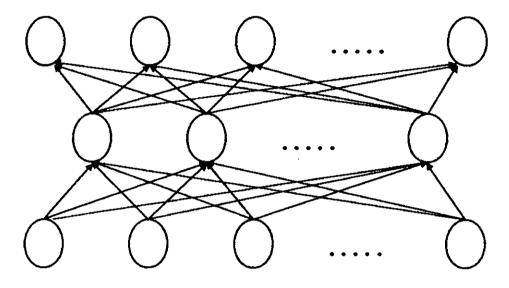

#### 2.2.1 BPN Operation

A summary description of BPN operation is described to illustrate how the BPN can be used to solve complex problems. A three layer back propagation architecture is shown in Figure 2.1. The layers are fully interconnected. When signal patterns are applied to the input layer of the network it propagates upwards

Input applied in parallel

Figure 2.1 The general back propagation network architecture.

towards the output layer through the interconnections of the middle layer, known as hidden layer. It is required that the propagated signal will finally produce a desirable output pattern.

The network learns a predefined set of input-output example pairs by using a two-phase **propagate-adapt** cycle. After an input pattern has been applied as a stimulus to the first layer of the network units, it is propagated through each upper layer until an output is generated. This output pattern is then compared to the desired output, and an error signal is computed for each output unit. The error signals are then transmitted backward from the output layer to each node in the intermediate layer that contributes directly to the output. However, each unit in the intermediate layer receives only a portion of the total error signal, based roughly on the relative contribution the unit made to the original output. This process repeats, layer by layer, until each node in the network has received an error signal that describes its relative contribution to the total error. Based on the error signal received, connection weights are then updated by each unit to cause the network to converge toward a set that allows all the training patterns to be encoded.

The significance of this process is that, as the network trains, the nodes in the intermediate layers organize themselves such that different nodes learn to recognize different features of the total input space. After training, when presented with an arbitrary input pattern, the units of the hidden layers of the network will respond with an active output which is very close to the target value.

As the signal propagates through the different layers in the network, the activity pattern present at each upper layer can be thought of as a pattern with

13

features that can be recognized by units in the subsequent layer. The output pattern generated can be thought of as a feature map that provides an indication of the presence and absence of many different feature combinations at the input. The total effect of this behavior is that the BPN provides an effective means of allowing the total system to examine data patterns that may be untrained and to recognize the corresponding output.

Several researchers have shown that during training, BPNs tend to develop internal relationships between nodes so as to organize the training data into classes of patterns. This tendency can be extrapolated to the hypothesis that all the hidden units in the BPN are somehow associated with specific features of the input pattern as a result of training. Exactly what association is may or may not be evident to the human observer. What is important is that the network has found an internal representation that enables it to generate the desired outputs when given the training inputs. This same internal representation can be applied to inputs that were not used during training. The BPN will classify these previously unseen inputs according to the features they share with the training examples.

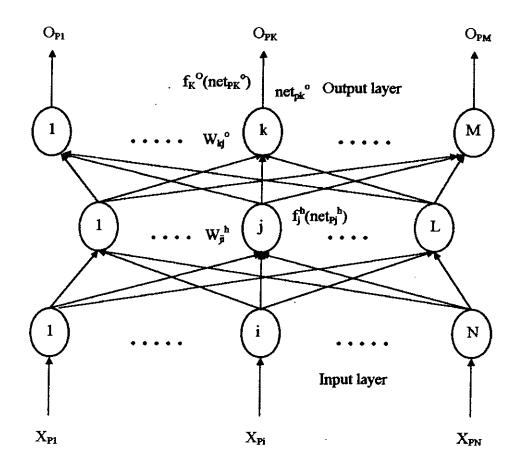

#### 2.2.2 Mathematical Analysis on BPN

In this article, a rigorous mathematical description of BPN will be represented with the detail derivation of **generalized delta rule** (GDR), which is the learning algorithm for the network. Figure 2.2 is the repetition of Figure 2.1 where suffix are included to serve as the reference of the discussion. The BPN is a layered, feedforward network that is fully interconnected by layers. There are no feedback connections and no connections that bypass one layer to go directly to a later layer.

Figure 2.2 The BPN network with suffix

The network will be trained to learn a functional mapping  $\mathbf{y} = \varphi(\mathbf{x}) : \mathbf{x} \in \mathbf{R}^{N}$ ,  $\mathbf{y} \in \mathbf{R}^{M}$ . A set of P vector pairs of the function are  $(\mathbf{x}_{1}, \mathbf{y}_{1}), (\mathbf{x}_{2}, \mathbf{y}_{2}), \dots, (\mathbf{x}_{P}, \mathbf{y}_{P})$ . Considering the mapping to be nonlinear and multidimensional, the iterative version of the simple least square method, called **steepest descent technique**, will be employed.

An input vector,  $\mathbf{x}_{P} = (\mathbf{x}_{P1}, \mathbf{x}_{P2}, \dots, \mathbf{x}_{PN})$ , is applied to the input layer of the network. The input units distribute the values to the hidden layer units. The net input to the jth hidden unit is

where  $w_{ji}^{h}$  is the weight on the connection from the ith input unit. The "h" superscript refers to quantities on the hidden layer. For a defined activation function of this node, the output of this node will be

$$i_{Pj} = f_j^h(net_{Pj}^h)$$

... ... (2.2)

The equations for the output nodes are

$$O_{pk} = f_k^{o}(net_{pk}^{o})$$

... ... (2.4)

where "o" superscript refers to quantities on the output layer. The initial set of weights represents a first guess as to the proper weights for the problem.

The error value at a single output unit "k" is defined as  $\delta_{Pk} = (y_{Pk} - O_{pk})$ , where the subscript "p" refers to the pth training vector, and  $y_{Pk}$  is the desired output value. The error that is minimized by the GDR is the sum of the squares of the errors of all the output units.

To determine the direction in which to change the weights, negative of the gradient of  $E_P$ ,  $\nabla E_P$ , with respect to the weights,  $w_{kj}$  is calculated. Then, the weights can be adjusted in such way so that the total error is reduced.

Considering only for the kth output unit, the component of  $\nabla E_P$  is calculated separately.

ð

$$\frac{\partial E_{P}}{\partial w_{kj}^{o}} = -(y_{Pk} - O_{Pk}) \cdot \frac{\partial f_{k}^{o}}{\partial (net_{Pk}^{o})} \cdot \frac{\partial (net_{Pk}^{o})}{\partial w_{kj}^{o}} \qquad \dots \qquad (2.7)$$

17

The last factor in Eq. (2.7) is

Combining Eqs. (2.7) and (2.8), the negative gradient is

$$-\frac{\partial E_{P}}{\partial w_{kj}^{o}} = (y_{Pk} - O_{Pk}) \cdot f_{k}^{o} \cdot (net_{Pk}^{o}) \cdot i_{Pj} \qquad \dots \qquad \dots \qquad \dots \qquad (2.9)$$

Thus the weights of the output layer are updated according to

The factor  $\eta$  is called the learning rate parameter. It is usually less than 1.

The weight update Eq. (2.10) can be reformed by defining a quantity

The weight update equation thus becomes

$$w_{kj}^{o}(t+1) = w_{kj}^{o}(t) + \eta \cdot \partial_{Pk}^{o} \cdot i_{Pj}$$

... ... (2.13)

So far only the weights of the output layer have been modified. The weights of the hidden layers should need modification as error signal propagates downwards. Going back to Eq. (2.6):

$$E_{P} = 0.5. \sum_{k} (y_{Pk} - O_{Pk})^{2}$$

= 0.5.  $\sum_{k} (y_{Pk} - f_{k}^{o} (net_{Pk}^{o}))^{2}$

= 0.5.  $\sum_{k} (y_{Pk} - f_{k}^{o} (\sum_{j} w_{kj}^{o}.i_{Pj}))^{2}$

Again,  $i_{pj}$  depends on the weights on the hidden layer through Eqs. (2.1) and (2.2). Exploiting this fact to calculate the gradient of  $E_P$  with respect to the hidden layer weights :

$$\frac{\partial E_{p}}{\partial w_{ji}^{h}} = 0.5 \sum_{k} \frac{\partial}{\partial w_{ji}^{h}} (y_{Pk} - O_{Pk})^{2}$$

$$= -\sum_{k} (y_{Pk} - O_{Pk}) \cdot \frac{\partial O_{Pk}}{\partial (\text{net}_{Pk}^{o})} \cdot \frac{\partial (\text{net}_{Pk}^{o})}{\partial i_{Pj}} \cdot \frac{\partial (\text{net}_{Pj}^{h})}{\partial (\text{net}_{Pj}^{h})} \cdot \frac{\partial (\text{net}_{Pj}^{h})}{\partial w_{ji}^{h}} \qquad (2.14)$$

$$= \sum_{k} (y_{Pk} - O_{Pk}) \cdot f_{k}^{o'} (\text{net}_{Pk}^{o}) \cdot w_{kj}^{o} \cdot f_{j}^{h'} (\text{net}_{Pj}^{h}) \cdot x_{Pi} \qquad (2.15)$$

With the help of Eq. (2.15) the weights of the hidden layer are updated.

$$\Delta_{\rm P}.w_{ji}^{\ h} = \eta.f_{j}^{\ h}({\rm net}_{\rm Pj}^{\ h}).x_{\rm Pi}.\sum_{k} (y_{\rm Pk} - O_{\rm Pk}).f_{k}^{\ o}({\rm net}_{\rm Pk}^{\ o}).w_{kj}^{\ o}$$

(2.16)

where  $\eta$  is once again the learning rate.

The weight updating Eq. (2.16) for the hidden layer can be rearranged with the help of  $\delta_{Pk}^{\circ}$  from Eq. (2.12).

$$\Delta_{\mathbf{P}}.\mathbf{w}_{ji}^{\ h} = \eta.\mathbf{f}_{j}^{\ h}.(\mathsf{net}_{\mathbf{P}j}^{\ h}).\mathbf{x}_{\mathbf{P}i}.\sum_{k}\partial_{\mathbf{P}k}^{\ o}.\mathbf{w}_{kj}^{\ o} \qquad \dots \qquad \dots \qquad (2.17)$$

A hidden layer error term similar to  $\delta_{Pk}^{\circ}$  can be defined.

$$\delta_{Pj}^{h} = f_{j}^{h'}(net_{Pj}^{h}). \sum_{k} \partial_{Pk}^{o} . w_{kj}^{o} ... ... ... ... (2.18)$$

Finally, weight update equation for the hidden layer is reduced to the following form :

$$w_{ji}^{h}(t+1) = w_{ji}^{h}(t) + \eta \cdot \delta_{Pj}^{h} \cdot x_{Pi}$$

... ... (2.19)

Before leaving this section there is one point yet to be mentioned. So far the activation function of the nodes were mathematically defined by Eqs. (2.2) and (2.4). These functions require to be differentiable. The simplest of all that can be thought of is surely the straight line function. But for a nonlinear mapping the activation function should have to be nonlinear. The most utilized function prescribed by Hopfield is the **sigmoid function**. It is said that this function closely resembles the biological neuron activation. The mathematical equation of sigmoid function is given below.

$$f_k^{0}(net_{jk}^{o}) = 0.5.(1 + tanh(\lambda.net_{jk}^{o}))$$

... ... (2.20)

The derivative of the sigmoid function can be arranged in the following way

$$f_k^{o'}(net_{jk}^{o}) = f_k^{o}(1-f_k^{o}) = O_{Pk}(1-O_{Pk})$$

... (2.21)

#### 2.2.3 BPN Features

In the previous article relevant mathematical equations required for BPN programming were presented. A computer program "LEARN.FOR" (Appendix-2) has been developed based on those equations. This program will calculate the weights of different layers for network convergence within acceptable error limit. Apart from the mathematical analysis of BPN, certain practical features of its algorithm require special attention which are discussed in this article.

• Training Data : There are no hard and fast rule of selecting the training patterns for BPN learning. Experience is often the best teacher. Yet it should be kept in mind that BPN is very good in generalization but equally bad in extrapolation. If a BPN is inadequately and insufficiently trained on a particular class of input vectors subsequent identification of members of that class may be unreliable. So training vectors should be selected in such way that they will cover the total range of variation the network might experience in practical field. For this present project 55 input patterns were generated which ultimately converged satisfactorily for about 896 patterns.

• Network sizing : The size of the input and output layer are usually dictated by the nature of the application. Determining the number of units to use in the hidden

layer is not so straight forward. The main idea is to use as few hidden layer units as possible. Because this makes the learning process fast and implementation of the network easy. But in case of too much complex mapping, size of the hidden layer may be large for network convergence. Usually networks are initially designed big in size. After learning, the network is pruned by examining the weight values.

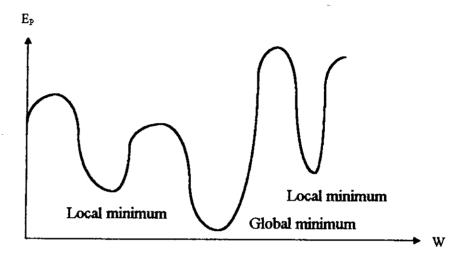

• Initial weights : The initial weights are generally selected at random. Values within  $\pm 0.5$  are chosen frequently. But there is always a possibility that the network may stuck to a local minimum in weight space. Figure 2.3 illustrates this phenomena. Once a network settles on a minimum, whether local or global, learning ceases. If a local minimum is reached, the error of the network may still be unacceptably high. In such a case initial weights need to be changed. Sometime increase in number of hidden layer or learning rate can fix the problem. But if the error keeps within acceptable limit, whether the network has stuck into local or global minimum does not matter.

• Learning rate parameter : Selection of the value of the learning rate parameter,  $\eta$ , has a significant effect on network performance. Usually,  $\eta$  must be a smaller number, on the order of 0.05 to 0.25, to ensure that the network will settle to a solution. A small value of  $\eta$  makes the iteration process slow. Too large value of  $\eta$  may make the network bounce around too far from the actual minimum value. It is often suggested that  $\eta$  initially kept high and as the network proceeds close to convergence, the value of  $\eta$  be reduced. Learning rate can also be modified just like the weights are updated within the computer program. For the present project it has been found that a constant  $\eta$  of 0.2 is good enough for convergence.

22

Figure 2.3 Hypothetical error surface showing global and local minimum.

### **2.3 BPN FOR REACTIVE POWER CONTROLLER**

The preceding section has elaborately explained different aspects of BPN algorithm. In this section total attention will be focused on the project of developing a "Reactive Power Controller" based on BPN.

The mathematical expression for reactive power is

$KVAR = (VOLT.CURRENT.SIN\theta)/1000$  ... ... (2.22)

where,  $\theta$  is the phase angle difference between voltage and current. Hence, it is evident from Eq. (2.22) that the network will have three input and one output variables. The network will converge for a three dimension, nonlinear, multiplication mapping. If the complexity of the network can be reduced to some extent, then the learning procedure of the network as well as its implementation will be much more easier. The following articles are devoted on the manipulation of input and output variables to reduce calculation complexity of the network.

#### 2.3.1 Input Variables of the Network

The three input variables of the network are line voltage (V), load current (I), and the phase angle difference ( $\theta$ ) between V and I. The objective of a reactive power controller is to maintain the power factor of the system within an acceptable range. To perform this, the controller delivers reactive power to the load from a capacitor bank connected in parallel with the load. In a power system, fluctuation of voltage range within a small limit. Moreover, because both the load and the capacitor bank are placed in parallel, any fluctuation of the voltage will equally effect the amount of KVAR demanded by the load as well as the KVAR supplied

by the capacitor bank. So, we can eliminate the necessity of voltage sensing in the input. The phase angle difference,  $\theta$ , can have a positive or negative value depending on whether the current is lagging or leading the voltage. To reduce complexity,  $\theta$  is restricted only to its positive value. A simple module has been designed later to distinguish the lead-lag condition. Generally, in an industry, the power factor varies within 1.0 to 0.6. This practical consideration will limit the variation of  $\theta$  within  $0^{\circ}$  to  $52^{\circ}$ . Again, a power factor above 0.95 is quite acceptable for the power system. So, sensing KVAR for a power factor above 0.95 is not required. This consideration prohibits the variation of  $\theta$  under 18°.

The maximum current sensing capability of the circuit has been limited up to 7 amperes for the time being. Of course, this rating can be enhanced several times with the use of current transformer. Capacitor banks delivers reactive power in discrete mode. There is always a limitation that the capacitor bank cannot deliver reactive power under a certain extent. So, training patterns, where KVAR demand is below unacceptable limit, can be eliminated.

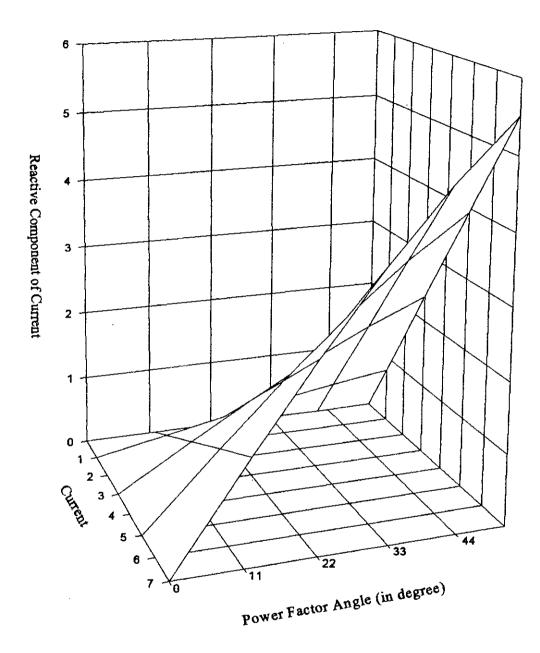

# 2.3.2 Output Variable of the Network

The only one output variable of the network is the KVAR requirement. The target pattern of the output is slightly modified in the computer program LEARN.FOR (Appendix-2) so that the output of the network limits within -0.4 to 0.4. It is focused that if the target pattern resembles a symmetry with the origin, then the net inputs in the hidden layers will be concentrated on the part of the sigmoid function ranging from -0.4 to 0.4. Figure 2.4 shows the graphical mapping of the two input variables with the output variable.

Figure 2.4 A 3-D mapping of inputs with the output.

#### 2.3.3 Hidden Units of the Network

Initially the number of hidden units is arbitrarily chosen to be 4. The activation function of the hidden layers are flat sigmoid (tanh(0.5.net)) function.

Hence, a BPN model has been introduced consisting of two input units, one output unit and 4 units of hidden layer having sigmoid activation function. For the convenience of proper convergence, all the input vectors are made fraction in the computer program LEARN.FOR (Appendix-2). The current vector is divided by an arbitrary constant 9.6 as well as the phase angle is divided by another arbitrary constant 98.7.

### 2.4 CONVERGENCE OF THE NETWORK

The BPN model was trained by 55 input patterns. The patterns were generated by within the program "LEARN.FOR" and was stored in a data file named "OUTPUT.DAT" (Appendix-3). Initial weights were chosen arbitrarily. At the beginning of training the learning rate was kept at 0.2. As learning proceeded and became slower, the learning rate parameter was made a function of error ( $\eta = 40.$ error). The weights of the network after satisfactory convergence are given below :

- Total iteration cycle : 576440

- Final RMS error : 0.00033

- Weights for node  $\theta$ :  $W_{11} = 2.028$ ,  $W_{21} = 0.01$ ,  $W_{31} = 1.048$ ,  $W_{41} = 15.535$

- Weights for node I :  $W_{12} = 0.6044$ ,  $W_{22} = 2.968$ ,  $W_{32} = 2.791$ ,  $W_{42} = 4.81$

- Weights at output :  $W_1 = 4.220, W_2 = 5.976, W_3 = -7.4676, W_4 = -0.6$

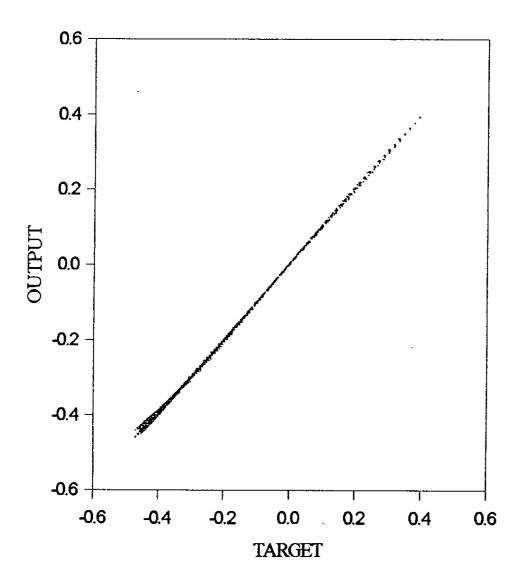

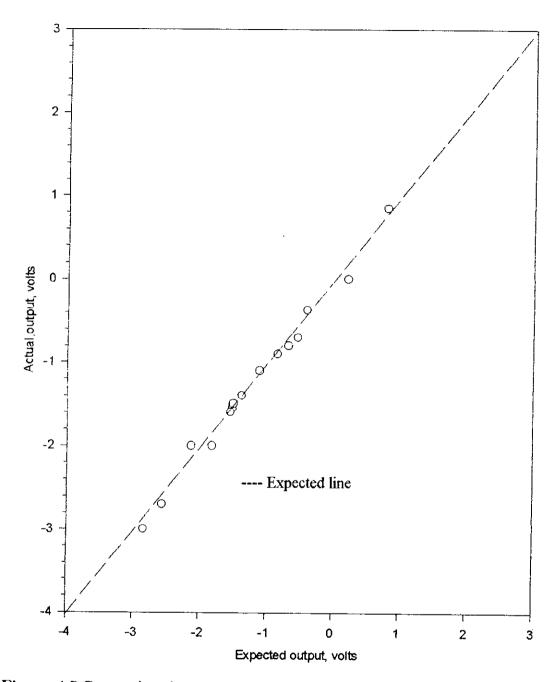

To check the convergence of the learned weight, another computer program "CHECK.FOR" (Appendix-4) is developed. This program checked the weights for 896 generated test pattern and found 844 of those data had errors less than 0.001. Figure 2.5 shows the correlation between target and output values.

For a perfect convergence the relation between target values and output values should have abided a perfect equality relation; i.e. target = output. The graphical result show that the gradient of the best fit line is 1.002 and the line constant is 0.0008756. This result indicates that output  $\approx$  target. So the obtained converging result is satisfactory.

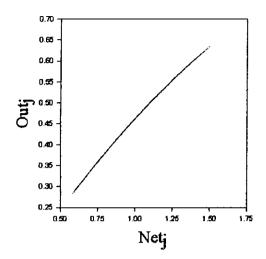

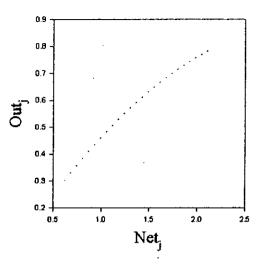

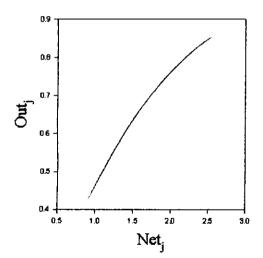

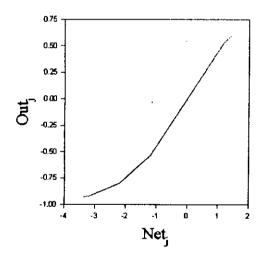

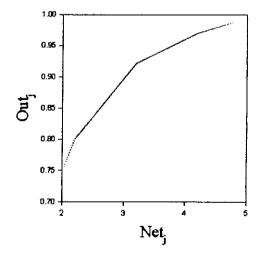

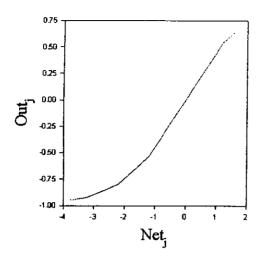

#### 2.4.1 Hidden Units

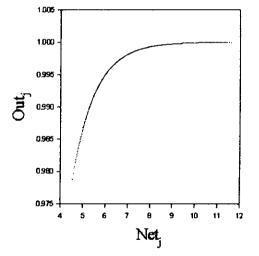

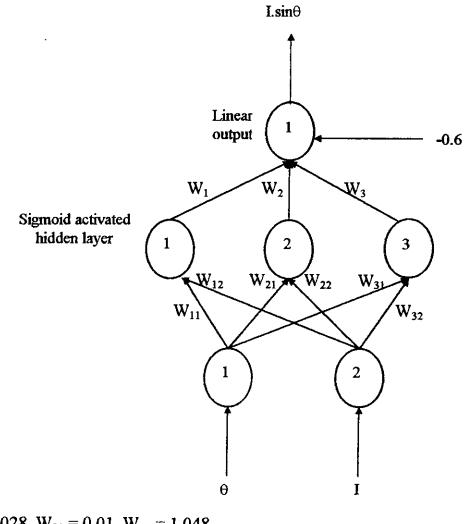

To observe the response of the hidden layers of the BPN network the "CHECK.FOR" program generates output data for each of the four nodes of the hidden layer. The behaviors of the four nodes for the test patterns are shown in Figure 2.6.a to 2.6.d. It will be observed that each node is activated only within a certain portion of the sigmoid function. This observation is very important because during the implementation of the hidden layers only that portion of the sigmoid function will be implemented within which the node activates. A detail analysis will be forwarded in chapter 3. Moreover, it is seen that, response of node 4 shown in figure 2.6.d has its output limited within 0.98 to 1.0. So it can be predicted that node 4 acts as a fixed bias for the network module because its output is always confined within the very small region close to unity of the sigmoid function. The fixed biasing introduced by this node is  $W_4$  which equals to -0.6. So the pruned BPN architecture ultimately reduces to a network consisting of three hidden unit and one fixed biased unit, which is drawn in Figure 2.7.

Figure 2.5 The correlation between output and target values of the test patterns. The graph shows a best fit analysis of  $output = 1.002 \times target + 0.0008756$ .

Figure 2.6.a Response of node 1.

Figure 2.6.b Response of node 2.

Figure 2.6.c Response of node 3.

Figure 2.6.d Response of node 4.

$W_{11} = 2.028, W_{21} = 0.01, W_{31} = 1.048$  $W_{12} = 0.6044, W_{22} = 2.968, W_{32} = 2.791$  $W_1 = 4.220, W_2 = 5.976, W_3 = -7.4676$

### **2.5 BPN WITH PIECE-WISE LINEAR ACTIVATION**

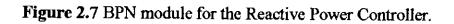

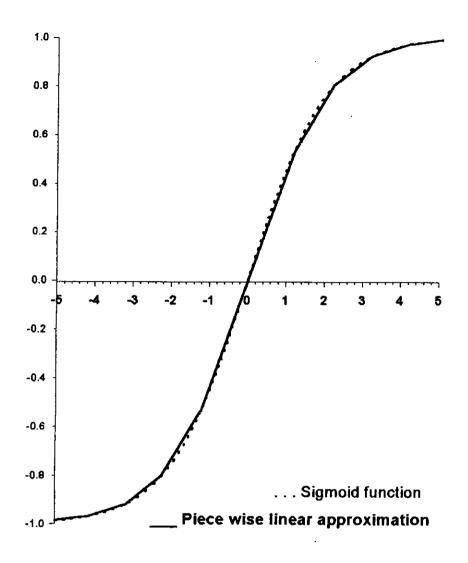

In the preceding section, BPN model was developed based on a non-linear sigmoid activation function. Hopfield [32] introduced an electronic circuit using nonlinear amplifiers and resistors, which suggests the possibility of building the sigmoid activation function using VLSI technology. But it is easier to implement piece wise linear function with diodes and resistors. In this section, a new BPN model will be designed with piece-wise linear activation function in the hidden units.

#### 2.5.1 Segmenting the Sigmoid Function

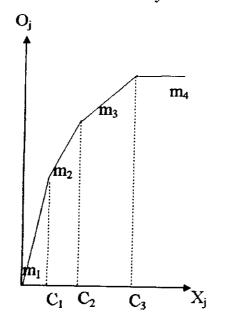

The sigmoid function will be segmented in a number of sections so that it can be closely approximated by linear functions. Figure 2.8 shows the resemblence between these two functions. The equations for PWL are given below :

| y = 0.4475.x            | $-1.2 \le y \le 1.2$  | ••• | ••• | (2.23.a) |

|-------------------------|-----------------------|-----|-----|----------|

| y = 0.263.x + 0.2214    | $1.2 \le y \le 2.2$   | ••• | *** | (2.23.b) |

| y = 0.12167.x + 0.53233 | $2.2 \le y \le 3.2$   | ••• | ••• | (2.23.c) |

| y = 0.04878.x + 0.76555 | $3.2 \le y < 4.2$     | ••• | ••• | (2.23.d) |

| y = 0.02955.x + 0.86463 | 4 $4.2 \le y \le 5.2$ | ••• | ••• | (2.23.e) |

| y = 1                   | 5.2 < y               | *** | ••• | (2.23.f) |

| y = 0.263.x - 0.2214 -1.    | .2 > y ≥ -2.2  | ••• | ••• | ( <b>2.24.b</b> ) |

|-----------------------------|----------------|-----|-----|-------------------|

| y = 0.12167.x - 0.53233 - 2 | 2.2 > y ≥ -3.2 | ••• | *** | (2.24.c)          |

| y = 0.04878.x - 0.76555 -3. | .2 > y ≥ -4.2  | ••• |     | ( <b>2.24.d</b> ) |

| y = 0.02955:x - 0.864634 -4 | 4.2 > y ≥ -5.2 | *** | ••• | (2.24.e)          |

| y = -1                      | -5.2 > y       | ••• | ••• | (2.24.f)          |

Figure 2.8 Approximating sigmoid to piece wise linear function.

To get proper convergence, it is mentioned in the mathematics of BPN that the activation function should be differentiable. The PWL activation function proposed here may not be differentiable as a whole, but it is piece wise differentiable. So, BPN learning is possible. Though Eqs. (2.23.f) and (2.24.f) are of constant values, yet a slope of 0.01 is assumed during learning process. A computer program, LRNSRT.FOR (Appendix-5) has been developed on this respect.

#### 2.5.2 Training of the Network

The BPN model is trained with the same 55 learning patterns used in the previous section. But this time number of hidden units has been increased to six. The learning rate parameter has been unchanged to 0.20 althrough the training process. After satisfactory convergence, the results of the training process are given below :

Total iteration cycle : 80800

| ٠ | Final RMS error :           | .00099                    |                                    |                         |

|---|-----------------------------|---------------------------|------------------------------------|-------------------------|

| ٠ | Weights for node $\theta$ : | W <sub>11</sub> = -1.644, | $W_{21} = -1.69,$                  | W <sub>31</sub> = 4.77, |

|   |                             | W <sub>41</sub> = 4.305,  | W <sub>51</sub> = - <b>8.416</b> , | $W_{61} = 2.38.$        |

| ٠ | Weights for node I :        | $W_{12} = -1.2808$        | $W_{22} = 2.155$                   | $W_{32} = -5.376$       |

|   |                             | $W_{42} = 3.525,$         | W <sub>52</sub> = 3.2767,          | $W_{62} = -0.11$        |

| ٠ | Weights for output node :   | $W_1 = -1.0811,$          | W <sub>2</sub> = 1.241,            | W <sub>3</sub> = -0.192 |

|   |                             | W <sub>4</sub> = -2.0332, | W <sub>5</sub> = -0.269,           | $W_6 = 1.88$            |

The BPN architechture for this purpose is shown in Figure 2.9.

$$\begin{split} W_{11} &= -1.644, \ W_{21} &= -1.69, \ W_{31} &= 4.77, \\ W_{41} &= 4.305, \ W_{51} &= -8.416, \ W_{61} &= 2.38, \\ W_{12} &= -1.2808, \ W_{22} &= 2.155, \ W_{32} &= -5.376 \\ W_{42} &= 3.525, \ W_{52} &= 3.2767, \ W_{62} &= -0.11 \\ W_1 &= -1.0811, \ W_2 &= 1.241, \ W_3 &= -0.192 \\ W_4 &= -2.0332, \ W_5 &= -0.269, \ W_6 &= 1.88 \end{split}$$

Figure 2.9 The BPN architechture of the neural network module with piece-wise linear activation.

#### 2.5.3 Convergence of the network

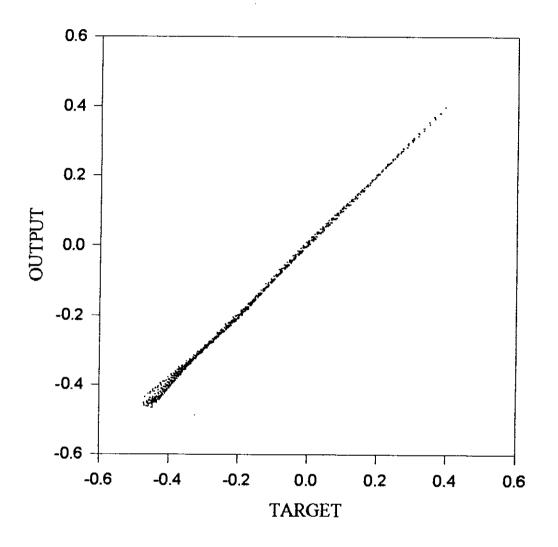

A computer program, CHKSRT.FOR (Appendix-6), has been developed to check the convergence of the network with 896 test patterns. The correlation between output and target values are given in Figure 2.10. Comparing this relationship with the previous correlation found in Figure 2.5 it is seen that the previous one converged better than the present case. This is expected because the final RMS error for this case is higher than the previous learning case. Yet the gradient of the best fit straight line is 1.00673 and the line constant is 0.00186 which indicates that output  $\approx$  target. So the converging result may be inferior to the previous learning case but it is still satisfactory. Moreover, it is realized that 100% accuracy is not required for power factor sensing, which is our ultimate desire.

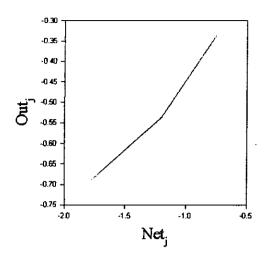

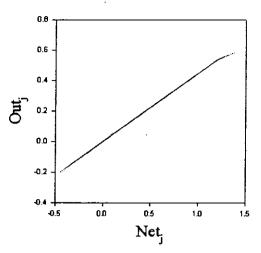

The responses for each of the hidden layers are given in Figure 2.11.a to 2.11.f. These graphs show that the response of the nodes are limited within particular regions. For example, node 1,2 and 6 have response within the first two straight lines of the sigmoid function. There is only one break point for these three hidden nodes. So, it is only necessary to implement that portion of the piece-wise linear sigmoid function within which the node operates. This consideration simplifies the implementation of the hidden layer which will be explained in details in chapter 3. On the other hand node 4 and 5 have their response spreading through three break points. So during the implementation of these two nodes special attention and care has to be observed. The response graphs of figure 2.11.a to 2.11.f will be needed during the implementation of the nodes which is described in detail in chapter 3.

• • •

Figure 2.10 The correlation between output and target values of the test patterns. The graph shows a best fit analysis of  $output = 1.00673 \times target + 0.00186$ .

Figure 2.11.a Response of node 1

Figure 2.11.c Response of node 3

Figure 2.11.b Response of node 2

Figure 2.11.d Response of node 4

Figure 2.11.e Response of node 5.

Figure 2.11.f Response of node 6.

### 2.6 SENSITIVITY ANALYSIS OF THE NETWORK

So far, a neural network model has been designed to perform the functional mapping  $I.\sin\theta$  for developing a reactive power controller. A theoretical analysis on the designed neural network will now be examined. Some interesting behaviors of the network during learning will also be put forward for future analysis in this final section.

During the period of learning process of the network with sigmoid activated function in the hidden layer, a faster convergence has occurred in comparison to the piece-wise linear activation function. This phenomena was expected because the sigmoid function is smooth and differentiable. Moreover, the number of hidden nodes required for learning is half of that required with piece-wise linear activated function. The percentage of error was also greater in the latter case. So, obviously a smooth and differentiable function is preferable in the hidden nodes. But, the present study has proven that, convergence with ramp activation may be difficult, but not impossible.

Learning rate has influenced the speed of convergence. Initially the learning rate was kept constant. As the convergence of the network became slower, the learning rate was made a function of root mean square of the error of the network. This increased the speed of convergence. But interestingly the change in learning rate had inverse effect with the network having piece-wise linear activation. Any change in the initial value of the learning parameter had increased the root mean square error of the network. So, for the second network a constant learning rate was observed. The mapping of the function  $I.\sin\theta$  seems simple. But practically it has proven to be pretty difficult. Because the network has to converge for almost infinite combinations of I and  $\theta$ . During the process of learning, the network used to stuck to a minimal where the change in error halted. To simplify such case, a condition was imposed on the neural network. It was considered that a minimum KVAR demand of 0.233 will be neglected by the RPC having maximum capacity of 1.2 KVAR. This consideration increased the convergence of the network to a greater extent.

The final network to be implemented by electronic circuit is shown in Figure 2.9. As it is closely observed, the response data of its nodes shows that node number 4 of the hidden layer is the most sensitive node among the others. Because, the response of node 4 ranges within 2 volts to 5 volts, and has the highest amplification weight of 2.0332 connected with the output node. So it may fairly be assumed that node 4 is the controlling node of the network and needs special attention during implementation. Observing the other nodes, it is seen that node 6 is almost dependent only on input 1. Because input 2 has a weak connection of 0.11 compared to the weight 2.38 connected with input 1.

Hence, a neural network module for the Reactive Power Controller has been designed and its various aspects are analyzed. The next chapter will concentrate on the implementation technic of the network.

# **CHAPTER THREE**

.

# IMPLEMENTATION OF THE NEURAL NETWORK

### **3.1 INTRODUCTION**

This chapter explores the steps involving the development of neural network based reactive power controller. A hardware implementation of a fully analog three layer perceptron artificial neural network is presented using simple electronic tools. A methodology is proposed showing the technology to by-pass the need of amplifiers for constructing synaptic weights in the hidden layers of the neural network. Mathematical analysis is forwarded in this respect. The implementation technology introduced in this chapter is a generalized approach considering the aspects from a broad point of view. So this chapter is dedicated not only to implement the neural network based RPC, but it also invents a very unique technology of implementing neural networks in general with the simplest of electronic tools. Implementation of other auxiliary interfacing circuits for the RPC is also described in this chapter. Finally, the performance of the network has been successfully tested.

# **3.2 CONTROL ALGORITHM**

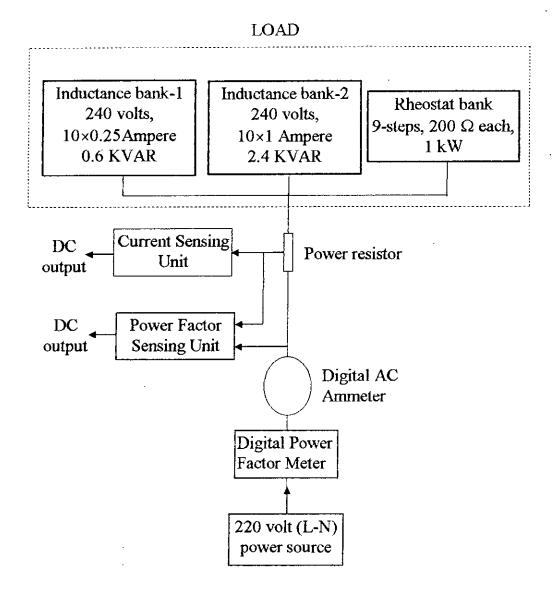

The neural network module designed in chapter 2 consists of two inputs and one output nodes. It was elaborately explained in chapter 2 that the network will sense load current and power factor in their equivalent DC voltage and will produce an output in DC which has a linear relation with the KVAR demand of the load. The control circuits of the developed RPC will sense the output of the neural network and initiate proper switching signals to activate capacitor banks connected with the RPC to supply the KVAR. Based upon the model designed in chapter 2 a simplified line diagram of the complete NN based RPC is developed in Figure 3.1. It shows the control algorithm of the proposed analog neural network based Reactive Power Controller.

Figure 3.1 Line diagram of the neural network based RPC.

### **3.3 CIRCUIT IMPLEMENTATION**

The hardware development of the RPC is divided in four main stages. The first stage develops the rectifier-filter circuit block to convert the AC input signals to equivalent DC inputs. The next stage invents a unique technique to implement the neural network module. The third stage describes the implementation process of the KVAR control circuit block. Finally, a brief description of the widely implemented capacitor switching block is presented.

### 3.3.1 Input Signal Conditioning Circuit

The neural network module for the proposed RPC has two inputs; current and power factor angle. Both of these signals should be in DC form. Simple rectifier-filter blocks is developed to perform this AC/DC conversion. The following article is presented in two separate sub-articles for the two different input signal conditioning circuits.

#### 3.3.1.1 Current Sensing Unit

The high ampere AC load current is stepped down to maximum 5 amperes small signal AC current by a C.T. as shown in Figure 3.1. The AC current is converted to equivalent AC voltage signal by a power resistor. Half wave rectification is used for the AC/DC conversion so that both input and output signals have identical grounding. The input-output relation of the circuit should abide Eq. 3.1, which was assumed during learning of the neural network (Appendix-5). The circuit diagram of this block is given in Figure 3.2.

Figure 3.2 The rectifier-filter circuit for current

One interesting addition in the above circuit is a constant  $-1.11\times(-3.R/R) =$ 3.33 volt DC biasing. This biasing is introduced because, during the learning process of the neural network module described in chapter 2, the current range was limited within 2 ampere to 7 ampere for the ease of convergence in the learning software routine "LRNSRT.FOR" (Appendix-5). Eq. 3.1 indicates that rms 2 ampere corresponds to 3.33 DC voltage. The current range can be changed to the conventionally used 0 to 5 ampere range simply by introducing a DC biasing of 3.33 voltage. Hence, an input current of rms 0 to 5 ampere should be linearly converted into 3.33 to 11.66 DC voltage through this implemented circuit. The gain control resistance is provided to establish this linear relationship.

### 3.3.1.2 Power Factor Sensing Unit

The phase angle difference between current and voltage is converted in equivalent DC voltage through the circuit shown in Figure 3.3. The current signal is taken from the power resistor terminal and the voltage signal is taken from a simple voltage divider. An equivalent voltage drop across the power resistor will act as the reference for the sensing of current. On the other hand, a small sample of the 220 volt power line from the voltage divider will be sufficient to obtain the phase angle between the voltage and the current. The width of the output pulses from the comparator shown in Figure 3.3 is directly related with the phase angle of the power line. Finally, the pulses are rectified and converted to pure DC voltage. The relation between phase angle and DC signal output is linear from 18° to 52° and follows Eq. 3.2. The variable gain control resistance will help to establish this relation.

DC output signal for phase shift = {(phase shift in degrees)  $\times 16$ }/98.6 (3.2)

Figure 3.3 Rectifier-filter circuit for power factor sensing.

### **3.3.2 Simulation of Activation Function**

This section describes the technique used to implement the neural network module. The fabrication of the neural module is based on the theoretical investigation of the converged network described in chapter 2. It has been mentioned in the conclusion of chapter 2 that piece-wise linear (PWL) activation function will be implemented for the purpose. This section also gives a broad description of the methodology forwarded for implementing neural networks in a generalized way. Before going through the implementation details, a general mathematical analysis of the neural network is forwarded.

### 3.3.2.1 Mathematical Analysis

The mathematical analysis forwarded in this section is applicable for any general neural network having piece-wise linear activation function. So, instead of constricting the mathematics only within piece-wise linear sigmoid function, a more general approach has been taken by considering the ramp function as the activation function of the hidden layers of the neural network having 'n-1' number of break points with 'n' number of different gradient lines.

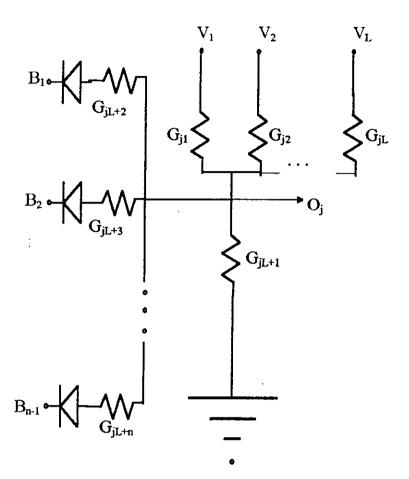

Figure 3.4 shows the j-th node of the hidden layer of neural network having PWL activation function. The break points of the function are represented by  $C_1$ ,  $C_2$  and  $C_3$ , and the slopes are denoted by  $m_1$ ,  $m_2$ ,  $m_3$  and  $m_4$ . The number of inputs to the j-th node of the hidden layer is 'L'. Weights connected from the inputs to the j-th node are  $W_{j1}$ ,  $W_{j2}$ ,  $W_{j3}$ , ....  $W_{jn}$ . The output of the j-th node connected with the output layer of the neural network is  $O_j$ .

Figure 3.4.a j-th node of the hidden layer

Figure 3.4.b PWL function of the hidden layer

For a generalized solution, the sigmoid function is considered having 'n' no. of slopes and 'n-1' no. of break points. The output to the j-th node  $O_j$  is related with the input  $X_j$  by

$$X_{j} = \sum_{i=1}^{L} I_{i} \cdot W_{ji}$$

... ... ... (3.3)

$$O_j = m_1 X_j, X_j \le C_1$$

... ... ... (3.4)

and,

$$O_j = m_n \cdot X_j + \sum_{r=1}^n (m_{r-1} - m_r) \cdot C_{r-1}, C_{n-1} < X_j \le C_n \qquad \dots \qquad (3.5)$$

Equating Eq.(3.3), (3.4) and (3.5),

$$O_{j} = m_{n} \sum_{i=1}^{L} I_{i} W_{ji} + \sum_{r=1}^{n} (m_{r-1} - m_{r}) C_{r-1}, C_{n-1} < X_{j} \le C_{n} \qquad ... \qquad (3.7)$$

#### 3.3.2.2 Implementation

The above equations govern the relations among inputs and outputs of a neural network having PWL activation. The equations were developed in a generalized way. So, the implementation technology developed in this section is also described in a broad and extensive way; applicable for implementing any neural networks. Figure 3.5 shows a simple electronic circuit with diodes and resistances to fabricate the PWL function together with the weights connected with the hidden nodes.

Figure 3.5 A simple voltage divider circuit

.

In the circuit shown in Figure 3.5, the input signal  $I_i$  of the NN module is considered proportional to the voltage  $V_i$ . Output voltage  $O_j$  for  $|O_j| \le |B_1|$  is,

$$O_{j} = \frac{\left[\sum_{i=1}^{L} V_{i} \cdot G_{ji}\right]}{\left[\sum_{i=1}^{L+1} G_{ji}\right]} \dots \dots \dots \dots \dots \dots \dots \dots (3.8)$$

Solving Eq. (3.6) and Eq. (3.8)

and,

$$G_{jL+1} = (1-m_1 \cdot \sum_{i=1}^{L} W_{ii}) \cdot G_{j1} / (m_1 \cdot W_{j1}) \dots \dots (3.10)$$

Assuming a suitable and practical value for one of the resistances the values of the others can be established. For  $|B_2| \ge |O_j| > |B_1|$ ,

From Eq. (3.7) and Eq. (3.11)

$$G_{jL+2} = [(1-m_2, \sum_{i=1}^{L} G_{ji}) \cdot G_{j1} / (m_2, W_{j1})] - G_{jL+1} \dots \dots (3.12)$$

and,

$$B_1 = [C_1.(m_1 - m_2). \sum_{i=1}^{L+2} G_{ji}] / G_{jL+2} \dots \dots \dots \dots (3.13)$$

.

From Eq. (3.12), the value of  $G_{jL+2}$  is obtained, while Eq. (3.13) establishes the first breaking potential. A generalized equation substituting (3.12) and (3.13) are

$$G_{jL+n} = \left[ (1 - m_n \cdot \sum_{i=1}^{L} G_{ji}) \cdot G_{j1} / (m_n \cdot W_{j1}) \right] - \sum_{i=1}^{n-1} G_{jL+i} \qquad \dots \qquad (3.14)$$

and,

$$B_{n-1} = [\{\sum_{r=1}^{n} (m_{r-1} - m_r), C_{r-1}, \sum_{i=1}^{L+n} G_{ji}\} - \sum_{i=1}^{n-2} B_i \cdot G_{jL+i+1}] / G_{jL+n}$$

(3.15)

It is evident from Eq. (3.10) that for a non negative value of  $G_{jL+1}$  the condition that should be imposed is,

$$m_1 \cdot \sum_{i=1}^{L} W_{ji} < 1 \qquad \dots \qquad \dots \qquad \dots \qquad \dots \qquad \dots \qquad (3.16)$$

So, there is a fair amount of possibility that all nodes cannot be implemented with a voltage divider circuit. Yet, this condition can be satisfied with some adjustment to the input values. Eq. (3.7) shows that the weights can be attenuated by a certain factor without hampering the output  $O_j$ , provided that the inputs are conversely amplified by the same factor. So, by choosing a proper attenuating factor Eq. (3.16) can be satisfied. It is not necessary to implement the whole PWL function for every node. Rather, it is essential to implement that portion of the PWL function within which the node operates. This consideration has simplified the implementation of the hidden layer. Finally, the output nodes are developed by using analog adders. Thus, necessity of using amplifier to implement weight for the hidden layer is eliminated.

Thus, it has been shown that a voltage divider circuit is quite capable to be used as the nodes of the hidden layer. The neural network developed for the reactive power controller is described in appendix-7.

#### 3.3.3 KVAR Control Circuit

In the previous section the neural network module was developed to sense the amount of KVAR required by the power system. A linear relationship between the output of the neural network and the KVAR demand was obtained. This section explains the development of the control circuitry required to switch proper capacitor banks to improve the power factor of the system.

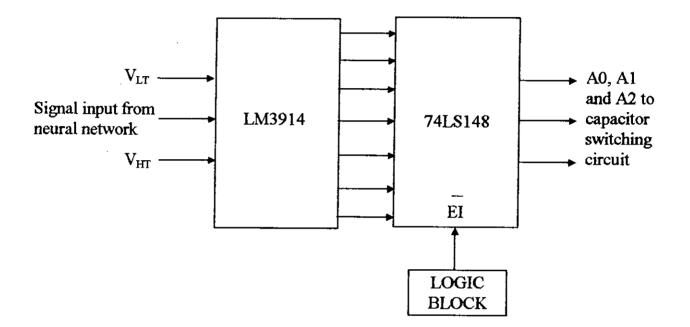

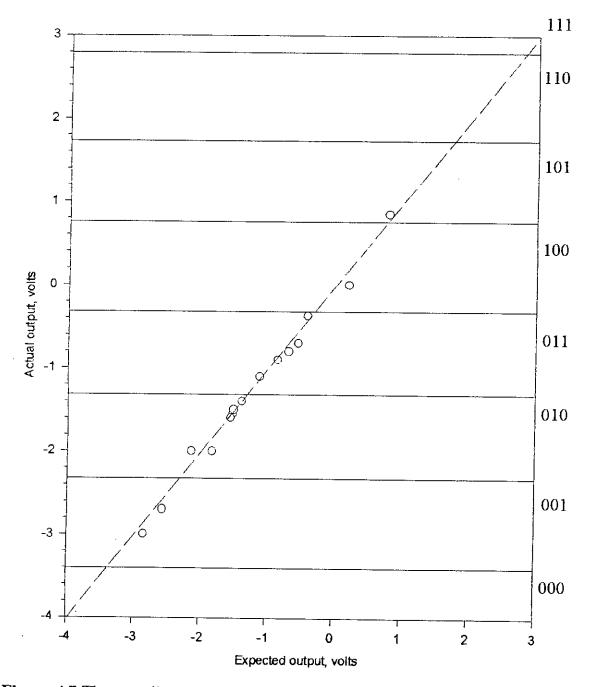

So far it was considered during the training of the neural network that maximum 7 amperes of current will be sensed by the network. The operation of the network showed that for this maximum current rating, the output of the neural network is 2.8 volts and the minimum KVAR sensed by the neural network corresponds an output of -3.03 volts. Hence, for an N step capacitor switching circuit the output range of -3.03 volt to 2.8 volt of the network should be divided in N linear ranges. The proposed RPC is designed with 3 stages of capacitor switchings. For such case, a maximum of  $2^3-1 = 7$  steps can be obtained. The KVAR control circuit of the designed RPC is implemented mainly with two IC's; LM3914 and 74LS148. Along them, an invertor IC 7404 and a voltage regulated IC 7805 were also used for the KVAR control block. The pin and block diagram of only the main two IC's are described in the following article.

#### 3.3.3.1 Function of the IC's

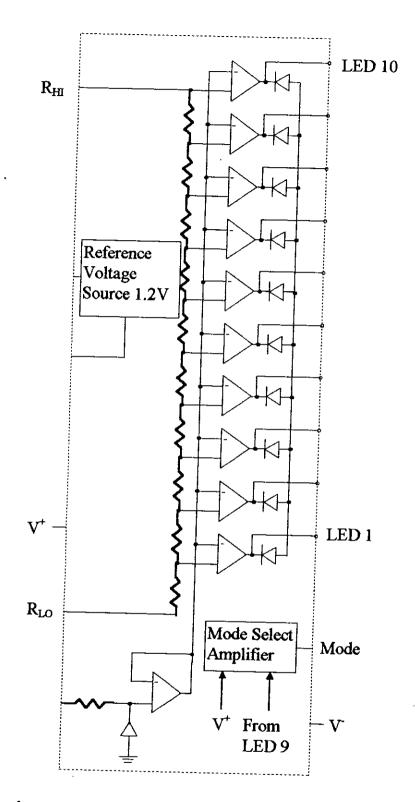

LM3914 : This IC is a simple analog level triggering chip consisting of 10 voltage comparators. This IC is widely used in bar displaying and is capable of driving 10 LEDs together. In this case, it is used to separate the linear output range of the neural network in seven uniformly divided sections. The internal components of this IC is shown in Figure 3.6.

Figure 3.6 Internal representation of IC LM3914

The figure shows that there are 10 voltage level comparators. The number of those comparators being used for the KVAR control circuit depends on the number of steps demanded in the capacitor switching stage. The biasing voltage,  $V_{\rm H}$  and  $V_{\rm L}$ , applied to the potential divider circuit of LM3914 will be obtained from solving the two Eq.s 3.17 and 3.18 given below:

$$(V_{\rm H} - V_{\rm L}).(N/10) + V_{\rm L} = V_{\rm HT}$$

... ... (3.17)

$(V_{\rm H} - V_{\rm L}).(1/10) + V_{\rm L} = V_{\rm LT}$  ... ... (3.18)

Where :

$V_{H}$  = Biasing voltage applied to  $R_{HI}$   $V_{L}$  = Biasing voltage applied to  $R_{LO}$   $V_{HT}$  = Threshold voltage to trigger maximum KVAR demand  $V_{LT}$  = Threshold voltage to trigger minimum KVAR demand N = No. of capacitor switching steps.

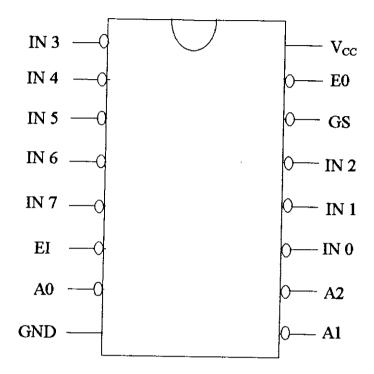

74LS148 : This is a Decimal/Binary high priority encoder chip. The pin diagram of this IC is shown in Figure 3.7.

The N signal outputs from LM 3914 will be the inputs of 74LS148. The three outputs of the encoder chip will generate binary signals equivalent to its highest input being activated. The binary signals will activate corresponding capacitor switching relays which is explained elabourately in the next section.

Figure 3.7 The pin diagram of 74LS148

.

#### 3.3.3.2 Elimination of Low KVAR Demand

Recalling back to the learning algorithm of the neural network developed in chapter 2 reminds that the network was not trained for patterns corresponding to very low KVAR demands. A simple logic function was introduced in the program "LRNSRT.FOR" (Appendix-5) for this purpose. The logic block divides the output function I.sin $\theta$  in two regions by two straight lines defined by Eq. 3.19 and Eq. 3.20.

$$Input_1 \times 0.25 + Input_2 = 0.2675 \dots \dots \dots \dots \dots \dots (3.19)$$

$$Input_1 + Input_2 = 0.53 \dots \dots \dots \dots \dots \dots \dots (3.20)$$

It was observed that the two input data combinations falling above both of the lines gives a KVAR output greater than 0.2 KVAR. So, any input combinations not satisfying the equations or having outputs less than the right hand side of the equations will be eliminated through the logic block. In this way the low KVAR demand of the circuit can be removed.

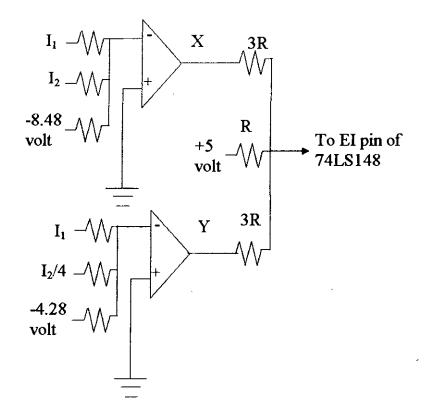

The block representing this logic function is implemented with three comparators shown in Figure 3.8. The upper comparator having output X will be positive; i.e. +15 volts only when the two input combinations lies above the Eq. 3.20. Similarly, the lower comparator having output Y will be positive; i.e. +15 volts only when the two input combinations lies above the Eq. 3.19. Finally the three resistance matrix is built to create an analog logic circuit. A brief analysis is presented in table 3.1. The output of this logic block will be used to activate the encoder chip by connecting it to the  $\overline{\text{EI}}$  pin of 74LS148. The complete connection diagram of the control circuit is given in Figure 3.9.

Figure 3.8 The logic block prohibiting the KVAR control circuit to operate at very low KVAR demand

### **Operation of the logic block:**

X = -15 volts if  $I_2 + I_1 > 8.48$  volts; else X = +15 volts

Y = -15 volts if  $I_2/4 + I_1 > 4.28$  volts; else Y = +15 volts

| Output = $X/5$ + | -Y/5 + 2.0 |

|------------------|------------|

|------------------|------------|

| X   | Y   | Analog output | Logic output | Operation of |

|-----|-----|---------------|--------------|--------------|

|     |     |               |              | 74LS148      |

| +15 | +15 | 8             | 1            | Prohibits    |

| +15 | -15 | 2             | 1            | Prohibits    |

| -15 | +15 | 2             | 1            | Prohibits    |

| -15 | -15 | -4            | 0            | Inhibits     |

Table 3.1 Operation of the logic block

Figure 3.9 The block diagram of KVAR control circuit

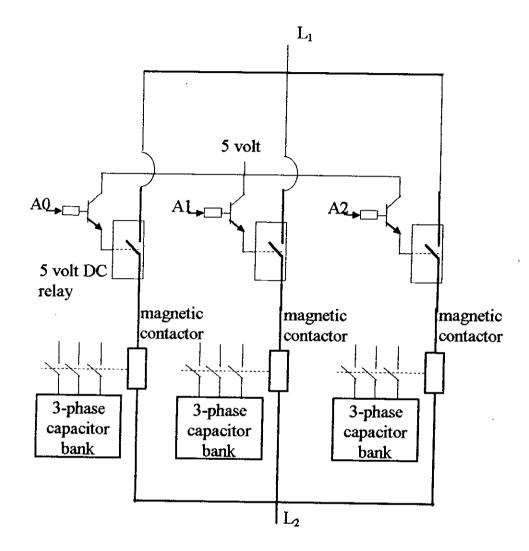

#### 3.3.4 Capacitor Switching Circuit

The three controlling signals A0, A1 and A2, obtained from the KVAR control circuit described in the previous article, is used to initiate three individual 5 volt DC normally open relays. These relays are in series with the magnetic contactors of each capacitor banks. The block diagram of capacitor switching circuit is shown in Figure 3.10.

The three controlling signals A0, A1 and A2 drives the base of the transistors to saturation or to cut off region according to the digital signals generated by the KVAR control circuit. Hence, the transistors acts as switches for the DC relays. The DC relays are initiated by these signals from the KVAR control circuit, current flows in the coil of the magnetic contactors from  $L_1$  to  $L_2$  and the capacitor banks are thus connected with the three bus bars. The connected capacitor bank delivers reactive power to improve power factor.

This chapter has described the implementation of the NN based RPC. The next chapter will discuss on the results obtained during the experiments done on the implemented circuits and highlight on the overall performance of the network.

Figure 3.10 Capacitor switching circuit

# CHAPTER FOUR

# RESULTS

# **4.1 INTRODUCTION**

The neural network based reactive power controller was developed systematically step by step. Design and implementation technology for developing the operating modules for the NN were elaborately described in chapter 3. All those modules were tested part by part and necessary measures were taken for precise and accurate operations of the modules. These modules were finally joined together to built the neural network based reactive power controller. At the end rigorous laboratory tests were performed on the implemented network. This chapter forwards the experimental setups and test results performed on the process of developing the neural network.

# 4.2 PERFORMANCE TESTING ON THE NN MODULES

Chapter 3 has divided the complete network in four sections. They are: Input signal conditioning unit, Activation function section, KVAR control block and Capacitor bank switching circuit. These four modules were developed separately and performance of all these modules were tested precisely. This section elaborates those tests in the following articles.

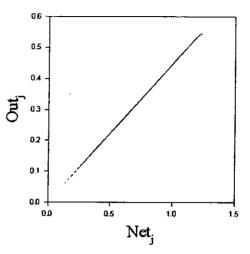

#### 4.2.1 Testing on Input Signal Conditioning Unit

The neural network has two input nodes. They are: Current sensing unit and Power factor sensing unit. The circuits implemented for these two units are described in sections 3.3.1.1 and 3.3.1.2. The desired response to be obtained from these two units are expressed in Eq. 3.1 and Eq. 3.2. To observe the actual response of both of these units a laboratory test was performed. The experimental setup is presented in Figure 4.1.

Figure 4.1 Experimental setup for testing input signal conditioning unit.