## Discrete Modeling and Common Rail Powered Reliability Improving Techniques for Nanoscale CMOS Transceiver Circuits

by

#### Apratim Roy

DOCTOR OF PHILOSOPHY

Department of Electrical and Electronic Engineering BANGLADESH UNIVERSITY OF ENGINEERING AND TECHNOLOGY

October 2015

The thesis entitled "Discrete Modeling and Common Rail Powered Reliability Improving Techniques for Nanoscale CMOS Transceiver Circuits" submitted by Apraim Roy, Student No.: 1012064001, Semioni October, 2012 has been accepted as satisfactory in partial fulfilment of the requirement for the degree of Doctor of Philosophy in Electrical and Electronic Engineering on October 31, 2015.

BOARD OF EXAMINERS

| (Dr. A. B. M. Harun-Ur-Rashid)                                                                             | Chairman              |

|------------------------------------------------------------------------------------------------------------|-----------------------|

| Professor                                                                                                  | (Supervisor)          |

| Department of Electrical and Electronic Engineering                                                        |                       |

| Bangladesh University of Engineering and Technology<br>Dhaka - 1000, Bangladesh.                           |                       |

|                                                                                                            |                       |

| The Jouron's                                                                                               |                       |

| 2 3                                                                                                        | and the second second |

| (Dr. Taifur Ahmed Chowdhury)                                                                               | Member                |

| Professor and Head<br>Department of Electrical and Electronic Engineering                                  | (Ex-officio)          |

| Bangladesh University of Engineering and Technology                                                        |                       |

| Dhaka - 1000, Bangladesh.                                                                                  |                       |

| Λ                                                                                                          |                       |

| P.L. 31/10/15                                                                                              |                       |

| 3. (Dr. Pran Kanai Saha)                                                                                   | Member                |

| Professor                                                                                                  |                       |

| Department of Electrical and Electronic Engineering<br>Bangladesh University of Engineering and Technology |                       |

| Dhaka - 1000, Bangladesh.                                                                                  |                       |

| 1- 1                                                                                                       |                       |

| 31/10/15                                                                                                   |                       |

| 4                                                                                                          |                       |

| (Dr. Md. Shafiqul Islam)<br>Professor                                                                      | Member                |

| Department of Electrical and Electronic Engineering                                                        |                       |

| Bangladesh University of Engineering and Technology                                                        |                       |

| Dhaka - 1000, Bangladesh.                                                                                  |                       |

| 5 ALZ 31.10.15                                                                                             |                       |

| 5. Al 31.10.13                                                                                             |                       |

| (Dr. Md. Anwarul Abedin)                                                                                   | Member                |

| Professor<br>Department of Electrical and Electronic Engineering                                           |                       |

| Department of Electrical and Electronic Engineering<br>Dhaka University of Engineering and Technology      |                       |

| Gazipur, Bangladesh.                                                                                       |                       |

| A 10110 01 10 1                                                                                            |                       |

| Juden 31. 10.15                                                                                            |                       |

| 6.<br>(Dr. Md. Forkan Uddin)                                                                               | Member                |

| Associate Professor                                                                                        |                       |

| Department of Electrical and Electronic Engineering                                                        |                       |

| Bangladesh University of Engineering and Technology<br>Dhaka - 1000, Bangladesh.                           |                       |

| /                                                                                                          |                       |

| 7. BUM& 31/10/15                                                                                           |                       |

| 7                                                                                                          |                       |

| (Dr. Md. Ashraful Hoque)<br>Professor                                                                      | Member<br>(External)  |

| Department of Electrical and Electronic Engineering                                                        | (marcinin)            |

| Islamic University of Technology                                                                           |                       |

| Gazipur, Bangladesh.                                                                                       |                       |

### CANDIDATE'S DECLARATION

It is hereby declared that this thesis or any part of it has not been submitted elsewhere for the award of any degree or diploma.

ii

Signature of the Candidate

Apratim Roy

## Dedication

To my parents and my aunt.

### Acknowledgments

I begin by acknowledging the Almighty who's given me silent support during this e ort.

I would like to convey my heartiest gratitude to my supervisor Dr. A.B.M. Harun-ur-Rashid, Professor, Department of Electrical and Electronic Engineering (EEE), Bangladesh University of Engineering and Technology (BUET) for guiding me through this arduous work with his continuous guidance, suggestions, and wholehearted support. His technical and editorial expertise was indispensable to the realization of this thesis and the dissertation would not have materialized without him.

I would also like to thank the members of my doctoral committee: Prof. Dr. Taifur Ahmed Chowdhury, Head, Department of EEE, BUET, Prof. Dr. Pran Kanai Saha, Department of EEE, BUET, Prof. Dr. Md. Sha qul Islam, Department of EEE, BUET, Prof. Dr. Md. Anwarul Abedin, Department of EEE, DUET and Associate Prof. Dr. Md. Forkan Uddin, Department of EEE, BUET for their encouragement and insightful comments. In addition, I want to acknowledge the Department of Electrical and Electronic Engineering of BUET for providing laboratory and library facilities which were instrumental to the continuation of the project.

I am eternally indebted to my family for their love and support which are the forces behind whatever little accomplishments I have made in my life. I also take a moment to remember the loving memories of my grandparents who always wished the best for me.

## Contents

| Dedica  | tion      |                                                       | iii |

|---------|-----------|-------------------------------------------------------|-----|

| Acknow  | vledgen   | nents                                                 | iv  |

| List of | Figures   |                                                       | ix  |

| List of | Tables    |                                                       | xiv |

| Abstra  | ct        |                                                       | 1   |

| 1 Intro | duction   |                                                       | 3   |

| 1.1     | Discret   | te Modeling for Nanoscale CMOS Architectures          | 3   |

| 1.2     | Improv    | vement of Reliability for CMOS Transceiver Circuits   | 10  |

| 1.3     | Objec     | tive of the Thesis                                    | 25  |

| 1.4     | Organ     | nization of the Thesis                                | 27  |

| 2 Accu  | urate Ge  | eometry Scalable CMOS Modeling of Low-power Nanoscale | ;   |

| Am      | plifier C | ircuits                                               | 29  |

| 2.1     | Introd    | uction                                                | 29  |

| 2.2     | Modeli    | ng of CMOS Elements                                   | 31  |

|         | 2.2.1     | Metal-insulator-metal Capacitor                       | 32  |

|         | 2.2.2     | Polysilicon Resistor                                  | 35  |

|         | 2.2.3     | Planar-spiral-symmetric Inductor                      | 38  |

|         | 2.2.4 \$  | Scalable Active Device Model                            | 42 |

|---------|-----------|---------------------------------------------------------|----|

| 2.3     | Modeli    | ng of Nanoscale Amplifiers                              | 44 |

| 2.4     | Compa     | arison of Performance                                   | 48 |

| 2.5     | Conclu    | isions                                                  | 49 |

| 3 Com   | mon-rail  | Powered Reliability Improving Technique for CMOS        |    |

|         | lifiers   |                                                         | 50 |

| 3.1     |           | ıction                                                  |    |

| -       |           | ility Improving Circuits (RIC)                          |    |

|         |           | Single-supply Amplifiers with RIC                       |    |

| 0.0     |           | 1.2-V High-gain CC Amplifier                            | 57 |

|         |           | Low-voltage CC Amplifier                                | 59 |

|         |           | 1.2-V CS Amplifier                                      | 60 |

| 3.4     |           | s of CMOS Reliability                                   | 61 |

| 5.4     |           | ·                                                       | 61 |

|         |           | Improvement against Process Variation                   |    |

|         |           | Effect on Threshold Modification and Supply Stability   |    |

|         | 3.4.3     | Frequency Domain Analyses                               | 66 |

|         | 3.4.4     | Resistance against Feature Mismatches                   | 72 |

|         | 3.4.5     | Results for Low-voltage CC and CS Amplifiers            | 73 |

|         | 3.4.6     | Comparison with Other Techniques                        | 79 |

| 3.5     | Conclus   | sions                                                   | 80 |

| 4 A Sta | bilizatio | on Technique for Single-ended and Differential Harmonic |    |

|         | llators   |                                                         | 82 |

| 4.1     |           | lction                                                  | 82 |

| 4.2     |           | y Modeling for Oscillators                              | 84 |

|         |           |                                                         |    |

|         |           | lizing Gate Circuit for Process Variation               | 84 |

| 4.3     | Results   | s of Reliability                                        | 92 |

|   |       | 4.3.1        | Stabilization of LCHO                                      | 93  |  |

|---|-------|--------------|------------------------------------------------------------|-----|--|

|   |       | 4.3.2        | Stabilization of DLCHO                                     | 101 |  |

|   |       | 4.3.3        | Comparison of Performance                                  | 103 |  |

|   | 4.4   | Concl        | usions                                                     | 105 |  |

| 5 | Volta | ige Low      | vering and Gain Control Techniques for a Single-supply-dri | ven |  |

|   | 0.7-  | V Ampl       | ifier                                                      | 106 |  |

|   | 5.1   | Introduction |                                                            |     |  |

|   | 5.2   | Front-       | end Architecture                                           | 108 |  |

|   |       | 5.2.1        | Single-supply-driven Amplifier Architecture                | 109 |  |

|   |       | 5.2.2        | Three-stage Amplifier without Scaled Gate Voltages         | 113 |  |

|   |       | 5.2.3        | Effect of Common-drain Stage                               | 117 |  |

|   |       | 5.2.4        | Gain Control Technique                                     | 120 |  |

|   |       | 5.2.5        | Small-signal Circuits                                      | 123 |  |

|   |       | 5.2.6        | Parasitic Considerations of Architecture                   | 126 |  |

|   |       | 5.2.7        | Process Optimization                                       | 126 |  |

|   | 5.3   | Resul        | ts and Discussion                                          | 128 |  |

|   | 5.4   | Comp         | arison of Results                                          | 132 |  |

|   | 5.5   | Concl        | usions                                                     | 132 |  |

| 6 | A Kı  | u-band       | Low-power Amplifier with a Built-in Output Buffer          | 135 |  |

|   | 6.1   | Introdu      | ıction                                                     | 135 |  |

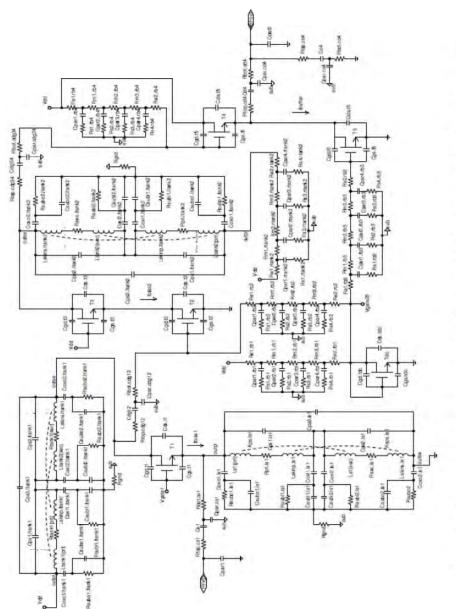

|   | 6.2   | Multist      | age Circuit Configuration                                  | 138 |  |

|   |       | 6.2.1        | Input CG Stage                                             | 138 |  |

|   |       | 6.2.2        | Secondary CSCG Stage                                       | 141 |  |

|   |       | 6.2.3        | Output Buffer                                              | 145 |  |

|   |       | 6.2.4        | Small Signal Equivalent Circuits                           | 146 |  |

|   | 6.3   | Resul        | ts with Discussion                                         | 148 |  |

| 6.4          | Performance Comparison      | 155 |

|--------------|-----------------------------|-----|

| 6.5          | Conclusions                 | 157 |

|              |                             |     |

| 7 Con        | clusions                    | 158 |

| 7.1          | Summary                     | 158 |

| 7.2          | Suggestions for Future Work | 160 |

|              |                             |     |

| Bibliography |                             |     |

# List of Figures

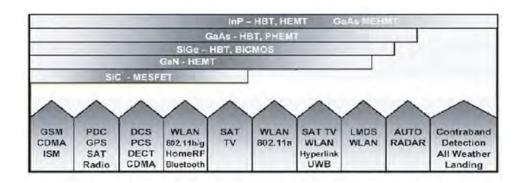

| 1.1  | Application of compound materials for various wireless technologies.     | 4   |

|------|--------------------------------------------------------------------------|-----|

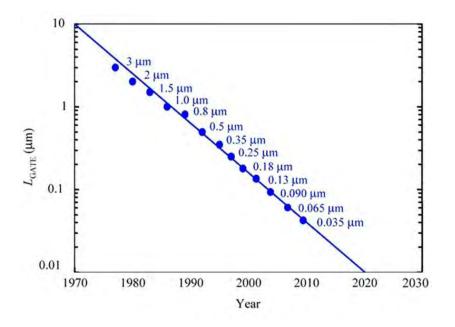

| 1.2  | The scaling trend achieved by the CMOS technologies over the years.      | 5   |

| 1.3  | Effect of scaling of the CMOS process on the number of channel           |     |

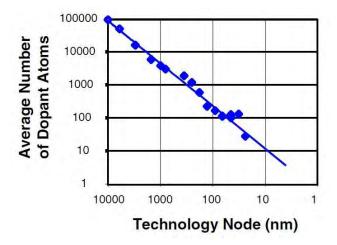

|      | dopant atoms                                                             | 17  |

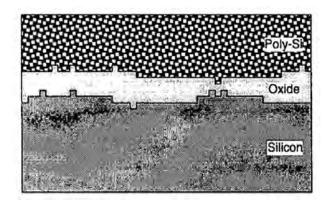

| 1.4  | Manifestation of dielectric thickness variation in a silicon technology. | 20  |

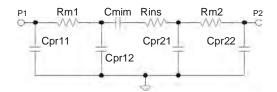

| 2.1  | Distributed RC model of MIM capacitor                                    | 32  |

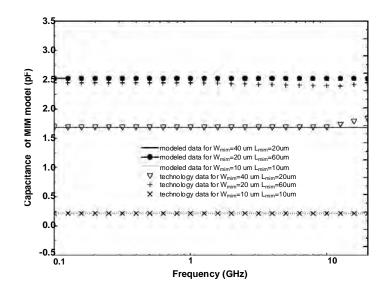

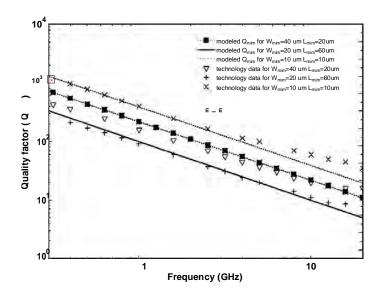

| 2.2  | Input capacitance of MIM model samples                                   | 33  |

| 2.3  | Quality factor of modeled capacitors plotted against frequency           | 35  |

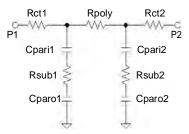

| 2.4  | Double-tee model of polysilicon resistor                                 | 35  |

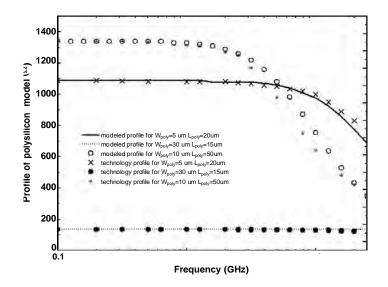

| 2.5  | Pro les of polysilicon model samples                                     | 36  |

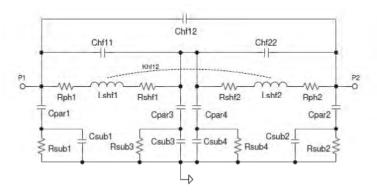

| 2.6  | Equivalent circuit model of planar-spiral-symmetric inductor             | 38  |

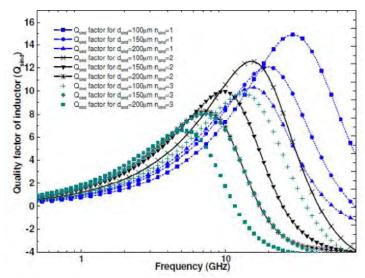

| 2.7  | Quality factors of the inductor model                                    | 40  |

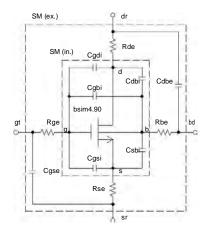

| 2.8  | Scalable composite model of an active device                             | 42  |

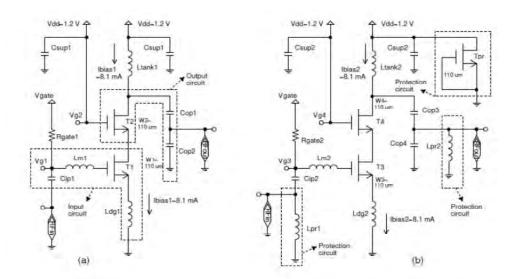

| 2.9  | CMOS circuits analyzed with the models: a) matched nanoscale le          | -wc |

|      | power amplifier and b) overvoltage-protected amplifier                   | 44  |

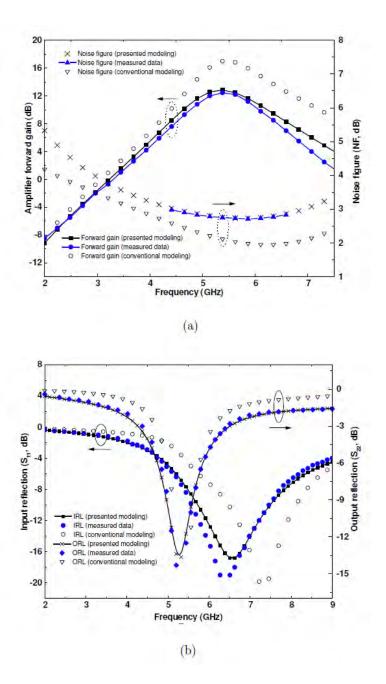

| 2.10 | Comparison in terms of a) forward gain, noise-figure and b) input        |     |

|      | reflection, output reflection between modeled and measured results       |     |

|      | of the first amplifier.                                                  | 46  |

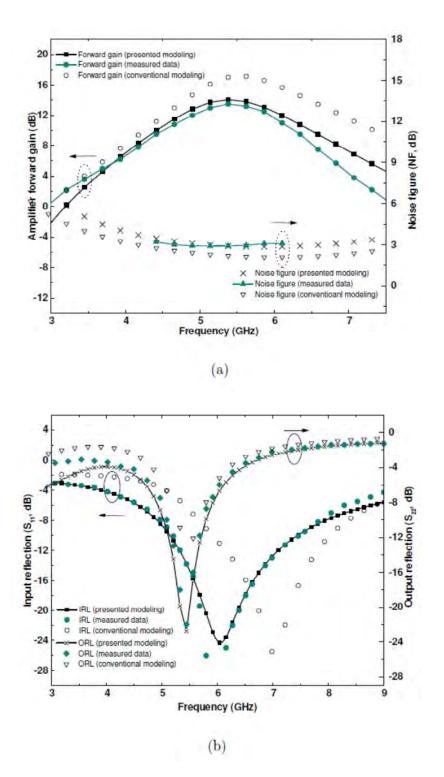

| 2.11 | Comparison between modeled and measured data of the overvolta                    | ge-     |

|------|----------------------------------------------------------------------------------|---------|

|      | protected amplifier with respect to a) forward gain, NF and b) $S_{11},$         |         |

|      | S <sub>22</sub>                                                                  | 47      |

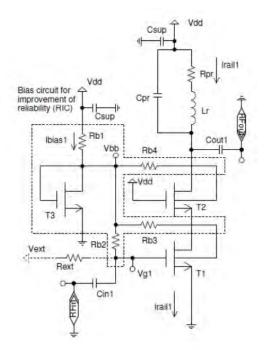

| 3.1  | The reliability improving circuit (RIC) applied to an unmatched                  | I       |

|      | amplifier                                                                        | 53      |

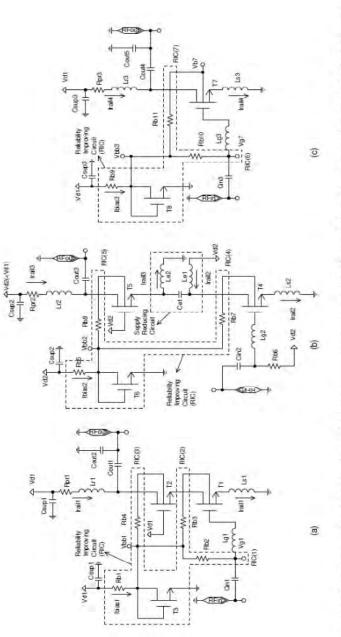

| 3.2  | Application of the RIC to a) a 1.2-V common-source-gate (CC                      | )       |

|      | amplifier, b) a low-voltage (0.7-V) CC amplifier, and c) a 1.2-V                 | /       |

|      | common-source (CS) amplifier                                                     | 58      |

| 3.3  | Effect of the RIC on the 1.2-V CC amplifier's a) $S_{21}$ and ORL                | -,      |

|      | b) NF and NF <sub>min</sub>                                                      | 62      |

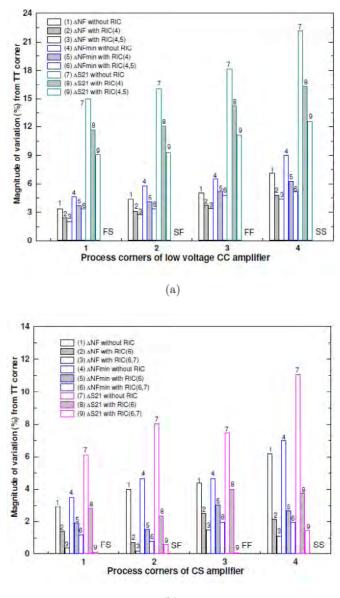

| 3.4  | Effect of the RIC on a) NF, NF <sub>min</sub> , and $S_{21}$ for the low-voltage | ge      |

|      | (0.7-V) CC amplifier, b) NF, NF <sub>min</sub> , and S <sub>21</sub> for the     |         |

|      | 1.2-V CS topology                                                                | 63      |

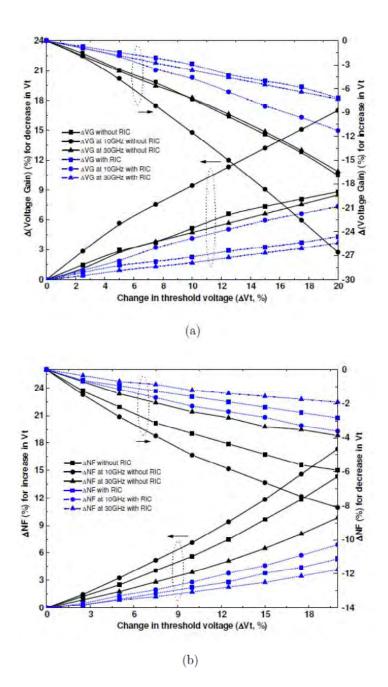

| 3.5  | Improvement against threshold variation in CMOS amplifier a)                     | )       |

|      | voltage gain and b) noise-figure                                                 | 64      |

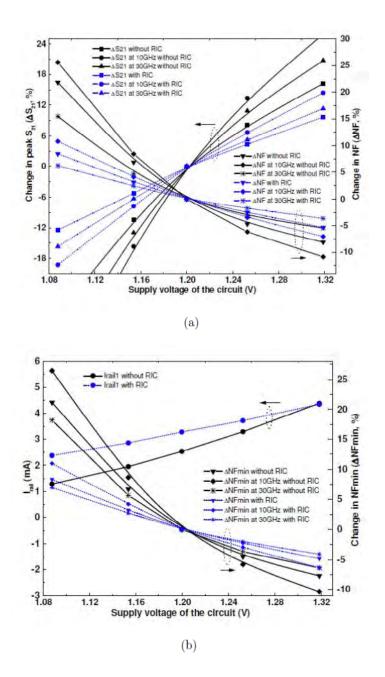

| 3.6  | Reduction of susceptibility to supply variation in terms of a) S2                | 21, NF  |

|      | and b) I <sub>rail</sub> , NF <sub>min</sub>                                     | 67      |

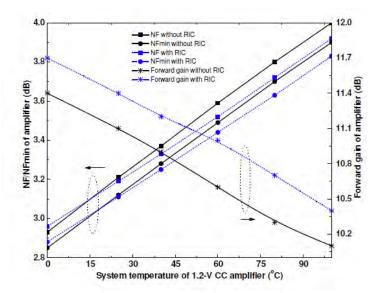

| 3.7  | Influence of thermal pro le on noise and gain                                    | 68      |

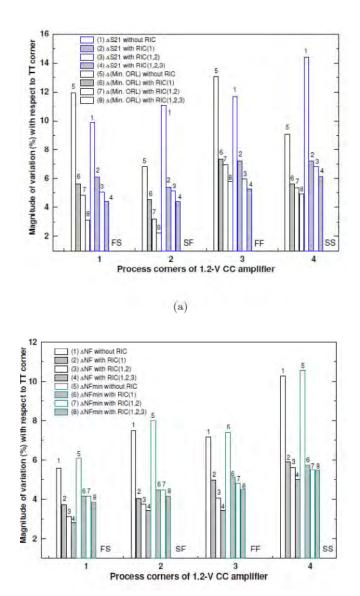

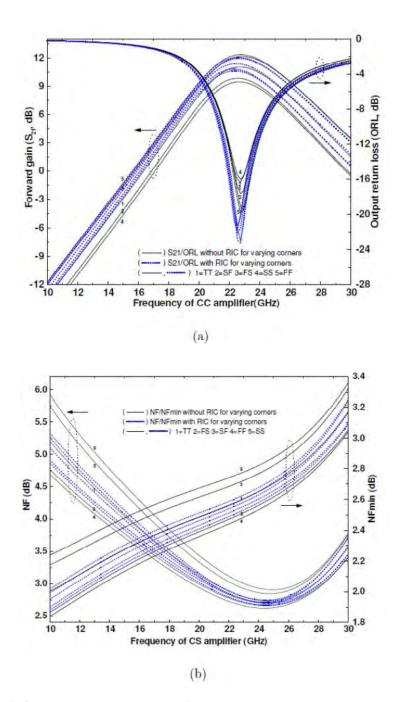

| 3.8  | a) Gain, reflection-loss and b) noise-figures for varying process poin           | nts. 69 |

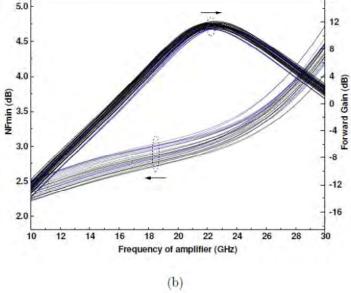

| 3.9  | Results of mismatch analysis in terms of noise and gain a) wit                   | hout    |

|      | and b) with the RIC                                                              | 70      |

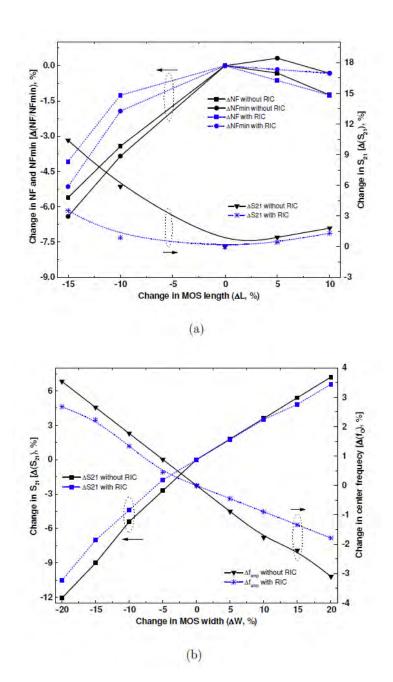

| 3.10 | ) Effect of variation in device a) feature length and b) feature wi              | dth     |

|      | on the 1.2-V CC amplifier                                                        | 71      |

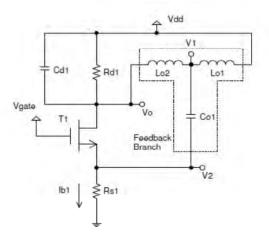

| 4.1  | A single-ended LC tuned harmonic oscillator.                                     | 84      |

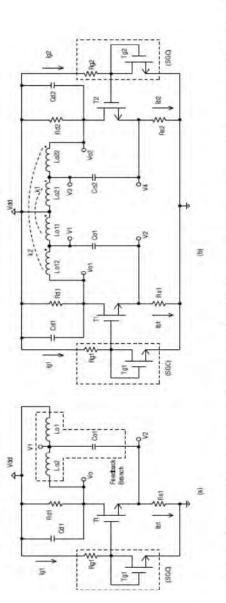

| 4.2  | a) Single-ended (LCHO) and b) differential (DLCHO) harmoni                       | с       |

|      | oscillator architectures with stabilizing gate circuits                          | 88      |

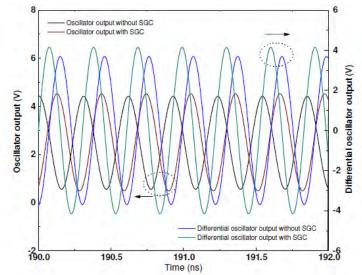

| 4.3  | Output response from uncompensated and stabilized harmonic                                             |

|------|--------------------------------------------------------------------------------------------------------|

|      | oscillator circuits                                                                                    |

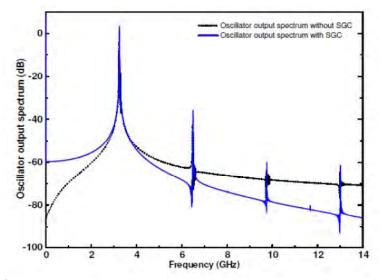

| 4.4  | Output spectrum characteristics of the harmonic oscillator (LCHO). 92                                  |

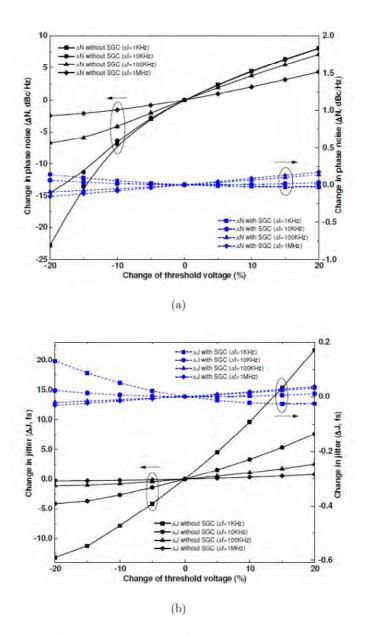

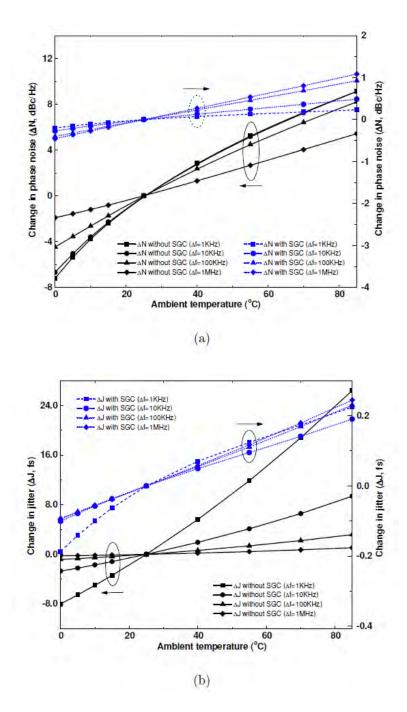

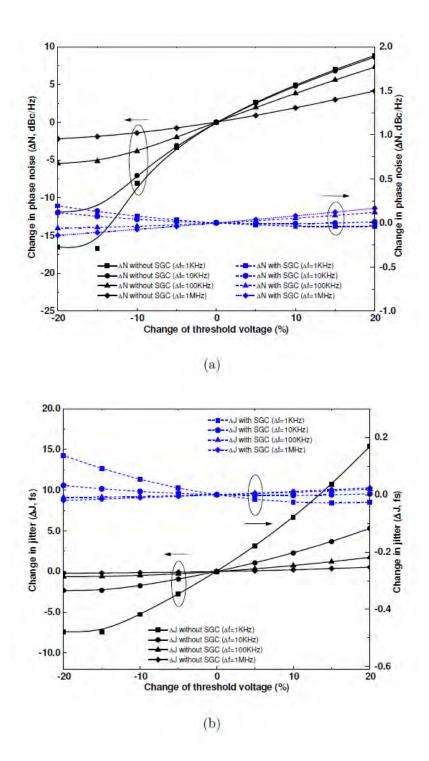

| 4.5  | Change in a) phase noise and b) period jitter against threshold shift. 94                              |

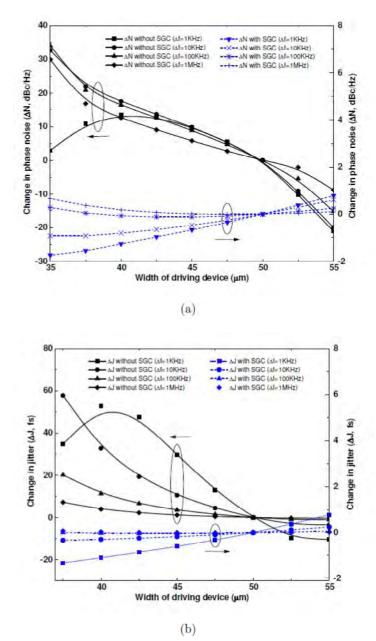

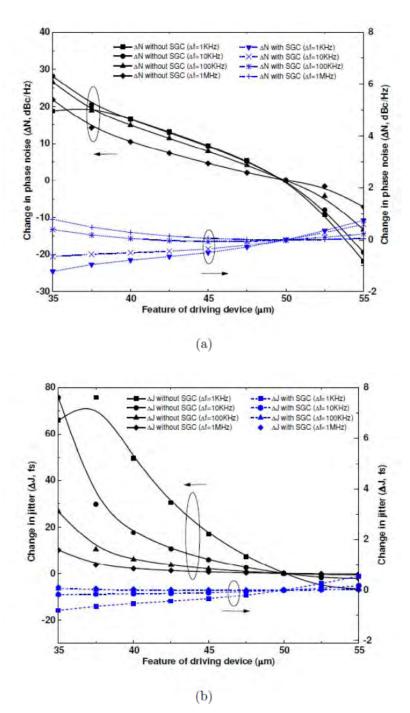

| 4.6  | Stabilization of a) noise and b) jitter against varying dimension 95                                   |

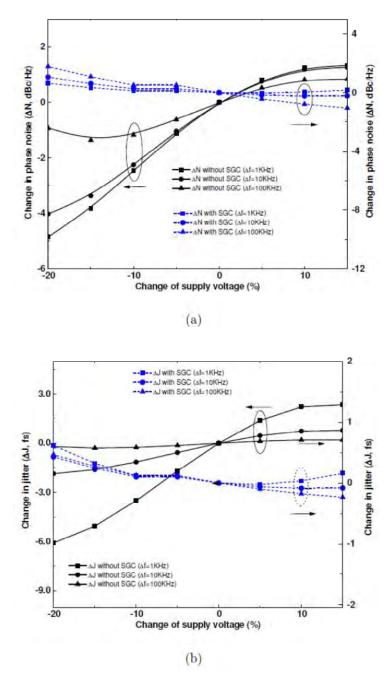

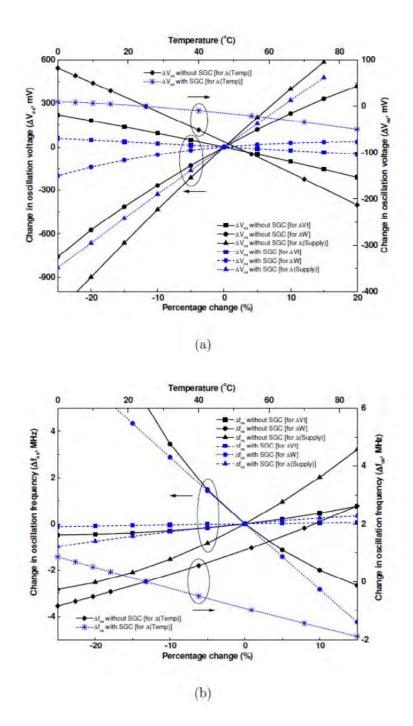

| 4.7  | Effect of variable supply on a) N and b) J of the LCHO 96                                              |

| 4.8  | Variation in a) phase noise and b) period jitter versus ambient                                        |

|      | thermal condition                                                                                      |

| 4.9  | Effect of the stabilizing circuit on a) oscillation amplitude and b)                                   |

|      | frequency of oscillation                                                                               |

| 4.10 | a) N and b) J for the DLCHO as a function of threshold shift. 100                                      |

| 4.11 | Compensation of a) noise and b) jitter in the DLCHO 101                                                |

| 4.12 | Improvement in reliability of oscillation magnitude for the differential                               |

|      | oscillator                                                                                             |

| 5.1  | A wireless receiver front-end housing a low-power amplifier 109                                        |

| 5.2  | a) An input-matched common-source-gate stage driven by a 1.2-                                          |

|      | V supply (V <sub>dd1</sub> ) and a separate gate voltage (V <sub>gate</sub> <v<sub>dd1) b) The</v<sub> |

|      | amplifier stage driven by a single lower bias supply $V_{dd2}$ (0.7-V) 110                             |

| 5.3  | a) Noise-figure (NF) and b) input/output return-loss (IRL/ORL)                                         |

|      | for the two structures presented in Fig. 5.2                                                           |

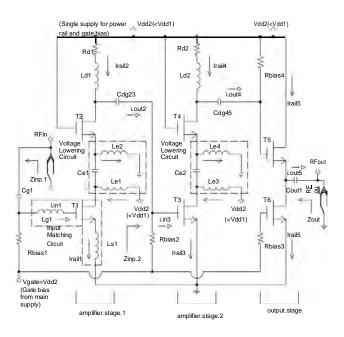

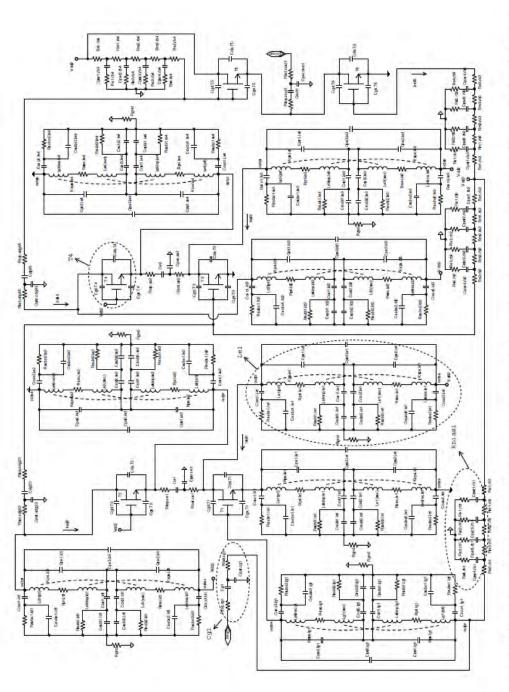

| 5.4  | The single-supply-driven CMOS amplifier architecture 112                                               |

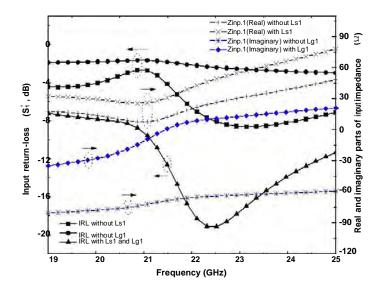

| 5.5  | Effect of matching inductors on input impedance and IRL 113                                            |

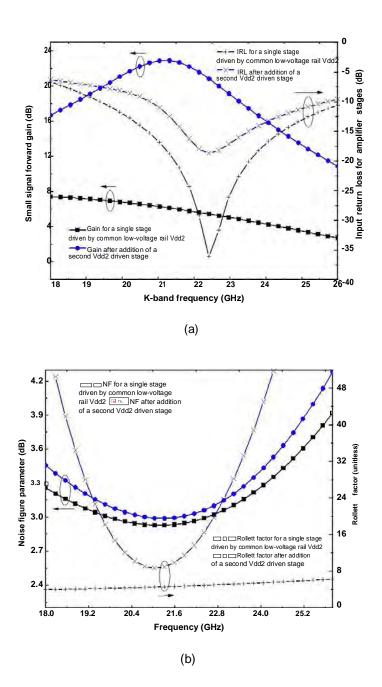

| 5.6  | a) Forward gain and input reflection, b) NF and stability factor                                       |

|      | for single- and two-stage single-supply amplifiers 115                                                 |

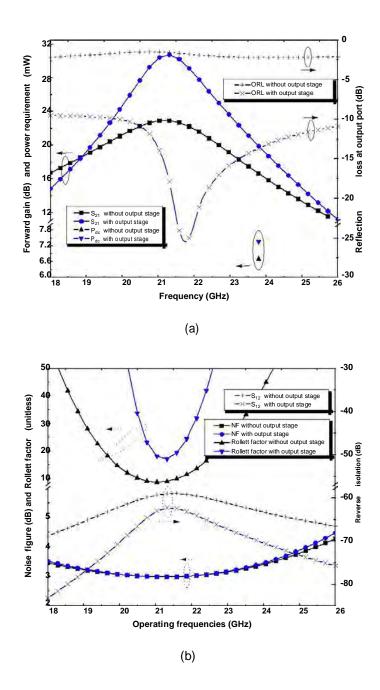

| 5.7  | The contribution of the output stage to a) forward gain, ORL, power                                    |

|      | and b) stability factor, reverse isolation, NF                                                         |

| 5.8  | Effect of variable device ratios on scattering parameters            | . 119   |

|------|----------------------------------------------------------------------|---------|

| 5.9  | The gain control technique implemented with the output stage         | 121     |

| 5.10 | Regulation of gain and power requirement as a function of out        | put     |

|      | control voltage                                                      | 121     |

| 5.11 | Small-signal equivalent circuits for the amplifier's a) input single | e-      |

|      | supply stage, b) secondary low-voltage stage, and c) output          |         |

|      | common-drain stage                                                   | 122     |

| 5.12 | The single-supply-driven architecture with possible parasitic        |         |

|      | elements generated by devices in a CMOS process                      | . 125   |

| 5.13 | Dependence of input return-loss and noise-figure on the source       | e       |

|      | inductor                                                             | 127     |

| 5.14 | Dependence of port reflection on the second interfacing capacito     | r. 128  |

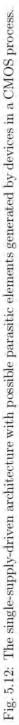

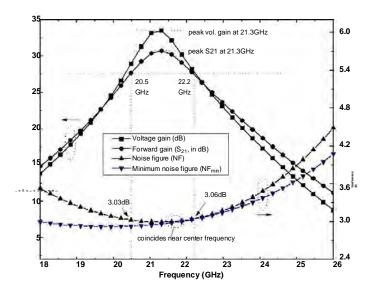

| 5.15 | Gain and noise parameters for the single-bias-supply architecture    | e. 129  |

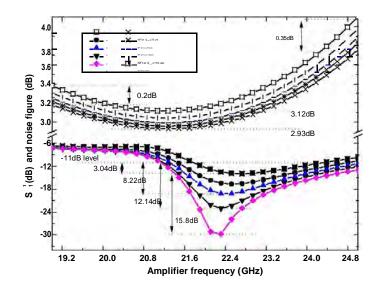

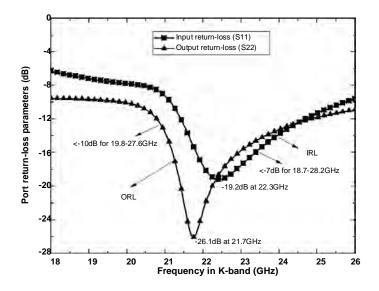

| 5.16 | Port return-loss parameters obtained over K-band                     | 129     |

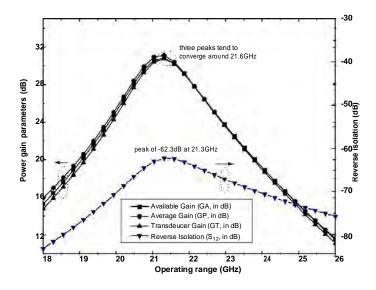

| 5.17 | Clustered power gain and reverse isolation curves                    | 130     |

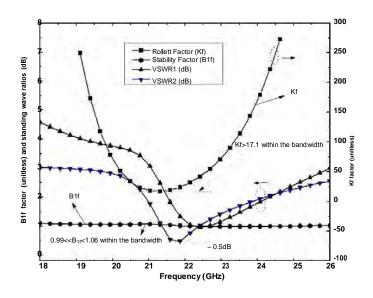

| 5.18 | $K_f$ and $B_{1f}$ factors and standing wave ratios                  | 130     |

| 6.1  | The 1.2-V low-power two-stage amplifier with bias and output         |         |

|      | circuits                                                             | 137     |

| 6.2  | Relative Effect of the input CG block and the secondary CSCC         | S stage |

|      | on a) linear amplifier operation (GCC: gain compression curve        | ) and   |

|      | b) impedance matching (input return-loss)                            | 142     |

| 6.3  | Noise contribution of di erent stages of the 1.2-V amplifier         | . 143   |

| 6.4  | Small signal equivalent circuits for a) input CG stage and b)        |         |

|      | secondary CSCG stage                                                 | 146     |

| 6.5  | The amplifier architecture with parasitic elements generated by      | у       |

|      | CMOS components                                                      | 149     |

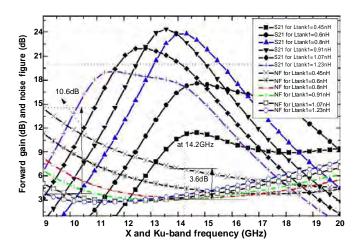

| 6.6  | The Effect of the first resonating inductor on noise contribution |        |

|------|-------------------------------------------------------------------|--------|

|      | and forward gain                                                  | 150    |

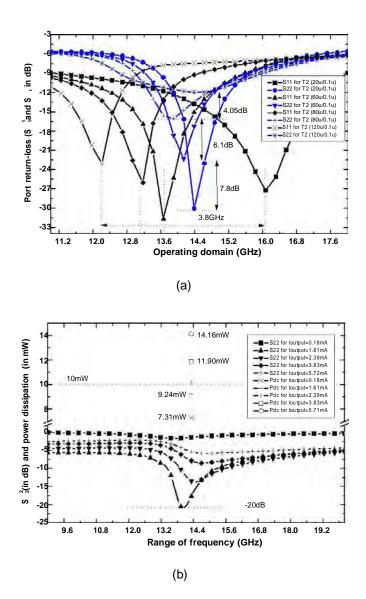

| 6.7  | a) The dependence of port reflection on device size and b) sel    | ection |

|      | of output current on the basis of power requirement               | 151    |

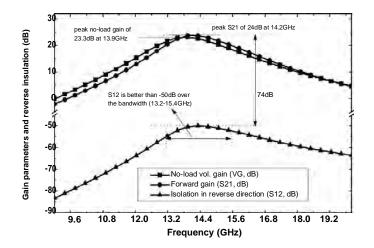

| 6.8  | Gain and reverse leakage for the amplifier.                       | 153    |

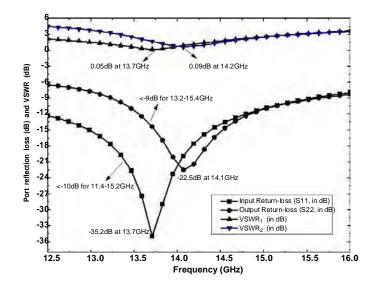

| 6.9  | Optimized port return-loss and standing wave ratios               | 154    |

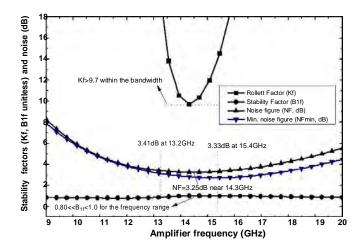

| 6.10 | Degree of stability and noise for the amplifier.                  | 155    |

## List of Tables

| 2.1 | Effective model resistance as a function of device geometry           | . 38  |

|-----|-----------------------------------------------------------------------|-------|

| 2.2 | Effective inductance of the PSS model                                 | 41    |

| 3.1 | Performance of 1.2-V CC amplifier against feature variability         | 72    |

| 3.2 | Performance of 1.2-V CC amplifier against feature variability (contd. | .).73 |

| 3.3 | Reliability of 0.7-V CC and 1.2-V CS topologies against threshold     | ł     |

|     | deviation                                                             | 74    |

| 3.4 | Reliability of 0.7-V CC and 1.2-V CS amplifiers against variable      |       |

|     | supply                                                                | 75    |

| 3.5 | Performance of 0.7-V CC and 1.2-V CS amplifiers with regard to        |       |

|     | process variation                                                     | 76    |

| 3.6 | Performance of 0.7-V CC and 1.2-V CS amplifiers against feature       | e     |

|     | variability                                                           | 77    |

| 3.7 | Performance of 0.7-V CC and 1.2-V CS amplifiers against feature       | е     |

|     | variability (contd.).                                                 | 78    |

| 3.8 | Comparison of percentage improvement in variability (PIV) achie       | ved   |

|     | by reliability compensation techniques                                | 79    |

| 4.1 | Comparison between process stabilizing techniques                     | 104   |

| 5.1 | Comparison of the presented architecture with available amplifiers.   | 133   |

| 6.1 | Comparative performance of submicron amplifiers                       | 156   |

### Abstract

During the evolution of integrated circuits, the noise content of silicon complementary metal oxide semiconductor (CMOS) process was initially considered too high, which made compound semiconductors preferable for achieving superior high frequency characteristics. Nevertheless, rapid advancement and scaling down of CMOS technology, having started with an original intention of improving digital circuits, have allowed the development of cost-efficient monolithic silicon integrated architectures for communication. An efficient way to reduce overhead of silicon circuits further is to develop accurate models of its member elements. It can significantly reduce the number of attempts (and hence cost) required to achieve desirable performance from a prototype transceiver. This study presents a technique to accurately estimate the behavior of nanoscale CMOS circuits with geometry scalable discrete modeling. Rather than individual characterization of elements as presented in literature, the scheme attempts to predict gain, noise, and reflectionloss of integrated low-noise amplifier architectures. It reduces number of dissociated parameters by formulating dependent functions through symmetric distributed modeling. Geometry scalable empirical expressions based on physical structure and describing parasitic components, which should lower the scheme's computational complexity, are developed for elements like metal-insulator-metal (MIM) capacitor, planar-spiral-symmetric (PSS) inductor, polysilicon (PS) resistor, and active device. Results obtained with the models are compared against literature data of 1.2-V amplifier circuits where high prediction accuracy is achieved for microwave parameters (S<sub>21</sub>, NF, S<sub>11</sub>, S<sub>22</sub>). In the next phase, the study focuses on a lowpower technique to improve performance reliability of CMOS amplifiers using a integrated voltage network

1

for transistors. The reliability improving circuit (RIC) significantly reduces discrepancy in amplifier gain (S21, VG), noise (NF/NFmin), and return-loss (ORL) figures (compared with other compensation techniques) resulting from variation in threshold, parasites, and supply. It performs well on both typical- (1.2-V) and lowvoltage (0.7-V) platforms of a 90-nm technology and is able to maintain its consistency within a wide frequency coverage for three different architectures. The scheme's biasing arrangement is common rail powered with respect to the amplifier which permits the overall circuit to be driven from a single supply. The reliability improving scheme is also tested as a stabilizing gate circuit (SGC) to reduce deviation of ancillary transceiver blocks (e.g., harmonic oscillators) against process variation. In this case, the SGC is able to improve fidelity of parameters like oscillation amplitude, phase noise, and period jitter with a small increase in power requirement. Process related phenomena like device aging (and attendant Effects), spatial limitations, feature uncertainty, and supply ripples are covered through provision of resistance against device threshold, and power rail variation. Singleended and differential circuits of LC tuned modified Hartley oscillators are analyzed to verify the SGC's Effectiveness for diverse front-end configurations. To reduce the probability of multiple rail variation affecting circuit behavior, the study also presents a front-end amplifier architecture with a voltage limiting technique so that it can be driven from a 0.7-V bias supply. The topology does not need scaled gate voltages and uses bias path sectioning to manage power requirement. A three-stage cascaded structure is adopted for high gain with the output common-drain block realizing a gain control mechanism. The circuit performs better in terms of power supply requirement when compared with millimeter-wave amplifiers. Moreover, the ability of an output block and an input stage to control port matching is demonstrated with the help of a multistage circuit.

### Chapter 1

### Introduction

#### 1.1 Discrete Modeling for Nanoscale CMOS Architectures

Nanoscale complementary-metal-oxide-semiconductor (CMOS) integrated architectures have been the focus of numerous recent research e orts to satisfy the high commercial demand for wireless applications involving personal (IEEE 802.15.3), local (802.11), metropolitan (802.16d), and wide (802.20) area networks [1, 2]. In this respect, the transformation from analog circuits made with discrete de-vices to single package networks initially depended on III-V materials (compound semiconductors made from groups III and V of the periodic table) as they offered better integration efficiency, high mobility of carries, and minimization of substrate loss [3]. Fig. 1.1 presents the scenario of how multiple compound technologies had been applied to realize commercial high frequency wireless applications [4]. However, with the advent of submicron CMOS technologies, the situation started to change and integrated monolithic structures built in silicon have since been widely reported to avail advantages like low cost (due to manufacturing efficiency), large production output, and compatibility with millimeter-wave communication and digital baseband circuitry [5, 6]. In addition, scaling down of the silicon process has improved radio-frequency (RF) performance of

active devices (Fig. 1.2 shows the CMOS scaling trend over the years [7]) and lowered voltage-power requirement of monolithic integrated circuits (MIC). To utilize these benefits, accurate modeling becomes an essential prerequisite during CMOS IC development and as it influences prediction accuracy of computer-aided-design schemes. Additionally, estimation of a circuit's characterizing parameters at high frequencies is usually dependent on model precision of its on-chip components. Moreover, efficiency during the design phase determines the subsequent masking cost and, as a result, Effective modeling can minimize silicon production overhead by reducing the number of iterations needed to satisfy predetermined design targets. In this respect, literature has presented a number of characterization methods for CMOS circuit components where they typically have focused on individual process elements. For instance, a partially depleted device model is presented in [8] which has the capacity to simulate floating body topologies. Low power and low voltage design of a silicon circuit is facilitated with an active resistor structure in [9]. A resistor model for floating gate metal-oxide-semiconductor structures is utilized in [10] to enhance area efficiency and improve linearity. Barth et al. [11] study a siliconon-insulator capacitor with a deep vertical trench to re ne soft error rate and critical charge limit. Electrical characterization of a dielectric ca-

Fig. 1.1: Application of compound materials for various wireless technologies [4].

pacitor is manifested in [12] which uses alumina for better leakage current and capacitance density. Polarization dependent modeling of a CMOS capacitor is discussed in [13] to investigate the controlling factors of negative quadratic volt-age coefficient. Song et al. [14] propose an insulator capacitor model to estimate circuit behavior for different bias conditions and feature dimensions. A technique to optimize planar inductor parameters has been proposed in [15] using a physical model to account for crossover capacitance and substrate parasites. A frequency dependent model of spirals is presented in [16] to estimate the Effect of magnetic coupling with dimensional considerations. Improvement of spiral characterization is achieved over field-solver techniques in [17] with a closed form approach. These examples highlight the importance of device and circuit modeling and the thesis will attempt to address the issue, with the help of a discrete modeling approach, for nanoscale integrated CMOS architectures. Rather than single element char-

Fig. 1.2: The scaling trend achieved by the CMOS technologies over the years [7].

acterization, it will try to develop geometry scalable empirical definitions for the process elements which remain valid for the ranges required in nanoscale amplifier applications. The technique will try to exploit model symmetry to enhance computational efficiency and include distributed sections to improve its prediction accuracy for high frequency architectures.

A key factor in estimating the figures-of-merit of microwave circuits is the precision of their assumed component structures which, in turn, depends on their ability to include loss mechanisms. These issues pose more challenges when circuit characterization needs to cover entire architectures (with power and bias supplies) rather than individual passive-active elements. In this case, the formulations need to limit the number of independent model parameters without compromising on prediction accuracy and simplify their interrelationships to reduce computational complexity. Additionally, for operations at high frequency, a number of events related to delay of carrier response and output distortion may have to be taken into account for making transistor predictions [18]. Moreover, the importance of the estimation process is enhanced for next generation CMOS technologies due to a number of reasons including scaling of eld Effect transistors in deep submicron regime and incorporation of multiple functionalities on a single chip.

Modeling of Passives: Although metal-oxide-semiconductor technologies have primarily made advances (indicated by continuous scaling of features) due to their compatibility with ever popular digital electronics, they have made head-way into the market of microwave integrated circuits at the same time. One of the reasons for this is the availability of high quality passive components on the silicon platform. For example, passive capacitors are essential in many submicron monolithic architectures where they may be used as reactive elements for power amplifiers, frequency oscillators, low-noise amplifiers, data converters, frequency mixers, analog Iters, intermediate-frequency Iters, and switched capacitor circuits. The specific application of capacitors in these topologies often involves matching and coupling sections of the structure. Among other examples, variable capacitors (varactors) are typically required in the frequency selective tank of voltage controlled oscillators. There are a number of forms of silicon capacitors which can achieve a reasonable quality factor, namely, interdigital structure, microstrip structure, metal-oxide-semiconductor structure, and conductor-insulatorconductor structure. Among them, interdigital structures have a maximum range of about 1 pF, and microstrip structures are used for rather small components (<200 fF). On the other hand, metal-insulator-metal structures cover a wider range of reactance and can be placed between 100 fF and 20 pF. They also su er from relatively less variability against temperature and perform well in terms of achieving linear behavior. Therefore, precise models of CMOS metal-insulator-metal capacitors, which can describe their characteristics as a function of component geometry and operating frequency, have the potential to play a pivotal role in predicting behavior of circuit passives and, additionally, they can assist in achievingfirst pass design success for capacitive elements.

Whereas active devices are the principal building blocks of any digital architecture, passive elements may take the driver's seat for realization of nanoscale analog circuits. Although they can be included and connected as o -chip components for a low-frequency application, the influence of parasitic components on their behavior starts to dominate at higher frequencies. This is particularly true for inductive elements which are essential parts of any tuned circuit and found in architectures like power/low-noise amplifiers, correlators, oscillators, and filters. As the inductances required in submicron silicon circuits are typically in the range of nanohenry, they have to be implemented as on-chip elements because, other-wise, inductive parasites generated by the assembling of components can be too high for the application. The shape of this silicon inductor is crucial for determining its performance and this aspect is often dominated by fabrication limitations imposed by the process. Although the circular shape is often preferable to optimize the performance of an on-chip spiral, process requirements may allow only right spiral angles, resulting in a rectangular coil structure. In addition, generation of rectangular or square shapes is considered to be easier even with the help of basic silicon platform tools [19]. Therefore, as a compromise between the choices, modern silicon technologies usually support polygon spirals (hexagonal and octagonal) to realize inductors which retain the benefits from both structural patterns. As opposed to a passive spiral configuration, it is also possible to realize an on-chip active inductor which depends on a gyrator structure to simulate the Effect of inductance (built with a pair of back to back connected transconductors and an intermediate capacitor) [20]. However, these components, despite being area efficient, may suffer from a high noise factor and increase the architecture's power requirement. Another option is the use of inductance of bond wires which can manage a high value for quality factors. Nevertheless, their reactance is easily influenced by manufacturing variables and undesirable coupling may result from their employment. In addition, they can be ill defined over a wide range of process variation [21]. As a result, passive spiral structures have emerged as the components which are predominantly used in nanoscale analog circuits. These planar inductors are realized on silicon and gallium-arsenide substrates and exploit manufacturing techniques and process features like metal line stacking, discriminating masking of substrate, thick dielectric material, high conductivity for metal lines, and substrate with high resistivity [22]. Models for spiral inductors may be obtained by developing lumped circuit configurations and it would be useful if they are scalable with respect to multiple structural factors. It is generally considered that characterization of silicon inductors is more di cult than that of CMOS resistors and capacitors.

Submicron Device Modeling: The low frequency and dc behavior of a transistor is typically described through an intrinsic model by a CMOS process and a tested option for this model is the Berkley Short-channel Insulated-gate Field-Effecttransistor Model version 4 (BSIM4) [23]. It is a compact model which is suitable for both digital and analog systems and uses a combination of device physics and test data to characterize measured parameters. The characterization of physical events covered by BSIM4 includes channel charge density and sub-threshold swing model, carrier mobility model, subthreshold I-V model, strong inversion I-V model, drain voltage model for current saturation, gate direct tunneling current model, asymmetric junction diode models, stress Effect model, parameters for regional difference, and subthreshold slope factor. Apart from BSIM, other examples of industry employed intrinsic device models are EKV (Enz Krummenacher Vittoz) field effect transistor model, PSP (PennState Phillips) compact model, and hierarchical HiCUM (high current model) for high-speed bipolar transistor applications. After deciding on the model core, the devices need to include extrinsic components to account for parasitic elements emerging during high frequency operation. In this domain, the intrinsic model alone is not sufficient for device characterization and, as a result, subcircuits describing relevant additions have to be appended to the core structure. These subcircuits should serve as a function of device geometry i.e. be scalable within the required range while maintaining the model's prediction capacity. In addition, series resistive elements may have to be incorporated in the structure as deep submicron transistors suffer from minute voltage drops in port regions owing to semiconductor resistivity and contact Effect [24]. These appendages are comparable with channel impedance, particularly for short channel devices, and they lose their ability to significantly alter device properties for transistors placed above the submicron regime.

#### 1.2 Improvement of Reliability for CMOS Transceiver Circuits

With the reduction in feature size for submicron silicon technologies, benefits like improved area efficiency and supply rail scaling have been achieved, but at the same time, susceptibility of nanoscale circuits to process and system variation has raised reliability issues. For instance, device threshold in a transceiver circuit may deviate from the process determined value under the influence of multiple reliability events (e.g., dopant fluctuation, bias temperature instability, hot carrier Effect, breakdown of dielectrics, CMOS aging). Threshold deviation is also the undesirable outcome of short channel limitation, which is a phenomenon able to manifest itself through conventional and reverse mechanisms. A study into the trends of process reliability analysis suggests that researchers started to characterize transistor failure events around the three-quarter point of the last century [25]. However, they focused initially on explaining the physics of the events rather than finding ways to counter their impact on the variability of figures of merit. Even during later studies, e orts were usually concentrated on quantifying device parameter deviation through measurements. The situation became more challenging during the last two decades with the introduction of improvised materials to facilitate the scaling of silicon technologies. In addition, modern submicron processes (realizing nanoscale circuits) face dimensional variability from uncontrolled parametric deviation and imperfection of manufacturing steps (related with lithography and etching phases). On top of that, factors which exist outside the architecture (e.g., supply rail and temperature stability) may have the ability to exert influence on reliability margins. These events put light on the importance of addressing process variation during the design of nanoscale circuits as the mentioned physical phenomena have the potential to affect the

lifetime of devices and packages.

The motivation behind incorporating a reliability improving technique (RIT) in a silicon circuit is to limit the fluctuation of the architecture's characterizing parameters due to process variation. Its efficacy may be judged in terms of percentage improvement in variability achieved after the RIT's inclusion in the topology. Published reports have addressed the issues involved with process reliability for various mixed-signal and digital circuits and dealt with the influence of materials/spatial-aspects on devices, physical-analytical models of technology variation, and circuit sensitivity improvement. However, investigation on power efficient voltage design techniques, which can stabilize the output of transceiver circuit blocks, remains rather limited. For example, electrical characterization of the influence of thin oxide films on transistor reliability is studied in [26]. It discusses how trap states in interfaces are passivated with the help of deuterium implantation instead of conventional hydrogen dopants. Gate oxide degradation of scaled complementary silicon devices is examined in [27] by observing time controlled defect generation (TCDG) from constant voltage stress. With the assumption of variation in activation energy following Fermi distribution, solutions for TCDG are determined from data related with gate leakage. A method to improve data retention properties of ash memory and hence reliability of silicon technologies is presented in [28] which provides resistance against channel hot carrier induced bias current limitation. To safeguard product yield and parametric reliability, a temporal degradation detection scheme is proposed in [29] which uses the control voltage of an oscillator as a dynamic performance signature. Kim et al. [30] study a leakagecurrent sensor serving as a process compensating technique to reduce deviation in robustness/delay and supply sensitivity. A general discussion on the impact of parameter variation on scaled silicon technologies is provided in [31] with a particular emphasis on microarchitectures to achieve

high frequency bins. Matching networks made with passive components, which are insensitive to process factors, ensure optimal noise-power match, and can be extended to broadband matching, are detailed in [32]. The influence of structural factors on dielectric breakdown in scaled silicon devices is manifested in [33] with emphasis on the mechanism of soft and other breakdown events. These illustrations signify the importance of understanding the role of reliability improving techniques for submicron architectures which will be explored in this dissertation.

To realize an Effective RIT for a submicron receiver chain, which is built by cascading a number of milimeter-wave circuits, we have to make a relative assessment of noise and gain contribution of the individual blocks. This is complicated by the fact that the operating frequency of CMOS receiver front-ends has been continuously pushing upward during the last two decades [34]. As mentioned before, initial radio-frequency front-ends were predominantly designed with structures like PHEMT (pseudomorphic high electron mobility transistors, GaAs/InSb/AISb) and HBT (heterojunction bipolar transistors, SiGe/GaAs) as they provide better noise performance (albeit with higher overhead and fabrication challenges) [35]. However, scaling down of CMOS process below 0.35- m has led to the reporting of numerous transceiver architectures in silicon [36, 38]. They have been employed as circuits suitable for applications like short-distance high-capacity wireless schemes, radar systems, and satellite communication. Ad-vantages offered by these nanoscale silicon architectures include higher performance per watt (PPW) for central processing units [39], limited power demand, high yield, and level of achievable integration for networks-on-a-chip. On the issue of the relative importance of CMOS transceiver blocks, the low-noise amplifier (LNA) which follows the antenna-filter section of a front-end proves to be the overall performance determining component. This amplifier determines the entire receiver's noise sensitivity and controls noise-figure (NF) of the following

blocks by its bandwidth limited forward gain. Additionally, the amplifier's in-put port has to be matched to an ideal characteristic impedance to interface it efficiently with the preceding segment. Regulation of port impedance remains as an important design issue as it controls the extent of attenuation when signal is transferred between the transceiver blocks. To complete the design of this amplifier, a number of trade-o s between factors like power limit, noise level, and gain have to be considered for optimization of performance. Consequently, a multistage topology may be employed to realize a high-gain low-noise front-end with its multiple stages adopting a combination of common-gate, common-drain, and common-source blocks. In addition, as the silicon process scales down, simultaneous lowering of supply voltage helps to curtail receiver power requirement and voltage demand can be relaxed even further if the chain can be driven from a single supply rail. Literature on reported sub-180nm amplifiers shows that, in addition to the main voltage rail, the circuits typically include multiple lower gate signals to place active devices in suitable modes. As a result, the package requires multiple regulated rails which result in an increased probability of supply ripples affecting circuit behavior. At the same time, the gain boasted by the amplifier needs to be sufficient as the received signal can be a variable and possess a rather small power rating. Therefore, the front-end would be able to cover a wider range of signal strength if it can house a gain control mechanism. In conclusion, the pivotal role played by the low-NF amplifier on overall transceiver performance means that an efficient reliability improving circuit for the nanoscale amplifier will positively influence and stabilize the front-end's behavior.

*Categories of Unreliability Events*: The downscaling of CMOS process, which has often been cited as aggressive, has been fueled by a number of technical and commercial reasons like improving circuit speed, raising number of devices per chip, curtailing power demand, and achieving better cost efficiency. However, practical limitations like reliability events started to affect this trend even before gate lengths became literally comparable with atomic dimensions, thus making additional scaling physically impossible. The technology's progress is also influenced by practical considerations involving matters like development cost, performance ceiling, and yield sufficiency. This subsection brie y discusses the classification of reliability events which appear as drawbacks as we move into the realm of nanoscale devices and circuits. Generally speaking, silicon reliability features can be divided into two categories: spatial unreliability and sequential unreliability, and both of them contribute to different aspects of process variation [40]. Time-related sequential unreliability issues have branches like CMOS aging and transient occurrences while spatial unreliability includes systematic effects and arbitrary perturbations. Silicon process variations can additionally be classified according to their relation with intrinsic events and foundry induced deviation. In this case, the former mechanism is attributed to constraints of device physics and the later mechanism can be associated with imperfections of manufacturing steps and process limitations. One of the first time dependent unreliability issues to be studied in literature was time dependent breakdown of dielectrics which became important as oxide layer was thinned down to atomic dimensions [41]. It was observed that, scaling of oxide increased the Effect of gate electric field and allowed injection of hot carriers to take place, thus degrading transistor performance. To walk around the limitations faced by a scaled silicon process, researchers tried out modification of materials and device construction. Yet, there were cases where the alteration had an adverse impact on reliability issues (e.g., negative and positive bias temperature instability) [40]. These experiences ensured that process variation was treated as a separate field for submicron technologies as the topologies became more sensitive to the Effects of parameter fluctuation. Moreover, the possibility of device features to be located within a

probable spread have to be taken into account to estimate the tolerance of circuit output and guarantee an acceptable yield. As the reliability events ultimately produce deviation in parameters like device threshold and feature, more investigation is required on circuit techniques which can work as process compensation schemes without compromising on overall performance.

Sequential reliability issues (SQRI) are dependent on time and controlled by a number of ambient/operating conditions (e.g., die temperature, voltage inputs, action of neighboring systems). They can be related to the natural degradation of circuit performance over its lifetime (referred to as CMOS aging) and short duration transient events. Examples of SQRIs include hot carrier Effect (HCE), negative bias temperature instability (NBTI), positive bias temperature instability (PBTI), time dependent breakdown of dielectrics (TDBD), and random telegraph noise (RTN). In contrast, spatial reliability issues (SPRI) are independent of time and controlled by manufacturing parameters, technology limitations, process materials, and architectural geometry. Even a newly fabricated prototype can manifest the Effect of these events. The dominant examples of SPRI involve line width/edge roughness (LWER), dopant perturbation (DP), dielectric thickness variations (DTV), and gradient Effects (GE). In the next subsection, the mechanisms of dominant reliability events behind process variation are brie y explained.

Hot Carrier Effects (HCE): For a CMOS technology, the term `hot carrier' refers to carrier particles in the MOS device which attain a relatively high amount of kinetic energy from being driven through a strong electric field. Physicists have identified four different types of energetic carriers up to now which may be categorized as channel hot carriers, secondary generated hot carriers, substrate hot carriers, and drain avalanche hot carriers. The higher energy of these particles allows them to enter undesirable regions of the device where they can create trapped charges and interface states. Ultimately, the consequence of these defects is the alteration of parameters like threshold voltage and process transconductance. The threshold deviation due to hot carrier Effects is generally described with the help of a time dependent power law [40]:

$$\Delta V_t \propto \frac{1}{\sqrt{L_e}} exp^{(\alpha_1 E_{ox})} exp^{(-\frac{\alpha_2}{E_m})} t_s^{\ n}.$$

(1.1)

In this equation, n is the rate coefficient (with various values),  $E_{ox}$  is the oxide electric field,  $E_m$  is the maximum value of lateral electric field,  $t_s$  is modeled as the stress time, and  $\square$  are process dependent factors. The equation suggests that hot carrier Effect has strong (exponential) dependence on oxide electric field and lateral electric field. Alternatively, the threshold deviation model may be expressed as a function of electron mean free path ( $\square$ ), energy of trap generation ( $\square$ ), and inversion charge (Q<sub>inv</sub>) [42]

$$\Delta V_t \propto \sqrt{Q_{inv}} exp^{\left(\frac{E_{ox}}{E_1}\right)} exp^{\left(-\frac{\phi_{tg}}{\lambda_{eqE_m}}\right)} t_s^{\ n} \tag{1.2}$$

where E<sub>1</sub> is also a process dependent factor. Hot carriers can be a problem for both n- and p-channel devices, as it affects NMOS parameters directly and influences PMOS bias temperature instability. The techniques which have been adopted to counter hot carriers have included graded junctions and lower supplies which reduce the probability of carriers assuming high kinetic energy. In addition, the use of high dielectric-constant metal gate (HKMG) process may make the dielectric layer less susceptive to intrusion of carrier traps. Nevertheless, energetic carriers remain as a stability concern for scaled silicon technologies.

Dopant Perturbation: Dopant perturbation (DP) refers to a phenomenon where variation of impurity concentration in the channel region results in alteration of device properties like turn-on voltage. It is an event which is particularly susceptible to channel scaling and has been termed as one of the significant sources

of process variation for active devices. As the total number of dopant atoms in the channel region decreases for smaller devices (the trend is demonstrated with the help of Fig. 1.3), the impact of dopant profile fluctuation becomes more visible on device behavior. Although a few compensating engineering steps (e.g., retrograde doping) have been proposed against DP, their Effectiveness is found to be limited for processes below 180-nm [44]. Impact of DP primarily manifests itself with a spread of device threshold and is influenced by relative position of dopants and disparity of distribution in the channel. In this respect, literature has reported that more than half of total threshold variation for silicon devices can be attributed to dopant shifts in sub-100nm technologies [45]. The deviation of device threshold obtained from an analytical model of arbitrary dopant fluctuation was initially derived as [46]

$$\Delta V_t \propto q \frac{t_{de}}{\epsilon_{de}} \frac{\sqrt{NW_{dep}}}{\sqrt{L_e}}.$$

(1.3)

Here N is the number of dopant atoms in the channel, q is the carrier charge,  $W_{dep}$  is the depletion layer width under gate, L<sub>e</sub> is the Effective channel length,

Fig. 1.3: Effect of scaling of the CMOS process on the number of channel dopant atoms [43].

and is the dielectric permittivity. The expression was later modified with a correction factor for uniform doping:

$$\Delta V_t \propto \frac{2}{\sqrt{3}} q \frac{t_{de}}{\epsilon_{de}} \frac{\sqrt{NW_{dep}}}{\sqrt{L_e}}.$$

(1.4)

Among the control factors of this expression, feature size exerts a dominating influence which may result in a disagreement between predicted deviation and measured data for short channel devices. A more frequently used statement of threshold deviation may be derived from the overall variation in total depletion charge (which reflects dopant perturbation) in the form of [47]

$$\Delta V_t \propto \frac{t_{de}}{\epsilon_{de}} \frac{\sqrt[4]{N}}{\sqrt{L_e}} \frac{\sqrt[4]{4q^3 \phi_B \epsilon_{si}}}{2} \tag{1.5}$$

$$\phi_B = 2k_B T \ln(\frac{N}{n_i}). \tag{1.6}$$

Here  $k_B$  is the Boltzmann constant,  $n_i$  is the intrinsic carrier concentration, and

is the permittivity of silicon. To have an understanding of the impact of these mechanisms on process variation, it may be noted that ratio of dielectric thickness to permittivity and dopant concentration decreases with technology scaling. However, Effective channel area is reduced at the same time and, as a result, process variation induced by dopant perturbation becomes evident for scaled CMOS processes.

Line Width-Edge Roughness (LWER): The distortion occurring along the edge of an active layer is usually termed as line edge roughness (LER) and, consequently, LER occurring along both edges of the layer leads to variation in feature width and is called line width roughness (LWR). Although DP is often cited as the dominant source of transistor deviation, it is predicted that LWER could take its place as features are pushed below the 65-nm line. LWER is mainly due to the limitation of the etching process which, in turn, is related with the source used for subwavelength lithography. Initially, source wavelength in a CMOS process was scaling with feature size, but it has been fixed at a constant position (193-nm) for deep submicron generations (below 130-nm). The main Effect of LWER gets visible for cases of gate patterning which ultimately result in modification of device threshold and subthreshold current. To complicate things further, al-though aspects of etching technology have been improving continuously, process deviation induced by LWER does not decrease in a proportionate manner. The physical events causing this phenomenon include photon flux variation, finite size of dissolved resist polymers, and distribution of resist chemicals, but their relative contribution is yet to be quantified. In addition, LWER is partly attributed to photon shot noise which is described in terms of deviation of intensity ( $\square$ ) during the lithography process. It is typically calculated with the help of characteristics of Poisson distribution [48]:

$$\frac{\delta_I}{\langle I \rangle} = \frac{1}{\sqrt{\langle N_{ph} \rangle}} = \frac{\delta_{N_{ph}}}{\langle N_{ph} \rangle} = [\langle I \rangle At \frac{\lambda}{ch}]^{-\frac{1}{2}}$$

(1.7)

$$I = \left(\frac{N_{ph}}{At}\right)\left(\frac{ch}{\lambda}\right). \tag{1.8}$$

Here is the source wavelength, h is the Planck constant, Nph is the number of photons which travel over an area of A over the time frame t and < Nph > is the expectation value of the photon population. The probability of availability of Nph photons can also be described by the Poisson distribution of binomial equations:

$$P(N_{ph}) = \left[\frac{(Lt)^{N_{ph}}}{N_{ph}!}\right]e^{-Lt}.$$

(1.9)

Here L is the average rate of photons emitted per unit time from the source and it is assumed that Lt remains a finite quantity as Nph approaches infinity.

Dielectric Thickness Variation: Dielectric thickness variation (DTV) is an issue which becomes apparent as area of the gate dielectric material is scaled down. It can be ascribed to surface roughness of the oxide-silicon interface at atomic level of a CMOS platform [49]. Even for next generation devices

using HKMG technology, DTV becomes a problem due to roughness of multi-ple interfaces existing between combinations like metal-gate/dielectric-layer and dielectric-layer/substrate. A manifestation of this phenomenon is presented with the help of a cross-sectional diagram of a silicon technology in Fig. 1.4. Research has shown that threshold variability from DTV can be observed independently from Effects like DP and LWER. Although this type of threshold fluctuation is primarily accompanied by deviation in tunnelling leakage current, other physical Effects of the event may include variation of drive current and carrier mobility. In this respect, the relationship between dielectric thickness variation (

$$\frac{\Delta_{I_{gt}}}{I_{gt}} = k\Delta_{t_{de}} = \frac{[(\frac{\partial I_{gt}}{\partial t_{de}})^2 \Delta_{t_{de}}^2]^{\frac{1}{2}}}{I_{gt}}.$$

(1.10)

Here k is a constant which is dependent on dielectric voltage, potential of barrier, and Effective mass of electron. Apart from DTV, non-ideal features involving gate dielectric may also arise from defects like oxide trapped charges and traps in the interface. In addition, advanced processes using HKMG devices have the potential to exacerbate the Effect of fixed charges in oxide. It may also lead to

Fig. 1.4: Manifestation of dielectric thickness variation in a silicon technology [50].

fast transient charge-trapping and result in degradation of device parameters.

Time Dependent Breakdown of Dielectrics (TDBD): Breakdown of dielectric material was observed as a degrading mechanism even in older CMOS processes with thicker oxides (>10-nm) but the underlying complex mechanism was not well understood. However, the situation started to change during the nineties as the improved silicon platforms allowed a wider variety of oxide dimensions to be employed. In this respect, it was found that the gate drive of a device primarily depends on gate voltage and dielectric thickness and is governed by Fowler-Nordheim tunneling for thick-oxides and quantum tunneling for thin-oxides (and lower voltages) [52]. Depending on the strength of applied electric field and aging, the dielectric sees an accumulation of different types of defects like recombination centers, carrier traps, and interface states. Additionally, the mechanisms of defect generation include trap creation from anode degradation at low voltages and holeinjection/impact-ionization for induced defects at higher voltages. With the passage of time, the extent of damage to the dielectric is manifested by parameters like stress induced leakage current and ultimately leads to soft, progressive, or hard breakdown (SBD/PBD/HBD). Here, different modes of the mentioned breakdowns may occur independently or one following the other. For SBD, the increase in gate injection is rather slow and the device remains functional with degraded dielectric properties and increased gate noise. For submicron technologies below 180-nm (Eox>2.4 MV/cm), SBD and PBD seem to be the dominant mechanisms behind dielectric degradation. Generally, the time to breakdown (Tbd) is defined with the help of instantaneous value of current density through gate dielectric (Jg). If Qbd is the time integrated dielectric current density (which flows until the breakdown of dielectric), the following relationship will hold for constant voltage stress for thin oxides (where current changes very little before

breakdown) [52]:

$$T_{bd} = \frac{Q_{bd}}{J_g}.\tag{1.11}$$

On the other hand, in case of hard breakdown, the cumulative density function for time to breakdown F ( $T_{bd}$ ) may be described with the help of Weibull probability distribution [53]

$$F(T_{bd}) = 1 - exp[-(\frac{T_{bd}}{\alpha})^{\beta}]$$

(1.12)

where  $\square_{1}^{\infty}$  and  $\square_{1}^{\infty}$  are process dependent factors, and typically, is called the characteristic life and is called the Weibull slope or slope parameter.

Bias Temperature Instability: Bias temperature instability (BTI) is another unreliability issue which affects all types of field Effect transistors after continuous operation at high temperatures. Two different forms of bias temperature instability have been experimentally verified: negative BTI (NBTI) and positive BTI (PBTI). Among the two, research on NBTI has been carried out for a longer period of time which shows that it can create threshold deviation across typical process, silicon oxynitride process, and next generation transistor structures. The mechanism behind BTI is not well understood and possible explanations have included build-up of charge in dielectric, interface states at oxide channel juncture, hole capturing by defects, and electron trapping by dielectric traps. Certain process steps like nitridation and surface channel devices are also believed to cause progression of BTI induced degradation. Historically, first attempts to explain bias temperature instability depended on reaction diffusion theory rather than charge trapping. It was able to explain the dependence of degradation on time adequately but fell short while trying to expound features of recovery. According to it, normalized reaction diffusion induced variation takes the form of [54]

$$\frac{\Delta V_t(t_s, t_r)}{\Delta V_t(t_s, 0)} = \frac{1}{1 + \left(\frac{t_r}{t_s}\right)^{\frac{1}{2}}}.$$

(1.13)

Here,  $t_s$  and  $t_r$  are stress time and relaxation time. The equation assumes universal recovery where threshold deviation depends on the ratio of  $t_s$  and  $t_r$ , and the relationship is normalized with respect to its value at stress end point. But this supposition opposed observations which suggested that recovery progresses without depending on stress time and becomes operational even before stress end point. Therefore, more recent models of BTI assume a combination of a fixed element and a rectifiable part for process deviation. If  $n_f$  and  $n_r$  are rate coefficients for the fixed and the rectifiable parts,  $E_a$  is the activation energy,  $m_f$  is another constant for fixed degradation, and  $\underbrace{[energy]}{energy}$  are process dependent factors, the threshold deviation model can be written as [55]

$$\Delta V_t \propto [exp^{(\delta_1 V_{gs})} t^{n_f} + V_{gs}^{\delta_2} \{m_f + n_r log(t)\}] exp^{(-\frac{L_a}{k_B T})}$$

(1.14)

where the equation remains valid if the stress voltage remains unchanged.

Short Channel Limitation: Devices of a silicon technology may also suffer from modification of threshold and drift characteristics as a result of short channel limitations (SCL). SCL becomes a factor for field effect devices when its channel size becomes comparable with the width of junction depletion layers. It can be understood by the fact that channel depletion charge is not only balanced by gate charge, it is also partially adjusted by charge in source/drain junctions which, in turn, is strongly correlated with channel size. Consequently, device reliability may be influenced as channel limitation affects parameters which are supposed to remain invariable against bias condition and feature dimension. In addition, the physical phenomena through which SCL can manifest itself can be as varied as velocity saturation, scattering at surface, ionization by impact, and drain induced lowering of barrier. The threshold modification due to short channel limitation

can be approximated as [56]

$$\Delta V_t \propto (\frac{x_j}{2L_e}) \sqrt{2q\epsilon_{si}N|2\phi_f|} \left[ (\sqrt{1 + \frac{2x_d}{x_j}} - 1) + (\sqrt{1 + \frac{2x_s}{x_j}} - 1) \right].$$

(1.15)

Supply and Temperature Variation: Apart from the phenomena related with device physics, CMOS reliability is also a ected by operation-related and ambient factors like supply and temperature variation. Involvement of aggressive scaling, design for high performance, higher operating frequencies, combination of multiple functionalities, and rising power density increase the probability of signi cant intra-die thermal variation. Among operating factors, continuous circuit operation can lead to supply noise and ultimately supply uctuation [57]. Moreover, silicon supply reliability may have a correlation with the architecture's voltage conditions. As companion to the main supply rail, CMOS structures typically require a number of scaled gate signals to place transistors in a suitable mode. If their number can be truncated, it would relax the circuit's voltage requirements and limit the combined upshot of multiple rail stability on overall performance. On the other hand, circuit induced variation of temperature may obtain the ability to produce nonuniform substrate thermal pro le and thermal gradients in the architecture. These uctuations have an impact on a number of circuit mechanisms including device transconductance and leakage current. Leak-age current is one of the non-ideal factors which may account for about a tenth of system's power requirement and its contribution is projected to increase by mul-tiple times for the future silicon technologies [58]. This phenomenon can have two

distinct sources: subthreshold leakage and gate leakage components. Subthreshold leakage was considered as the dominant source for older processes but gate leakage becomes equally important for technologies with scaled dielectric layers. In addition, fluctuation of operating and ambient factors has an influence on an architecture's current rating, which in turn determines several figures of merit for the circuit. As a result, system reliability is affected by unexpected deviation of supply voltage and system temperature.

The reliability events described in the previous subsections have the potential to significantly degrade circuit consistency, may lead to unacceptable circuit variation, and highlight the importance of considering process deviation during design phases of a CMOS system. Under such circumstances, a reliability improving technique may be included in circuits of a transceiver to reduce variation of the system's figures of merit. In case of submicron amplifiers, these RITs need to work with different voltage ratings and stabilitate characterizing parameters against deviation of process and system factors. In addition, it will be beneficial if the compensation technique can be adapted as a stabilizing mechanism for other blocks of the transceiver (e.g., oscillators) where it will face the challenge of improving the variability of a different set of frequencydependent parameters.

#### 1.3 Objective of the Thesis

The objective of this thesis includes devising a discrete modeling technique of and establishing common rail powered reliability improving techniques for nanoscale silicon transceiver circuits. At first, it will attempt to develop a scheme to accurately predict characteristics of complementary-metal-oxidesemiconductor (CMOS) circuits through geometry scalable modeling of their discrete components. It will focus on forecasting of noise, loss, and gain parameters for complete architectures (e.g., low-noise amplifiers) rather than separate characterization of circuit elements (passives, transistors). It will try to regulate number of independent parameters needed for model equation formulation with symmetry of distributed model structures and through exploitation of parameter interdependency. Compact equations based on empirical modeling will be developed for devised equivalent-circuits of metal-insulator-metal capacitors (MIMC), planar-spiral-symmetric inductors (PSSI), polysilicon resistors (PSR), and active transistors. The models will cover the size of devices required in reported nanoscale CMOS circuits and modeled results will be compared against literature data for verification.

- 2. Additionally, the thesis will focus on a common rail powered technique to improve performance reliability of CMOS circuits through a shared bias network for active devices. The reliability improving circuit (RIC) will try to increase the stability of a topology's amplification (voltage gain, forward gain), noise (noise figure, minimum noise figure), and port loss (input/output reflection) against variation of process and voltage. It will be verified for a number of front-end architectures which will ensure that the RIC remains compatible with a wide range of isolation, noise, linearity, and gain requirements.

- 3. To investigate the reliability improving scheme's Effectiveness for additional transceiver blocks, it will be applied as a stabilizing gate circuit (SGC) to a harmonic oscillator against aspects of technology and system deviation. Without incurring significant power penalties, the SGC will attempt to im-prove the consistency of important oscillator parameters like phase noise, period jitter, and oscillation amplitude. Various phenomena related to pro-

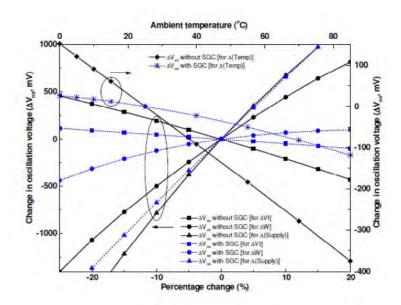

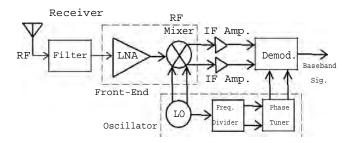

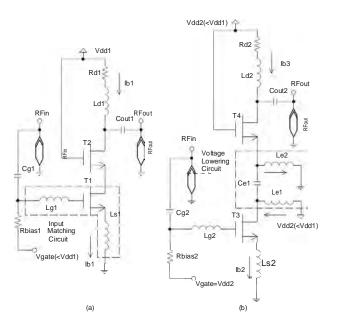

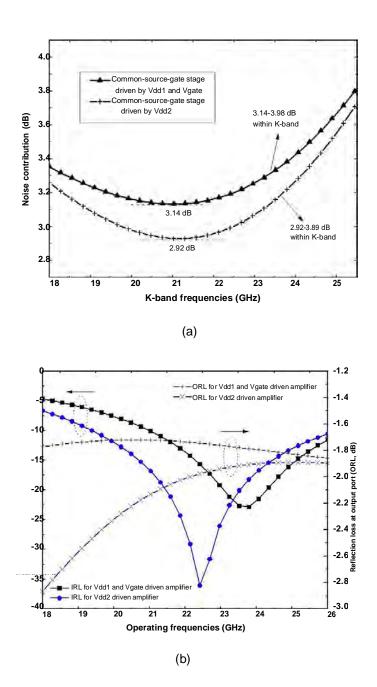

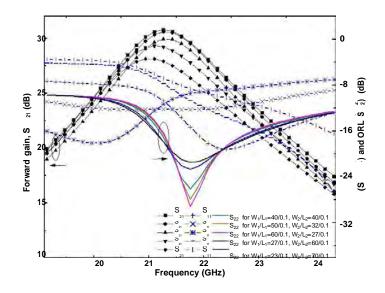

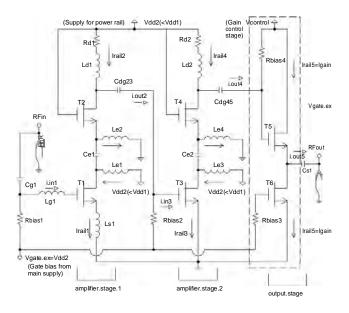

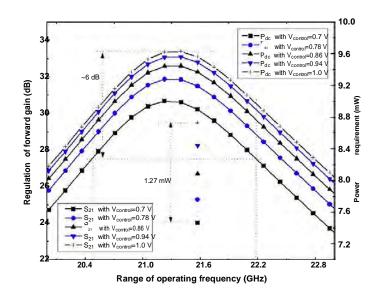

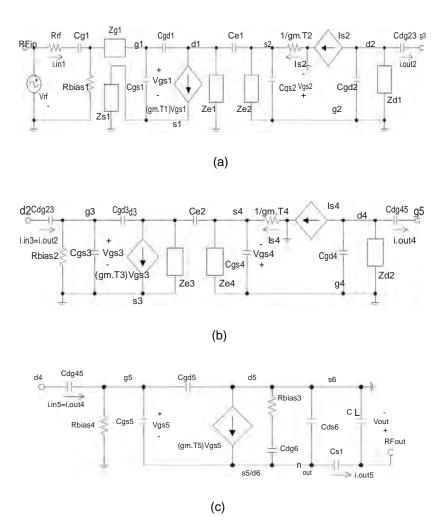

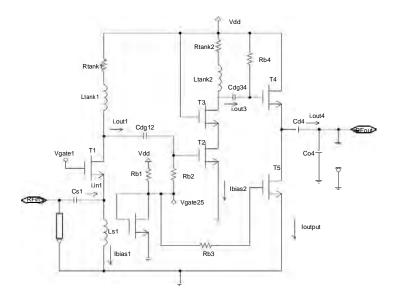

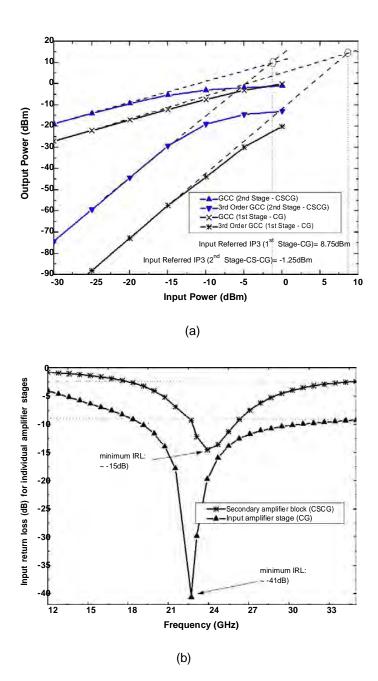

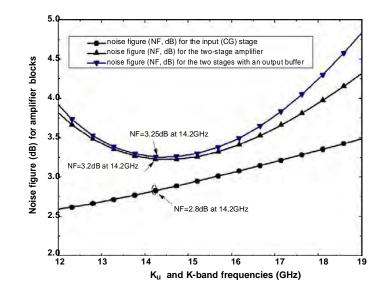

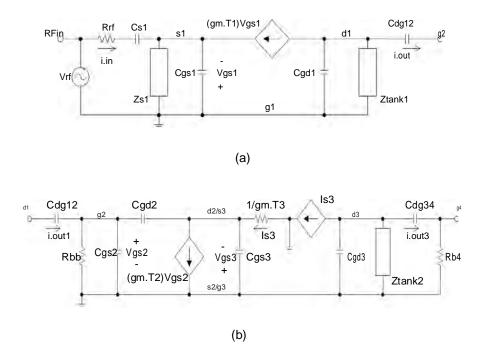

cess fluctuation will be addressed through consideration of device threshold, feature dimension, and power rail variation. The technique will try to be efficient for a wide range of o set frequencies and it will be compared with reported compensation mechanisms.