## AN INVESTIGATION INTO SOME

METAL-SILICON SCHOTTKY BARRIER DIODES

ΒY

MD.SHAMSUL ALAM

### A THESIS

SUBMITTED TO THE DEPARTMENT OF ELECTRICAL ENGINEERING IN PARTIAL FULFILMENT OF THE REQUIREMENTS FOR THE DEGREE OF MASTER OF SCIENCE IN ENGINEERING (ELECTRICAL)

MDS

623.3815122

1978

DEPARTMENT OF ELECTRICAL ENGINEERING BANGLADESH UNIVERSITY OF ENGINEERING AND TECHNOLOGY, DACCA, BANGLADESH

JUNE <u>1978</u>

#### CERTIFICATE

This is to certify that this work has been done by me and it has not been submitted elsewhere for the award of any degree or diploma. A paper entitled "Barrier Heights and Interface Effects in Silicon Schottky Diodes" was presented at the 3rd Annual Conference of the Association for the Advancement of Science, Bangladesh, held at Chittagong , January, 8-12, 1978.

Countersigned:

0.7-0 - 21.6 21.6.78

(Supervisor)

(Signature of the candidate)

Accepted as satisfactory for partial fulfilment of the requirement for the Degree of M.Sc.(Engg.) in Electrical Engineering.

Examiners:

M. Gater 1. 21.6.78 (Professor A.M.Patwari)

CHAIRMAN

21.6.78 Hug) (Professor Shamsul

EXTERNAL MEMBER

3. (Professor A.M.Zahoorul Huq)

MEMBER

(Professor Shansuddin Abried) 4.

MEMBER

#### ACKNOWLEDGEMENT

The author expresses his great indebtedness and deep sense of gratitude to Professor A.M.Patwari of Electrical Engineering Department, BUET for rendering his invaluable supervision and ceaseless inspiration throughout this work. The author also acknowledges Professor Patwari's initiative and effort to develop the Micro-electronics Laboratory without which this work could not have been possible to complete.

The author also wishes to express his gratefulness to Professor A.M. Zahoorul Huq, Head of Electrical Engineering Department, BUET for his helpful suggestions and all out encouragement.

The author expresses his sincere gratitude to Dr.S. Mahdi, Professor of Electrical Engineering Department, BUET for his critical suggestions about measurements.

Finally, the author thanks Professor M.Ibrahim, Head of Metallurgical Engineering Department, BUET for lending the microscopes and extending the facilities of dark room of his department.

and the second second

and the second second

#### ABSTRACT

Schottky barrier diodes are obtained by the contact of a metal to a semiconductor. The barrier height and the ideality parameter are the two parameters which determine the quality of these diodes. Schottky diodes have been fabricated on both n-type and p-type silicon and their physical behaviours have been derived from current-voltage (I-V) and capacitance -voltage (C-V) measurements. Aluminium, silver and gold were used as metal contacts. Also a combination of two metals have been used as metal contact.

Methods have been developed to control the barrier height which is very important because a particular application may need a preset value of barrier height. By heat-treatment, the aluminium n-type silicon barrier height can be increased and aluminium p-type silicon barrier height can be decreased. Silver and gold barrie**ps** did not show any significant change in barrier with high-temperature heat-treatment. Also control of barrier height in the higher range was obtained by deposition of aluminium and gold in succession on silicon. Freshly prepared barrier on n-type silicon was higher and on p-type silicon was lower than their known values, which revealed that fixed positive charges were present at metalsemiconductor interface.

The ideality parameter was found to deviate largely from unity. Increased value of ideality parameter was attributed to the thicker interfacial oxide layer. Interface-states density has been calcuated from I-V and C-V data and was found to increase slightly with reverse bias. The normal barrier height values were in the close agreement with results glready published.

|   | -                              | LIST OF SYMBOLS                                                      |

|---|--------------------------------|----------------------------------------------------------------------|

|   | А <b>*</b>                     | Richardsons Constant, 4/cm <sup>2</sup> /o <sub>K</sub> 2            |

|   | **<br>A                        | Effective Richardsons Constant, A/cm <sup>2</sup> /o <sub>K</sub> 2  |

|   | Č.                             | Depletion Layer Capacitance, F/cm <sup>2</sup>                       |

|   | $\mathbf{D}_{d,g}$             | Diffusion constant, cm <sup>2</sup> /sec.                            |

|   | Ė                              | Electric field, V/cm.                                                |

| , | E.                             | Lowest energy level in conduction band, ev.                          |

|   | E <sub>F</sub>                 | Fermi energy, ev.                                                    |

|   | Eg                             | Band gap, ev.                                                        |

|   | Ev                             | Highest energy level in Valence band, ev.                            |

|   | h                              | Planck's Constant, 6.624 x 10 <sup>-34</sup> Joules/sec.             |

|   | J ;                            | Current density, A/cm <sup>2</sup>                                   |

|   | Js                             | Saturation current density, A/cm <sup>2</sup> .                      |

|   | I.                             | Current, A.                                                          |

|   | Is                             | Saturation current, A.                                               |

|   | К                              | Boltzman's constant, 8.62 x $10^{-5}$ ev/o <sub>K</sub> .            |

|   | L <sub>p</sub> /L <sub>n</sub> | Diffusion Length of hole/electron. cm.                               |

|   | <sup>m</sup> o                 | Free electron mass.                                                  |

|   | *<br>11.                       | Effective mass of electron.                                          |

|   | N <sub>D</sub> /N <sub>A</sub> | Shallow, donor/acceptor impurity, cm <sup>-3</sup> .                 |

|   | N <sub>D</sub> /N <sub>A</sub> | Shallow, donor/acceptor impurity, cm <sup>-3</sup> .                 |

|   | N <sup>1+</sup>                | Fixed positive charge density at the interface, , cm <sup>-2</sup> . |

|   | <sup>N</sup> t                 | Concentration of traps, cm <sup>-3</sup> .                           |

|   | n                              | Ideality parameter.                                                  |

| • | n                              | Intrinsic concentration of semiconductor cm <sup>-3</sup> .          |

|   |                                |                                                                      |

|   |                                |                                                                      |

|   | •                              |                                                                      |

| <b>٢</b>                           | Minority carrier life-time.                                                               |

|------------------------------------|-------------------------------------------------------------------------------------------|

| <sup>n</sup> (x)                   | Electron concentration as a function of $x$ in deplo tion layer, $cm^{-3}$ .              |

| N <sub>ss.</sub>                   | Density of surface states, cm <sup>-2</sup> cv <sup>-1.</sup>                             |

| Nsb                                | Surface-states equilibrium with silicon, cm <sup>-2</sup> ev <sup>-1</sup> .              |

| N <sub>sa</sub>                    | Surface-states equilibrium with metal, $cm^{-2} ev^{-1}$ .                                |

| q                                  | Electronic charge, 1.602 x 10 <sup>-19</sup> col.                                         |

| т                                  | Temperature <sup>O</sup> K                                                                |

| V                                  | Applied potential, V .                                                                    |

| v <sub>T</sub>                     | Transport velocity, cu/sec.                                                               |

| <sup>V</sup> bio                   | Built-in or Diffusion potential at zero applied field, V.                                 |

| V <sub>bi</sub>                    | Built-in-potential, V.                                                                    |

| v <sub>n</sub> /v <sub>p</sub>     | Depth of Fermi Level below conduction band (n-type)<br>or above valence-band (p-type), V. |

| Ŵ                                  | Width of depletion layer, cm.                                                             |

| Es                                 | Permittivity of the semiconductor, f/cm.                                                  |

| <b>f</b> i                         | Permittivity of interfacial oxide layer, /cm.                                             |

| ९                                  | Charge density, col./cm <sup>2</sup> .                                                    |

| 8                                  | Thickness of interfacial oxide layer, $o_A$ .                                             |

| ø <sub>Bno</sub> /ø <sub>Bpo</sub> | Zerc field barrier height of n-type/p-type semiconductor, V                               |

| ø <sub>Bn</sub> /ø <sub>Bp</sub>   | Barrier height of n-type/p-type semiconductor, V.                                         |

| ø <sub>o</sub>                     | Energy level at the surface of silicon, v.                                                |

| ø                                  | Image Force barrier lowering, V.                                                          |

| Ø <sub>m</sub>                     | Metal work function, V.                                                                   |

| ø <sub>g</sub> .                   | Band gap, = $E_g/q$ , V.                                                                  |

| , K                                | Electron affinity of semiconductor, V.                                                    |

| y<br>un/Ap                         | Minority carrier injection ratio,                                                         |

| un/Ap                              | Mobility of electrons/holes.                                                              |

# CONTENTS

s yn ner

|               | •                                                    | PAGE NO. |

|---------------|------------------------------------------------------|----------|

|               | Abstract                                             | I<br>I   |

|               | List of the Symbols                                  |          |

| Chapter-One   | INTRODUCTION                                         | 1        |

| •             | 1.1 Introduction                                     | 5        |

|               | 1.2 Brief Literature Review                          | 5        |

|               | 1.3 Scope of the Thesis                              | 12       |

| Chapter-Two   | AN INTRODUCTION TO THE SCHOTTKY<br>BARRIER           | ·        |

|               | 2.1 Preliminaries                                    | 14       |

|               | 2.2 Formation of the Schottky Barrier                | 14       |

|               | 2.3 Capacitance and Width of Depletion<br>Layer      | 17       |

| -             | 2.4 The Image Force Barrier Lowering                 | 20       |

|               | 2.5 The Barrier Height and the Surface-<br>States    | 22       |

| Chapter-Three | CHARGE-TRANSPORT THEORY OF SCHOTTK<br>BARRIER DIODES | У        |

|               | 3.1 Preliminaries                                    | 25       |

|               | 3.2 Thermionic-Emission Theory                       | 25       |

|               | 3.3 Diffusion Theory                                 | 26       |

|               | 3.4 Other Theories                                   | 28       |

ŝ

| Chapter-Four        |                                                                                | PAGE NO. |

|---------------------|--------------------------------------------------------------------------------|----------|

| -                   | FABRICATION OF SCHOTTKY DIODES                                                 |          |

| <i>k</i>            | 、<br>、                                                                         | 31       |

| 4.⊥                 | Preliminaries                                                                  | 31       |

| 4.2                 | Fabrication Process                                                            | 51       |

| 4                   | 2.1 Chemical Cleaning                                                          | 31       |

| 4.<br>-             | 2.2 Ohmic Contact                                                              | 32       |

| 4.                  | 2.3 Schottky Metal Contact                                                     | 33       |

| 4.                  | 2.4 Dicing, Mounting and Lead Connecti                                         | on 33    |

| 4.3                 | Measurements                                                                   | 37       |

| 4.                  | 3.1 Current-Voltage (I-V) Measurement                                          | 37       |

| 4.                  | 3.2 Capacitance-Voltage (C-V) Measurem                                         | ient 39  |

| Chapter-Five        | RESULTS AND DISCUSSIONS                                                        | 42       |

| Chapter-Six         | CONCLUSIONS AND RECOMMENDATIONS                                                | 72       |

| 6.1                 | Conclusions                                                                    | 72       |

| 6.2                 | The Scope of Future Work.                                                      | 74       |

|                     | APPENDICES                                                                     | ,        |

| APPENDIX A          | Interface State Density from C-V and Characteristics.                          | I-V 76   |

| APPENDIX B          | Effective Richardson's Constant A**                                            | 82       |

| APPENDIX C          | The Effect of Metal-Oxide-Semiconduct<br>Potential on the value of Ideality Pa | 67       |

| APP <b>END</b> IX D | Minority Carrier Injection Ratio                                               | 88       |

|                     | BIBLIOGRAPHY                                                                   | 92       |

# LIST OF FIGURES:

| FIGURE | NO 🖕          | TITLE                                                                                                      | PAGE NO.        |

|--------|---------------|------------------------------------------------------------------------------------------------------------|-----------------|

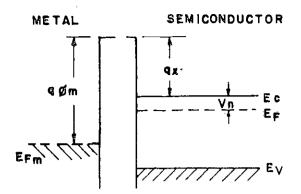

| ,<br>  | 2.1           | Formation of Schottky Barrier from Metal<br>and Semiconductor                                              | 16              |

|        | 2.2           | Schottky Barrier Formation with Surface<br>States                                                          | <b>1</b> 6      |

|        | 2.3           | Energy-band Digram of Metal n-type and<br>Metal p-type Semiconductor under different<br>Biasing conditions | 18              |

|        | 2,4           | Inage Force Barrier Lowering                                                                               | 21              |

|        | 2.5           | Energy-band Diagram of a Metal n-type semiconductor with an Interfacial layer.                             | 21              |

|        | 4.1           | Sectional View of a Schottky Diode                                                                         | 36`             |

|        | 4.2           | Equivalent circuit of a Schottky Diode                                                                     | 38              |

|        | 4.3           | Set-up for Capacitance Measurement                                                                         | 38              |

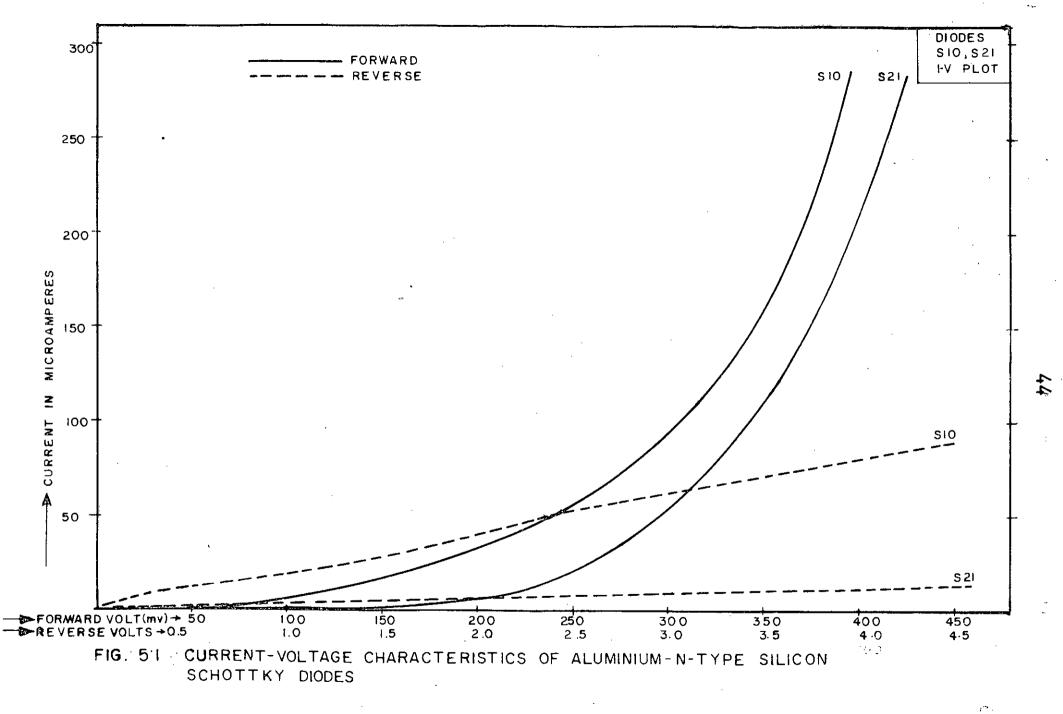

| ٠      | 5 <b>.</b> 1. | Current-voltage (I-V) Characteristics<br>of Aluminium n-type silicon Schottky<br>Barrier                   | 44´             |

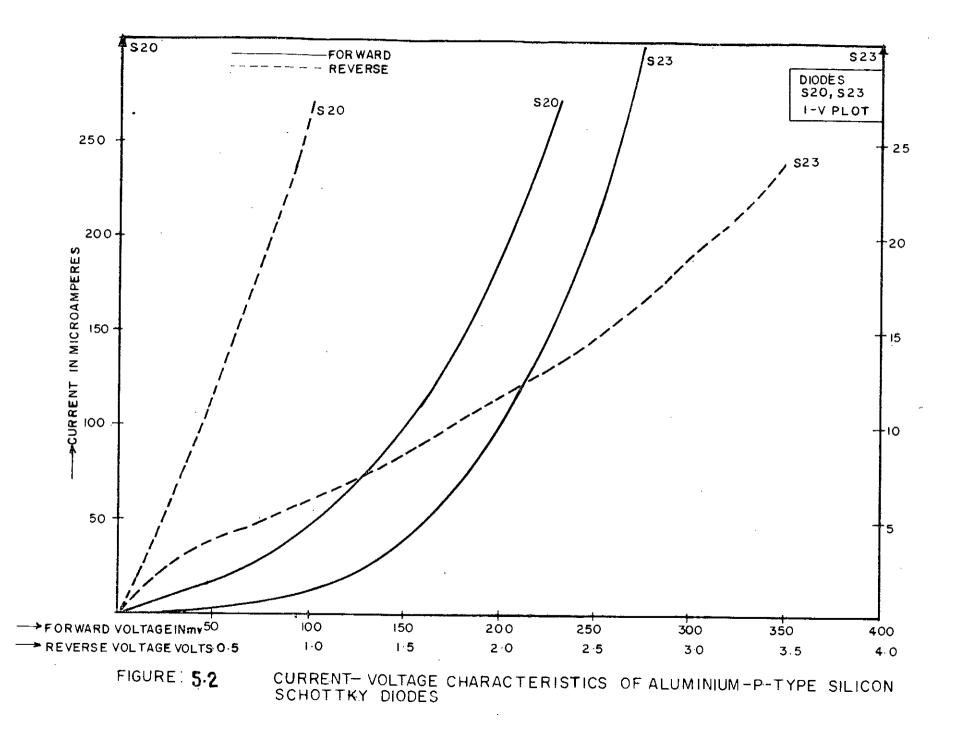

|        | 5.2           | Current-Voltage (I-V) Characteristics of<br>Aluminium p-type silicon Schottky<br>Barrier                   | 45 <sup>5</sup> |

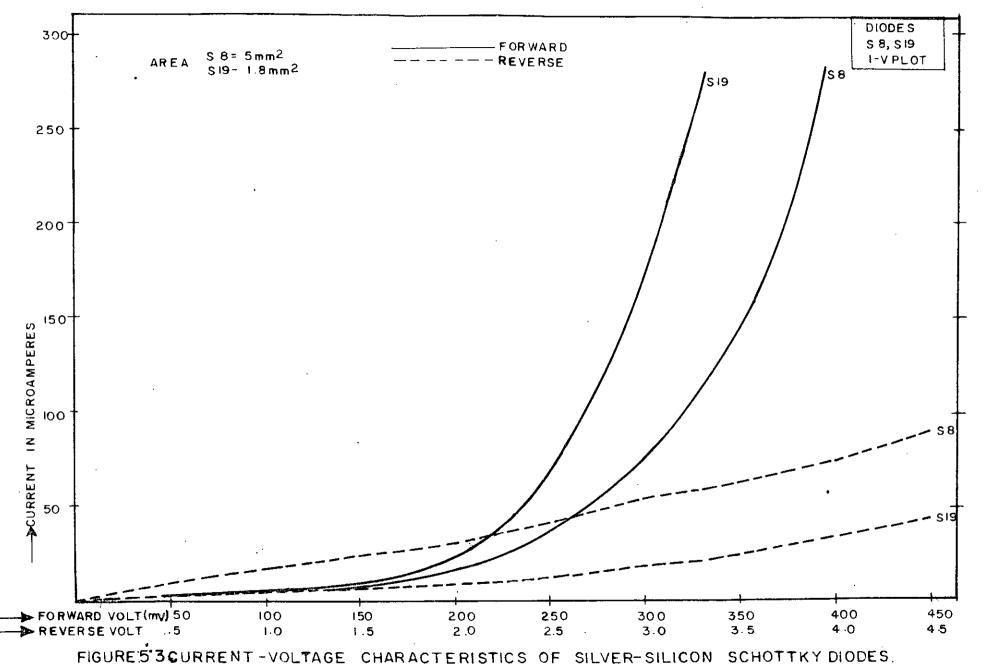

|        | 5.3           | Current-voltage (I-V) Characteristics of<br>Silver-silicon Schottky Barrier                                | 46`             |

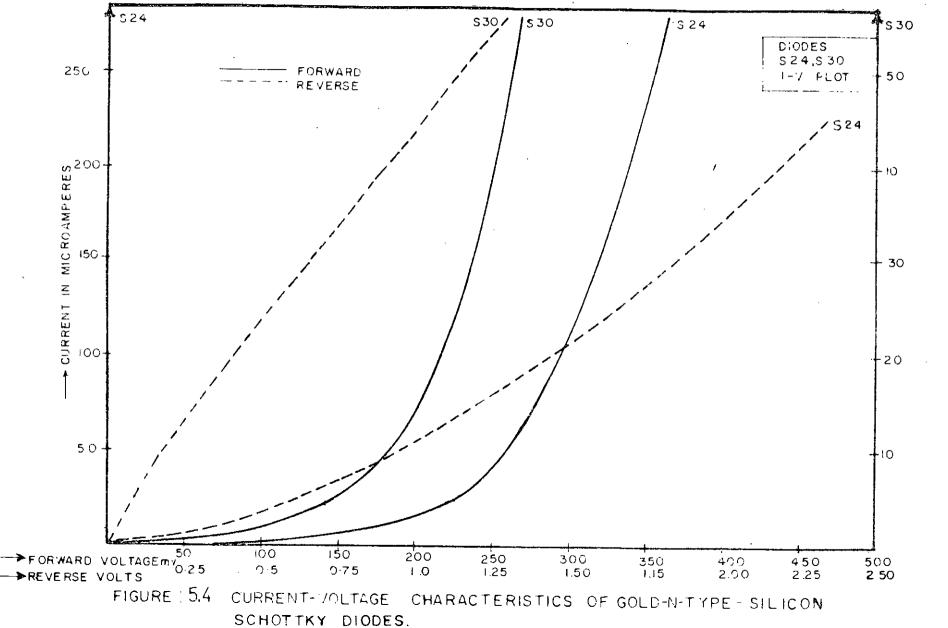

|        | 5.4           | Current voltage(I-V) Characteristics of<br>Gold-n-silicon Schottky Barrier                                 | 47              |

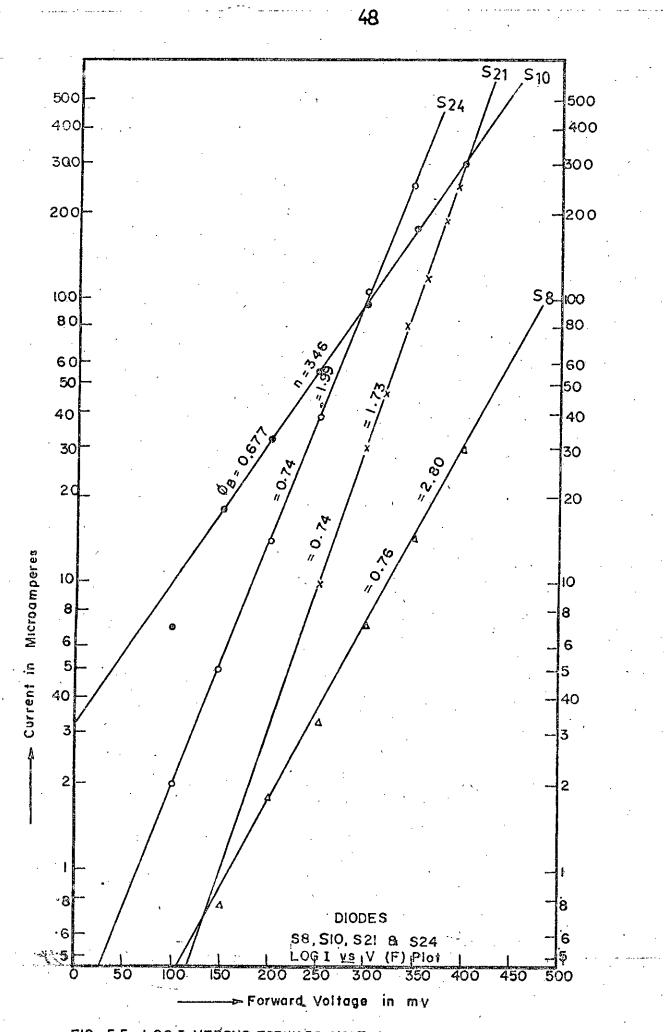

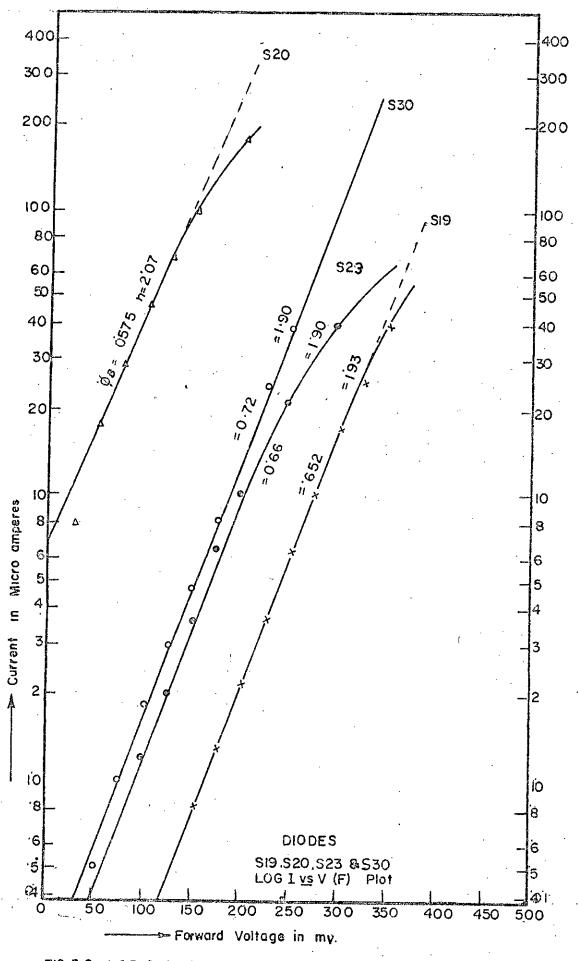

|        | 5.5           | Log I Vs. Forward Voltage for Schottky<br>Diodes                                                           | 48              |

|        | 5.6           | Log I vs. Forward voltage for Schottky<br>Diodes                                                           | <b>4</b> 9      |

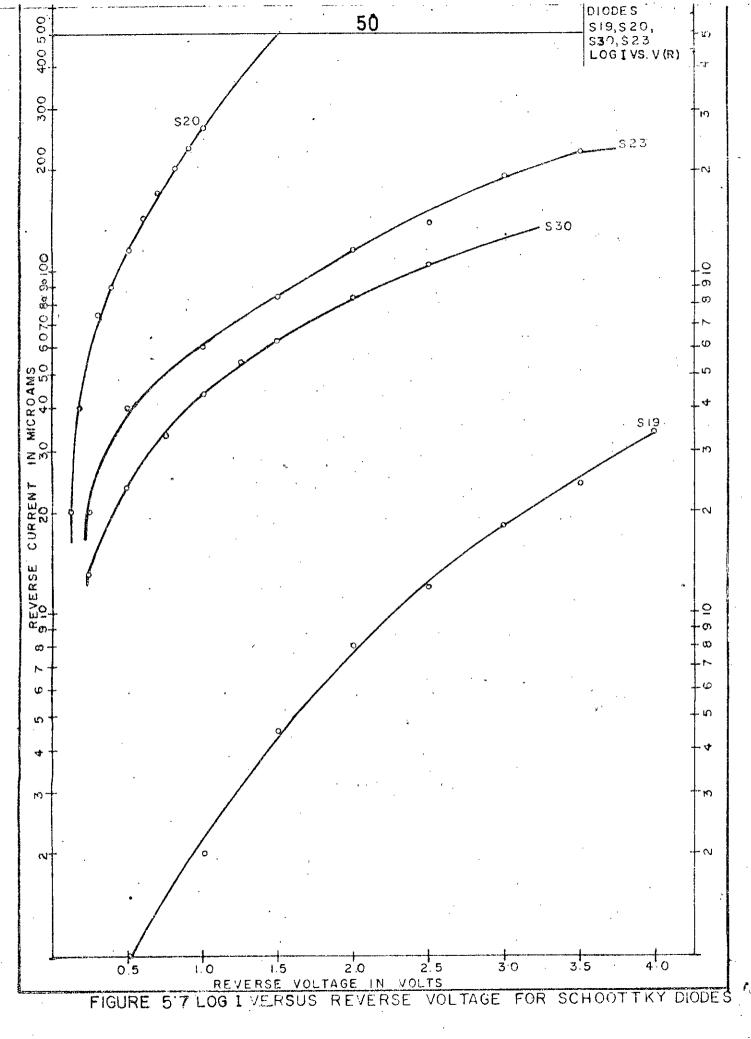

|        | .5.7          | Log I Vs. Reverse Voltage for Schottky<br>Diodes                                                           | 50              |

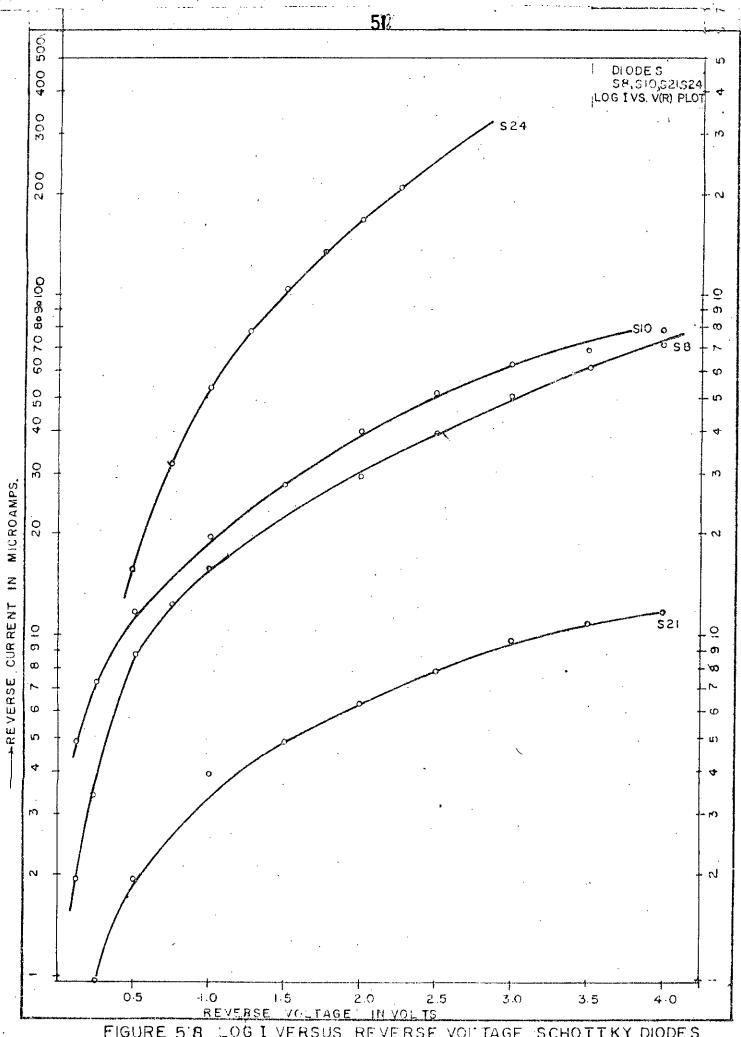

|        | 5.8           | Log I Vs. Reverse Voltage for Schottky                                                                     | 5'1'            |

| FIGURE NO.   | TITLE                                                                                                           | PAGE NO.     |

|--------------|-----------------------------------------------------------------------------------------------------------------|--------------|

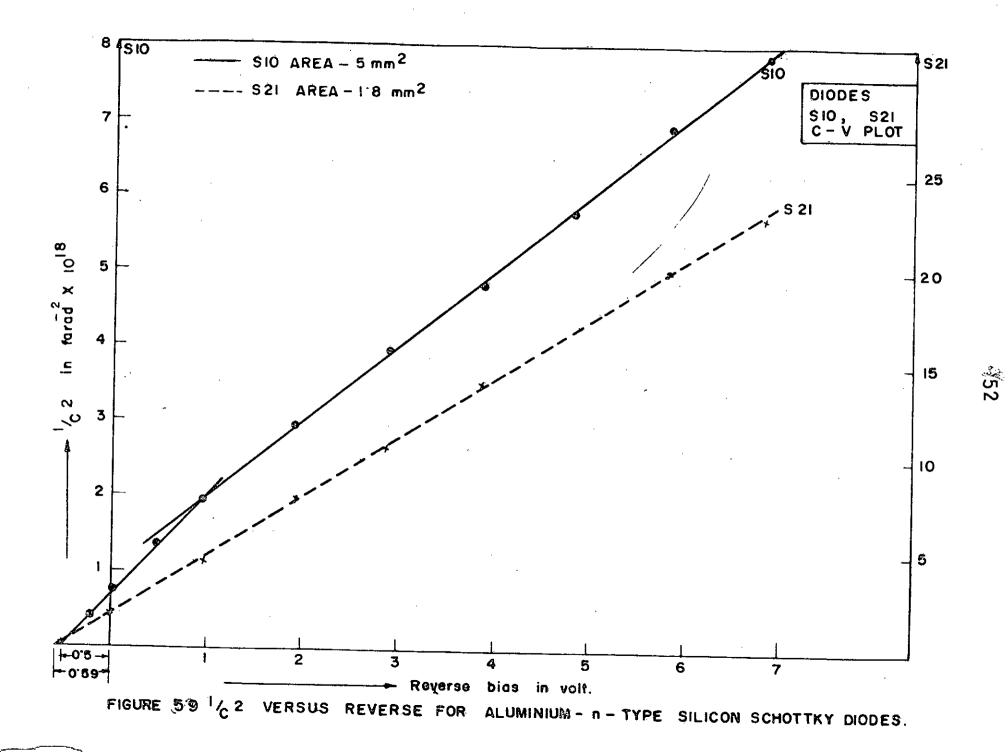

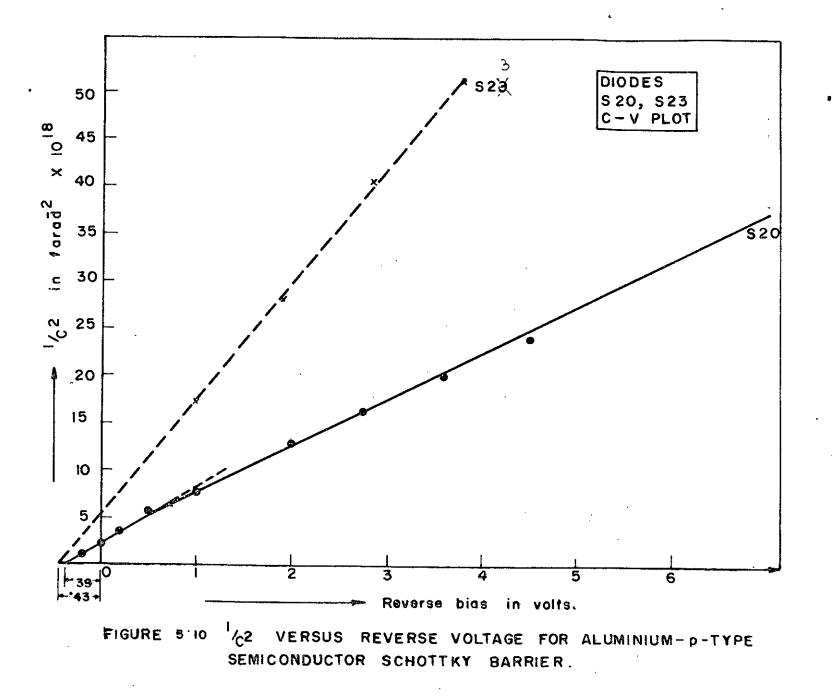

| 5•9          | 1/C <sup>2</sup> vs. Reverse Voltage for Aluminium<br>n-type silicon Schottky Diodes                            | 52           |

| 5.10         | 1/C <sup>2</sup> vs. Reverse Voltate for Aluminium<br>p-type silicon Schottky Diodes                            | • 53         |

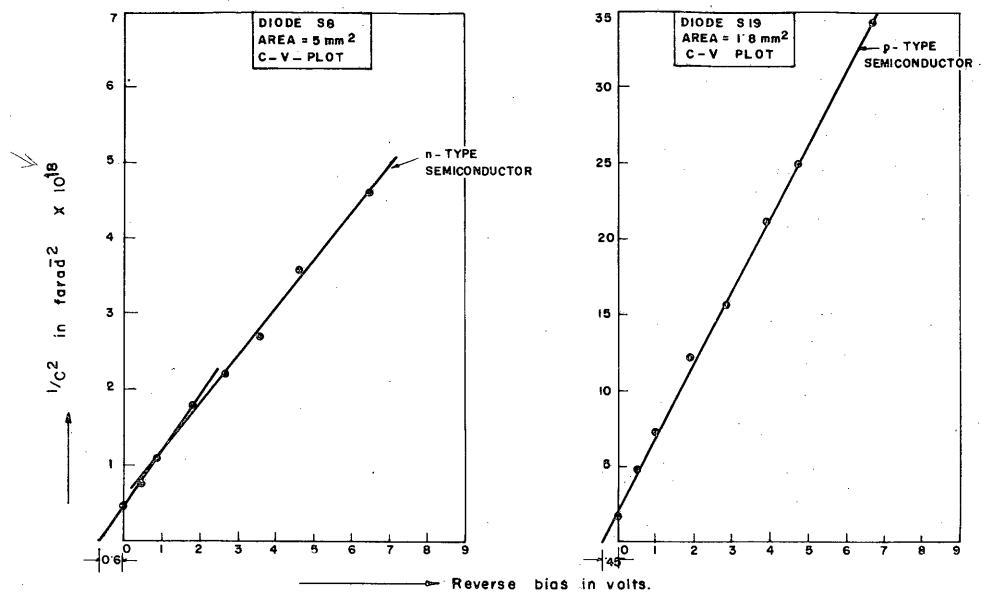

| 5.11         | 1/C <sup>2</sup> Vs. Reverse Voltage for Silver-Silicon<br>Schottky Diodes                                      |              |

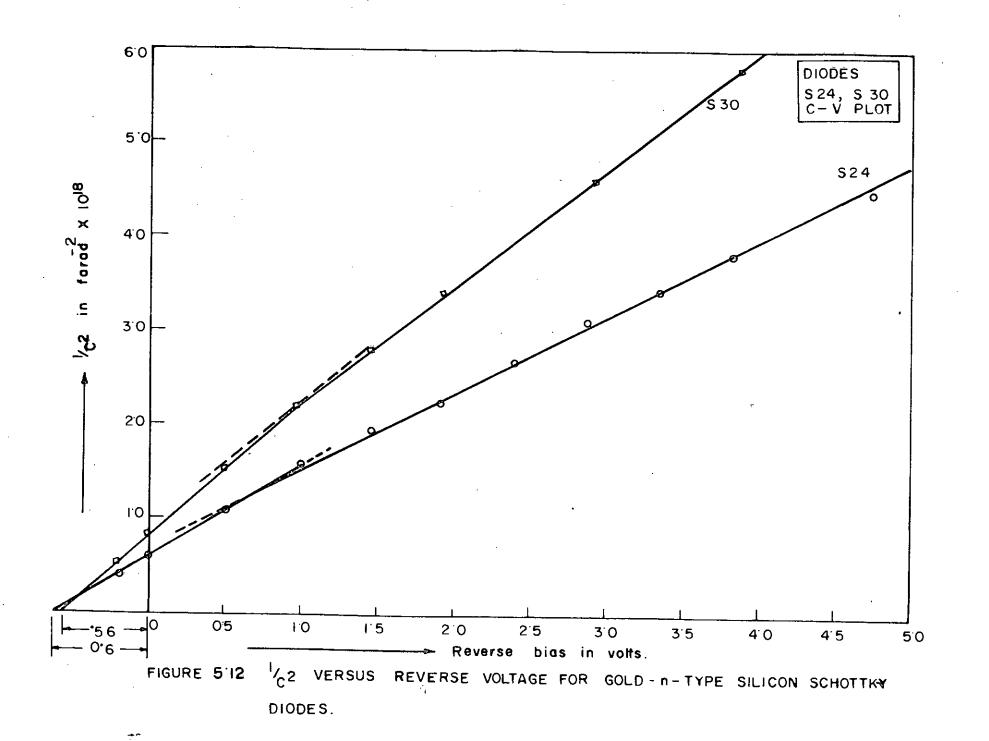

| 5.12         | 1/C <sup>2</sup> Vs. Reverse Voltage for Gold-n-type<br>Silicon Schottky Diodes                                 | 55           |

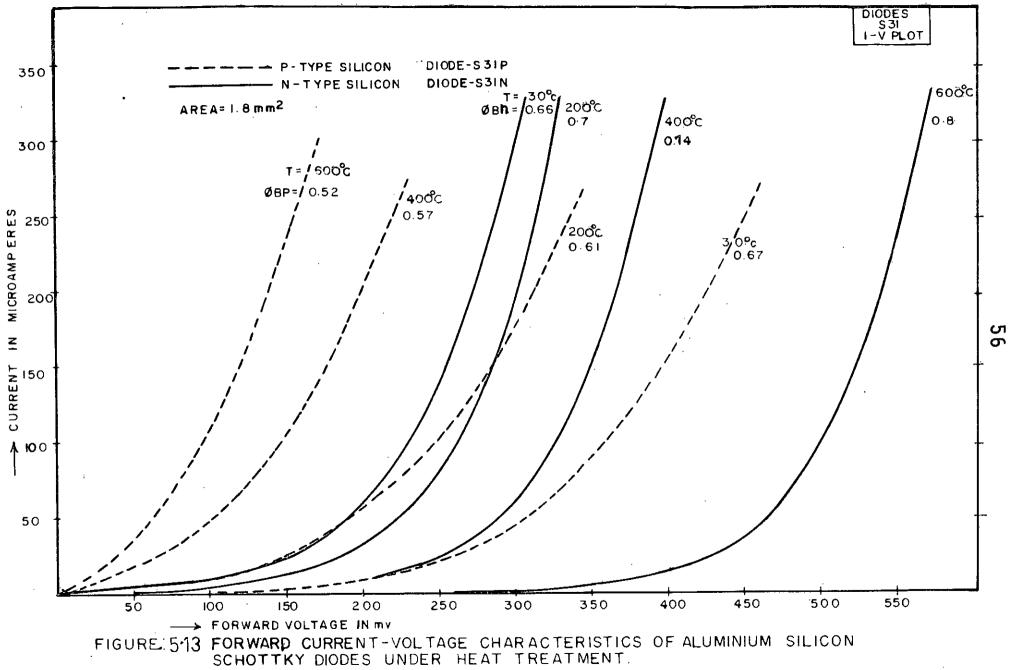

| 5.13         | Forward Current-voltage (I-V) Characteris-<br>tics of Aluminium Silicon Schottky Diodes<br>under Heat-Treatment | 56           |

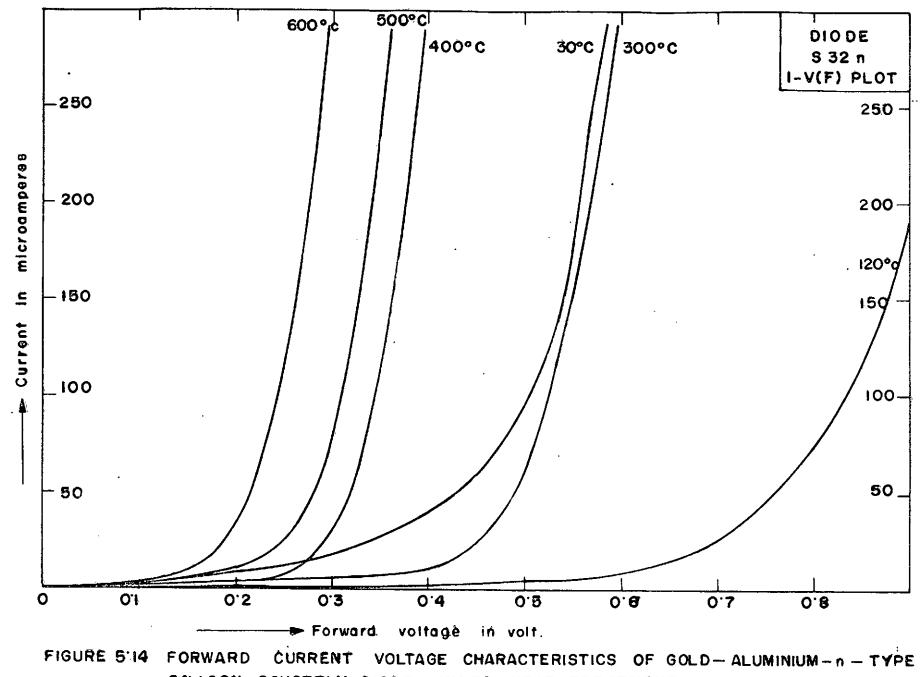

| <b>5.</b> 14 | Forward Current-Voltage (I-V) Characteris-<br>tics of Gold-aluminium n-type-Silicon<br>Schottky Diodes          | 57           |

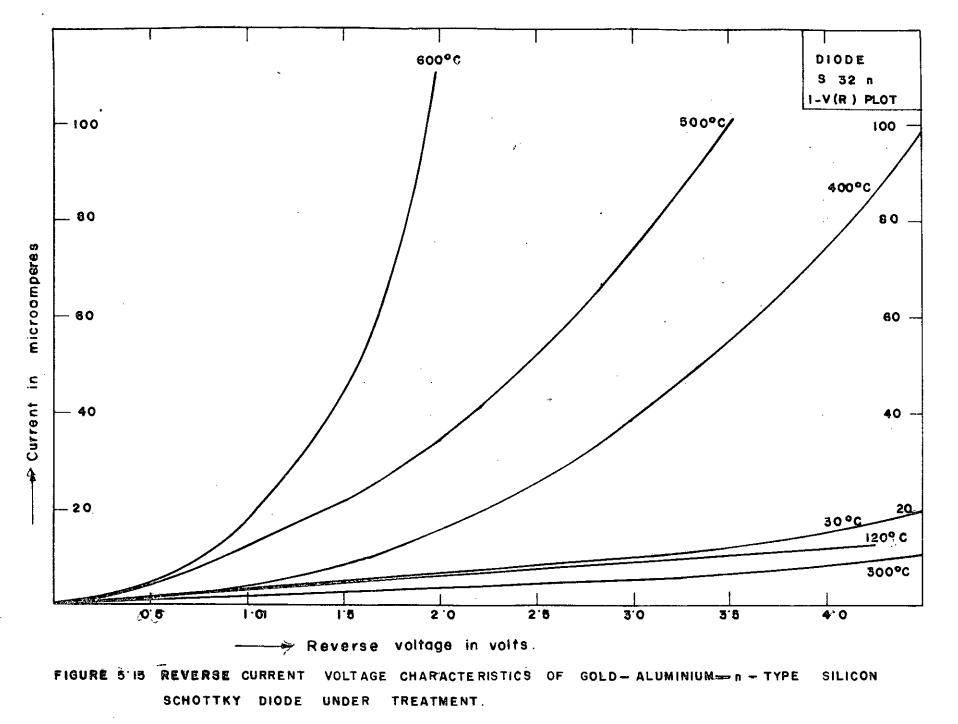

| 5.15         | Reverse Current-Voltage (I-V) Characteris-<br>tics of Gold-Aluminium-n-type-Silicon<br>Schottky Diodes          | 58           |

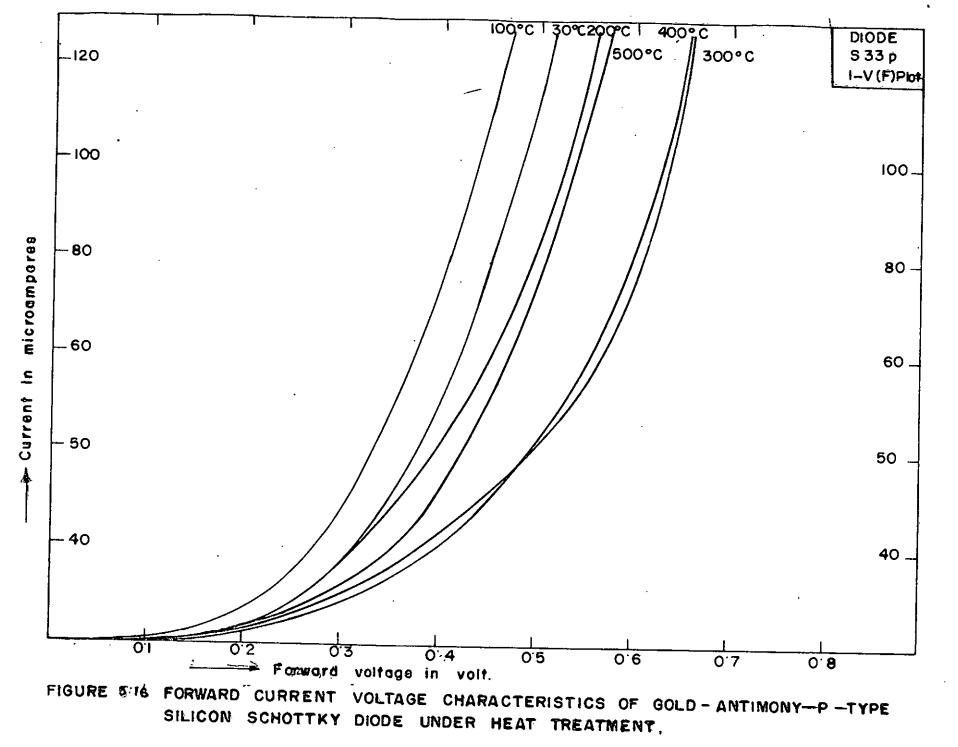

| 5.16         | Forward Current-Voltage (I-V) Characteris-<br>tics of Gold-Antimony-p-type Silicon<br>Schottky Diodes           | 59           |

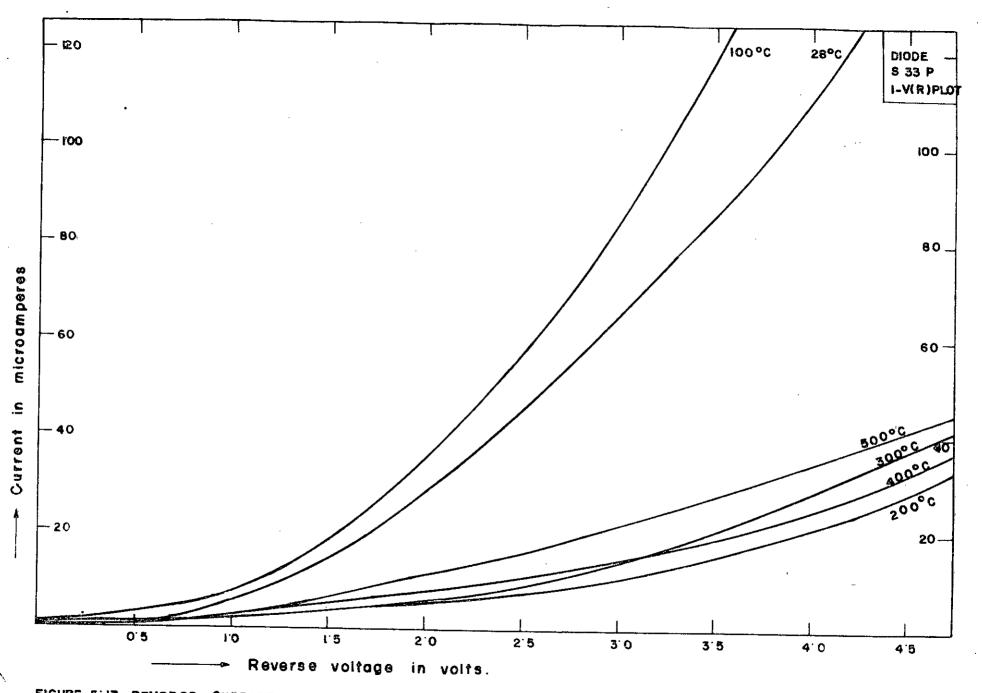

| 5. 17        | Reverse Current Voltage (I-V) Characteris-<br>tics of Gold-Antimony - p-type-Silicon<br>Schottky Diodes         | 60 、         |

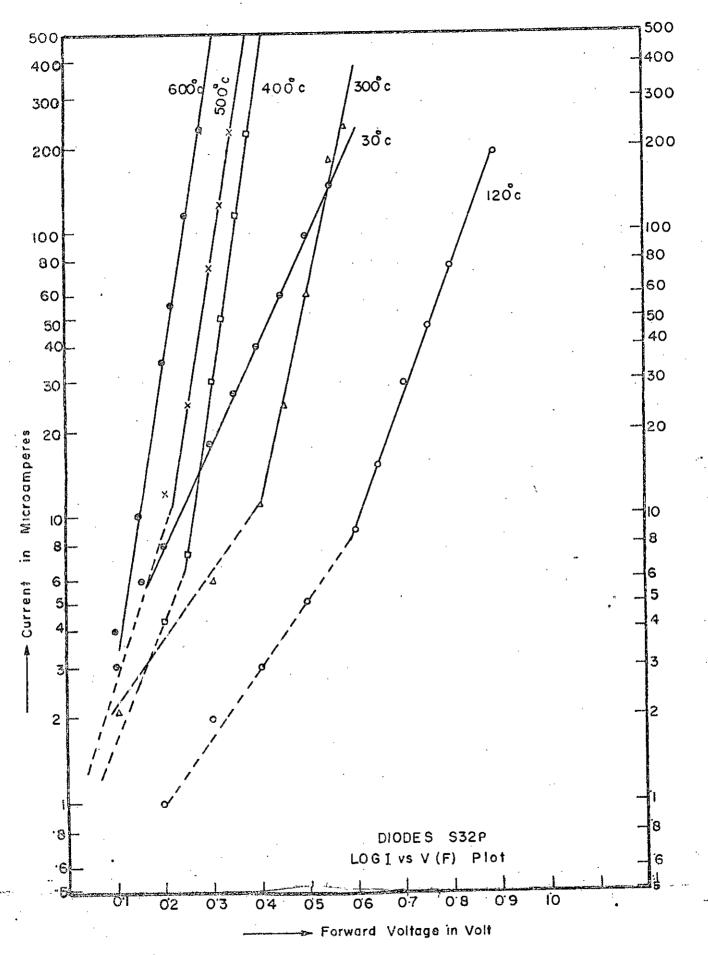

| 5. 18        | Log I Vs. Forward Voltage for Gold Alumi-<br>nium n-type-Silicon Schottky Diodes                                | 61           |

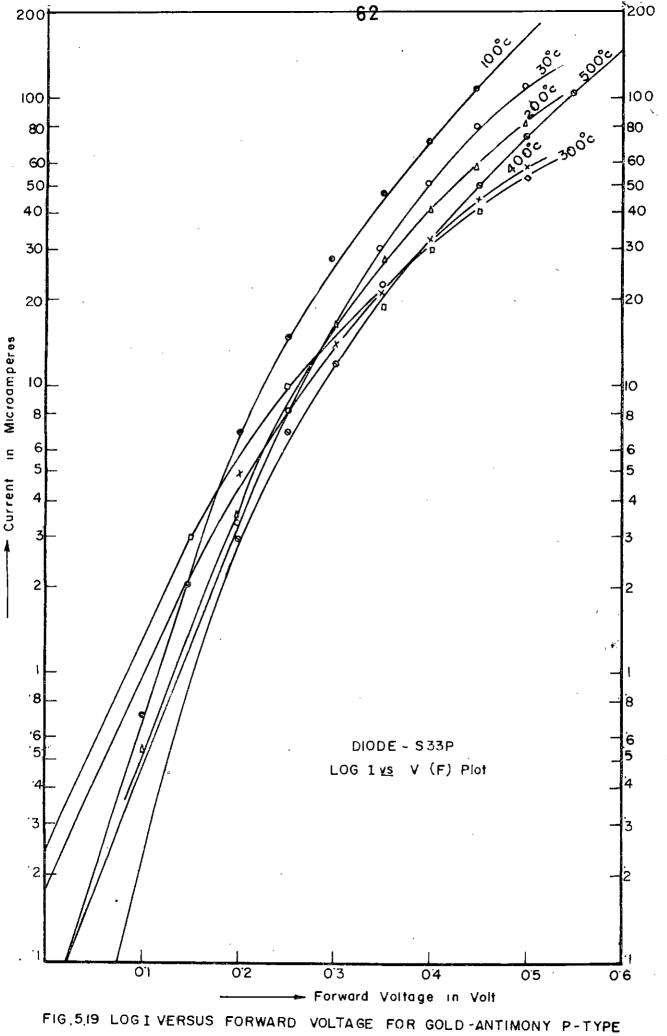

| 5.19         | Log I Vs. Forward Voltage for Gold-Antinon<br>-p-type-Silicon Schottky Diodes                                   | y 62         |

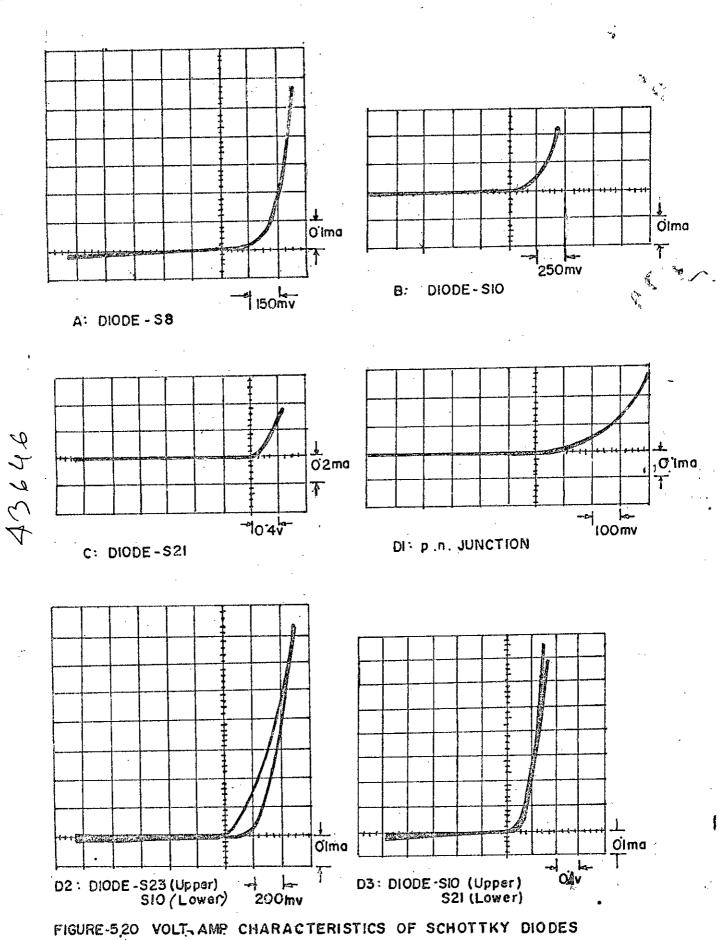

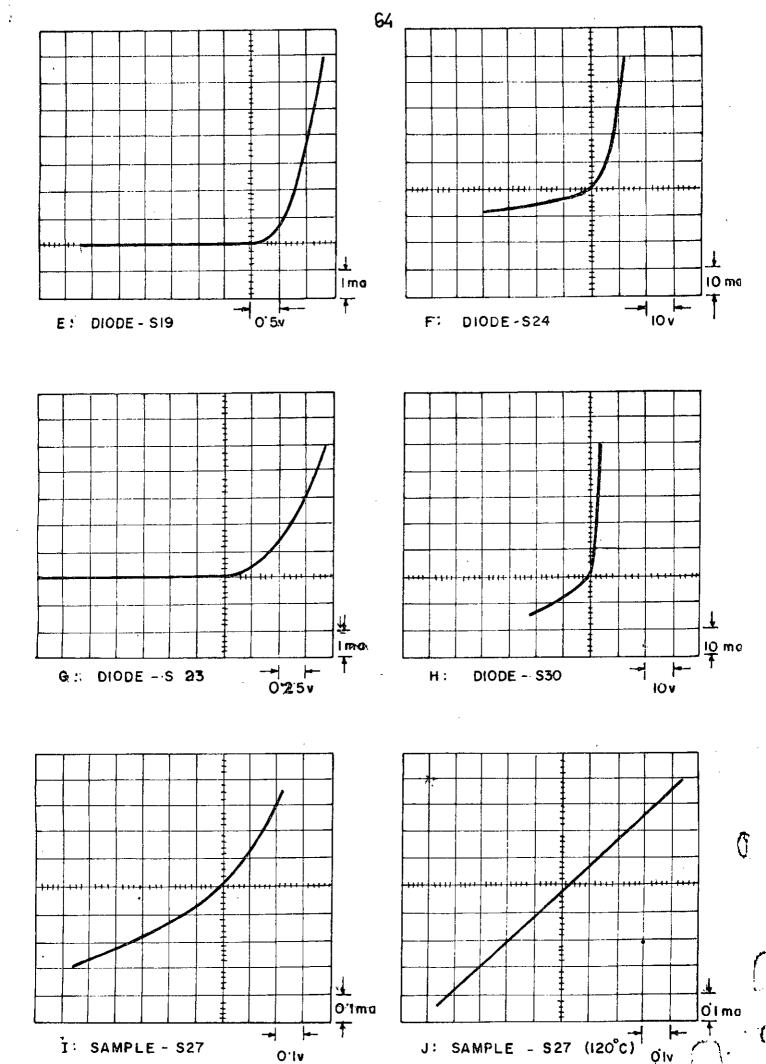

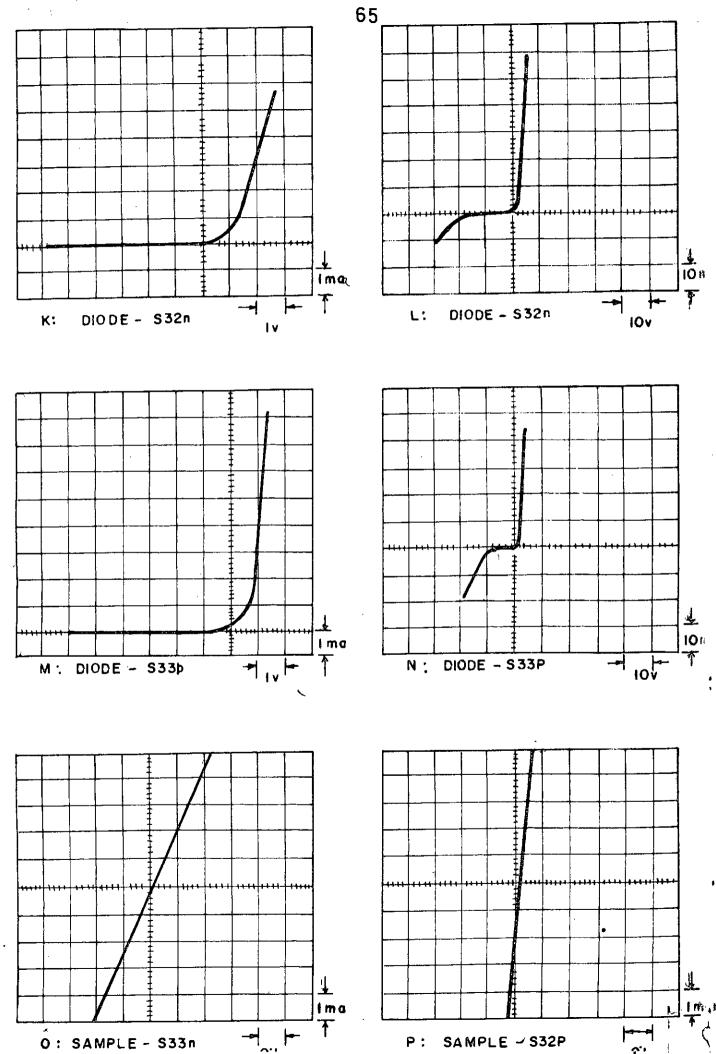

| 5.20(A-P)    | Volt-amp Characteristics of all the Schott<br>Diodes'Fabrication taken as Oscilloscope<br>Pictures              | ky <b>63</b> |

ŗ

(

Fi.

.

•

.

•

•

. . .

....

. •

CHAPTER - ONE

<u>.</u> .

INTRODUCTION

#### INTRODUCTION

1.1

In recent years much interest has been shown in the study of properties of metal-semiconductor contacts because of its wide field of applications. Metal-Semiconductor contacts can be classified into two groups according to their current-voltage characteristics. Those contacts exhibiting rectifying behaviour are called schottky barrier diodes and those with linear current-voltage characteristics are called ohmic contacts. Schottky barriers are generally obtained by metal contacts on lightly doped semiconductor and the ohmic contacts are achieved by the contact of metal on comparatively heavily-doped semiconductors.

Schottky barrier diodes are found to be useful as devices in electronic applications as well as in the studies of fundamental physical parameters. In such diodes the minority carrier effect is virtually eliminated making it suitable for applications in microwave frequencies. Important information on deep level impurities, impact ionisation co-efficient and band structure in semiconductors can be obtained with the help of Schottky barriers.

Though metal-semiconductor contacts are older than p-n junctions, the development in this field was slow for a long time. However, recent advances in planer technology of ideal contacts renewed great interest in the development of Schottky barriers. At present it is possible to fabricate Schottky barriers with reliable and near-ideal electrical characteristics which are reproducible. These advantages are wildely exploited in integrated circuit processing. Thus it is now cheaper and economical to produce discrete Schottky barrier devices.

The metal-semiconductor contacts are now occupying a major place among the devices used in modern electronic systems. The greatest advantage that it offers is the reduction of storage time due to the absence of minority carriers. This makes it an ideal device for applications in microwave frequencies as switching devices (1), mixers and varactor (2). Because of its simplicity in processing and excellent noise performance to other devices the aluminium Schottky barrier with oxide overlap has been found to be superior (3) to those of others. In the field-effect transistor it is used as the gate (4) . An important application of Schottky barrier is in integrated circuit where it performs various gating and clamping functions. The reduced forward voltage in this diode results in reduced fan-out along with increased noise immunity<sup>(5)</sup>, It is also widely used as a collector clamp of n-p-n transistors in order to reduce the awitching time (6) . Schottky barriers have also found useful applications in microstrip integrated circuits, (7), Solar cells (8), and in many others as are reported in Literature (9), (10), (11), (12)

Barrier height and ideality parameter are the two parameters which determine the quality of Schottky dicdes. Theoretically one should be able to obtain a range of barrier heights for various applications by selecting suitable metals and semiconductors having appropriate work functions. However, in practice the presence of the interface states and a thin interfacial layer make the system

less controllable. The fact that these interface parameters cannot be controlled precisely makes the system barrier height and the ideality parameters to deviate from predicted values. So a simple scheme that can control the barrier height to suit a particular application keeping at the same time the ideality parameter very close to unity, is needed to be developed.

#### 1.2 BRIEF LITERATURE REVIEW:

The metal-semiconductor rectifier is known to be the oldest solid-state device used in Electronics. Braun<sup>(13)</sup> in 1874 first reported the asymmetrical nature of conduction between metal point and crystal like lead sulphide. In 1906 pickard<sup>(14)</sup> took a patent for silicon point contact rectifier and in 1907 Pierce<sup>(15)</sup> fabricated diodes by sputtering metals to different semiconductors. The point contact rectifiers were extensively used in early days of radio. In 1931 Wilson<sup>(16)</sup> formulated the transport theory of semiconductors based on the band theory of solids which was applied to metal- semiconductor contact. But the correct physical model was forwarded by Schottky<sup>(17)</sup>in 1938 and hence the name Schottky diode. same year, Mott<sup>(18)</sup> devised an appropriate model for swept In the out metal-semiconductor known as Mott barrier. Bardeen in 1947<sup>(19)</sup> pointed out the presence of surface states which determined the rectifying property of such devices. Then p-n junction diode was discovered in Bell laboratories and since then almost all the research in the field of semiconductor was directed toward the understanding, fabrication and development of junction devices. In early 1960's research interest stated grow again in the development

of the metal semiconductor contacts as Schottky barrier devices A large number of useful research works has been reported in literature. An up-to-date survey of the more important publications is being presented in this section. The objective and main findings of each of the publications are briefly outlined here in a chronological order.

The Pioneering work in this field was done by Archer and Atalla<sup>(20)</sup> who obtained the barrier heights of different metals on silicon. In 1962 Macdonald<sup>(21)</sup> obtained a precise digital-computer solution to the diffusion equation for the idealised one-carrier metal-semiconductor junction problem which was idealised by omitting the effects of traps, image forces, tunnelling, recombination, breakdown phenomenon and hot electrons. He considered a situation similar to that of Wagner<sup>(22)</sup> and Schottky and Spenke<sup>(23)</sup> and obtained more accurate results for static I-V characteristics, dist-dependance of field electrostatic potential and quasi Fermi level potentials.

In 1963 Goodman<sup>(24)</sup> pointed out the factors responsible for the deviation of the diode from the ideal case. He identified these factors to be the series resistance, traps in the depletion layer, the insulating interfacial layer and the edge effect. He illustrated these effects on gold-plated contacts on CdS and derived a correct expression for using the differential capacitance method for the measurement of barrier height. Khange<sup>(25)</sup> studied gold-silicon system of different resistivities. How resistivity silicon resulted in an excess current which he attributed to space charge recon-

bination. Below room temperature the reverse current was dominated by excess current due to recombination-generation and at high temperature image force effect reduced barrier height. He obtained barrier height of 0.8 V by using cufrent-voltage (I-V), capacitancevoltage(C-V) and photoelectric methods. In the same year Spitzer and Mead<sup>(26)</sup> evaporated different metals on cleaned(chemically and vacuum cleaved)n-type CdS and p-type GaAs. Barrier height for GaAs showed little dependence on metal work function and for CdS the barrier height depended on metal but deviated from predicted theory. He concluded that the barrier height values were very sensitive to the surface preparation. A comparison of these values with those obtained by Archer and Attala<sup>(20)</sup>, showed larger deviations.

Cowley and Sze<sup>(27)</sup> (1965) found the dependence of the barrier height on the metal work function, density of surface states and thickness of the interfacial layer. Their derivation was based upon the assumptions that extremely thin inter-facial layer was transparent to electrons and that the surface-states were only the factor which influenced the barrier height of the semiconductor. Barrier height data and metal work function were fitted by the least square method for Si, GaP and CdS and the results were compared with those of Archer and Atalla<sup>(20)</sup>. Padovani and Sumner<sup>(28)</sup> in 1965 analysed the gold-GaAs system replacing KT by  $K(T + T_0)$  in the thermonic equation whence  $T_0$  was found to be  $50^{\circ}C \pm 5^{\circ}C$ . The obtained barrier height was equal to 0.89  $\pm$  .05 volt.

In 1965 Crowell<sup>(29)</sup> modified the Richardon's constant for thermionic emission in vacuum by considering tensor masses of carriers.

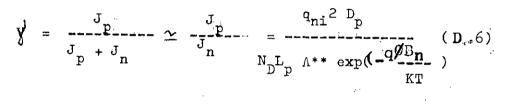

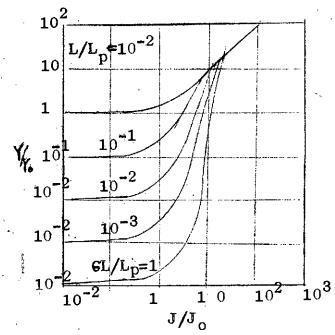

For semiconductor having energy band with enlipsoidal constant energy surfaces in momentum space, the Richardson's constant changes depending on the planes of crystal surfaces. The values obtained agreed well with experimental values. At the same time Scharfetter <sup>(30)</sup> investigated the effect of minority carrier injection under moderate as well as high injection conditions. For Schottky diodes an injection ratio  $\mathbf{y}$  defined as the ratio of minority carrier current to total current was found to increased with forward current. This was due to increase in drift transport of electric field in the quasi-neutral region. He found that below a critical value of current density,  $\mathbf{y}'$  was given by diffusion equation and its value was small. Beyond this critical value, the value of  $\mathbf{v}'$  increased linearly with the electric field.

In 1966 Growell and Sze<sup>(31)</sup> combined the thermionic emission(T) theory and Schottky diffusion (D) theory into a single thermionic-diffusion (T-D) theory which included the image force barrier lowering. A low electric field limit for application of this theory was estimated considering phonon-induced back Scattering near the potential energy maxima. The high electric field limit of the validity of thermionic emission theory was found to be due to quantum-mechanical reflection and tunnelling. Predicted value of ideality parameter was higher than unity because of field dependence of barrier height. At the same time Mead <sup>(32)</sup> published a review paper on Schottky barriers. A qualitative explanation of the type of contact to be expected at an arbitrary metal-semi- conductor interface was presented in his paper.

In 1968 Turner and Rhoderick<sup>(33)</sup> found the barrier height of a number\*metal contacts to n-type silicion. They showed that the initial values of barrier heights depended upon the methods of surface preparation and these values changed slightly with time. They showed that the final value was independent of surface preparation and depended nainly upon the metal work function. However in the case diodes where depositions are made on cleaved surfaces, the barrier height did not show any ageing. In 1968 Padovani<sup>(34)</sup> showed that at room temperature the reverse current in lightly doped GaAs gold Schottky barriers was dominated by thermionic emission from the metal and that the barrier height did not depend upon the applied bias as was expected from the effect of simple image force lowering. Random variation of barrier height lowering together with its temperature dependence as observed from device to device however remaimed unexplained.

Yu and Mead<sup>(35)</sup> in 1970 worked on aluminium barriers. They observed that in silicon the barrier height was  $0.69 \pm 01$  v. Thermionic emission theory was found to be valid in this case. With low temperature heat treatment, the barrier height was found to decrease slightly. Noise and switching behaviours were determined and it was concluded that such a diode was useful as a discrete device. Moreover this could be used in integrated circuits as a Schottky contact. In 1970 Archer and Yep<sup>(36)</sup> experimentally showed that within the range of doping of  $10^{14}$  to  $10^{19}$  cm<sup>-3</sup>, the barrier height was independent of doping as was found in the case of gold-silicon

barrier obtained by both etch-polished and vacuum-cleaved interface. Results obtained from C-V and photoelectric measurements were explained in terms of a simple model having interface of thickness  $\delta$ . This finally led to a limit of the interfacial parameters given by  $(\epsilon t/\epsilon) + 1.8 \times 10^{-6} \text{ N}_{ss} > 3.8 \times 10^8 \text{ cm}^{-1}$ , where  $\epsilon_1$  was the permittivity of interfacial layer, and N<sub>ss</sub>, the surface states.

In 1971 Smith and Rhoderick (37) found that barriers with p-type silicon were generally lower than those with n-type. Gold barrier was so low that it was apparently ohmic. The ideality parameter was found to be about 1.1. The variations of barrier height with metal work function indicated that the surface states parameters were primarily responsible. Crowell and Beguwala (38) calculated ideality parameter, (n) and saturation current  $density(J_s)$  using parabolic band bending. It was found that the quasi-Fermi level in both forward and reverse bias was discontineous at the interface. Under moderate bias the electron inref was nearly constant through the depletion region. In reverse bias imref deviates from constancy for applied bias in excess of KT/q. In 1971 Card and Rhoderick (39)conducted a theoretical and experimental study of metal-silicon system separated by interfacial oxide layer. A generalised approach was considered where the interface states communicated with both metal and semiconductor. Amount of current was explained by a transmission co-efficient which was also a function of thickness of interfacial layer.

In 1972 Tanta porn<sup>(40)</sup> used an interative computer method for finding values of six parameters including barrier height from the measurements of temperature, current and voltage of metal-semi conductor-metal system. With no prior assumptions the output parameters emerged as natural iterative solutions. Thenailakis and Northrop<sup>(41)</sup> determined metal-germanium barrier heights. Aluminiumgermanium barrier showed slight aging and density of surface states was found to be  $2 \times 10^{13}$ ,  $ev^{-1}$  cm<sup>-2</sup>. Barrier height was found to be  $m_{-}$ dependent on impurity concentration of germanium.

In 1973 Card and Rhoderick <sup>(42)</sup> investigated the effect of interfacial layer on minority carrier injection ratio,  $\gamma$  . Inclusion of thin oxide layer favoured reduction of barrier height. The flow of the minority carrier was explained to be due to tunnelling from metal to semiconductor. The authors obtained values of  $\gamma$  for different thickness of oxide interfacial layers.

In 1974 Patwari and Hartnagel<sup>(43)</sup> studied aluminium- GaAs and Nickel-GaAs Schottky barriers under non-ideal surface conditions. The aim of the study of damaged surface Schottky barrier was to find out whether any economy could be achieved with surfaces of the semiconductors whose surfaces were slightly damaged, and whether the ge were useful as devices. Results showed that damage and pitting effectively reduced the barrier height along with slight increase of the ideality parameter.

In 1976 Sinha et al<sup>(44)</sup> found out barrier height and ideality : parameter of Schottky diodes made on n-GaAs metallised with Ti

and Pt/Ti.Also the effect of temp.upto  $500^{\circ}$ c was investigated.Taylor and Morgan<sup>(45)</sup> studied the effect of radiation induced damage caused to N<sub>i</sub>- GaAs Schottky diodes. This damage produced defect levels and led to increased band bending . An excess current was observed in I-V characteristics which was thought to be due to recombinationgeneration. At higher reverse bias a trap assisted tunnelling was observed. Barrier height and ideality parameter were found to be higher.

In 1976 Shanon <sup>(46)</sup> used ion-implantation techniques to obtain doped surface of silicon in  $N_i$ -S<sub>i</sub> barrier. He showed that doping of the surface by antimony atoms decreased barrier height for n-type silicon whereas doping of p-type material by the same metal increased the barrier height. This change in barrier height- depending upon the depth of doped surface layer were explained by suitable equation and thus the control of barrier height was achieved.

Wilkinson et al<sup>(47)</sup>(1977) performed experiments on  $1^{i}$ -si barrier at higher current density. They showed that the value of ndepended upon band bending according to theory of Crowell and Beguwala<sup>(38)</sup> Accurate determination of séries resistance was said to be important because it was found that the ideality parameter, n and the current density, J<sub>s</sub> were very sensitive to it.

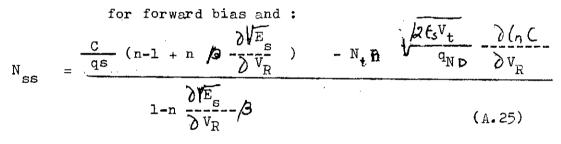

Recently Borrego et al<sup>(48)</sup> (1977) presented a model for determining surface-state density of Schottky diodes directly from I-V and C-V measurements. The interface state density for goldGaAs barrier was calculated to be of the order of  $2 \times 10^{13} \text{ ev}^{-1} \text{ cm}^{-2}$ . The

effects of image force barrier lowering and deep level impurities were considered. Thermionic emission theory was found to be satisfactory except at the reverse bias where a nonthermionic current was observed. This was attributed to enhanced field emission from the traps.

From the very brief review of the papers as presented here a few observations can be made. Almost all the works refer exclusively to n-type semiconductors. Very few works are available with p-type semiconductor because of the fact that the barriers with p-type material were smaller and measurements were difficult. It is noted that extensive works have been done with GaAs<sup>(49)</sup>. This is passibly because GaAs has very high electron mobility . At present various metal-silicides are evoking interest of engineers. It is observed that barrier height data are more abundantly available in literature but few satisfactory models are available to explain the higher values of the ideality.parameters.

As regards, metals used in Schottky diodes, aluminium and gold have been used, of which aluminium extensively because it is cheaper and also easier to evaporate, though gold contacts are more stable. Some research interest is also observed with metals like titanium, platinum and nickel.

#### 1.3. SCOPE OF THE THESIS

The purpose of this thesis is to investigate the fabrication process so that Schottky diodes can be fabricated with controlled barrier height.Control of Schottky barrier height by doping (45) the semiconductor by ion-implantation (46) produces defect levels in semiconductor. So a simpler and inexpensive method is sought to that a preset value of barrier height can be obtained by proper choice of the metal, the semiconductor and controlling the fabrication process. Thus a small value of barrier height would be used for a fast detector where level of signal is low and a high value of barrier height would be achieved in a photo-diode.

So investigations were carried with varied process of fabrication with respect to semi-conductor surface preparation, sequence of metal deposition, heat treatment and ohmic contacts. Silver-tin, gold and gold alloy ohmic contacts were used. Aluminium, silver, gold, gold-aluminium and gold-antinomy as Schottky metal contacts have been investigated.

A theoretical formulation on this subject is given within the first three chapters of which chapter -1 deals with the brief account of the some works done in this field. Chapter-2 gives basic physics of barrier formation along with derivations for barrier height and interface parameters. Chapter-3 deals with the current-transport theory across the barrier. Fabrication process description for different diode series and their measurements are included in chapter-4. All the results are summarised in chapter-5, including the

discussions considering all important and related factors. Conclusions of the thesis along with a few suggestions for further research in this field have been given in chapter-6.

Thus the state-of-art of fabrication of Schottky barrier diodes has been established in our new Micro-electronics laboratory. A new scheme of controlling the barrier height has been introduced where the effect of surface electric field is considered to be dominant. Image force barrier lowering effect is included in deriving the barrier height. Results are based upon the measurements of current -voltage (I-V) and capacitance-voltage (C-V) of the diodes. Larger values of ideality parameter are explained with the help of a model where interfacial layer is thicker. The effect of series resistance was included in processing the current voltage and capacitance-voltage data. Minority carrier current has not been considered as it is negligible as predicted theor@tically.

. ŝ.

11

•

2

U

2

·

# CHAPTER - TWO

# AN INTRODUCTION TO THE SCHOTTKY BARRIER

#### 2.1 PRELIMINARIES:

The potential barrier formed at a metal-semiconductor contact is primarily a function of metal work function, electron affinity of the semiconductor and semiconductor surface states. In this chapter the fundamental process of formation of the barrier has been explained together with the derivation of an expression for the barrier height values considering the inter-facial oxide layer. The effect of image force lowering of barrier has also been taken into consideration in the derivation. The solution of Poisson's equation gave the width and capacitance of the de**ple**stion layer. The method of obtaining the barrier height and impurity concentration from capacitance-voltage (C-V) measurement are based upon the deductions given in this chapter. The density of surface states may be determined from current-voltage (I-V) and capacitance-voltage (C-V) measurements according to the formulation given later in this chapter.

4

#### 2.2. FORMATION OF SCHOTTKY BARRIER

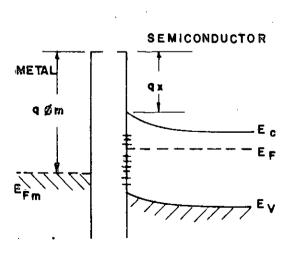

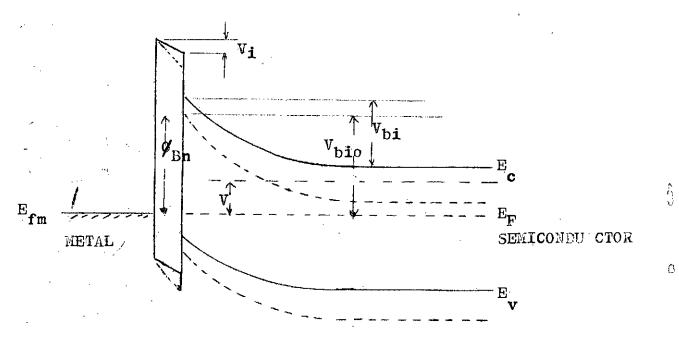

When a metal is braught into an intimate contact with a semiconductor, the valence band and conduction band of the semiconductor is braught into definite energy relationship with the Fermi level in the metal. The energy band diagram is shown in figure-2.1. (a) Where the metal and the semiconductor are separated. If a wire is now connected between them the electrons of the semiconductor will pass to the metal and their Fermi levels are forced into coincidence. An electric field would then result in the gap because there must be negative charges on the metal side balanced by posi-

tive charges on the semiconductor side. Bec use the concentration of donors for an n-type semiconductor is many order of less in magnitude than the concentration of electrons occupy an appreciable thickness and band in semiconductor is bent upward as shown in figure -2,1(b). As the metal and semiconductor approach each other the drop in electrostatic potential (A) associated with field gap tend to be zero if the field is to remain finite. Finally when the gap becomes truely zero (i.e. perfect contact), the potential across the thin layer separating them disappears altogether as shown in figure 1(d) leaving behind only the barrier arising from band-bending. Evidently in the limit of perfect contact the following relationship derived by Schettky<sup>(17)</sup> holds good.

The semiconductor in figure 2.1(a) possesses no net charge at the surface. However the discontinuities in the lattice at the surface of the crystal produce in most semiconductor a number of possible energy states which are localised at the surface and usually there lies a number of states within the forbidden band. Depending on the density of these states, called surface-states, at equilibrium may either exceed or fall short of the number necessary to preserve the local charge neutrality. Bardeon <sup>(19)</sup> was the first to point out that the effect of surface-states on the height of pot.torr ier. Surface-states are usually continuously distributed in energy within the forbidden band and are characterised by a neutral level,  $\emptyset_o$  which is such that if the surface-states are occupied upto  $\emptyset_o$ and empty above  $\emptyset_o$ , the surface is electrically neutral. In case

- (a) NEUTRAL AND ISOLATED

- Q'Ø'm Q'Ø'm EFm

- (b) ELECTRICALLY CONNECTED

(c) SEPERATED BY NARROW GAP

ť

(d) PERFECT CONTACT

FIGURE 2 1 FORMATION OF SCHOTTKY BARRIER FROM METAL AND SEMACONDUCTOR

(a) NEUTRAL AND ISOLATED

(b) CONNECTED ELECTRICAL WITH Thin interfacial layer.

FIGURE 2',2 SCHOTTKY BARRIER FORMATION WITH SURFACE STATES.

In a p-type semiconductor the position is reverse and for ideal contact, the barrier height is given by

And thus the sum of the barrier heights for an n-type and a p-type semiconductor is expected to be equal to the energy band gap i.e.

$$q(\mathbf{\emptyset}_{Bp} + \mathbf{\emptyset}_{Bn}) = \mathcal{E}_{\mathcal{B}}$$

(2.3)

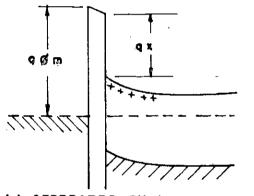

#### 2.3 CAPACITANCE AND WIDTH OF DEPLETION LAYER:

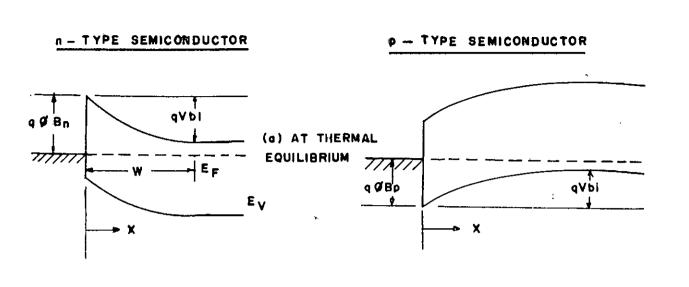

The potential within the depletion region is obtained from the solution of Ppisson's equation  $d^2V/dx^2 = -\frac{1}{2}$  with appropriate bounding conditions. The boundary conditions are known from the knowledge of energy-band relationship. The energy band diagram for n-type and p-type semiconductors are shown in figure 2.3 under different biasing conditions.

The metal-semiconductor barrier is identical to that of an one-sided abrupt junction. Thus for an n-type semiconductor having donor concentration  $N_D$ , we have charge density

FIGURE 2'3 ENERGY BAND DIAGRAM OF METAL n-TYPE & METAL p-Type Semiconductor under different biasing conditions.

F

歌

12

.• . .

4.

E.

$$\mathbf{\hat{q}} = \mathbf{q} \, \mathbf{N}_{\mathrm{D}} \qquad \text{for } \mathbf{x} \, \langle \mathbf{W} \rangle$$

$$= 0 \qquad \text{for } \mathbf{x} \, \langle \mathbf{W} \rangle \qquad (2.4)$$

$$\frac{\text{and } dV}{d\mathbf{x}} = 0, \, \mathbf{V} = - \, \mathscr{D}_{\mathrm{Bn}} \text{ for } \mathbf{x} \, \mathbf{z} \, \mathbf{W}$$

Where W is width of the depletion layer. Integrating Poisson's equation we get electric field.

$$\mathbf{c}(\mathbf{x}) = + q N_{D} (W-\mathbf{x})$$

$$= \mathbf{e}_{m} - \frac{q N_{D}}{\epsilon_{s}} \mathbf{x}$$

Integrating again, the potential is given by

$$V(\mathbf{x}) = \frac{qN_{D}}{\epsilon_{s}} (W\mathbf{x} - \frac{1}{2}\mathbf{x}^{2}) \cdots \emptyset_{Bn}$$

Width of depletion layer is given by (51)

$$W = \left[\frac{2}{-q}\frac{\epsilon_{s}}{N_{D}}(V_{bi} - V - KT/q)\right]_{cm}^{\gamma_{2}} (2.5)$$

Where KT/q arises from the contribution of the mobile carriers to the electric field and is the correction applied by Goodman<sup>(24)</sup>. The maximum electric field  $\boldsymbol{\xi}_{1}$  is then given by

$$\mathcal{E}_{m} = \mathcal{E}(x=0) = \sqrt{2qN_{D}\mathcal{E}(V_{bi} - V - kT/q)} \quad V/cn \quad (2.6)$$

e charge per unit area of the semiconductor

The space

$$Q_{sc} = qN_D W = \sqrt{2q \in N_D (V_{bi} - V - kT/q)} \operatorname{coul}(2.7)$$

Î

٤.

Hence the capacitance C per unit area

$$C = \frac{dQ}{2(V_{bi} - V - kT/q)} = \frac{e_s}{W} f/cm^2 \qquad (2.8)$$

or

$$1/c^2 = \frac{2(V_{bi}-V-kT/q)}{q \in N_D}$$

(2.9)

where <sup>C</sup> is the capacitance per unit area,

#### 2.4 THE IMAGE FORCE BARRIER LOWERING:

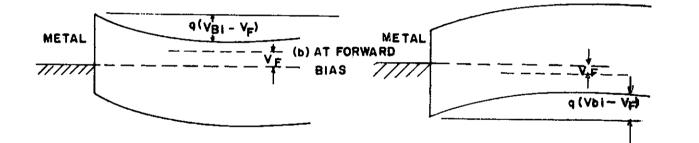

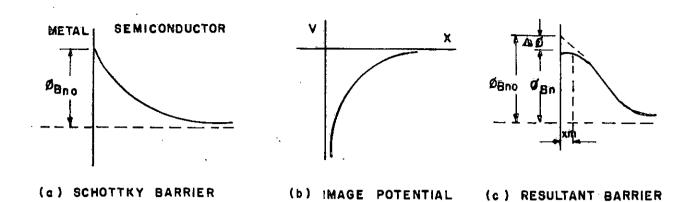

A charged particle close to a conducting plane produces an electrostatic force as if there were an equal and opposite charge at the mirror image of the particle. This image charge being of opposite sign lowers the potential energy of the body. In Schottky barrier this effect is called Schottky effect which reduces the height of the potential barrier and this illustrated in figure-2.4.

An electron at a distance x from metal surface, the attractive force due to image charge is

$$F = \frac{-q^2}{4 (2x)^2 \xi} = \frac{-q^2}{16 \xi x^2}$$

(2.10)

Due to electric field within depletion layer, the total potential energy 2

$$PE(x) = \frac{q}{16\pi\epsilon_0 x} + q \xi x$$

To find the amount of lowering of the barrier this equation is differentiated and set to zero, which yields the following condition

$$X_{\rm m} = \sqrt{\frac{q}{16 \pi \epsilon_0 \epsilon}} \, {\rm cm}$$

(2.11)

The amount of barrier lowering is given by,

$$4\phi = \sqrt{-\frac{q}{4} \frac{g}{k_{g}}} = 2k_{m} x_{m} \qquad (2.12)$$

Where  $\checkmark \phi$  is caused by maximum electric field  $\mathcal{E}_{m}$  within the depletion region. Substituting  $\mathcal{E}_{m}$  from equation -(2.6) in equation-(2.12) we get

$$\mathcal{A} \varphi = \left[ \frac{q^3 N_{\rm D} (V_{\rm bi} - V - KT/q)}{8 \pi^2 \epsilon_3^3} \right]^4$$

(2.13)

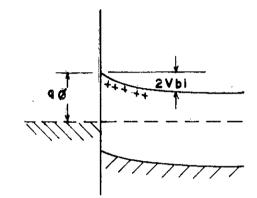

FIGURE 2 4 IMAGE FORCE BARRIER LOWERING

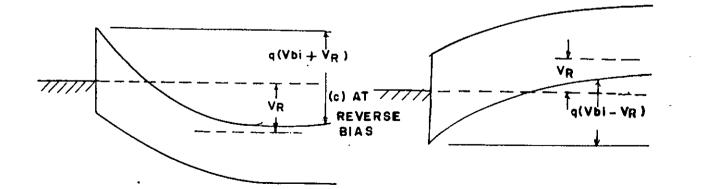

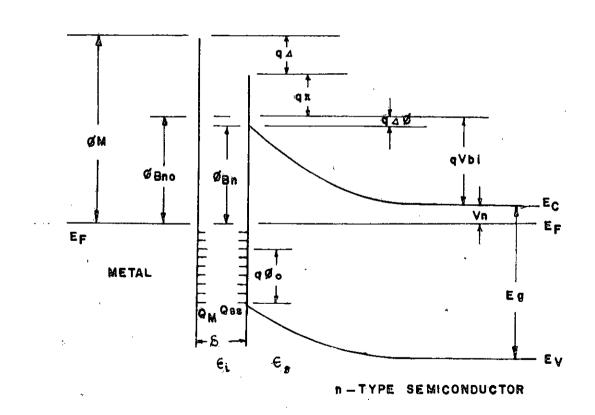

FIGURE 2'5 ENERGY BAND DIAGRAM OF A METAL n-TYPE Semiconductor with an interfacial layer

Because of this  $A\emptyset$ , the reverse current-voltage (L.V ) characteristic does not show saturation and in the forward direction the barrier height is increased slightly.

#### 2.5 BARRIER HEIGHT AND THE SURFACE STATES:

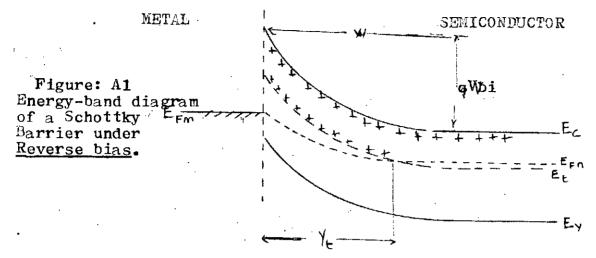

The detailed energy band diagram of a metal- n-type barrier with an inter-facial layer is shown in figure-2.5. The following assunptions<sup>(27)</sup> are made in deriving the expression of barrier height.

a) In an intimate contact, the interfacial layer is of few atomic distance so that it is transparent electrons and it can with-

b) The surface states per unit area per electron-volt at the interface are the properties of semiconductor only.

For most semiconductors  $q \not \otimes_{\mathbf{D}} \not \subset \mathbf{E}_{\mathbf{F}}$  i.e. the surface-states are acceptor-like whose density is  $N_{ss}$ . Thus surface charge density on the semiconductor.

$$Q_{ss} = -q N_{ss} \left( E_g - q \phi_0 - q \phi_{Bn} - q \Delta \phi \right)$$

(2.14)

The space charge formed in the depletion layer at thermal equilibrium is obtained from equation (2.7)

$$Q_{sc} = 2q \in N_D ( \mathscr{P}_{Bn} - V_n + \Delta \mathscr{P} - KT/q )^{\frac{3}{2}}$$

Coul/cn<sup>2</sup> (2.15)

In the absence of any space charge in the interfocial layer, the total equivalent charge density on the semiconductor surface is exactly equal and opposite to  $Q_{M}$  developed on the metal surface. Thus

$$Q_{\rm M} = -(Q_{\rm ss} + Q_{\rm sc})$$

(2.16)

Applying Gauss' Law to the surface charge on the metal and semiconductor, the applied potential across the interfacial layer is given by,

$$\Delta = -\delta Q_{\rm M}/\epsilon_{\rm i} \qquad (2.17)$$

Also from energy band diagram

$$\Delta = \emptyset_{\rm m} - (\mathscr{U} + \emptyset_{\rm Bn} + \Delta \emptyset)$$

Eliminating  $\Delta$  from equation (2.14), (2.15) and (2.16) we obtain.

$$(\not p_{\rm n}-\not x) - (\not p_{\rm Bn}+\not d \not p) = \left\{ \frac{2q \xi_{\rm s} N_{\rm D}}{\epsilon i^{2}} (\not p_{\rm Bn}-v_{\rm n}-KT/q) \right\}^{\frac{1}{2}}$$

$$- \frac{q N_{\rm ss}}{i} \left( E_{\rm g} - q \not p_{\rm o} - c_{\rm o} - q \not p_{\rm Bn}-q \not d \not p \right) \qquad (2.18)$$

Let us define two constants as

$$C_{1} = 2q \epsilon_{s} N_{ss} \delta^{2} \epsilon^{2}$$

$$C_{2} = \epsilon_{i} (\epsilon_{i} + q^{2} \delta N_{ss})$$

(2.19)

Thus equation (2.18) can be written as

$$\begin{split} \boldsymbol{\emptyset}_{\mathrm{Bn}} &= \left[ \mathbf{C}_{2} \left( \boldsymbol{\emptyset}_{\mathrm{m}} - \boldsymbol{\mathcal{D}} \right) + \left( 1 - \mathbf{c}_{2} \right) \left( -\frac{\mathbf{E}_{q}}{\mathbf{q}} - \boldsymbol{\emptyset}_{0} \right) - \boldsymbol{\Delta} \boldsymbol{\emptyset} \right] \\ &+ \left( -\frac{\mathbf{C}_{2}^{2} - \mathbf{C}_{1}}{2} - \mathbf{C}_{2}^{3/2} \right] \left[ \mathbf{C}_{1} \left( \boldsymbol{\emptyset}_{\mathrm{m}} - \boldsymbol{\mathcal{L}} \right) + \left( 1 - \mathbf{C}_{2} \right) \left( -\frac{\mathbf{E}_{g}}{\mathbf{q}} - \boldsymbol{\vartheta}_{0} \right) \frac{\mathbf{C}_{1}}{\mathbf{C}_{2}} \right] \\ &- \frac{\mathbf{C}_{4-}}{\mathbf{C}_{2}} \left( -\mathbf{V}_{\mathrm{m}} + \mathbf{KT}/\mathbf{q} \right) + -\frac{\mathbf{C}_{2}\mathbf{C}_{1}^{2}}{4} \right] \frac{\mathbf{V}_{2}}{4} \right] \\ &\cdot \\ &\cdot \\ &\text{For } \boldsymbol{\xi}_{\mathrm{m}} = 10 \, \boldsymbol{\xi}, \boldsymbol{\xi}_{\mathrm{i}} = \boldsymbol{\xi}_{\mathrm{0}} \text{ and } \mathbf{N}_{\mathrm{D}} \neq 10^{18} \text{ cm}^{-3}, \mathbf{C}_{1} \text{ is and} \end{split}$$

the order of 'OL V, with the approximation that for clean condition

$\delta$  is of the order of 4 to 5°A. Thus the term within the second bracket in equation (2.20) is negligible and the equation reduces to

$$\mathcal{P}_{Bn} = C_2 (\mathscr{I}_{m} - \mathscr{K}) + (1 - C_2) (\mathscr{I}_{g} - \mathscr{I}_{o}) - 4\mathscr{I}$$

(2.21)

Similarly we can derive the barrier height for a p-type semiconductor and this is given by,

$$\mathcal{P}_{Bp} = c_2 (\mathscr{P}_g + \mathbf{X} - \mathscr{P}_m) + (1 - c_2) \mathscr{P}_o - \Delta \mathscr{P} \quad (2.22)$$

where  $\mathscr{P}_g = E_g / q$

$N_{SS} = \frac{C}{q (n_{F}-1)} \text{ for forward bias}$   $= \frac{C (n_{R}-1)}{q (n_{F}-1)} \text{ for reverse bias} (2.23)$ where  $n_{F,R} = \frac{Q}{KT} - \frac{V}{(\ln I_{F,R})}$

and  $n_F$  and  $n_R$  can be found from current-voltage plot in forward and reverse conditions respectively.

CHAPTER - THREE

# CHARGE-TRANSPORT THEORY OF SCHOTTKY BARRIER DIODES

# 3.1 PRELIMINARIES:

Current flow in a Schottky barrier diode is due to majority carriers in constrast to p-n junction diode where current is determined by minority carriers. Several theories approaches exist for finding the amount of current flow across the Schottky barrier.First is the diffusion theory which was proposed in 1939 by Wagner (22)Schottky and Spenke (23). According to this theory current is limited by the process of drift and diffusion. In 1942 Bethe (32) formulated the thermhonic emission theory according to which current was assumed to be limited by thermionic emission. Crowell and Sze(31) combined these two theories into a single thermionic-diffusion theory in which the effect of image force barrier lowering was also considered.Several other theories which are just modification of above theories and suited to particular condition exist. Besides there are emperical approaches for determination of behaviour of the diodes. Some of these will be discussed in the last article of this chapter.

#### 3.2 THERMIONIC-EMISSION THEORY:

This is Bethe's model commonly known as diode model and is based upon the following assumptions:- (i) the mean free path should be greater than the distance in which barrier height falls by an amount KT from its maximum value. (ii) the effect of image force is neglected.

. The current density due to electrons crossing over the potential barrier  $\mathcal{K}_{Bn}$  and flowing to metal from semiconductor under the application of potential V is given by (52)

$J_{sm} = A_0^* T^2 \exp(\frac{-q \not{Q}_{Bn}}{KT}) \exp(\frac{-q V}{KT})$  (3.1)

Where  $A_0^*$  is Richardson's constant for Thermionic emission in vaccum and is given by  $\pi^* \kappa^2 / \kappa^3$

Here n<sup>\*</sup> is the electron effective mass considered as a scalor quantity. But actually effective mass is tensor quantity and therefore depends upon the crystallographic orientation of emitting surfaces, For multiple-valley in energy band of silicon the appropriate Richardson's constant A\* associated single-energy minimum was given by Crowell<sup>(29)</sup> as

$$\frac{A^{*}}{A^{*}_{o}} = \frac{1}{n_{o}} \left( \frac{1^{2}}{1} \frac{x_{0}}{y} + \frac{n_{z}}{z} + \frac{1^{2}}{2} \frac{n_{z}}{z} + \frac{1^{2}}{3} \frac{n_{x}}{z} + \frac{1^{2}}{3} \frac{n_{$$

where  $l_{1,12}$  and  $l_{3}$  are the direction cossine of the normal to the emitting plane relative to the principal axes of the ellipsoid and  $n_{\mathbf{x}}^{*}$ ,  $n_{\mathbf{y}}^{*}$  and  $n_{\mathbf{z}}^{*}$  are the components of effective tensor mass.

Since the barrier for the electrons moving from the metal to the semiconductor remains the same, the current flowing into semmiconductor is thus unaffected by applied potential. Thus

$$J_{\rm IIS} = -A^* T^2 \exp \left(\frac{-\underline{q}\mathscr{D}_{\rm BN}}{KT}\right)$$

Total current, density  $J' = J + J_{ms} + J_{sm}$

$$J = (A * T^{2} \exp \left(\frac{-g}{KT} \overset{\varnothing}{P}_{Pn}\right)) \exp \left(\frac{qV}{KT}\right) - 1 ]$$

$$= J_{ST} \left[ \exp \left(\frac{qV}{KT}\right) - 1 \right]$$

$$(3.3)$$

$$(3.4)$$

where  $J_{sT} = A^{*}T^{2} \exp{(\frac{-q^{\beta}Bh}{KT})}$ , is called saturation current density for thermionic emission.

# 3.3. <u>DIFFUSION THEORY</u>:

This theory is based upon the following assumptions.

(i) The barrier height is much greater than KT ;

(ii) The effect of electron collision within depletion region is included ;

(iii) The carrier concentration of the ends of the Semiductor, are unaffected by current flow and

(iv) The impurity concentration of the Semiconductor is non-degenerate.

The total current is the sum of drift and diffusion currents and is given by

$$J = 2 \left[ n(x) \mu \mathcal{E} + D_n \partial n(x) / \partial x \right]$$

= 2  $D_n \left[ -\frac{2 n(x)}{kT} \frac{\partial V(x)}{\partial x} + \frac{\partial n(x)}{\partial x} \right]$  (3.57)

together with the following boundary conditions:

$$q V(0) = -q (V_{n} + V_{bi}) = -q \mathcal{P}_{Bn}$$

$$q V(w) = -q V_{n} - q V$$

$$n(0) = N_{c} \exp \frac{-E_{c}(0) - E_{F}}{K_{T}} = N_{c} \exp \left(-\frac{q}{K_{T}}\right)$$

$$n(w) = N_{c} \exp \left(-\frac{q}{V_{n}}\right)$$

(3.6)

Substatuting the boundary conditions in equation (3.5) and replacing W in terms of  $V_{bi} + V$  lead to the following expression.

$$J = \frac{q^2 D_n N_c}{kT} \left[ \frac{2(V_{bi} - V) 2N_b}{\epsilon_s} \right]^{\frac{1}{2}} exp \left( \frac{2V_{bi}}{kT} \right) \frac{exp \left( \frac{2V_{kT}}{kT} \right) - 1}{1 - exp \left[ -2\frac{2}{k} \frac{(V_{bi} - V)}{kT} \right]}$$

Where V, the applied potential is positive for forward bias and negative for reverse bias. Since  $\mathcal{G}$  is it is the exponential term in denuminator can be neglected for reverse voltages and small forward voltages, thus we get.

$$J = \frac{q^{2} D_{n} N_{c}}{KT} \left[ \frac{2(V_{bi} - V) 2N_{D}}{\varepsilon_{s}} \right]^{\frac{1}{2}} \exp\left(\frac{-2\varphi_{sn}}{KT}\right) \left[ \exp\left(\frac{2V}{KT}\right) - 1 \right] \qquad (3.7)$$

=  $J_{SD} \left[ \exp\left(\frac{2V}{KT}\right) - 1 \right] \qquad (3.6)$

where  $J_{SD} = \frac{q^{2} N_{c} D_{n}}{KT} \left[ \frac{2(V_{bi} - V) 2N_{D}}{\varepsilon_{s}} \right]^{\frac{1}{2}} \exp\left(\frac{-2\varphi_{sn}}{KT}\right)$

Saturation current in diffusion theory varies more rapidly with voltage but is less sensitive to temperature in comparison with the saturation current in thermionic-emission theory.

# 3.4 OTHER THEORIES

Crowell and  $S_{ze}^{(31)}$  synthesised thermionic emission theory and diffusion theory into thermionic- diffusion theory. They derived the current transport equation from the boundary condition of thermionic recombination velocity,  $v_R$ , near the netal-semiconductor interface. In addition, effects of electron-phonon Scattering<sup>(53)</sup> and quantum-mechanical reflection<sup>(54)</sup> at the interface are incorporated. The electron optical-phonon Scattering between the barrier energy maximum and metal predicts a low field limit for applying the thermionic emission theory i.e. for assuming that the metal acts as perfect sink for carriers which cross the potential maximum in the direction of the metal. The effect of quantum-mechanical reflection and quantum tunnelling on the recombination velocity predicts the high field of validity of thermionic emission theory and the onset of thermionic-field emission. The complete expression for J-V chargecteristics taking into account of these two factors is given by

$J_{i} = J_{s} \left[ exp\left(\frac{v}{kr}\right) - 1 \right]$

Where  $\mathbf{J}_{S} = A^{**} + T^{2} \exp\left(-2\frac{\phi_{B_{n}}}{\kappa T}\right)$ and  $A^{**}$  is called effective Richardson's constant (Appendix -g)

Thus at room temperature the semiconductors having impurity concentration below  $10^{17}$  cm<sup>-3</sup>, the current transport mechanism in Schottky diodes is due to thermionic emission of majority carriers.

(3.9)

These theories are derived considering the barrier height is constant and contact is such that the interfacial layer is very thin. But in practice, diodes fabricated do not fit to the theoritcal expression of equation (3.9) exactly because of nonuniformity in semiconductor space charge, thicker interfacial oxide layer, minority carrier injection and recombination generation in the depletion region. However, it is found that all the experimental results could be fitted to the following well-accepted equation

$I = I_{s} \exp \left(\frac{9\sqrt{7} KT}{7}\right) \text{ for } (3.10)$ biases  $V > \frac{3 KT}{9}$ , where n is called the ideality parameter which varies in the range unity to 10 and I<sub>s</sub> is the saturation current.

So far we have considered only the majority carriers. The effect of minority carrier was investigated by the model of Schar-fetter (30). Magnitude of minority carrier injection was measured by Y<sub>n</sub> and Snow (55). The minority carrier injection(App-D)

was measured to be very small and current was primarily due to the majority carriers. Also the existence of recombination generation current was detected by  $Y_u$  and  $Snow^{(55)}$  and  $Sinhe^{(44)}$  which is important in low current levels otherwise negligible.

Card and Rhoderick (39) derived a model on Schottky barrier current where interfacial layer is thick. They assumed two types of interface states one is N<sub>SA</sub> and another is N<sub>Sb</sub>. The oxide layer which was intentionally introduced was supposed to form a barrier of average height / Transmission component of electron tunnel was dependent upon  $/2^{1/2}$  and thickness of the oxide layer, Thus the equation was derived

$$J = A^{**}T^{2} exp(-\psi^{y_{2}}\xi) exp(-\frac{2}{\kappa_{T}}\theta_{3n}) [exp(\frac{2}{n\kappa_{T}}) - 1]$$

where n was given by (Appendix **t**)  $n = 1 + \frac{\left(\frac{\delta}{\epsilon_i}\right)\left(\frac{\epsilon_s}{w} + \frac{\epsilon_s}{N_sb}\right)}{1 + \left(\frac{\delta}{\epsilon_i}\right)\left(\frac{\epsilon_s}{W}\right)}$ (3.11)

If all the interface states communicates with the semiconductor, then  $N \rightarrow 0$  and we get sa

$$n = 1 + \frac{\delta}{\epsilon_i} \left( \frac{\epsilon_s}{W} + 2 N_{sb} \right)$$

(3.12)

We have neglected in all cases the effect of treps, but in practice generally the deep level impurities are found to be present. They contribute to change of interface states and capacitance of the diode.

30

÷.

CHAPTER - FOUR

t: .

> FABRICATION OF SCHOTTKY DIODES AND MEASUREMENTS

#### 4.1 PRELIMINARIES:

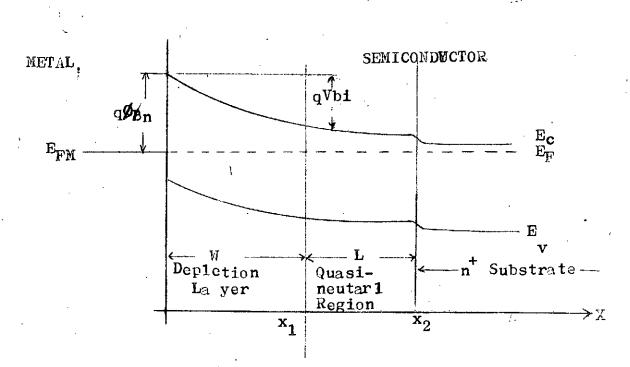

In this chapter the process of fabrication of reproducible Schottky barrier diodes have been described. All of them were obtained by vacuum deposition of metals on cleaned surfaces of doped semiconductor wafers. The vacuum system was Edwards-306 coating unit fitted with a film thickness monitor having an accuracy of one **engetrom** Deposition of metals <sup>(62)</sup> were carried out at residual pressures in the range of  $10^{-5}$  to  $5 \times 10^{-6}$  torn, and liquid nitrogen was used as trap. Both n-type and p-type silicons were used. Fabrication of diodes started with chemical cleaning of the silicon substrates. The substrates had doped epitaxial layers. The current-voltage (I-V) and capacitance-voltage (C-V) measurements were performed on the diodes. A X-Y plotter and a radio-frequency bridge were used in measurements.

# 4.2 FABRICATION PROCESS:

In general the following steps were followed in the fabrication process-

i) Chemical cleaning of the substrates.

ii) Preparation of ohmic contact.

iii) Preparation of metal contact and

iv) Dicing, mounting and lead connection.

4.2.1 Chemical Cleaning: The epitaxial layer side of the substrates was already mirror polished . These were cleaned chemically where some variations were introduced e.g.some of them were slightly etched and some were not. Thus we devide this

step into two categories.

- (a) Ultrasonic cleaning in methanol for 3 minutes.

- Boiling in mixture of methanol and acetone .

- Rinsing in Acetone.

- Drying at 80°C.

- (b) Ultrasonic cleaning in methanol for 3 minutes.

- Etching in the solution of 1 part hydrofloric acid, 5 parts nitric acid and 12 parts of acetic acid by volume (1 HF: 5 HNO<sub>3</sub>: 12 cH<sub>3</sub> COOH) for 1-4 minutes.

- Washing in deionised water.

- Ultrasonic cleaning in methanol for 3 minutes.

- Rinsing in acetone.

- Drying at 80°C.

4.2.2. <u>Ohnic Contact</u>: The n-type subtrates which were  $n^{\pm}n$  type had their backside unpolished . Well-known silver-tin contact was applied. Tin and silver were deposited in sequence of  $200^{\circ}A$  and  $2000^{\circ}A$  respectively at a pressure of  $10^{-5}$  torr and then alloyed in vacuum  $(10^{-2} \text{ torr})$  at  $600^{\circ}C$  for one minute.

The p-type substrates were both p-type and  $p^{\ddagger} - p$ -type. The ohmic contact was obtained by gold or gold-aluminium alloy. Some of the  $p^{\ddagger}$  -p substrates were gold deposited (1000°A) in vacuum (10<sup>-5</sup> torr) and then heated at 550°C for 5 minutes in a chamber having a pressure of 10<sup>-2</sup> torr. And rest of these were given contact of aluminium gold which were deposited in succession of 100°A and 1000°A respectively and then alloyed at 450°C for 4 minutes in a chamber with a pressure of 10<sup>-2</sup> torr. This process gave reproducible contact and contact with a large contact area, they were ohnic.

4.2.3 <u>Schottky Metal Contact</u>: This was done by various metal such as aluminium, gold, silver, aluminium-gold and antimony-gold. Metals were deposited through metal masks to give a few circular contacts at residual pressure in the range of  $5 \times 10^{-6}$  torr to  $10^{-5}$  torr. Thickness of metal film was varied in the range of 1000,  $^{\circ}$ A to  $2000^{\circ}$ A and the rate of deposition was in the range  $10 - 20^{\circ}$ A/sec. The list of diode-series fabricated are given in table 4.1 m which conditions of each process have been shown. Generally the metal contacts were heated at  $120^{\circ}$ C to have a stable contact. For aluminium-gold and antinony-gold system, aluminium or antimony was deposited with a thickness of  $50^{\circ}$ A before the deposition of gold. Then gold was deposited of thickness  $1000^{\circ}$ A.

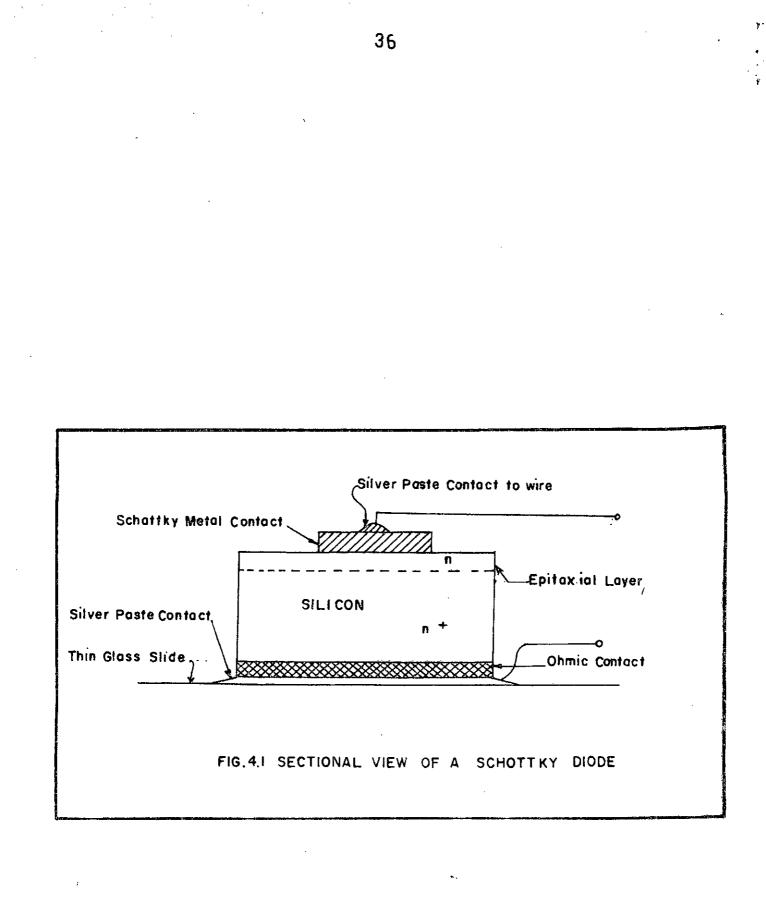

4.2.4 <u>Dicing Mounting and Lead Connection</u>: The Schottky diodes were separated by dicing with the help of a diamond pencil and were mounted on thin glass slides with adhesives of silver preparation. And the wires were connected on both sides of diodes with silver pastes. A sectional view of such a diode is given in figure-4.1.

Heat-treatment of the diodes were performed in a furnace where they were heated at certain temperature for 3 to 5 minutes and were left there for about one hour. Then the samples were taken out to be cooled in atmospheric condition for at least 15 minutes. In this way a slow cooling was achieved.

TABLE- 4.1

| .Sl.<br>no. | seri <b>-</b><br>es | Chemical<br>cleaning<br>by proce-<br>ss (a) or<br>(b) | Type of<br>semi-con-<br>ductor | Type of<br>ohmic<br>contact | ≬ Schottky<br>Metal<br>contact | of depo-                  | Area of<br>contact<br>in cm <sup>2</sup> | Heat<br>treatment<br>if any   |

|-------------|---------------------|-------------------------------------------------------|--------------------------------|-----------------------------|--------------------------------|---------------------------|------------------------------------------|-------------------------------|

| <br>l.      | <br>s8              | <br>(a)                                               |                                | SilVer-tin                  | Silver                         | 10-5                      | 0.05                                     | -X                            |

| 2.          | slo                 | (a)                                                   | n <sup>+</sup> -n              | Silver-tin                  | Aluminium                      | 8 x 10 <sup>-6</sup>      | 0.05                                     | Х                             |

| 3.          | s19                 | (a)                                                   | р <sup>+</sup> -р              | Gold                        | Silver                         | 7x10 <sup>-6</sup>        | 0.018                                    | Х                             |

| 2•<br>4.    | s20                 | (a)                                                   | <b>₽</b> <sup>+</sup> - ₽      | Gold                        | Aluminium                      | 10 <sup>-5</sup>          | 0.018                                    | 450 <sup>°</sup> C            |

| 5.          | s21                 | (b)                                                   | $n^+ - n$                      | Silver-tin                  | Aluminium                      | 6x10 <sup>-6</sup>        | 0.018                                    | 4 <u>0</u> 0°С                |

| 6.          | s23                 | (b)                                                   | р                              | Gold                        | Aluminium                      | 6x1 <b>0<sup>-6</sup></b> | 0.018                                    | Х                             |

| 7.          | s24                 | (b)                                                   | n <sup>+</sup> -n              | Silver-tin                  | Gold                           | 6x10 <sup>-6</sup>        | 0.018                                    | 450 <sup>0</sup> C            |

| 8.          | s2 <b>7</b>         | (b)                                                   | q <b>-</b> +q                  | Gold                        | Gold                           | 7x10 <sup>-6</sup>        | 0.018                                    | 120°C                         |

| 9.          | s30                 | (b)                                                   | n <sup>+</sup> -n              | Silver-tin                  | Gold                           | 6x10 <sup>-6</sup>        | 0.018                                    | x                             |

| 10.         | 531 n               | <b>(</b> b)                                           | n <sup>+</sup> -n              | Silve <b>r-</b> tin         | Aluminium                      | 8x10 <sup>-6</sup>        | 0.018                                    | o <b></b> €600 <sup>°</sup> C |

$\geq$

TABLE-4.1 (Contd)

| Sl.<br>No. |       | Chemical<br>eleaning<br>by proce-<br>ss (a)or<br>(b) | seni-con-         | <pre>§ Type of § ohmic contact</pre> | Schottky<br>Metal<br>contact | Pressure<br>of depo-<br>sition in<br>torr | Area of A<br>contact<br>in cn <sup>2</sup> | Heat<br>treatment<br>if any |

|------------|-------|------------------------------------------------------|-------------------|--------------------------------------|------------------------------|-------------------------------------------|--------------------------------------------|-----------------------------|

|            | ~     |                                                      |                   |                                      |                              |                                           |                                            |                             |

| 11         | S31 p | (b)                                                  | p <sup>+</sup> ∸p | Gold                                 | Aluminium                    | 8x10 <sup>-6</sup>                        | 0.018                                      | 0 <b>-6</b> 00°C            |

| 12         | 532 n | (b)                                                  | n <sup>+</sup> -n | Silver-tin                           | Gold -alumi-<br>nium         | 5×10 <sup>-6</sup>                        | 0.018                                      | o‰600°℃                     |

| 13         | s32 p | (b)                                                  | p <sup>+</sup> -p | Gold -<br>Aluniniun                  | Gold-<br>Aluminium           | <b>5x</b> 10 <sup>-6</sup>                | 0.018                                      | 200°C                       |

| 14         | 533 n | (b)                                                  | n <b>+ -</b> n    | Silver-<br>tin                       | Gold-<br>Antimony            | 6x10 <sup>-6</sup>                        | 0.018                                      | ∩-500°€                     |

| 15         | \$33p | (b)                                                  | ₽ <b>+ ~</b> ₽    | Gold-<br>Aluninium                   | Gold-Antinon;                | y 5x10 <sup>6</sup>                       | 0:018                                      | 120 <sup>°</sup> c          |

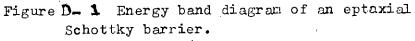

#### 4.3 MEASUREMENTS:

Current-voltage (I-V) and Capacitance-voltage (C-V) measurements were performed on the Schottky diode in order to find out the parameters e.g. barrier height, ideality parameter, series resistance and interface-states density etc. A low frequency equivalent circuit of a Schottky diode is given in figure -4.2 where  $R_s$  represents the series resistance, R is the diode resistance and C is the capacitance of the diode.  $R_s$  is the sum of resistance of quosisi-neutral region (within epitaxial layer), the spreading resistance of the barrier, and the contact resistance due to ohnic contact.

# 4.3.1 CURRENT - VOLTAGE MEASUREMENT:

I-V measurements was performed on the diodes both in forward and reverse directions. These were obtained directly on a x-y plotter. The forward-characteristics were drawn upto 500 mV and reverse characteristics were drawn upto 4/5 volts. The value of barrier height  $\emptyset_B$  and ideality parameter, n can be obtained from the plot of LogI Vs V in forward direction according to the following equation. (4.1). Log I Vs. V plots were straight lines.

$$\delta_{\rm B} = -\frac{{\rm KT}}{{\rm q}} - \ln \left( -\frac{{\rm SA}^{**} {\rm T}^2}{{\rm I}_{\rm S}} \right)$$

(4.1)

and

$$n = -\frac{q}{KT}$$

.  $\frac{\partial v}{\partial (\ln I)}$

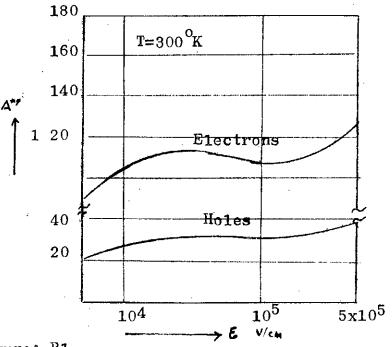

The effective Richardson's constant A\*\* is function of electric field at the interface. In the range of electric field of

R ₩-R S С FIG. 42 EQUVALENT CIRCUIT OF SCHOTTKY DIODE 25 mh 122N m 0.] uí 1 δ ٠. GR - 916A RF RADIO RECIEVER RF BRIDGE GENERATOR DETECTOR AS FIG.4.3 SET UP FOR CAPACITANCE MEASUREMENT . -

10<sup>4</sup> to  $2x10^5 v$  /cm, A\*\* is given by (Appendix-2)

A\*\* = 115  $\operatorname{amp/cm}^2 / \operatorname{o}_K^2$  ..... for electrons = 30  $\operatorname{amp/cm}^2 / \operatorname{o}_K^2$  ..... for holes.

Diode Series resistance R was neasured by biasing the diodes far beyond the diode region, usually above 5 ma.

# 4.3.2 <u>CAPACITANCE -VOLTAGE MEASUREMENT</u> (24)

Diode capacitance, C was measured with a small ac voltage superimposed upon the reverse bias. Straight line was obtained by plotting  $1/C^2$  versus the reverse voltage. The barrier height is derived from the intercept V<sub>i</sub> of this plot and the impurity concentration of the semiconductor is found from the slope of the straight line plot according to following equation (4.2).

Where C is the capacitance per unit area.

However, when deep level impurities are present, these levels are filled upto quasi-Fermi level under forward bias condition and their space charge density is simply given by  $N_D$ . But under the reverse bias, the traps empty down to a certain level below conduction band and the space charge is nonuniform and their density is given by  $N_D + N_t$ , where  $N_t$  is deep level impurity concentration. Thus Goodman<sup>(24)</sup> showed that

$$\frac{d(1/C^2)}{dV} = \frac{-2}{q N_D} \text{ for forward bias}$$

$$\frac{d(1/C^{-})}{dV} = \frac{-2}{q(N_{D} + N_{t})} \epsilon_{s}$$

for large reverse bias (4.3)

Thus when the traps are present, the plot of  $1/c^2$  Vs. V does not show just one straight line, instead it gives two straight lines. The slope of the straight line in forward bias and small reverse bias is determined by the shallow impurity and at large reverse bias the slope is different and is due to sum of shallow and deep level impurities.

The experimental set-up for capacitance measurement has been shown in figure-4:3 where the biasing to the diode is done external to the bridge. GR-916A radio-frequency bridge was used where the lead capacitance correction were provided. Measurement was carried out at 1 MH<sub>z</sub> because with such a high frequency the traps cannot respond. The bridge measures the series resistance and series capacitance directly and these values were transformed into parallel resistance R<sub>p</sub> and parallel capacitance C<sub>p</sub>. Diode resistance R and capacitance C may be calculated from the following equations:-

$$\frac{1}{R_{p}} = \left[-\frac{1}{R} + \left(\frac{R_{p}}{R} + 1\right) + \frac{\omega^{2} R_{s}^{2} c^{2}}{R}\right] / \left[\left(\frac{R_{s}}{R} + 1\right) + \frac{\omega^{2} R_{s}^{2} c^{2}}{R}\right]$$

$$c_{p} = c / \left[\left(-\frac{R_{s}}{R} + 1\right) + \frac{\omega^{2} R_{s}^{2} c^{2}}{R}\right]$$

40.

1-2 \

Thus when

$$R_s/R \ll 1$$

and  $w^2 R_s^2 c^2 \ll 1$ , then

$c \cong c_p$

(4.4)

These two conditions are satisfied because under, reverse bias  $R_{s}/R$  (<1 and diode capacitance is smaller than a nanofarad.

Also it can be derived that

$$\frac{(2 (V_{bi} - V - KT/Q))}{1/C_{p}^{2}} = \frac{(2 (V_{bi} - V - KT/Q))}{Sq \in N_{D}} + 2 \mathcal{W}^{2} R_{s}^{2} \qquad (4.5)$$