# ANALYTICAL MODELLING OF BREAKDOWN IN SHORT CHANNEL MOSFET's

A Thesis submitted to the Electrical and Electronic Engineering Department of BUET, Dhaka, in partial fulfilment of the requirements for the degree of Master of Science in Engineering (Electrical and/Electronic)

### MD. TANVIR QUDDUS

OCTOBER 1993

The thesis ANALYTICAL MODELLING OF BREAKDOWN IN SHORT CHANNEL MOSFET's submitted by Md. Tanvir Quddus, Roll No. 901327P, Session '88-89 to the Electrical and Electronic Engineering Department of B.U.E.T. has been accepted as satisfactory for partial fulfilment of the requirements for the degree of Master of Science in Engineering (Electrical and Electronic).

#### **BOARD OF EXAMINERS**

- Dr. M. M. Shahidul Hassan Associate Professor Department of EEE B.U.E.T., Dhaka-1000, Bangladesh.

- 2. Dr. Saiful Islam Professor and Head Department of EEE B.U.E.T., Dhaka-1000, Bangladesh.

- Dr. Mohammad Ali Choudhury Associate Professor Department of EEE B.U.E.T., Dhaka-1000, Bangladesh.

- Dr. Shamsuddin Ahmed Head Department of EEE ICTVTR, Board Bazar, Gazipur, Dhaka.

Chairman (Supervisor)

Member \_\_\_\_\_\_ 26/10/93 (Ex-officio)

machondhu Member .

Chinece 28.10.9 Member

(External)

# DECLARATION

I hereby declare that this work has been done by me and it has not been submitted elsewhere for the award of any degree or diploma.

Countersigned

(Dr. M. M. Shahidul Hassan)

Supervisor

And dus . tanik

(Md. Tanvir Quddus)

### ACKNOWLEDGEMENTS

The author would like to express his profound indebtness and deep sense of gratitude to his supervisor Dr. M. M. Shahidul Hassan, Associate Professor of the department of Electrical and Electronic Engineering, BUET, for his continious guidance, friendly supervision, constant encouragement and specially for his valuable suggestions and help during the entire progress of the work.

The author wishes to express his thanks and deep respect to Dr. Saiful Islam, Professor and Head, Department of Electrical and Electronic Engineering, BUET, for his support to complete this work successfully.

The author also wishes to express his thanks to Dr. Lutful Kabir and Dr. Mohammad Ali Choudhury for their helpful comments and suggestions. Finally, the author expresses his sincerest and special thanks to Mr. Masud Mustafa and Mr. Iqbal Yousuf along with other friends and colleagues for their support.

iν

### ABSTRACT

MOSFETs are used extensively in VLSI Technology specially in various digital circuits such as microprocessors, semiconductor memories etc. Since the birth of the IC fabrication the need for the reduction of device dimensions is driven by the requirement that IC of high complexity can be fabricated. The purpose of microminiaturization of the MOSFET is not only to increase the packing density but also to improve the circuit performance. The fundamental issue of downsizing the MOS transistor is to preserve the long channel characteristics after miniaturization. But as the dimension of the MOSFET is reduced, departure from the long channel behaviour occur due to various undesirable short channel effects./Among the various short channel problems, avalanche induced breakdown due to hot carriers produced by impact ionization is a major one. The drain characteristics of the short channel MOSFET exhibits a rapid rise in the current due to this destructive phenomena which leads to the destruction of the device. So the study of short channel MOSFET along with the physics in the avalanche induced breakdown regime is very important from the design point of view. A number of breakdown models have been developed for short channel MOSFET in the last few years. In this thesis a simple analytical breakdown model incorporating the physics of the breakdown has been presented. This model not only establishes the relation between different voltage and current of the MOSFET but also demonstrates the ability to represent various short channel effects. The model also shows that the primary phase of breakdown is initiated by excess channel current whereas the secondary phase is due to emitter current and both these currents again strongly depend on the flow of substrate current.

v

## CONTENTS

iv

ν

$\mathbf{x}$

xili

$\mathbf{x}\mathbf{v}$

### ACKNOWLEDGEMENTS

### ABSTRACT

### LIST OF FIGURES

LIST OF SYMBOLS

### LIST OF ABBREVIATIONS

| 1. | 1. INTRODUCTION |                                            | 1          |

|----|-----------------|--------------------------------------------|------------|

|    | 1.1             | Short channel MOSFETs                      | 1          |

|    | 1 <b>.2</b>     | Short-channel effects of a MOSFET          | 8          |

|    | 1 <b>.3</b>     | Effect of substrate bias                   | , 9        |

|    | 1.4             | Characteristics of a short channel MOSFET  | 11         |

|    | 1.5             | Hot carrier effect and avalanche breakdown | 1 <b>2</b> |

vi

|    | 1.6         | Review of recent works on the breakdown of MOSFET      | 14         |

|----|-------------|--------------------------------------------------------|------------|

|    | 1 <b>.7</b> | Summary of the thesis                                  | 16         |

| 2. |             | ALYTICAL BREAKDOWN MODEL OF SHORT CHANNEL              | ,<br>• ,   |

|    | мо          | SFET                                                   | 18         |

|    | <b>2</b> .1 | Introduction                                           | 18         |

|    | 2.2         | Enhanced Body Effect                                   | 22         |

|    | 2.3         | Channel current model                                  | 24         |

|    | 2.3         | .1 Velocity saturation effect                          | <b>3</b> 0 |

|    | 2.3         | .2 Effect of $L$ , $V_{DS}$ , $Z$ on threshold voltage | 34         |

|    | 2.3         | .3 Channel length modulation                           | 41         |

| :  | 2.4 \$      | Substrate current model                                | 45         |

| 2  | 2.5 H       | Excess channel current model                           | 49         |

|    | 2.5.        | 1 Transition phase                                     | 55         |

| 2  | 2.6 E       | Emitter current model                                  | 57         |

|     | 2.7 Co        | onclusions                                       | 65         |

|-----|---------------|--------------------------------------------------|------------|

| 3.  | MOD           | EL IMPLEMENTATION AND RESULTS                    | 67         |

|     | 3.1 Int       | roduction                                        | 67         |

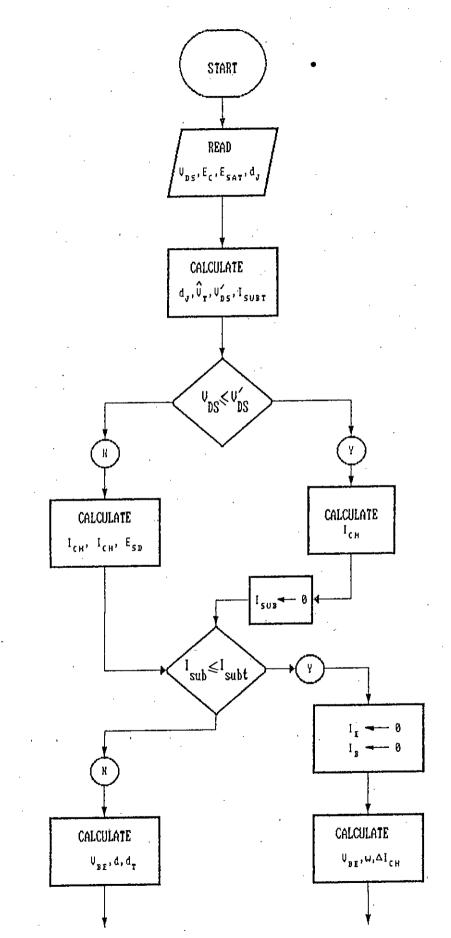

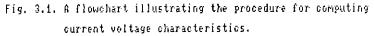

|     | 3.2 A         | nalysis of the Computational method used         | <b>6</b> 8 |

|     | 3.3 Re        | sults and Discussions                            | 72         |

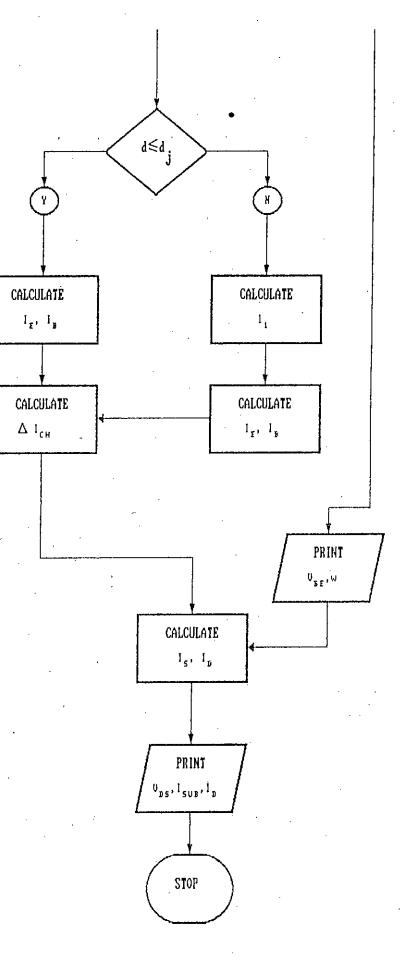

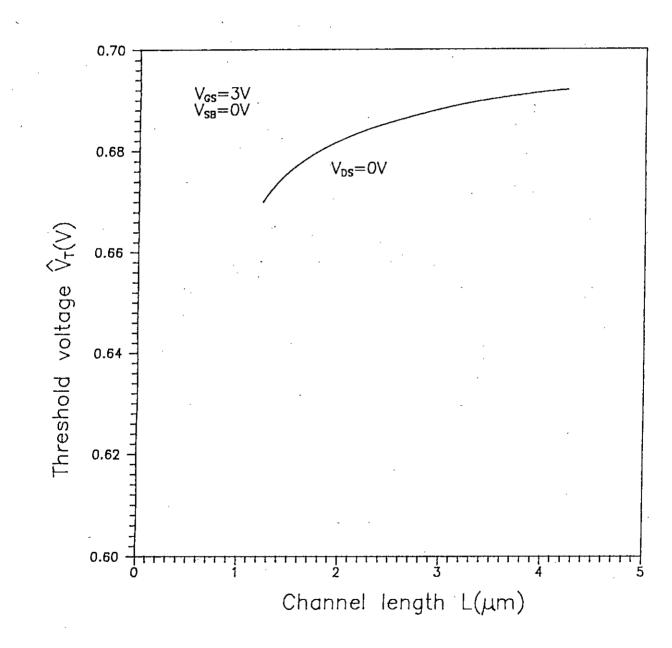

|     | <b>3.3</b> .1 | Threshold and saturation voltage                 | 72         |

|     | 3.3.2         | Channel current                                  | 75         |

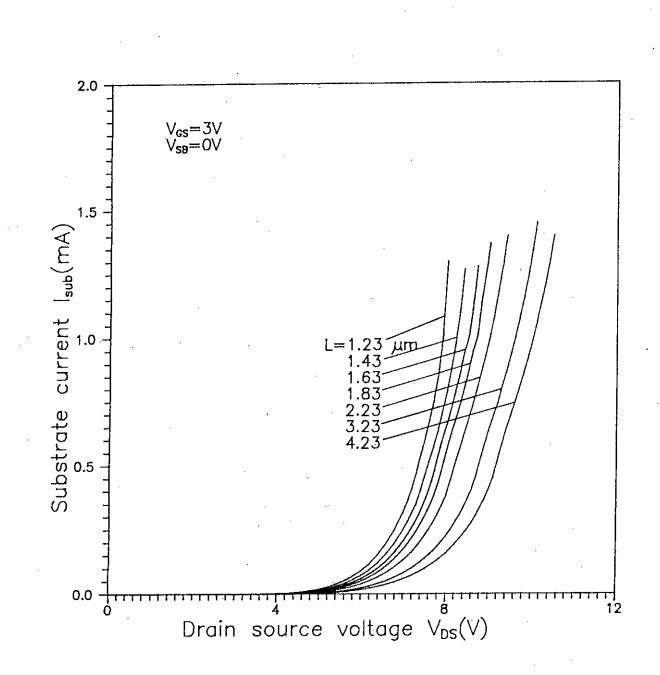

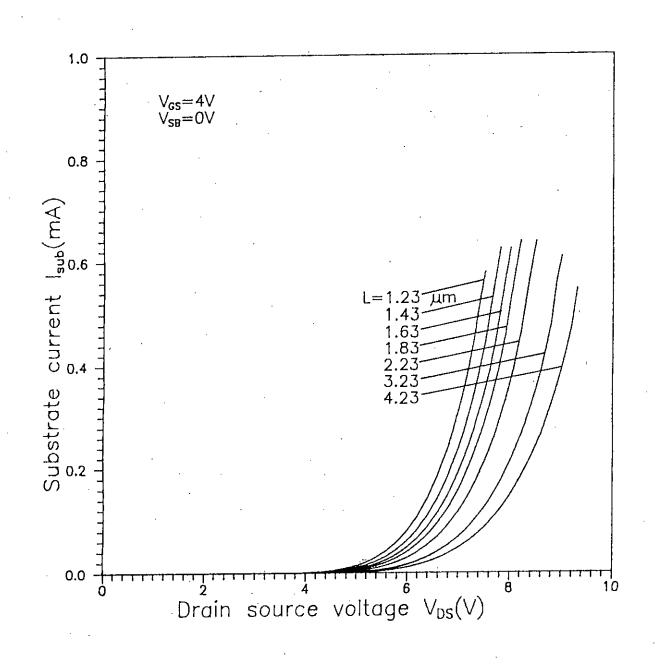

|     | 3.3.3         | Lateral electric field and substrate current     | 78         |

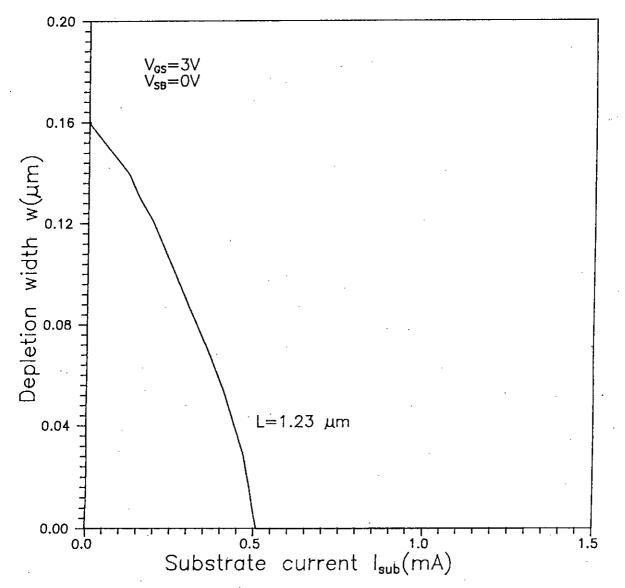

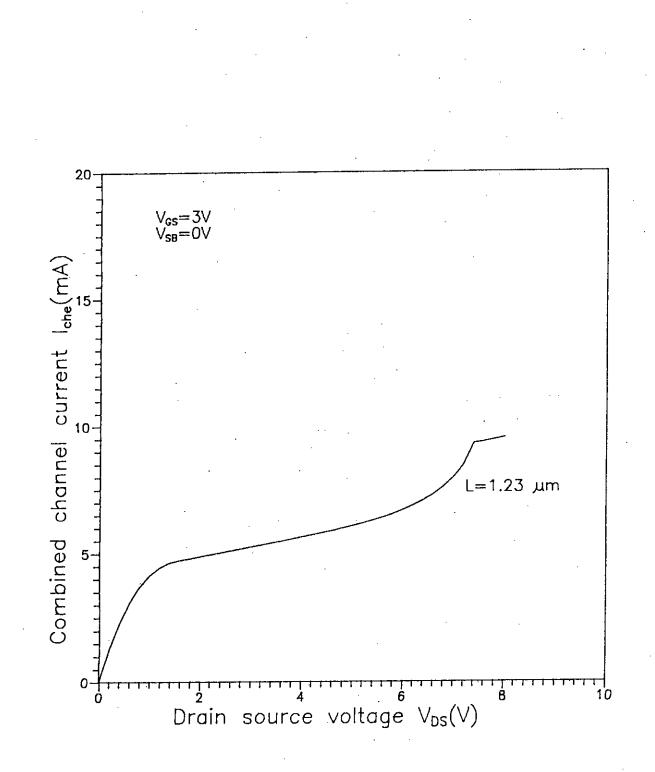

|     | 3.3.4         | Depletion width and the combined channel current | 82         |

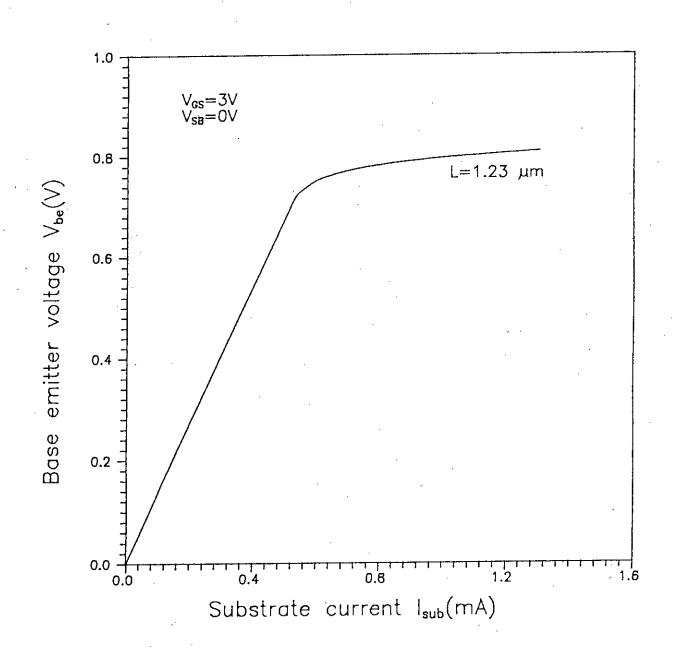

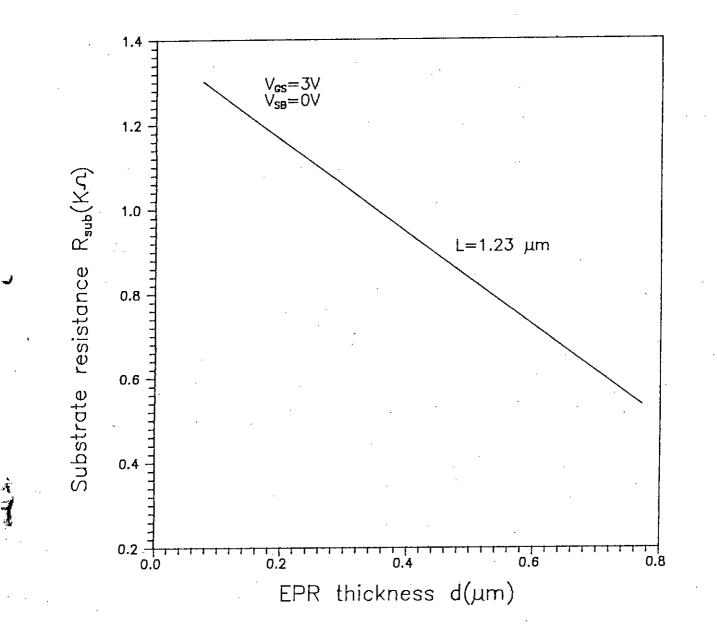

|     | 3.3.5         | Base emitter voltage and substrate resistance    | 86         |

| -   | 3.3.6         | Drain current                                    | 86         |

| 3.4 | Conclu        | isions                                           | 90         |

viii

| 4. | Co  | clusions and Suggestions | 91 |

|----|-----|--------------------------|----|

|    | 4.1 | Conclusions              | 91 |

|    |     |                          | 92 |

|    |     | LENCES                   | 93 |

### APPENDICES

| APPENDIX A   | Determination of the expression of $l_m$ as a function of $L$ |                |

|--------------|---------------------------------------------------------------|----------------|

| and $V_{DS}$ |                                                               | 96             |

|              |                                                               |                |

| APPENDIX B   | Determination of substrate resistance $R_{sub}$ in EBE phase  | <del>9</del> 8 |

# LIST OF FIGURES

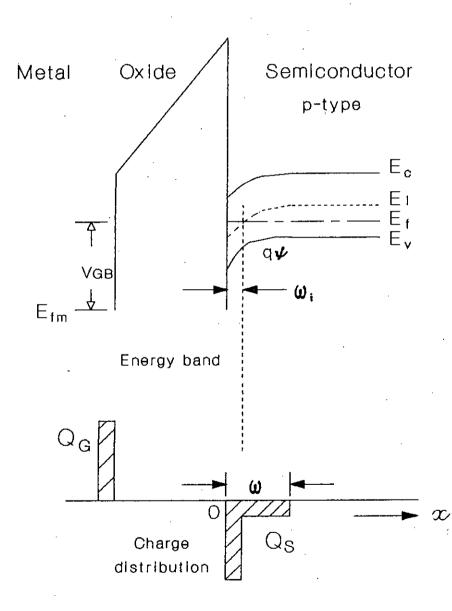

| 1.1 | Energy band and charge distribution diagram of a MOSFET                   | 2          |

|-----|---------------------------------------------------------------------------|------------|

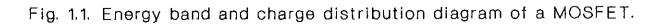

| 1.2 | Energy band diagram of a MOSFET at the onset of strong inversion $\ .$    | 4          |

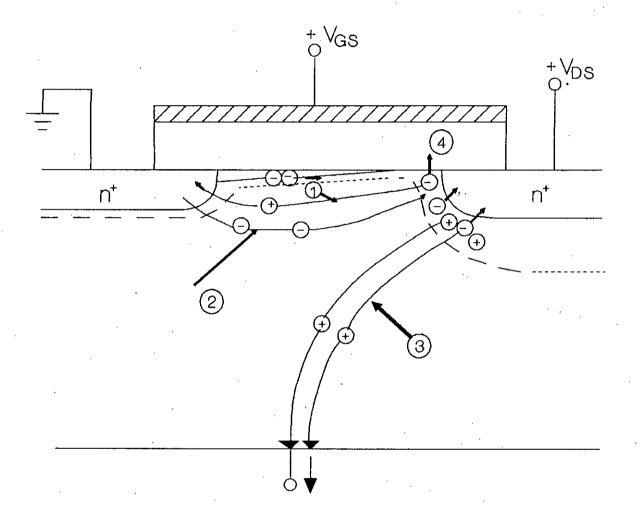

| 1.3 | Effect of hot carrier in short channel MOSFET                             | 13         |

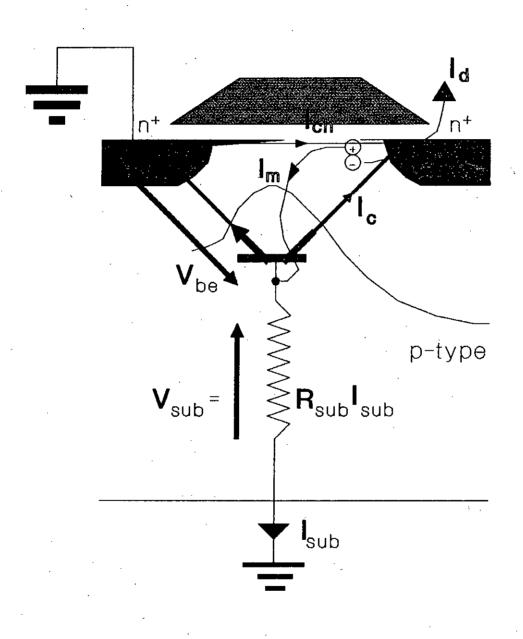

| 2.1 | Current components with bipolar induced breakdown in short channel MOSFET | 19         |

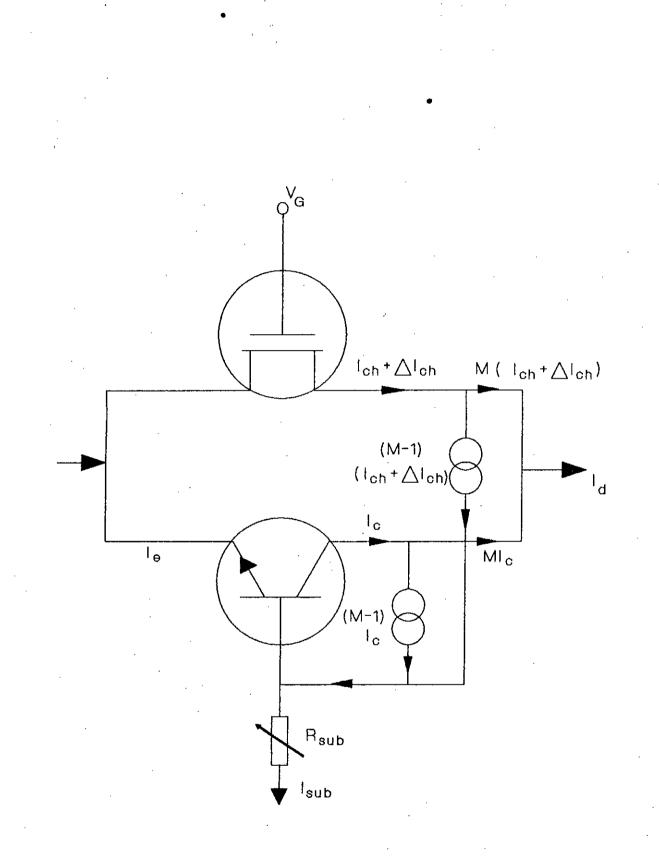

| 2.2 | Equivalent circuit of a short channel MOSFET after the bipolar turn on    | 21         |

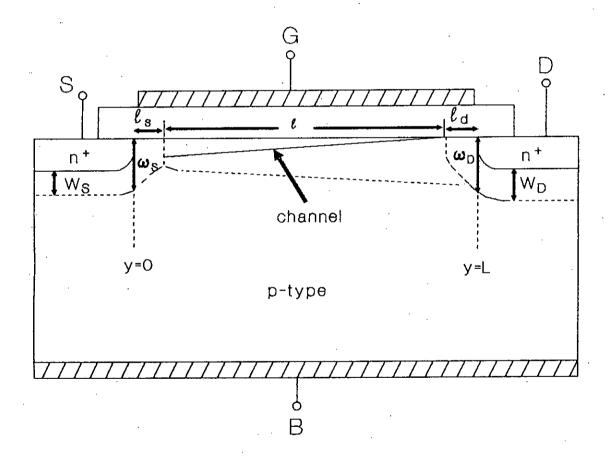

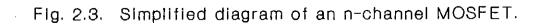

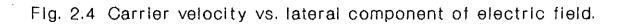

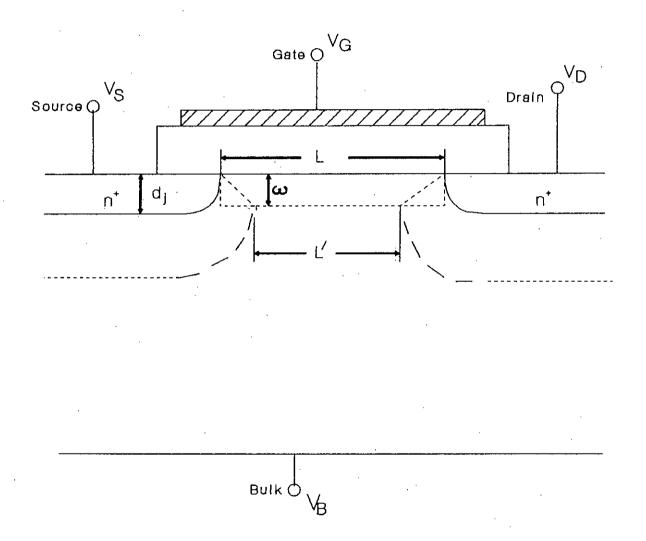

| 2.3 | Simplified diagram of an n-channel MOSFET                                 | 25         |

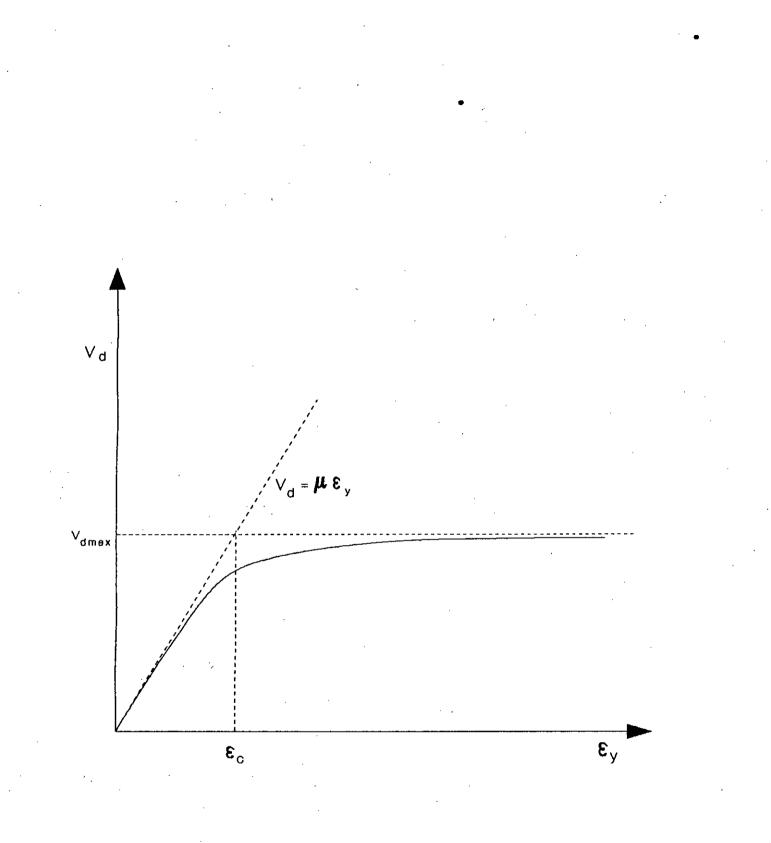

| 2.4 | Carrier velocity versus lateral component of electric field               | <b>3</b> 1 |

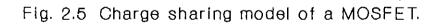

| 2.5 | Charge sharing model of a MOSFET                                          | 35         |

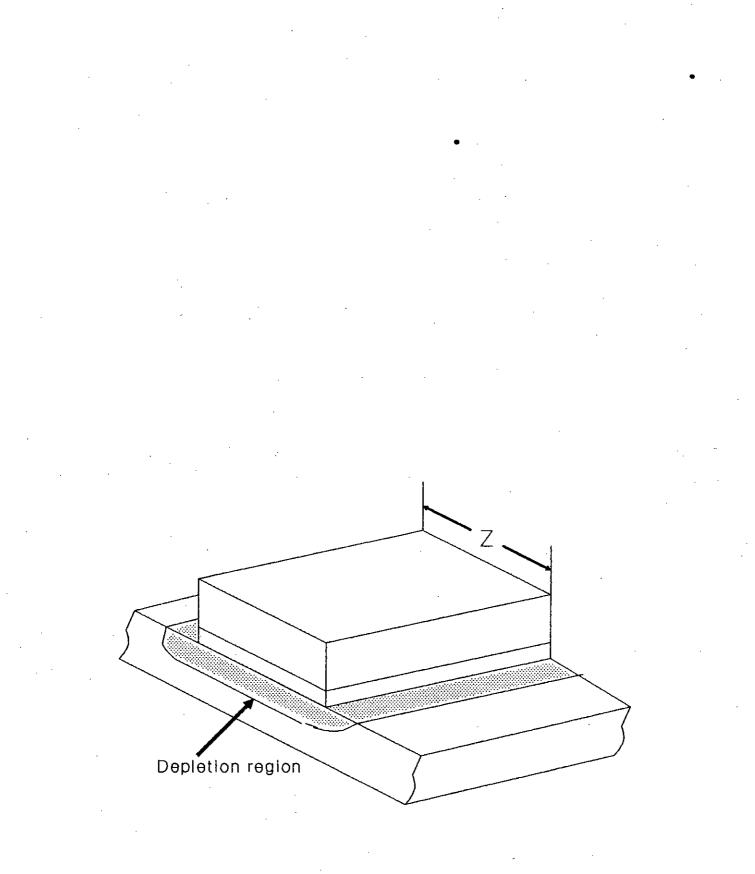

| 2.6 | Effect of fringing field in narrow channel MOSFET                         | 39         |

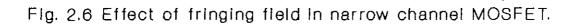

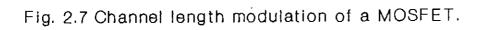

| 2.7 | Channel length modulation of a MOSFET                                     | 42         |

х

| 2.8  | Schematic illustration of the EBE phase with corresponding potential                                 |    |

|------|------------------------------------------------------------------------------------------------------|----|

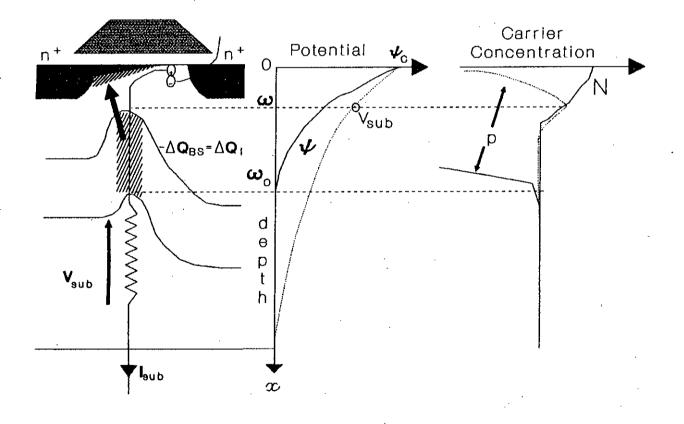

|      | and carrier distribution                                                                             | 50 |

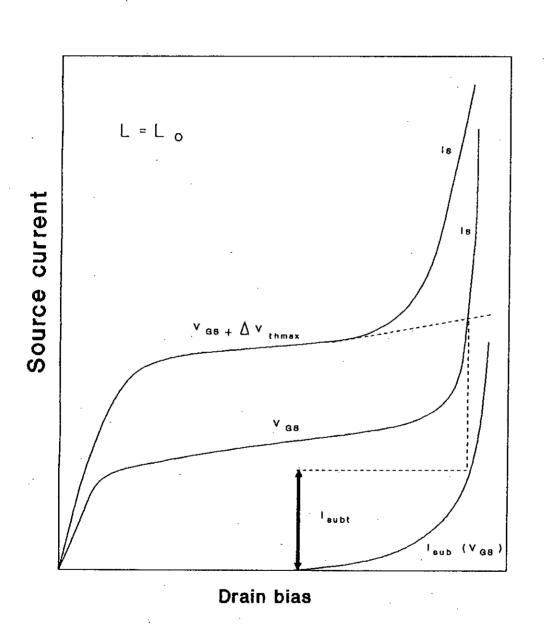

| 2.9  | Illustration of the method of extracting the $I_{subt}$ current $\ldots$                             | 54 |

| 2.10 | Schematic illustration of the transition phase with corresponding potential and carrier distribution | 56 |

| 2.11 | Schematic illustration of the bipolar phase with corresponding potential and carrier distribution    | 58 |

| 2.12 | Schematic diagram of the evolution of EPR                                                            | 62 |

| 3.1  | A flow chart illustrating the procedure of computing current voltage characteristics.                | 70 |

| 3.2  | Effect of channel length on threshold voltage of a MOSFET                                            | 73 |

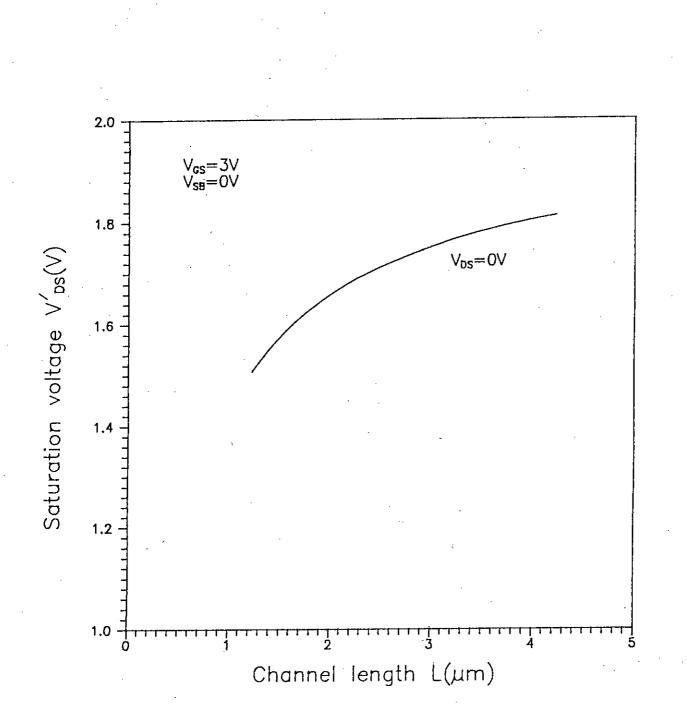

| 3.3  | Effect of channel length on saturation voltage of a MOSFET                                           | 74 |

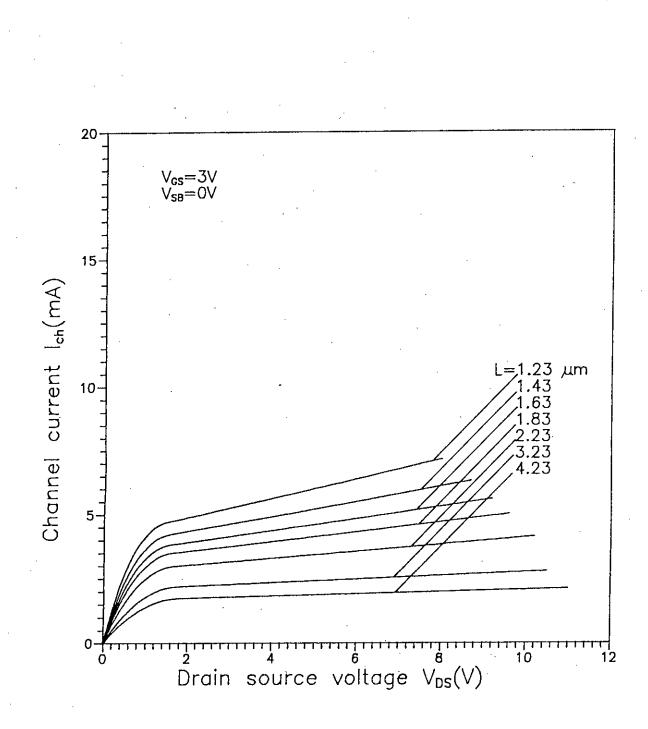

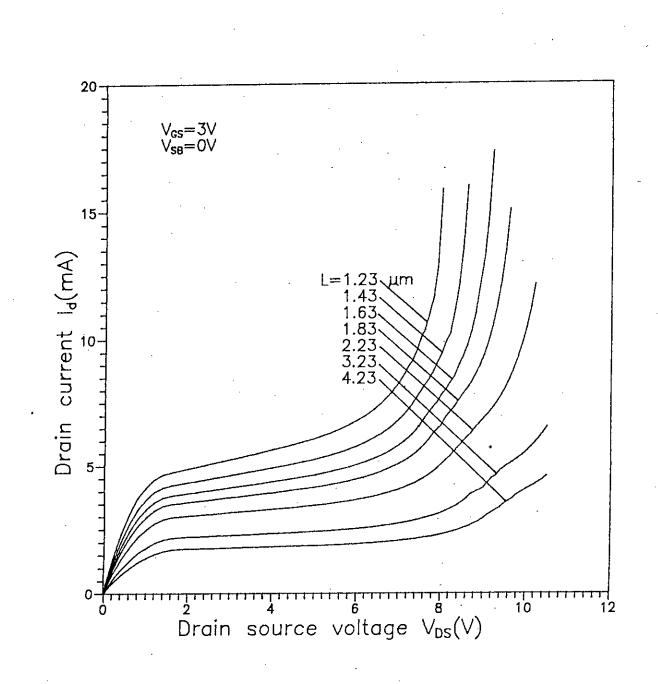

| 3.4  | Channel current vs. drain source voltage characteristics for $V_{GS} = 3V$ .                         | 76 |

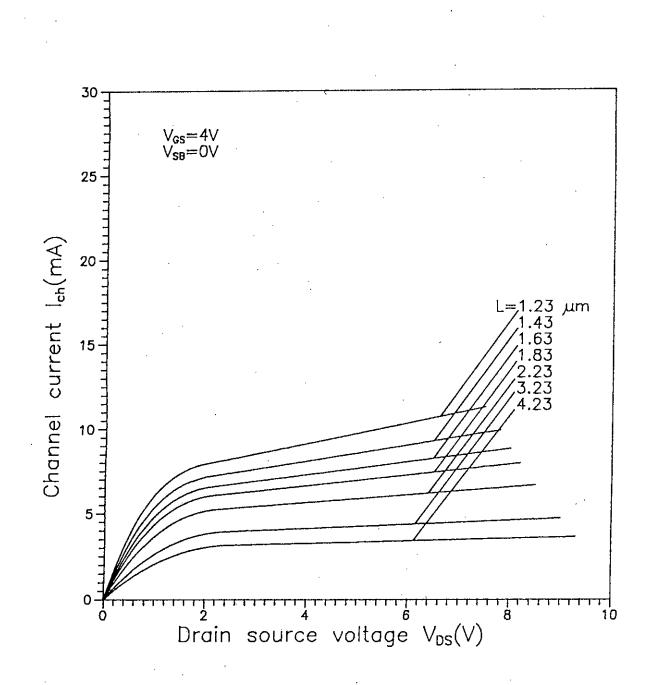

| 3.5  | Channel current vs. drain source voltage characteristics for $V_{GS} = 4V$ .                         | 77 |

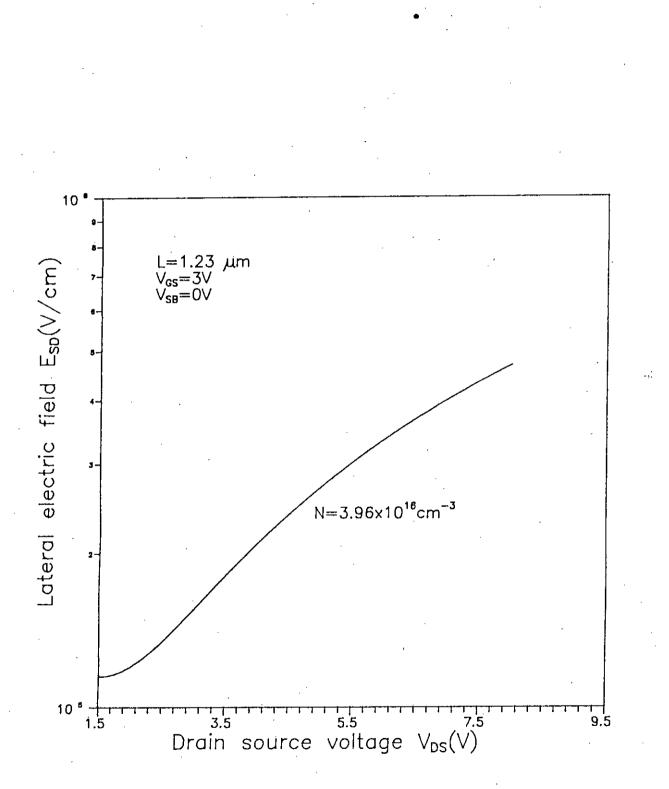

| 3.6  | Effect of drain source voltage on lateral electric field.                                            | 79 |

xi

| 3.7         | Substrate current vs. drain source voltage characteristics for $V_{GS} = 3V$ | 80 |

|-------------|------------------------------------------------------------------------------|----|

| 3.8         | Substrate current vs. drain source voltage characteristics for $V_{GS} = 4V$ | 81 |

| 3.9         | Effect of substrate current on depletion width                               | 83 |

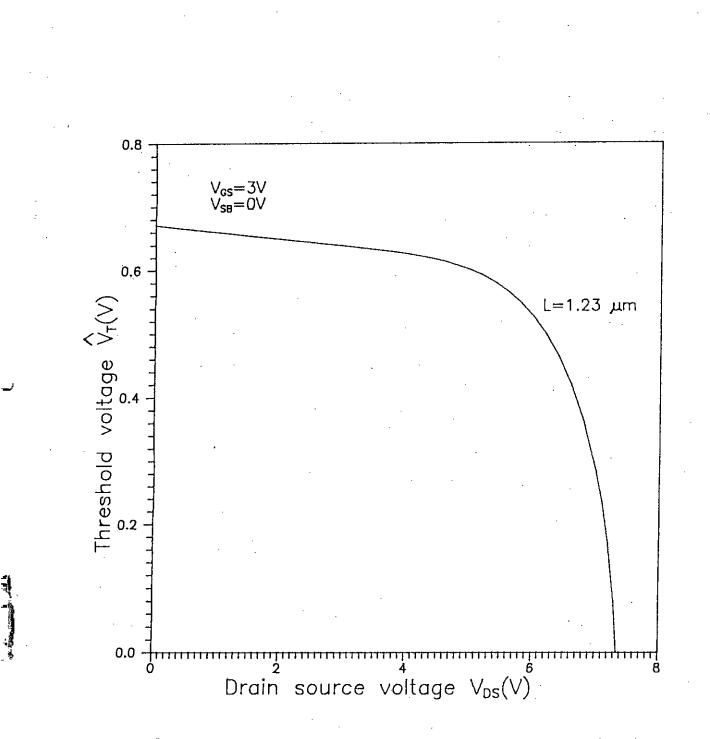

| 3.10        | Effect of drain source voltage on threshold voltage of a MOSFET              | 84 |

| <b>3.11</b> | Effect of drain source voltage on combined channel current                   | 85 |

| 3.12        | Effect of substrate current on base emitter voltage.                         | 87 |

| 3.13        | Effect of EPR thickness on substrate resistance.                             | 88 |

| 3.14        | Drain current vs. drain source voltage characteristics                       | 89 |

# LIST OF SYMBOLS

| 1.          | $V_T$           | V                   | Threshold voltage.          |

|-------------|-----------------|---------------------|-----------------------------|

| 2.          | $\phi_{f}$      | v                   | Fermi potential.            |

| 3.          | $\phi_{ m si}$  | V                   | Surface potential at strong |

| 4.          | ψ,              | V                   | Surface potential.          |

| 5.          | w               | m                   | Depletion width.            |

| 6.          | Ws              | m                   | Source depletion width.     |

| 7.          | $W_D$           | m                   | Drain depletion width.      |

| 8.          | $\epsilon_x$    | $Vm^{-1}$           | Normal electric field.      |

| 9.          | $\epsilon_v$    | $Vm^{-1}$           | Lateral electric field.     |

| 10.         | $Q_I$           | $Cm^{-2}$           | Inversion layer charge.     |

| 11.         | $Q_B$           | $Cm^{-2}$           | Bulk charge.                |

| 1 <b>2.</b> | $Q_S$           | $Cm^{-2}$           | Surface charge.             |

| 1 <b>3.</b> | Im              | Α                   | Multiplication current.     |

| 14.         | l               | m                   | Effective channel length.   |

| 15.         | Ζ               | m                   | Channel width.              |

| 16.         | $\mu_p$         | $m^2 V^{-1} s^{-1}$ | Hole mobility.              |

| 17.         | $\mu_n$         | $m^2 V^{-1} s^{-1}$ | Electron mobility.          |

| 18.         | E,              | $Fm^{-1}$           | Permittivity of silicon.    |

| 19.         | $\alpha_1$      |                     | Empirical constant.         |

| .20.        | $\alpha_2$      |                     | Empirical constant.         |

| <b>2</b> 1. | $\alpha_3$      |                     | Empirical constant.         |

| 22.         | Vd              | $ms^{-1}$           | Drift velocity.             |

| 23.         | d <sub>j</sub>  | m                   | Junction depth.             |

| 24.         | d               | m                   | EPR thickness.              |

| 25.         | N               | $m^{-3}$            | Substrate doping.           |

| 26.         | N <sub>SD</sub> | $m^{-3}$            | Source and drain Doping.    |

|             |                 |                     |                             |

ltage. ial. itial at strong inversion. tial. lth. ion width. on width. ic field. ic field. er charge. e. n current. nnel length. h. ility. of silicon. istant. istant. istant. h.

xiii

| 27.         | $\hat{V}_T$ | V        | Short channel threshold.   |

|-------------|-------------|----------|----------------------------|

| 28.         | $	au_n$     | <b>S</b> | Electron lifetime.         |

| 29.         | $L_n$       | m        | Electron diffusion length. |

| <b>3</b> 0. | $L_p$       | m        | Hole diffusion length.     |

| <b>3</b> 1. | $V_{DS}$    | V .      | Drain source voltage.      |

| 32.         | $V_{GS}$    | V        | Gate source voltage.       |

| 33.         | $V_{GB}$    | v        | Gate bulk voltage.         |

| 34.         | $V_{SB}$    | V        | Source bulkvoltage.        |

| 35.         | $U_T$       | V        | Thermal voltage.           |

|             |             |          |                            |

xıv

in Ali

i

# LIST OF ABBREVIATIONS

| 1. | QNR | Quasi neutral region.         |

|----|-----|-------------------------------|

| 2. | EBE | Enhanced body effect.         |

| 3. | EPR | Equipotential region.         |

| 4. | VDT | Voltage doping transformation |

### CHAPTER 1

### INTRODUCTION

### 1.1 Short channel MOSFETs

A MOSFET is a four terminal device in which the lateral current flow is controlled by an externally applied vertical electric field. A typical n-channel enhancement MOSFET consists of a relatively lightly doped p type substrate into which two heavily doped  $n^+$  regions are diffused which act as source and drain respectively. The region of inversion layer of mobile electrons between source and drain is the channel and a thin layer of insulating material separates the channel from the metal gate electrode. The metal area of the gate in conjunction with the insulating dielectric oxide layer and the semiconductor channel form a parallel plate capacitor. The voltage applied to the gate controls the carriers in the conduction channel and thus controls the conductivity of the device.

The threshold voltage  $V_T$  of a MOSFET is defined as the minimum voltage required to induce the conduction channel. When a gate voltage equal to  $V_T$  is applied to a MOSFET it produces a downward bending of the energy band-diagram at semiconductor-oxide interface and causes the midgap energy  $E_i$  to cross over

the constant fermi level by an amount  $\phi_f$  at or near the silicon surface (Fig. 1.1) (Fig. 1.2). When this happens an inversion layer of width  $w_i$  is formed at the silicon surface in which the electron density is equal to the hole density in the bulk because the electron and the hole density in the substrate is given by

$$n = n_i e^{\frac{S_p - S_I}{KT}} \tag{1.1}$$

and

$$p = n_i e^{\frac{B_j - B_p}{KT}} \tag{1.2}$$

where,  $n_i$  is the intrinsic carrier concentration,  $E_F$  is the fermi energy level and  $E_I$  is the intrinsic energy level. The values of  $E_F$  and  $E_I$  are given by

$$E_F = -q\phi_f \tag{1.3}$$

and

$$E_I = -q\psi \tag{1.4}$$

where ,  $\phi_f$  and  $\psi$  are the potential of the fermi and the intrinsic level respectively. This condition is defined as the onset of the strong inversion and the surface potential  $\psi_s$  under this condition is given by

$$\psi_s = 2\phi_f = \phi_{si} \tag{1.5}$$

The left side of  $X_I$  (Fig. 1.2) remains n type whereas the the right side remains

•

•

Fig. 1.2. Energy band diagram of a MOSFET at the onset of strong inversion.

p type. So, at the left side of  $X_I$  a region of inversion layer of width  $w_i$  and at the right side of  $X_I$  a surface depletion region of width w is produced which extends upto bulk. The depletion layer width w and bulk charge  $Q_B$  is given by

$$w = \sqrt{\frac{2\epsilon_s \psi_s}{qN_A}} \tag{1.6}$$

(1.7)

and

$$Q_B = -qN_A w$$

where,  $N_A$  is the doping density of the substrate.

The charge balance equation in the surface region of a MOSFET can be written as

$$Q_S = Q_I + Q_B$$

$$= Q_G \tag{1.8}$$

where,  $Q_S$ ,  $Q_I$ ,  $Q_G$  are total charge, inversion layer charge and gate charge respectively.

The applied gate voltage  $V_G$  in a MOSFET is shared by the flat band voltage  $V_{FB}$ , surface potential  $\psi_s$  and voltage across the oxide  $V_o$  and is given by

$$V_{GB} = V_{FB} + \psi_s - \frac{Q_S}{C_o}$$

$$= V_{FB} + \psi_s + \gamma \sqrt{\psi_s}$$

(1.9)

where,

$$\gamma = \frac{\sqrt{2q\epsilon_* N_A}}{C_o} \tag{1.10}$$

In this equation  $C_o$  is the oxide capacitance per unit area and is given by

$$C_o = \frac{\epsilon_{ox}}{t_{ox}} \tag{1.11}$$

where,  $t_{ox}$  is the oxide thickness.

From the expression of the gate voltage the threshold voltage can be represented as

$$V_T \equiv V_{FB} + \psi_s - \frac{Q_B}{C_o} \tag{1.12}$$

where,  $\psi_{\bullet} = 2\phi_{I}$

At the onset of strong inversion  $Q_I \ll Q_B$ , therefore, equation (1.8) reduces to  $Q_S = Q_I + Q_B \approx Q_B$ . Now the inversion layer charge at a gate voltage above threshold is given by

$$Q_I = -C_o(V_{GB} - V_T)$$

(1.13)

When a positive gate voltage greater than  $V_T$  is applied to the gate with respect to substrate, positive charge in effect is deposited on the metal and in response, negative charge is induced in the semiconductor below the semiconductor-oxide interface by the formation of a depletion region of immobile negative charge and a surface region of a very thin layer containing mobile electrons. These thin layer of induced electron form the effective channel of the MOSFET and the effect of gate voltage is to vary the conductance of this induced channel for a low drain to source voltage. When a drain voltage  $V_{DS}$  greater than saturation voltage  $V'_{DS}$  is applied between drain and source, the electron density near the drain will be reduced at  $V_{DS} > V'_{DS}$ , pinch-off will occur near the drain. After the pinchoff of the channel the effective channel length of a MOSFET differs from its physical channel length. Depending on the physical length of the channel MOSFETs are catagorised into long and short channel MOSFET. When the channel length L is much longer than the sum of source and drain depletetion widths  $(W_S + W_D)$  (Fig. 2.3) then it is called long channel MOSFET and when  $L \leq (W_S + W_D)$  then the MOSFET is called short channel MOSFET. The depletion widths  $W_S$  and  $W_D$  are controlled by bias voltage  $V_{DB}$  and  $V_{SB}$  respectively where  $V_{DB}$  represents drain-bulk bias and  $V_{SB}$  the source bulk bias. In short channel MOSFETs the difference between effective and physical channel length increases with the increase of drain source voltage, wheras in long channel it almost remains constant.

The main applications of MOSFET are in VLSI technology, specially in case of digital system such as semiconductor memories, long shift registers, microprocessors etc. To fabricate integrated circuits of high complexity, to increase the packing density and to improve the circuit performance it is required to reduce the size of a MOSFET. But when the device dimensions are reduced by reducing the channel length, the behaviour of the MOSFET departs from the long channel behaviour and we have to consider the short channel effects which arises due to two dimensional potential distribution and high electric field in the channel region.

#### **1.2** Short-channel effects of a MOSFET

When the length of the channel is sufficiently long then the edge effects along the sides of the channel can be neglected and the electric field lines are everywhere

perpendicular to the surface i.e. they had components only along the x direction and a one dimensional analysis is sufficient. But when the length of the channel is reduced, the depletion layer widths of drain and source junctions become comparable to the channel length and a significant part of the electric field lines will have components along both x and y direction. The latter being the direction along the channel length. Hence a two dimensional analysis will be needed for the analysis of short channel MOSFET. Thus, unlike the long channel MOSFET the potential distribution in the short channel MOSFET depends on both the normal field  $\epsilon_x$  (controlled by the gate voltage and back-surface bias) and the lateral field  $\epsilon_{y}$  (controlled by the drain bias). This two dimensional potential results in degradation of the subthreshold behaviour, dependence of the threshold voltage on channel length, biasing voltages and failure of current saturation due to punch through. If the channel is both short and narrow then a three dimensional analysis becomes necessary. Though three dimensional analysis is accurate it is very complex and can be replaced by a simple model for effecient calculation by using empirical approximations and by examining separate phenomena one at a time. The short channel effects can be summarized as i) the edge effects along the sides of the channel at source and drain ii) channel length modulation iii) velocity saturation effects iv) hot carrier effects.

In short channel MOSFET the charges at drain and source edges must be taken into account while calculating the threshold voltage of the MOSFET. Again in short channel MOSFET the lateral extension of the depletion layer region reduces the effective channel length after the channel is pinched off which is known as channel length modulation. When the lateral electric field is increased, the channel mobility becomes field dependent and eventually velocity saturation occurs. If the field is increased further carrier multiplication near the drain occurs leading to substrate current and bipolar transistor action. High field also cause hot carrier injection into

the oxide, leading to oxide charging and subsequent threshold voltage shift. These are the short channel effects of a MOSFET which complicate the device operation and degrade device performance and should be eliminated or minimised so that a physical short channel device can preserve the electrical long channel behaviour and at the same time can maintain its desirable features.

#### **1.3** Effect of substrate bias

In a MOSFET generally the source is connected to the substrate and both terminals are grounded. But when a negative  $V_{BS}$  is applied to the p type substrate (body) with respect to the source  $(n^+)$  a reverse bias voltage  $V_{SB}$  will be induced between the channel and the body junction and also between the source and the substrate junction. In this case the inversion layer-substrate combination will act as a field induced  $n^+p$  junction and the source substrate junction will act as a regular pn junction. In either case, the depletion region is widened and the threshold voltage required to achieve inversion must be increased to accomodate the larger  $Q_B$ .

When a voltage  $V_{SB}$  is applied between the source and substrate the bias will shift the quasi fermi level at the source by  $V_{SB}$ . So the surface potential at the source during strong inversion can be modified as

$$\psi_s = V_{SB} + \phi_{si} \tag{1.14}$$

When  $V_{SB}$  is zero the surface potential and the charge in the space charge layer is given by

$$\psi_s = 2\phi_f \tag{1.15}$$

and

$$Q_B = -q N_A w$$

=  $-(2q\epsilon_A N_A \phi_{si})^{1/2}$  (1.16)

For an arbitary reverse bias voltage  $V_{SB}$ , the bulk charge becomes

$$Q_B = -[2q\epsilon_s N_A (V_{SB} + \phi_{si})]^{1/2}$$

(1.17)

Therefore, the increased differential charge is

$$\Delta Q_B = -(2q\epsilon_s N_A)^{1/2} [(V_{SB} + \phi_{si})^{1/2} - \phi_{si}^{1/2}]$$

(1.18)

To reach the strong inversion, the applied gate voltage must be increased to compensate for  $\Delta Q_B$ . Therefore,

$$\Delta V_T = -\frac{\Delta Q_B}{C_o}$$

=  $\frac{(2q\epsilon_s N_A)^{1/2}}{C_o} [(V_{SB} + \phi_{si})^{1/2} - \phi_{si}^{1/2}]$  (1.19)

When a positive  $V_{BS}$  is applied to the substrate with respect to source then the situation will be reversed. The source-substrate and channel-substrate junction both will be forward biased and to maintain the charge balance equation the inversion layer charge must be increased, whereas, the depletion layer charge is decreased. So in an n channel MOSFET,  $V_{BS}$  must be zero or negative to avoid the forward biase of the source junction.

### **1.4 Characteristics of short channel.MOSFET**

When the dimensions of a MOSFET are reduced the distinct features are seen in device characteristics. First the drain current is found to increase with the drain voltage due to channel length modulation beyond pinch-off. This is in contrast with the I-V curve of a long channel MOSFET, where the drain current becomes constant after the pinch-off condition. But the output current in short channel MOSFET does not saturate. The second feature of a short channel MOSFET can be seen in the subthreshold region where the gate losses control over the drain current. In other words, the output drain current can't be reduced to zero i.e. can't be turned off. The third feature is that due to the presence of velocity saturation the drain current in short channel MOSFET for a fixed drain-source voltage is smaller than the corresponding drain current in long channel MOSFET. The fourth distinct feature of a short channel MOSFET is the shift of its threshold voltage with the channel length as well as drain bias voltage. Whereas, the threshold voltage of a long channel MOSFET is not a function of either drain bias or channel length.

### 1.5 Hot carrier effect and avalanche breakdown

At relatively small  $V_{DS}$ , high electric field will exist in the drain depletion region and electron hole pairs will be generated due to impact ionization. The mechanism of avalanche breakdown of a junction involves the impact ionization of host atoms by energetic carriers. Normal lattice-scattering event can result in the creation of electron-hole pair if the carrier being scattered has sufficient energy. If a large reverse voltage is applied across a p-n junction, the electric field in the transition region becomes large and an electron entering from the p side may be accelerated

to high kinetic energy to cause an ionizing collision with the lattice. A single such interaction results in carrier multiplication. The degree of multiplication can become very high if carriers generated within the transition region also have ionizing collisions with the lattice. This is an avalanche process, since each incoming carrier can initiate the creation of a large number of new carriers.

In the reverse bias drain to substrate junction, the electric field may be quite high in short channel device. Carriers that are injected into the depletion layer are accelerated by the high field, and some of them may gain enough energy to cause impact ionization. These carriers have higher energy than thermal energy and are called hot carriers. Most of the electrons generated by the avalanche multiplication are normally attracted by the drain and the holes generated by multiplication can flow to the subtrate, giving rise to a large substrate current (Fig 1.3). The situation is further complicated by the fact that the region between the source and drain can act like the base of a bipolar npn transistor, with the source acting as the emitter and the drain as the collector. Now if the substrate current produces a voltage drop in the substrate material of the order 0.7 V, the substrate-source pn junction will conduct significantly. Electrons can be injected from the source to the substrate, just like electrons injected from emitter to base in an npn transistor. These electrons can in turn, gain sufficient energy as they travel toward the drain to cause additional impact ionization and create new electron-hole pairs. This constitutes a positive feedback mechanism, which can sustain itself if the drain voltage exceeds a certain value. This is observed externally as breakdown causing current values higher than normally expected.

### Fig. 1.3. Effect of hot carrier in short channel MOSFET.

- (1) Holes reaching the source

- (2) Electron injection from the source

- (3) Substrate hole current

- (4) Electron injection into the oxide

#### 1.6 Review of recent works on the breakdown of MOSFET

A number of analytical and numerical models on the breakdown of short channel MOSFET have been developed in the last few years. D.P Kennedy and A. Phillips [6] in 1973 first developed a source drain breakdown model and suggested that the positive feedback effect involving bipolar transistor action is the main breakdown mechanism in short channel MOSFET. But in his work the dependence of breakdown on biases and geometries were not investigated. In 1977 T. Toyabe [7] developed a two dimensional avalanche breakdown model of short channel MOSFET and concluded that the breakdown in short channel MOSFET occurs when the voltage across the source-substrate junction is of the order of 0.7 V. Later in 1978 he proposed a numerical model of avalanche breakdown which is a modified version of his previous model. E. Sun [8] in his breakdown model of short channel MOSFET showed that the turning on of the source substrate junction is not a sufficient condition for breakdown. Later Fu-Chieu Hsu, Simon Tam [9] derived a simple analytical breakdown model that combines the effects due to ohmic drop caused by the substrate current and the positive feedback effect of the substrate lateral bipolar transistor. They pointed out that drain source breakdown in most short channel MOSFETs is neither simple junction avalanche breakdown nor source to drain punchthrough but avalanche-induced breakdown and two conditions must be satisfied before the breakdown can occur. One is the emission of minority carrier into the substrate from the source and the other is sufficient avalanche multiplication to cause significant positive feedback. Wolfgang Muller [18] analysed MOS transistor in avalanche multiplication region for different doped transistor at varying channel lengths. In his work ionization integrals, internal body effect and parasitic bipolar turn-on have been investigated in dependence of channel doping profile and substrate doping level. He suggested that a deep channel implant in devices with

high resistivity substrate improves the source barries and lower substrate resistivity to shift the bipolar trigger voltage to higher drain voltage of the order of 1-2 V.

Chenning Hu [10] in 1982 showed that a phenomena of second breakdown similar to that in bipolar transistor can also occur in vertical power MOSFET. A good agreement between measured and calculated values based on his analysis was achieved over a wide range of device parameters. In 1983 Hsu [11] presented a simplified model which is an extended version of his previous work. In this work Hsu included the effects of those carriers injected from the source into the substrate and collected by the drain. He also incorporated substrate conductivity modulation to account for the behaviour of the substrate current and current collected at nearby junction in the breakdown region. Tomasz Skotnicki, Gerard Merckel [20] revealed in 1989 that the physics of multiplication induced breakdown is eventually different from what the previous authors have reported. They proposed that two consecutive phases of breakdown, enhanced body effect and parasitic bipolar action have to be treated differently. They also showed that enhanced body effect can't be replaced by ordinary body effect resulting from the external positive bulk bias. Similarly they proposed an unconventional mode of biasing of the bipolar transistor and took into account the effect of variable geometry of the substrate to incorporate the variation of substrate resistance with drain source voltage. Tomasz resolved the shortcomings of the work done by the previous authors who failed to explain the constant substrate voltage with the increase of substrate current and limit its value to 0.7 V to match the measured I-V characteristics of the MOSFET in the breakdown region which leads to a number of contradictions. The first contradiction is that the substrate voltage remains fixed while substrate current is increasing and substrate resistance is fixed. The second contradiction is the saturation of substrate current as reported by some authors which is in complete disagreement with the measured substrate current. The third contradiction is that the saturation of sub-

strate current implies almost constant drain current which is also contradictory to the rapid increase of drain current with  $V_{DS}$ .

#### **1.7** Summary of the thesis

A number of different models have been developed so far to find the drain characteristics of a short channel MOSFET in the multiplication breakdown region. Different authors have used different approaches to develop their models. But most of the reported works failed to incorporate the exact physical mechanism that drives a short channel MOSFET in the breakdown region. In this thesis, an analytical model comprising of a detailed physics of a short channel MOSFET in its avalanche multiplication region is presented. The main model consists of four small different models namely channel current model  $I_{ch}$ , excess channel current model  $\triangle I_{ch}$ , the substrate current model  $I_{sub}$  and the emitter current model  $I_e$ . Various short channel effects have been taken into account while developing these models.

In the first chapter of this thesis, the literature survey of a MOSFET including its threshold voltage, body (substrate bias) effect and various undesirable effects have been undertaken. The effect of hot carrier and substrate current produced by the mechanism of avalanche multiplication that drives a short channel MOSFET into the breakdown mode have been described briefly in this chapter. Recent works carried out by various authors on the breakdown of short channel MOSFET are also reviewed in this chapter.

In chapter 2, a detailed analysis of the breakdown model along with the physics is presented to find the I-V characteristics of a short channel MOSFET. The total drain current in the avalanche multiplication region consists of four different cur-

rent components i) conventional channel current due to electron flow from source to drain ii) excess channel current due to threshold lowering iii) substrate current due to hole produced by avalanche multiplication iv) emitter current due to bipolar action of the MOSFET. For the channel current model a simple but efficient method is used where the change of threshold voltage with drain source voltage and channel length have been taken into account. An accurate substrate current model is developed where the effect of junction depth, oxide thickness, drain voltage, substrate doping on multiplication factor have been incorporated. In developing the emitter current model the effective channel length is represented by an analytical one and later an empirical expression is derived to find the complete drain and substrate characteristic of the short channel MOSFET.

In chapter 3 of the thesis the drain and substrate characteristics based on the analytical model developed in chapter 2 and a computer programme scheme to study the characteristics are presented.

The final chapter contains the concluding remarks with suggestions for further work on this topic.

### CHAPTER 2

# ANALYTICAL BREAKDOWN MODEL OF SHORT CHANNEL MOSFET

### 2.1 Introduction

The mechanism of bipolar induced breakdown due to impact ionization in short channel MOSFET has been studied by many authors [6-11, 20]. In this thesis an analytical model is presented. This model can be applied for a wide range of MOSFET channel lengths to find different I-V characteristics of the MOSFET.

The physics of the avalanche induced breakdown problem along with different current components has been illustrated in Fig. 2.1 for an n channel MOSFET. Channel electrons that travel through the high field avalanche region cause impact ionization. The electric field in the high-field region sweeps the electron generated by impact ionization into the drain and holes into the bulk. The holes created at the high field avalanche region first causes a reduction in the channel region depletion width and thus lowers the threshold voltage  $\hat{V}_T$  of the MOSFET and then the ohmic drop caused by the hole flowing through the high resistivivity substrate forward biases the source junction to initiate the bipolar action of the MOSFET and

Fig. 2.1 Current components with bipolar induced breakdown in short channel MOSFET.

hence cause it to inject electrons. Part of these injected electrons travel to the drain junction and will further be multiplied by the drain field, causing positive feedback action. So after the bipolar turn-on of the MOSFET the drain current  $I_d$  consists of three components of current i) channel current  $I_{ch}$ , ii) excess channel current  $\Delta I_{ch}$  due to threshold lowering of the MOSFET and iii) the collector current  $I_c$  of the bipolar npn transistor. On the other hand, the hole current  $I_m$  due avalanche multiplication consists of base current  $I_b$  and the substrate current  $I_{sub}$ . From the equivalent circuit (Fig. 2.2) of a MOSFET after the bipolar turn on, the necessary equations relating different current components can be represented as follows,

$$I_{\rm d} = M(I_{\rm c} + I_{\rm ch} + \Delta I_{\rm ch})$$

(2.1)

$$I_{\rm m} = (M-1)(I_{\rm c} + I_{\rm ch} + \triangle I_{\rm ch})$$

(2.2)

where, M is the multiplication factor. From equations (2.1) (2.2) and (fig 2.5) we get

$$I_{\rm m} = I_{\rm sub} + I_{\rm b} = (1 - \frac{1}{M}) I_{\rm d}$$

(2.3)

But the drain current is related to substrate current as follows (from equation 2.1 and 2.2)

$$I_{d} = M(I_{c} + I_{ch} + \triangle I_{ch})$$

$$= I_{m} + I_{c} + I_{ch} + \triangle I_{ch}$$

Fig. 2.2 Equivalent circuit of a short channel MOSFET after the bipolar turn on.

$$= I_{sub} + I_b + I_c + I_{ch} + \Delta I_{ch}$$

$$= I_{sub} + I_e + I_{ch} + \Delta I_{ch}$$

$$= I_{sub} + I_s \qquad (2.4)$$

where,  $I_0$  is the emitter current and  $I_5$  is the source current and is given by

$$I_{\rm g} = I_{\rm ch} + \Delta I_{\rm ch} + I_{\rm e} \tag{2.5}$$

So from equation (2.4) and (2.5) the expression for substrate current can be given by the relation

$$I_{sub} = (1 - \frac{1}{M}) (I_{sub} + I_{s}) - I_{b}$$

(2.6)

If the multiplication factor M can be found we shall be able to find the substrate current  $I_{sub}$ .

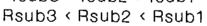

#### 2.2 Enhanced Body Effect

The breakdown in short channel MOSFET is not a simple junction avalanche breakdown rather it is a breakdown induced by avalanche multiplication. Two consecutive phases of breakdown occur in such a small channel MOSFET. First, the rise in drain current is caused by the enhanced body effect (EBE) and then the sharp rise in drain current is initiated by the parasitic bipolar action of the MOSFET. The physical mechanism of the enhanced body effect is that the holes, multiplied in the drain junction, bias the substrate spreading resistance when flowing towards the substrate terminal. This bias corresponds to a reduction in the channel region depletion width from  $w_o$  which corresponds  $(I_{sub} = 0)$  to w and thus releases a certain amount of bulk charge  $Q_B$  of ionized impurities, which was initially tied by the gate field. This reduction in bulk charge of the amount  $\Delta Q_{BS}$  implies a threshold lowering of the MOSFET and enhancement of inversion layer charge by the amount  $\Delta Q_{BS}$  so as to preserve the overall charge neutrality,

$$Q_B + Q_I = Q_G$$

=  $C_o (V_{GB} - \psi_s)$

= const.

(2.7)

This enhanced body effect is quite different from the body effect resulting from the applied external positive biasing of the bulk (body) which also causes a reduction in threshold voltage. But the difference between these two body effects results from the fact that the ordinary body effect does not involve any electric field in the bulk whereas, the enhanced body effect EBE requires a nonvanishing electric field in the bulk, necessary to drive the substrate current. In case of EBE, the variation in potential in the bulk no longer disappears along the depth from depletion edge boundry to the substrate terminal and the substrate current in the bulk flows due to drift of the holes rather than diffusion. The holes after multiplication spread towards the bulk and follow the doping distribution (p = N) which makes the gradient of concentration along the depth of the MOSFET zero and leads to zero diffusion current in the bulk. The nonzero electric field required to ensure the drift of holes is given by

$$E = \frac{I_{sub}}{q\mu_p NlZ}$$

(2.8)

In the equation l accounts for the lateral spreading of the substrate current and

$$l = L - (l_{\rm s} + l_{\rm d})$$

where, L is the physical channel length of the MOSFET and

$$l_{\rm g} \approx \sqrt{\frac{2\epsilon_s}{qN_A}} (V_{\rm bi} - \psi_s)$$

$$l_{\rm d} \approx \sqrt{\frac{2\epsilon_s}{qN_A}}(V_{\rm bi} - \psi_s + V_{DS})$$

# 2.3 Channel current model

In this section first the channel current model for a long channel MOSFET is developed and by some modifications to this model a channel current model for a short channel MOSFET is derived. With strong inversion guaranteed at the source end of the channel the drain end will also be strongly inverted. With both channel ends strongly inverted, the application of bias voltage  $V_{SB}$  at the source end and  $V_{DB}$  at the drain end will shift the quasi fermi level at the corresponding end by  $V_{SB}$  and  $V_{DB}$  respectively. The corresponding surface potentials at the ends can be represented as

$$\psi_{SO} = \phi_{si} + V_{SB}$$

(2.10)

(2.9)

25.

$$\psi_{SL} = \phi_{si} + V_{DB}$$

(2.11)

where  $\psi_{SL}$  and  $\psi_{SO}$  are the surface potential at the drain and source end respectively. In strong inversion the concentration of carriers in the channel region is high and there is a significant variation in surface potential from  $\psi_{SO}$  at the source end to  $\psi_{SL}$  at the drain end. Hence, the channel current is predominantly due to drift mechanism of the carrier rather than diffusion as the gradient of concentration along the channel is small. The drift component of the channel current along the channel due to variation in surface potential  $\psi_s(y)$  determines the channel current  $I_{ch}$  in strong inversion.

$$I_{\rm ch} = \mu Z(-Q_I) \frac{d}{dy} \psi_s(y) \tag{2.12}$$

where, Z is the width of the channel.

But the variation of surface potential  $\psi_s$  can be represented as

$$I_{\rm ch} = \mu Z(-Q_I) \frac{d}{dy} \psi_s(y) \tag{2.13}$$

where, with channel length L

$$V_{CB}(y) = V_{SB}, \qquad y = 0$$

$$V_{CB}(y) = V_{DB}, \qquad y = L$$

Now,

$$I_{\rm ch} = \mu Z(-Q_I) \frac{d}{dy} V_{CB}$$

(2.14)

The inversion layer charge  $Q_I$  is given by

$$Q_{I} = -C_{o}(V_{GB} - V_{FB} - \psi_{s} + \frac{Q_{B}}{C_{o}})$$

=  $-C_{o}(V_{GB} - V_{FB} - \phi_{si} - V_{CB} - \gamma \sqrt{\phi_{si} + V_{CB}})$  (2.15)

where, the depletion layer charge  $Q_B$  is

$$Q_B = -C_o \gamma \sqrt{\phi_{si} + V_{CB}} \tag{2.16}$$

and

$$\frac{Q_B}{C_O} = -\gamma \sqrt{\phi_{si} + V_{CB}} \tag{2.17}$$

By expanding the equation (2.17) into Taylor series around  $V_{CB} = V_{SB}$  we get

$$\frac{Q_B}{C_o} \approx \gamma \sqrt{\phi_{si} + V_{SB}} + \gamma \frac{(V_{CB} - V_{SB})}{2\sqrt{\phi_{si} + V_{SB}}}$$

(2.18)

$$\approx \gamma \sqrt{\phi_{si} + V_{SB} + \delta_1 (V_{CB} - V_{SB})}$$

(2.19)

$\mathbf{t}_{\mathbf{f}_1}$

where,

$$\delta_{\rm I} = \frac{\gamma}{2\sqrt{\phi_{si} + V_{SB}}}$$

The value of  $\delta_1$  is modified again by  $\delta$  for the best fitting of the curve. The value of  $\delta$  is

$$\delta = \frac{d_2\gamma}{2\sqrt{\phi_{si} + V_{SB}}}$$

where,  $d_2$  varies from 0.5 to 0.8 [12]

Now, the expression for the inversion layer charge  $Q_I$  becomes

$$Q_{I} = -C_{o} \left[ V_{GB} - V_{FB} - \phi_{si} - \gamma \sqrt{\phi_{si} + V_{SB}} - \delta(V_{CB} - V_{SB}) - V_{CB} \right]$$

=  $-C_{o} \left[ (V_{GB} - V_{SB}) - V_{FB} - \phi_{si} - \gamma \sqrt{\phi_{si} + V_{SB}} - (1 + \delta) (V_{CB} - V_{SB}) \right]$

=  $-C_{o} \left[ (V_{GS} - V_{T}) - (1 + \delta) (V_{CB} - V_{SB}) \right]$  (2.20)

In equation (2.20) the threshold voltage taking the effect of body bias  $V_{SB}$  is given by

$$V_T = V_{FB} + \phi_{si} + \gamma \sqrt{\phi_{si} + V_{SB}}$$

The channel current  $I_{ch}$  from equation (2.12) is

$$I_{\rm ch} = \mu Z (-Q_I) \frac{dV_{CB}}{dy}$$

(2.21)

$$\int_{o}^{L} I_{\rm ch} \, dy = \int_{o}^{L} \mu Z(-Q_I) \frac{dV_{CB}}{dy} dy \qquad (2.22)$$

i.e.,

$$I_{ch}L = \int_{V_{RB}}^{V_{DB}} \mu Z(-Q_I) dV_{CB}$$

(2.23)

With  $V_{DB} = V_{DS} + V_{SB}$  and  $V_{GB} = V_{GS} + V_{SB}$  the channel current after integration of equation (2.23) is obtained as

$$I_{\rm ch} = \frac{Z\mu C_s}{L} \left[ (V_{GS} - V_T) V_{DS} - .5 (1 + \delta) V_{DS}^2 \right]$$

(2.24)

By taking the effect of normal component of the electric field on the mobility of electrons in the inversion layer that leads to acceleration of electrons toward the oxide-interface we get the effective mobility  $\mu_{eff}$  [4]

where,

$$\mu_{eff} = \frac{\mu_o}{1 + \theta(V_{GS} - V_T) + \theta_{\beta} V_{SB}}$$

The expression of the channel current  $I_{ch}$  with  $\mu$  replaced by  $\mu_{eff}$  becomes

$$I_{\rm ch} = \frac{Z\mu_{eff}C_o}{L} \left[ (V_{GS} - V_T) V_{DS} - .5 (1 + \delta) V_{DS}^2 \right]$$

(2.25)

The expression of the channel current is valid up to saturation voltage  $V'_{DS}$ , beyond which the channel is pinched off and the current is saturated.

Accordingly,

$$I_{ch} = \frac{Z\mu_{eff}C_o}{L} \left[ (V_{GS} - V_T) V_{DS} - .5 (1 + \delta) V_{DS}^2 \right] \quad for \ V_{DS} \le V'_{DS} \quad (2.26)$$

=  $I'_{ch} \qquad \qquad for \ V_{DS} > V'_{DS} \quad (2.27)$

where,  $I'_{ch}$  is the channel current  $I_{ch}$  at a drain source voltage  $V'_{DS}$  obtained from equation (2.26). This is the channel current model for a long channel MOSFET and by considering various short channel effects the corresponding model for the short channel MOSFET can be obtained from this model.

For a short channel MOSFET which is also narrow, a three dimensional analysis is required for obtaining the accurate channel characteristics. Such an analysis involves the solution of three dimensional Poisson's equation and is very complex. However, for efficient calculation a simple channel current model can be developed by taking into consideration the following short channel effects simultaneously in the long channel model and combining them in a single model.

The various short channel effects are : i) Effect of velocity saturation. ii) Effect of channel length modulation. iii)Effect of channel length L on effective threshold. iv) Effect of drain source voltage  $V_{DS}$  on effective threshold. v) Effect of width Z of the channel on effective threshold.

### 2.3.1 Velocity saturation effect

8.6

75

In the channel current model developed for the long channel MOSFET, it is assumed that the lateral (horizontal) component  $\varepsilon_v$  of the electric field is small enough so that the drift velocity of the carrier  $v_d$  is proportional to  $\varepsilon_v$ . But in case of short channel MOSFET this relation is violated due to high value of electric field  $\varepsilon_v$  and the previously developed channel current model for long channel MOSFET requires some modifications. Actually the velocity of carriers in the inversion layer of short channel MOSFET saturates at a high value of electric field  $\varepsilon_v$  and does not increase with the electric field (Fig. 2.4) due to the generation of phonons by the scattering collision of the carriers with the lattice. So the drift velocity is modified

$|v_d| = \mu |\varepsilon_y| \qquad for |\varepsilon_y| \ll \varepsilon_c$  (2.28)

$v_{dmax}$  for  $|\varepsilon_y| \gg \varepsilon_c$  (2.29)

where,  $\varepsilon_c$  is the critical field and is given by

$$\varepsilon_c = \frac{v_{dmax}}{\mu} \tag{2.30}$$

A single expression of drift velocity  $v_d(y)$  can be obtained from equation (2.28) and (2.29) and is given by

$$v_d = v_{dmax} \frac{\varepsilon_v / \varepsilon_c}{1 + \varepsilon_v / \varepsilon_c}$$

(2.31)

where, the lateral electric field  $\varepsilon_{y}$  is given by

$$\epsilon_{v} = \frac{dV_{CB}}{dy} \tag{2.32}$$

Hence,  $v_d(y)$  is given by

$$\begin{aligned}

\psi_d(y) &= \psi_{dmax} \frac{(1/\varepsilon_c)(dV_{CB}/dy)}{1 + (1/\varepsilon_c)(dV_{CB}/dy)} \\

&= \mu \frac{dV_{CB}/dy}{1 + (dV_{CB}/dy)(1/\varepsilon_c)}

\end{aligned} (2.33)$$

Now, the channel current of long channel MOSFET will be modified due to velocity saturation effect in short channel MOSFET as below,

$$I_{ch} = Z(-Q_I) \mu \frac{dV_{CB}/dy}{1 + (dV_{CB}/dy)(1/\varepsilon_c)}$$

(2.34)

Integrating both sides of the equation and after some simplification we ultimately get the channel current  $I_{ch}$  including velocity saturation.

$$\int_{o}^{L} I_{ch} dy + I_{ch} \int_{V_{RB}}^{V_{DB}} dV_{CB} (1/\varepsilon_{c}) = Z \mu \int_{V_{RB}}^{V_{DB}} (-Q_{I}) dV_{CB}$$

(2.35)

Upon integration the channel current  $I_{ch}$  becomes

$$I_{\rm ch} = \frac{Z}{L} \quad \frac{\mu}{1 + V_{DS}/(L\epsilon_c)} \quad \int_{V_{SB}}^{V_{DB}} (-Q_l) dV_{CB}$$

(2.36)

where,

$$V_{DB} - V_{SB} = V_{DS}$$

Comparing with equation (2.23) the channel current expression in all the nonsaturation region taking the effect of velocity saturation can be modified as follows

$$I_{\rm ch,\ including\ velocity\ saturation} = \frac{I_{\rm ch,\ not\ including\ velocity\ saturation}}{1 + V_{DS}/(L\varepsilon_c)}$$

(2.37)

2.3.2 Effect of L,  $V_{DS}$ , Z on threshold voltage

The threshold voltage of a long channel MOSFET is given by

$$V_T = V_{FB} + \phi_{si} - \frac{Q_B}{C_O}$$

=  $V_{FB} + \phi_{si} + \gamma \sqrt{\phi_{si} + V_{SB}}$  (2.38)

where  $Q_B$  is the depletion region charge and is given by

$$Q_B = -qN_A w \quad \bullet$$

where, w is the depletion width.

The total charge that is contributing to the threshold in equation (2.38) is  $ZLQ_B$ , the charge represented by rectangle with width Z and length L. But in short channel MOSFET, a part of this charge is shared by drain and source such that only the area inside the trapezoid (Fig. 2.5) is controlled by gate and the charge inside it contributes to the actual threshold of the short channel MOSFET. So the actual bulk charge  $Q'_B$  will be less than  $Q_B$  and is given by

$$Q'_{B} = Q_{B} \left(\frac{L+L'}{2}\right) \frac{Z w}{Z L w}$$

$$= Q_{B} \frac{L+L'}{2 L}$$

(2.39)

But

$$\frac{L+L'}{2L} = 1 - (\sqrt{1 + \frac{2w}{d_j}} - 1) \frac{d_j}{L}$$

$$\approx 1 - \frac{d_j}{L} \left[ 1 + (\frac{1}{2}) \cdot \frac{2w}{d_j} + \dots - 1 \right]$$

$$\approx 1 - \frac{w}{L}$$

(2.40)

The validity of the expression for the effective charge  $Q'_B$  can be extended by introducing an empirical constant  $\alpha_1$

$$Q'_B = Q_B(1 - \frac{\alpha_1 w}{L}) \qquad (2.41)$$

$$\frac{Q_B}{Q_B} = (1 - \frac{\alpha_1 w}{L})$$

(2.42)

Now the reduction in threshold voltage  $\Delta V_T$  due to significant charge sharing at drain and source end in short channel MOSFET is given by

$$\Delta V_T = \frac{Q_B}{C_o} - \frac{Q'_B}{C_o}$$

=  $\frac{Q_B}{C_o} (1 - \frac{Q'_B}{Q_B})$

=  $\gamma \sqrt{\phi_n} + V_{SB} \left(\frac{\alpha_1 w}{L}\right)$  (2.43)

Replacing the values of  $\gamma = \frac{\sqrt{2qc_1N_4}}{C_0}$  and  $C_0 = \frac{c_0}{t_0}$  in equation (2.43) we get

$$\Delta V_T = 2 \alpha_1 \frac{\epsilon_s}{\epsilon_{ox}} \frac{t_{ox}}{L} (\phi_{si} + V_{SB})$$

(2.44)

This expression is valid when drain source voltage  $V_{DS} = 0$  so that depletion width  $w_S$  at the source end and the depletion width at the drain end  $w_D$  are equal and we can assume a uniform depletion width along the channel. For a drain source voltage greater than 0 the depletion region width around the drain end will widen and the trapezoid assumption will lead erroneous result. Considering an average depletion width of  $\frac{w_S + w_D}{2}$  the effective charge  $Q'_B$  from equation (2.41) is given by

$$Q'_B = Q_B \left( 1 - \frac{w_S + w_D}{2} \frac{\alpha_1}{L} \right)$$

(2.45)

. <del>د</del> ا

i.e.

where,

$$w_{S} = \sqrt{\frac{2 \epsilon_{s} (\phi_{si} + V_{SB})}{q N_{A}}} = \zeta \sqrt{\phi_{si} + V_{SB}}$$

(2.46)

$$w_D = \sqrt{\frac{2 \epsilon_s (\phi_{si} + V_{DB})}{q N_A}} = \zeta \sqrt{\phi_{si} + V_{DB}}$$

(2.47)

$\zeta = \sqrt{\frac{2\epsilon_s}{q N_A}}$

But, the average depletion width can be approximated as

$$\frac{w_{S} + w_{D}}{2} = \frac{\zeta}{2} \left( \sqrt{\phi_{si} + V_{SB}} + \sqrt{\phi_{si} + V_{DB}} \right)$$

$$= \frac{\zeta}{2} \left[ \sqrt{\phi_{si} + V_{SB}} + \sqrt{\phi_{si} + V_{SB} + V_{DS}} \right]$$

$$= \frac{\zeta}{2} \left[ \sqrt{\phi_{si} + V_{SB}} + \sqrt{\phi_{si} + V_{SB}} \left( 1 + \frac{V_{DS}}{\phi_{si} + V_{SB}} \right)^{1/2} \right]$$

$$\approx \frac{\zeta}{2} \left[ \sqrt{\phi_{si} + V_{SB}} + \sqrt{\phi_{si} + V_{SB}} \left( 1 + \frac{1}{2} \frac{V_{DS}}{\phi_{si} + V_{SB}} \right) \right]$$

$$\approx \zeta \left( \sqrt{\phi_{si} + V_{SB}} + \alpha_{2} \frac{V_{DS}}{\sqrt{\phi_{si} + V_{SB}}} \right) \qquad (2.48)$$

So, after some simplification the general expression for threshold reduction  $\Delta V_T$  due to charge sharing in short channel MOSFET, incorporating the effect of drain source voltage  $V_{DS}$ , can be obtained as follows :

$$\Delta V_T = \frac{\Delta Q_B}{C_o}$$

$$= \frac{Q_B}{C_o} - \frac{Q'_B}{C_o}$$

$$= \frac{Q_B}{C_o} \left(1 - \frac{Q'_B}{Q_B}\right)$$

=  $\gamma \sqrt{\phi_{si} + V_{SB}} \left(\frac{\alpha_1}{L} \frac{w_S + w_D}{2}\right)$

=  $2\alpha_1 \frac{\epsilon_s}{\epsilon_{ox}} \frac{t_{ox}}{L} \left[(\phi_{si} + V_{SB}) + \alpha_2 V_{DS}\right]$  (2.49)

If the width of the channel Z in a short channel MOSFET is narrow then the depletion region (Fig. 2.6) on the sides of the channel is comparable to the total depletion region volume and cannot be neglected and this charge on the sides should be added to  $Q_B$  to find the effective charge  $\hat{Q}_B$ . Now the increase in threshold  $\Delta V_{T1}$  due to narrow channel width is given by

$$\Delta V_{TI} = \left(\frac{\hat{Q}_B}{Q_B} - 1\right) \left(\gamma \sqrt{\phi_{si} + V_{SB}}\right)$$

(2.50)

If we assume the side parts of the depletion region is an area of quarter circle cross section then charge  $Q''_B$  inside the region is given

$$\frac{Q'_B}{Q_B} = \frac{2 (\pi/4) w^2 L}{Z L w}$$

$$= \frac{w \pi}{2 Z}$$

(2.51)

By introducing an empirical constant the total effective charge  $\hat{Q}_B$  can be represented as

$$\hat{Q}_B = Q_B \left( 1 + \alpha_3 \frac{\pi w}{2 Z} \right)$$

(2.52)

- 38

So the change in threshold voltage from (2.50) is given by

$$\Delta V_{T1} = \gamma \sqrt{\phi_{si} + V_{SB}} \left( \frac{\alpha_3 \zeta \pi}{2Z} \sqrt{\phi_{si} + V_{SB}} \right)$$

(2.53)

Replacing the values of  $w = \zeta \sqrt{\phi_{si} + V_{SB}}$ ,  $C_o = \frac{\epsilon_m}{t_{os}}$  and  $\gamma = \frac{(2 - q - \epsilon_o - N_A)^{1/2}}{C_o}$  in equation (2.53) the ultimate increase in thresold voltage is given by

$$\Delta V_{T1} = \alpha_3 \pi \frac{\epsilon_s}{\epsilon_{ox}} \frac{t_{ox}}{Z} (\phi_{si} + V_{SB})$$

(2.54)

Combining the effect of L,  $V_{DS}$  and Z on the long channel threshold voltage  $V_T$ the expression of effective thresold voltage  $\hat{V}_T$  for short channel MOSFET is

$$\hat{V}_T = V_T - \triangle V_T + \triangle V_{T1} \tag{2.55}$$

# 2.3.3 Channel length modulation

In a MOSFET at a certain drain source voltage  $V'_{DS}$  the channel is pinched off . At the pinchoff point zero inversion layer charge is situated at the drain end of the channel. If drain source voltage  $V_{DS}$  is increased beyond  $V'_{DS}$  then the depletion region at the drain substrate region starts to increase. This lateral extension of the depletion region into the channel beyond pinch off reduces the effective channel length. Since the depletion region is bias dependent it changes with drain source voltage and thus modulates the effective channel length. This change in channel

length due to bias voltage is negligible in long channel MOSFET, whereas, in short channel MOSFET it is comparable to the length of the MOSFET itself. So like the long channel MOSFET the current in short channel MOSFET does not saturate after pinchoff, rather it increases after saturation due to the fact that the channel current is inversely proportional to the channel length. So if  $I'_{ch}$  is the channel current at saturation voltage  $V'_{DS}$  then the channel current  $I_{ch}$  after saturation is

$$I_{ch} = I'_{ch} \frac{1}{(1 - \Delta L/L)}$$

$$\approx I'_{ch} \left(1 + \frac{\Delta L}{L}\right)$$

(2.56)

The value of  $\Delta L$  can be found in the following way by solving an one dimensional Poisson's equation with appropriate boundary condition (Fig. 2.7) in the pinchoff region near drain end.

$$\frac{d\varepsilon_{\mathbf{y}}}{dy} = \frac{q}{\epsilon_{s}} N_{A}$$

$$\Rightarrow \varepsilon_{\mathbf{y}} = \varepsilon_{0} + \frac{qN_{A}}{\epsilon_{s}} y$$

$$= E_{SAT} + \frac{qN_{A}}{\epsilon_{s}} y$$

(2.57)

$$\int_0^{\Delta L} d\psi_y = \int_0^{\Delta L} -\left(E_{SAT} + \frac{qN_A}{\epsilon_s}y\right) dy \qquad (2.58)$$

So,

$$V_{DS} - V'_{DS} = -E_{SAT} \bigtriangleup L - \frac{1}{2} (\bigtriangleup L)^2 \frac{q N_A}{\epsilon_*}$$

(2.59)

)

)

42

Solving equation (2.59) for  $\Delta L$ ,  $\Delta L$  can be written as

$$\Delta L = \sqrt{\frac{2\epsilon_s}{qN_A}} \left[ \sqrt{\phi_D + (V_{DS} - V'_{DS})} - \sqrt{\phi_D} \right]$$

(2.60)

On the other hand,

$$\frac{\Delta L}{L} = \sqrt{\frac{2\epsilon_s}{qN_A}} \frac{1}{L} \left[ \sqrt{\phi_D} (1 + \frac{1}{2} \frac{V_{DS} - V'_{DS}}{\phi_D} + \cdots) - \sqrt{\phi_D} \right]$$

$$= \sqrt{\frac{2\epsilon_s}{qN_A}} \frac{1}{L} \frac{V_{DS} - V'_{DS}}{2\sqrt{\phi_D}}$$

$$= \frac{V_{DS} - V'_{DS}}{V_A}$$

(2.61)

where,

$$\phi_D = \frac{\epsilon_s \ E_{SAT}^2}{2 \ q \ N_A}$$

and

$$V_{A} = \frac{2\sqrt{\phi_{D}} L\sqrt{qN_{A}}}{\sqrt{2\epsilon_{a}}} = E_{SAT} L$$

From equations (2.56) and (2.61) the channel current  $I_{ch}$  after saturation is

$$I_{\rm ch} = I'_{\rm ch} \left( 1 + \frac{V_{DS} - V'_{DS}}{V_A} \right)$$

(2.62)

Finally, by combining all the effects of short channel MOSFET that have been described in this section and recalling the channel current model of a long channel MOSFET from equations (2.26) and (2.27), the channel current model for short channel MOSFET can be represented as follws:

For a drain source voltge  $V_{DS} \leq V'_{DS}$  the channel current  $I_{ch}$  is

$$I_{ch} = \frac{\mu_0 C_o \frac{W}{L} \left[ \{ V_{GS} - \hat{V}_T (V_{DS}) \} V_{DS} - .5(1+\delta) V_{DS}^2 \right]}{\left[ 1 + \theta \{ V_{GS} - \hat{V}_T (V_{DS}) \} + \theta_\beta V_{SB} \right] \left[ 1 + V_{DS} / (L\epsilon_c) \right]}$$

(2.63)

$$= \frac{\mu_{eff} C_o \frac{W}{L} \left[ V_{G1} V_{DS} - .5(1+\delta) V_{DS}^2 \right]}{\left[ 1 + \frac{V_{DS}}{V_c} \right]}$$

(2.64)

where,

$$\mu_{eff} = \frac{\mu_0}{\left[1 + \theta \{V_{GS} - \hat{V}_T(V_{DS})\} + \theta_\beta V_{SB}\right]}$$

and  $V_{G1} = V_{GS} - \hat{V}_T(V_{DS})$

and  $V_c = L\epsilon_c$

For a drain source voltage  $V_{DS} > V_{DS}'$  the channel current  $I_{ch}$  is

$$I_{ch} = I'_{ch} \left( 1 + \frac{V_{DS} - V'_{DS}}{V_A} \right)$$

=

$$\frac{\mu_0 C_o \frac{W}{L} \left[ \{ V_{GS} - \hat{V}_T (V'_{DS}) \} V'_{DS} - .5(1 + \delta) V'_{DS} \right]}{\left[ 1 + \theta \{ V_{GS} - \hat{V}_T (V'_{DS}) \} + \theta_\beta V_{SB} \right] \left[ 1 + \frac{V'_{DS}}{V_c} \right]} \left( 1 + \frac{V_{DS} - V'_{DS}}{V_A} \right) (2.65)$$

Now, we have to focus on the saturation voltage  $V'_{DS}$  which still remains to be found. Neglecting the dependence of  $\hat{V}_T$  on  $V_{DS}$  and equating the expression  $\frac{d'_{Ch}}{dV_{DS}}$  of equations (2.64) and (2.65) at  $V_{DS} = V'_{DS}$ , we get a transcendental equation after the following simplification. By solving the equation numerically we can get the saturation voltage  $V'_{DS}$ .

$$\left(1 + \frac{V'_{DS}}{V_c}\right) \left\{ V_{GI} V'_{DS} - \frac{1}{2} (1+\delta) V'^2_{DS} \right\}$$

$$= V_{A} \left[ (1 + \frac{V'_{DS}}{V_{c}}) \{ V_{G1} - V'_{DS}(1 + \delta) \} \right]$$

$$- \frac{1}{V_{c}} \left[ \{ V_{G1} V'_{DS} - \frac{1}{2} (1 + \delta) V'^{2}_{DS} \} \right]$$

$$= V_{A} \left[ V_{G1} - \frac{V'^{2}_{DS}}{2V_{c}} (1 + \delta) - V'_{DS}(1 + \delta) \right] (2.66)$$

# 2.4 Substrate current model

In a short channel MOSFET the substrate current is composed of holes generated by impact ionization in the drain region due to high lateral electric field. This current is detectable when the drain source voltage  $V_{DS}$  is one or two volts above  $V'_{DS}$ . The substrate current is a function of multiplication factor M as shown in equation (2.6). But the general expression of multiplication factor M is given by [25]

$$1 - \frac{1}{M} = \int_{x_n}^{x_p} \alpha_n \exp\left[-\int_x^{x_p} (\alpha_n - \alpha_p) dx'\right] dx$$

$$= \int_0^{\Delta L} \alpha_{eff} dx \qquad (2.67)$$

But

$$\alpha_{eff} = A_i \ e^{-\frac{B_i}{B}} \tag{2.68}$$

where, E is the lateral (y direction) electric field (fig 2.2)  $\alpha_n$ ,  $\alpha_p$ , are the ionization rates for electron and hole respectively and  $A_i$  and  $B_i$  are the ionization coefficients.

$$\int_{0}^{\Delta L} \alpha_{eff} dy = \int_{0}^{\Delta L} A_{i} e^{-\frac{B_{i}}{B}} \frac{dy}{dE} dE \qquad (2.69)$$

$$\approx \left| \frac{dy}{dE} \right|_{\mathcal{B}_{SD}} A_{i} \int_{\mathcal{B}_{SAT}}^{\mathcal{B}_{SD}} e^{-\frac{B_{i}}{B}} dE \qquad (2.70)$$

$$\approx A_{i} \left| \frac{dy}{dE} \right|_{\mathcal{B}_{SD}} \left[ E^{2} + e^{-\frac{B_{i}}{B}} \left( 1 - \frac{2}{B_{i}} E + 6\frac{E^{2}}{B_{i}^{2}} \right) \right]_{\mathcal{B}_{SAT}}^{\mathcal{B}_{SD}}$$

$$\approx \frac{A_{i}}{B_{i}} E_{SD}^{2} \left| \frac{dy}{dE} \right|_{\mathcal{B}_{SD}} \left( 1 - 2\frac{E_{SD}}{B_{i}} + 6\frac{E^{2}_{SD}}{B_{i}^{2}} \right) e^{-\frac{B_{i}}{B_{SD}}}$$

$$- \frac{A_{i}}{B_{i}} E_{SAT}^{2} \left| \frac{dy}{dE} \right|_{\mathcal{B}_{SD}} (1 - 2\frac{E_{SAT}}{B_{i}} + 6\frac{E^{2}_{SAT}}{B_{i}^{2}}) e^{-\frac{B_{i}}{B_{AAT}}}$$

$$\approx (C_{1} - C_{2}) \qquad (2.71)$$

Since, the lateral electric field E in the channel increases sharply toward the drain and the substrate current is very strongly dependent on the field, equation (2.69) reduces approximately to (2.70).

From equations (2.67) and (2.71) we get

$$1 - \frac{1}{M} = C_1 - C_2 \tag{2.72}$$

where,

$$C_{1} = \frac{A_{i}}{B_{i}} \left. E_{SD}^{2} \left| \frac{dy}{dE} \right|_{\mathcal{B}_{SD}} \left( 1 - 2 \frac{E_{SD}}{B_{i}} + 6 \frac{E_{SD}^{2}}{B_{i}^{2}} e^{-\frac{B_{i}}{B_{SD}}} \right)$$

(2.73)

and

$$C_{2} = \frac{A_{i}}{B_{i}} E_{SAT}^{2} \left| \frac{dy}{dE} \right|_{\mathcal{B}_{BD}} \left( 1 - 2 \frac{E_{SAT}}{B_{i}} + 6 \frac{E_{SAT^{2}}}{B_{i}^{2}} e^{-\frac{B_{i}}{E_{SAT}}} \right)$$

(2.74)

The substrate current can be represented From equation (2.6)

$I_{sub} = (C_1 - C_2) (I_{sub} + I_s) - I_b$  (2.75)

The lateral electric field E can be related to drain source voltage [21] as,

$$E = \sqrt{A^2 (V - V'_{DS})^2 + E^2_{SAT}}$$

(2.76)

where,

$$A = \sqrt{\frac{\epsilon_{ox}/\epsilon_{si}}{t_{ox} \left\{ (d_j + .01(V - V'_{DS})(d_1 - d_j) \right\}}}$$

and

$$d_{\rm I} = \sqrt{\left(\frac{2\;\epsilon_{\rm s}}{q\;N_{\rm stab}}\right)\;(V_{DS}'+2\phi_f)}$$

$$\frac{dE}{dy} = \frac{dE}{dV} \frac{dV}{dy} = E \frac{dE}{dV}$$

(2.77)

From equations (2.72), (2.73), (2.74) and (2.76) we find that the multiplication factor M is a strong function of lateral electric field near the drain junction and thus is a function of drain source voltage  $V_{DS}$ , oxide thickness  $t_{ox}$ , junction depth  $d_j$  and substrate doping  $N_{sub}$ . The substrate current can be found from equation (2.75) by knowing the parameters  $C_1$  and  $C_2$ . The essential variables required to evaluate these parameters are the electric field  $E_{SD}$  and the gradient of electric field  $\left|\frac{dE}{dy}\right|_{E_{SD}}$  at the drain end of the channel which can be found in the following way.

$$\frac{dE}{dV} = \frac{d}{dV} \{ A^2 (V - V'_{DS})^2 + E^2_{SAT} \}^{1/2} \\ = \frac{(V - V'_{DS})}{E} A^2 \left[ 1 + (V - V'_{DS}) \frac{1}{A} \frac{dA}{dV} \right] \\ E \frac{dE}{dV} = (V - V'_{DS}) A^2 \left[ 1 + \frac{1}{A} \frac{dA}{dV} (V - V'_{DS}) \right]$$

(2.78)

Putting  $x_1 = \frac{\epsilon_{ax}}{\epsilon_e}$  and  $y_1 = t_{ox} \{ d_j + .01(V_{DS} - V'_{DS})(d_1 - d_j) \}$

$$\frac{dA}{dV} = -\frac{x_1^{1/2}}{y} \frac{d}{dV} (y_1^{1/2})$$

$$= -\frac{(x_1^{1/2}/y_1^{1/2})}{2y_1} \frac{d}{dV} [t_{ox} \{d_j + .01(V - V'_{DS})(d_1 - d_j)\}]$$

$$= -\frac{A}{2y_1} t_{ox} \{.01 (d_1 - d_j)\}$$

$$\Rightarrow \frac{1}{A} \frac{dA}{dV} = \frac{1}{2y_1} t_{ox} \{.01(d_1 - d_j)\}$$

$$= -bA^2$$

(2.79)

where,

$$b = \frac{1}{2} \ 0.01 \ (d_1 - d_j) \ \epsilon_s \ \frac{t_{ax}}{\epsilon_{ox}}$$

From equation (2.76), (2.77) and (2.79) we get

$$\frac{dE}{dy} = A^2 (V - V'_{DS}) \left[ 1 - bA^2 (V - V'_{DS}) \right]$$

(2.80)

The lateral electric field  $E_{SD}$  and the gradient  $\left|\frac{dB}{dy}\right|_{E_{SD}}$  at the drain end can be found by replacing V in equation (2.76) and (2.80) by  $V_{DS}$ .

# 2.5 Excess channel current model .

Due to the enhanced body effect EBE (Fig. 2.8) the enhancement of the inversion is achieved through a excess channel current  $\Delta I_{ch}$  injection in addition to the conventional channel current  $I_{ch}$ . This excess channel current corresponds to an equivalent threshold lowering of  $V_{th}$  which is equal to:

$$-\Delta V_{th} = \frac{-\Delta Q_{BS}}{C_o} = \frac{q}{C_o} \int_w^{w_o} N^*(x) dx \qquad (2.81)$$

and consequently the excess channel current $\Delta I_{ch}$  is given by

$$\Delta I_{\mathbf{ch}} \equiv I_{\mathbf{ch}} \mid_{\hat{V}_T + \Delta V_{\mathbf{fh}}} - I_{\mathbf{ch}} \mid_{\hat{V}_T}$$

(2.82)

where, the symbol  $N^*(x)$  represents the transformed doping profile which replaces the real doping profile N(x) in short channel case according to VDT technique[16]. The VDT technique allows the two dimensional Poisson's equation, inherent in short channel MOSFET to be reduced to one dimensional form. According to [16]  $N^*(x)$ is given by

For

$$x \leq \lambda$$

$N^*(x) = N_s^*$

$$= N_s - \frac{2\epsilon_s}{qL_{el}^2} \left[ V_{DS} + 2(V_{bi} - 2\phi_f) + 2\sqrt{(V_{bi} - 2\phi_f)(V_{DS} + V_{bi} - 2\phi_f)} \right] 2.84)$$

$$= N_s - V$$

(2.85)

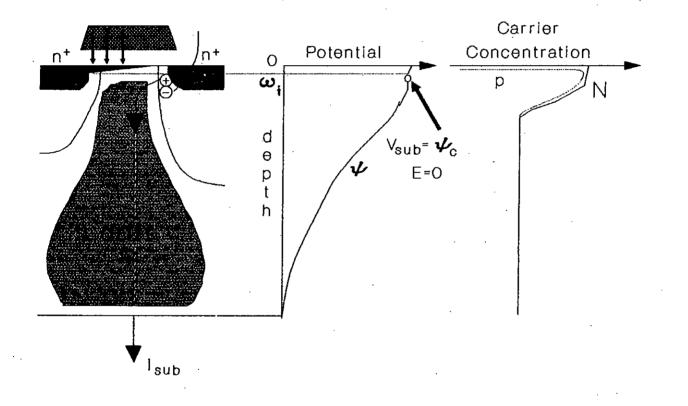

Fig.2.8. Schematic illustration of the EBE phase with corresponding potential and carrier distribution

For  $x > \lambda$

$$N^*(x) = N_B \tag{2.86}$$

Here,  $N_s$ ,  $N_B$  and  $\lambda$  are the parameters of the box approximation of the doping profile and stand, respectively for the surface and bulk box doping concentrations, and the range of the surface enhanced doping,  $V_{\rm bi}$  is the built in potential of the source bulk junction. For most practical case the depletion width  $w_o$  at a substrate current  $(I_{\rm sub} = 0)$  is less or equal than the  $\lambda$  i.e.  $w_o \leq \lambda$

where,

$$w_o = w(I_{sub} = 0) = \sqrt{\frac{2\epsilon_s \psi_c}{q N_s^*}}$$

(2.87)

By using the VDT technique,  $\Delta V_{th}$  can be found by solving a one dimensional Poisson's equation with appropriate boundry condition of potential  $\psi_w$  and field  $E_w$ at the depletion edge boundry which is shown below. The threshold lowering  $\Delta V_{th}$ due to substrate current is related to depletion width w at a particular substrate current and  $w_o$  by the following expression.

$$\Delta V_{\rm th} = -\frac{q}{C_o} N^*_{\bullet}(w_o - w) \qquad for \quad I_{\rm sub} \leq I_{\rm subt} \qquad (2.88)$$

where,  $I_{subt}$  corresponds to the substrate current which causes the depletion layer to dissappear completely  $(w \rightarrow 0)$ .

The surface potential at the silicon surface x = 0 is given by

$$\psi_c \equiv 2\phi_f + V_{SB} = \psi(0) \tag{2.89}$$

$$\frac{d\varepsilon_x}{dx} = -\frac{q N_s^*}{\epsilon_s} \tag{2.90}$$

Upon integration

$$\epsilon_x = \epsilon_o - \frac{q N_s^*}{\epsilon_s} x \tag{2.91}$$

By putting boundary conditions

$$\varepsilon_o = E_w + \frac{qN_s^*}{\epsilon_s} w \tag{2.92}$$

Using equation (2.91) and (2.92) we get

$$\psi_o = \psi_c = \psi_w + wE_w + \frac{1}{2} \frac{qN_s^*}{\epsilon_s} w^2 \qquad (2.93)$$

The boundary conditions are as follows :

l

$$\psi_{w} = R_{\text{sub}} I_{\text{sub}}$$

$$E_{w} = \frac{r}{2} I_{\text{sub}} \qquad [from equation (2.8)]$$

$$(2.94)$$

$$(2.95)$$

where,

$$r = (q\mu_p NZ)^{-1}$$

$R_{sub}$  is the substrate resistance which is a function of the substrate current  $I_{sub}$ when  $I_{sub} > I_{subt}$  and is equal to a constant value  $R_{subt}$  when  $I_{sub} \leq I_{subt}$ .

Rearranginging the equation (2.93)

$$w^{2} + w \left(\frac{2\epsilon_{s}E_{w}}{qN_{s}^{*}}\right) + \frac{2\epsilon_{s}}{qN_{s}^{*}} \left(\psi_{w} - \psi_{c}\right) = 0$$

$$(2.96)$$

Solving the equation we get the depletion layer width w in terms of  $w_o$

$$w = -\frac{1}{2} \frac{2E_{w}\epsilon_{s}}{qN_{s}^{*}} + \frac{1}{2} \sqrt{\left(\frac{2E_{w}\epsilon_{s}}{qN_{s}^{*}}\right)^{2} - 4 \frac{2\epsilon_{s}}{qN_{s}^{*}}(\psi_{w} - \psi_{c})}$$

$$= -\frac{\epsilon_{s}r I_{sub}}{q l N_{s}^{*}} + \sqrt{\left(\frac{\epsilon_{s} r I_{sub}}{qlN_{s}^{*}}\right)^{2} + \left(\frac{2\epsilon_{s}\psi_{c}}{qN_{s}^{*}}\right)^{2}\psi_{c}(1 - \frac{\psi_{w}}{\psi_{c}})}$$

$$= \sqrt{\left(\frac{\epsilon_{s} r I_{sub}}{qlN_{s}^{*}}\right)^{2} + w_{o}^{2}(1 - \frac{R_{sub} I_{sub}}{\psi_{c}}) - \frac{\epsilon_{s} r I_{sub}}{qlN_{s}^{*}}} \qquad (2.97)$$

where,

$$w_o = w(I_{\rm sub} = 0) = \sqrt{\frac{2\epsilon_s \psi_c}{q N_s^*}}$$

(2.98)

From equation (2.88) and (2.97) we find that depletion width w decreases and the  $|\Delta V_{th}|$  value increases with the increase of substrate current. The value of  $|\Delta V_{th}|$  will reach its maximum value when the depletion edge reaches the boundary of inversion layer  $w_i$  or in other words the Si surface since ( $w_i \approx 0$ ). Under this condition the depletion width (w = 0) and the corresponding substrate current is given by

$$I_{\rm subt} = \frac{\psi_c}{R_{\rm subt}} \tag{2.99}$$

where,  $R_{subt}$  is the substrate resistance which corresponds  $(w \rightarrow 0)$ . During the EBE phase the substrate resistance  $R_{sub}$  equals the  $R_{subt}$ , the resistance of the bulk, but in the bipolar phase it varies with d, thickness of equipotential region (EPR). So in the EBE phase the expression of substrate resistance can be represented by the following empirical relation [Appendix A]

$$R_{\rm sub} \cong R_{\rm subt} = R_0 + k_L (L_0/L - 1) \tag{2.100}$$

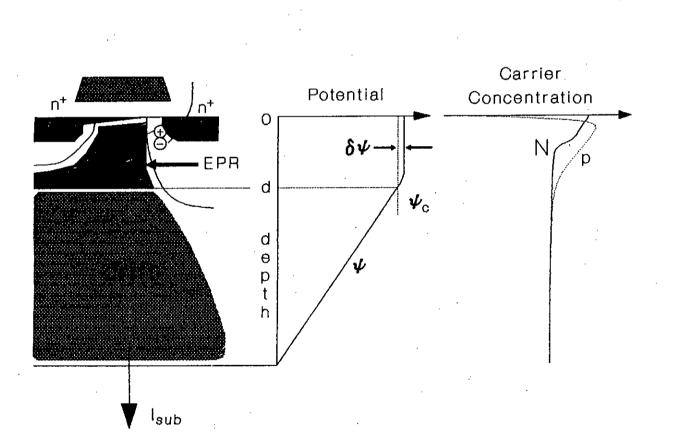

### 2.5.1 Transition phase

The operational phase when the depletion layer vanishes at a substrate current  $I_{sub} = I_{subt}$  and the threshold voltage  $\hat{V}_T$  reaches its minimum value is the transition phase (Fig. 2.10). This corresponds to the maximal threshold voltage reduction  $|\triangle V_{thmax}|$  where

$$\left| \Delta V_{\text{thmax}} \right| = -\frac{\Delta Q_{BSmax}}{C_o}$$

$\triangle Q_{BSmax} = -q \int_{a}^{u_{o}} N^{*}(x) dx$

and

In the transition phase the normal electric field

$$E$$

vanishes at the inversion layer

boundary  $w_i$  and the potential at this boundry become  $\psi_c$  since the electric field

Fig. 2.10. Schematic illustration of the transition phase with corresponding potential and carrier distribution.

lines originating from the gate terminate within the inversion layer and there is no free charge available which can change the boundary condition. In the transition phase the bulk below the inversion region also becomes quasineutral, i.e  $p \cong N$  and is denoted as QNR (Quasi neutral region).

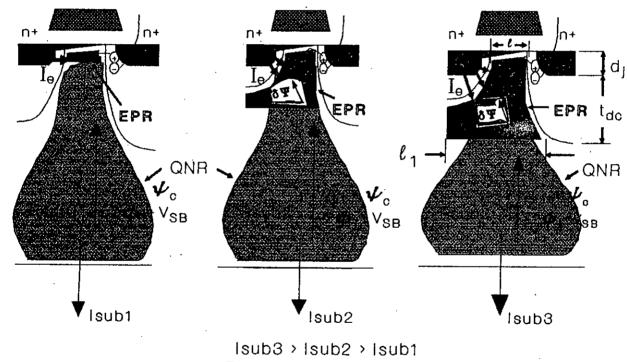

### 2.6 Emitter current model

After the transition phase the MOSFET enters in its bipolar phase (Fig. 2.11). When the substrate current  $I_{sub}$  exceeds  $I_{subt}$ , the current at transition phase, the excess holes due to avalanche multiplication is neutralised by injection of electrons from source junction in order to preserve the charge neutrality condition. The region where the bipolar action takes place is EPR (Equipotential region) because of the constant potential. This region of EPR acts as the base of the npn transistor formed by the source, substrate and drain of the MOSFET where source acts as the emitter and drain as the collector. EPR is a perfectly neutral (p - n - N = 0) and the normal field E at its upper boundary vanishes, the potential  $\psi_c$  is reproduced throughout the EPR. But the potential at the upper boundary of EPR near the source junction is  $\psi = \psi_c + \delta \psi \approx \psi_c$  and  $\delta \psi$  increases with increase of EPR thickness d and the electric field at this boundary is slightly greater than 0. So the potential at the upper boundary near the source junction rises very slowly with increasing carrier concentration.

As a result the substrate current in the EPR is due to diffusion mechanism, whereas, in the bulk below the EPR it is due to drift mechanism. In the bipolar phase, concentration gradient occurs in both horizontal and vertical direction. The concentration gradient  $\frac{\Delta p}{d}$  is responsible for the substrate current and  $\frac{\Delta n}{l}$  is responsible of the emitter current due to electrons. The components of emitter current are

Fig. 2.11 Schematic Illustration of the bipolar phase with corresponding pontential and carrier distribution.

$I_{nSB}$  and  $I_{pBS}$  of which  $I_{nSB}$  is due to excess electrons injected into EPR (base) from source and  $I_{pBS}$  is the excess holes injected from the EPR into the source.

$$I_{\rm sub} \cong q\mu_p \ U_T \frac{\Delta p}{d} \ lZ \tag{2.101}$$

The neutrality condition implies

$$\Delta n = \Delta p = \frac{d}{q\mu_p U_T \, lZ} \, I_{\rm sub} \tag{2.102}$$

Considering a typical  $n^+p$  junction of source and EPR, different current components can be expressed as follows

$$I_{nSB} = q\mu_n U_T \frac{\Delta n}{l} Zd$$

$$= \frac{\mu_n}{\mu_p} \left(\frac{d}{l}\right)^2 I_{sub} \qquad (2.103)$$

and

$$I_{pBS} = q\mu_{p}U_{T}\frac{N_{s}}{N_{SD}}\frac{\Delta n}{L_{p}}Zd$$