# DESIGN OF A HIGH SPEED OFDM TRANSMITTER AND RECEIVER

*By* Foisal Ahmed

Post Graduate Diploma (PGD) In Information and Communication Technology

Institute of Information and Communication Technology BANGLADESH UNIVERSITY OF ENGINEERING AND TECHNOLOGY 2014

-

The project titled "Design of a high speed OFDM Transmitter and Receiver" Submitted by Foisal Ahmed ID No: 0411311006, Session April, 2011 has been accepted as satisfactory in partial fulfillment of the requirement for the degree of Post Graduate Diploma in Information and Communication Technology held on the 26th February, 2014.

### **BOARD OF EXAMINERS**

Supervisor

Dr. Md. Liakot Ali Professor Institute of Information and Communication Technology BUET, Dhaka-1000.

Member

Dr. Mohammad Jahangir Alam Professor Department of Electrical and Electronic Engineering BUET, Dhaka-1000.

Member

Dr. Mohammad Shah Alam Assistant Professor Institute of Information and Communication Technology BUET, Dhaka-1000.

# Declaration

I, do hereby solemnly declare that this research work fully or any part of it has not been submitted elsewhere for the award of any degree or diploma.

.....

Foisal Ahmed

# ACKNOWLEDGEMENT

I would like to thank Almighty Allah for giving me the ability to complete this work successfully.

I pay my gratitude to my project supervisor, Dr. Md. Liakot Ali, Professor and Associate Director (Academics), Institute of Information & Communication Technology (IICT), BUET for his continuous support, careful guidance and direction throughout the project period.

I would like to thank to Prof. Dr. Md. Saiful Islam, Director, Institute of Information & Communication Technology (IICT), BUET for sharing his valuable experience and guidance.

Finally I acknowledge with thanks the help of all members of IICT and my classmates for their cordial cooperation and useful suggestion.

### ABSTRACT

System–on-a-chip (SoC) is now a trend in digital design because it gives a lot of advantages over discrete electronic based product such as higher speed, lower power consumption, smaller size, lower cost etc. Reconfigurable platform such as FPGA, CPLD, and PLD etc. is now being used for designing and implementing SoC due to its low cost and high capacity and tremendous speed. In this project single chip Orthogonal Frequency Division Multiplexing (OFDM) transmitter and receiver has been designed using Verilog HDL. OFDM is a multi carrier modulation technique used in the various digital communication systems like 3G GSM, WiMAX, and LTE etc. The main advantage of this transmission technique is their robustness to channel fading in wireless communication environment. There are many applications of OFDM in communication such as digital audio Broadcasting, asynchronous digital subscriber line (ADSL) and high bit-rate digital subscriber line (HDSL) systems etc. In OFDM, two digital signal processing algorithm Fast Fourier transform (FFT) and Inverse Fast Fourier Transform (IFFT) are mainly involved. The 8points IFFT/FFT decimation-in-frequency (DIF) with radix-2 algorithm have been analyzed and incorporated in the design. The design has been simulated on the FPGA platform under Altera's Quartus II environment. Simulation results show that each of the modules of the proposed OFDM is working as desired. The test output achieved from the simulation result of the OFDM has been verified with that of the MATLAB output.

# TABLE OF CONTENTS

| Declaration    |                                                                                                            | 3  |

|----------------|------------------------------------------------------------------------------------------------------------|----|

| Acknowledgen   | nent                                                                                                       | 4  |

| Abstract       |                                                                                                            | 5  |

| Table of Conte | nt                                                                                                         | 6  |

| List of table  |                                                                                                            | 8  |

| List of figure |                                                                                                            | 9  |

| Chapter 1      | Introduction                                                                                               | 10 |

| 1.1            | Introduction                                                                                               | 10 |

| 1.2            | Overview of Digital Communication System                                                                   | 10 |

| 1.3            | Motivation of the project                                                                                  | 11 |

| 1.4            | Project objectives                                                                                         | 12 |

| 1.5            | Organization of the Project                                                                                | 12 |

| Chapter 2      | Fundamental concepts of OFDM and FPGA                                                                      |    |

| 2.1            | Introduction                                                                                               | 13 |

| 2.1.1          | OFDM overview                                                                                              | 13 |

| 2.1.2          | Data transmission                                                                                          | 13 |

| 2.1.3          | Parameters                                                                                                 | 14 |

| 2.1.4          | Sub-Channelization                                                                                         | 14 |

| 2.1.5          | Basic OFDM implementation                                                                                  | 16 |

| 2.1.6          | Fast Fourier Transform (FFT) and Inverse Fast Fourier Transform (IFFT)                                     | 17 |

| 2.1.7          | Analysis FFT and IFFT algorithm for OFDM                                                                   | 19 |

| 2.1.8          | Pros and Cons of OFDM                                                                                      | 22 |

| 2.1.9          | Applications of OFDM                                                                                       | 23 |

| 2.2            | Hardware Description Language (HDL)                                                                        | 23 |

| 2.2.1          | Types of HDL Coding Style                                                                                  | 24 |

| 2.2.2          | Synthesis Process in Verilog HDL                                                                           | 26 |

| 2.3            | Field Programmable Gate Arrays (FPGA)                                                                      | 27 |

| 2.3.1          | FPGA Implementation of a Design                                                                            | 28 |

| Chapter 3      | Design of 8 point IFFT/ FFT for OFDM Transmitter/Receiver                                                  | 30 |

| 3.1            | Introduction                                                                                               | 30 |

| 3.2            | Proposed technique of an 8-point Inverse Fast Fourier Transform<br>(IFFT) and Fast Fourier Transform (FFT) | 30 |

| 3.2.1          | Implementing structural method of an 8-point IFFT                                                          | 30 |

| 3.2.2          | Expanding Direct method of an 8-point IFFT                                                                 | 32 |

| 3.3            | Implementation of an 8-point IFFT processor                                                                | 37 |

| 3.3.1          | Store module of an 8-point IFFT processor                                                                  | 38 |

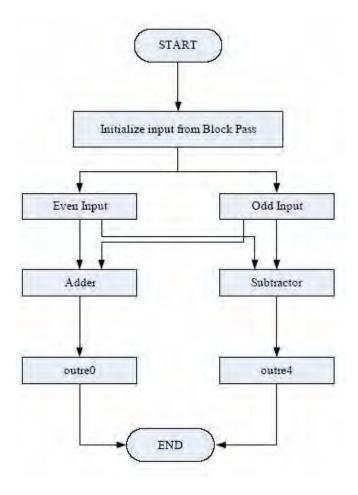

| 3.3.2          | Channel 0 and Channel 4 module of an 8-point IFFT processor                                                | 38 |

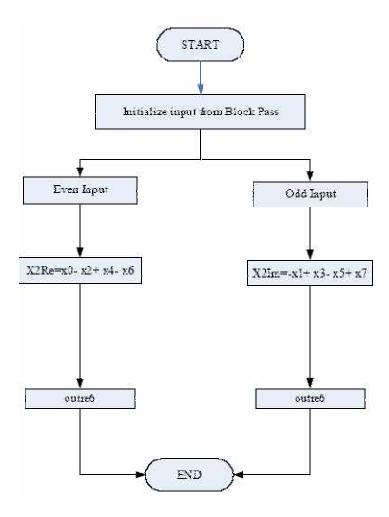

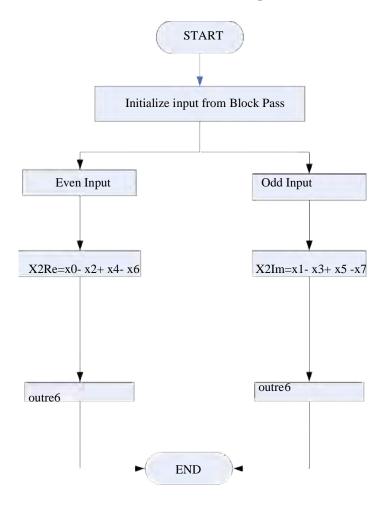

| 3.3.3          | Channel 2 and Channel 6 module of an 8-point IFFT processor                                                | 39 |

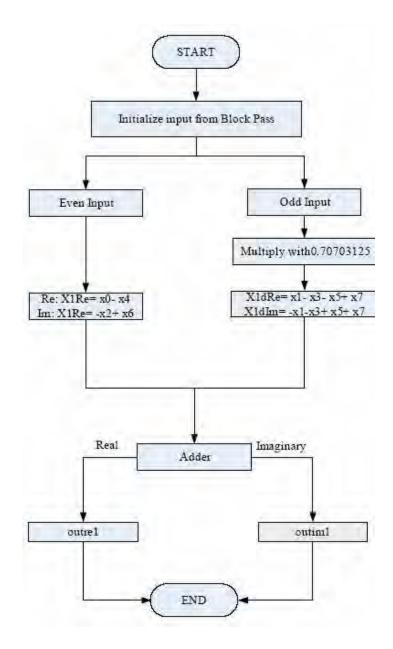

| 3.3.4          | Channel 1, Channel 3 and Channel 5 module of an 8-point IFFT processor                                     | 39 |

| 3.4            | Implementation of an of an 8-point Fast Fourier Transform (FFT) processor                                  | 40 |

| 3.4.1          | Expanding Direct method of an Direct method of an 8-point FFT                                              | 41 |

| Chapter 4  | Result of Verilog HDL Simulation                                                             | 46 |

|------------|----------------------------------------------------------------------------------------------|----|

| 4.1        | Introduction                                                                                 | 46 |

| 4.2        | Proposed 8-point FFT Processor Result                                                        | 46 |

| 4.2.1      | Store Module Simulation Result for FFT Processor                                             | 46 |

| 4.2.2      | Channel 0 and Channel 4 Module Simulation Result for FFT<br>Processor                        | 47 |

| 4.2.3      | Channel 2 and Channel 6 Module Simulation Result for FFT<br>Processor                        | 49 |

| 4.2.4      | Channel 1, Channel 3, Channel 5 and Channel 7 Module Simulation<br>Result for FFT Processor  | 50 |

| 4.2.5      | 8-Point FFT Simulation Result                                                                | 53 |

| 4.3        | Proposed 8-point IFFT Processor Result                                                       | 54 |

| 4.3.1      | Channel Module Simulation Result for IFFT Processor                                          | 54 |

| 4.3.2      | Channel 0 and Channel 4 Module Simulation Result for IFFT<br>Processor                       | 54 |

| 4.3.3      | Channel 2 and Channel 6 Module Simulation Result for IFFT<br>Processor                       | 56 |

| 4.3.4      | Channel 1, Channel 3, Channel 5 and Channel 7 Module Simulation<br>Result for IFFT Processor | 57 |

| 4.3.5      | 8-Point IFFT Simulation Result                                                               | 60 |

| 4.4        | Resources Used                                                                               | 61 |

| 4.5        | Verification of Verilog HDL Simulation output                                                | 61 |

| Chapter 5  | Conclusion                                                                                   | 64 |

| 5.1        | Conclusion                                                                                   | 64 |

| 5.2        | Future Work                                                                                  | 64 |

| References |                                                                                              | 65 |

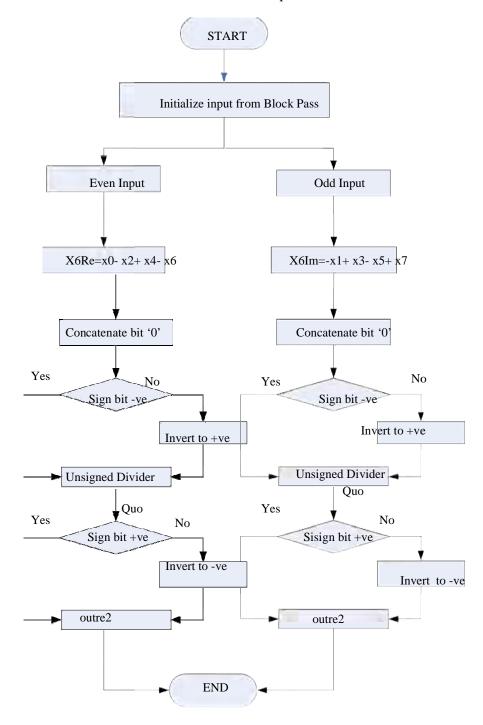

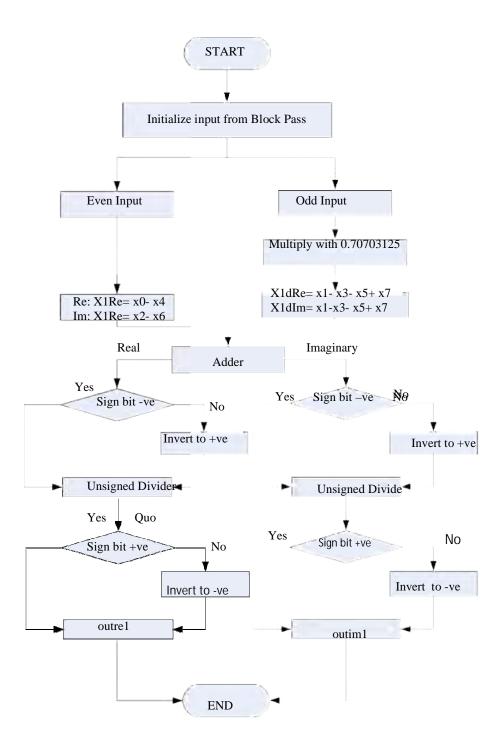

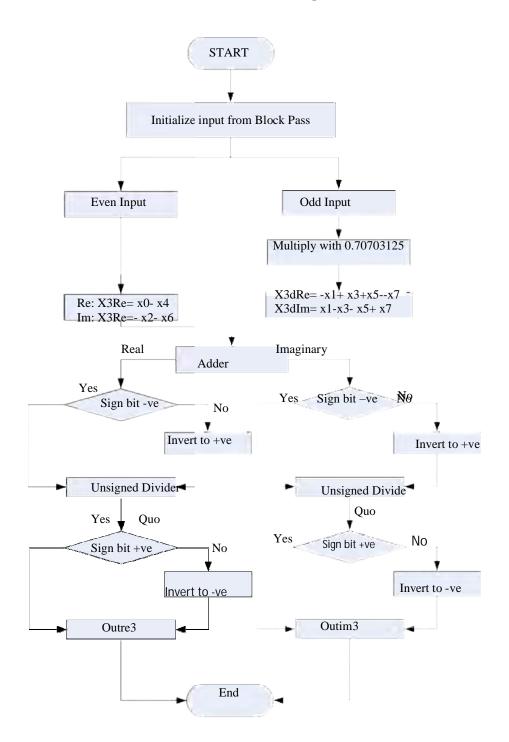

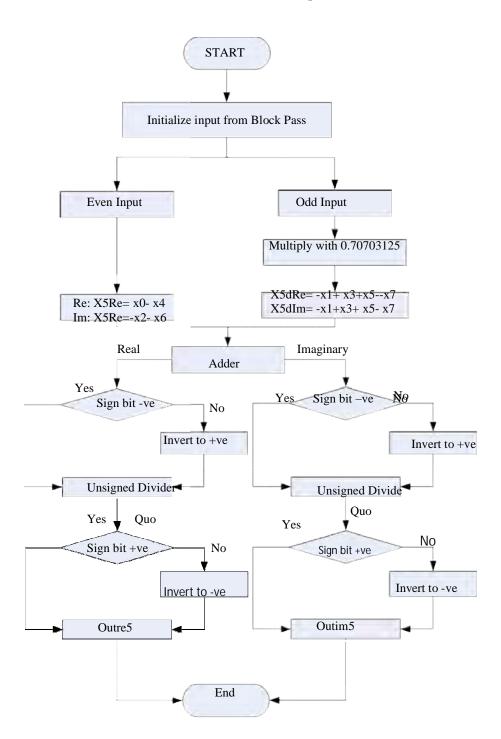

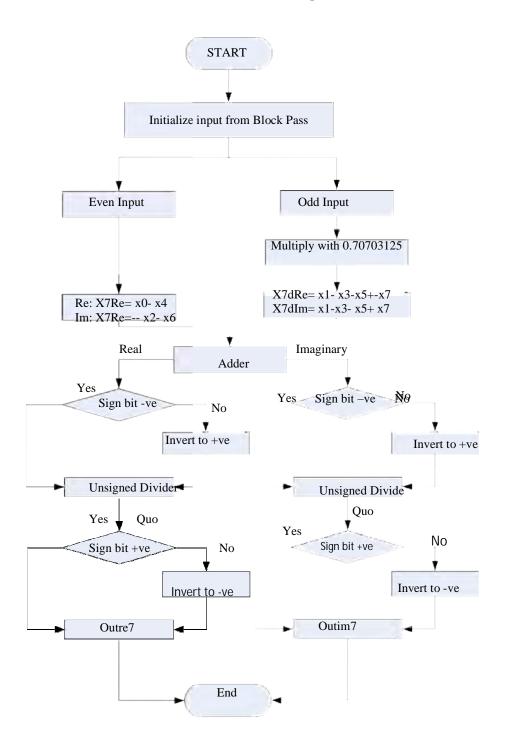

| Appendix A | FFT Verilog HDL IMPLEMENTATION FLOW CHART                                                    | 67 |

| Appendix B | IFFT Verilog HDL IMPLEMENTATION FLOW CHART                                                   | 75 |

| Appendix C | Verilog HDL Synthesis code for FFT and IFFT Processor.                                       | 83 |

|            |                                                                                              |    |

# LIST OF TABLES

| Title                                                           | Page No |

|-----------------------------------------------------------------|---------|

| Table 2.1 Symmetric properties of Twiddle factor                | 21      |

| Table 2.2 Computation of DFT in direct method and DIF algorithm | 25      |

| Table 2.3 Example of structural code showing a 2/1 MUX          | 28      |

| Table 2.4 Example of Behavioral Verilog Code                    | 29      |

| Table 3.1 Final equations for an 8-point IFFT processor         | 41      |

| Table 3.2 Symmetric properties of Twiddle factor                | 47      |

| Table 3.3 Final equations for an 8-point FFT processor          | 50      |

| Table 4.1 MAT Lab FFT simulation output                         | 69      |

| Table 4.2 MAT Lab IFFT simulation output                        | 70      |

# LIST OF FIGURES

| Figure 1.1 Digital Communication Systems                                               | 12 |

|----------------------------------------------------------------------------------------|----|

| Figure 2.1: Time and Frequency diagram of Single and Multi-carrier signals             | 14 |

| Figure2. 2: Downstream transmission of OFDM spectrum                                   | 17 |

| Figure 2. 3: Upstream transmission of OFDM spectrum                                    | 17 |

| Figure 2. 4: Upstream transmission of OFDM spectrum from the CPE                       | 17 |

| Figure2.5: OFDM communication system Block Diagram                                     | 17 |

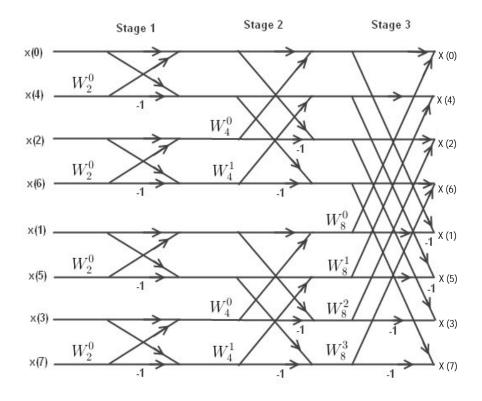

| Figure 2.6: 8-Point DIF FFT flow chart                                                 | 22 |

| Figure 2.7: (a) Block diagram of a A 2/1 Mux (b) Example of RTL Code Showing a 2/1 Mux | 25 |

| Figure 2.8: Logic diagram of a 2/1 Mux                                                 | 26 |

| Figure 2.9: Synthesis Process in Verilog HDL Environment                               | 28 |

| Figure2.10: Digital system design and implementation using FPGA                        | 33 |

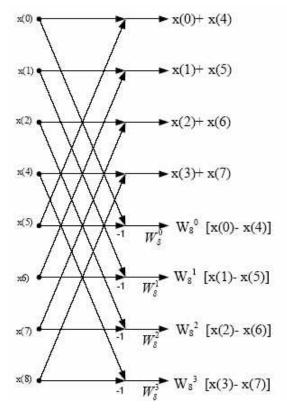

| Figure 3.1 Single Butterfly Flow Chart in IFFT                                         | 35 |

| Figure 3.2 Structural Implementation of IFFT                                           | 36 |

| Figure 3.3 : Stage 1 Computation Flow Chart of an 8-Point IFFT Computation             | 37 |

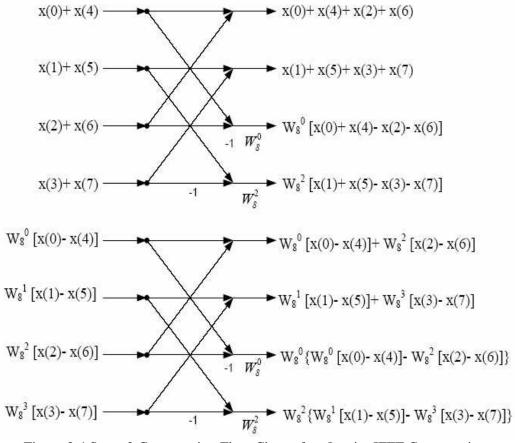

| Figure 3.4 Stage 2 Computation Flow Chart of an 8-point IFFT Computation               | 38 |

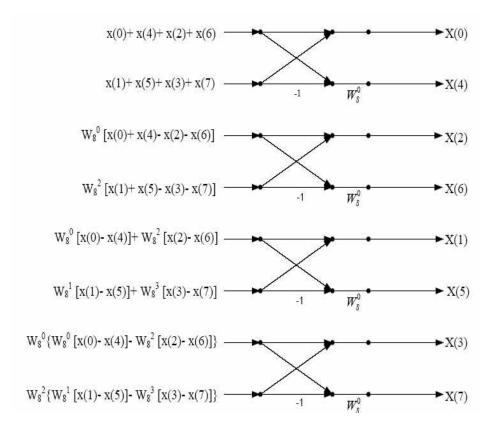

| Figure 3.5: Stage 3 Computation Flow Chart of an 8-Point IFFT Computation              | 40 |

| Figure 4.15 Channel 6 Module Simulation Output for IFFT Processor                      | 44 |

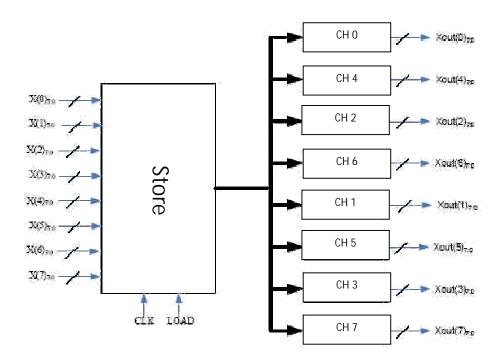

| Figure 3.6 Block diagram of an 8 point IFFT processor                                  | 45 |

| Figure 3.7 8-point FFT flow chart                                                      | 46 |

| Figure 3.8 Stage 1 Computation Flow Chart of an 8-point FFT Computation                | 47 |

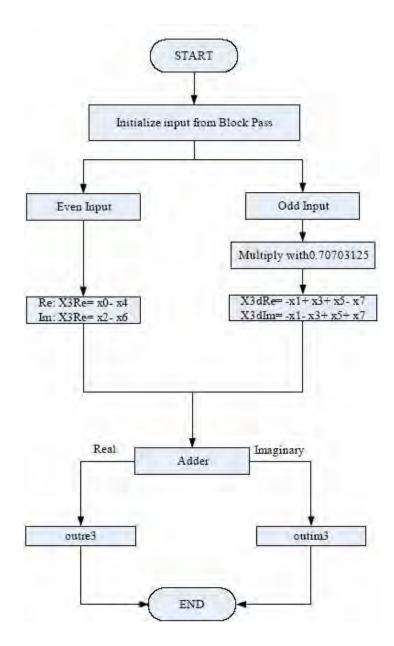

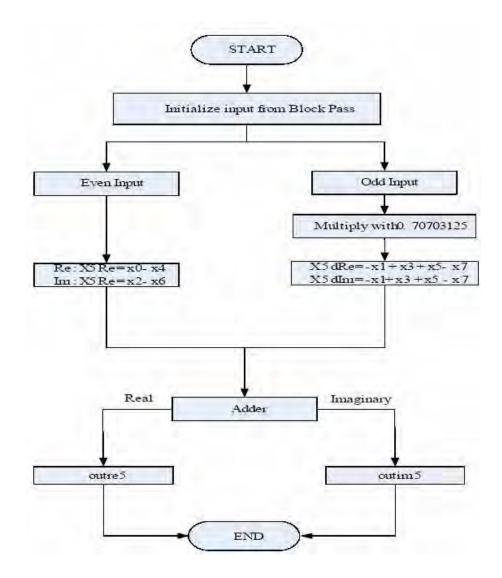

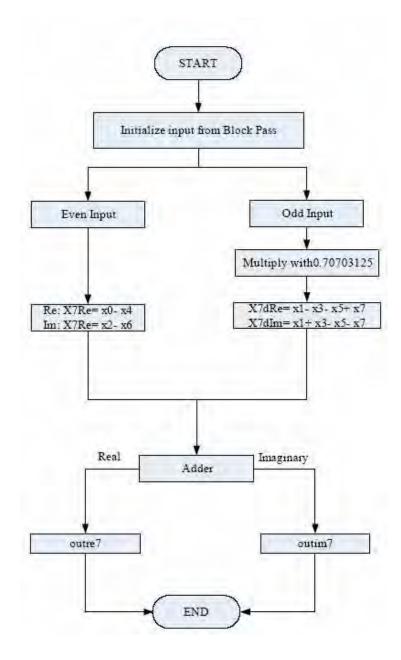

| Figure 3.9 Stage 2 Computation Flow Chart of an 8-point FFT Computation                | 51 |

| Figure 3.10 Stage 3 computation flow chart of an 8-point IFFT Computation              | 52 |

| Figure 4.1 Store Module Simulation Output for FFT Processor                            | 52 |

| Figure 4.2: Channel 0 Module Simulation Output for FFT Processor                       | 53 |

| Figure 4.3: Channel 4 Module Simulation Output for FFT Processor                       | 54 |

| Figure 4.4: Channel 2 Module Simulation Output for FFT Processor                       | 55 |

| Figure 4.5: Channel 6 Module Simulation Output for FFT Processor                       | 55 |

| Figure 4.6: Channel 1 Module Simulation Output for FFT Processor                       | 56 |

| Figure 4.7: Channel 3 Module Simulation Output for FFT Processor                       | 56 |

| Figure 4.8: Channel 5 Module Simulation Output for FFT Processor                       | 56 |

| Figure 4.9: Channel 7 Module Simulation Output for FFT Processor                       | 58 |

| Figure 4.10: FFT Processor output                                                      | 59 |

| Figure 4.11 Store Module Simulation Output for IFFT Processor                          | 59 |

| Figure 4.12 Channel 0 Module Simulation Output for IFFT Processor                      | 60 |

| Figure 4.13 Channel 4 Module Simulation Output for IFFT Processor                      | 60 |

| Figure 4.14 Channel 2 Module Simulation Output for IFFT Processor                      | 61 |

|                                                                                        | 62 |

| Figure 4.16 Channel 1 Module Simulation Output for IFFT Processor                      |    |

| Figure 4.17 Channel 3 Module Simulation Output for IFFT Processor                      | 63 |

| Figure 4.18 Channel 5 Module Simulation Output for IFFT Processor                      | 64 |

| Figure 4.19 Channel 7 Module Simulation Output for IFFT Processor                      | 65 |

| Figure 4.20: IFFT processor output                                                     | 65 |

# Chapter 1 Introduction

# **1.1 Introduction**

In this modern world wireless technology is becoming the main important things not only for communication but also in the field of industry day by day. In early 1990, a mobile phone was still expensive for a single man but today we see it at every hand even most teenagers have. They use it not only for calls but also for various multimedia and educational purposes. It has become possible only for the technological development in the field of digital communication and applied electronics. Now a day's most of the communication systems are digital like mobile communication, TV & Radio Communication, Wired and Wireless Internet, satellite communication and so on. Many of these communication systems use one of the most sophisticated techniques known as *orthogonal frequency division multiplexing* (OFDM) for its strong immunity against noise and other advantages.

# 1.2 Overview of Digital Communication System

Communication means to exchange information (voice, audio, video, text, picture etc.) from one place to another place. Communication system is regarding some things which involve these processes of information. The main parts of the communication system are transmitter, channel and receiver.

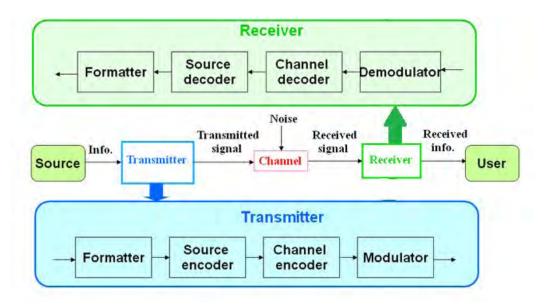

Figure 1.1 Digital Communication Systems

Figure 1.1 shows the block diagram of a basic communication system. The source of information is the messages that are to be transmitted to the other end in the receiver. A transmitter consists of formatter, source encoder, channel encoder and modulator. Firstly formatter transforms the signal from one type to another type suitable for the transmitter operation like transducer. Source

encoder is employed for an efficient representation of the information such that resources can be conserved. The main purpose of the channel encoder is for error correction and detection. The aim is to increase the redundancy in the data to improve the reliability of transmission. A modulation process converts the base band signal into band pass signal before transmission. When the signal is transferring through media (wired or wireless) it faces various noises which attenuate the signal amplitude and distort signal phase. Also, the signals transmitting through a channel also impaired by noise, which is assumed to be Gaussian distributed component.

In the receiver section, the opposite steps in the transmitter are occurred. The process in the receiving section is to be in such a way that same information could be recovered which is similar to the transmitted information.

### **1.3 Motivation of the project**

Orthogonal Frequency Division Multiplexing (OFDM) is a multi carrier modulation technique used in the various digital communication systems like 3G GSM, WiMAX, and LTE etc. OFDM is based on a mathematical process called Fast Fourier Transform (FFT) and Inverse Fast Fourier Transform (IFFT), which enables number of channels to overlap without losing their individual characteristics (orthogonality) [1]. This is a more efficient use of the spectrum and enables the channels to be processed at the receiver more efficiently. When the data is transmitted at high data/bit rates over mobile radio channels then the channels may cause severe fading of transmitted signal when passed through channel and inter symbol interference (ISI). The focus of the fourth generation (4G) mobile system is on supporting higher data rates. Orthogonal Frequency Division Multiplexing (OFDM) is one of the promising techniques for 4G to mitigate ISI and fading in multi-path environment [2]. However, the main constraints nowadays for FFT processors used in wireless communication systems for OFDM are execution time and lower power consumption [3-4]. In conventional computer systems, the instructions are stored in the program memory and it is executed in sequential fashion. So inherently the whole process of operation becomes slow. FPGA technology is now an emerging technology which offers huge number of parallel processing in a single clock. The cost of the platform is also low. Due to availability of huge gate counts in a single chip, FPGA is now being used in various signal processing applications. It facilitates the implementation of the whole process in s single chip which in turn offers improved performance, lower power consumption, shorter time to market and higher reliability than the conventional computer platforms. Due to these attractive features, the proposed OFDM system has been implemented using the FPGA technology.

### **1.4 Project objectives**

The project has the following objectives:

- i. To design an OFDM base band transmitter and receiver using Verilog HDL

- ii. To simulate the design using Quartus II simulator

- iii. To verify the output with that generated using Mat lab Software

- iv. To implement the design using DE2 Altera FPGA Education board

The outcome of this project will be a prototype OFDM base band transmitter and receiver..

### **1.5 Organization of the Project**

The project is organized into five chapters, namely introduction, Fundamental concepts of OFDM and FPGA, Design of 8 point IFFT/ FFT for OFDM Transmitter/Receiver, Result of Verilog HDL Simulation and Conclusion.

**Chapter 1** discusses the general idea of the project which covers the overview, project objective, project background and scope of the project.

**Chapter 2** focuses the literature review of the OFDM system. The history and principle of the OFDM system, Fast Fourier Transform introduction, FPGA and Verilog programming basic idea is explained in this chapter.

**Chapter 3** derives the Fast Fourier Transform and Inverse Fourier Transform algorithm using direct mathematical method. The equations are optimized for digital implementation.

**Chapter 4** shows the Verilog simulation output. The results are presented in their sub-modules and then all the modules are combined to give the final output. Then, the Verilog output is compared with MATLAB simulation output.

**Chapter 5** consists of conclusion, problems encountered in completing this project and suggestion to further improve this project.

### **Chapter 2**

# **Fundamental Concept of OFDM and FPGA**

### **2.1 Introduction**

OFDM is a multi carrier high speed modulation technique used in the various digital communication systems like 3G GSM, WiMAX, and LTE etc. The ultimate goal of wireless communication technology is to provide universal personal and multimedia communication irrespective of mobility and location with high data rates. Orthogonal Frequency Division Multiplexing (OFDM) is one of the promising technique for 4G to mitigate ISI and fading in multi-path environment.

### 2.1.1 OFDM overview

The Orthogonal Frequency Division Multiplexing (OFDM) is developed to support high data rate and can handle multi carrier signals. Its specialty is that, it can minimize the Inter Symbol Interference (ISI) much more compared to other multiplexing schemes. It is more likely improved Frequency Division Multiplexing (FDM) as FDM uses guard band to minimize interference between different frequencies which wastes a lot of bandwidth but OFDM does not contain intercarrier guard band which can handle the interference more efficiently than FDM. On top of that, OFDM handles multipath effect by converting serial data to several parallel data using Fast Fourier Transform (FFT) and Inverse Fast Fourier Transform (IFFT).

### 2.1.2 Data transmission

Data transmission in OFDM is high enough compared to FDM as OFDM follows multicarrier modulation. For this, OFDM splits high data bits into low data bits and sends each sub-stream in several parallel sub-channels, known as OFDM subcarriers. These subcarriers are orthogonal to each other and the each subcarrier bandwidth is much lesser than the total bandwidth. Inter Symbol Interference is reduced in OFDM technique as the symbol time  $T_s$  of each sub-channel is higher than the channel delay spread  $\varsigma$ .

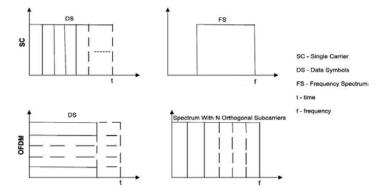

Fig 2.1: Time and Frequency diagram of Single and Multi-carrier signals

In the Fig 2.1, it is clear that OFDM resists the multipath effect by adopting smaller frequency bandwidth and longer period of time which leads to get better spectral efficiency.

### 2.1.3 Parameters

The implementation of OFDM physical layer is different for two types of WiMAX. For fixed WiMAX, FFT size is fixed for OFDM-PHY and it is 256 but for mobile WiMAX, the FFT size for OFDMA-PHY can be 128, 512, 1024 and 2048 bits [16]. This helps to combat ISI and Doppler spread. Other difference between OFDM-PHY and OFDMA-PHY is, OFDM splits a single high bit rate data into several low bit rate of data sub-stream in parallel which are modulated using IFFT whereas OFDMA accepts several users' data and multiplex those onto downlink sub-channel. Uplink multiple accesses are provided through uplink sub-channel. OFDM-PHY and OFDMA-PHY parameters are discussed briefly in the following subsection.

### 2.1.4 Sub-channelization

WiMAX divides the available subcarriers into several groups of subcarriers and allocates to different users based on channel conditions and requirement of users. This process is called subchannelization. Sub-channeling concentrates the transmit power to different smaller groups of subcarrier to increase the system gain and widen up the coverage area with less penetration losses that cause by buildings and other obstacles. Without sub-channelization, the link budget would be asymmetric and bandwidth management would be poor [17]. Fixed WiMAX based OFDM-PHY permits a little amount of sub-channelization only on the uplink. Among 16 standard sub-channels, transmission can take place in 1, 2, 4, 8 or all sets of subchannels in the uplink of the Security Sub-layer (SS). SS controls the transmitted power level up and down depending on allotted sub-channels. When the allotted sub-channels increase for uplink users, the transmitted power level increases and when the power level decreases, it means the allotted subchannels decreased. The transmitted power level is always kept below the maximum level. In fixed WiMAX, to improve link budget and the performance of the battery of the SS, the uplink sub-channelization permits SS to transmit only a fraction of the bandwidth usually below 1/16 allocated by the BS Mobile WiMAX's OFDMA-PHY permits sub-channelization in both uplink and downlink channels. The BS allocates the minimum frequency and sub-channels for different users based on multiple access technique. That is why this kind of OFDM is called OFDMA (Orthogonal Frequency Division Multiple Access). For mobile application, frequency diversity is provided by formation of distributed subcarriers. Mobile WiMAX has several distributed carrier based sub-channelization schemes. The mandatory one is called Partial Usage of Sub-Carrier (PUSC).

Another sub-channelization scheme based on unbroken subcarrier is called Adaptive Modulation and Coding (AMC) in which multiuser diversity got the highest priority. In this, allocation of sub-channels to users is done based on their frequency response. It is a fact that, contiguous sub-channels are best suited for fixed and low mobility application, but it can give certain level of gain in overall system capacity [16].

Fig 2. 2: Downstream transmission of OFDM spectrum

Fig 2. 3: Upstream transmission of OFDM spectrum

Figure 2.3 shows the upstream transmission of OFDM spectrum from a customer premises equipment (CPE) where the carriers are quarter in size compared to fig 2.2 downstream transmission from BS

Fig 2. 4: Upstream transmission of OFDM spectrum from the CPE

Figure 2.4 illustrates the transmitted upstream OFDM spectrum from a CPE where the carriers are as same as BS in size and range but with small capacity. [13]

### 2.1.5 Basic OFDM implementation

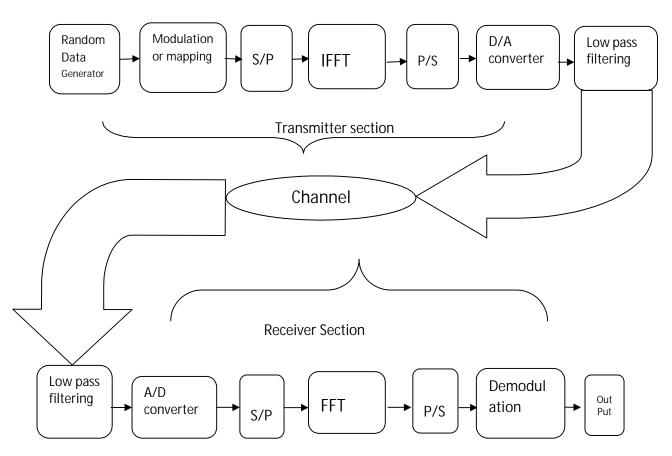

Figure 2.5 shows the block diagram of basic OFDM communication system model. The Figure 2.5 indicates the step by step operation of each functional block. At the transmitter side, the input binary data stream obtained from the source. The retrieved binary data stream is passed through to the other required steps (source of encoder, channel coder) as the signal has to transmit.

Figure-2.5: OFDM communication system Block Diagram

In OFDM system, the carriers are sinusoidal. Two periodic sinusoidal signals are called orthogonal when their integral product is equal to zero over a single period. Each orthogonal subcarrier has an integer number of cycles in a single period of OFDM system. To avoid inter channel interference these zero carriers are used as a guard band in this system.

The first step of the OFDM transmitter is to split up the data stream into K parallel sub-streams, and is modulated on its own subcarrier at frequency  $f_k$  in the complex baseband. Actually, we do not modulate the data stream, rather then we are just mapping the symbols for further operation. Different types of Digital modulation are available to do this as for example Amplitude shift keying (ASK), frequency shift keying (FSK), Phase Shift Keying (PSK), and Quadrature Amplitude modulation (QAM) etc. The data is being modulated depending on their size and on the basis of different modulation scheme like BPSK, QPSK, 16 QAM and 64 QAM. The

modulation has done on the basis of incoming bits by dividing among the groups of *i*. That is why there are  $2^{1}$  points. The total number of bits represented according to constellation mapped of different modulation techniques. The size of *i* for BPSK, QPSK, 16QAM and 64 QAM is 1, 2, 4, and 16 respectively

The next block of the Figure 2.5 in the OFDM transmitter is IFFT part which is the major part of the OFDM transmitter. In OFDM Transmitter, IFFT (Inverse Fast Fourier Transform) used to create OFDM waveform or symbol with the help of modulated data streams. IFFT converts the data streams of frequency domain into time domain in the discrete form. Then again convert the signal parallel into serial.

Before transmit the OFDM signal in the wireless media, the signal must be converted into analog signal and pass it through the low pass filter. Then the OFDM signals transmit by the antenna to the multipath channel.

On the other hand in OFDM receiver end the FFT (Fast Fourier Transform)used to demodulate the data streams as time domain into frequency domain in the discrete from and take just the opposite operation step by step as well.

In wireless transmission the transmitted signals might be distort by the effect of echo signals due to presence of multipath delay for multichannel propagation which is called Inter-symbol Interference (ISI). To avoid Inter-symbol Interference (ISI) the Cyclic Prefix (CP) is inserted in OFDM system before each transmitted symbol. After performing Inverse Fast Fourier Transform (IFFT) the CP will be added with each OFDM symbol. The ISI is totally eliminated by the design when the CP length is greater than multipath delay. The time duration of the OFDM symbol is defined as symbol time, Tb. A copy of symbol period, Tg which is termed of Cyclic Prefix (CP) used to collect multipath where maintaining the orthogonality of the codes.

# **2.1.6** Fast Fourier Transform (FFT) and Inverse Fast Fourier Transform (IFFT)

The OFDM symbol threats the source symbols to perform frequency-domain into time domain. If we chose the N number of subcarriers for the system the basic function of IFFT receives the N number of sinusoidal and N symbols at a time. The output of IFFT is the total N sinusoidal signals and makes a single OFDM symbol.

The mathematical model of OFDM symbol defined by Inverse Discrete Fourier Transform IDFT which would be transmitted as given bellow:

$$x(n) = \frac{1}{N} \sum_{k=0}^{N-1} X(K) e^{j2\pi k/N}$$

x (n) represents the IDFT time domain output at the *n*-th spectral point where n ranges from 0 to N-1. The N represents the number of sample points in the IDFT data frame. The quantity X(k) represents the *k*-th time sample, where k also ranges from 0 to N-1. In general equation, X(k) could be real or complex.

And the corresponding Discrete Fourier Transform (DFT) operates on sample time domain signal which is periodic. The sequence x(n) gives a sequence X(k) defined only on the interval from 0 to N-1. The equation for DFT is:

$$X(k) = \sum_{n=0}^{N-1} x(n) e^{-j2\pi k/N}$$

The DFT equation is:

$$X(k) = \sum_{n=0}^{N-1} x(n) W_N^{nK}$$

The factor  $W_N^{nK}$  is defined as:

$$W_N^{nK} = e^{-j2\pi k/N}$$

It is called twiddle factor. It is mainly a sinusoidal function written in the polar form.

By analyzing the first equation we found that the computation of each point of FFT requires the following computation, (N-1) complex multiplication, (N-1) complex addition (the first term in sum involves  $e^{j0}=1$ ). Thus, to compute N points in FFT require N(N-1) complex multiplication and N(N-1) complex multiplication and N(N-1) complex addition.

And as the number of FFT/IFFT point (N) increases, the number of multiplications and addition required is significant because the multiplication function requires a relatively large amount of processing time even using computer. Thus, many methods for reducing the number of multiplication have been investigated over the last 50 years. The next section discussed in detail one of the method made popular by Cooly and Tukey.[8]

The twiddle factor is the combination of sine and cosine basis functions. By taking the advantages of the symmetric and periodic of the twiddle factors as shown:

$$W_N^{r+N/2} = -W_N^r$$

$$W_N^{r+N} = W_N^r$$

The twiddle factor for N=8 is calculated as shown in Table 2.1

| M | <i>W</i> <sup><i>m</i></sup> <sub>8</sub> |

|---|-------------------------------------------|

| 0 | +1                                        |

| 1 | +0.7071-j0.7071                           |

| 2 | -j                                        |

| 3 | -0.7071+j0.7071                           |

| 4 | -1                                        |

| 5 | -0.7071+j0.7071                           |

| 6 | +j                                        |

| 7 | 0.7071-j0.7071                            |

Table 2.1 symmetric properties of  $W_8^m$

### 2.1.7 Analysis FFT and IFFT algorithm for OFDM

This is a "decimation in time" FFT, because the input value to the FFT is the time wave, x(t). The time wave could be a sound wave, for example. The only reason to use FFT rather than DFT is for speed. For example if we use 1024 sample

For a DFT  $O(N^2)$  operations are required and for FFT only  $O(N Log_2(N))$  operations are required, where N is the number of samples.

For example 1024 samples a straight DFT requires =  $1024^2 = 1048576$  operations.

For the same number of samples an FFT requires only  $1024* Log_2(1024) = 10240$  operations

This means that a 1024 sample FFT is 102.4 times faster than the "straight" DFT. For larger numbers of samples the speed advantage improves. For example, for 4096 samples the FFT is over 340 times faster.

The first step to convert the FFT we should know the **"Danielson-Lanczos Lemma"** (D-L Lemma). This will require long equation writing, but it's a vital component of the FFT.

### Here is the Danielson-Lanczos Lemma:

It is a DFT broken up into two summations of half the size of the original. The first summation is the "even terms", E, and the second is the "odd terms", O. W is the "twiddle factor", and understanding it is another key to understanding the FFT. Consider the DFT equation  $X(k) = \sum_{n=0}^{N-1} x(n) W_N^{nK}$  (Eqn..1)

The DFT equation 1 can be divided into first half and last half in the following manner.

$$X(k) = \sum_{n=0}^{\frac{N}{2}-1} x(n) W_N^{nK} + \sum_{n=\frac{N}{2}}^{N-1} x(n) W_N^{nK} \quad (Eqn..2)$$

$$X(k) = \sum_{n=0}^{\frac{N}{2}-1} x(n) W_N^{nK} + \sum_{n=0}^{N/2-1} x(n+N/2) W_N^{(n+\frac{N}{2})K} \quad (Eqn..3)$$

$$X(k) = \sum_{n=0}^{\frac{N}{2}-1} x(n) W_N^{nK} + W_N^{\frac{Nk}{2}} \sum_{n=0}^{N/2-1} x\left(n + \frac{N}{2}\right) W_N^{nK} \quad (Eqn..4)$$

$$X(k) = \sum_{n=0}^{\frac{N}{2}-1} [x(n) + (-1)^k x \left(n + \frac{N}{2}\right)] W_N^{nK} \qquad (Eqn. 5)$$

Now, consider k as even and odd separately. Let K=2r(even) and k=(2r+1) (odd).

$$X(2r) = \sum_{n=0}^{\frac{N}{2}-1} [x(n) + x(n + N/2)] W_N^{2nr}(Eqn..6)$$

$$X(2r+1) = \sum_{n=0}^{\frac{N}{2}-1} \left[ x(n) + x\left(n + \frac{N}{2}\right) \right] W_N^{(2r+1)n}(Eqn..7)$$

Given

$$W_N^{2nr} = W_{N/2}^{nr}$$

$$W_N^{(2r+1)n} = W_{\underline{N}}^{nr} \quad W_N^n$$

Equation 6 and Equation 7 can be simplified into:  $N_{-1}$

$$X(2r) = \sum_{n=0}^{\frac{1}{2}-1} [x(n) + x(n + N/2)] W_{N/2}^{nr}$$

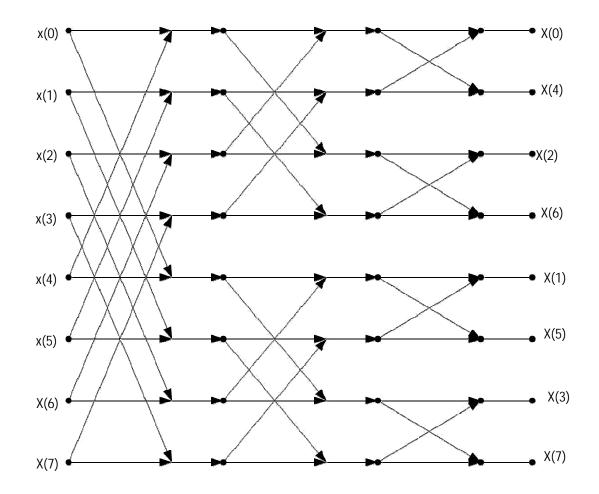

The above two equations are recognizeed as (N/2)-point DFT. The (N/2) –point DFT can be subdivided until only two points are left in each DFT. The result flowgraph also called **"Butterfly Diagram"** for this method for 8-point data shown in figure 2.6. The Butterfly diagram is a diagrammatic representation of an FFT algorithm where the outputs were subdivided to obtain. It is referred to as decimation -in – frequency (DIF) FFT algorithm or radix-2 algorithm.

Figure 2.6: 8-Point DIF FFT flow chart

From Figure 2.6, it is clear that the final output for 8-point FFT is carried out in three stages and each stage requires 4 multiplications and hence a total of 12 complex multiplications are

required. So we can say that for *N* point sequence there is  $\log_2 N$  stages and each stage requires N/2 complex multiplication hence a total of  $N/2 \log_2 N$  complex multiplications are required. Number of additions required is  $N \log_2 N$ . Table 2.2 shows the comparison on the computation basis between the direct method and decimation-in-frequency.

# Table 2.2 Computation of DFT in direct method and decimation-in-frequency algorithm

| Direct Method |                                      | Decimation –in-frequency FFT   |                                                      |                                              |

|---------------|--------------------------------------|--------------------------------|------------------------------------------------------|----------------------------------------------|

| N             | Complex<br>Multiplications<br>N(N-1) | Complex<br>Additions<br>N(N-1) | Complex<br>Multiplications<br>N/2 log <sub>2</sub> N | Complex<br>Additions<br>N log <sub>2</sub> N |

| 4             | 12                                   | 12                             | 4                                                    | 8                                            |

| 8             | 56                                   | 56                             | 12                                                   | 24                                           |

| 16            | 240                                  | 240                            | 32                                                   | 64                                           |

| 32            | 992                                  | 992                            | 80                                                   | 160                                          |

Hence, from the Table 2.2, definitely we can say that DIF FFT algorithm achieves considerable reduction in the computation of DFT

### 2.1.8 Pros and Cons of OFDMA

There are certain pros and cons of OFDMA which made mobile WiMAX to choose OFDMA as its multiplexing schemes. It would be clear if we just have a look description below.

Pros

- 1. Can fights much better against multipath with less computational complexity and more robustness than other techniques.

- 2. OFDMA permits portions of spectrum to be used to transmit data by different users.

- 3. Divides channels into narrow band flat fading sub-channels.

- 4. More resistant to frequency selective flat fading.

- 5. Easy to filter out noise.

- 6. Shorter and constant delay.

- 7. Cyclic prefix helps to eliminate Inter Symbol Interference and Inter Frequency Interference.

- 8. Channel equalization is simpler than single carrier channel.

- 9. Computational efficient as it uses FFT and IFFT.

- 10. It degrades its performance gracefully when the system delay reaches its highest limit.

- 11. Provides benefit of transmitting low power for low data rate users.

- 12. Narrowband interference can be reduced through spectral efficiency.

- 13. Suitable for coherent demodulation.

- 14. Accepts simultaneous low data rates from multiple users .

- 15. Provides different channel quality to different users depending on the requirement and condition of the channel.

#### Cons

- 1. Strong synchronization is required between users and FFT receiver.

- 2. For synchronization purpose, OFDMA technique uses pilot signals.

- 3. Very much sensitive to phase noise and frequency offset.

- 4. Delay in co-channel interference is more complex in OFDMA than CDMA.

- 5. Inefficient power consumption as FFT algorithm and FEC is constantly active.

- 6. If very few sub-carriers are allotted to each user, the diversity gain of OFDM and frequency Selective fading might be vanished. Much complex adaptive sub-carrier channel assignment compared to CDMA Power control system.

### **2.1.9 Applications of OFDM**

In the beginning, the implementation of the OFDM was very complicated task, so their applications were very limited. But at present, OFDM has been adopted as the new European digital audio broadcasting (DAB) standard and for terrestrial digital video broadcasting (DVB) [16]. In fixed-wire applications, OFDM is employed in asynchronous digital subscriber line (ADSL) and high bit-rate digital subscriber line (HDSL) systems. It has been proposed for power line communications systems as well due to its resilience to dispersive channel and narrow band interference.

Beside these applications, OFDM is also used in Digital Audio Broadcasting (DAB), Terrestrial Digital Video Broadcasting (DVB), Magic WAND (Wireless ATM Network Demonstrator), IEEE802.11a/HiperLAN2 and MMAC Wireless LAN etc.

#### 2.2 Hardware Description Language (HDL)

The impact of digital electronics in our daily life is so much now a days, the current period is named as digital age. Digital solutions are being observed in all areas such as telecommunications, consumer electronics, controls, data manipulations etc. To design a digital system, once the conventional approach such as hand-draw, schematic based design technique etc. was the only choice to the designer. However the scenario has been changed. Now millions of transistors are being integrated on a single chip integrated circuit (IC) where the conventional design technique is impossible to be used. It points towards a new approach for designing today's complex digital system and that new approach is designing VLSI chip using Hardware Description Language (HDL).

# 2.2.1 Types of HDL Coding Style

There are three types of Verilog coding style as follows:

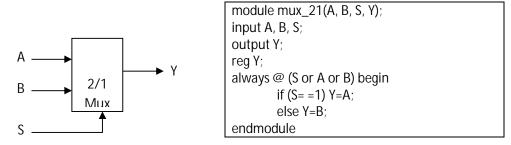

• **RTL Verilog Code:** Digital circuit can be represented in different ways such as gate level representation, transistor level representation etc. RTL, acronym of Register transfer Level (RTL), is also another type of representation style for digital circuit. The reason why it is named as RTL is that any complex digital system can be partitioned into different modules where each module is basically consists of registers and gates. Information is stored in the registers and specific operation is performed using the information, and then it is transferred among the registers. Hence the said representation style is known as RTL. For example, we may define an addition event: X=A+B; It means that the sum of the content of register A and register B is transferred to the storage device X. Figure 2.7 shows the example of RTL code of a 2/1 Mux.

Figure 2.7: (a) Block diagram of aA 2/1 Mux (b) Example of RTL Code Showing a 2/1 Mux

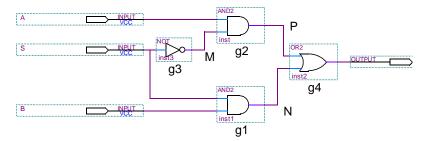

• **Structural Verilog Code:** It describes the components and interconnections present in a design. Electronic Design Automation (EDA) tool compiles and synthesizes the RTL code of a design and produces the netlist of the design in the form of structural code. Table 2.3 shows the example of structural code for a circuit of a 2/1 Mux as shown in Figure 2.8.

| Table 2.3 : | Example of | f Structural | Code Showir | ng a 2/1 Mux |

|-------------|------------|--------------|-------------|--------------|

|             |            |              |             |              |

| module mux (A, B, S, Out); |

|----------------------------|

| input A, B, S;             |

| output Out;                |

| wire M, N, P;              |

| and g1 (N, B, S);          |

| and g2 (P, M, A);          |

| not g3 (M, S);             |

| or g4 (Out, N, P);         |

| endmodule                  |

Figure 2.8: Logic diagram of a 2/1 Mux

**Behavioral Verilog code:** Behavioral code describes the functionality and behavior of the functional block diagram of a design. It is often used for system level modeling and simulation of a design. Table 2.4 shows an example of behavioral Verilog code (using fork and join). Usually many of the commands in behavioral code are not synthesizable (for example, wait command as shown in Table 2.4) and the code length of a design is much smaller than to write for RTL code of the same design because it is only for simulation purpose.

| Table 2.4: Example of Behavioral Verilog Code |

|-----------------------------------------------|

| fork                                          |

| // start of fork block 1                      |

| begin                                         |

| wait (y != 0);                                |

| a = y;                                        |

| end                                           |

| // start of fork block 2                      |

| begin                                         |

| wait (z != 0);                                |

| b = z;                                        |

| end                                           |

| join                                          |

### 2.2 Synthesis Process in Verilog HDL

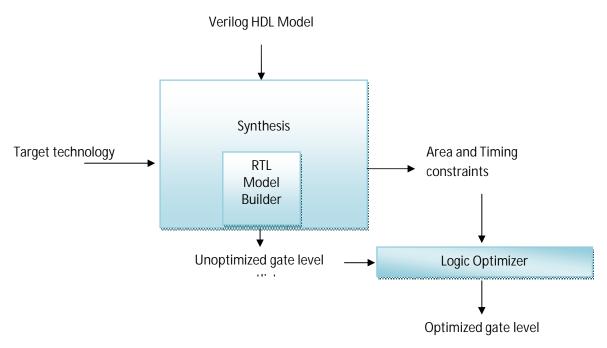

Verilog HDL is a hardware description language that allows designers to model a circuit at different level of abstraction, ranging from the gate level, RTL level, and behavioral level to the algorithmic level. Synthesis process is to construct a gate-level net list from a model of a circuit described in Verilog HDL. The synthesis process is described in diagram below. [7]

Figure 2.9: Synthesis Process in Verilog HDL Environment.

A synthesis program may alternately generate a RTL net list, which is consists of registertransfer level blocks such as flip-flops, arithmetic-logic-units, and multiplexers interconnected by wires. All these are performed by RTL module builder. This builder is to build or acquire from a library predefined components, each of the required RTL blocks in the user-specified target technology.

The above synthesis process produced an unoptimized gate level net list. A logic optimizer can used the produced net list and the constraint specified to produce an optimized gate level net list. This net list can be programmed directly into a FPGA chip.

### 2.3 Field Programmable Gate Arrays (FPGA)

By modern standards, a logic circuit with 20000 gates is common. In order to implement large circuit, it is convenient to use a type of chip that has a large logic capacity. A field-programmable gate arrays (FPGA) is a programmable logic device that support implementation of relatively large logic circuits. FPGA is different from other logic technologies like CPLD and SPLD because FPGA do not contain AND or OR planes. Instead, FPGA consists of logic blocks for implementing required functions. [10]

A FPGA contain 3 main types of resources: logic blocks, I/O blocks for connecting to the pins of the package, and interconnection wires and switches. The logic blocks are arranged in a twodimensional array, and the interconnection wires are organized as horizontal and vertical routing channels between rows and columns of logic blocks. The routing channels contain wires and programmable switches that allow the logic blocks to be interconnected in many ways. FPGA can be used to implement logic circuits of more than a few hundred thousand equivalent gates in size. Equivalent gates is a way to quantify a circuit's size by assume the circuit is to be built using only simple logic gates and then estimate how many of these gates are needed.

Each logic block in a FPGA typically has a small number of inputs and one output. The FPGA products on the market feature different types of logic blocks. The most commonly used logic block is a lookup table (LUT), which contains storage cells that are used to implement a small logic function. Each cell is capable of holding a single logic value, either 0 or 1. The stored value is produced as the output of the storage cell. LUT of various sizes may be created, where the size is defined by the number of inputs.

For a logic circuit to be realized in a FPGA, each logic function in the circuit must be small enough to fit within a single logic block. In practice, a user's circuit is automatically translated into the required form by using CAD tools. When a circuit is implemented in an FPGA, the logic blocks are programmed to realize the necessary functions and the routing channels are programmed to make the required interconnections between logic blocks.

FPGA is configured by using the in-system programming (ISP) method; the FPGA can be programmed while the chip is still attached to its circuit board. The storage cells in the LUTs in an FPGA are volatile, which means that they lose their stored contents whenever the power supply for the chip is turned off. Hence the FPGA has to be programmed every time power is applied. Of this, a small memory chip that holds its data permanently, called a programmable read-only memory (PROM) is included on the circuit board that houses the FPGA. The storage cells in the FPGA are loaded automatically from the PROM when power is applied to the chips.

### 2.3.1 FPGA Implementation of a Design

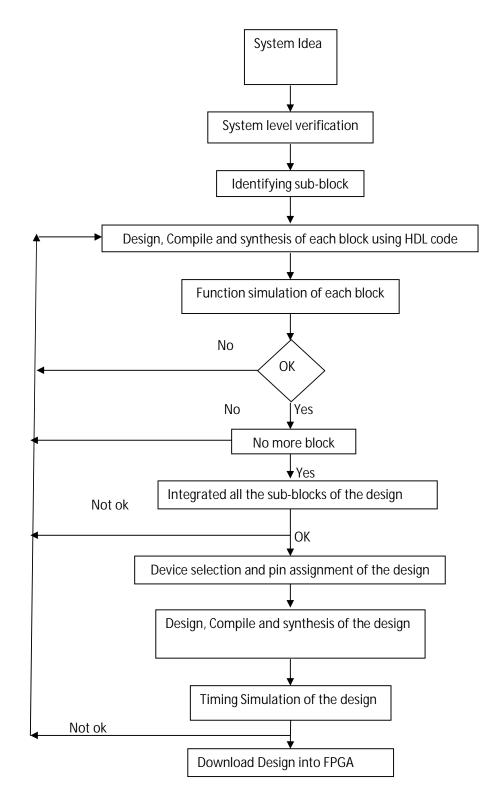

Design of a digital system can be realized into hardware using FPGA device. It reduces the time to market, reduces the cost and offers the design flexibility. There are many FPGA vendors such as Altera, Xilinx, Latice, Philips etc. The vendors provide the Electronic Design Automation (EDA) software for compilation, synthesis and simulation. Figure shows flow diagram of a design to be realized into FPGA hardware. Once the sub-modules of a design are identified, each of the modules is designed, compiled and synthesized using FPGA vendor provide software. Then functional simulation is performed upon each module. The correct simulation result ensures the proper functionality of a design. Once the simulation result of all the sub modules are as desired then they are integrated and simulated again. Then for hardware realization, suitable FPGA device is selected for the design, inputs and outputs are assigned to specific pins of the FPGA, It is again compiled and synthesized. After that timing simulation of the design is performed to ensure that the design functions in real time. Then the design is downloaded into the FPGA. [9]

### **Design Flow for FPGA Implementation**

Figure 2.10: Digital system design and implementation using FPGA

# Design of an 8-point IFFT/FFT for OFDM Transmitter /Receiver

### **3.1 Introduction**

This chapter focuses the technique and method for designing the core processing block in an OFDM transmitter. The computational time of FFT is faster than that of DFT because the number of multiplications and additions operation in FFT is less compared to DFT method as shown in Table 2.2. The computational time between FFT and IFFT is assumed to be same because of their operations which are almost similar except for scaling and conjugation of the twiddle factor. There are two techniques to implement the OFDM transmitter, namely structural method and direct computation method. Both methods will be discussed in the following section.

# **3.2** Proposed technique of an 8-point Inverse Fast Fourier Transform (IFFT) and Fast Fourier Transform (FFT)

The core processing block in an OFDM transmitter is the Inverse Fast Fourier Transform. The IFFT can be implemented using two methods, structural method or direct mathematical method.

In our total project work, we consider here only 8-point IFFT /FFT calculations for simplicity. Otherwise if want to use 16, 32,  $64....2^n$  (n= 4, 5, 6...) point IFFT /FFT calculations, it would increase much complexity of our project work.

### 3.2.1 Implementing structural method of an 8-point IFFT

Structural method implements a single butterfly computation.

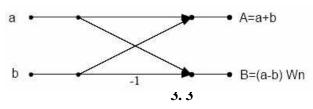

Figure 3.1 Single Butterfly Flow Chart in IFFT

The single butterfly computation is implemented in the data path unit for IFFT operation. A control unit controlling the data path and determine the stage of operations. The control unit coordinates the appropriate pairs of inputs into the butterfly computation and the output pairs are store in the memory. Each pair of random input bits will undergo multiples of butterfly computation in stage 1. Assume the input string bits are x0, x1, x2, x3, x4, x5, x6, and x7 respectively, Stage 1 computation will store its result in certain memory location, assume memory M.

At stage 2, the result in memory M is feed into butterfly computation in pairs. The control unit acts as a selector to select the correct input for the butterfly computation in every stage. The output from Stage 2 is stored in the same memory location at M.

For 8-point IFFT, the process ends at Stage 3. The output of the Stage 3 is divided by 8 and hence the final output is the computed Inverse Fast Fourier Transform.

Figure 3.2 Structural Implementation of IFFT

Figure 3.2 shows that there are 3 stages in an 8-point IFFT where Stage 1 accepts the input data directly.

### 3.2.2 Expanding Direct Method of an 8-point IFFT

To make simplicity of the implementation we can use direct method where the final output is derived from the input directly. In a structural method, the single butterfly and summation has to be carried out 12 times for an 8-point IFFT. The multiplication and summation has to be carried out, although some twiddle factor has value of 0 or 1. This introduces redundancy in the implementation.

For example, the implementation of structural approach is X = (0) a + (1) b, where in the direct mathematical approach, the implementation is simply X=b. Multiplication of the twiddle factor is skipped to avoid redundancy in and reduce computation time. Thus, this method is optimized.

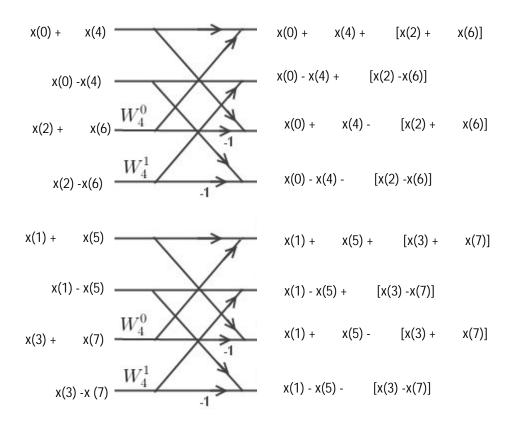

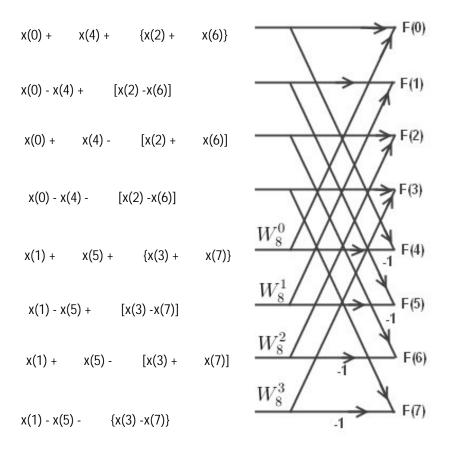

Figure 3.3 Stage 1 Computation Flow Chart of an 8-point IFFT Computation

The Figure 3.3 shows the computation in Stage 1. It is shown the even samples and odd samples are processed separately. The outputs of Stage 1 are feed as the inputs of the Stage 2. Stage 2 computation take place and this process repeats at the final stage, Stage 3.

The output of Stage 1 is connected to the input of Stage 2. The complexity of the output equations increases as the Stage number increases because twiddle factor computations are involved. The twiddle factor includes multiplication and additions operations.

Figure 3.4 Stage 2 Computation Flow Chart of an 8-point IFFT Computation

Figure 3.4 shows the Stage 2 computation. The even inputs are grouped together and summed up in pairs. The other inputs are multiplied with their respective twiddle factor. Each of these inputs will undergo butterfly operation. Some of the outputs will have to multiply again with the twiddle factor. The outputs of the Stage 2 are fed into Stage 3. At Stage 3, the butterfly computations are repeated. The computations complexity is increased.

Figure 3.5: Stage 3 Computation Flow Chart of an 8-Point IFFT Computation

The final output equations derived from Figure 3.5 is shown as below (before divide 8):

$$\begin{split} &X(0)=x(0)+x(4)+x(2)+x(6)+x(1)+x(5)+x(3)+x(7) \\ &X(4)=W_8^0 \left[x(0)+x(4)+x(2)+x(6)-x(1)-x(5)-x(3)-x(7)\right] \\ &X(2)=W_8^0 \left[x(0)+x(4)-x(2)-x(6)\right]+W_8^2 \left[x(1)+x(5)-x(3)-x(7)\right] \\ &X(6)=W_8^0 \left\{W_8^0 \left[x(0)+x(4)-x(2)-x(6)\right]-W_8^2 \left[x(1)+x(5)-x(3)-x(7)\right]\right\} \\ &X(1)=W_8^0 \left[x(0)-x(4)\right]+W_8^2 \left[x(2)-x(6)\right]+W_8^1 \left[x(1)-x(5)\right]+W_8^3 \left[x(3)-x(7)\right] \\ &X(5)=W_8^0 \left\{W_8^0 \left[x(0)-x(4)\right]+W_8^2 \left[x(2)-x(6)\right]-W_8^1 \left[x(1)-x(5)\right]+W_8^3 \left[x(3)-x(7)\right]\right\} \\ &X(3)=W_8^0 \left\{W_8^0 \left[x(0)-x(4)\right]-W_8^2 \left[x(2)-x(6)\right]+W_8^2 \left\{W_8^1 \left[x(1)-x(5)\right]-W_8^3 \left[x(3)-x(7)\right]\right\} \\ &X(7)=W_8^0 \left\{W_8^0 \left[X(0)-x(4)\right]-W_8^2 \left[x(2)-x(6)\right]\right\}-W_8^2 \left\{W_8^1 \left[x(1)-x(5)\right]-W_8^3 \left[x(3)-x(7)\right]\right\} \\ \end{split}$$

By using Verilog HDL the final equations are implemented to make an 8-point IFFT processor which is shown Table 3.1. Using direct method the equations have been optimized for an efficient implementation. The twiddle factors are represented by 8 bit binary number. There will be slight error percentage in this design due to the approximation of the twiddle factor values.

### Table 3.1 Final equations for an 8-point IFFT processor

| X(0) = x(0) + x(4)     | + x(2) + x(6) + x(1) + x(5) + x(3) + x(7)                             |

|------------------------|-----------------------------------------------------------------------|

| X(4) = x(0) + x(4)     | x + x(2) + x(6) - x(1) - x(5) - x(3) - x(7)                           |

| X(2) = x(0) + x(4)     | -x(2)-x(6)+jx(1)+jx(5)-jx(3)-jx(7)                                    |

| X(6) = x(0) + x(4)     | - $x(2)$ - $x(6)$ - $jx(1)$ - $jx(5)$ + $jx(3)$ + $jx(7)$             |

| X(1) = x(0) - x(4) +   | jx(2) - jx(6) + 0.7071x(1) + j0.7071x(1) - 0.7071x(5) - j0.7071x(5) - |

| 0.7071x(3)             | -j0.7071x(3) + 0.7071x(7) + j0.7071x(7)                               |

| X(5) = x(0) - x(4) +   | -jx(2)-jx(6)-0.7071x(1)-j0.7071x(1) + 0.7071x(5)+j0.7071x(5)          |

|                        | + 0.7071x (3) + j0.7071x (3) - 0.7071x (7) - j0.7071x (7)             |

| X(3) = x(0) - x(4) -   | jx(2)-jx(6)-0.7071x(1)+j0.7071x(1) + 0.7071x(5)-j0.7071x(5)           |

| + 0.7071x(3)           | 3)- j0.7071x(3) - 0.7071x(7)+ j0.7071x(7)                             |

| X(7) = x(0) - x(4) - j | x(2)- jx(6)+ 0.7071x(1)- j0.7071x(1) - 0.7071x(5)+ j0.7071x(5) -      |

| 0.7071x(3              | )+ $j0.7071x(3) + 0.7071x(7) - j0.7071x(7)$                           |

|                        |                                                                       |

#### 3.3 Implementation of an 8-point IFFT processor

Now we implement the 8-point IFFT processor which involved few modules. All these modules are joined together to produce an 8 point IFFT processor. Figure 3.6 shows an 8 point IFFT block diagram and their interconnections.

Figure 3.6 Block diagram of an 8 point IFFT processor

Figure 3.6 shows the full functional block diagram of an 8 point IFFT processor where the inputs are passed into the design to store the input data synchronously at every positive edge triggered. Then, the path module shows the arithmetic computation for each respective output.

From table 3.1, for the IFFT algorithm, the even and odd outputs are computed separately in two main groups. The odd output blocks computation is more complex compared to the even group computation. The odd output computations are represented by CH 1, CH 3, CH 5 and CH 7. The even output computations are CH 0, CH 2, CH 4 and CH 6.

From the Table 2.1 we see that, in the even outputs, the twiddle factor at the output equations has been simplified.

In the sub-modules, few digital circuitries are implemented. The most important components are adder, subtractor and unsigned divider. Multiplexers are used to approximate the decimal values to the nearest integer. They are also used to convert the summation to unsigned numbers which are connected to the divider. If the signed bit is '1', then the quotient value will be converted into unsigned number. Conversion of signed and unsigned numbers is not required for positive summation values.

The input range is from -15 to 15 to avoid overflow from occurring in Xout(0). The maximum summation (before division) value which can be supported ranges from 128 to +127. Any value which exceeds this range will contribute to overflow problem.

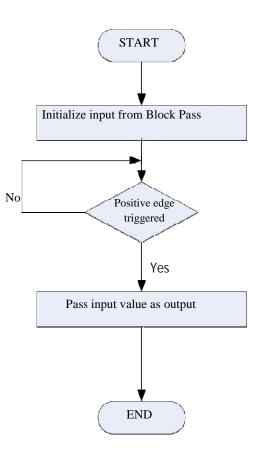

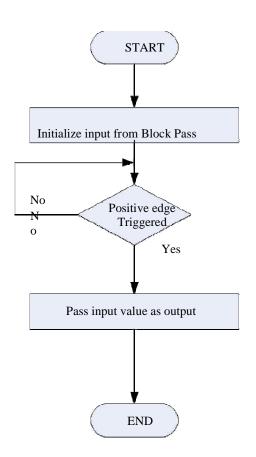

#### 3.3.1 Store module of an 8-point IFFT processor

The first step of an 8-point IFFT processor is to store the input for other sub-module. This module passes the inputs to the sub-modules that do the IFFT computations. The Store module consists of 8 D type flip flop registers. The outputs of this block are 8 lines of 8 bit output which are connected to Channel 0, Channel 1, Channel 2, Channel 3, Channel 4, Channel 5, Channel 6 and Channel 7.

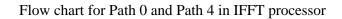

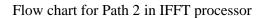

#### 3.3.2 Channel 0 and Channel 4 module of an 8-point IFFT processor

The purpose of Channel 0 and Channel 4 is to compute and display the result of these computations. The outputs are Xout(0) and Xout(4) respectively. The arithmetic operation for Xout(0) is summation. The Xout(4) arithmetic involves summation, subtraction and division.

$\begin{aligned} X(0) &= x(0) + x(4) + x(2) + x(6) + x(1) + x(5) + x(3) + x(7) \\ X(4) &= x(0) + x(4) + x(2) + x(6) - x(1) - x(5) - x(3) - x(7) \end{aligned}$

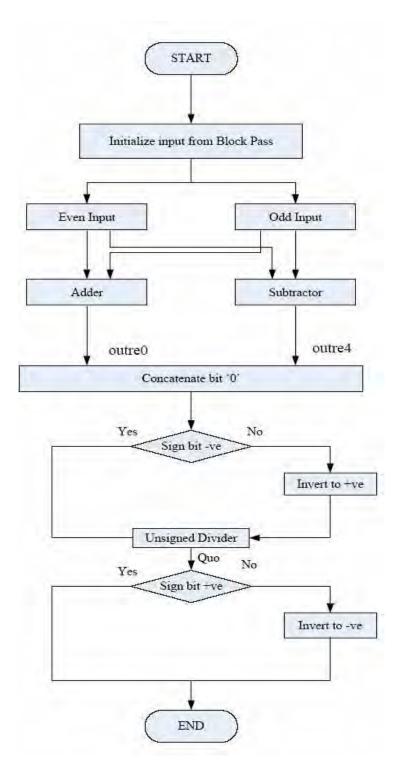

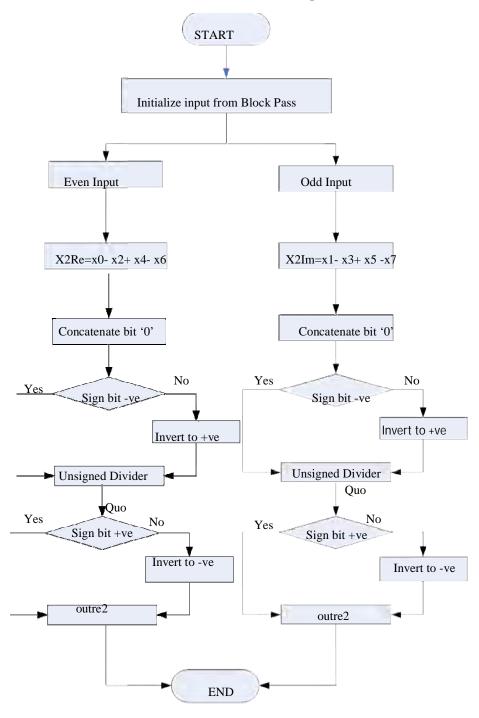

#### 3.3.3 Channel 2 and Channel 6 module of 8 point IFFT processor

The work of Channel 2 and Channel 6 is to compute and display the result of these computations. The outputs are Xout(2) and Xout(6) respectively. The arithmetic operation for Xout(2) and Xout(6) involves real and imaginary operation. They are performed separately. The arithmetic operation involves summation, subtraction and division. The twiddle factor for this output is either j or -j which contributes to the imaginary component for this path.

$$X(2)=x(0)+x(4)-x(2)-x(6)+jx(1)+jx(5)-jx(3)-jx(7)$$

$$X(6)=x(0)+x(4)-x(2)-x(6)-jx(1)-jx(5)+jx(3)+jx(7)$$

## **3.3.4 Channel 1, Channel 3, Channel 5, Channel 7 modules of an 8 point IFFT processor**

The function of Channel 1, Channel 3, Channel 5 and Channel 7 is to compute and display the result of these computations. The outputs are Xout(1), Xout(3), Xout(5) and Xout(7) respectively. The arithmetic operations for all of these modules involve real and imaginary operation. They are performed separately. The arithmetic operation involves summation, subtraction and division.

The twiddle factor for all these modules consists of a real and an imaginary value of sine 45 degree or cos 45 degree. The output of the twiddle factor is approximated to 0.7071 in our proposed design.

The output equations implemented are as below:

$$X(0) = x(0)+ x(4)+ x(2)+ x(6)+ x(1)+ x(5)+ x(3)+ x(7)$$

$$X(4) = x(0)+ x(4)+ x(2)+ x(6)- x(1)- x(5)- x(3)- x(7)$$

$$X(2) = x(0)+ x(4)- x(2)- x(6)+ jx(1)+ jx(5)- jx(3)- jx(7)$$

$$X(6) = x(0)+ x(4)- x(2)- x(6)- jx(1)- jx(5)+ jx(3)+ jx(7)$$

$$\begin{split} X(1) &= x(0) - x(4) + jx(2) - jx(6) + 0.7071x(1) + j0.7071x(1) - 0.7071x(5) - j0.7071x(5) - \\ & 0.7071x(3) - j0.7071x(3) + 0.7071x(7) + j0.7071x(7) \\ X(5) &= x(0) - x(4) + jx(2) - jx(6) - 0.7071x(1) - j0.7071x(1) + 0.7071x(5) + j0.7071x(5) \end{split}$$

$$+ 0.7071x (3) + j0.7071x (3) - 0.7071x (7) - j0.7071x (7)$$

$$X(3) = x(0) - x(4) - jx(2) - jx(6) - 0.7071x(1) + j0.7071x(1) + 0.7071x(5) - j0.7071x(5)$$

$$+ 0.7071x(3) - j0.7071x(3) - 0.7071x(7) + j0.7071x(7)$$

$$X(7) = x(0) - x(4) - jx(2) - jx(6) + 0.7071x(1) - j0.7071x(1) - 0.7071x(5) + j0.7071x(5) - 0.7071x(3) + j0.7071x(3) + 0.7071x(7) - j0.7071x(7)$$

# **3.4 Implementation of an of an 8-point Fast Fourier Transform (FFT)** processor

In the preceding section, we developed the algorithm for 8-point IFFT by using direct method. Now we develop 8-point FFT processor. The equation for FFT is similar to IFFT equation except for the negative sign in the twiddle factor and the scaling factor. Thus, the algorithm developed for the IFFT in the previous section can be used for FFT algorithm development with minor modification.

The FFT equation is shown below.

$$\boldsymbol{X}(\boldsymbol{k}) = \sum_{n=0}^{N-1} \boldsymbol{x}(n) W_N^{nK}$$

### 3.4.1 Expanding direct method of an 8 point FFT

In the Figure 3.6, it is shown that there are 3 stages in an 8-point FFT. Stage 1 accepts the input data directly. The Figure 3.7 shows the computation in Stage 1.

Figure 3.7 8-point FFT flow chart

| Table 3.2 symmetric properties of |

|-----------------------------------|

|-----------------------------------|

| М |                 |

|---|-----------------|

| 0 | +1              |

| 1 | +0.7071+j0.7071 |

| 2 | +j              |

| 3 | -0.7071-j0.7071 |

| 4 | +1              |

| 5 | -0.7071-j0.7071 |

| 6 | -j              |

| 7 | 0.7071+j0.7071  |

Figure 3.8: Stage 1 computation flow chart of an 8-point FFT Computation.

Figure 3.8 shows the even samples and odd samples which are processed separately. The outputs of Stage 1 are feed as the inputs of the Stage 2. Stage 2 computation take place and this process repeats at the final stage, Stage 3.

The output of Stage 1 is connected to the input of Stage 2. The complexity of the output equations increases as the Stage number increases because twiddle factor computations are involved. The twiddle factor includes multiplication and additions operations.

Figure 3.9 Stage 2 Computation Flow Chart of an 8-point FFT Computation

Figure 3.9 shows the Stage 2 computation. The even inputs are grouped together and summed up in pairs. The other inputs are multiplied with their respective twiddle factor. Each of these inputs will undergo butterfly operation. Some of the output will have to multiply again with the twiddle factor. The outputs of the Stage 2 are fed into Stage 3.

Figure 3.10 Stage 3 computation flow chart of an 8-point FFT Computation

At Stage 3, the butterfly computations are repeated and the computations complexity is increased. Therefore from Figure 3.10 which is the stage 3 computation, we get the final output.

The final output equations derived from Figure 3.10 is shown as below:

$$\begin{aligned} X(0) &= x(0) + x(4) + [x(2) + x(6)] + [x(1) + x(5) + {x(3) + x(7)}] \\ X(4) &= x(0) - x(4) + [x(2) - x(6)] + [x(1) - x(5) + {x(3) - x(7)}] \\ X(2) &= x(0) + x(4) - [x(2) + x(6)] + [x(1) + x(5) - {x(3) + x(7)}] \\ X(6) &= x(0) - x(4) - [x(2) - x(6)] + [x(1) - x(5) - {x(3) - x(7)}] \\ X(1) &= x(0) + x(4) + [x(2) + x(6)] - [x(1) + x(5) + {x(3) + x(7)}] \\ X(5) &= x(0) - x(4) + [x(2) - x(6)] - [x(1) - x(5) + {x(3) - x(7)}] \\ X(3) &= x(0) + x(4) - [x(2) + x(6)] - [x(1) + x(5) - {x(3) + x(7)}] \end{aligned}$$

Table 3.1 shows the final equations that are implemented using Verilog HDL to produce an 8point IFFT processor. The equations have been optimized for an efficient implementation. The twiddle factors are represented b 8 bit binary number. There will be slight error percentage in this design due to the approximation of the twiddle factor values.

#### Table 3.3 Final equations for an 8-point FFT processor

| X(0) = x(0) + x(4) + x(2) + x(6) + x(1) + x(5) + x(3) + x(7)                                 |

|----------------------------------------------------------------------------------------------|

| $X(4) = x(0) - x(4) - j[x(2) - x(6)] + [0.7071 - 0.7071j] [x(1) - x(5) - j \{x(3) - x(7)\}]$ |

| X(2) = x(0) + x(4) - x(2) - x(6) - j [x(1) + x(5) - x(3) - x(7)]                             |

| $X(6) = x(0) - x(4) + j [x(2) - x(6)] + [0.7071 - j0.7071][x(1) - x(5) + j \{x(3) - x(7)\}]$ |

| X(1) = x(0) + x(4) + x(2) + x(6) - [x(1) + x(5) + x(3) + x(7)]                               |

| $X(5) = x(0) - x(4) - j[x(2) - x(6)] - [0.7071 - 0.7071j] [x(1) - x(5) - j \{x(3) - x(7)\}]$ |

| X(3) = x(0) + x(4) - x(2) - x(6) + j [x(1) + x(5) - x(3) - x(7)]                             |

| $X(7) = x(0) - x(4) + j [x(2) - x(6)] - [0.7071 - j0.7071][x(1) - x(5) + j {x(3) - x(7)}]$   |

## **Chapter 4**

## **Result of Verilog HDL Simulation**

#### 4.1 Introduction

In the previous chapter we have designed the core processing block of IFFT and FFT for an OFDM transmitter and receiver. We showed there are two techniques to implement the design and we use direct method of an 8-pont IFFT and FFT for simplicity.

This chapter discusses the results and simulation which are carried by Altera Quartus -II simulator with various input samples. Each of the input samples contains 4-bits of input. The accuracy of the output is also verified to the output from MATLAB simulation. The result is divided into 2 different sections, for FFT processor and IFFT processor. The output from each of the modules is shown and followed to the overall output.

#### 4.2 FFT Processor Result

In this sub section, the output of FFT processor is presented. This module is combined of eight sub-modules.

#### 4.2.1 Store Module Simulation Result for FFT Processor

This module is to pass the input data at each positive clock edge to the different modules of FFT processor with the condition that the load signal is active high. One clock signal is required to pass the data in. The result is shown in Figure 4.1

| ate: Ju | ne 30, 20    | 013 |    | pass_fft.vwf* |          | F            | Project: pass0 |  |

|---------|--------------|-----|----|---------------|----------|--------------|----------------|--|

|         | ps<br>3.8 ns |     | 20 | 0,0 ns        | 400,0 ns | 500.0 ns     |                |  |

| rst 1   | 5.8 hs       |     |    |               |          |              |                |  |

| clk     |              |     | _  |               |          | _            | -              |  |

| in_x0   | 1            | 5   | 2  | 8             | × ×      | 9            | 12             |  |

| in_x4   | 1            | 5 X | 11 | 6             | χ        | 5            | 2              |  |

| in_x2   | 1            | 5   | 2  | X 9           | X        | 5            | 11             |  |

| in_x6   | 1            | 5 X | 14 | 12            | X        | 11 X         | 2              |  |

| in_x1   | 1            | 5 X | 1  | X 0           | X        | 8            | 6              |  |

| in_x5   | 1            | 5 X | 7  | X 3           | X        | 11 X         | 2              |  |

| in_x3   | 1            | 5   | 9  | X 5           |          | 11           | 3              |  |

| in_x7   | 1            | 5 X | 14 | 15            |          | 6 X          | 9              |  |

| out_x0  | 0            | 15  | X  | 2 X           | 8        | X 9          | 12             |  |

| out_x1  | 0            | 15  | )  | 1 )           | 0        | ) 8          | 6              |  |

| out_x2  | 0            | 15  | (  | 2 )           | 9        | X 5          | ) 11           |  |

| out_x3  | 0            | 15  | X  | 9 )           | 5        | ) <b>1</b> 1 | 3              |  |

| out_x4  | 0            | 15  | X  | 11 X          | 6        | 5            | 2              |  |

| out_x5  | 0            | 15  | X  | 7             | 3        | )11          | 2              |  |

| out_x6  | 0            | 15  | X  | 14 X          | 12       | X 11         | χ 2            |  |

| out_x7  | 0            | 15  | X  | 14            | 15       | Y 6          | 9              |  |

Figure 4.1 Store Module Simulation Output for FFT Processor

The above Figure 4.1 shows that each data in the corresponding input is successfully pass to the output buffer out\_x0,out\_x1,out\_x2,out\_x3,out\_x4,out\_x5,out\_x6, and out\_x7, respectively. This simulation and other rest of simulations we use five (5) different 8-input data (ASCII) which is provided for corresponding 8-point FFT operation at every positive clock.

## 4.2.2 Channel 0 and Channel 4 Module Simulation Result for FFT Processor

These modules implement almost the identical mathematical operation except the mathematical operators are different. The equations are shown in Chapter 3. There is no imaginary component present at the output. The result is shown in Figure 4.2 and Figure 4.3.

|          | ) ps<br>3.8 ns | 200  | 200.0 ns |      |    |  |  |  |

|----------|----------------|------|----------|------|----|--|--|--|

| rst      |                |      |          | 1    |    |  |  |  |

| clk      |                |      |          |      |    |  |  |  |

| in_x0    | 15             | 2    | 8        | 9    | 12 |  |  |  |

| in_x4    | 15             | 11   | 6        | 5    | 2  |  |  |  |

| in_x2    | 15             | 2    | 9        | 5    | 11 |  |  |  |

| in_x6    | 15             | 14   | 12       | × 11 | 2  |  |  |  |

| in_x1    | 15             | X 1  | 0        | 8    | 6  |  |  |  |

| in_x5    | 15             | X 7  | 3        | 11   | 2  |  |  |  |

| in_x3    | 15             | 9    | 5        | 11   | 3  |  |  |  |

| in_x7    | 15             | X 14 | 15       | 6    | X9 |  |  |  |

| out_reg0 | 0 120          | 60   | X 58     | 66   | 47 |  |  |  |

Figure 4.2: Channel 0 Module Simulation Output for FFT Processor

Figure 4.2 indicates the first output **out\_reg0** by calculating eight(8) input data in the 8-point FFT operation.

| 0 ps     |    | 200.  | 0 ns | 400. | 0 ns 500.0 ns |

|----------|----|-------|------|------|---------------|

| 13.8     | ns |       |      |      |               |

| rst      |    |       |      |      |               |

| clk      |    |       |      |      |               |

| in_x0    | 15 | 2     | 8    | 9    | 12            |

| in_x4    | 15 | ()    | 6    | 5    | 2             |

| in_x2    | 15 | 2     | 9    | 5    | ( 11          |

| in_x6    | 15 | ( 14  | 12   | ×11  | 2             |

| in_x1    | 15 | ( 1 ) | 0    | 8    | 6             |

| in_x5    | 15 | 7     | 3    | ()   | 7             |

| in_x3    | 15 | 9     | 5    | 11   | 3             |

| in_x7    | 15 | 12    | ( 11 | 6    | 9             |

| out_reg4 | 0  | 200   | 96   | 180  | 144           |

Figure 4.3: Channel 4 Module Simulation Output for FFT Processor

Figure 4.3 shows the fifth output **out\_reg4** by calculating eight (8) input data in the 8-point FFT operation.

# **4.2.3** Channel **2 and** Channel **6 Module Simulation Result for FFT Processor**

These modules implement almost the identical mathematical operation except the mathematical operators are different. The equations are shown in Chapter 3. There is a imaginary component present at the output. Thus, Channel 2 and Channel 6 have more complex mathematical expressions rather than Channel 1 and Channel 4. The result is shown in Figure 4.4 and Figure 4.5

| 0 ps<br>13.8 ns |    | 200 <sub>1</sub> | 0 ns | 400.   | 0 ns 500.0 ns |    |

|-----------------|----|------------------|------|--------|---------------|----|

| rst             |    |                  |      |        |               |    |

| clk             |    |                  |      |        |               |    |

| in_x0           | 15 | 2                | 8    | 9<br>5 | 8 X 9 X       | 12 |

| in_x4           | 15 | ()               | 6    |        | 2             |    |

| in_x2           | 15 | 2                | 9    | 5      | ()            |    |

| in_x6           | 15 | 14               | 12   | 11     | 2             |    |

| in_x1           | 15 | ( 1 )            | 0)   | 8      | 6             |    |

| in_x5           | 15 | 7                | 3    | 11     | 7             |    |

| in_x3           | 15 | 9                | 5    | 11     | 3             |    |

| in_x7           | 15 | (11)             | 15   | 6      | 9             |    |

| out_reg2        | 0  | 253              | 249  | 254    | χ             |    |

| outim2          | 0  | 12               | 17   | 254    | 255           |    |

Figure 4.4: Channel 2 Module Simulation Output for FFT Processor

Figure 4.4 shows the third output which consists of one real output **out\_reg2** and one imaginary output *outim2* by calculating eight (8) input data in the 8-point FFT operation.

|          | 0 ps<br>13.8 ns | 200  | 0 ns<br>I | 400 0 ns 500. |     |  |  |

|----------|-----------------|------|-----------|---------------|-----|--|--|

| rst      |                 |      |           |               |     |  |  |

| clk      |                 |      |           |               |     |  |  |