# VHDL BASED MODELING AND DESIGN OF PARAMETERIZABLE MULTIPLIERS FOR TESTABILITY

A thesis submitted to the Department of Electrical and Electronic Engineering BUET, Dhaka in partial fulfillment of the requirements for the degree of Master of Science in Engineering (Electrical and Electronic)

## SHAIKH ARIF SHAMS

ROLL NO: 9406214P SESSION: 1993-94-95

AUGUST 1998

The thesis titled "VHDL based modeling and design of parameterizable multipliers for testability" submitted by Shaikh Arif Shams, Roll No. 9406214P to the Department of Electrical and Electronic Engineering, BUET has been accepted as satisfactory for partial fulfillment of the requirements for the degree of Master of Science in Engineering (Electrical and Electronic).

## **BOARD OF EXAMINERS**

1.

2.

3.

4.

(Dr. Syed Mahfuzul Aziz) Professor Department of Electrical and Electronic Engineering BUET, Dhaka 1000.

Dr. Enamul Basher Professor and Head Department of Electrical and Electronic Engineering BUET, Dhaka 1000.

aucher 27 aprou

(Dr. Joarder Kanpuzzaman)//8/ Associate Professor Department of Electrical and Electronic Engineering BUET, Dhaka 1000.

HR 3.8.98

(Dr. Chowdhury Mofizur Rahman) Assistant Professor Department of Computer Science and Engineering BUET, Dhaka 1000. Chairman (Supervisor)

Member (Ex-Officio)

> Member (Internal)

Member (External)

## **DECLARATION**

I hereby declare that this work has been done by me and it has not been submitted elsewhere for the award of any other degree or diploma.

### Countersigned

## ACKNOWLEDGEMENT

It is the author's pleasure to acknowledge his heartiest gratitude and profound obligation to his Supervisor, Dr. Syed Mahfuzul Aziz, Professor, Department of Electrical and Electronic Engineering, Bangladesh University of Engineering and Technology for his excellent supervision, continuous guidance and valuable suggestion throughout the progress of the work.

The author is indebted to Mr. Nazmul Ula, Ph. D., Assistant Professor, Electrical Engineering & Computer Science, Loyola Marymount University for allowing the author to simulate the VHDL code of his design on the *ModelTek* simulator in Mr. Ula's laptop. The author is also grateful to him for his constructive criticisms and valuable suggestions.

The author wishes to thanks Dr. Iftekhar Ahmed, Lecturer, University telecom Malaysia for his help with VHDL based design tools.

## ABSTRACT

Full custom design of VLSI circuits is very time consuming and costly. Such a design for a target process cannot be reused for fabrication even in a scaled down version of the same process. This makes the approach less attractive, since the complete chip has to be redesigned for the process. As a result, language based design approach has gained tremendous popularity because of the versatility and portability of such designs. Sophisticated CAD tools are being developed to automate the design procedure of complex integrated circuits.

This thesis presents the VHDL (VHSIC Hardware Description Language) based design of a parallel multiplier of variable operand wordlengths. The multipliers are very easily testable with only 19 vectors irrespective of the operand size. All the single stuckat faults in the multiplier can be tested with these vectors. The VHDL code for the proposed multiplier can be incorporated into logic synthesis tools for the automatic generation of multiplier macrocells within a few minutes.

## CONTENTS

| Ackno   | wledgement   |                                    |     | iv       |

|---------|--------------|------------------------------------|-----|----------|

| Abstra  | ct           |                                    | •   | <b>v</b> |

| List of | Figures      |                                    |     | ix       |

| List of | Tables       |                                    |     | x        |

| List of | Abbreviation | ns                                 |     | xi       |

|         |              | · ·                                |     |          |

|         |              |                                    | ·   |          |

| CHAP    | TER 1 Intro  | oduction                           |     | 1        |

|         | 1.1          | Aims                               |     | 1        |

|         | 1.2          | Literature Review                  | · · | 2        |

|         | 1.3          | Organization of the Thesis         |     | • 4      |

|         |              |                                    |     |          |

| CHAP    | TER 2 Mult   | iplier Algorithms and Architecture |     | 5        |

| сĸ |     | ipher Algorithms and Architecture                 | 5  |

|----|-----|---------------------------------------------------|----|

| •  | 2.1 | Introduction                                      | 5  |

|    | 2.2 | Straightforward Carry-Save Array Multiplication   | 5  |

|    | 2.3 | Booth Algorithm                                   | 7  |

|    | 2.4 | Modified Booth Algorithm                          | 9  |

|    | 2.5 | Removal of Sign-Bit Extension Circuitry           | 12 |

|    | 2.6 | An Architecture Based on Modified Booth Algorithm | 14 |

|    |     |                                                   |    |

vi

| CHAPTER                               | 3 Test | ability of the Multiplier                          | 17  |

|---------------------------------------|--------|----------------------------------------------------|-----|

|                                       | 3.1    | Introduction                                       | 17  |

|                                       | 3.2    | Testing Approach                                   | 17  |

| · · ·                                 | 3.3    | Modification of the Architecture for Testability   | 18  |

|                                       | 3.4    | Testing of Individual Cells                        | 20  |

| · · ·                                 |        | 3.4.1 Testing of MBEs for Single Stuck-at Fault    | 20  |

|                                       |        | 3.4.2 Testing of the SCs for Single Stuck-at Fault | 21  |

| х.<br>Х                               | 3.5    | Testing the Multiplier                             | -24 |

|                                       |        | 3.5.1 Test Vectors                                 | 24  |

|                                       |        | 3.5.2 Exhaustive Testing of the FAs                | 24  |

| •                                     |        | 3.5.3 Exhaustive Testing of the MCAs               | 27  |

|                                       |        | 3.5.4 Testing of the MBEs                          | 28  |

|                                       | •      | 3.5.4.1 Exhaustive Testing                         | 28  |

|                                       |        | 3.5.4.2 Testing for Single Stuck-at                | 29  |

|                                       |        | Fault                                              |     |

|                                       |        | 3.5.5 Test Vectors for SCs                         | 30  |

|                                       | 3.6    | Calculation of Overhead                            | 30  |

| •                                     |        | 3.6.1 Hardware Overhead                            | 30  |

| ·<br>. · · ·                          |        | 3.6.2 Delay Overhead                               | 31  |

| · · · · · · · · · · · · · · · · · · · | 3.7    | Summary                                            | 31  |

|                                       |        |                                                    |     |

| CHAPTER 4                             | I VHĎ  | L Modeling of the Multiplier                       | 32  |

|                                       | 4.1    | Introduction                                       | 32  |

| ·                                     | 4.2    | Partitioning                                       | 32  |

|                                       | 4.3    | Design Hierarchy                                   | 35  |

|                                       | 4.4    | VHDL Model                                         | 35  |

|                                       |        | vii                                                |     |

|               | 4.4.1     | The Modified Booth Encoder   | 36 |

|---------------|-----------|------------------------------|----|

| •             | 4.4.2     | The sc_n                     | 37 |

| · · · ·       | 4.4.3     | The n_adder                  | 38 |

|               | 4.4.4     | The adder_sc_n               | 40 |

| •<br>• •      | 4.4.5     | The n_mca                    | 41 |

|               | 4.4.6     | The Multiplier               | 42 |

|               | 4.4.7     | Achieving Parameterizability | 47 |

| 4.5           | Testbend  | ch and Simulation            | 47 |

| CHAPTER 5 Col | nclusions | and Recommendations          | 53 |

| 5.1           | Concl     | usions                       | 53 |

| 5.2           | Futur     | e Work                       | 54 |

viii

**References:**

# List of Figures

| Fig. 2.1      | A parallel multiplier array using carry save adders           | . 6 |

|---------------|---------------------------------------------------------------|-----|

| Fig. 2.2      | Multiplication example using bit-pair recoding                | 11  |

| Fig. 2.3      | Sign extended partial product array                           | 12  |

| Fig. 2.4      | Recoded sign extended partial product array                   | 14  |

| Fig. 2.5      | An 8 by 8 bit modified Booth multiplier array                 | 16  |

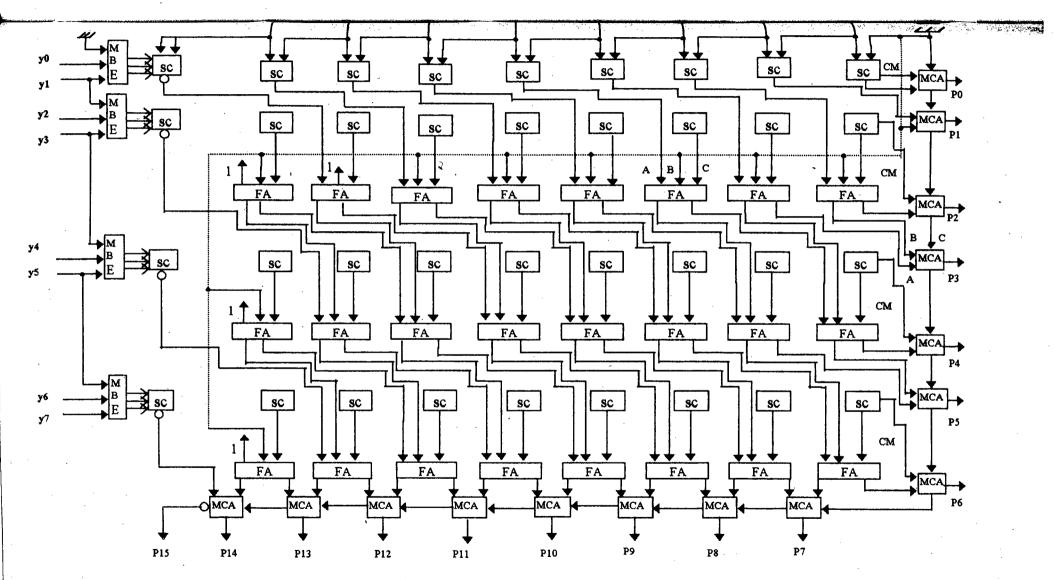

| Fig. 3.1      | Architecture of a 6 x 8 bit multiplier with recoded sign bits | 19  |

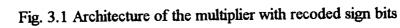

| Fig. 3.2      | Gate level design of the modified Booth encoder (MBE)         | 20  |

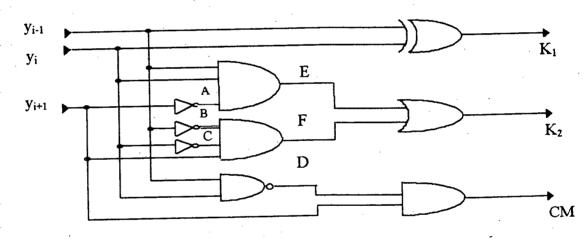

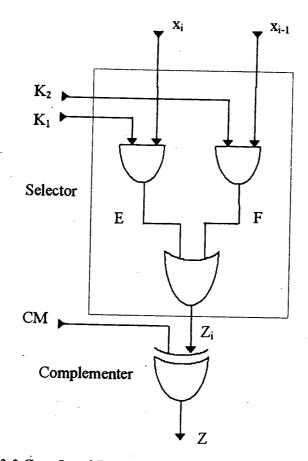

| Fig. 3.3      | Gate level design of the selector-complementer block          | 22  |

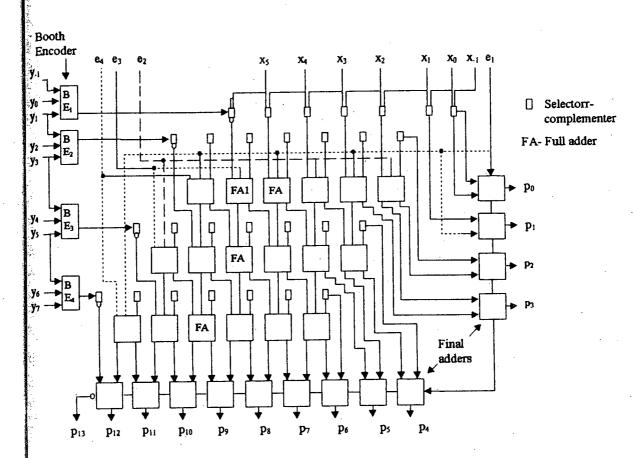

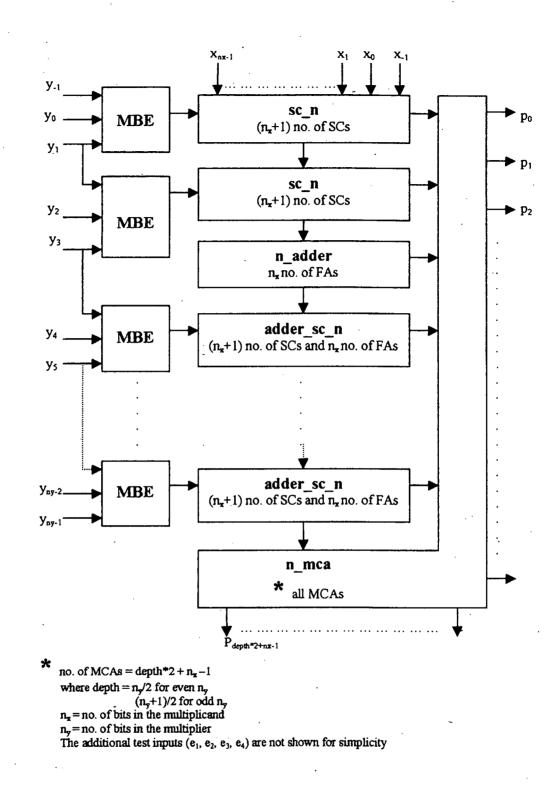

| -<br>Fig. 4.1 | Partitioning the multiplier into modular blocks               | 33  |

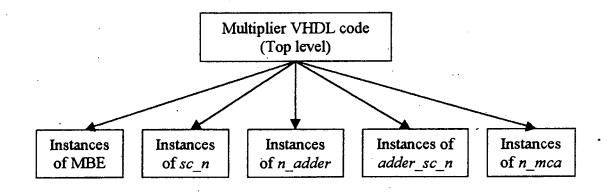

| Fig. 4.2      | Design hierarchy                                              | 35  |

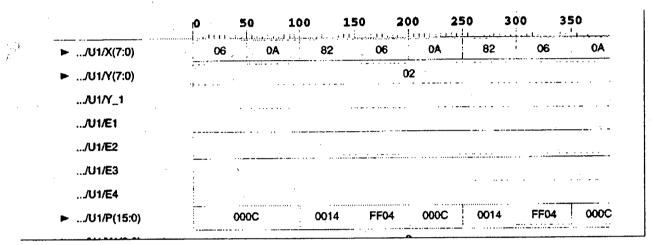

| Fig. 4.3      | Simulation result                                             | 52  |

ix

# List of Tables

| Table 2.1 | Multiplier bit-pair recoding scheme               | - 11 |

|-----------|---------------------------------------------------|------|

| Table 2.2 | Modified Booth recoding table                     | 15   |

| Table 3.1 | Fault matrix for the MBE logic circuit            | , 21 |

| Table 3.2 | Fault matrix for the selector block               | 23   |

| Table 3.3 | A set of test vectors for an 8 X 8 bit multiplier | 25   |

| Table 3.4 | Exhaustive testing of the FAs                     | 26   |

| Table 3.5 | Exhaustive testing of the MCAs                    | 27   |

| Table 3.6 | Exhaustive testing of the MBEs                    | 28   |

х

# List of Abbreviations

|       | CPLD  | Complex Programmable Logic Device   |

|-------|-------|-------------------------------------|

|       | DCVS  | Differential Cascode Voltage Switch |

|       | FA    | Full-Adder                          |

| · · · | FPGA  | Field Programmable Gate Array       |

| •     | LSB   | Least Significant Bit               |

|       | MBE   | Modified Booth Encoder              |

|       | MCA   | Manchester Carry Adder              |

|       | MSB   | Most Significant Bit                |

|       | SC    | Selector-Complementer               |

|       | VHDL  | VHSIC Hardware Description Language |

|       | VHSIC | Very High Speed Integrated Circuit  |

|       | VLSI  | Very Large Scale Integration        |

xi

## **Chapter 1**

## Introduction

#### 1.1 Aims

With the continuing advancements of VLSI technologies and marked shrinkage of process features, the need to develop process independent chip design tools is growing [1], [2]. The use of a hardware description language (HDL) for integrated circuit design eliminates the need to worry about process design rules at the design stage [2], [3]. This reduces the design complexity and time required in completing chip designs. This is very important since vendors need to market their products in the shortest possible time in order to capture a major share of the IC market and also to remain competitive. The fact that such high level designs can be implemented on a variety of target processes reduce the design cost as well. The aim of this thesis is to design easily testable parameterizable multipliers. VHSIC Hardware Description Language (VHDL) will be used for the design since it includes some very useful features for hardware design which are not available in other languages [2]-[4]. The use of VHDL will make the design portable and reusable. This chapter presents brief review of the literature on popular multiplication algorithms and their testable implementations. The review also includes a discussion of the multiplier compilers found in the available literature.

#### **1.2 Literature Review**

Multipliers are often one of the key elements in single chip digital information processors [5]-[8]. Various algorithms have been developed for multiplication of binary numbers [9]-[17]. Some of them perform unsigned multiplication while others perform two's complement multiplication. The speed of multiplication varies from one algorithm to another. While speed is one of the criteria for selection of multiplication algorithm, the power consumption and regularity of structure are two other very important criteria for VLSI implementation. Especially, for automatic synthesis, the regularity of structure is the most critical factor. The modified Booth algorithm [9], [10] for two's complement multiplication essentially reduces the number of partial products by a factor of two compared to the straightforward carry-save array multiplier [11]. Multiplication speed is almost doubled. Besides, there is no need for precomplementing the multiplier or postcomplementing the product. The multiplier structure is regular, therefore suitable for VLSI implementation.

With the advancement of integrated circuit technology, the implementation of large array multipliers on a single chip has become possible. However, due to the increasing complexity of VLSI circuits it is becoming more and more difficult and costly to test them [18], [19]. As a result, it is a common practice among circuit designers these days to give due consideration to testability at the early stages of design. Extra hardware and/or inputs are added to the original circuits to make them easily testable thereby reducing testing time and cost. The testability of parallel array multipliers have been investigated by several researchers. A number of testable multiplier architectures have been proposed by them [20]-[24]. In [20], C-testable designs of carry-save array multiplier and Baugh-Wooley's two's complement array multiplier are presented. Two designs of easily testable gate-level and DCVS logic multipliers have been proposed in [21]. These designs are based on the straightforward carry-save array multiplication

scheme and have been shown to be testable with a constant number of test vectors irrespective of the array size. Such designs are referred to as "C-testable". Gate-level C-testable multipliers based on the modified Booth algorithm have been presented in [22] and [23]. A C-testable DCVS design using this algorithm has also been presented in [24].

In order to find out an optimal area and speed of a processor chip, the different modules within the chip have to be tried out for various architectures. Since it is time consuming to verify many possible layouts for each module, one approach is to use software packages called *module generators* or *silicon compilers* to provide fast and efficient design of parameterized modules. The multiplier compilers presented in [25]-[26] generate parameterizable layouts for MOS technology. The technology independence of the compiler presented in [27] is limited by the requirement that the leaf cells have to be recharacterized in the new technology. The aim of this thesis is to present the design of totally process independent VLSI array multipliers of variable size (parameterizable) using VHDL.

The proposed multiplier is based on the modified Booth algorithm. There is some specific reasons for this particular choice. First of all it reduces the number of partial products to almost half compared to straightforward carry-save array multiplier. Besides, the multiplier has a regular structure which is an extremely important criterion in the selection of schemes for VLSI design. The multipliers are made C-testable [28], i.e., they can be tested for all single stuck-at faults with a constant number of test vectors irrespective of the size of the operands. Although stuck-at fault models cannot adequately model transistor stuck-on and stuck-open faults [29]-[30], it is possible to derive equivalent stuck-at test sets for logic gates to cover transistor stuck-on and stuck-open faults [31]. Since the number of test vectors is constant for any multiplier size, the test generation for the proposed designs are considerably small. In this thesis, VHDL is chosen for designing the testable, parameterizable multipliers because of its unique

features for hardware design [2]-[4]. The use of VHDL will make the designs portable and reusable.

#### 1.3 Organization of the Thesis

Chapter 2 presents the parallel multiplication scheme using a straightforward array of carry-save adders. It also introduces the Booth algorithm for multiplication of signed binary numbers. Bit-pair recoding technique and modified Booth multiplier is also presented in this chapter. Chapter 3 analyzes the testability of the multiplier architecture based on modified Booth algorithm and presents the design of a C-testable multiplier. The VHDL model of the parameterizable and easily testable multiplier is presented in chapter 4. Finally, chapter 5 concludes the thesis with some recommendations for further research.

## Chapter 2

## **Multiplier Algorithms and Architecture**

#### 2.1 Introduction

In this chapter, multiplication of two fixed point binary operands will be discussed. Some most common parallel multiplication schemes such as the straightforward carry-save array multiplication, Booth algorithm and method of bit-pair recoding or modified booth algorithm will be considered. An architecture based on the modified Booth algorithm for multiplication of two signed numbers will also be presented in this chapter.

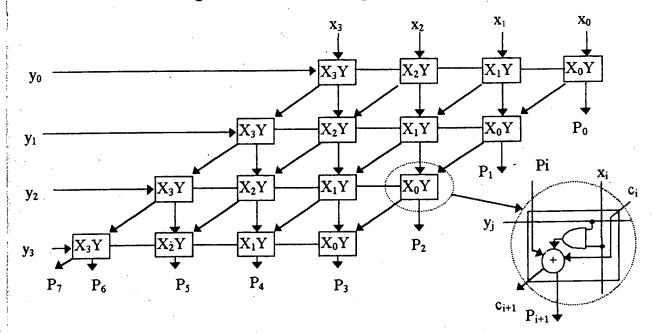

### 2.2 Straightforward Carry-Save Array Multiplication

Multiplication can be defined as repeated addition. The number to be added is the multiplicand, the number of times it is added is the multiplier, and the result is the product. Each step of addition generates a partial product and when the operands are integer the product is twice the length of the operands in order to preserve the information content. Binary multiplication is equivalent to the logical AND operation. Thus the evaluation of partial products consists of the logical ANDing of the multiplicand and the relevant multiplier bit. Each column of partial products must then be added, and if necessary, any carry value passed to the next column. A parallel multiplier [11] is based on the observation that all partial products in the multiplication process may be

independently computed in parallel. The partial product terms are called summands. If the multiplicand and the multiplier have m and n bits respectively then there will be m x n summands, which are produced by a set of mn AND gates. In a straightforward carrysave array multiplier the summands are collected through a cascaded array of carry-save adders. At the bottom of the array, an adder is used to convert the "carry save form" to the required form of output. The depth of the array and the carry propagation characteristics of the adder fix the multiplication time.

A 4 x 4 bit straightforward carry save array multiplier with the partial products enumerated [11] is shown in Fig. 2.1. The basic cell that may be used to construct this parallel multiplier is also shown in this figure. The multiplicand term  $x_I$  is propagated vertically, while the multiplier term  $y_I$  is propagated horizontally. Incoming partial product bits enter at the top and the incoming CARRY IN bits enter at the top right of the cell. The bit-wise AND operation is performed in the cell, and the SUM is passed to the next cell at the lower right. The CARRY OUT is passed to the bottom of the cell.

Fig. 2.1 A parallel multiplier array using carry save adders

#### 2.3 Booth Algorithm

Booth Algorithm is a powerful direct tool for signed-number multiplication [10]. In the standard add-shift method, each non zero bit of the multiplier causes one addition of the multiple of multiplicand to the partial product. The execution time of multiplication instruction is determined mainly by the number of additions to be performed. So, the execution time can be reduced if we can reduce the number of additions. This is achieved by a method of bit-scanning which reduces the number of multiplicand multiples. This technique uses recoding of the multiplier based on the string property. The process is often referred to as "skipping over 0s" and can be generalized to shift of variable lengths if string of 0s can be detected. The greater the number of 0s in the multiplier the faster the operation. Consider a string of k consecutive 1s in the multiplier as shown below.

.....,

$$i + k$$

,  $i + k - 1$ ,  $i + k - 2$ ,....,  $i$ ,  $i - 1$ ,....

k consecutive 1s

by using the following property of binary strings

$$2^{i+k} - 2^{i} = 2^{i+k-1} + 2^{i+k-2} + \dots + 2^{i+1} + 2^{i}$$

(2.1)

The consecutive 1s can be replaced by the following string

.....,

$$i + k+1$$

,  $i + k$ ,  $i + k-1$ ,....,  $i +1$ ,  $i, i - 1$ ,....

....., 0, 1, 0, ...., 0, -1, 0, .....

k-1 consecutive 0s

Addition Subtraction

Now consider a multiplication example in which a positive multiplier has a single block of 1s with at least one 0 at each end, for example  $0\ 0\ 1\ 1\ 1\ 0\ (14)$ . The number of

addition can be reduced by observing that a multiplier in this form can be regarded as the difference of two numbers as follows:

010000 (16) -) 000010 (2) ------

#### 001110 (14)

This was shown in Eq. 2.1 and indicates that the product can be generated by one addition (addition of  $2^4$ ) and one subtraction (subtraction of  $2^1$ ). In the standard notation, the multiplier can be written as

0 0 +1 +1 +1 0

and the recoded multiplier can be written as

#### 0 +1 0 0 0 -1 0

Note that the -1 times the left-shifted multiplicand occurs at 0 to 1 boundaries and +1 times the left-shifted multiplicand occurs at 1 to 0 boundaries as the multiplier is scanned from right to left. The transformation that takes

011111.....0-10 into +10000.....0-10

is often referred as the technique of skipping over 1s. The reasoning is that in cases in which the multiplier has its 1s grouped into a few blocks, only a few versions of the multiplicand need to be added to generate the product hence, the multiplication process

becomes much faster. It can also be shown that the Booth recoded multiplier algorithm works equally well for negative multiplier.

#### 2.4 Modified Booth Algorithm

Modified Booth Algorithm is a multiplication speedup technique that guarantees that an n-bit multiplier will generate at most n/2 partial products [9], [10]. It can multiply two two's complement numbers directly and gives the product also in two's complement form. This represents a multiplication speed increase of almost a factor of 2 over the standard add-shift method.

This new technique is derived from the Booth technique. Recall from the previous discussion of a positive multiplier of  $0\ 0\ 1\ 1\ 1\ 0\ (+14)$ . The number of addition can be reduced by observing that the multiplier in this form can be regarded as the difference of two numbers as shown below.

$2^{5} 2^{4} 2^{3} 2^{2} 2^{1} 2^{0}$  0 1 0 0 0 0 (16) -) 0 0 0 0 1 0 (2)

$Multiplier \rightarrow 0 \quad 0 \quad 1 \quad 1 \quad 1 \quad 0 \quad (14)$

This indicate that the number 0 0 1 1 1 0 (14) has the same value as

$$2^4 - 2^1 = 16 - 2 = 14$$

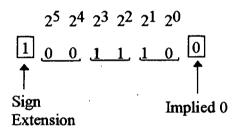

This is true for any number of contiguous 1s, including the case in which there is a single 1 with 0s on either side. The entire concept of bit-pair recoding revolves around this method of regarding a string of 1s as the difference of two numbers. Now returning to the multiplier being discussed and scanning it from right to left, bit by bit. In going from 0  $(2^0)$  to 1  $(2^1)$ , we saw previously that this resulted in subtracting the value of the 1 in that position, in this case -  $2^1$ . Scanning from 1  $(2^1)$  to 1  $(2^2)$  resulted in no change, that is, neither addition nor subtraction. The same is true in scanning from 1  $(2^2)$  to 1  $(2^3)$ . However, in going from 1  $(2^3)$  to 0  $(2^4)$ , we saw that this resulted in an addition of  $2^4$ . There is no change in scanning from 0  $(2^4)$  to 0  $(2^5)$ . The results of scanning this multiplier are as follows:  $2^1$  was subtracted and  $2^4$  was added. The same results can be obtained by looking at pairs of bits in the multiplier in conjunction with the bit that is to the right of the bit pair being considered, as shown below.

That is, bit pair  $2^1$ ,  $2^0$  is examined with an implied 0 to the right of the low-order bit; bit pair  $2^3$ ,  $2^2$  is examined with bit  $2^1$ , bit pair  $2^5$ ,  $2^4$  is examined with bit  $2^3$ . Scanning the bit pairs from right to left and using the rightmost bit of each pair as the column reference for the partial product placement (it is the center bit of the three bits being examined), we obtain the following multiplier bit-pair recoding scheme shown in table 2.1. It should be noted that there are a total of eight possible versions of the multiplicand.

|     | iplier<br>pair | Multiplier bit<br>on the right | Multiplicand<br>multiples to be | Explanation             |

|-----|----------------|--------------------------------|---------------------------------|-------------------------|

| i+1 | i              | <u>i-1</u>                     | added                           |                         |

| 0   | 0              | 0                              | $0 \times multiplicand$         | No string               |

| 0   | 0              | 1                              | + 1 × multiplicand              | End of string           |

| 0   | 1              | 0                              | + 1 × multiplicand              | Single 1 (+2 -1)        |

| 0   | 1              | 1                              | + 2 × multiplicand              | End of string           |

| 1   | 0              | 0                              | - 2 × multiplicand              | Beginning of string     |

| 1   | 0              | 1                              | - 1 × multiplicand              | End/beginning of string |

| 1   | 1              | 0                              | -1 × multiplicand               | Beginning of string     |

| 1 . | 1              | 1                              | $0 \times multiplicand$         | Strings of 1s           |

Table 2.1. Multiplier bit-pair recoding scheme

Fig. 2.2 gives an example of the bit-pair recoding multiplication technique using two 5 bit operands represented in two's complement form.

| Multiplicand X = | 00110 (+6)              |

|------------------|-------------------------|

| Multiplier Y =   | [1] 1 0 0 1 0 [0] (-14) |

| . <b>-</b>       | 111110100               |

|                  | 00000110                |

|                  | 111010                  |

| Product P =      | 1←1110101100 (-84)      |

Fig. 2.2 Multiplication example using bit-pair recoding

#### 2.5 Removal of Sign-bit Extension Circuitry

The modified Booth algorithm for multiplying two binary numbers basically consists of two steps. First to obtain the partial product from the proper version of the multiplicand and second to add these partial products in an appropriate array of full adders considering that summation in an array has to be done with sign bit extension, because it is a signed multiplication. However, if explicit sign extension scheme is observed large amount of circuitry is required merely to accommodate the sign-extension of the partial products. The redundancy of the sign-bit extension can be eliminated by a simple method, i.e., reducing the number of variable inputs to the array, thus reducing the number of full adders involved. Several approaches for removing the sign-extension circuitry from Booth multiplier have been proposed by previous researchers [32], [33].

Let us consider the multiplication of two 8-bit binary numbers using modified Booth algorithm. Since this algorithm scans three bits of the multiplier at a time and retires two of them to generate a partial product, the total number of partial products generated for the 8-bit multiplier is four. If a, b, c, d represents these partial products, then the addition of these partial product is illustrated in Fig. 2.3. Each partial product is shifted two bit positions to the left with respect to the preceding one in accordance with the modified Booth algorithm.

| a <sub>8</sub> | $a_8$      | $a_8$       | <i>a</i> 8 | <i>a</i> 8 | a8         | <b>a</b> 8 | <b>a</b> 8 | а7        | аб | a5        | a4        | a3         | a2 | a1 | <i>a</i> 0 |

|----------------|------------|-------------|------------|------------|------------|------------|------------|-----------|----|-----------|-----------|------------|----|----|------------|

| <b>b</b> 8     | <b>b</b> 8 | <i>b</i> 8  | <i>b8</i>  | <b>b</b> 8 | <i>b</i> 8 | b7         | <i>b6</i>  | b5        | b4 | <i>b3</i> | <i>b2</i> | <b>b</b> 1 | 60 |    |            |

| c <sub>8</sub> | <i>c</i> 8 | <i>c</i> 8  | .08        | с7         | сб         | ·c5        | C4         | <i>c3</i> | c2 | c1        | c0        |            |    |    |            |

| <i>d</i> 8     | <b>d</b> 8 | <b>d</b> 7, | d6         | d5         | d4         | d3         | d2         | d1        | d0 |           |           |            |    |    |            |

|                |            |             |            |            |            |            |            |           |    |           |           |            |    |    |            |

P15 P14 P13 P12 P11 P10 P9 P8 P7 P6 P5 P4 P3 P2 P1 P0 Fig 2.3 Sign extended partial product array Here  $a_8$ ,  $b_8$ ,  $c_8$ ,  $d_8$  are the sign bits. It is seen that the direct implementation of explicit sign extended array will be an uneconomical choice.

Let us assume for simplicity that the arithmetic weight of the  $p_8$  column is 2<sup>0</sup>, i.e., 1. Thus the  $p_{15}$  column represents a weight of 2<sup>7</sup>. Then the sum of the sign and sign extended bits can be written as

Sum =

$$a_8(2^7 + 2^6 + 2^5 + 2^4 + 2^3 + 2^2 + 2^1 + 2^0) + b_8(2^7 + 2^6 + 2^5 + 2^4 + 2^3 + 2^2) + c_8(2^7 + 2^6 + 2^5 + 2^4) + d_8(2^7 + 2^6)$$

=  $a_8(2^8 - 2^0) + b_8(2^8 - 2^2) + c_8(2^8 - 2^4) + d_8(2^8 - 2^6)$

Since  $p_{15}$  is the most significant bit of the product output, module  $2^8$  addition can be used to sum the sign bits. Thus, the sum of the sign bits can be written as

Sum =

$$-a_8(2^0) - b_8(2^2) - c_8(2^4) - d_8(2^6)$$

which expressed as a binary number is

$$Sum = -(0 d_8 0 c_8 0 b_8 0 a_8)$$

(2.2)

The two's complement of the word  $(0 d_g 0 c_g 0 b_g 0 a_g)$  is

$$-(0 \, d_8 \, 0 \, c_8 \, 0 \, b_8 \, 0 \, a_8) = (1 \, \overline{d_8} \, 1 \, \overline{c_8} \, 1 \, \overline{b_8} \, 1 \, \overline{a_8}) + 1 \tag{2.3}$$

When the recoding scheme of Eq. 2.3 is used, the sign extended Booth partial product array appears like the one shown in Fig. 2.4.

$1 \quad \overline{a_8} \quad a_7 \quad a_6 \quad a_5 \quad a_4 \quad a_3 \quad a_2 \quad a_1 \quad a_0$   $1 \quad \overline{b_8} \quad b_7 \quad b_6 \quad b_5 \quad b_4 \quad b_3 \quad b_2 \quad b_1 \quad b_0$   $1 \quad \overline{c_8} \quad c_7 \quad c_6 \quad c_5 \quad c_4 \quad c_3 \quad c_2 \quad c_1 \quad c_0$   $1 \quad \overline{d_8} \quad d_7 \quad d_6 \quad d_5 \quad d_4 \quad d_3 \quad d_2 \quad d_1 \quad d_0$

$p_{15}$   $p_{14}$   $p_{13}$   $p_{12}$   $p_{11}$   $p_{10}$   $p_{9}$   $p_{8}$   $p_{7}$   $p_{6}$   $p_{5}$   $p_{4}$   $p_{3}$   $p_{2}$   $p_{1}$   $p_{0}$

Fig 2.4 Recoded sign extended partial product array

Hence it is seen that elimination of the sign-extension circuitry in a modified Booth algorithm multipliers can be achieved by inverting the MSB of each partial product and adding a logic '1' at every higher significance (including the MSBs). This procedure is equivalent to recoding the MSBs of the partial products as a two's complement number and adding a logic '1' to the most significant full adder in each row of the main array.

#### 2.6 An Architecture Based on Modified Booth Algorithm

Fig. 2.5 represents an 8 by 8 bit multiplier architecture based on the modified Booth algorithm for multiplication of two binary numbers that are in two's complement form [24]. Elimination of the sign extension circuitry is achieved by the procedure described above. The modified Booth encoder (MBE) block in each row operates on three multiplier bits to generate the control signals CM,  $K_1$  and  $K_2$  according to the modified Booth recoding scheme as shown in Table 2.2. In this recoding scheme five possible partial products can be formed: 0, +X, -X, +2X, -2X where X denotes the multiplicand. The selector complementers (SC) in Fig. 2.5 consist of multiplexers which operate on the multiplicand bits to generate 0, X or 2X as partial products depending on

the control signals  $K_1$ ,  $K_2$  and complementers (2-input EX-OR gates) which generate one's complements of these partial products only when CM signal is high. Moreover, these one's complemented partial products are converted to their two's complement form by addition of a logic '1' to their LSBs. The addition of the partial products are accomplished by an array of carry save full adders (FA). The Manchester carry adders (MCA) on the right-hand side and the bottom of the Fig. 2.5 operates on the results coming out of the main array (the array containing SCs and FAs) to generate the final product output.

| М                | BE inpu | its              | MBE outputs    |     | puts | Partial Product | SC output        |

|------------------|---------|------------------|----------------|-----|------|-----------------|------------------|

| Y <sub>i+1</sub> | Y       | Y <sub>i-1</sub> | к <sub>1</sub> | К2  | CM   | Generated       | Z                |

| 0                | 0       | 0                | 0              | 0   | 0    | 0               | 0                |

| 0                | 0       | 1                | 1              | 0   | 0    | +X              | X <sub>i</sub>   |

| 0                | 1       | 0                | 1              | 0   | · 0  | +X              | . X <sub>i</sub> |

| 0                | 1       | 1                | 0              | - 1 | 0    | +2X             | X <sub>i-1</sub> |

| 1                | 0       | Q                | 0              | . 1 | 1    | -2X             | x <sub>i-1</sub> |

| 1                | 0       | 1                | 1              | 0   | 1    | -X              | Σ <sub>i</sub>   |

| 1                | 1       | 0                | 1              | 0   | 1    | -X              | $\bar{x}_i$      |

| 1                | , 1     | 1                | 0              | 0   | 0    | 0               | 0                |

Fig 2.5 : An 8 by 8 bit modified Booth multiplier arrray (Horizontal Controls and vertical multiplicand routings are omitted for clarity)

## Chapter 3

## **Testability of the Multiplier**

#### **3.1 Introduction**

With the increasing complexity of VLSI circuits, it is difficult to test them unless due consideration to testability is given at the early stages of design. The high device-topin ratio severely limits the controllability of internal signal lines in VLSI chip [19]. Also, there exists a large number of faults of various types, many of which cannot be modelled by the traditional stuck-at fault model. Test pattern generation and verification procedures are becoming very costly or even computationally infeasible to implement [18]. However, VLSI circuits like array multipliers having regular iterative structure have been shown to be easily testable by slight modification of the conventional design [20]. The multiplier architecture presented in Chapter 2 will be modified in this chapter in order to convert it to an easily testable one.

#### **3.2 Testing Approach**

The objective of the testing approach adopted in this research is to exhaustively test the full-adders (FAs), Manchester carry adders (MCAs) and modified Booth encoders (MBEs). Such a test set will be applicable to any arbitrary logic implementation of these cells. The fault model used in this research assumes:

a) at most one basic cell in an array multiplier is faulty at a time;

- b) the fault is a permanent fault (i.e. the fault permanently changes the circuit's logic characteristics);

- c) the fault may alter the cell's output functions in any arbitrary way, as long as the faulty cell remains combinational circuit.

It is necessary to modify the design of the modified Booth encoders with a significant increase in complexity and gate count in order to generate exhaustive test set for the selector-complementers (SCs). However, Takach and Jha [21] have shown that hardware overhead reduction is possible for array multipliers if a fault model based on single (stuck-at) faults is used instead of the single cell fault model. They have also shown that a set of test vectors which detect all single stuck-at faults in a gate level carry-save multiplier can be readily adopted to detect all detectable single stuck-at, transistor stuck-on and stuck-open faults in a DCVS implementation of the multiplier. Therefore, the selector-complementers will be tested for single stuck-at faults only. Moreover, although MBEs are eventually exhaustively tested, this testing does not guarantee the fault propagation to the primary outputs of the array. Due to this, equivalent gate level circuit for MBE will be tested for single stuck-at faults.

#### 3.3 Modification of the Architecture for Testability

The main challenge in testing array multipliers is the difficulty of controlling the inputs of internal adder cells from the primary inputs, namely the multiplier (Y) and multiplicand (X) inputs. In fact, some patterns cannot be applied to some adders cells. To overcome this problem, extra inputs and sometimes extra hardware is added to enhance controllability and observability of the internal signal lines in VLSI circuits.

A testable architecture for an  $6 \times 8$  bit multiplier is shown in Fig. 3.1. Comparing to its non testable version, this architecture has 4 extra controllable inputs  $e_1$ ,  $e_2$ ,  $e_3$ ,  $e_4$ ,

$x_{-1}$  and  $y_{-1}$  to enhance the controllability of various cells. For normal multiplication operation these extra inputs will have the following logic values:  $e_1 = 0$ ,  $e_2 = 0$ ,  $e_3 = 1$ ,  $e_4 = 1$ ,  $x_{-1} = 0$  and  $y_{-1} = 0$ .

#### 3.4 Testing the Individual Cells

In this section, the patterns required for testing the various individual cells of the multiplier for single stuck-at faults are derived.

### 3.4.1 Testing of MBEs for Single Stuck-at Fault

The logic diagram of the modified Booth encoder used in the multiplier is shown in Fig. 3.2.

Figure: 3.2 Gate level design of the Modified Booth Encoder (MBE)

The circuit has twelve nodes and so twenty four possible stuck-at faults. For the three primary inputs there will be eight possible test vectors which will be identified as  $t_0$  to  $t_7$ , where the suffix is the decimal equivalent of the binary numbers ( $y_{I-1}y_{I}y_{I+1}$ ). The fault coverage is conveniently displayed in the fault-matrix shown in Table 3.1. The tick against each test indicates the fault covered by that test.

| <u> </u>   |              |              |              |              |              |                  |    |    |    |    |              |    |              |    |    |    |    |    |              |              |          |                |    |         |

|------------|--------------|--------------|--------------|--------------|--------------|------------------|----|----|----|----|--------------|----|--------------|----|----|----|----|----|--------------|--------------|----------|----------------|----|---------|

| Test       | <b>y</b> i-1 | <b>y</b> i-1 | yi           | yi           | Уi+1         | y <sub>i+1</sub> | A  | A  | в  | в  | с            | с  | D            | D  | Е  | Е  | F  | F  | к1           | ĸı           | к2       | к <sub>2</sub> | СМ | СМ      |

| an an      | /0           | /1           | /0           | /1           | /1           | /1               | /0 | /1 | /0 | /1 | /0           | /1 | /0           | /1 | /0 | /1 | /0 | /1 | /0           | /1.          | /0       | /1             | /0 | /1      |

| 40         |              | 1            |              | √            |              | V                |    |    |    |    |              |    |              |    |    | 1  |    | 1  |              | 1            |          | 1              |    | 1       |

| <b>l</b> 1 |              | $\checkmark$ |              | 1            | $\checkmark$ |                  |    |    | √  |    | $\checkmark$ |    | $\checkmark$ |    |    |    | 1  |    |              | $\checkmark$ | 1        |                | 1  |         |

| 12         |              | $\checkmark$ | $\checkmark$ |              |              | $\checkmark$     |    |    |    |    |              |    |              |    |    | V  |    | 1  | $\checkmark$ |              |          | 1              |    | 1       |

| łz         |              | $\checkmark$ | $\checkmark$ |              | $\checkmark$ |                  |    |    |    |    |              | 1  | 1            | _  |    | √. |    | √  | √            |              |          | 1              | 1  |         |

| 4          | $\checkmark$ |              |              | $\checkmark$ |              | $\checkmark$     |    |    |    | V  |              |    |              |    |    | √  |    | 1  | 1            |              |          | •              | Y  | √       |

| 5          | $\checkmark$ |              |              | √'           | $\checkmark$ |                  |    |    |    | 1  | _            |    | 1            |    |    | √  |    | 1  | 1            |              |          | 1              | √  | V       |

| 4          | $\checkmark$ |              | 1            |              |              |                  | V  |    |    |    |              |    | -            |    |    |    |    |    | V            | 1            | 1        |                | v  | V       |

| 17         | 1            |              | 1            |              |              |                  |    | 1  |    |    |              |    |              | 7  |    | 1  |    |    |              | √            | <u>У</u> | 1              |    | _¥<br>√ |

## Table 3.1 Fault matrix for the MBE logic circuit

From the above fault matrix it is seen that the test vectors  $t_1$ ,  $t_3$ ,  $t_6$  and  $t_7$  are the essential tests. These four essential tests cover all the faults except  $y_{I+1}/1$  and B/1. A single test that covers both of these faults is  $t_4$ . Hence a set of test patterns for the inputs  $(y_{I-1}y_Iy_{I+1})$  of the MBE of Fig. 3.2 that detect any single stuck-at fault in the MBE is {001, 011, 100, 110, 111}.

### 3.4.2 Testing of the SCs for Single Stuck-at Fault

The logic diagram of the selector –complementer block is shown in Fig. 3.3. It has a total of five inputs. However, for testing of single stuck-at fault we will derive fault matrix for only the selector part. This is because the complementer part is nothing but an EX-OR gate whose one input is the complement signal CM and the other is output of selector circuit  $Z_i$ . Since output of an EX-OR gate inverts due to inversion of any one of its inputs so if we can test only the selector part for single stuck-at fault we may declare that this fault will propagate to the SC output due to that fault propagation property of EX-OR gate. This criterion will also reduce the number of input test vectors of SC blocks from twenty five to sixteen. These will be identified as  $t_0$  to  $t_{15}$ , where suffix is the decimal equivalent of the binary number ( $K_1x_iK_2x_{I-1}$ ). Table 3.2 shows the fault matrix.

Fig. 3.3 Gate Level Design of the Selector-Complementer Block

| 14<br>2                                               |                   |                   |      |                   |      |                          |                     |                     |     |     |     |          |                   |                   |

|-------------------------------------------------------|-------------------|-------------------|------|-------------------|------|--------------------------|---------------------|---------------------|-----|-----|-----|----------|-------------------|-------------------|

| Test                                                  | к <sub>1</sub> /0 | к <sub>1</sub> /1 | K2/0 | K <sub>2</sub> /1 | x;/0 | <b>x</b> <sub>i</sub> /1 | x <sub>i-1</sub> /0 | x <sub>i-1</sub> /1 | E/0 | E/1 | F/0 | F/1      | Z <sub>i</sub> /0 | Z <sub>i</sub> /1 |

| to_                                                   |                   |                   |      |                   |      |                          |                     |                     |     | 1   |     | √        |                   | ا                 |

| t <sub>1</sub>                                        |                   |                   |      | 1                 |      |                          |                     |                     |     | √   |     | <b>√</b> |                   | √                 |

| t2                                                    |                   |                   |      |                   |      |                          |                     | √                   |     | 1   |     | √        |                   | √                 |

| t3                                                    |                   |                   | √    |                   |      |                          | 1                   |                     |     | 1   | 1   |          | 1                 |                   |

| t <sub>4</sub>                                        |                   | √                 |      | -                 |      |                          |                     |                     |     | V   |     | 1        |                   | V                 |

| t5                                                    |                   | √                 |      | V                 |      |                          |                     |                     |     | √   |     | √        |                   | √                 |

| t <sub>6</sub>                                        |                   | V                 |      |                   |      |                          |                     | 1                   |     | V   | V   | √        |                   | √                 |

| t7                                                    |                   | V                 | V    |                   |      |                          | √                   |                     |     | V   |     |          | √                 |                   |

| tg                                                    |                   |                   |      |                   |      | V                        | -                   |                     |     | V   |     | 1        |                   | V                 |

| tg                                                    |                   |                   |      | 1                 |      | 1                        |                     |                     |     |     |     | √        |                   | V                 |

| t <sub>10</sub>                                       |                   |                   |      |                   |      | 1                        |                     | V                   |     | V   |     | √        |                   |                   |

| t <sub>10</sub>                                       |                   |                   | . 🗸  |                   |      | 1                        | V                   |                     |     | V   | V   |          | V                 |                   |

| t <sub>12</sub>                                       | V                 |                   | -    |                   | 1    |                          |                     |                     | 1   |     |     | V        | 1                 |                   |

| t <sub>13</sub>                                       | V                 |                   |      | V                 | V    |                          |                     |                     | V   |     |     | √        | 1                 |                   |

| t <sub>13</sub><br>t <sub>14</sub><br>t <sub>15</sub> | √                 |                   |      |                   | V    |                          |                     | 1                   | √   |     | •   | √        | V                 |                   |

| t <sub>15</sub>                                       | V                 | ·                 | V    |                   | 1    |                          | √                   |                     | √   |     | √   |          | 1                 |                   |

**Table 3.2 Fault Matrix for the Selector Block**

Identifying the indistinguishable faults and dominant faults in the fault matrix of Table 3.2, it is found that the test vectors needed to test any single stuck-at fault are  $t_2$ ,  $t_7$ ,  $t_8$  and  $t_{13}$ . So the set of test pattern for the inputs ( $K_1x_iK_2x_{I-1}$ ) of the selector circuit to detect any single stuck-at fault is {0010, 0111, 1000, 1101}.

#### 3.5 Testing the Multiplier

In this section, a set of test vectors for testing the multiplier will be derived. The vectors will cover the exhaustive testing of the FAs, MCAs, MBEs as well as the stuck-at faults in the selector-complementers.

#### 3.5.1 Test Vectors

A set of test vectors for detecting all single stuck-at faults in a larger version of the multiplier of Fig. 3.1 is shown in Table 3.3. An 8-bit multiplicand X and a 8-bit multiplier Y are shown with their LSBs to the right most position. The underlined bits have to be replicated for generating the test vectors for multipliers with larger operand wordlenths.

#### 3.5.2 Exhaustive Testing of the Full-Adders

The first twelve test vectors  $t_1-t_{12}$  of Table 3.3 set up the patterns required for exhaustive testing of all the full-adders as explained in the following steps:

1) The test vector  $t_1$  applies 000 to most of the full-adders. However, the full adders affected by the inverted sign bits of the partial products receive 100. Test vector  $t_2$  applies 000 to these full-adders.

2) Application of pattern 111 to all the full-adders is accomplished with the vectors  $t_3$  and  $t_4$ .

3) The vector  $t_5$  applies 100 to all the full-adders except the one labeled 'FA1' in the second row of Fig. 3.1 which receives the pattern 010.  $t_6$  applies 100 to FA1.

4) The vector t7 applies 011 to all the full-adders except the one labeled 'FA1' which receives the pattern 101. tg applies 011 to FA1.

| Vectors         | Х                      | $\mathbf{x}_{1}$ | Y                 | У-1 | $e_4e_3e_2e_1$ |  |

|-----------------|------------------------|------------------|-------------------|-----|----------------|--|

| t <sub>1</sub>  | <u>0000 0000</u>       | 0                | 0000 0000         | 0   | 0000           |  |

| t2              | 1000 000 <u>0</u>      | 0                | <u>01</u> 01 0101 | 0   | 0000           |  |

| t3              | 1111 111 <u>1</u>      | 1                | <u>01</u> 01 0101 | 0   | 1111           |  |

| t <sub>4</sub>  | 1000 000 <u>0</u>      | 0                | <u>10</u> 10 1010 | 1   | 1111           |  |

| t5              | <u>0000 0000</u>       | 0                | <u>1</u> 111 1111 | 0   | 1100           |  |

| <sup>t</sup> 6  | <u>0000 0000</u>       | 0                | <u>0011</u> 0011  | 1   | 0011           |  |

| t7              | 1111 111 <u>1</u>      | 1                | <u>01</u> 01 0011 | 0   | 0011           |  |

| tg              | 1111 111 <u>1</u>      | 1                | <u>0100</u> 0100  | 1   | 1100           |  |

| tg.             | 0101 01 <u>01</u>      | 0                | <u>1100</u> 1100  | 1   | 0110           |  |

| t10             | 010101 <u>01</u>       | 0                | <u>0011</u> 0011  | 0   | 1001           |  |

| t <sub>11</sub> | 1111 111 <u>1</u>      | 1                | <u>0011</u> 0011  | 0   | 0011           |  |

| t <sub>12</sub> | 1111 111 <u>1</u>      | 1                | <u>1100</u> 1100  | 1   | 1100           |  |

| t <sub>13</sub> | 0000 0000              | 0                | <u>10</u> 10 1010 | 1   | 1100           |  |

| t <sub>14</sub> | 1111 111 <u>1</u>      | 1                | <u>10</u> 10 1010 | 1   | 0000           |  |

| t <sub>15</sub> | 111 1111 <u>1</u>      | 0                | <u>1001</u> 1001  | 1   | 1111           |  |

| t <sub>16</sub> | 111 1111 <u>1</u>      | 0                | 0110 0110         | 0   | <u>,</u> 0000  |  |

| t <sub>17</sub> | <u>0000 0000</u>       | 0                | 0110 0110         | 0   | 1111           |  |

| t <sub>18</sub> | 1111 111 <u>1</u>      | 1                | <u>1001</u> 1001  | 1   | 1001           |  |

| t19             | -<br>1111 111 <u>1</u> | 1                | <u>1</u> 111 1111 | 1   | 0000           |  |

Table 3.3 A set of test vectors for an 8  $\times$  8 bit multiplier

رب

\* The bits to be replicated for larger multipliers are underlined

5) to applies 001 and 110 to alternate full-adders,  $t_{10}$  applies 110 and 001 to alternate full-adders in each row.

6) t<sub>6</sub> applies 010 to the full-adders in the even rows except FA1. It was seen in step 3 that FA1 gets 010 by t<sub>5</sub>. Application of 010 to the full-adders in the odd rows is accomplished with the test vector  $t_{11}$ .

7) tg applies 101 to the full-adders in the even rows except FA1. It was seen in step 4 that FA1 gets 101 by t7. Application of 101 to the full-adders in the odd rows is accomplished with the test vector  $t_{12}$ .

Table 3.4 shows the results of exhaustive testing of the full-adders.

| Pattern applied to FAs | Test vector required            |

|------------------------|---------------------------------|

| 000                    | t <sub>1</sub> , t <sub>2</sub> |

| 111                    | t3, t4                          |

| 100                    | t5, t6                          |

| 011                    | t7, t8                          |

| 001                    | t9, t <sub>10</sub>             |

| 110                    | t9, t <sub>10</sub>             |

| 010                    | t5, t6, t11                     |

| 101                    | t7, t8, t12                     |

Table 3.4 Exhaustive testing of the FAs

Now let us consider how the effect(s) of a fault in a full-adder is transmitted to the primary outputs (observable outputs) of the multiplier. The sum output of a full-adder is

the parity (EX-OR) of the three input bits. Therefore, if one of these three inputs is inverted due to appearance of a faulty signal then the sum output of the full-adder is also inverted. The carry output may or may not be inverted depending on the logic values of the other two inputs. This is also true for manchester carry adder (MCA), because it realizes the same logic function as a full-adder. Since all the full-adders are exhaustively tested, the effect of a fault in a full-adder is transmitted to it's output(s). The two outputs of each full-adder of Fig. 3.1 are connected to the primary outputs of the multiplier through two different chains of three input EX-OR gates (of FAs and final MCAs). Hence the effect of a fault in a full-adder is transmitted to the observable output(s).

#### 3.5.3 Exhaustive Testing of the Manchester Carry Adders

All the manchester carry adders are exhaustively tested using a subset of test vectors from Table 3.3. The combinations of test vectors that apply various patterns to all the manchester carry adders are listed in Table 3.5. The effect of a fault in any MCA is transmitted to it's sum output which is a primary output of the multiplier.

| Table 5.5 Exhaustive testing of the MCAs |                                 |  |

|------------------------------------------|---------------------------------|--|

| Pattern applied to MCAs                  | Test vector required            |  |

| 000                                      | t <sub>1</sub> , t <sub>2</sub> |  |

| 111                                      | t3, t4                          |  |

| 101                                      | t3, t5, t7                      |  |

| 011                                      | t7, t <sub>13</sub>             |  |

| 010                                      | t6, t8, t <sub>14</sub>         |  |

| 100                                      | t <sub>6</sub> , t8             |  |

| 001                                      | t9, t10, t11,t12, t15, t16      |  |

| 110                                      | t9, t10, t11,t12, t15, t16      |  |

Table 3.5 Exhaustive testing of the MCAs

# 3.5.4 Testing of the Modified Booth Encoders

The modified Booth encoders are tested in two ways. First they are exhaustively tested However unlike the FAs and MCAs, exhaustive testing of the MBEs does not necessarily guarantee the transmission of the effect of a faults in an MBE to the primary outputs of the multiplier. That is why the MBE block is also tested for single stuck-at faults.

# 3.5.4.1 Exhaustive Testing

The modified Booth Encoders are exhaustively tested by the vectors shown in Table 3.6.

| Pattern applied to MBEs | Test vector required              |

|-------------------------|-----------------------------------|

| 000                     | t <sub>1</sub>                    |

| 010                     | t <sub>2</sub>                    |

| 101                     | t <sub>4</sub>                    |

| 111                     | t5, t6                            |

| 011                     | t <sub>11</sub> , t <sub>12</sub> |

| 100                     | t <sub>11</sub> , t <sub>12</sub> |

| 001                     | <sup>t</sup> 15, <sup>t</sup> 16  |

| 110                     | t <sub>15</sub> , t <sub>16</sub> |

## Table 3.6 Exhaustive testing of the MBEs

### 3.5.4.2 Testing for Single Stuck-at Fault

Unlike the full-adders and manchester carry adders, exhaustive testing of the MBEs does not necessarily guarantee the transmission of the effect of a fault in an MBE to the primary output of the multiplier. Fault propagation depends on the type of fault and its effect on the output of the MBE. Also, note from Figures 3.1 and 3.2 that the output of an MBE in any row, namely CM,  $K_1$ , and  $K_2$  are inputs to the selector-complementers (SC) in that row (fan-out nodes). In the rest of this sub-section, the test vectors which propagates any single stuck-at fault in an MBE to the primary outputs of the multiplier will be derived.

It was shown in Section 3.4.1 that a set of test patterns for the inputs  $(y_{i-1}y_iy_{i+1})$ of the MBE of Fig. 3.2 that detect any single stuck-at fault in the MBE is {001, 011, 100, 110, 111}. Note from Fig. 3.2 that every input to the MBE has a fan-out of three. This means that the effect of a fault at one of the input nodes might propagate to more than one output of the faulty MBE. Because of the fan-outs at the outputs of the MBE these faulty signals from MBE might propagate through two different paths, i.e. the SC and the chains of carry-save adders, and then reconverge at the final adders (MCAs). Also, note from Fig. 3.1 that the adjacent MBEs share one multiplier bit. Therefore, a fault on one of the shared multiplier bits might affect both the MBE sharing that bit resulting in transmission of the fault through both the MBEs and subsequent reconvergence in the array of FAs and MCAs. It can be verified that because of these reasons some path sensitive patterns (mentioned above) applied to the MBEs for detecting some single stuck-at faults result in negative reconvergence [18] of the fault effects unless these patterns are accompanied by application of appropriate patterns to the multiplicand. It was extensively verified in this research that the test vectors  $t_{11}$ ,  $t_{12}$ ,  $t_{15}$ ,  $t_{16}$  and  $t_{19}$ apply all the necessary patterns to all the MBEs along with appropriate multiplicand

patterns so that any single stuck-at fault in the MBE is propagated to the primary outputs of the multiplier.

JU

### 3.5.5 Test Vectors for SCs

As mentioned in Section 3.4.2, a set of test patterns for the inputs  $(K_1x_iK_2x_{i-1})$  of the selector block of Fig. 3.3 that detect any single stuck-at fault in the selector is {0010, 0111, 1000, 1101}. The selector in any row have two common input nodes, namely K<sub>1</sub>, and K<sub>2</sub> (fan-out nodes). It is verified that the vectors t<sub>2</sub>, t<sub>3</sub>, t<sub>5</sub>, t<sub>17</sub> and t<sub>18</sub> sensitize the single stuck-at faults at these nodes and propagate them to the output of the selectors. Each of this selector output is passed though a complementer (an EX-OR gate) whose other input is the MBE output CM (complement signal). The effect of a single stuck-at fault at one of the multiplicand bits is propagated through the outputs of the SCs in that column to one of the inputs of the full-adders in that column. Now the sum output or both the sum and carry outputs of a full-adder are inverted due to a faulty input signal. Each output of every full-adder is connected to the primary outputs of the multiplier through a chain of 3-input EX-OR circuits (of FAs and final MCAs). Thus, these faults are essentially propagated to the primary outputs of the multiplier.

### 3.6 Calculation of Overhead

#### 3.6.1 Hardware Overhead

The testable design of the multiplier presented earlier does not require any extra logic compared to the original design presented in Chapter 2. However, the testable version requires four extra inputs which increases the number of input pins of the multiplier chip. For a large multiplier, e.g.,  $32 \times 32$  bit multiplier the penalty in terms of extra pins will not be as severe as for a multiplier of small operand wordlengths, e.g.,  $8 \times 8$

bit. The lines carrying the above extra signals will increase the silicon area of the testable multiplier chip compared to the non-testable design.

# 3.6.2 Delay Overhead

Compared to the non-testable design, the testable multiplier will not have an extra logic gate delay. However, there will be some additional delay due to the extra wiring capacitances associated with various nodes connected to the extra inputs.

#### 3.7 Summary

The testable design of the multiplier presented in this chapter requires only test vectors to test all single stuck-at faults. Also, the full-adders, Manchester carry adders and the modified Booth encoders are exhaustively tested. The numbers of test vectors for any larger multiplier will still remain the same, i.e., 19. Therefore, this testable multiplier can be said to be C-testable [28].

# Chapter 4

# **VHDL** Modeling of the Multiplier

#### **4.1 Introduction**

Design of VLSI circuits entirely at custom level is very time consuming and costly. Such a design for a target process cannot be reused for fabrication even in a scaled down version of the same process. So, to get versatility and portability, high level languages are being used to design process independent VLSI circuits. One of the recent methodology is the introduction of VHDL (VHSIC Hardware Description Language). It not only allows the design of process independent VLSI circuits, but also the automation of the complete design process. In this chapter, the design of a parameterizable and easily testable multiplier is presented using VHDL. Because of the use of VHDL, it will be possible to generate multiplier layouts for various target processes and also program FPGAs (Field Programmable Gate Arrays), CPLDs (Complex Programmable Logic Devices) from various vendors. The capabilities of VHDL to generate arbitrary n-bit modules is exploited in this chapter in designing the parameterizable multiplier.

#### 4.2 Partitioning

The first step toward developing a VHDL code is to partition the design into simpler modular blocks. The multiplier architecture presented in Fig. 3.1 has a regular structure which is very convenient for high level coding. Only four different types of basic cells, viz., modified Booth encoder (MBE), selector-complementer (SC), full-adder

Fig. 4.1 Partitioning the multiplier into modular blocks

(FA) and manchester carry adder (MCA) can be identified in this multiplier. However, considering the interconnection of these cells, the whole multiplier is partitioned into a few parameterized blocks each of which is composed of a number of these basic cells. The multiplier architecture of Fig. 3.1 can be redrawn as shown in Fig. 4.1 and contains the following modular blocks:

- (i) Modified Booth encoder (MBE)

- (ii) sc\_n

- (iii) n\_adder

- (iv) adder\_sc\_n

- (v) n\_mca

The first one, i.e., the MBE is a single modified Booth encoder. This component has to be instantiated as many times as required depending on the number of multiplier bits  $n_y$ . The exact number of instantiation required is termed as the *depth* of the multiplier and is given by

depth =

$$n_y/2$$

for even  $n_y$  (4.1)

( $n_y+1$ )/2 for odd  $n_y$ .

The block  $sc_n$  is composed of  $(n_x+1)$  number of selector-complementers, where  $n_x$  is the number of bits in the multiplicand. As shown in Fig. 4.1, this block is used in the first two rows of the multiplier array corresponding to the first two rows of selector-complementers in the architecture of Fig. 3.1. The next block in the modular array of Fig. 4.1 is the *n\_adder* block corresponding to the first row of full adders of the multiplier array of Fig. 3.1. This block consists of  $n_x$  number of full adders. The block *adder\_sc\_n* is a combination of one row of SCs followed by one row of FAs. It consists of  $(n_x+1)$  number of selector-complementers and  $n_x$  number of full adders. This block is used as many times as required after the first row of full-adders. The exact number of *adder\_sc\_n* blocks depends on the depth of the multiplier and is determined from the number of bits in the multiplier ( $n_y$ ) using equation no. 4.1. The next block in the modular array of Fig.

4.1 is the  $n_{mca}$  block which consists of (depth\*2+n<sub>x</sub>-1) manchester carry adders. This block in Fig. 4.1 corresponds to all the MCAs at the final stage of the multiplier array shown in Fig. 3.1.

#### 4.3 Design Hierarchy

The VHDL code of the multiplier is at the top level of the design hierarchy. The hierarchy is shown in Fig. 4.2. In the top level VHDL code, all the modular blocks mentioned above are instantiated as many times as required depending on the operand wordlengths. For the modified Booth encoders, the code of only one MBE cell is written in VHDL. In the top level code, this block is instantiated a number of times equal to the *depth* of the multiplier. The VHDL codes of the blocks  $sc_n$ ,  $n_adder$  and  $adder_sc_n$  are written such that they are already parameterized on the value of  $n_x$ . Two instantiations of  $sc_n$  and one instantiation of  $n_adder$  are made in the VHDL code of the multiplier. Number of instances of  $adder_sc_n$  in the top level code depends on  $n_y$ . The VHDL code of the block  $n_mca$  is written such that it is already parameterized completely on the value of both  $n_x$  and  $n_y$ . Only one instantiation of this block is made in the top level VHDL code of the multiplier.

#### Fig. 4.2 Design Hierarchy

#### 4.4 VHDL Model

In this section, the VHDL codes developed for all the modular blocks discussed in section 4.2 are presented.

<u>5</u>)

#### 4.4.1 The Modified Booth Encoder

As mentioned before, the number of modified booth encoders in the multiplier array depends on the number of bits  $(n_y)$  in the multiplier (Y). The VHDL code for a single modified Booth encoder is developed first. Then in the top level VHDL code of the multiplier, the required number of modified Booth encoders is specified as one of the generics *depth* and then instantiated [2], [4]. The logic functions performed by the modified Booth encoder shown in Fig. 3.2 are as follows:

$$\mathbf{K}_{1} = \mathbf{y}_{i-1} \oplus \mathbf{y}_{1} \tag{4.2}$$

$$K_{2} = y_{i-1} y_{i} \overline{y}_{i+1} + \overline{y}_{i-1} \overline{y}_{i} y_{i+1}$$

(4.3)

$$CM = y_{i-1}y_i \cdot y_{i+1} = y_{i-1}y_{i+1} + y_i y_{i+1}$$

(4.4)

The VHDL code of a single modified Booth encoder is given below:

```

-- Modified Booth's encoder

-- For C-testable Modified Booth's Array multiplier

library IEEE;

use IEEE.std_logic_1164.all;

```

entity mod\_both\_encoder is

port(y\_i\_1, y\_i, y\_i\_2: in std\_logic;

K1, K2, CM: out std\_logic

);

end mod both encoder;

architecture dataflow of mod\_both\_encoder is begin

$K1 \le y_i_1 x \text{ or } y_i;$

$K2 \le (y_i_1 \text{ and } y_i \text{ and } (not y_i_2)) \text{ or }$

((not y\_i\_1) and (not y\_i) and y\_i\_2); CM <= (y\_i\_2 and (not y\_i)) or ((not y\_i\_1) and y\_i\_2); end dataflow;

configuration cfg\_mod\_both\_encoder of mod\_both\_encoder is

for dataflow

end for;

end cfg\_mod both encoder;

# 4.4.2 The sc\_n

This block consists of a number of selector-complementers depending on the number of bits  $(n_x)$  in the multiplicand (X). There are  $(n_x+1)$  selector-complementers in this block including the leftmost selector-complementer whose output is complemented. In the VHDL code of  $sc_n$ , the number of bits in the multiplicand is explicitly specified as one of the generics, nx. The VHDL code for the entire  $sc_n$  block is written and two instantiations of this are made in the top level VHDL code of the multiplier as per Fig. 4.1. The logic function performed by one selector-complementer shown in Fig. 3.3 is given by

$$Z_i = K_1 X_i + K_2 X_{i-1}$$

The VHDL code of the sc *n* block is given below:

-- Selector-complementer -- Generic model with N-bit size -- For C-testable Modified Booth's Array multiplier library IEEE; use IEEE.std logic 1164.all; (4.5)

```

entity sc n is

generic (nx : integer := 8);

port(X : in std_logic_vector (nx-1 downto 0);

CM, K1, K2, X_1 : in std_logic;

Z : out std logic vector (nx downto 0)

);

end sc_n;

architecture rtl of sc n is

begin

process (X,CM,K1,K2,X_1)

variable r in : std_logic;

variable y : std_logic;

begin

for I in nx downto 0 loop

if I = 0 then

r in := X_1;

else

r in := X(I-1);

end if;

y := (X(I) \text{ and } K1) \text{ or } (K2 \text{ and } r_in);

if I = nx then

Z(I) \leq not(CM xor y);

else

Z(I) \leq CM xor y;

end if;

end loop;

end process;

end rtl;

configuration cfg_sc n of sc n is

for rtl

end for;

end cfg sc n;

```

### 4.4.3 The n\_adder

As mentioned in section 4.2, the number of full adders in the  $n_adder$  block is  $n_x$ , which is explicitly specified in the VHDL code as one of the generics, nx. One instantiation of this block is made in the top level VHDL code of the multiplier in

accordance with Fig. 4.1. The logic functions performed by a single 1-bit full-adder is as follows:

$$SUM = A \oplus B \oplus C \tag{4.6}$$

(4.7)

$$CARRY = AB + BC + CA$$

Where, A, B and C are the three inputs to the full-adder.

The VHDL code of the block  $n_adder$  is shown below:

```

-- Generic N number of 1-bit Full adder

-- For C-testable Modified Booth's Array multiplier

library IEEE;

use IEEE.std logic 1164.all;

entity n adder is

generic (nx : integer := 8);

port(A, B, Cin: in std logic_vector (nx-1 downto 0);

Sum, Cout: out std_logic_vector (nx-1 downto 0));

end n adder;

architecture rtl of n adder is

begin

process (A, B, Cin)

begin

Sum <= A xor B xor Cin;

Cout <= (A and B) or (B and Cin) or (Cin and A);

end process;

end rtl;

configuration cfg n adder of n adder is

for rtl

end for;

end cfg n adder;

```

#### 4.4.4 The adder\_sc\_n

In this block, the number of selector-complementers is  $(n_x+1)$  in a row and the number of full adders is  $n_x$  in the following row. One of the inputs of all the full-adders in this block comes from the outputs of the selector-complementers of the same block except the leftmost one. In the VHDL code of the *adder\_sc\_n* block, *nx* is specified as a generic. The VHDL code of the block *adder sc\_n* is given below:

```

-- Combined selector-complementer and adder

-- Generic model with N-bit size

-- For C-testable Modified Booth's Array multiplier

library IEEE;

use IEEE.std logic 1164.all;

entity adder sc n is

generic (nx : integer := 8);

port(A, B, X: in std logic vector (nx-1 downto 0);

CM, K1, K2, X 1: in std logic;

Z not: out std logic;

Sum, Cout: out std logic vector (nx-1 downto 0));

end adder sc n;

architecture rtl of adder sc n is

signal Z : std logic vector (nx-1 downto 0);

begin

process (A, B, CM, K1, K2, X 1)

variable r_in, y : std_logic;

begin

for I in 0 to nx loop

if I = 0 then

r_in := X_1;

else

r in := X(I-1);

end if;

if I < nx then

Z(I) \leq (X(I) \text{ and } K1) \text{ or } (K2 \text{ and } r \text{ in});

else

y := (X(I) \text{ and } K1) \text{ or } (K2 \text{ and } r \text{ in});

end if;

end loop;

```

The following part is for adder. Sum  $\leq$  A xor B xor Z; Cout <= (A and B) or (B and Z) or (Z and A); Z not <= (not y);end process; end rtl; configuration cfg\_adder\_sc\_n of adder\_sc\_n is

for rtl

end for;

end cfg adder sc n;

# 4.4.5 The n\_mca

This block consists of a number of manchester carry adders, depending on the number of bits  $(n_x)$  in the multiplicand and the number of modified Booth encoders (depth) which is dependent on the number of bits  $(n_y)$  in the multiplier. The exact number of manchester carry adders in this block is (depth\*2+  $n_x -1$ ). In the VHDL code of the block  $n_mca$ , the numbers nx and depth are explicitly specified as generics in order to generate the parameterized manchester carry adder chain. The manchester carry adders often employ some form of fast carry propagation scheme [11] and are implemented differently than the carry save adders (full-adders) used in the array. However, both these adders perform the same logic functions and therefore may be regarded to be the same from the point of view of logic functionality. The VHDL code of the block  $n_mca$  is shown below:

-- Carry Adder Chain -- For C-testable Modified Booth's Array multiplier

library IEEE; use IEEE.std\_logic\_1164.all;

```

entity n mca is

generic (nx : integer := 8; ny : integer := 10; depth :

integer := 5;

port(A, B : in std_logic vector (depth*2+nx-2 downto 0);

e1 : in std logic;

P : out std logic vector (depth*2+nx-1 downto 0));

end n mca;

architecture rtl of n mca is

begin

process (A, B, e1)

variable Cin, Cout : std logic;

begin

for I in 0 to depth*2+nx-2 loop

if I = 0 then

Cin := el;

else

Cin := Cout;

end if; ·

P(I) \leq A(I) \text{ xor } B(I) \text{ xor } Cin;

Cout := (A(I) \text{ and } B(I)) or (B(I) \text{ and } Cin)

or (Cin and A(I));

end loop;

P(depth*2+nx-1) <= (not Cout);</pre>

end process;

end rtl;

configuration cfg n mca of n mca is

for rtl

end for;

```

42

#### 4.4.6 The Multiplier

end cfg n mca;