# DESIGN AND ANALYSIS OF A SINGLE PHASE SINGLE SWITCH ĈUK AND SEPIC AC-DC CONVERTER WITH IMPROVED PERFORMANCE

By

#### Md. Shamsul Arifin

A Thesis submitted to the Department of Electrical and Electronic Engineering in Partial Fulfillment of the requirements for the Degree of

MASTER OF SCIENCE (M.SC.) IN ELECTRICAL AND ELECTRONIC ENGINEERING

DEPARTMENT OF ELECTRICAL AND ELECTRONIC ENGINEERING BANGLADESH UNIVERSITY OF ENGINEERING AND TECHNOLOGY January 2016

## **APPROVAL**

This thesis titled "DESIGN AND ANALYSIS OF A SINGLE PHASE SINGLE SWITCH ĈUK AND SEPIC AC-DC CONVERTER WITH IMPROVED PERFORMANCE" submitted by Md. Shamsul Arifin, Roll No. 0413062120, Session: April 2013 has been accepted as satisfactory in partial fulfillment of the requirement for the degree of Masters of Science in Electrical and Electronic Engineering on January 30, 2016.

## **BOARD OF EXAMINERS**

| DARON                                               |                      |

|-----------------------------------------------------|----------------------|

| 1                                                   | Chairman             |

| Dr. Mohammad Jahangir Alam                          | (Supervisor)         |

| Professor                                           |                      |

| Department of Electrical and Electronic Engineering |                      |

| BUET, Dhaka, Bangladesh.                            |                      |

| 2. Sj. D.                                           | Member               |

| Dr. Satya Prasad Majumder                           | (Ex-officio)         |

| Professor and Head                                  |                      |

| Department of Electrical and Electronic Engineering |                      |

| BUET, Dhaka, Bangladesh.                            |                      |

| 3. malleondu                                        | Member               |

| Dr. Mohammad Ali Choudhury                          |                      |

| Professor                                           |                      |

| Department of Electrical and Electronic Engineering |                      |

| BUET, Dhaka, Bangladesh.                            |                      |

| 4. 0800810MM.                                       | Member<br>(External) |

| Dr. Kazi Khairul Islam                              | (Externar)           |

| Professor                                           |                      |

| Department of Electrical and Electronic Engineering |                      |

IUT, Gazipur, Bangladesh

## **CANDIDATE'S DECLARATION**

It is hereby declared that this thesis titled "DESIGN AND ANALYSIS OF A SINGLE PHASE SINGLE SWITCH ĈUK AND SEPIC AC-DC CONVERTER WITH IMPROVED PERFORMANCE" or any part of it has not been submitted elsewhere for the award of any degree or diploma.

Signature of the candidate

Md. Shamsul Arifin

# DEDICATED TO MY PARENTS

# **TABLE OF CONTENTS**

| Chap | oter 1: : Introduction                                     | 1  |

|------|------------------------------------------------------------|----|

| 1.1  | Introduction                                               | 1  |

| 1.2  | Background                                                 | 1  |

| 1.3  | Goal of the thesis                                         | 3  |

| 1.4  | Thesis Organization                                        | 3  |

|      |                                                            |    |

| Chap | oter 2:Rectifiers                                          | 4  |

| 2.1  | Introduction                                               | 4  |

| 2.2  | Single-Phase Half-Wave Rectifiers                          | 4  |

| 2.3  | Single-Phase Full-Wave Rectifiers                          | 5  |

|      | 2.3.1. Full-Wave Rectifiers with Center-Tapped Transformer | 6  |

|      | 2.3.2 Bridge Rectifiers                                    | 7  |

|      | 2.3.3 Performance Parameters                               | 8  |

| 2.4  | Three-Phase Diode Rectifiers                               | 9  |

|      | 2.4.1 Three-Phase Star Rectifiers                          | 10 |

|      | 2.4.2 Three-Phase Bridge Rectifirs                         | 11 |

|      |                                                            |    |

| Chap | oter 3 :DC-DC Converters                                   | 13 |

| 3.1  | Introduction                                               | 13 |

| 3.2  | Linear Regulator                                           | 14 |

| 3.3  | DC Choppers                                                | 15 |

| 3.4  | Buck (Step-Down) Converter                                 | 16 |

| 3.5  | Boost (Step-Up) Converter                                  | 18 |

| 3.6  | Buck-Boost Converter                                       | 20 |

| 3.7  | Ĉuk Converter                                              | 22 |

| 3.8  | SEPIC Converter                                            | 25 |

| 3.0  | Inverse SEPIC Converter                                    | 27 |

| <b>Chapter 4</b> | : Power Factor Correction                                   | 28 |

|------------------|-------------------------------------------------------------|----|

| 4.1              | Definitions                                                 | 28 |

| 4.2              | Power Factor Correction and Harmonic Reduction              | 28 |

| 4.3              | Need for Power Factor Correction                            | 29 |

| 4.4              | Types of Power Factor Correctors                            | 30 |

| 4.5              | Passive Power Factor Correction Methods                     | 30 |

|                  | 4.5.1 Improving Harmonics with the Filter Capacitance of    | 31 |

|                  | Rectifier Filter Circuits                                   |    |

|                  | 4.5.2 Passive PFC                                           | 33 |

|                  | 4.5.2.1 Passive PFC with Inductor on the AC Side            | 33 |

|                  | 4.5.2.2 Passive PFC with Inductor on the DC Side            | 34 |

| 4.6              | Active Power Factor Correction Methods                      | 35 |

|                  | 4.6.1. High Frequency Active PFC                            | 35 |

|                  | 4.6.1.1 Buck Converter Based Active PFC                     | 36 |

|                  | 4.6.1.2Boost Converter Based Active PFC                     | 37 |

|                  | 4.6.1.3 Buck-Boost Converter Based Active PFC               | 37 |

| 4.7              | Four Switches based bidirectional rectifier                 | 39 |

| 4.8              | The Future of Power Factor Correction                       | 40 |

| Chapter 5        | :Proposed ĈUK AC-DC Converter                               | 41 |

| 5.1              | Proposed Single phase ĈUK AC-DC Converter                   | 41 |

| 5.2              | Principle of Operation                                      | 42 |

| 5.3              | Simulation Results                                          | 44 |

|                  | 5.3.1 Circuit Parameters                                    | 44 |

|                  | 5.3.2 Results from Simulation                               | 45 |

|                  | 5.3.3 Quantitative Comparison                               | 60 |

|                  | 5.3.4. Performances under Load Variation                    | 70 |

| 5.4              | The Proposed Ĉuk Converter with Feedback Controller Circuit | 73 |

| Chapter 6        | : Proposed SEPIC AC-DC Converter                            | 80 |

| 6.1              | Proposed Single phase SEPIC AC-DC Converter                 | 80 |

| 6.2              | Principle of Operation                                      | 81 |

| 6.3              | Simulation Results                                          | 83 |

|                  | 63.1 Circuit Parameters                                     | 83 |

|              | 6.3.2 Results from Simulation                               | 84  |

|--------------|-------------------------------------------------------------|-----|

|              | 6.3.3 Quantitative Comparison                               | 105 |

|              | 6.3.4. Performances under Load Variation                    | 115 |

| 6.4          | The Proposed Ĉuk Converter with Feedback Controller Circuit | 118 |

|              |                                                             |     |

| Chapter 7: C | Conclusion and Suggestion for Future Work                   | 122 |

| 7.1          | Conclusion                                                  | 122 |

| 7.2          | Suggestion for Future Work                                  | 122 |

|              |                                                             |     |

|              | References                                                  | 124 |

# LIST OF FIGURES

| Fig. 2.1  | A single-phase half-wave rectifier with resistive Load.       | 5     |

|-----------|---------------------------------------------------------------|-------|

| Fig. 2.2  | Voltage and current waveforms of the half-wave rectifier with | 5     |

|           | resistive Load.                                               |       |

| Fig. 2.3  | Full-wave rectifier with center-tapped transformer.           | 6     |

| Fig. 2.4  | Voltage and current waveforms of the full-wave rectifier with | 7     |

|           | center-tapped transformer.                                    |       |

| Fig. 2.5  | Bridge rectifier.                                             | 7     |

| Fig. 2.6  | Voltage and current waveforms of the bridge rectifier.        | 8     |

| Fig. 2.7  | Three-phase star rectifier.                                   | 10    |

| Fig. 2.8  | Waveforms of voltage and current of the three-phase star      | 11    |

|           | rectifier as shown in Fig. 2.7.                               |       |

| Fig. 2.9  | Three-phase bridge rectifier.                                 | 12    |

| Fig. 2.10 | Voltage and current waveforms of the three-phase bridge       | 12    |

|           | rectifier.                                                    |       |

| Fig. 3.1  | Linear regulator circuit.                                     | 14    |

| Fig. 3.2  | DC chopper circuit.                                           | 15    |

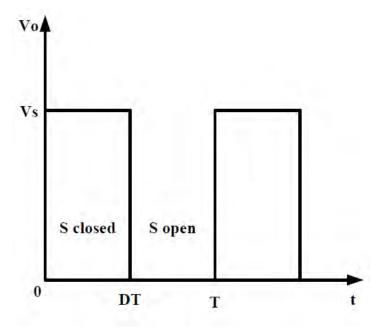

| Fig. 3.3  | Output voltage waveform of a DC chopper with resistive Load.  | 15    |

| Fig. 3.4  | Buck DC-DC converter.                                         | 16    |

| Fig. 3.5  | Equivalent circuit of Buck DC-DC converter when (a) switch    | 16-17 |

|           | closed (b) switch open                                        |       |

| Fig. 3.6  | Waveforms of Buck converter                                   | 17    |

| Fig. 3.7  | Boost DC-DC converter.                                        | 19    |

| Fig. 3.8  | Equivalent circuit of Boost DC-DC converter when (a) switch   | 19    |

|           | closed (b) switch open                                        |       |

| Fig. 3.9  | Waveforms of Boost converter                                  | 20    |

| Fig. 3.10 | Buck-Boost DC-DC converter.                                   | 21    |

| Fig. 3.11 | Equivalent circuit of Buck-Boost DC-DC converter when (a)     | 21-22 |

|           | switch closed (b) switch open                                 |       |

| Fig. 3.12 | Waveforms of Buck-Boost converter.                            | 22    |

| Fig. 3.13 | Cuk DC-DC converter                                            | 23    |

|-----------|----------------------------------------------------------------|-------|

| Fig.3.14. | Equivalent circuit of Ĉuk DC-DC converter when (a) switch      | 23-24 |

|           | closed (b) switch open.                                        |       |

| Fig. 3.15 | Waveforms of Ĉuk Converter                                     | 24    |

| Fig. 3.16 | SEPIC DC-DC converter                                          | 26    |

| Fig. 3.17 | Equivalent circuit of SEPIC DC-DC converter when (a) switch    | 26    |

|           | closed (b) switch open                                         |       |

| Fig. 3.18 | Inverse SEPIC DC-DC converter                                  | 27    |

| Fig. 3.19 | Equivalent circuit of Inverse SEPIC DC-DC converter when (a)   | 27    |

|           | switch closed (b) switch open.                                 |       |

| Fig. 4.1  | Single phase bridge rectifier.                                 | 29    |

| Fig. 4.2  | Typical simulated line voltage and current waveforms.          | 30    |

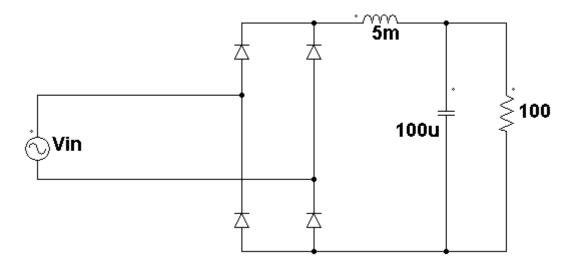

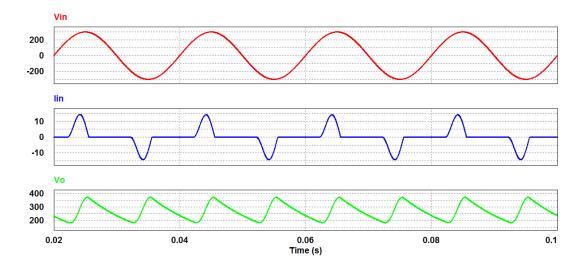

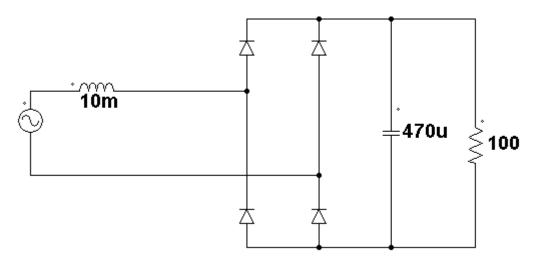

| Fig. 4.3  | Typical single-phase diode rectifier.                          | 31    |

| Fig. 4.4. | Simulated input current, output ripple waveforms for output    | 32    |

|           | capacitor values of 68μF.                                      |       |

| Fig. 4.5  | Typical single-phase diode rectifier.                          | 32    |

| Fig. 4.6  | Simulated input current, output ripple waveforms for output    | 33    |

|           | capacitor values of 470μF.                                     |       |

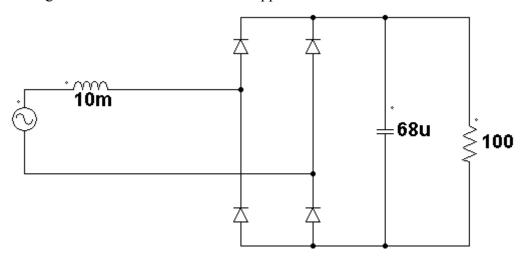

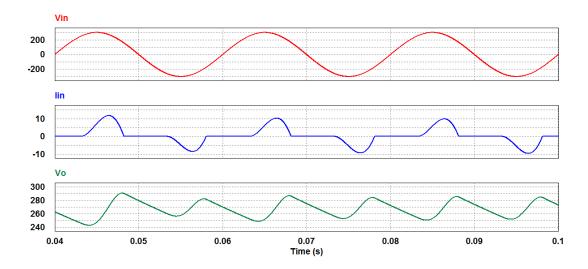

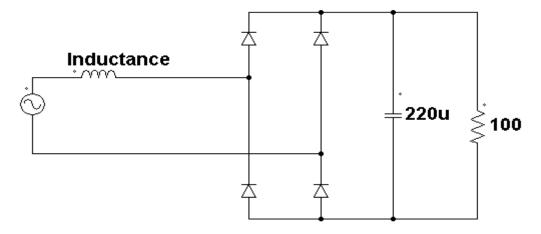

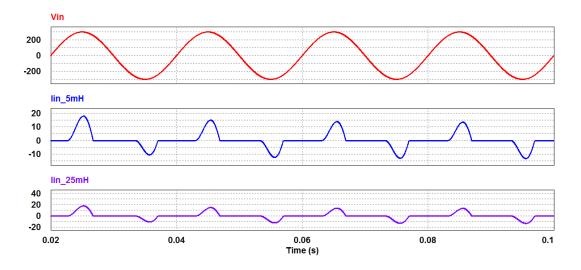

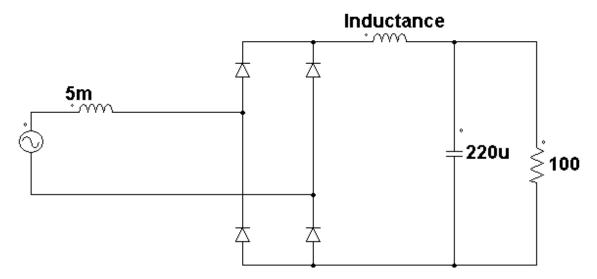

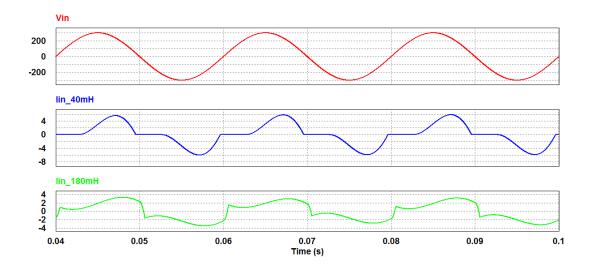

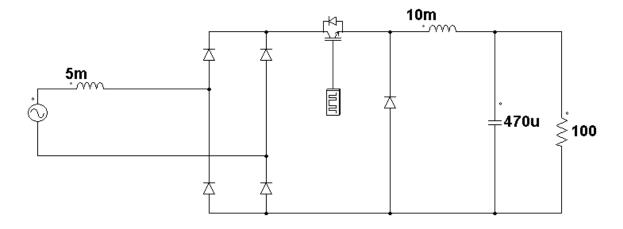

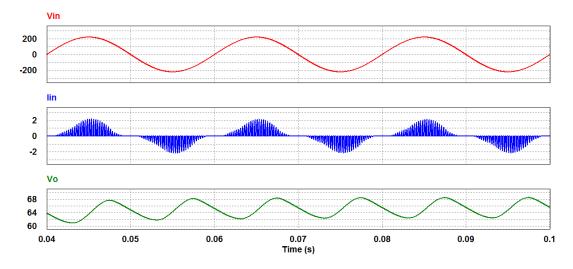

| Fig. 4.7  | Inductor on the AC side of the diode bridge rectifier.         | 33    |

| Fig. 4.8  | Simulated input voltage and current waveforms                  | 34    |

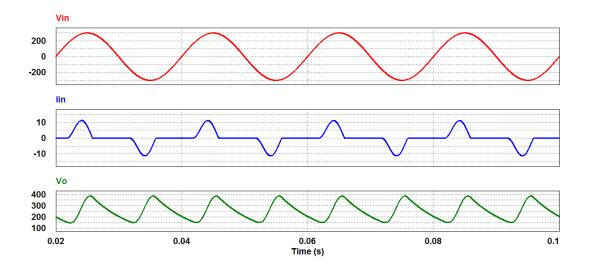

| Fig. 4.9  | Inductor on the DC side of the diode bridge rectifier.         | 34    |

| Fig. 4.10 | Simulated input voltage and current waveforms                  | 35    |

| Fig. 4.11 | Buck converter based active PFC circuit.                       | 36    |

| Fig. 4.12 | Simulated voltage and current waveforms                        | 36    |

| Fig. 4.13 | Boost converter based active PFC circuit.                      | 37    |

| Fig. 4.14 | Simulated voltage and current waveforms.                       | 37    |

| Fig.4.15  | Buck-Boost converter based active PFC circuit.                 | 38    |

| Fig. 4.16 | Simulated voltage and current waveforms.                       | 38    |

| Fig. 4.17 | Four Switches based bidirectional rectifier                    | 39    |

| Fig. 4.18 | Wave shape of the bidirectional rectifier before filtering.    | 39    |

| Fig. 4.19 | Wave shape of the bidirectional rectifier after filtering.     | 40    |

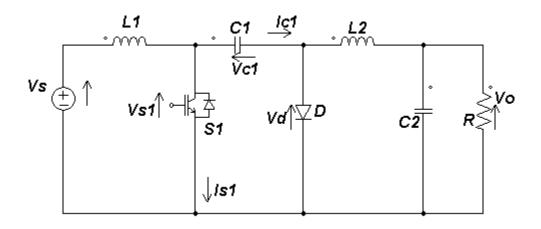

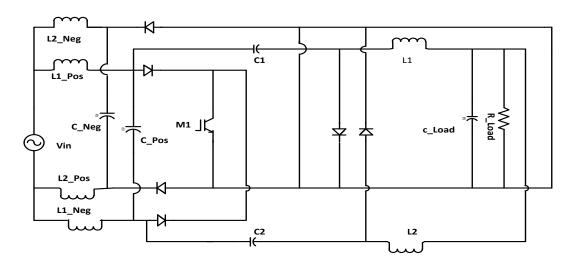

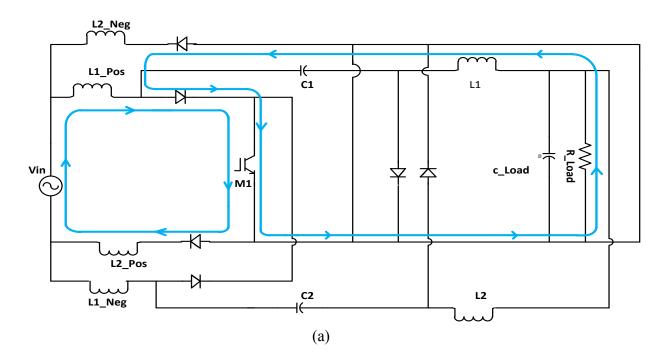

| Fig. 5.1  | Proposed AC-DC Ĉuk Converter                                   | 41    |

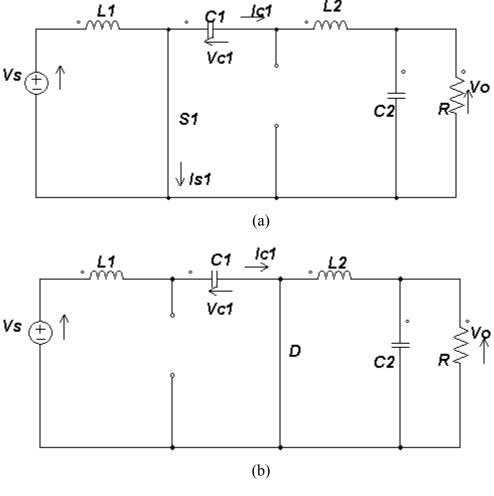

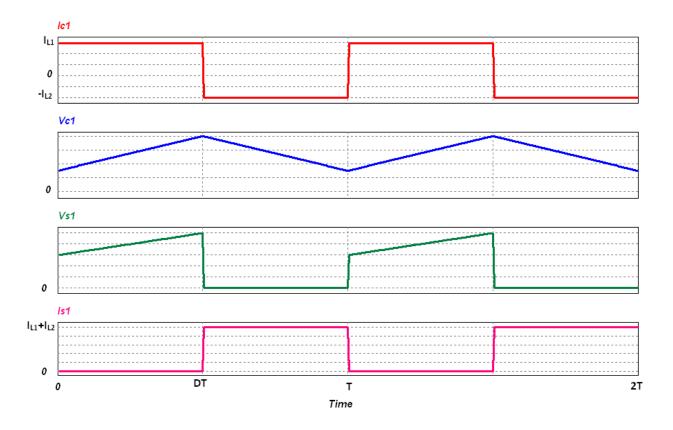

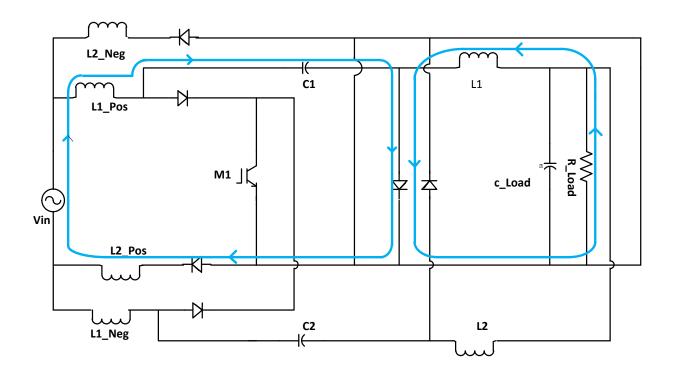

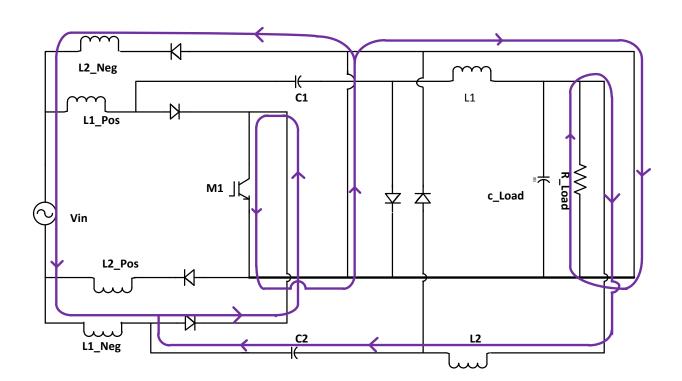

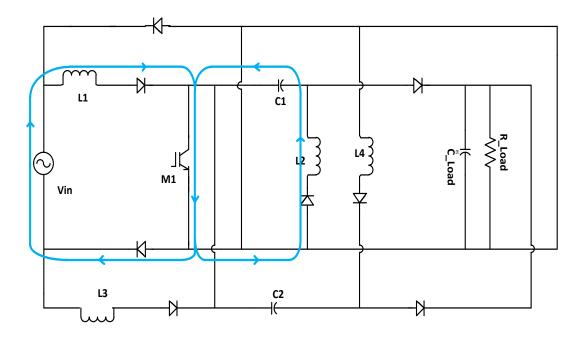

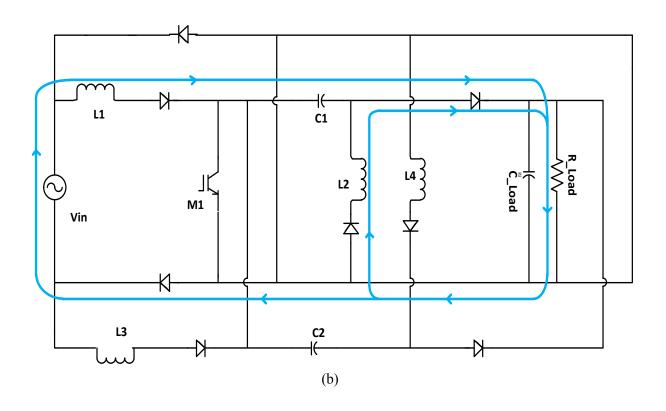

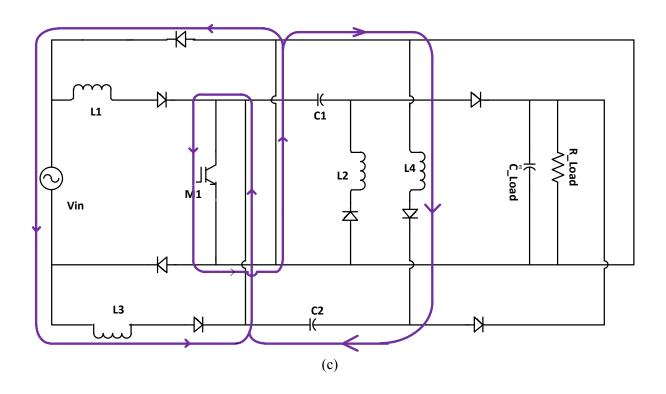

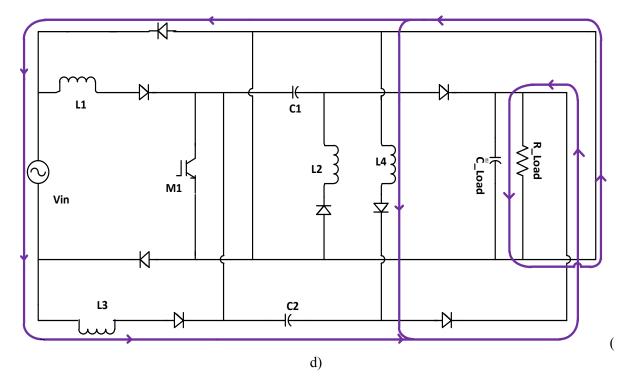

| Fig. 5.2. | Four states of operation of proposed AC-DC converter (A) State | 42-44 |

|          | 1, circuit when switch is ON during positive half cycle of the    |    |

|----------|-------------------------------------------------------------------|----|

|          | AC supply, (B) State 2, circuit when switch is OFF during         |    |

|          | positive half cycle of the AC supply,(C) State 3, circuit when    |    |

|          | switch is ON during negative half cycle of the AC supply,(D)      |    |

|          | State 4, circuit when switch is OFF during negative half cycle of |    |

|          | the AC supply                                                     |    |

| Fig.5.3  | Conventional Ĉuk AC-DC Converter                                  | 45 |

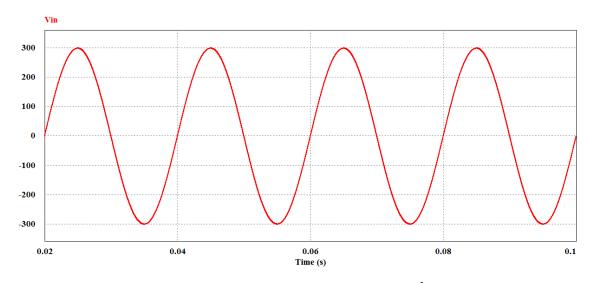

| Fig.5.4  | Wave shape of input voltage of Proposed AC-DC Ĉuk                 | 45 |

|          | Converter                                                         |    |

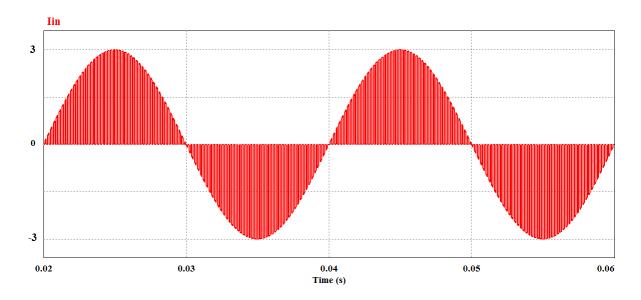

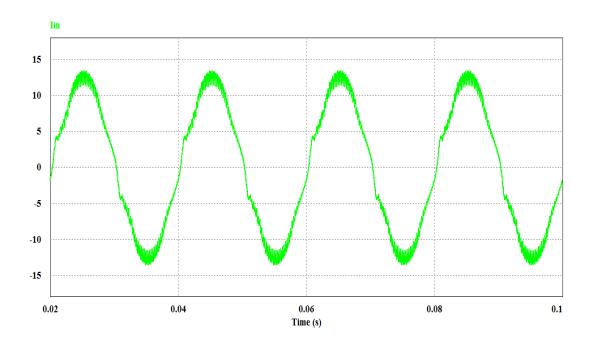

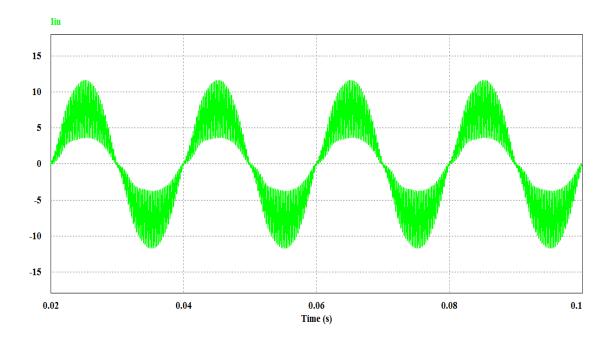

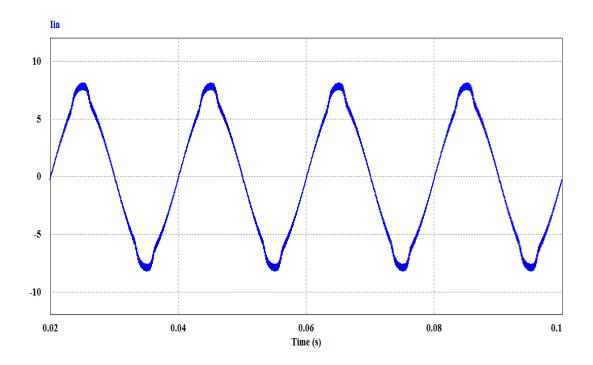

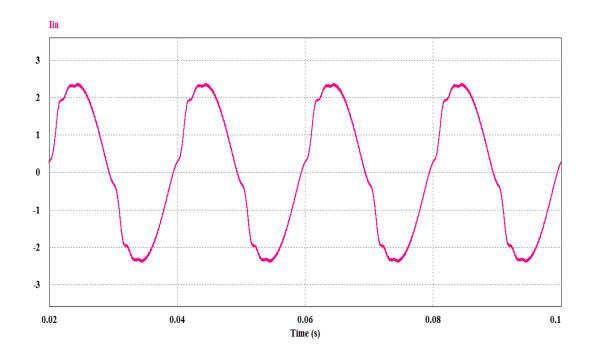

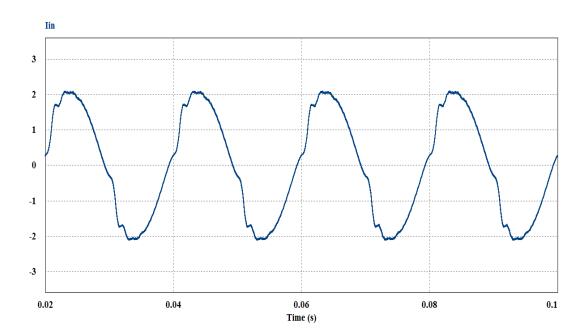

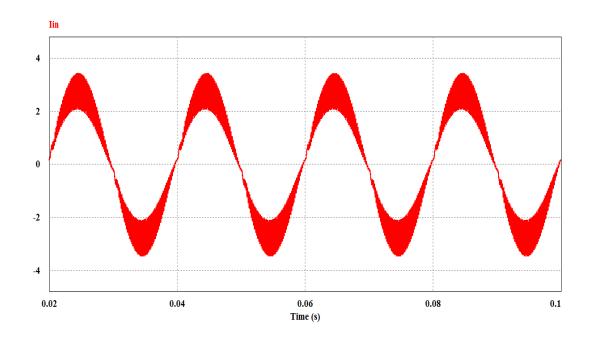

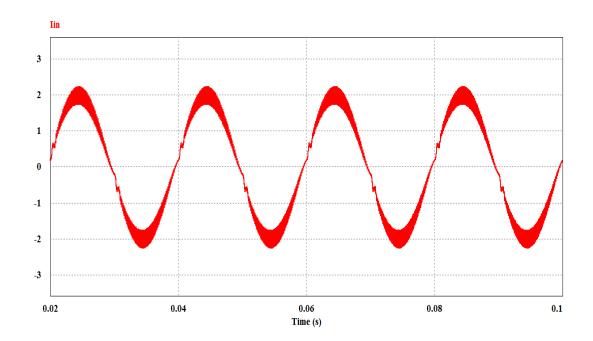

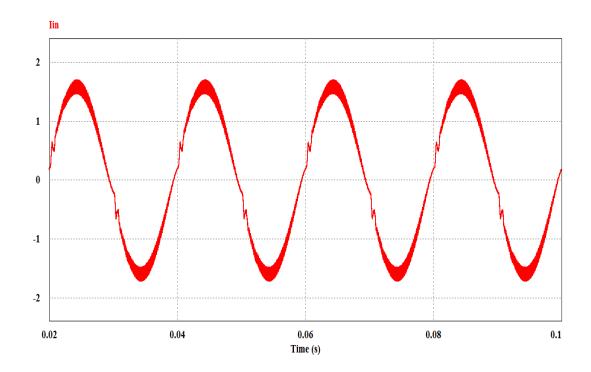

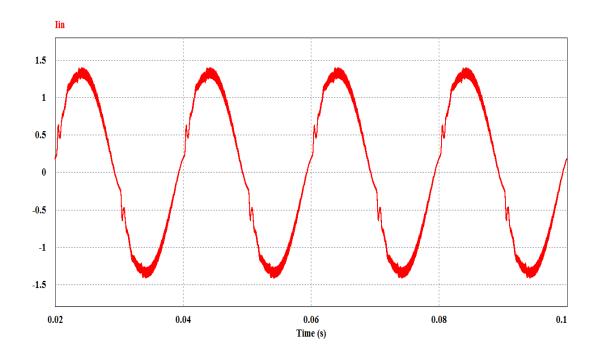

| Fig.5.5  | Input current of proposed Ĉuk Converter at fs = 4000 Hz. and      | 46 |

|          | D=0.6                                                             |    |

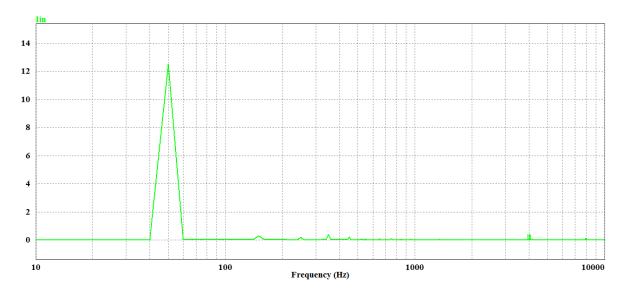

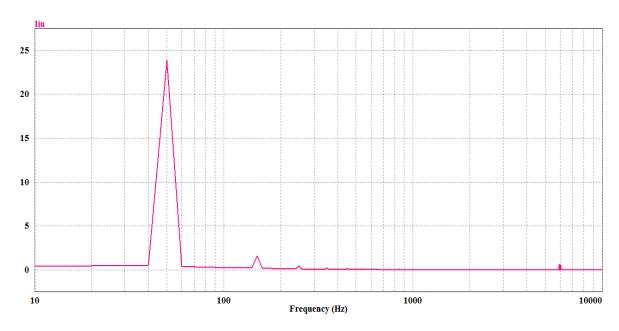

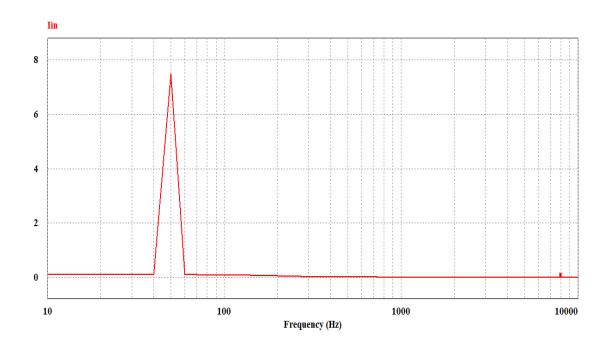

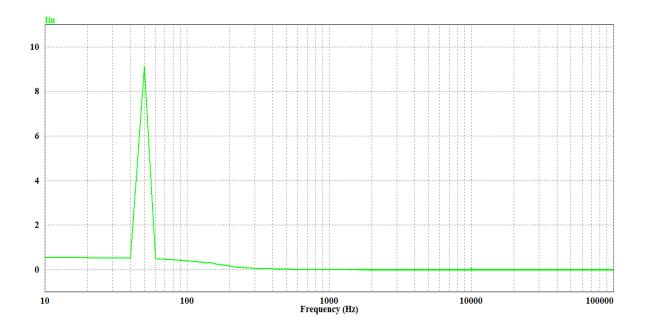

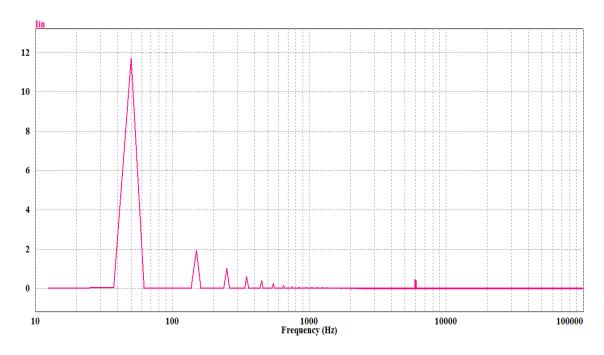

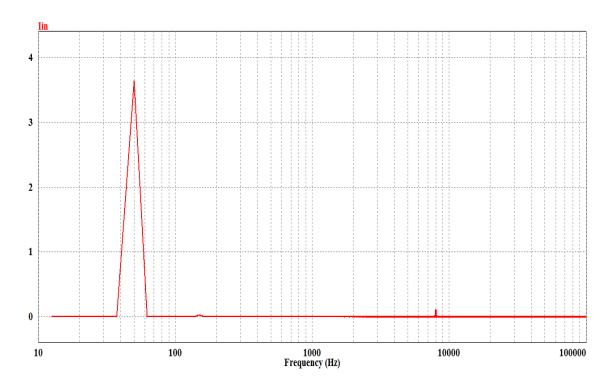

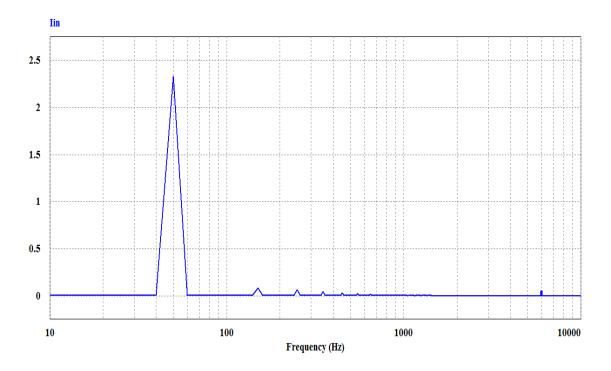

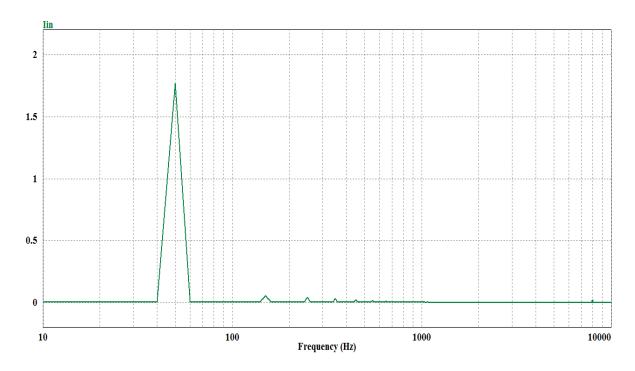

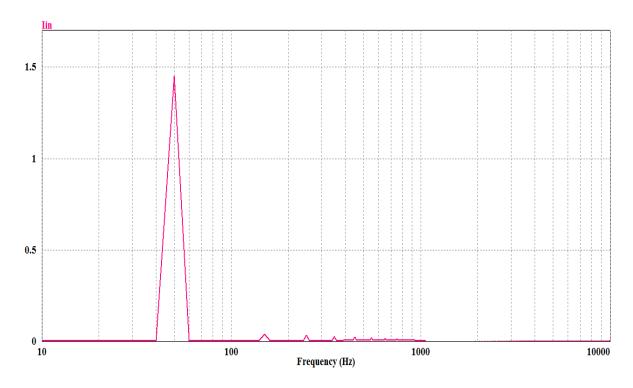

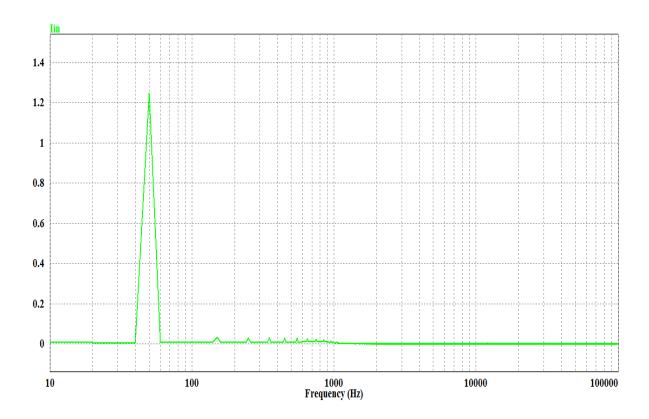

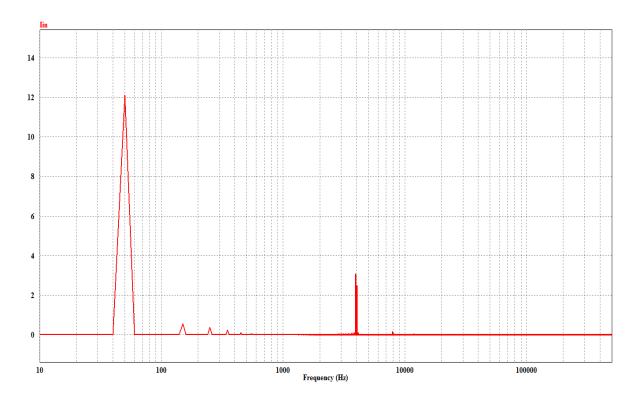

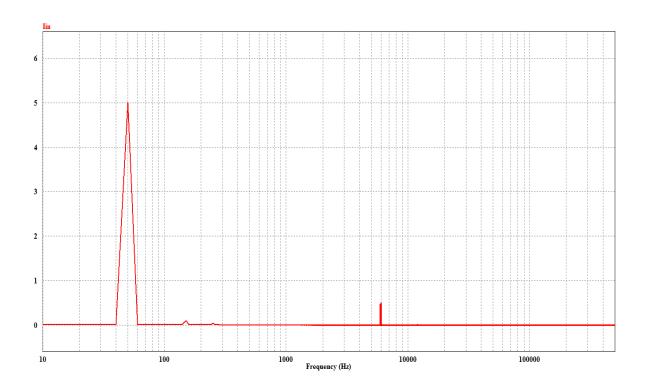

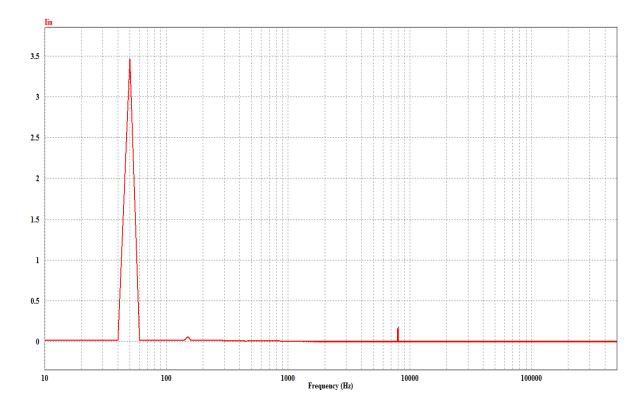

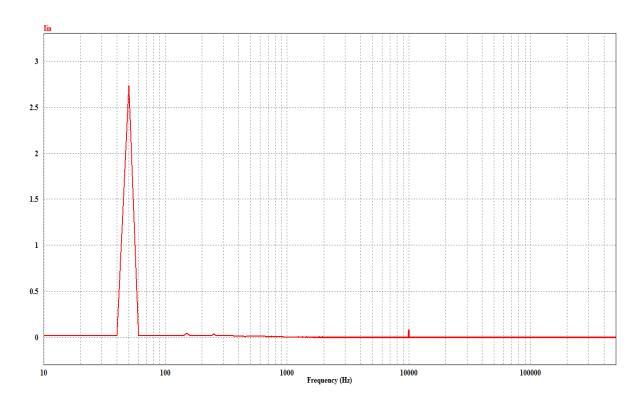

| Fig.5.6  | Input current spectrum of proposed Ĉuk Converter at fs = 4000     | 46 |

|          | Hz. and $D=0.6$ .                                                 |    |

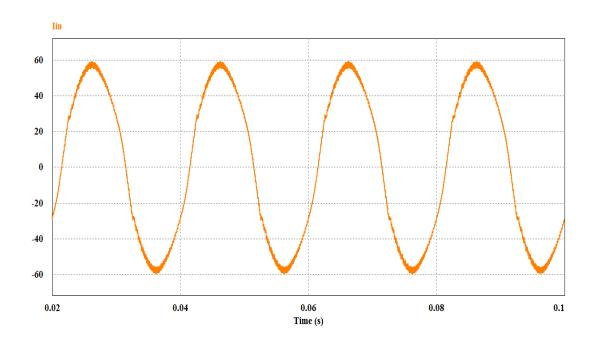

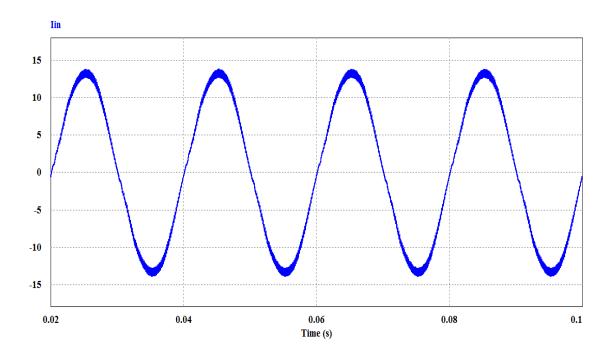

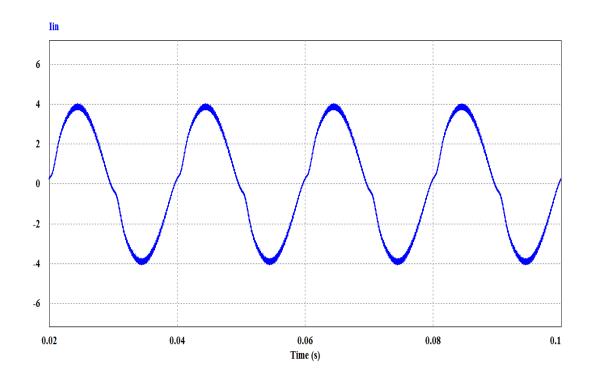

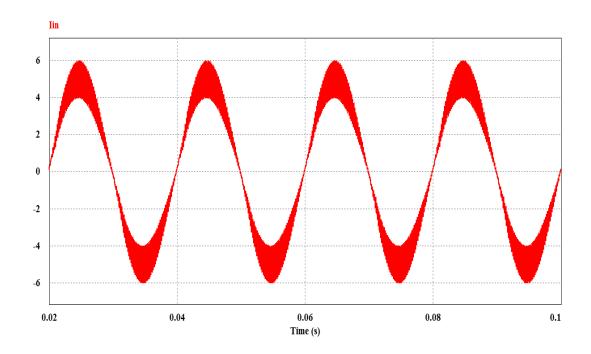

| Fig.5.7  | Input current of proposed Ĉuk Converter at fs = 6000Hz. D =       | 47 |

|          | 0.6                                                               |    |

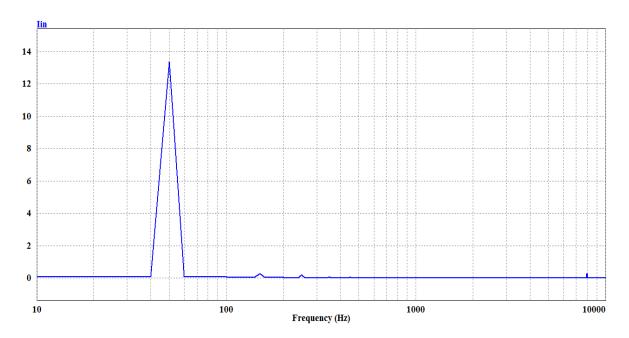

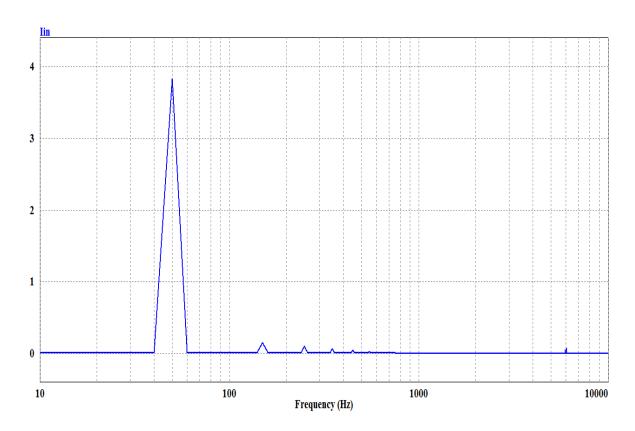

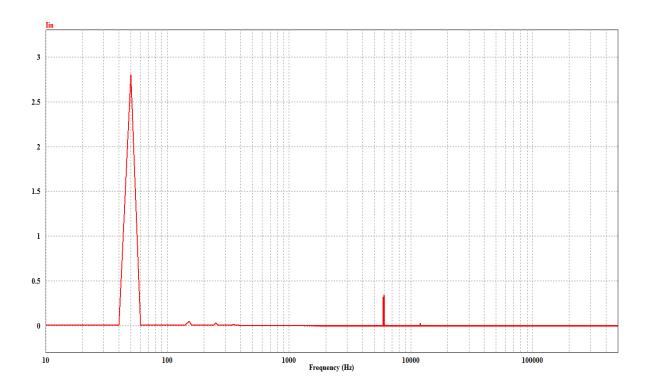

| Fig.5.8  | Input current spectrum of proposed Ĉuk Converter at fs = 6000     | 47 |

|          | Hz. and $D=0.6$                                                   |    |

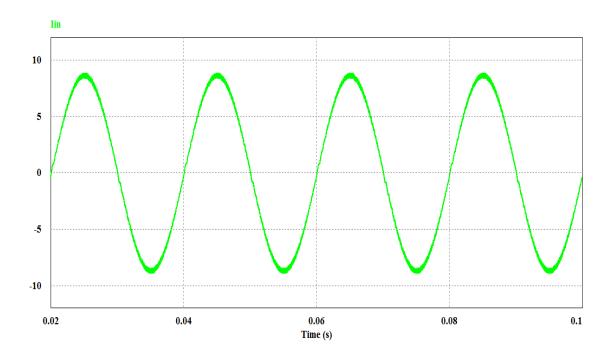

| Fig.5.9  | Input current of proposed Ĉuk Converter at fs = 6000 Hz. and      | 48 |

|          | D=0.8                                                             |    |

| Fig.5.10 | Input current spectrum of proposed Ĉuk Converter at fs = 6000     | 48 |

|          | Hz. and $D=0.8$                                                   |    |

| Fig.5.11 | Input current of proposed Ĉuk Converter at fs = 8000 Hz. and      | 49 |

|          | D = 0.4                                                           |    |

| Fig.5.12 | Input current spectrum of proposed Ĉuk Converter at fs = 8000     | 49 |

|          | Hz. and D= 0.4                                                    |    |

| Fig.5.13 | Input current of proposed Ĉuk Converter at fs = 8000 Hz. and      | 50 |

|          | D=0.5                                                             |    |

| Fig.5.14 | Input current spectrum of proposed Ĉuk Converter at fs = 8000     | 50 |

|          | Hz. and $D=0.5$                                                   |    |

| Fig.5.15 | Input current of proposed Ĉuk Converter at fs = 10000 Hz. and     | 51 |

|          | D = 0.5                                                           |    |

| Fig.5.16 | Input current spectrum of proposed Ĉuk Converter at fs = 10000    | 51 |

|          | Hz and $D=0.5$                                                    |    |

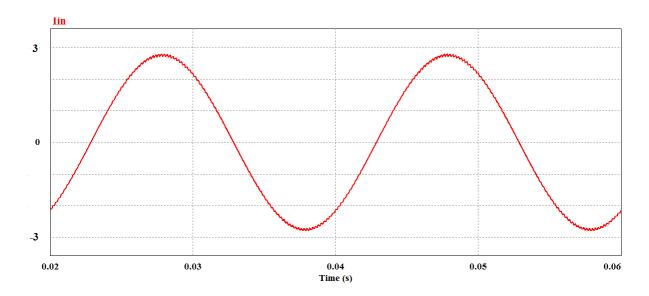

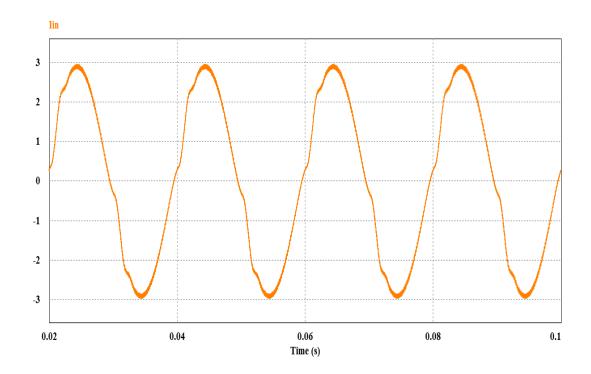

| Fig.5.17 | Input current of conventional Ĉuk Converter at fs = 4000 Hz.           | 52 |

|----------|------------------------------------------------------------------------|----|

|          | and D= 0.6                                                             |    |

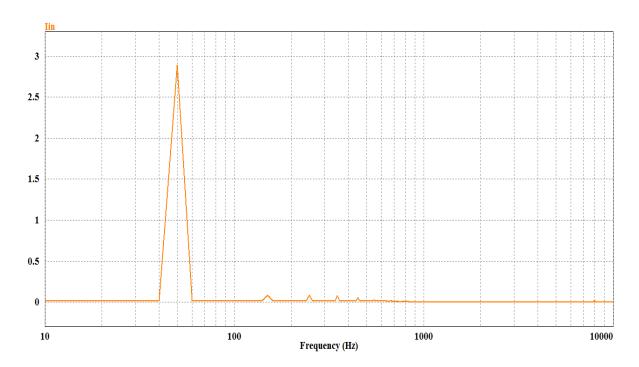

| Fig.5.18 | Input current spectrum of conventional Ĉuk Converter at fs =           | 52 |

|          | 4000 Hz. and D= 0.6                                                    |    |

| Fig.5.19 | Input current of conventional Ĉuk Converter at fs = 6000 Hz.           | 53 |

|          | and D= 0.6                                                             |    |

| Fig.5.20 | Input current spectrum of conventional Ĉuk Converter at fs =           | 53 |

|          | 6000 Hz. and D= 0.6                                                    |    |

| Fig.5.21 | Input current of conventional $\hat{C}uk$ Converter at $fs = 6000$ Hz. | 54 |

|          | and D= 0.8                                                             |    |

| Fig.5.22 | Input current spectrum of conventional Ĉuk Converter at fs =           | 54 |

|          | 6000 Hz. and D= 0.8                                                    |    |

| Fig.5.23 | Input current of conventional Ĉuk Converter at fs = 8000 Hz.           | 55 |

|          | and D= 0.4                                                             |    |

| Fig.5.24 | Input current spectrum of conventional Ĉuk Converter at fs =           | 55 |

|          | 8000 Hz. and D= 0.4                                                    |    |

| Fig.5.25 | Input current of conventional Ĉuk Converter at fs = 8000 Hz.           | 56 |

|          | and D= 0.5                                                             |    |

| Fig.5.26 | Input current spectrum of conventional Ĉuk Converter at fs =           | 56 |

|          | 8000 Hz. and D= 0.5                                                    |    |

| Fig.5.27 | Input current of conventional Ĉuk Converter at fs = 10000 Hz.          | 57 |

|          | and D= 0.5                                                             |    |

| Fig.5.28 | Input current spectrum of conventional Ĉuk Converter at fs =           | 57 |

|          | 10000 Hz. and D= 0.5                                                   |    |

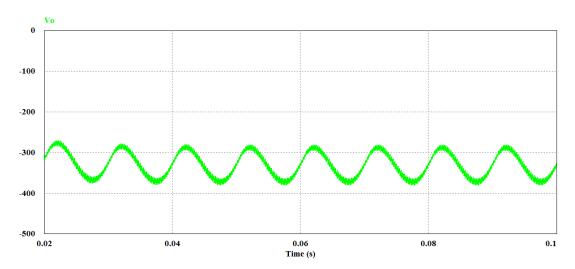

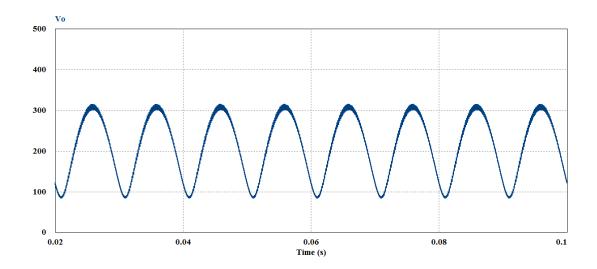

| Fig.5.29 | Output voltage waveform of proposed $\hat{C}uk$ converter at $f_s$ =   | 58 |

|          | 4000Hz. and D = $0.1$                                                  |    |

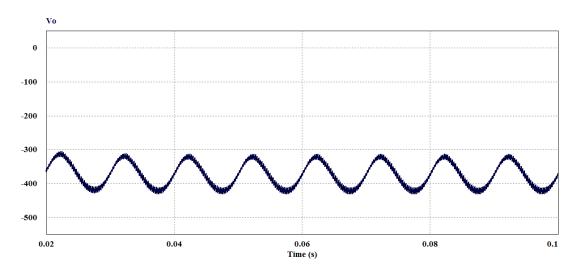

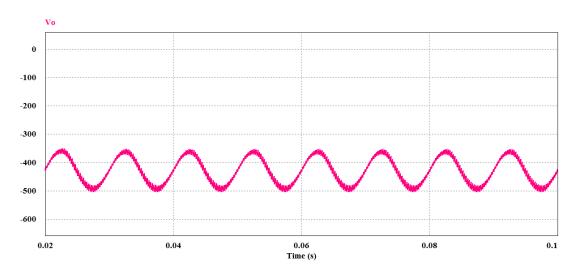

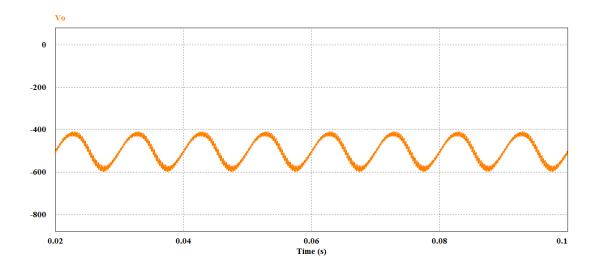

| Fig.5.30 | Fig.5.29 Output voltage waveform of proposed Ĉuk converter at          | 58 |

|          | $f_s = 4000$ Hz. and $D = 0.2$                                         |    |

| Fig.5.31 | Fig.5.29 Output voltage waveform of proposed Ĉuk converter at          | 58 |

|          | $f_s = 4000$ Hz. and $D = 0.3$                                         |    |

| Fig.5.32 | Fig.5.29 Output voltage waveform of proposed Ĉuk converter at          | 59 |

|          | $f_s = 4000$ Hz. and $D = 0.4$                                         |    |

| Fig.5.33 | Fig.5.29 Output voltage waveform of proposed Ĉuk converter at          | 59 |

|           | $f_s = 4000$ Hz. and D = 0.5                                              |    |

|-----------|---------------------------------------------------------------------------|----|

| Fig.5.34  | Fig.5.29 Output voltage waveform of proposed Ĉuk converter at             | 59 |

|           | $f_s = 4000$ Hz. and $D = 0.6$                                            |    |

| Fig.5.35  | Fig.5.29 Output voltage waveform of proposed Ĉuk converter at             | 60 |

|           | $f_s = 4000$ Hz. and $D = 0.7$                                            |    |

| Fig.5.36  | Fig.5.29 Output voltage waveform of proposed Ĉuk converter at             | 60 |

|           | $f_s = 4000$ Hz. and $D = 0.8$                                            |    |

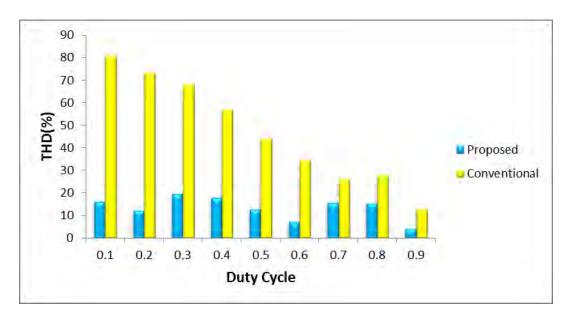

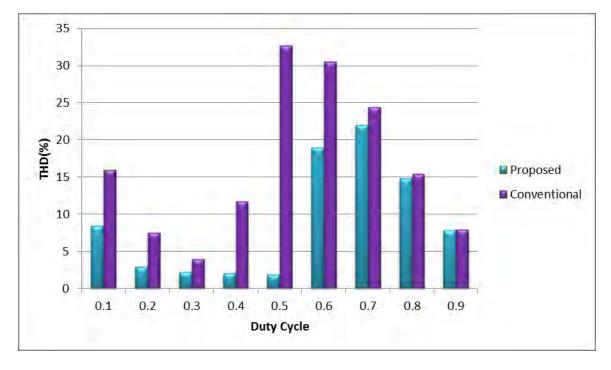

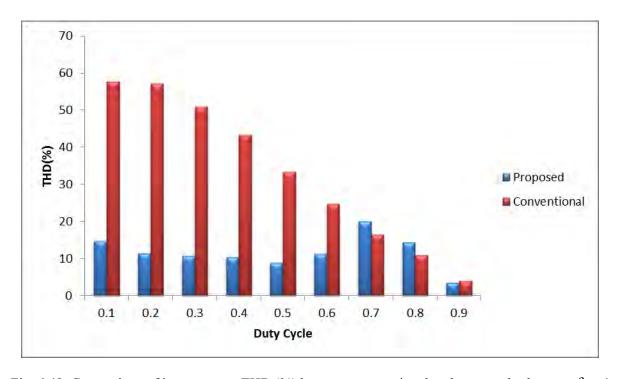

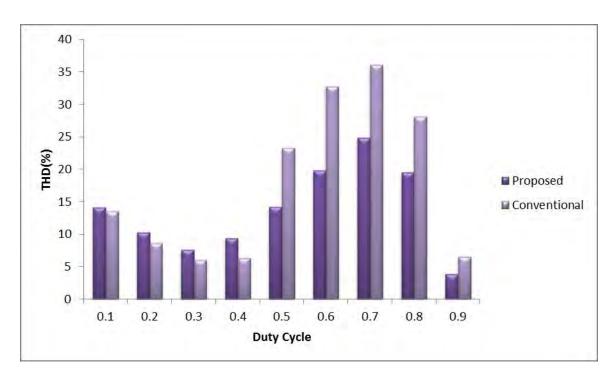

| Fig. 5.37 | Comparison of input current THD (%) between conventional                  | 6  |

|           | and proposed scheme at fs = 4 kHz. and R_Load = $100\Omega$ .             |    |

| Fig. 5.38 | Comparison of input current THD (%) between conventional                  | 6  |

|           | and proposed scheme at fs = 6 kHz. and R_Load = $100\Omega$ .             |    |

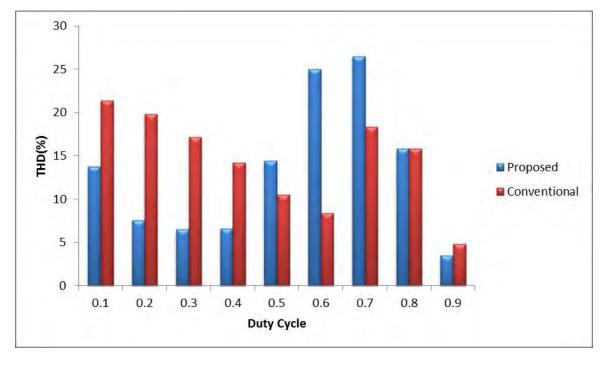

| Fig. 5.39 | Comparison of input current THD (%) between conventional                  | 62 |

|           | and proposed scheme at fs = 8 kHz. and R_Load = $100\Omega$ .             |    |

| Fig. 5.40 | Comparison of input current THD (%) between conventional                  | 62 |

|           | and proposed scheme at fs = $10 \text{ kHz}$ . and R_Load = $100\Omega$ . |    |

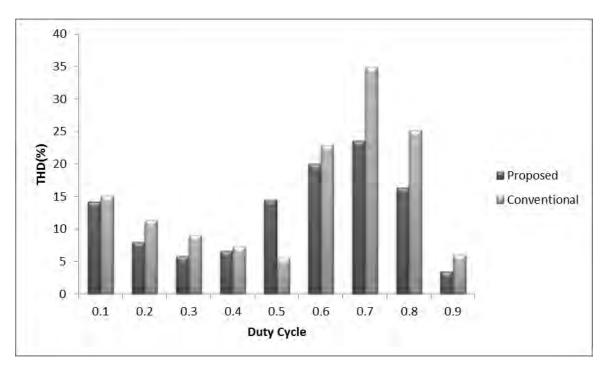

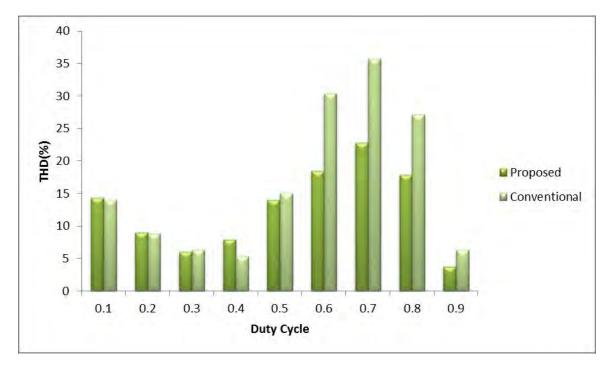

| Fig. 5.41 | Comparison of input current THD (%) between conventional                  | 63 |

|           | and proposed scheme at fs = 12 kHz. and R_Load = $100\Omega$ .            |    |

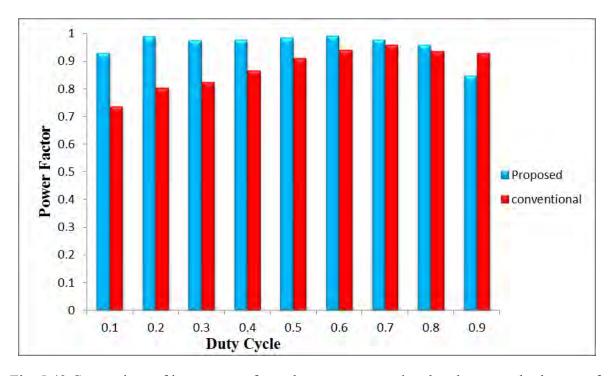

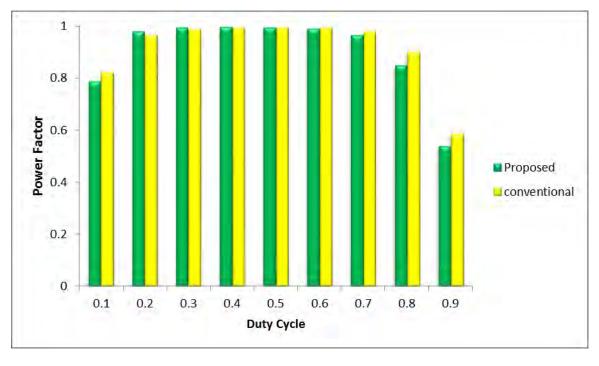

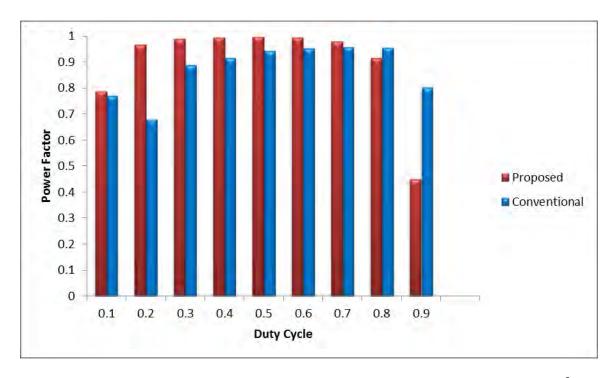

| Fig. 5.42 | Comparison of input power factor between conventional and                 | 63 |

|           | proposed scheme at fs = 4 kHz. and R_Load = $100 \Omega$                  |    |

| Fig. 5.43 | Comparison of input power factor between conventional and                 | 64 |

|           | proposed scheme at fs = 6 kHz. and R_Load = $100 \Omega$ .                |    |

| Fig. 5.44 | Comparison of input power factor between conventional and                 | 64 |

|           | proposed scheme at fs = 8 kHz. and R_Load = $100 \Omega$ .                |    |

| Fig. 5.45 | Comparison of input power factor between conventional and                 | 65 |

|           | proposed scheme at fs = 10 kHz. and R_Load = 100 $\Omega$ .               |    |

| Fig. 5.46 | Comparison of input power factor between conventional and                 | 65 |

|           | proposed scheme at fs = 12 kHz. and R_Load = 100 $\Omega$ .               |    |

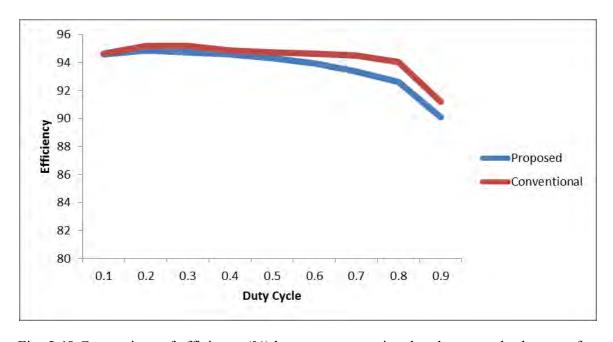

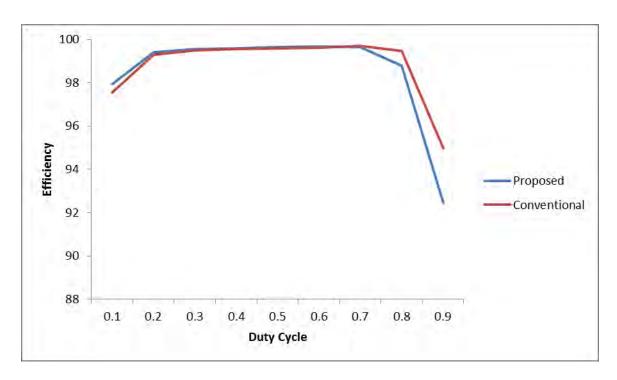

| Fig. 5.47 | Comparison of efficiency (%) between conventional and                     | 66 |

|           | proposed scheme at fs = 4 kHz. and R_Load = $100 \Omega$ .                |    |

| Fig. 5.48 | Comparison of efficiency (%) between conventional and                     | 66 |

|           | proposed scheme at fs = 6 kHz. and R_Load = $100 \Omega$ .                |    |

| Fig. 5.49 | Comparison of efficiency (%) between conventional and                     | 67 |

|           | proposed scheme at $fs = 8 \text{ kHz}$ and $R$ I oad = 100 O             |    |

| Fig. 5.50 | Comparison of efficiency (%) between conventional and                     | 67 |

|-----------|---------------------------------------------------------------------------|----|

|           | proposed scheme at fs = 10 kHz. and R_Load = 100 $\Omega$ .               |    |

| Fig. 5.51 | Comparison of efficiency (%) between conventional and                     | 68 |

|           | proposed scheme at fs = 12 kHz. and R_Load = $100 \Omega$ .               |    |

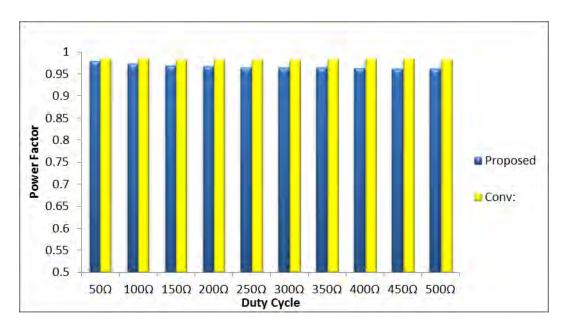

| Fig. 5.52 | Comparison of input power factor between conventional and                 | 71 |

|           | proposed scheme with Load variation at $fs = 8$ kHz. and $D = 0.4$ .      |    |

| Fig. 5.53 | Comparison of efficiency between conventional and proposed                | 72 |

|           | scheme with Load variation at $fs = 8 \text{ kHz}$ . and $D = 0.4$ .      |    |

| Fig. 5.54 | Comparison of input current THD (%) between conventional                  | 72 |

|           | and proposed scheme with Load variation at fs = $8 \text{ kHz}$ . and D = |    |

|           | 0.4                                                                       |    |

| Fig. 5.55 | Output Voltage of the proposed converter at $fs = 8000 \text{ Hz}$ . and  | 73 |

|           | D=0.4                                                                     |    |

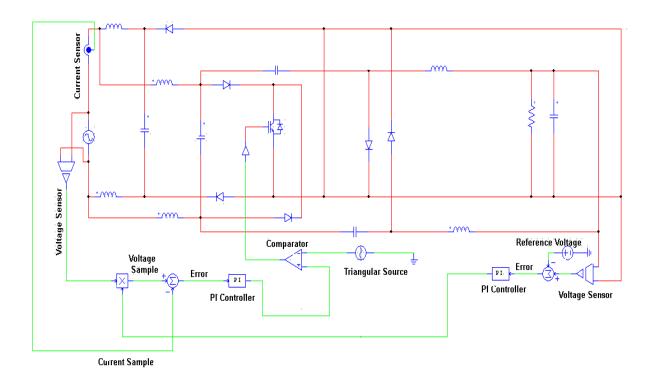

| Fig. 5.56 | The proposed ĉuk converter with feedback controller circuit.              | 74 |

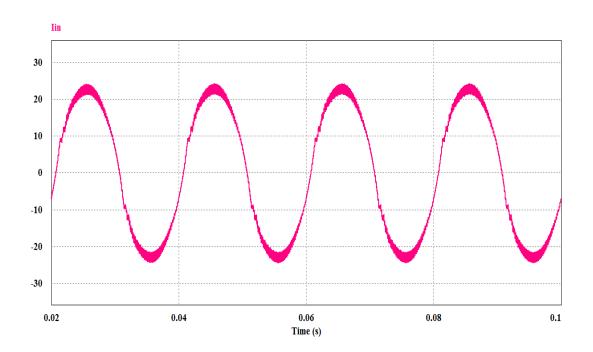

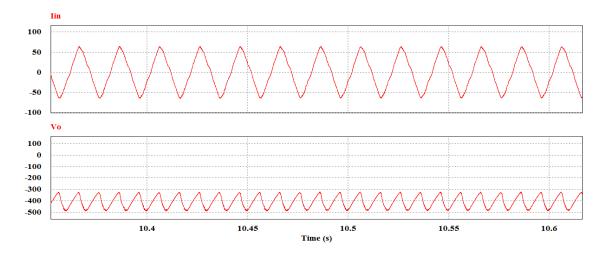

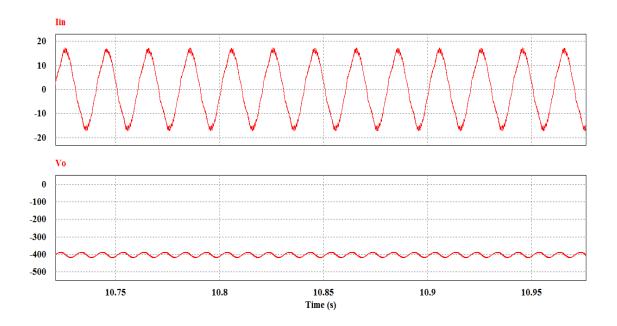

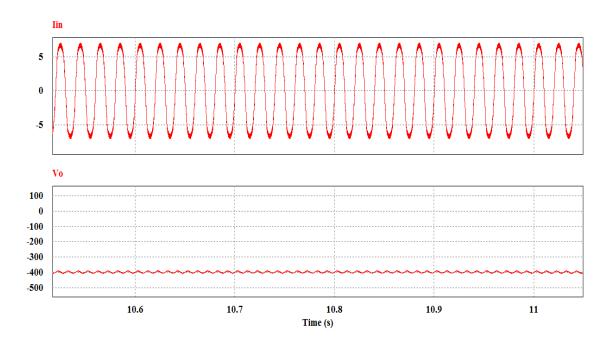

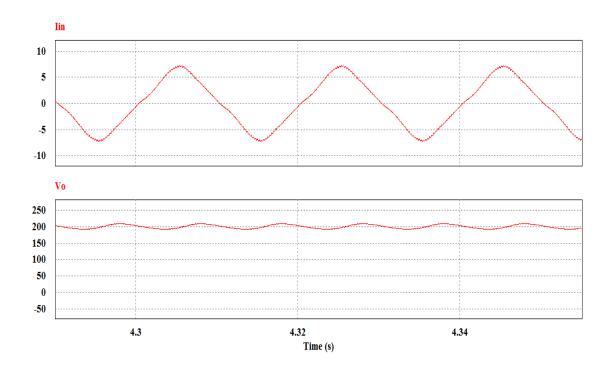

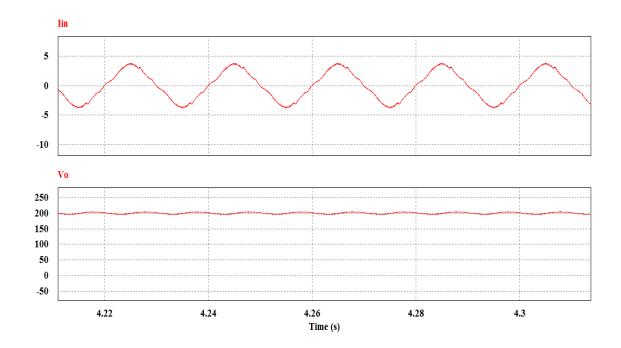

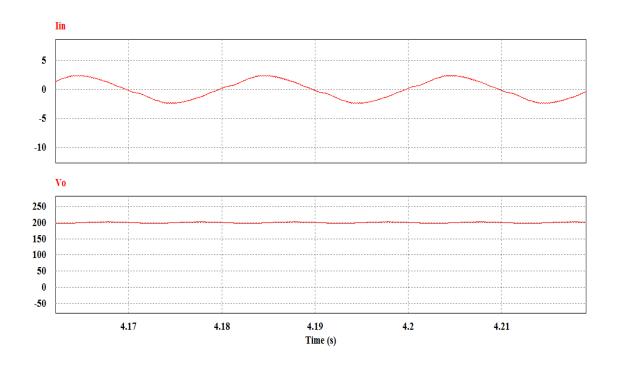

| Fig.5.57  | Input current and output voltage of proposed ĉuk converter with           | 74 |

|           | feedback controller for Load resistance of 30 $\Omega$                    |    |

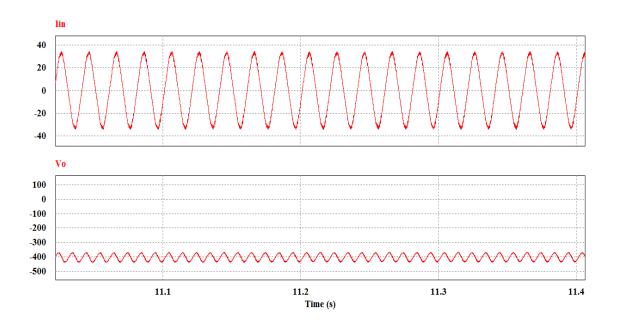

| Fig.5.58  | Input current and output voltage of proposed ĉuk converter with           | 75 |

|           | feedback controller for Load resistance of 50 $\Omega$                    |    |

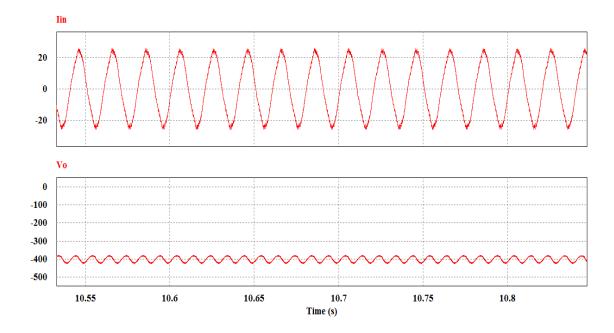

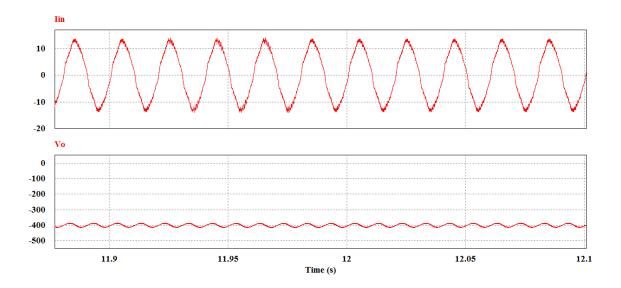

| Fig.5.59  | Input current and output voltage of proposed ĉuk converter with           | 75 |

|           | feedback controller for Load resistance of 70 $\Omega$                    |    |

| Fig.5.60  | Input current and output voltage of proposed ĉuk converter with           | 76 |

|           | feedback controller for Load resistance of 100 $\Omega$                   |    |

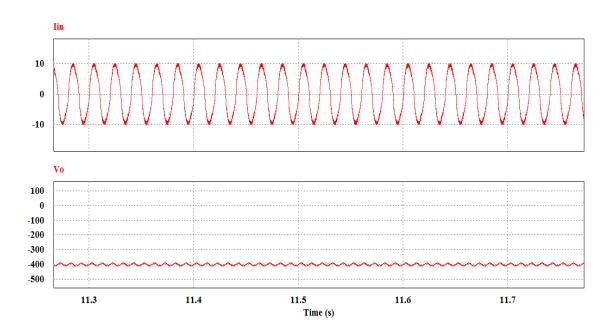

| Fig.5.61  | Input current and output voltage of proposed ĉuk converter with           | 76 |

|           | feedback controller for Load resistance of 120 $\Omega$                   |    |

| Fig.5.62  | Input current and output voltage of proposed ĉuk converter with           | 77 |

|           | feedback controller for Load resistance of 150 $\Omega$                   |    |

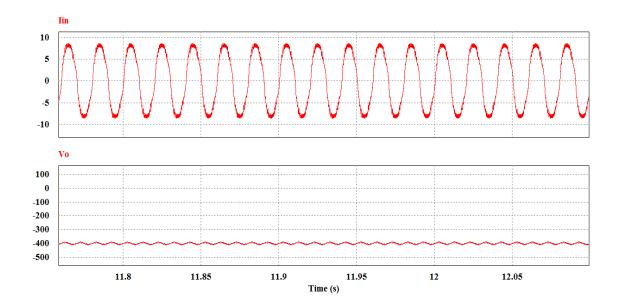

| Fig.5.63  | Input current and output voltage of proposed ĉuk converter with           | 77 |

|           | feedback controller for Load resistance of 170 $\Omega$                   |    |

| Fig.5.64  | Input current and output voltage of proposed ĉuk converter with           | 78 |

|           | feedback controller for Load resistance of 200 $\Omega$                   |    |

| Fig.5.65  | Input current and output voltage of proposed ĉuk converter with           | 78 |

|           | feedback controller for Load resistance of 230 $\boldsymbol{\Omega}$      |    |

| Fig.5.66  | Input current and output voltage of proposed ĉuk converter with           | 79 |

|          | feedback controller for Load resistance of 250 $\Omega$                    |       |

|----------|----------------------------------------------------------------------------|-------|

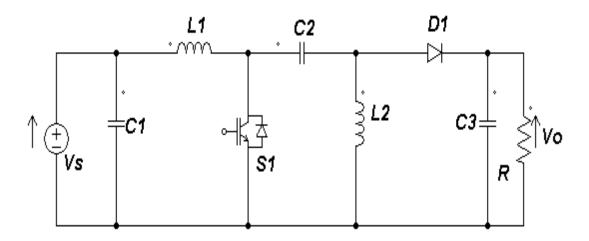

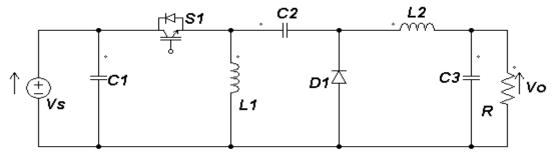

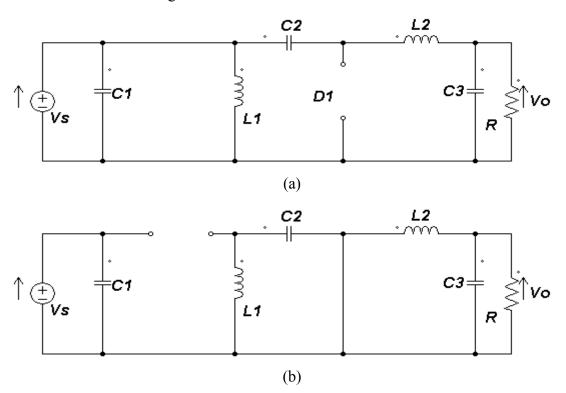

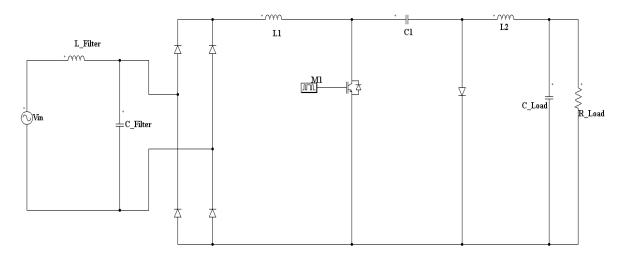

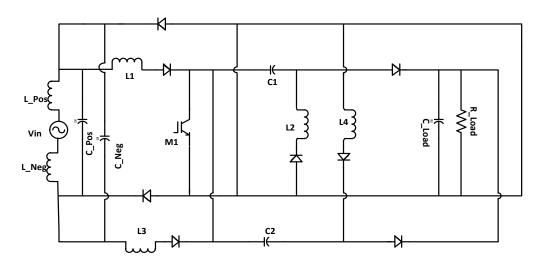

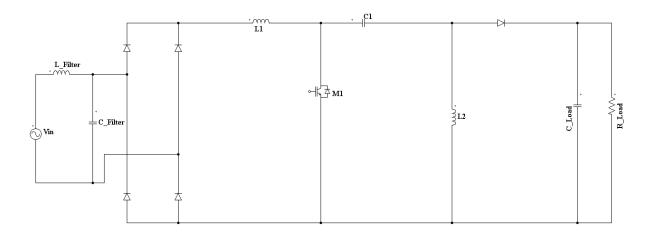

| Fig. 6.1 | Proposed AC-DC SEPIC Converter                                             | 80    |

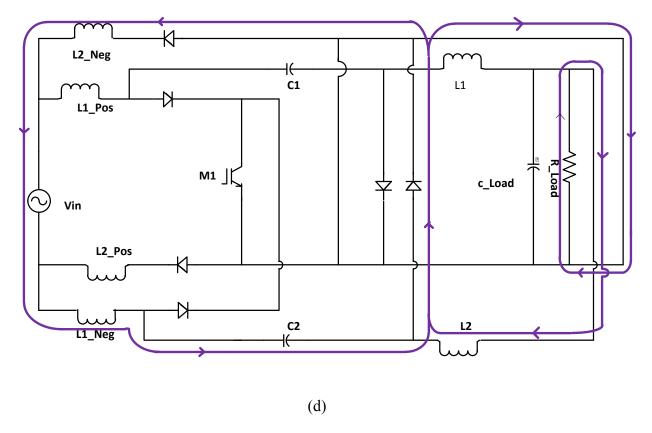

| Fig. 6.2 | Four states of operation of proposed AC-DC SEPIC converter                 | 81-83 |

|          | (A) State 1, circuit when switch is ON during positive half cycle          |       |

|          | of the AC supply, (B) State 2, circuit when switch is OFF during           |       |

|          | positive half cycle of the AC supply,(C) State 3, circuit when             |       |

|          | switch is ON during negative half cycle of the AC supply,(D)               |       |

|          | State 4, circuit when switch is OFF during negative half cycle of          |       |

|          | the AC supply.                                                             |       |

| Fig. 6.3 | Conventional SEPIC AC-DC Converter                                         | 84    |

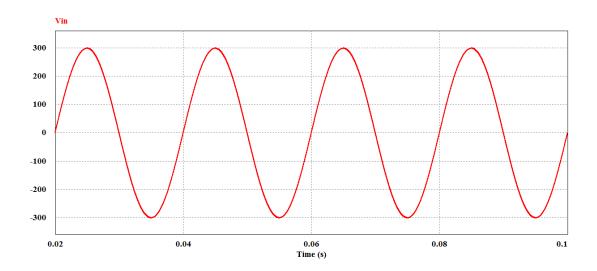

| Fig. 6.4 | Wave shape of input voltage of Proposed AC-DC Ĉuk                          | 84    |

|          | Converter                                                                  |       |

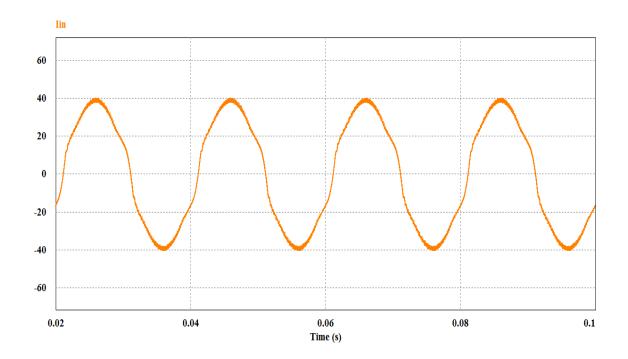

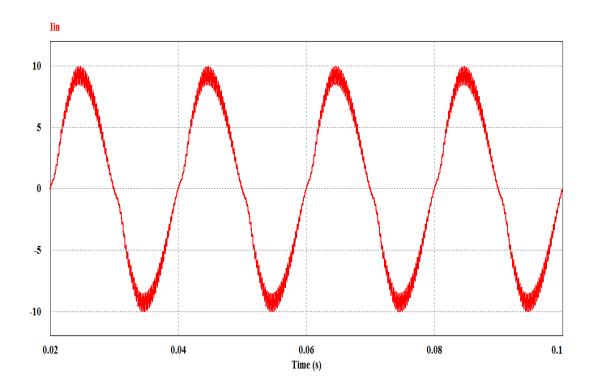

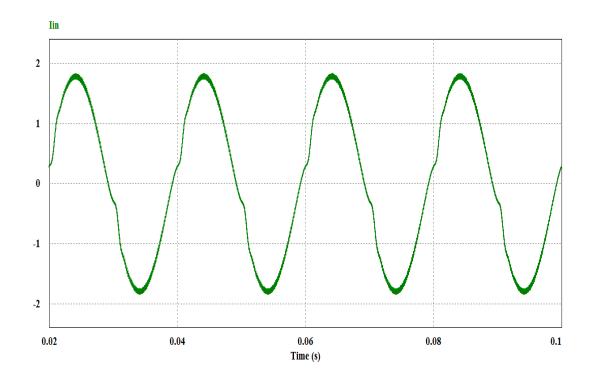

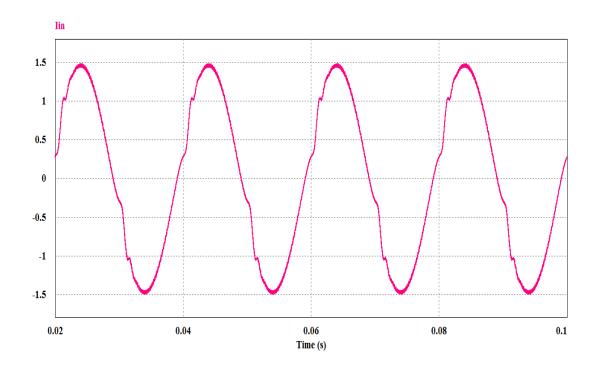

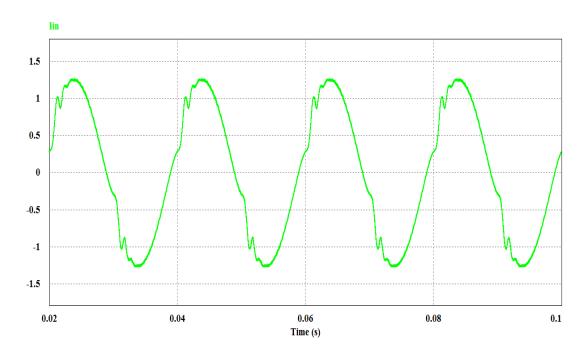

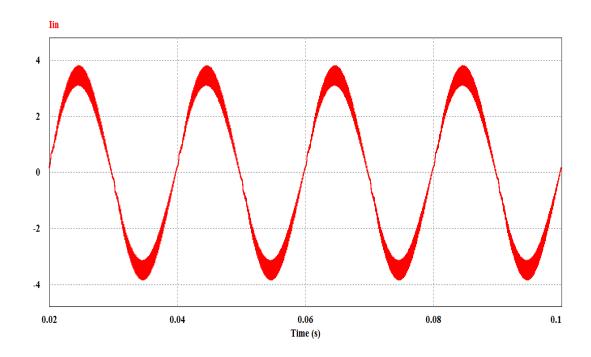

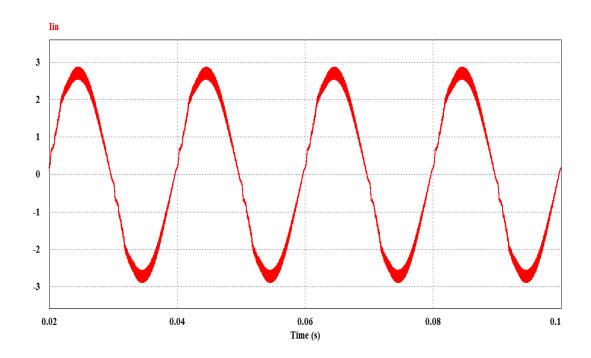

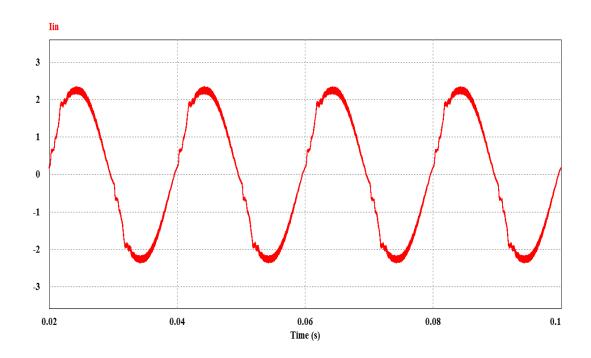

| Fig.6.5  | Input current of proposed SEPIC converter at fs = $4000 \text{ Hz.}$ , D = | 85    |

|          | 0.5                                                                        |       |

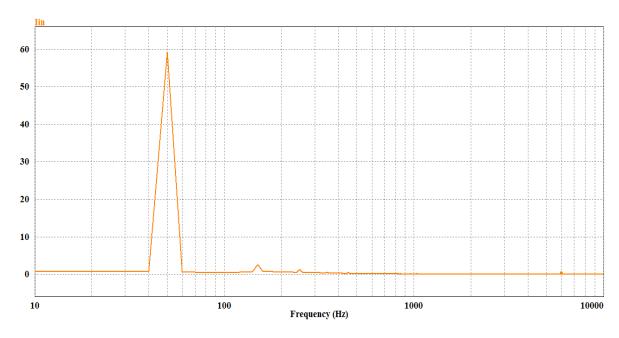

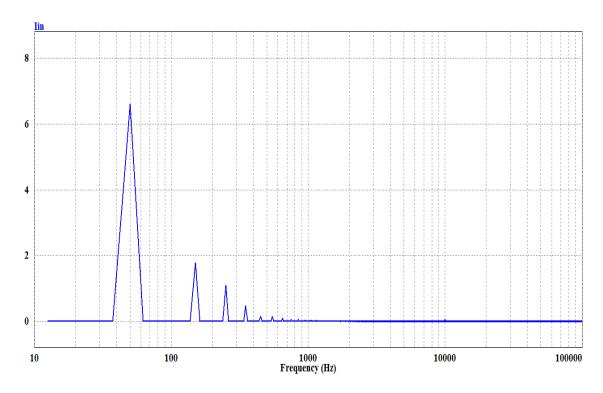

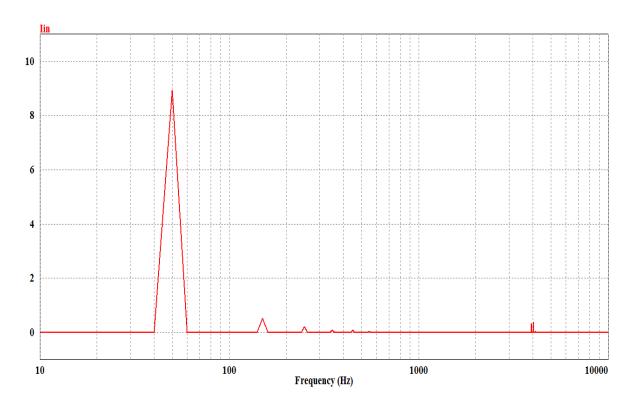

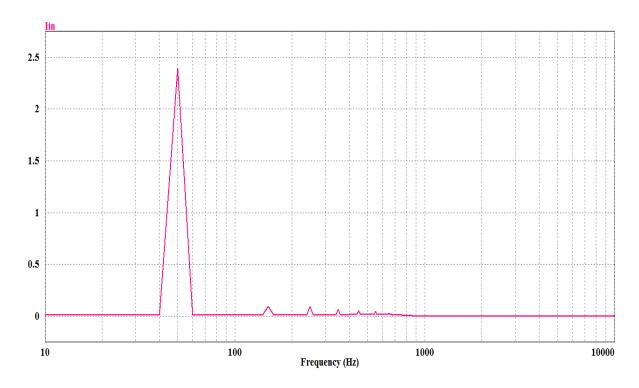

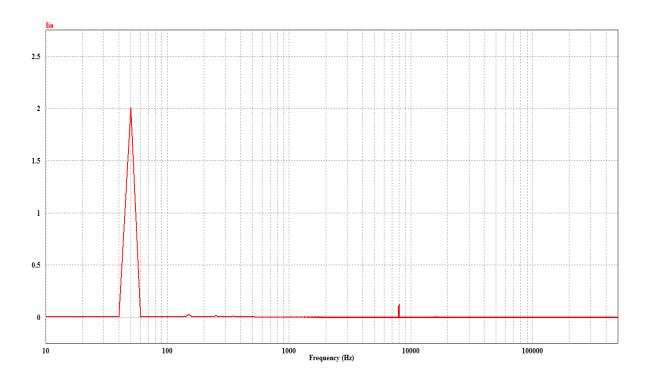

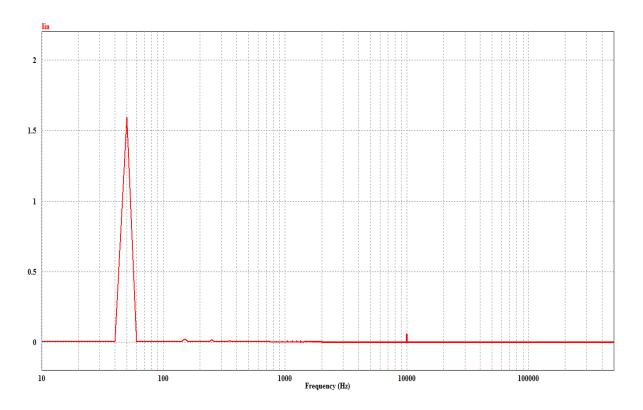

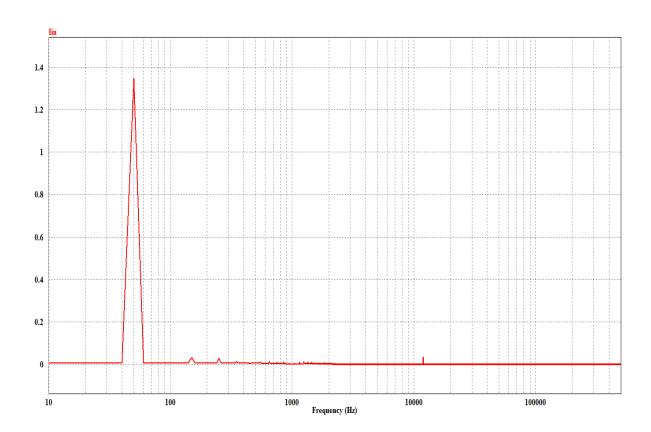

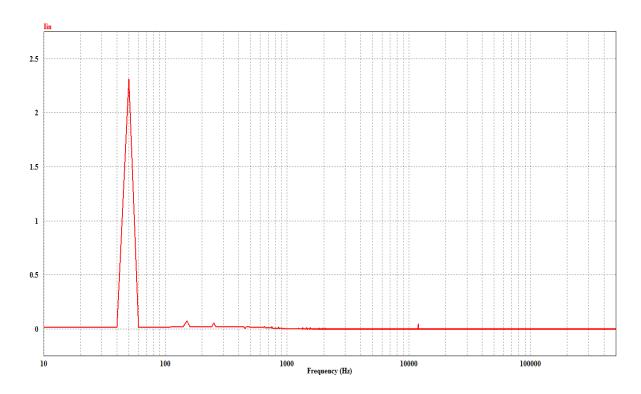

| Fig.6.6  | Input current spectrum of proposed SEPIC converter at fs =                 | 85    |

|          | 4000 Hz. and D= 0.5                                                        |       |

| Fig.6.7  | Input current of proposed SEPIC converter at fs = 6 K Hz. and              | 86    |

|          | D=0.3                                                                      |       |

| Fig.6.8  | Input current spectrum of proposed SEPIC converter at fs = 6 K             | 86    |

|          | Hz. and $D=0.3$                                                            |       |

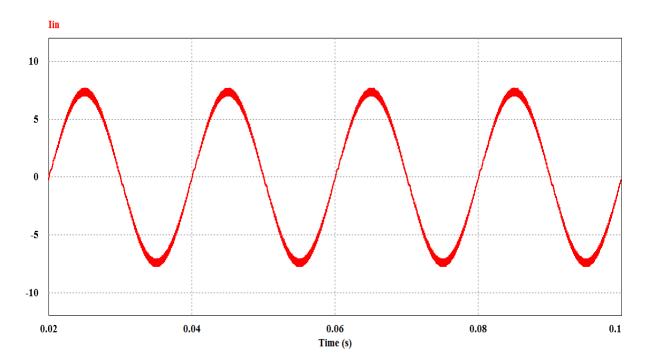

| Fig.6.9  | Input current of proposed SEPIC converter at fs = 6 K Hz. and              | 87    |

|          | D = 0.4                                                                    |       |

| Fig.6.10 | Input current spectrum of proposed SEPIC converter at fs = 6 K             | 87    |

|          | Hz. and $D=0.4$                                                            |       |

| Fig.6.11 | Input current of proposed SEPIC converter at fs = 8 K Hz. and              | 88    |

|          | D=0.3                                                                      |       |

| Fig.6.12 | Input current spectrum of proposed SEPIC converter at fs = 8 K             | 88    |

|          | Hz. and $D=0.3$                                                            |       |

| Fig.6.13 | Input current of proposed SEPIC converter at fs = 8 K Hz. and              | 89    |

|          | D = 0.4                                                                    |       |

| Fig.6.14 | Input current spectrum of proposed SEPIC converter at fs = 8 K             | 89    |

|          | Hz. and $D=0.4$                                                            |       |

| Fig.6.15 | Input current of proposed SEPIC converter at $fs = 10 \text{ K}$ Hz. and   | 90    |

|           | D = 0.3                                                                  |    |

|-----------|--------------------------------------------------------------------------|----|

| Fig.6.16  | Input current spectrum of proposed SEPIC converter at $fs = 10$          | 90 |

|           | K Hz. and $D=0.3$                                                        |    |

| Fig.6.17  | Input current of proposed SEPIC converter at fs = 10 K Hz. and           | 91 |

|           | D=0.4                                                                    |    |

| Fig.6.18  | Input current spectrum of proposed SEPIC converter at fs = 10            | 91 |

|           | K Hz. and D= 0.4                                                         |    |

| Fig.6.19  | Input current of proposed SEPIC converter at fs = 12 K Hz. and           | 92 |

|           | D=0.3                                                                    |    |

| Fig.6.20  | Input current spectrum of proposed SEPIC converter at fs = 12            | 92 |

|           | K Hz. and $D=0.3$                                                        |    |

| Fig.6.21  | Input current of proposed SEPIC converter at $fs = 12 \text{ K}$ Hz. and | 93 |

|           | D = 0.4                                                                  |    |

| Fig.6.22  | Input current spectrum of proposed SEPIC converter at $fs = 12$          | 93 |

|           | K Hz. and $D=0.4$                                                        |    |

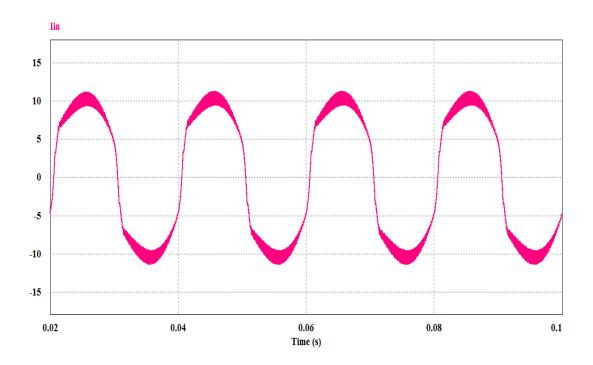

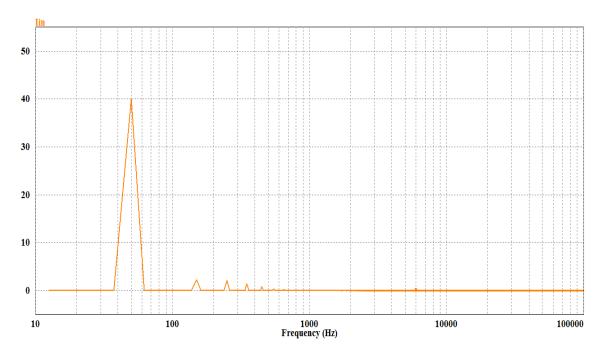

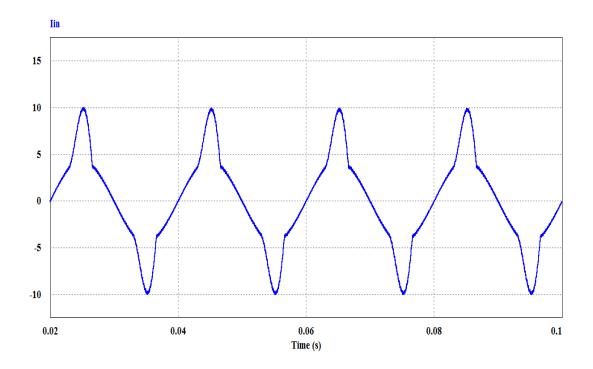

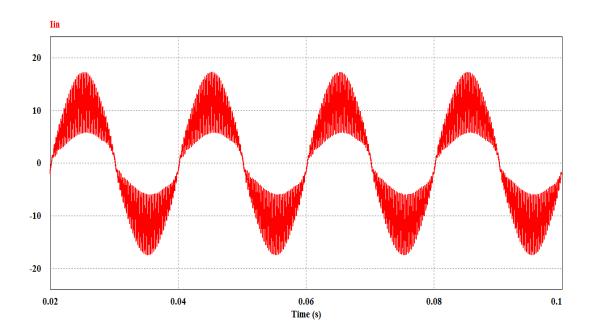

| Fig.6. 23 | Input current of conventional SEPIC converter at fs = 4 K Hz.            | 94 |

|           | and D= 0.5                                                               |    |

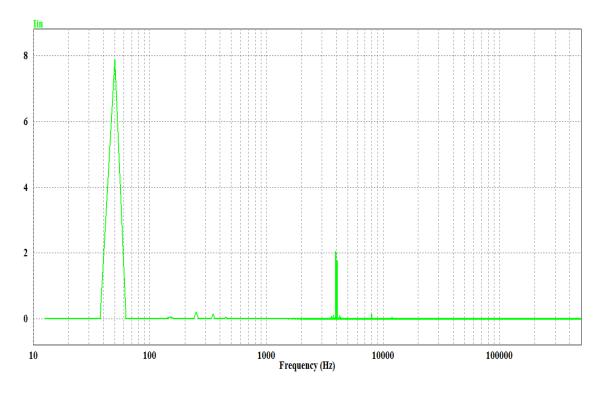

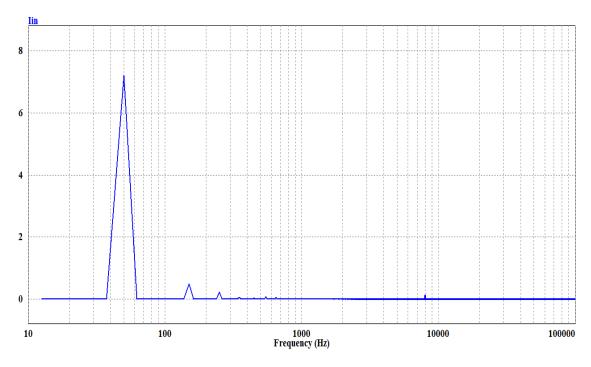

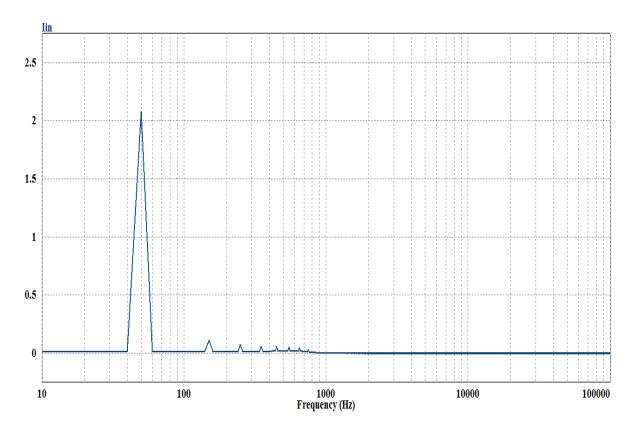

| Fig.6. 24 | Input current spectrum of conventional SEPIC converter at fs =           | 94 |

|           | 4 K Hz. and D= 0.5                                                       |    |

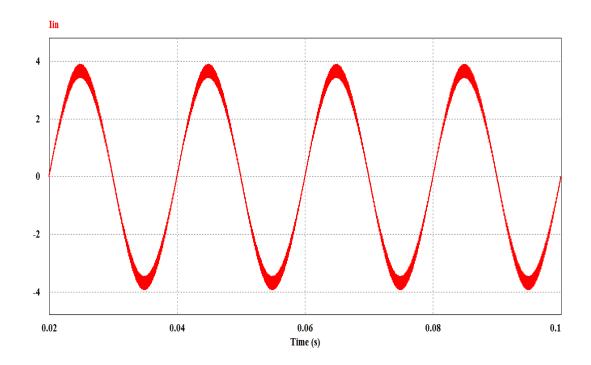

| Fig.6. 25 | Input current of conventional SEPIC converter at fs = 6 K Hz.            | 95 |

|           | and $D=0.3$                                                              |    |

| Fig.6. 26 | Input current spectrum of conventional SEPIC converter at fs =           | 95 |

|           | 6 K Hz. and D= 0.3                                                       |    |

| Fig.6. 27 | Input current of conventional SEPIC converter at fs = 6 K Hz.            | 96 |

|           | and D= 0.4                                                               |    |

| Fig.6. 28 | Input current spectrum of conventional SEPIC converter at fs =           | 96 |

|           | 6 K Hz. and D= 0.4                                                       |    |

| Fig.6. 29 | Input current of conventional SEPIC converter at fs = 8 K Hz.            | 97 |

|           | and $D=0.3$                                                              |    |

| Fig.6.30  | Input current spectrum of conventional SEPIC converter at fs =           | 97 |

|           | 8 K Hz. and D= 0.3                                                       |    |

| Fig.6.31  | Input current of conventional SEPIC converter at fs = 8 K Hz.            | 98 |

|           | and $D=0.4$                                                              |    |

| Fig.6.32 | Input current spectrum of conventional SEPIC converter at fs =           | 98  |

|----------|--------------------------------------------------------------------------|-----|

|          | 8  K Hz.  and  D = 0.4                                                   |     |

| Fig.6.33 | Input current of conventional SEPIC converter at $fs = 10 \text{ K}$ Hz. | 99  |

|          | and $D = 0.3$                                                            |     |

| Fig.6.34 | Input current spectrum of conventional SEPIC converter at fs =           | 99  |

|          | 10  K  Hz.  and  D = 0.3                                                 |     |

| Fig.6.35 | Input current of conventional SEPIC converter at $fs = 10 \text{ K}$ Hz. | 100 |

|          | and D= 0.4                                                               |     |

| Fig.6.36 | Input current spectrum of conventional SEPIC converter at fs =           | 100 |

|          | 10  K Hz.  and  D = 0.4                                                  |     |

| Fig.6.37 | Input current of conventional SEPIC converter at $fs = 12 \text{ K}$ Hz. | 101 |

|          | and $D = 0.3$                                                            |     |

| Fig.6.38 | Input current spectrum of conventional SEPIC converter at fs =           | 101 |

|          | 12 K Hz. and $D=0.3$                                                     |     |

| Fig.6.39 | Input current of conventional SEPIC converter at fs = 12 K Hz.           | 102 |

|          | and D= 0.4                                                               |     |

| Fig.6.40 | Input current spectrum of conventional SEPIC converter at fs =           | 102 |

|          | 12 K Hz. and D= 0.4                                                      |     |

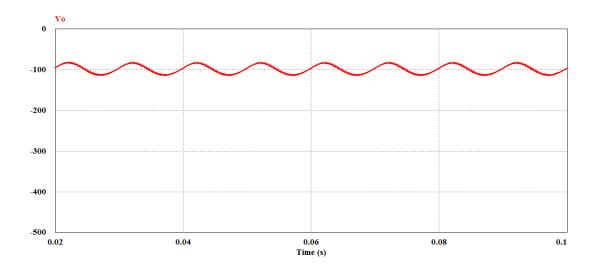

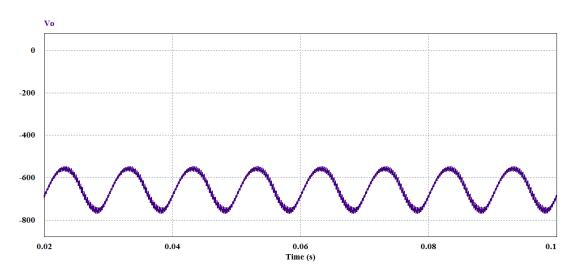

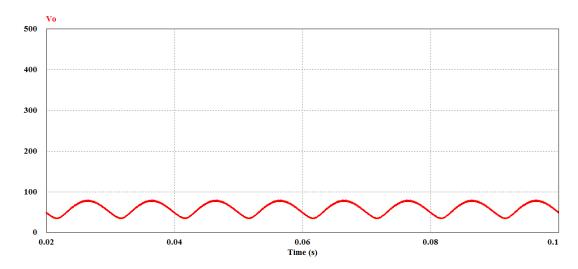

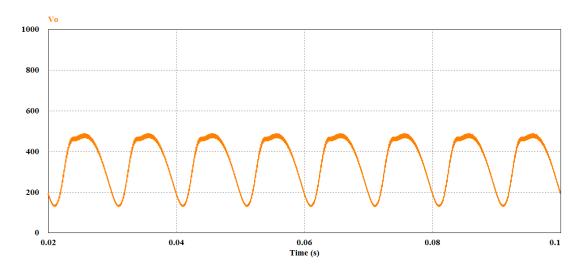

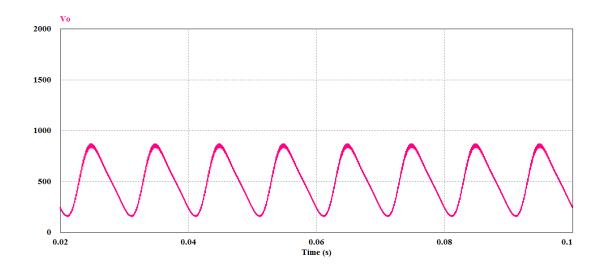

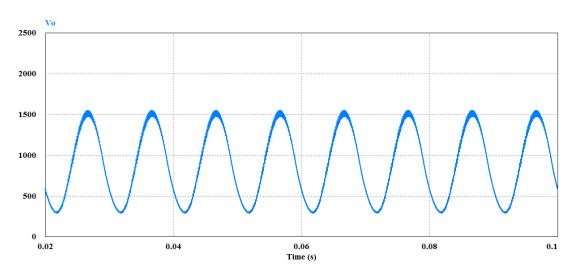

| Fig.6.41 | Output voltage waveform of proposed SEPIC converter at $f_s = 8$         | 103 |

|          | K Hz. and $D=0.1$                                                        |     |

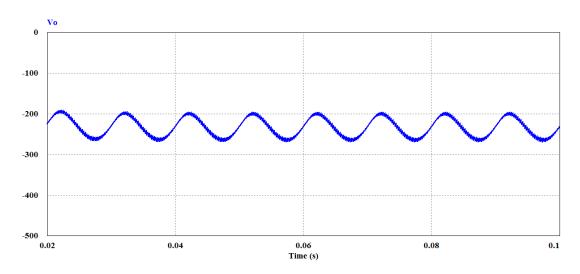

| Fig.6.42 | Output voltage waveform of proposed SEPIC converter at $f_s = 8$         | 103 |

|          | K Hz. and $D=0.2$                                                        |     |

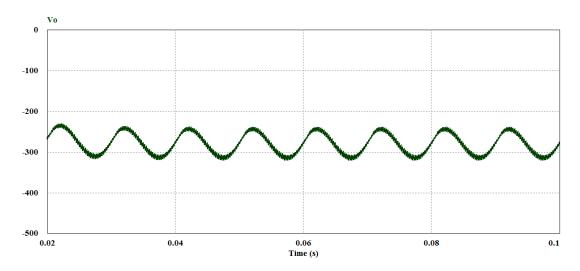

| Fig.6.43 | Output voltage waveform of proposed SEPIC converter at $f_s = 8$         | 103 |

|          | K Hz. and $D=0.3$                                                        |     |

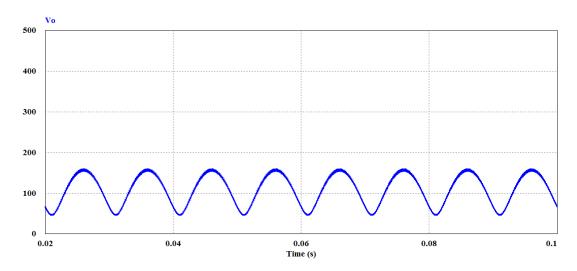

| Fig.6.44 | Output voltage waveform of proposed SEPIC converter at $f_s = 8$         | 104 |

|          | K Hz. and $D=0.4$                                                        |     |

| Fig.6.45 | Output voltage waveform of proposed SEPIC converter at $f_s = 8$         | 104 |

|          | K Hz. and $D=0.5$                                                        |     |

| Fig.6.46 | Output voltage waveform of proposed SEPIC converter at $f_s = 8$         | 104 |

|          | K Hz. and $D=0.6$                                                        |     |

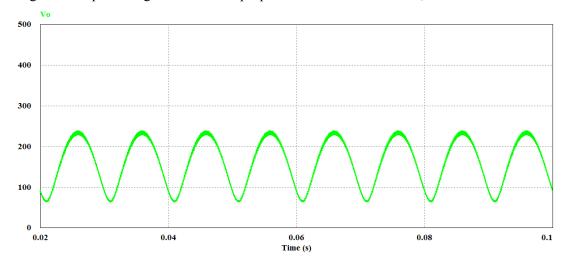

| Fig.6.47 | Output voltage waveform of proposed SEPIC converter at $f_s = 8$         | 105 |

|          | K Hz. and $D=0.7$                                                        |     |

| Fig.6.48 | Output voltage waveform of proposed SEPIC converter at $f_s = 8$         | 105 |

# K Hz. and D=0.8

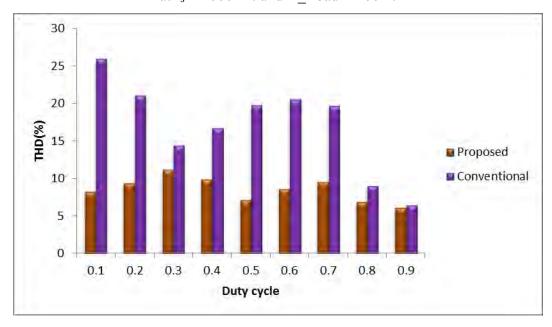

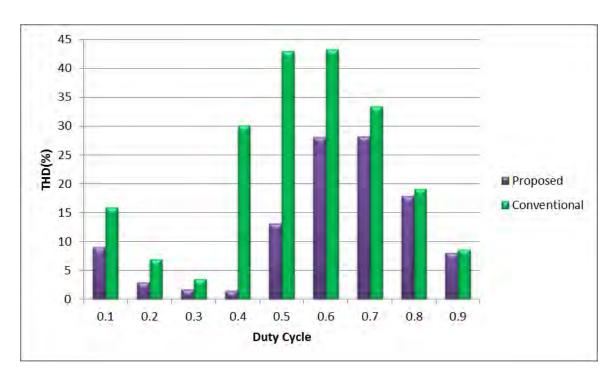

| Fig. 6.49 | Comparison of input current THD (%) between conventional       | 106 |

|-----------|----------------------------------------------------------------|-----|

|           | and proposed scheme at fs = 4 kHz. and R_Load = $100\Omega$ .  |     |

| Fig. 6.50 | Comparison of input current THD (%) between conventional       | 106 |

|           | and proposed scheme at fs = 6 kHz. and R_Load = $100\Omega$ .  |     |

| Fig. 6.51 | Comparison of input current THD (%) between con100ventional    | 107 |

|           | and proposed scheme at fs = 8 kHz. and R_Load = $100\Omega$ .  |     |

| Fig. 6.52 | Comparison of input current THD (%) between conventio101nal    | 107 |

|           | and proposed scheme at fs = 10 kHz. and R_Load = $100\Omega$ . |     |

| Fig. 6.53 | Comparison of input current THD (%) between conventional       | 108 |

|           | and proposed scheme at fs = 12 kHz. and R_Load = $100\Omega$ . |     |

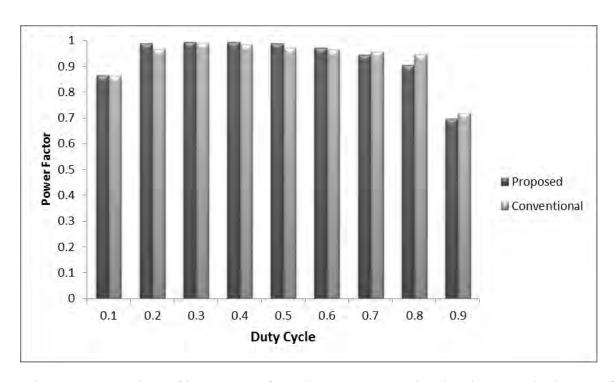

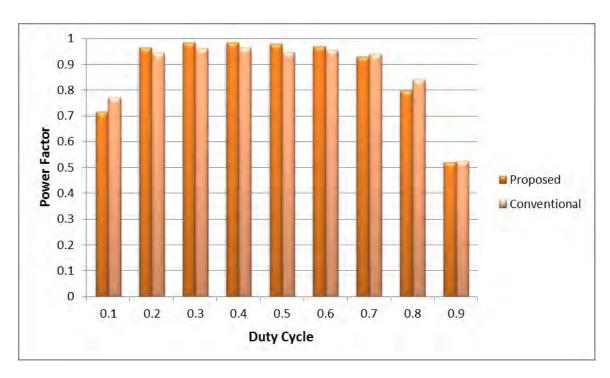

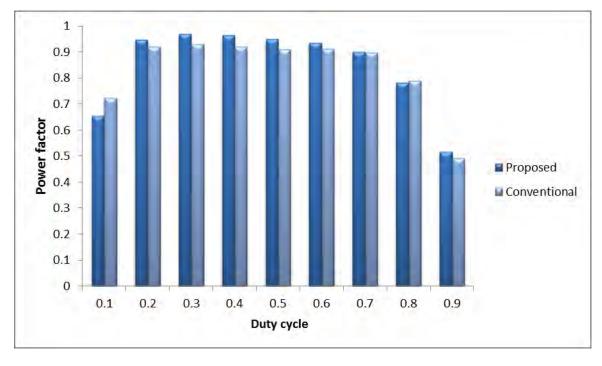

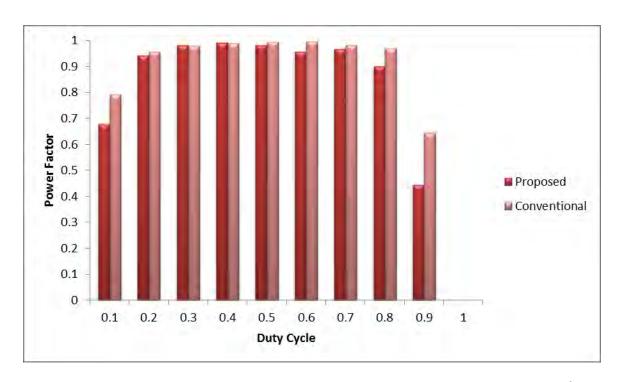

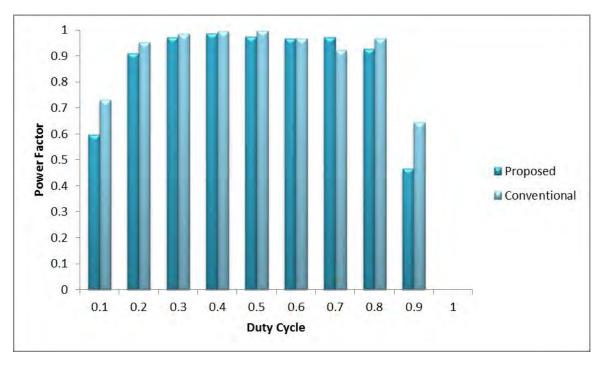

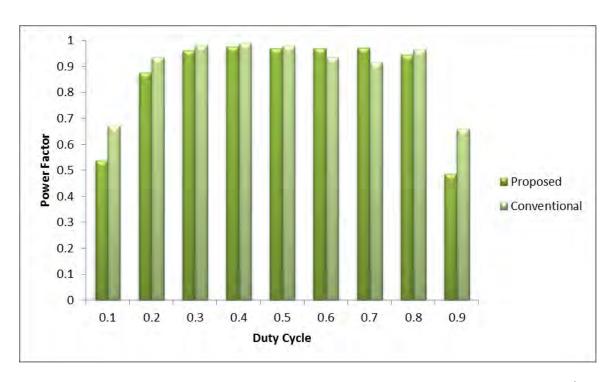

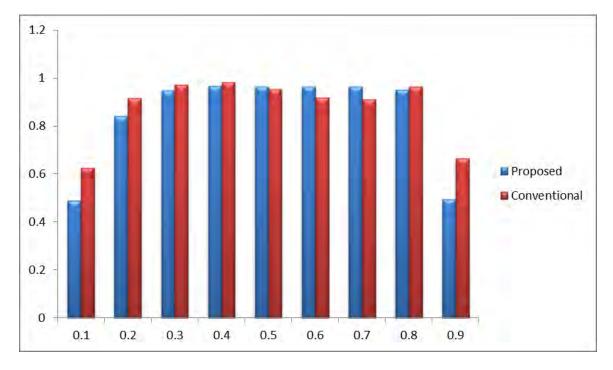

| Fig. 6.54 | Comparison of input power factor between conventional and      | 108 |

|           | proposed scheme at fs = 4 kHz. and R_Load = $100 \Omega$ .     |     |

| Fig. 6.55 | Comparison of input power factor between conventional and      | 109 |

|           | proposed scheme at fs = 6 kHz. and R_Load = $100 \Omega$ .     |     |

| Fig. 6.56 | Comparison of input power factor between conventional and      | 109 |

|           | proposed scheme at fs = 8 kHz. and R_Load = $100 \Omega$ .     |     |

| Fig. 6.57 | Comparison of input power factor between conventional and      | 110 |

|           | proposed scheme at fs = 10 kHz. and R_Load = 100 $\Omega$ .    |     |

| Fig. 6.58 | Comparison of input power factor between conventional and      | 110 |

|           | proposed scheme at fs = 12 kHz. and R_Load = $100 \Omega$ .    |     |

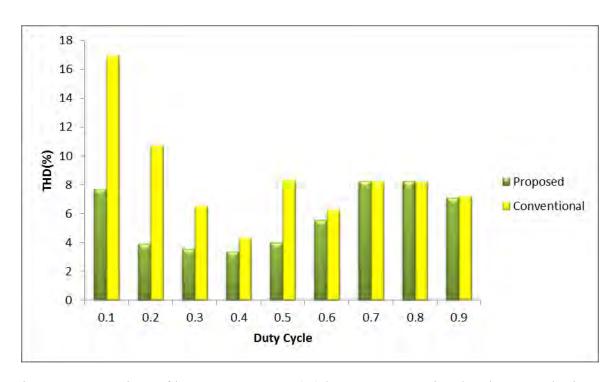

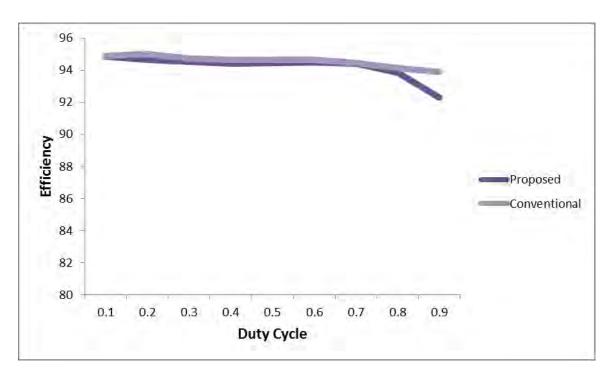

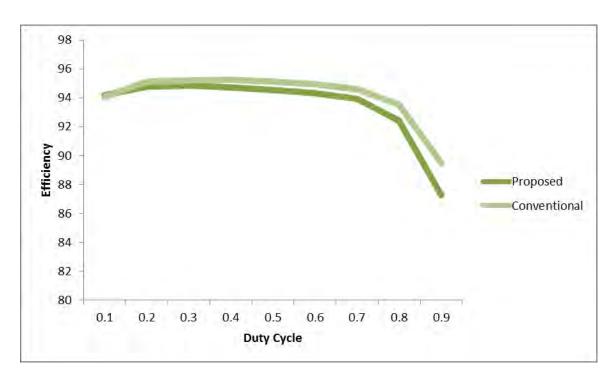

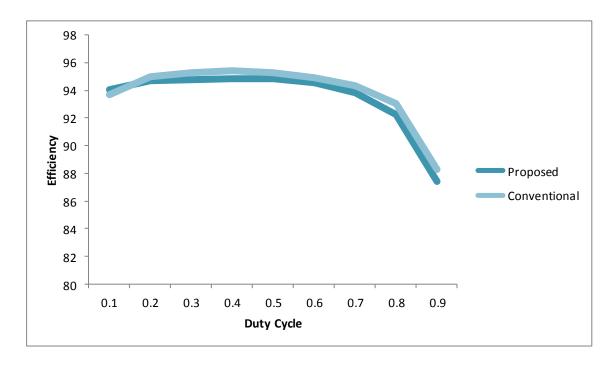

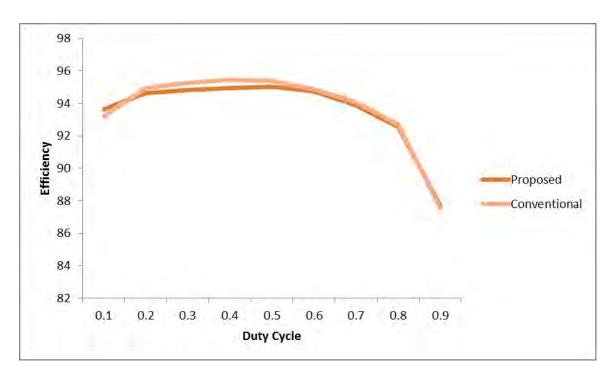

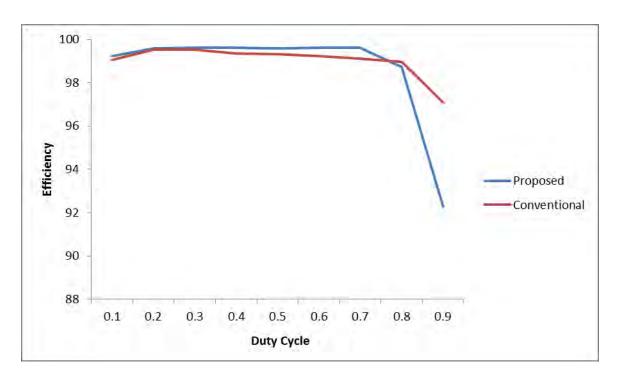

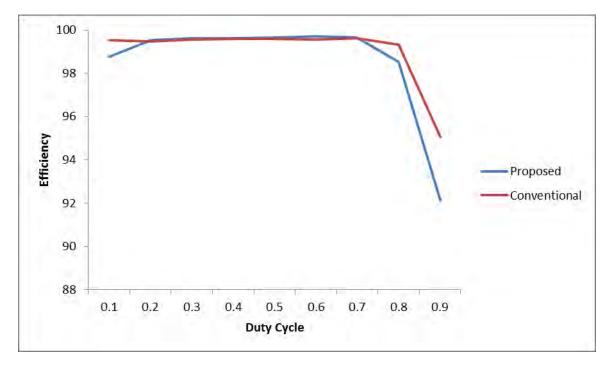

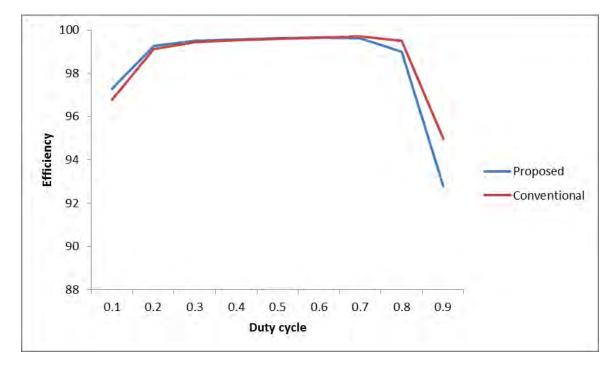

| Fig. 6.59 | Comparison of efficiency (%) between conventional and          | 111 |

|           | proposed scheme at fs = 4 kHz. and R_Load = $100 \Omega$ .     |     |

| Fig. 6.60 | Comparison of efficiency (%) between conventional and          | 111 |

|           | proposed scheme at fs = 6 kHz. and R_Load = $100 \Omega$ .     |     |

| Fig. 6.61 | Comparison of efficiency (%) between conventional and          | 112 |

|           | proposed scheme at fs = 8 kHz. and R_Load = $100 \Omega$ .     |     |

| Fig. 6.62 | Comparison of efficiency (%) between conventional and          | 112 |

|           | proposed scheme at fs = 10 kHz. and R_Load = $100 \Omega$ .    |     |

| Fig. 6.63 | Comparison of efficiency (%) between conventional and          | 113 |

|           | proposed scheme at fs = 12 kHz. and R_Load = $100 \Omega$ .    |     |

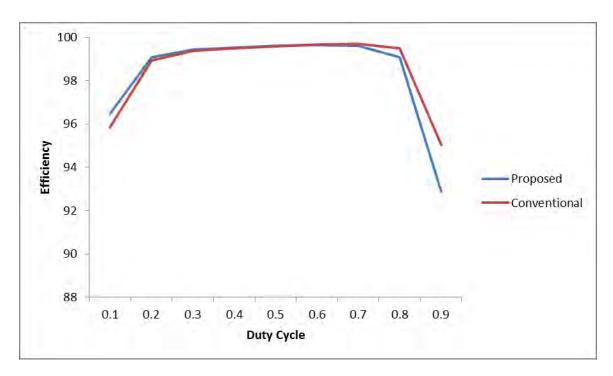

| Fig. 6.64 | Comparison of input power factor between conventional and      | 116 |

|           | proposed scheme with Load variation at $fs = 8$ kHz. and $D = 0.3$ .        |     |

|-----------|-----------------------------------------------------------------------------|-----|

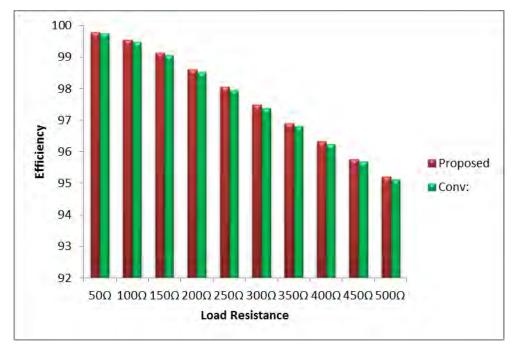

| Fig. 6.65 | Comparison of efficiency between conventional and proposed                  | 116 |

|           | scheme with Load variation at $fs = 8$ kHz. and $D = 0.3$ .                 |     |

| Fig. 6.66 | Comparison of input current THD (%) between conventional                    | 117 |

|           | and proposed scheme with Load variation at $fs = 8 \text{ kHz}$ . and $D =$ |     |

|           | 0.3                                                                         |     |

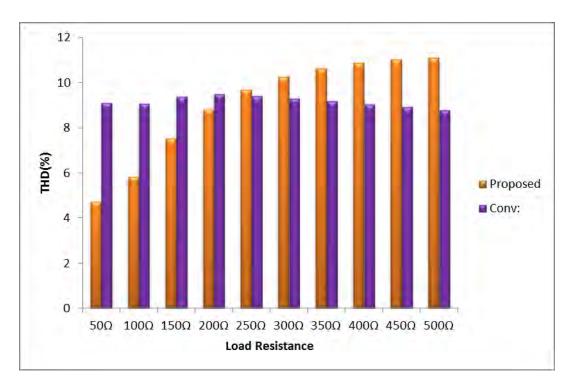

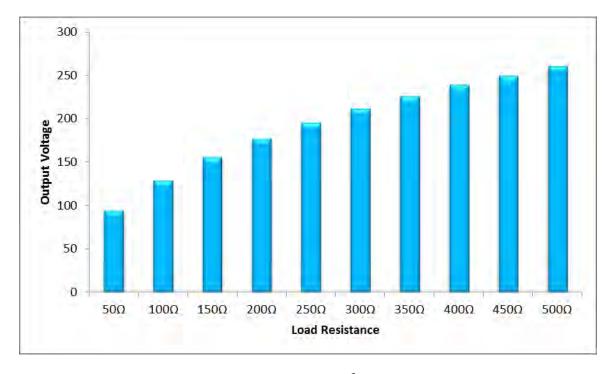

| Fig. 6.67 | Output Voltage of the proposed converter at fs = 8000 Hz. and               | 117 |

|           | D= 0.3 with Load variation.                                                 |     |

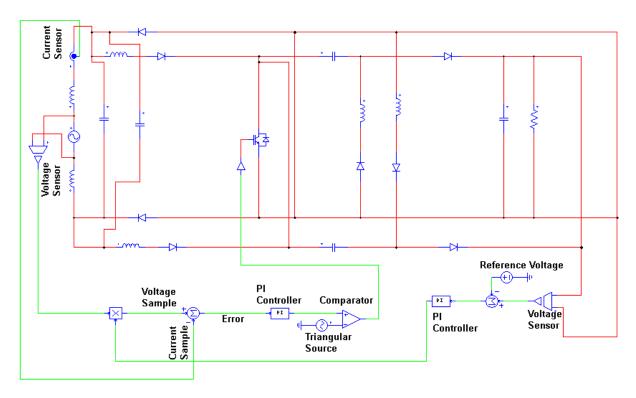

| Fig.6.68  | The Proposed SEPIC Converter with Feedback Controller                       | 118 |

|           | Circuit.                                                                    |     |

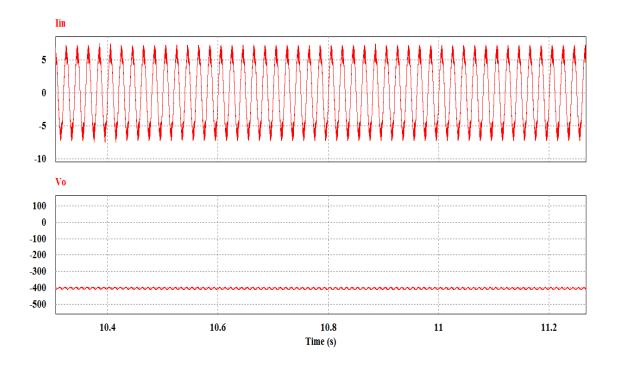

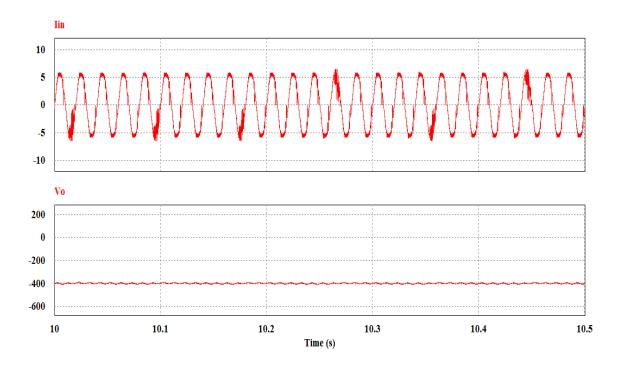

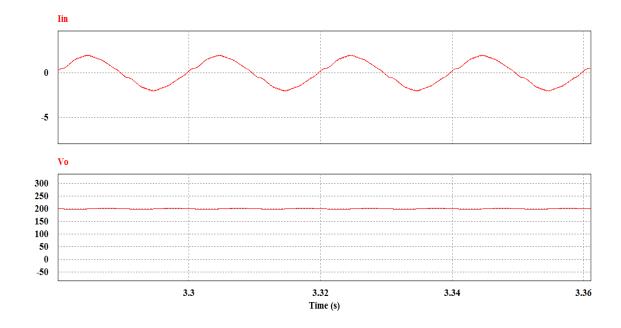

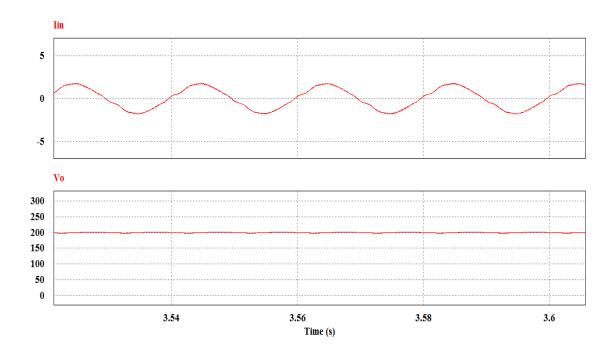

| Fig.6.69  | Input current and output voltage of proposed SEPIC converter                | 119 |

|           | with feedback controller for Load resistance of 100 $\Omega$                |     |

| Fig.6.70  | Input current and output voltage of proposed SEPIC converter                | 119 |

|           | with feedback controller for Load resistance of 200 $\Omega$                |     |

| Fig.6.71  | Input current and output voltage of proposed SEPIC converter                | 120 |

|           | with feedback controller for Load resistance of 300 $\Omega$                |     |

| Fig.6.72  | Input current and output voltage of proposed SEPIC converter                | 120 |

|           | with feedback controller for Load resistance of 400 $\Omega$                |     |

| Fig.6.73  | Input current and output voltage of proposed SEPIC converter                | 121 |

|           | with feedback controller for Load resistance of 500 O                       |     |

#### LIST OF ACRONYMS

AC: Alternating Current

CCM: Continuous Conduction Mode

DCM: Discontinuous Conduction Mode

DC: Direct Current

DM: Differential Mode

IEC: International Electro technical Committee

IEEE: Institute of Electrical and Electronics Engineers

IGBT: Insulated Gate Bipolar Transistor

LN: Line-to-neutral

MOSFET: Metal Oxide Semiconductor Field Effect Transistor

PFC: Power Factor Correction

PWM: Pulse Width Modulation

RMS: Root Mean Square

SEPIC: Single-Ended Primary-Inductor Converter

THD: Total Harmonic Distortion

## LIST OF TABLES

| Table No. | Description                                                 | Page |

|-----------|-------------------------------------------------------------|------|

|           |                                                             | No.  |

| 5.1       | Numerical values of simulation data for proposed AC-DC Ĉuk  | 68   |

|           | converter.                                                  |      |

| 5.2       | Numerical data for proposed Ĉuk converter after introducing | 79   |

|           | feedback controller                                         |      |

| 6.1       | Numerical values of simulation data for proposed AC-DC      | 113  |

|           | SEPIC converter.                                            |      |

| 6.2       | Numerical data for proposed Ĉuk converter after introducing | 121  |

|           | feedback controller                                         |      |

#### **ACKNOWLEDGEMENT**

At first, I want to thank Almighty Allah, the most merciful, the most gracious for giving me the opportunity to complete the thesis.

I would like to express my sincere appreciation to my supervisor, **Dr. Mohammad Jahangir Alam,** Professor, Department of Electrical and Electronic Engineering, Bangladesh

University of Engineering and Technology, Dhaka, Bangladesh for his guidance,

encouragement, and continuous support throughout the completion of this thesis. His

valuable scientific guidance and encouraging attitude have motivated much of the research

described in this dissertation. I think I am fortunate to have worked under his guidance. I

thank him for his support, belief, patience, fairness, and for his feedback. He taught me

attitude, initiative, and how to have passion for what I believe. I have to thank him for the

many opportunities he has given me over the years.

I would like to thank gratefully to **Dr. Mohammad Ali Choudhury,** Professor, Department of Electrical and Electronic Engineering, Bangladesh University of Engineering and Technology, Dhaka, Bangladesh, for his guidance and suggestions for further improvement of my work.

At last, I want to mention about the contribution of my family members who have always encouraged me and rendered their supports to continue my studies and thesis work.

#### **ABSTRACT**

Single phase full wave bridge rectifiers are nonlinear in nature and draws non sinusoidal current from a sinusoidal voltage source. This causes low input power factor and high input current THD and causes a lot of problems in sensitive electronic equipment and high power equipment in power system. There are several methods including passive and active filtering to solve the problem. Passive filtering uses bulky sized inductors and capacitors, while active filtering uses switching mode regulators to improve the input current and power factor. The inductors and capacitors required in active filtering are smaller sized than that of passive filters. Generally, switching is performed in output side of the rectifier, which makes input current high frequency switched. Then a passive filter is used to get low THD and high input power factor. In this thesis, two new topologies of single phase single switch AC-DC converter using Ĉuk and SEPIC conversion is proposed. These converters' input current is chopped at high frequency during positive and negative cycle by a single semiconductor switch to get step up/step down AC to DC conversion, instead of using a single phase rectifier followed by a DC-DC converter or using a bridge rectifier with two diodes and two switches. Comparison is made between proposed and conventional circuit under same Load and operating conditions. The proposed circuit shows better performance i.e. higher power factor and lower THD than conventional one. The efficiency of these converters is also high. No additional control scheme is required to achieve these advantages. The feedback controller circuits are also introduced to the proposed converters to achieve regulated output voltage. The results after connecting the feedback controller are also presented in the thesis.

## **CHAPTER 1**

## INTRODUCTION

#### 1.1 Introduction

Telecommunications and computer industries have become essential part of modern society. Currently electric vehicles are occupying the place of conventional vehicles due to their environment friendly technology. DC power supply is necessary to run these devices, which consist of battery storage and charging system. Moreover renewable energy specially the solar energy is becoming a dominating power source in almost every country. DC power conditioning and processing is a major challenge in these sectors. The DC power supply is also required in operating sensitive electronic devices, separating magnets, particle acceleration, fusion, electrolyte cells, electro refining, chemical process, industrial cranes, protective and measuring instrument like relay and in DC motors. In most of the cases this DC power supply has come from AC supply. That's why input power factor, input current THD and efficiency are the major issues to be considered while using AC-DC conversion.

### 1.2 Background

Single phase full wave bridge rectifier draws non sinusoidal currents from sinusoidal voltage source due to its non-linear characteristics. Several power quality problems arise at source side due to this non-linear characteristic. These problems include low input power factor, high input current THD, failure of transformer due to overheating, interference at communication channel, harmonic pollution at power system [1,2] etc. Due to harmonic pollution at power system power supply is interrupted, which cause malfunction or damage of sensitive electric device. Restrictions on current and voltage harmonics are maintained through IEEE 519-1992 and IEC 61000-3-2/IEC 61000-3-4[3] standard in most of the countries.

There are several methods to solve the problem of harmonic pollution in power system and new methods are still being investigated. One of these methods is to use a passive filter in input side. This filter consists of an inductor and a capacitor, which are bulky in size. This filter can improve THD but input power factor remains low. Moreover using bulky inductor and capacitor imposes a restriction on using it for high power application. To overcome these problems switch mode regulator has been introduced. This method employs a single phase

rectifier followed by a DC-DC converter. This method is also known as active filtering [4-10]. In this case the input filter required is relatively smaller than passive filter. Moreover improved input power factor is achieved in this method.

The Boost DC-DC converter is commonly used after rectifier for power factor correction. Buck, Buck-Boost etc. are also used to get different input/output voltage gain relationship [10-18]. The DC-DC converters chop the input current at high frequency which can be filtered with a low pass filter to get near sinusoidal input current with high input power factor and low THD.

The DC-DC converter use unidirectional switch for switching purpose, which may be a BJT, MOSFET or IGBT. The boost rectifier must be operated in critical mode [19-22] in boost regulated AC-DC conversion. In this case the switch should be ON at the instant of zero current in the boost diode. This needs variable switching frequency operation of the DC-DC converter with the change of load or source voltage. Another approach for boost regulated rectifier involves controlling to a constant level of the average current of the boost diode [18-22]. To do this the duty cycle must be modulated.

In this thesis, two new single phase single switch AC-DC converters on Ĉuk and SEPIC topologies of high performance are reported. Very few remarkable works are done with Ĉuk and SEPIC topology based AC-DC converter. Ĉuk topology has several advantages over Buck-Boost topology like continuous input and output current. Moreover Ĉuk converter supplies energy to load both when switch is open and close. Ĉuk circuit has also reduced circuit parameters than SEPIC converter, hence reduces cost [3, 23-26]. Similarly SEPIC topology has advantage of less active components than conventional Boost+Buck or Buck+Boost converter. It also has other advantages like low noise operation, simple control scheme etc. Moreover SEPIC is more stable and produces less power ripples than Ĉuk converter. Ĉuk topology is frequently used in renewable energy sector [25-26].

The proposed converters chop input current by a single switch. These converters are different from conventional DC-DC converter regulated rectifiers because input current switching ensures input AC current to be almost in phase with input voltage without any control scheme. This would result almost sinusoidal input current with using of small filter and also ensure good input power factor. The proposed converters provide step up/step down output DC voltage with the duty cycle control of switch. The efficiency is also high for both converters.

#### 1.3 Goal of the thesis

The objectives of the proposed work are

- 1. To develop and design of schemes for high input power factor, high efficiency single switch AC-DC converter.

- 2. To select the circuit parameters to achieve low THD, high input power factor and efficiency.

- 3. To analyze the performance of proposed circuits by simulation.

- 4. To compare the performance of proposed schemes with conventional switch mode AC-DC SEPIC and Ĉuk converter (rectifier followed by DC-DC converter).

#### 1.4 Thesis Organization

This thesis consists of seven chapters.

Chapter-1 is the introduction of the thesis work and provides a brief discussion about back ground and objective of this research.

Chapter-2 illustrates the types of Diode Rectifier, their construction, operation principle, wave shapes and performance of these rectifiers.

Chapter-3 describes the operation of linear regulator circuit and a simple chopper circuit. Then it illustrates types of dc-dc converter, their construction, operation principle wave shapes etc.

Chapter-4 discusses the idea of power factor and power factor correction, necessity of power factor correction, methods of power factor correction and selection of appropriate method of power factor correction in details.

Chapter-5 presents the proposed converter based on Ĉuk topology. It describes the circuit configurations, analyzes their operation and presents their performance under different frequencies and different load conditions.

Chapter-6 presents the proposed converter based on SEPIC topology. It describes the circuit configurations, analyzes their operation and presents their performance under different frequencies and different load conditions.

Chapter-7 concludes the thesis with a summary on the research and suggests for future works.

## **CHAPTER 2**

## RECTIFIERS

#### 2.1 Introduction

A rectifier is a circuit that converts an AC supply to a unidirectional output. Diodes are extensively used in rectifier circuits.

Diode rectifiers are of two types:

- 1. Single phase Diode rectifier.

- 2. Three phase Diode rectifier.

There are two types of single-phase diode rectifier:

- 1. Full wave Rectifier.

- 2. Half wave Rectifier.

There are also two types of three-phase diode rectifier:

- 1. Full wave Rectifier.

- 2 Half wave Rectifier

In the following subsections, the operations of these rectifier circuits are investigated. To avoid complexity the diodes are considered to be ideal, that is, they have zero forward voltage drop and reverse recovery time. Furthermore, it is assumed that the load is purely resistive such that load voltage and load current have similar waveforms.

#### 2.2 Single-Phase Half-Wave Rectifiers

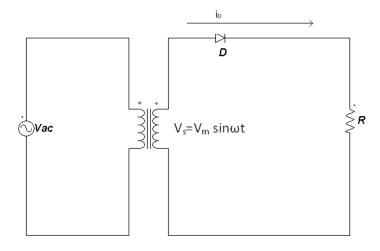

The single-phase diode rectifier is the simplest rectifier. A single-phase half-wave rectifier with resistive load is shown in Fig. 2.1. The circuit consists of one diode that is normally connected to a transformer secondary as shown. During the positive half-cycle of the transformer secondary voltage, diode D conducts. During the negative half-cycle, diode D does not conduct. Providing perfect sinusoidal voltage on its secondary winding, the voltage and current waveforms of resistive load R and the voltage waveform of diode D are shown in Fig. 2.2.

Fig. 2.1 A single-phase half-wave rectifier with resistive load.

Fig. 2.2 Voltage and current waveforms of the half-wave rectifier with resistive load.

## 2.3 Single-Phase Full-Wave Rectifiers

There are two types of single-phase full-wave rectifier,

- 1. Full-wave rectifiers with center-tapped transformer

- 2. Bridge rectifiers.

## 2.3.1. Full-Wave Rectifiers with Center-Tapped Transformer

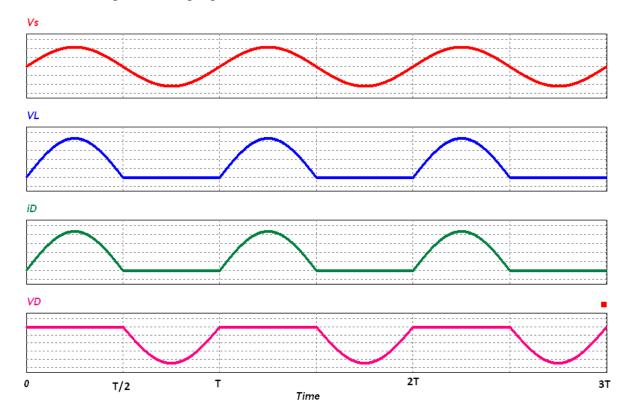

A full-wave rectifier with a center-tapped transformer is shown in Fig. 2.3. In this full wave rectifier each diode is associated with the half of the transformer and acts as a half-wave rectifier. The outputs of the two half-wave rectifiers are combined to produce full-wave rectification in the load.

Fig. 2.3 Full-wave rectifier with center-tapped transformer.

As the transformer is concerned, the DC currents of the two half-wave rectifiers are equal and opposite, such that there is no DC current for creating a transformer core saturation problem. The voltage and current waveforms of the full-wave rectifier are shown in Fig. 2.4.

Fig. 2.4 Voltage and current waveforms of the full-wave rectifier with center-tapped transformer.

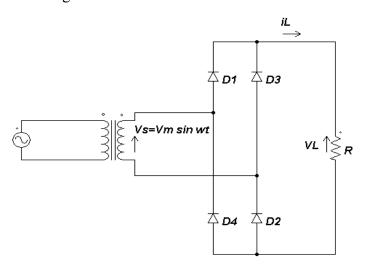

## 2.3.2 Bridge Rectifiers

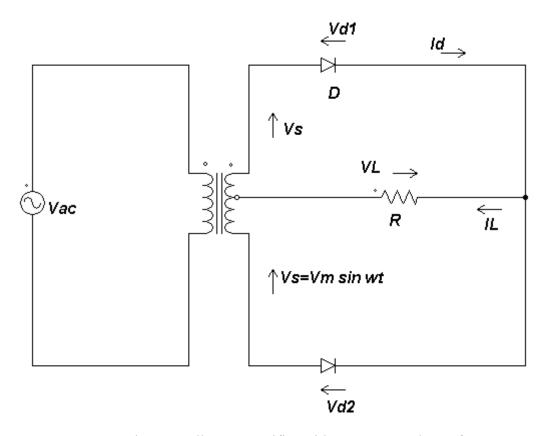

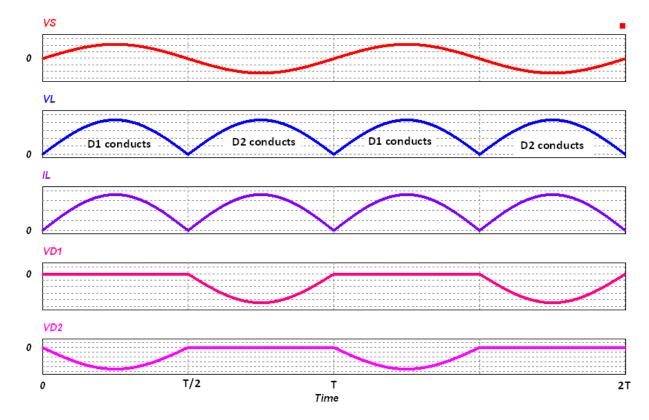

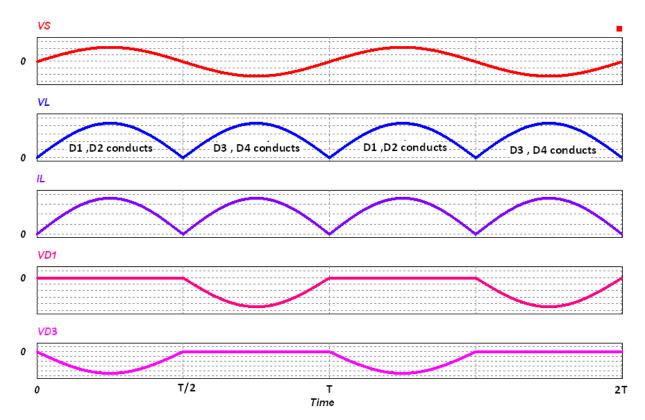

Using four diodes instead of two, a bridge rectifier as shown in Fig. 2.5 can provide full-wave rectification without using a center-tapped transformer. During the positive half-cycle of the transformer secondary voltage, the current flows to the load through diodes D1 and D2. During the negative half cycle, D3 and D4 conduct. The voltage and current waveforms of the rectifier is shown in Fig. 2.6.

Fig. 2.5 Bridge rectifier.

Fig. 2.6 Voltage and current waveforms of the bridge rectifier.

#### 2.3.3 Performance Parameters

In this section the performance of the rectifiers mentioned in the preceding will be evaluated in terms of the following parameters.

The average value of the load voltage  $v_L$  is  $V_{dc}$  and it is defined as

$$V_{dc} = \frac{1}{T} \int_{0}^{T} VL(t)dt.$$

(2.1)

Therefore, for half wave rectifier

$$V_{dc} = 0.318 \ V_m \dots (2.2)$$

In the case of a full-wave rectifier,  $v_L$  (t)=Vm sin  $\omega t$  for both the positive and negative half-cycles. Hence,

$$V_{dc} = \frac{1}{\pi} \int_0^{\pi} Vm \sin \omega t \ d(\omega t) \dots (2.3)$$

Therefore, for half wave rectifier

$$V_{dc} = 0.636 V_{m}$$

(2.4)

The root-mean-square (rms) value of load voltage v is V<sub>rms</sub>, which is defined as

$$V_{rms} = \sqrt{\frac{1}{T} * \int_{0}^{T} V^{2}(t) dt}$$

(2.5)

Therefore, for half wave rectifier

$$V_{rms} = 0.5 V_{m}$$

(2.6)

In the case of a full-wave rectifier,  $v(t) = V_m \sin \omega t$  for both the positive and negative half-cycles. Hence, for half wave rectifier

$$V_{rms} = \sqrt{\frac{1}{\pi} * \int_{0}^{\pi} (Vm \sin \omega t)^{2} (t) d(\omega t)} .....(2.7)$$

$$= 0.707 V_{m}$$

The result is as expected because the rms value of a full-wave rectified voltage should be equal to that of the original AC voltage.

The rectification ratio, which is a figure of merit for comparing the effectiveness of rectification, is defined as

$$\sigma = \frac{Pdc}{PL} \tag{2.8}$$

In the case of a half-wave diode rectifier, the rectification ratio  $\sigma$  is 40.5%, and for a full-wave rectifier, the rectification ratio  $\sigma$  is 81%

#### 2.4 Three-Phase Diode Rectifiers

Single-Phase diode rectifiers are suitable only for low to medium power applications. For power output higher than 15 kW, three-phase or poly-phase diode rectifiers are used. There are two types of three-phase diode rectifier that convert a three-phase AC supply into a DC voltage, star rectifiers and bridge rectifiers. In the following subsection, the operations of these rectifiers are investigated and their performances are analyzed. For the sake of simplicity, the diodes and transformers are considered to be ideal, that is, the diodes have zero forward voltage drop and reverse current, and the transformers do not have either resistance or leakage inductance. Furthermore, it is assumed that the load is purely resistive, such that the load voltage and the load current have similar waveforms.

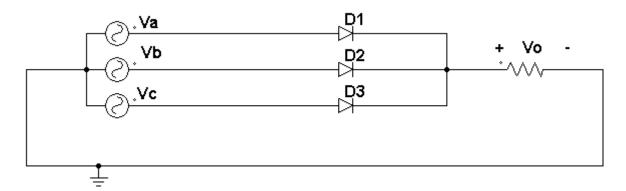

#### 2.4.1 Three-Phase Star Rectifiers

A half bridge three-phase star rectifier circuit is shown in Fig. 2.7. This circuit can be considered as three single-phase half-wave rectifiers combined together. For this reason, it is sometimes referred to as a three-phase half-wave rectifier. The diode in a particular phase conducts during the period when the voltage on that phase is higher than that on the other two phases. The voltage waveforms of each phase and the load are shown in Fig. 2.8. This circuit is used where the required DC output voltage is relatively low and the required output current is too large for a practical single-phase system.

Fig. 2.7 Three-phase star rectifier.

The average value of the output is

$$\begin{split} V_{dc} = & \frac{3}{2\pi} \int_{\pi/6}^{5\pi/6} Vm \sin\theta \ d\theta \qquad (2.9) \\ & \text{or,} \\ V_{dc} = & \frac{3\sqrt{3}}{2\pi} V_m \end{split}$$

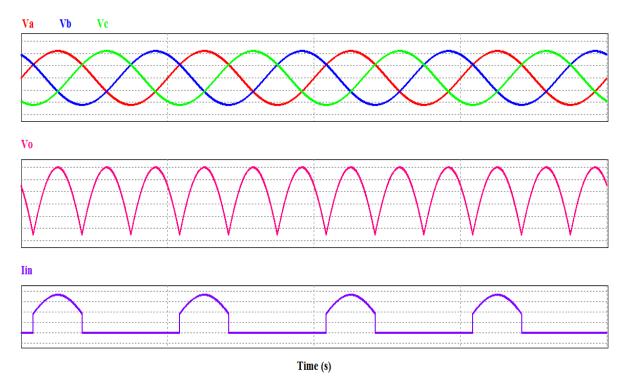

Fig. 2.8 Waveforms of voltage and current of the three-phase star rectifier

## 2.4.2 Three-Phase Bridge Rectifirs

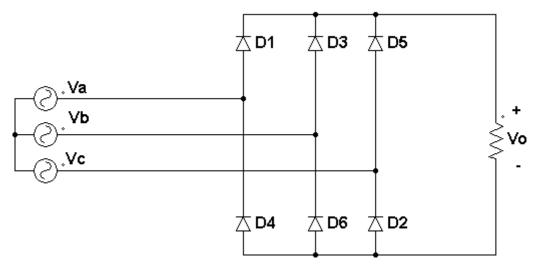

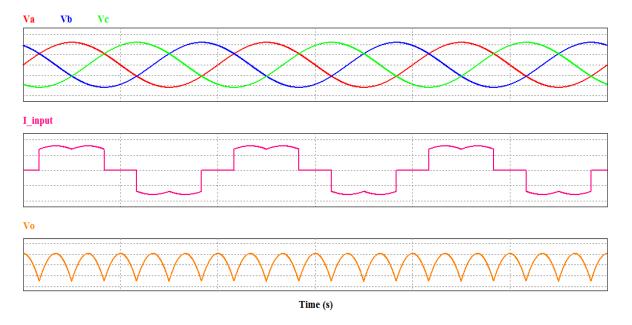

The commonly used rectifiers for high-power applications are three-phase bridge rectifiers because of their highest possible transformer utilization factor for a three-phase system. The circuit of a three-phase bridge rectifier is shown in Fig. 2.9. The diodes are numbered in the order of conduction sequences and the conduction angle of each diode is  $2\pi = 3$ . The conduction sequence for diodes is 12, 23, 34, 45, 56 and 61. The voltage and current waveforms of the three-phase bridge rectifier are shown in Fig. 2.10. The line voltage is  $\sqrt{3}$  times the phase voltage of a three-phase star-connected source. There is no problem to use any combination of star- or delta- connected primary and secondary windings because the currents associated with the secondary windings are symmetrical.

Fig. 2.9 Three-phase bridge rectifier.

The average value of the output can be found as,

$$V_{dc} = \frac{6}{2\pi} \int_{\pi/3}^{2\pi/3} \sqrt{3} \text{ Vm sin } \Theta \ d\Theta .....(2.10)$$

$$\text{or,}$$

$$V_{dc} = \frac{3\sqrt{3}}{\pi} V_{m}$$

Fig. 2.10 Voltage and current waveforms of the three-phase bridge rectifier.

## **CHAPTER 3**

### DC-DC CONVERTERS

#### 3.1 Introduction

The conversion of variable DC voltage from a fixed DC voltage source is required frequently in many industrial applications. A converter that converts DC directly from DC is known DC-DC converter. DC converters are widely used in motor controlling, trolley cars, marine hoists, forklift trucks and mine haulers. Moreover DC converters can be used as a DC voltage regulators as well as the conjunction with an inductor, which can be used as a current source.

Linear power regulators operate based on the principle of voltage divider or current divider, which are inefficient. This is because their output voltages are always smaller than the input voltage. Linear regulators can, however, provide a very high-quality output voltage. These regulators can be used in low power levels. But at low and medium power levels switching regulators are used. Power electronic semiconductor switches (like BJT, MOSFET, IGBT etc.) are used in switching regulators because of their small power loss in both states (low voltage across a switch in the on state, zero current through a switch in the off state). Moreover, switching regulators are efficient for power conversion. Modern power electronic switches can operate at high frequencies. By applying higher switching frequency, we can reduce the size of inductors and capacitors. In addition, the dynamic characteristics of converters improve with increasing operating frequencies.

High operating frequencies allow achieving faster dynamic responses to rapid changes in the load current and the input voltage. The functions of DC-DC converters are:

- I. to convert a DC input voltage  $V_S$  into a DC output voltage  $V_O$ ;

- II. to regulate the DC output voltage against load and line variations;

- III. to reduce the AC voltage ripple on the DC output voltage below the required level;

- IV. to protect the supplied system and the input source from electromagnetic interference (EMI);

- V. to satisfy various international and national safety standards;

- VI. to provide isolation between the input source and the load (isolation is not always required).

The DC-DC converters can be divided into two main types:

I. hard-switching pulse width modulated (PWM) converters

#### II. resonant and soft-switching converters.

This chapter deals with PWM DC-DC converters, which are widely used at all power levels. Advantages of PWM converters include low component consumption, high conversion efficiency, constant frequency operation, relatively simple control scheme and commercial availability of integrated circuit controllers and ability to achieve high conversion ratios for both step-down and step-up application. A disadvantage of PWM DC-DC converters is that PWM rectangular voltage and current waveforms cause turn-on and turn-off losses in semiconductor devices, which limit practical operating frequencies to hundreds of kilohertz. Rectangular waveforms also inherently generate EMI.

This chapter begins with a discussion on DC choppers that are used primarily in DC motor drives. The output voltage of DC choppers is controlled by adjusting the on time of a switch, which in turn adjusts the width of an output voltage pulse. That's why it is called pulse width modulation (PWM) control. The DC choppers with additional filtering components form PWM DC-DC converters.

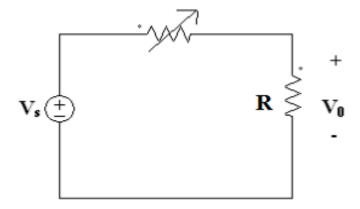

#### 3.2 Linear Regulator

A basic linear regulator with a resistive load is shown in Fig. 3.1. It consists of a series connection of a DC input voltage source  $V_S$ , a variable resistance, and load resistance R. To keep the output voltage fixed with the variation of input voltage or load, this regulator adjusts the variable resistance.

Fig. 3.1 Linear regulator circuit.

# 3.3 DC Choppers

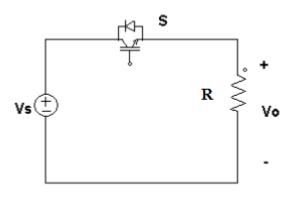

A step-down DC chopper with a resistive load is shown in Fig. 3.2. It consists of a series connection of a DC input voltage source  $V_S$ , controllable switch S, and load resistance R. In most cases, switch S is unidirectional. Power electronic switches are usually implemented with power MOSFETs, IGBTs, MCTs, power BJTs, or GTOs. Fig. 3.3 shows waveforms of a step-down chopper. The switch is operated with a duty ratio, D defined as a ratio of the on time to the sum of the on and off times of the switch.

$$D = \frac{\text{Ton}}{\text{Ton+Toff}} = \frac{\text{Ton}}{\text{T}}...(3.1)$$

Fig. 3.2 DC chopper circuit.

Fig. 3.3 Output voltage waveform of a DC chopper with resistive load.

The average value of the output voltage is

$$V_0 = DV_S$$

....(3.2)

Vo can be regulated by adjusting the duty ratio D. The average output voltage is always smaller than the input voltage.

## 3.4 Buck (Step-Down) Converter

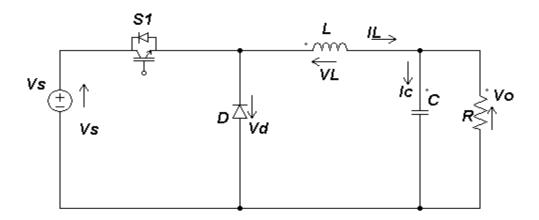

The step-down DC-DC converter, commonly known as a buck converter, is shown in Fig. 3.4. It consists of DC input voltage source V<sub>S</sub>, controlled switch S, diode D, filter inductor L, filter capacitor C, and load resistance R. The operation of this converter is shown in Fig. 3.5. Typical waveforms of the converter are shown in Fig. 3.6. The state of the converter in which the inductor current never reaches to zero for any period of time is called the continuous conduction mode (CCM). It can be seen from the circuit that when the switch S is in on state, the diode D is reverse-biased. When the switch S is off, the diode conducts to support an uninterrupted current in the inductor.

Fig. 3.4 Buck DC-DC converter.

Fig. 3.5 Equivalent circuit of Buck DC-DC converter when (a) switch closed (b) switch open

Fig. 3.6 Waveforms of Buck converter

The relationship among the input voltage, output voltage, and the switch duty ratio D can be derived, for instance, from the inductor voltage  $V_L$  waveform. For the buck converter,

$$(Vs - Vo) DT = - Vo(1 - D)T$$

Hence, the DC voltage transfer function, defined as the ratio of the output voltage to the input voltage, is

$$D = \frac{Vo}{Vs}$$

(3.3)

It can be seen from Eq. 3.4 that the output voltage is always smaller than the input voltage. The DC-DC converters can operate in two modes with respect to the inductor current  $I_L$ . Figure 3.6 shows the CCM in which the inductor current is always greater than zero. When the average value of the output current is low (high R) or the switching frequency f is low, the converter may enter the discontinuous conduction mode (DCM).

For the buck converter, the value of the filter inductance that determines the boundary between CCM and DCM is given by

$$L_{b} = \frac{(1-D)R}{2f}.$$

(3.4)

To limit the peak-to-peak value of the ripple voltage below a certain value Vr , the filter capacitance C must be greater than

$$C_{\min} = \frac{(1-D)Vo}{8Vr L f^2}$$

(3.5)

Equations (3.4) and (3.5) are the key design equations for the buck converter. The input and output DC voltages (hence, the duty ratio D), and the range of load resistances R are usually considered as initial specifications. The designer needs to determine values of passive components L and C, and of the switching frequency f.

#### 3.5 Boost (Step-Up) Converter

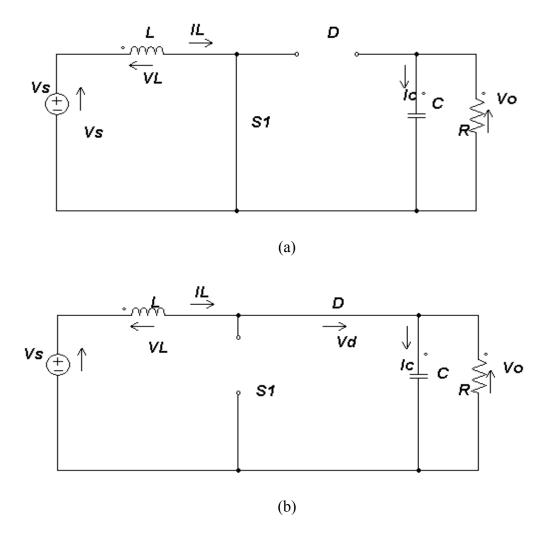

Fig. 3.7 shows a step-up or a PWM boost converter. It consists of DC input voltage source  $V_S$ , boost inductor L, controlled switch S, diode D, filter capacitor C, and load resistance R. The converter operation is shown in Fig. 3.8.The waveforms in the CCM are presented in Fig. 3.9. When the switch S is in the on state, the current in the boost inductor increases linearly and the diode D is off at that time. When the switch S is turned off, the energy stored in the inductor is released through the diode to the output RC circuit.

For the boost inductor,

$$V_{S} DT = (V_{O}-V_{S}) (1 - D) T$$

From which the DC voltage transfer function turns out to be

$$\frac{\text{Vo}}{\text{Vs}} = \frac{1}{1-D}$$

(3.6)

Fig. 3.7 Boost DC-DC converter.

Fig. 3.8 Equivalent circuit of Boost DC-DC converter when (a) switch closed (b) switch open

Fig. 3.9 Waveforms of Boost converter

As the name of the converter suggests, the output voltage is always greater than the input voltage.

The boost converter operates in the CCM for  $L > L_b$  where

$$L_{b} = \frac{(1-D)^{2} DR}{2f}.$$

(3.7)

The filter capacitor must provide the output DC current to the load when the diode is off. The minimum value of the filter capacitance that results in the voltage ripple Vr is given by

$$C_{\min} = \frac{D \text{ Vo}}{\text{Vr Rf}}.$$

(3.8)

# 3.6 Buck-Boost Converter

A buck-boost converter is shown in Fig.. 3.10. The converter consists of DC input voltage source  $V_S$ , controlled switch S, inductor L, diode D, filter capacitor C, and load resistance R. With the switch on, the inductor current increases while the diode is maintained off. When the switch is turned off, the diode provides a path for the inductor current. Note the polarity of the diode that results in its current being drawn from the output. The buck-boost converter operation is depicted in Fig. 3.11. Fig. 3.12 shows the waveforms for CCM of buck-boost converter.

The condition of a zero volt-second product for the inductor in steady state yields

$$V_{S} DT = -V_{O} (1 - D) T$$

Hence, the DC voltage transfer function of the buck-boost converter is

$$\frac{\text{Vo}}{\text{Vs}} = -\frac{\text{D}}{\text{1-D}}.$$

(3.9)

The output voltage  $V_O$  is negative with respect to the ground. Its magnitude can be either greater or smaller (equal at D=0.5) than the input voltage as the name of the converter implies.

The value of the inductor that determines the boundary between the CCM and DCM is

$$L_b = \frac{(1-D)^2 R}{2f}$$

(3.10)

The minimum value of the filter capacitance that results in the voltage ripple Vr is given by

$$C_{\min} = \frac{D \text{ Vo}}{\text{Vr Rf}}.$$

(3.11)

Fig. 3.10 Buck-Boost DC-DC converter.

Fig. 3.11 Equivalent circuit of Buck-Boost DC-DC converter when (a) switch closed (b) switch open

Fig. 3.12 Waveforms of Buck-Boost converter.

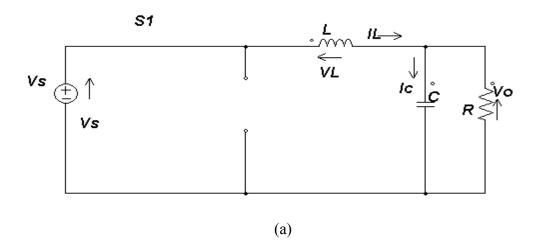

# 3.7 Ĉuk Converter

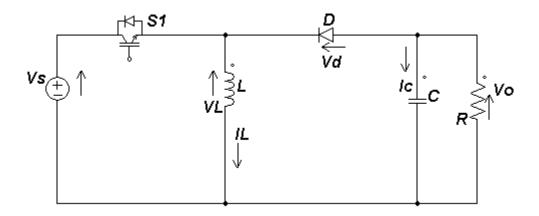

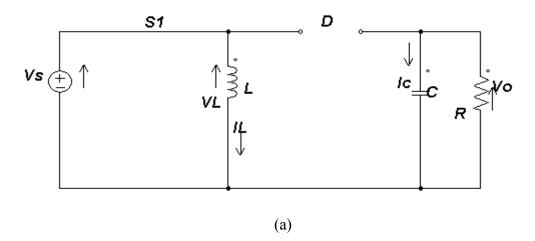

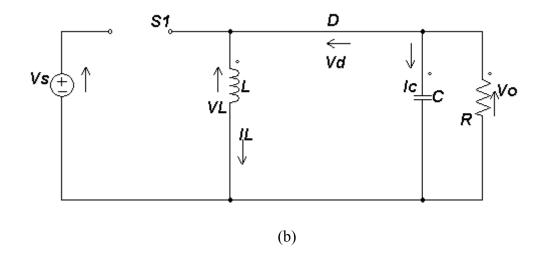

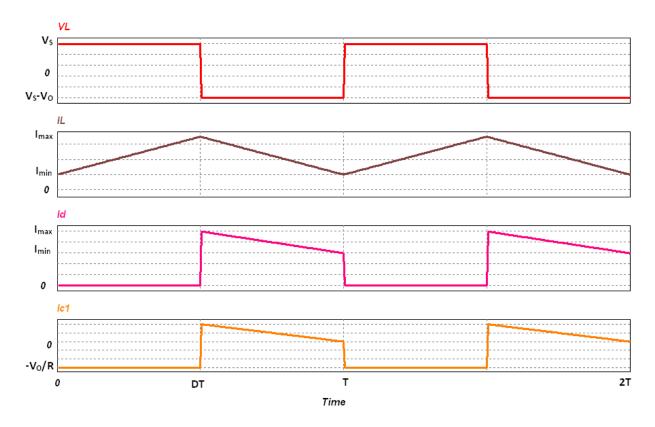

The circuit of the  $\hat{C}uk$  converter is shown in Fig. 3.13. It consists of DC input voltage source  $V_S$ , input inductor  $L_1$ , controllable switch S, energy transfer capacitor  $C_1$ , diode D, filter inductor  $L_2$ , filter capacitor  $C_2$ , and load resistance R. An important advantage of this topology is a continuous current at both the input and the output of the converter. Disadvantages of the  $\hat{C}uk$  converter are a high number of reactive components and high

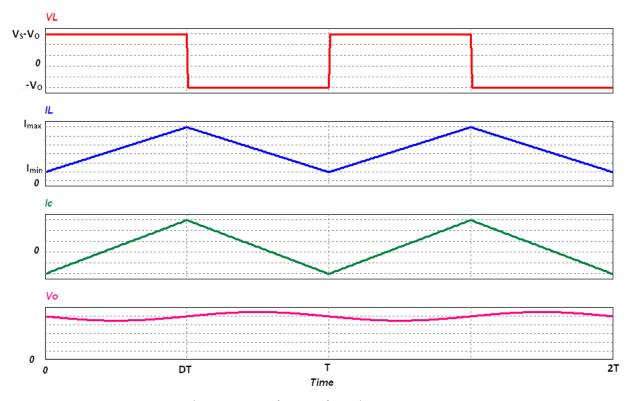

current stresses on the switch, the diode, and the capacitor  $C_1$ . The operation of the converter is presented in Fig. 3.14. When the switch is on, the diode is off and the capacitor  $C_1$  is discharged by the inductor  $L_2$  current. With the switch in the off state, the diode conducts currents of the inductors L1 and L2, whereas capacitor C1 is charged by the inductor L1 current. The waveforms of the converter are shown in Fig. 3.15

Fig. 3.13 Ĉuk DC-DC converter

Fig. 3.14 Equivalent circuit of Ĉuk DC-DC converter when (a) switch closed (b) switch open.

Fig. 3.15 Waveforms of Ĉuk converter

For Ĉuk converter,

$$I_{L2} DT = I_{L1}(1-D)T$$

For a lossless conversion

$$P_S = V_S I_{L1} = - V_O I_{L2} = P_O$$

Combining these two equations, the DC voltage transfer function of the Ĉuk converter is

$$\frac{V0}{Vs} = -\frac{D}{1-D}$$

...(3.12)

This voltage transfer function is the same as that for the buck-boost converter.

The boundaries between the CCM and DCM are

For L<sub>1</sub>

$$L_{b1} = \frac{(1-D)R}{2Df}....(3.13)$$

For L<sub>2</sub>.

$$L_{b2} = \frac{(1-D)R}{2f}...(3.14)$$

The output part of the Ĉuk converter is similar to that of the buck converter. Hence, the expression for the filter capacitor C is

$$C_{\min} = \frac{(1-D)Vo}{8Vr L2 f^2}$$

...(3.15)

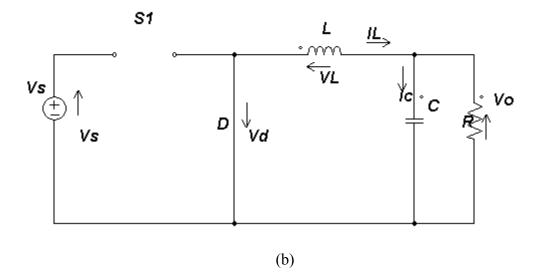

### 3.8 SEPIC Converter

Single-ended primary-inductor converter (SEPIC) is a type of DC-DC converter allowing the electrical potential (voltage) at its output to be greater than, less than, or equal to that at its input. A SEPIC is similar to a traditional buck-boost converter, but has advantages of having non-inverted output.

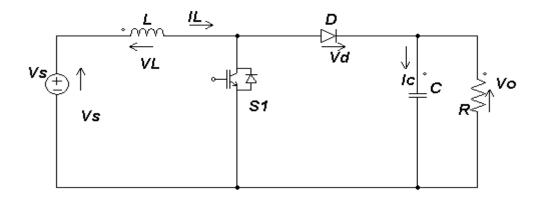

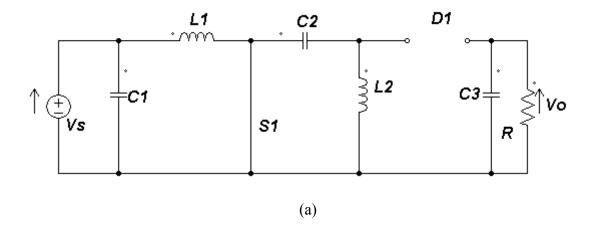

The circuit of the SEPIC converter is shown in Fig. 3.16. It consists of DC input voltage source  $V_S$ , inductors  $L_1$ ,  $L_2$  and  $L_3$ , controllable switch  $S_1$ , capacitors  $C_1$ ,  $C_2$ ,  $C_3$ , diode  $D_1$ , and load resistance R. Capacitor  $C_3$  is used for filtering .

Figure 3.17 shows the circuit operation when the switch is on and off respectively.

For SEPIC converter

$$\frac{\text{Vo}}{\text{Vs}} = \frac{\text{D}}{1-\text{D}}.$$

(3.16)

Fig. 3.16 SEPIC DC-DC converter

Fig. 3.17 Equivalent circuit of SEPIC DC-DC converter when (a) switch closed (b) switch open.

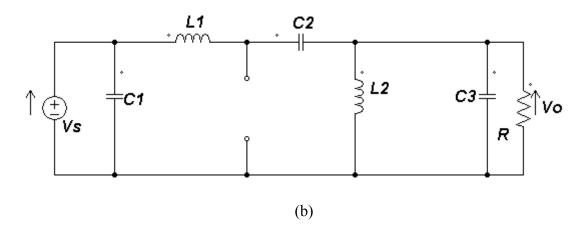

### 3.9 Inverse SEPIC Converter

The circuit of the inverse SEPIC converter is shown in Fig. 3.18. It consists of DC input voltage source  $V_S$ , inductors  $L_1$ ,  $L_2$ ,  $L_3$ , controllable switch  $S_1$ , capacitors  $C_1$ ,  $C_2$ ,  $C_3$ , diode  $D_1$ , and load resistance R. Capacitor  $C_3$  is used for filtering .

Figure 3.19a and Fig. 3.19b show the circuit operation when the switch is on and off respectively.

For inverse SEPIC converter

$$\frac{\text{Vo}}{\text{Vs}} = \frac{\text{D}}{1-\text{D}}.$$

(3.17)

Fig. 3.18 Inverse SEPIC DC-DC converter

Fig. 3.19 Equivalent circuit of Inverse SEPIC DC-DC converter when (a) switch closed (b) switch open.

# **CHAPTER 4**

# POWER FACTOR CORRECTION

#### 4.1 Definitions

Power factor is defined as the ratio of the average power to the apparent power drawn by a load from an AC source. If the input voltage source is sinusoidal, then power factor can be expressed as the product of the distortion power factor and displacement power factor.

The ratio of the fundamental root-mean-square (RMS) current ( $I_{rms(1)}$ ) to the total RMS current ( $I_{rms}$ ) is called distortion power factor  $K_d$ . The distortion power factor  $K_d$  is given by the following equation.

$$K_d = I_{rms(1)} / I_{rms}$$

The cosine of the displacement angle between the fundamental input current and the input voltage is called displacement power factor  $K_{\theta}$ . The displacement power factor  $K_{\theta}$  is given by the following equation.

$$K_{\theta} = \cos\theta$$

So from the definition of power factor (PF) we can write-

$$PF = K_d * K_\theta$$

$$= (I_{rms(1)} / I_{rms}) * cos\theta$$

Less than unity power factor of a converter means that absorbs apparent power, which is higher than the active power that it consumes. Therefore, the higher VA rating is required for a power source than the load needs. The power quality of the source deteriorates for the current harmonics generated by the converter [27].

## 4.2 Power Factor Correction and Harmonic Reduction

There is no direct relation between power factor and THD [27]. But it is not easy to get High power factor and low harmonics at the same time. The following equations can give some relations between total harmonic distortion (THD) and power factor.

THD (%) =

$$100 \times \sqrt{\left(\frac{1}{\text{Kd}}\right)^2 - 1}$$

.....(4.1)

The distortion power factor K<sub>d</sub> can be written as-

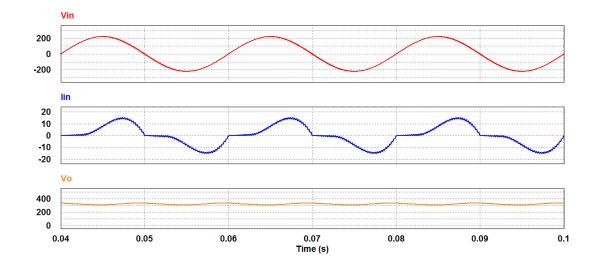

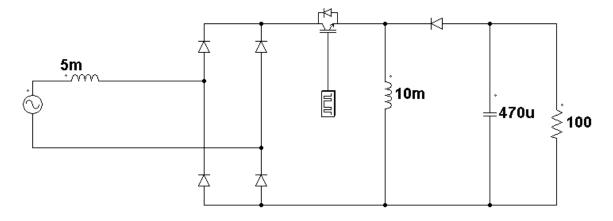

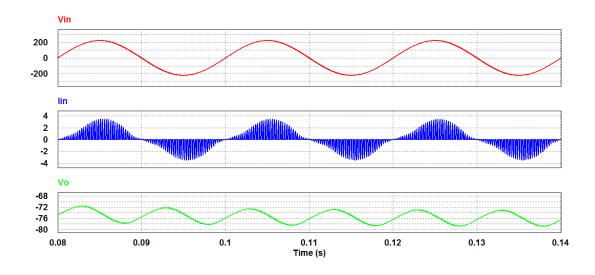

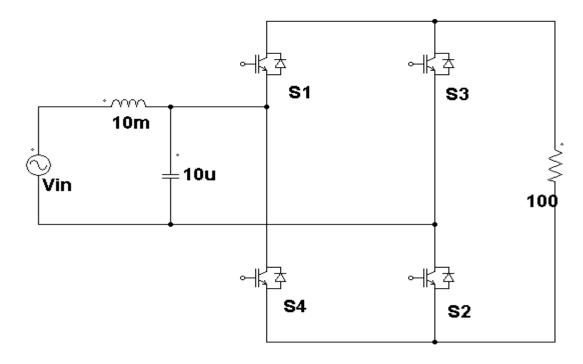

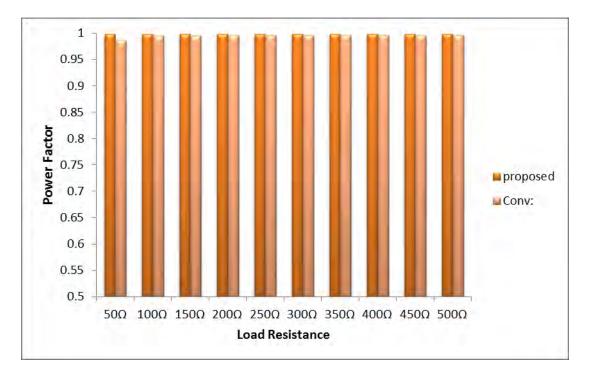

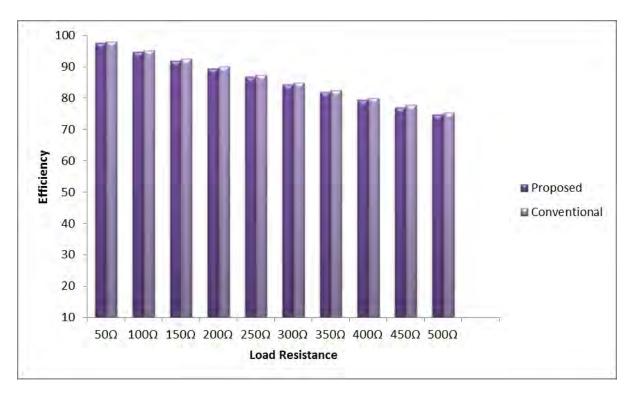

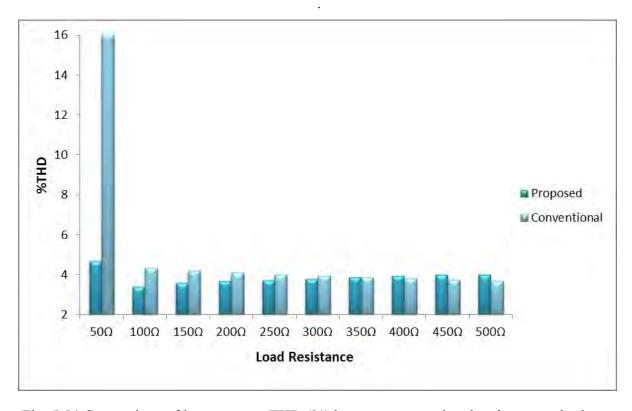

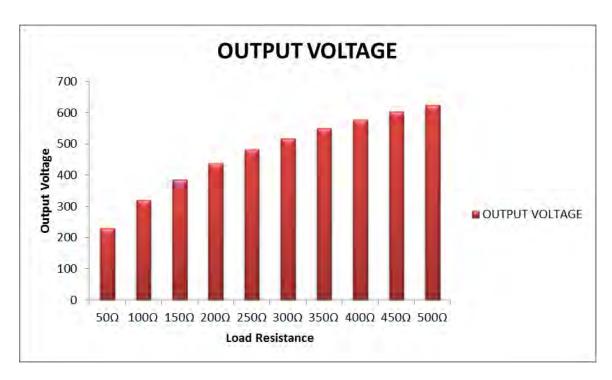

$$K_d = \frac{1}{\sqrt{1 + \left(\frac{THD(\%)}{100}\right)^2}}$$