# QUANTUM MECHANICAL MODELING AND SIMULATION OF MONOLAYER WSe<sub>2</sub> CHANNEL FIELD EFFECT TRANSISTOR

A thesis submitted in partial fulfillment of the requirements for the degree of Master of Science in Electrical and Electronic Engineering

by

Saeed-Uz-Zaman Khan

Student No: 0413062246 P

Department of Electrical and Electronic Engineering

Bangladesh University of Engineering and Technology

February, 2016

# Approval

The thesis titled "QUANTUM MECHANICAL MODELING AND SIMULATION OF MONOLAYER WSe<sub>2</sub> CHANNEL FIELD EFFECT TRANSISTOR" submitted by Saeed-Uz-Zaman Khan, Student No: 0413062246 P, Session: April 2013, has been accepted as satisfactory in partial fulfillment of the requirements for the degree of Master of Science in Electrical and Electronic Engineering on February 29, 2016.

## **Board of Examiners**

| 1, 02                                               |              |

|-----------------------------------------------------|--------------|

| 1. m                                                |              |

| Dr. Quazi Deen Mohd Khosru                          | Chairman     |

| Professor                                           | (Supervisor) |

| Department of Electrical and Electronic Engineering |              |

| Bangladesh University of Engineering and Technology |              |

| Dhaka – 1205, Bangladesh.                           |              |

|                                                     |              |

| Dr. Taifur Ahmed Chowdhury                          | Member       |

| Professor and Head                                  | (Ex-officio) |

| Department of Electrical and Electronic Engineering |              |

| Bangladesh University of Engineering and Technology |              |

| Dhaka – 1205, Bangladesh.                           |              |

|                                                     |              |

|                                                     |              |

| 3. Some Subno                                       |              |

| Dr. Samia Subrina                                   | Member       |

| Associate Professor                                 |              |

| Department of Electrical and Electronic Engineering |              |

| Bangladesh University of Engineering and Technology |              |

| Dhaka – 1205, Bangladesh.                           |              |

| 4. Takid Hose Well                                  |              |

| Dr. Zahid Hasan Mahmood                             | Member       |

| Professor                                           | (External)   |

| Department of Electrical and Electronic Engineering |              |

| University of Dhaka                                 |              |

| Dhaka = 1000 Bangladesh                             |              |

# **Declaration**

It is hereby declared that this thesis or any part of it has not been submitted elsewhere for the award of any degree or diploma.

Signature of the Candidate

29.02.16

(Saeed-Uz-Zaman Khan)

To my beloved parents

# Acknowledgment

All praise goes to the Almighty for giving me the patience and drive required to complete my M.Sc. research and finish the dissertation in due time.

I would begin by heartily thanking my thesis supervisor Dr. Quazi Deen Mohd Khosru, Professor, D epartment of E lectrical and E lectronic Engineering (EEE), Bangladesh University of E ngineering and T echnology (BUET), for his generous help, edifying suggestions and well-defined guidance throughout the thesis work. I feel grateful to him for giving me sufficient freedom and having faith in my capabilities, which made the research work very much enjoyable for me. His passion and dedication to academic research has motivated me to push my boundaries harder and excel at my research work, which I believe will inspire me to be a better researcher in future days to come.

I am also thankful to the Head of EEE Department, Dr. Taifur Ahmed Chowdhury for his support during my thesis work. I would also like to thank the members of the board of examiners for taking the time to evaluate my work and provide insightful suggestions.

I want to express my gratitude to Imtiaz Ahmed, Lecturer, Department of Electrical and Electronic Engineering (EEE), Bangladesh University of Engineering and Technology (BUET), for his kind help with the format of the dissertation. I also want to thank Kanak Datta, Lecturer from the same institution, for his sincere help with the DFT simulations.

I would like to thank my parents, Mofakkar A li K han and Nahida K han, and dedicate my thesis to them. They have been the encouragement behind my every successful endeavor. This thesis work is not a nexception and would not have been completed without their constant support and inspiration.

Finally, I put forward my humble gratitude to all my colleagues, friends and well wishers for their help, support and words of encouragement during my research work.

# **Abstract**

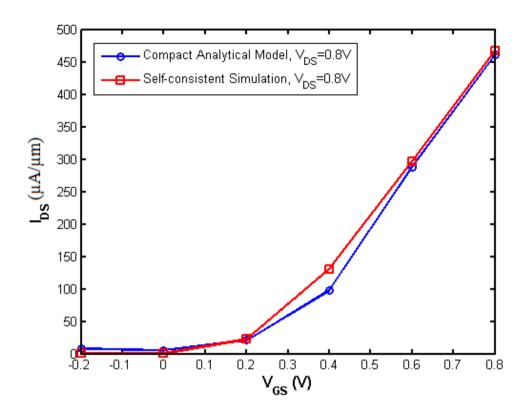

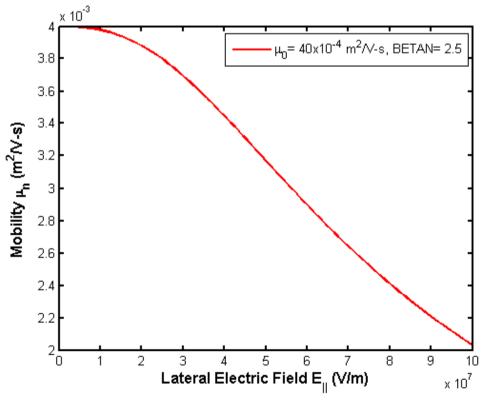

In recent years, researchers have been working on Graphene and Monolayer Transition Metal Dichalcogenides l ike M oS<sub>2</sub> and WSe<sub>2</sub> to f ind the c hannel m aterial f or ne xt g eneration ultimately s caled transistors. The absence of intrinsic band g ap in G raphene s heet made researchers focus more on Dichalcogenides lately and as a result of that endeavor monolayer WSe<sub>2</sub> based pFET has been fabricated. This experimental device with high band gap (1.6 eV) showed higher carrier mobility (250 cm<sup>2</sup>/Vs) than monolayer MoS<sub>2</sub> based devices. In recent literature me thods of n-type and p-type dopi ng of m onolayer W Se<sub>2</sub> FET have b een demonstrated, which led to the fabrication of high performance CMOS inverter solely based on m onolayer W Se<sub>2</sub> channel. D espite of t hese pr omising e xperimental r esults, r igorous Transport and E lectrostatic study of monolayer W Se<sub>2</sub> based F ET is yet to a ppear in the literature. Moreover, at p resent n o analytical model f or cu rrent-voltage c haracteristics is available specifically for WSe<sub>2</sub> FET. The purpose of this work is to perform a simulation study of Quantum Mechanical electrostatics by solving Schrödinger-Poisson equations selfconsistently using material parameters extracted from literature and to determine the transport characteristics using Fast Uncoupled Mode Space (FUMS) approach. The second objective of this work is to develop a compact Transport model for Monolayer WSe<sub>2</sub> FET. In this thesis work bot h objectives h ave b een fulfilled a nd a fully num erical d evice s imulator a nd a compact an alytical transport model have been demonstrated. The numerical simulator has been used to study the transport performance of a monolayer WSe<sub>2</sub> FET structure with 20 nm of channel length. The performance analysis revealed excellent on and off state performances of the device with an impressive ON/OFF current ratio of 10<sup>10</sup>, on current of 467.2 μA/μm, effective m obility of 30 0 c m<sup>2</sup>/V.s, and S S of 77.72 mV/dec. T he proposed de vice al so demonstrated promising resistance to Short Channel Effects (SCEs) with a Drain Induced Barrier Lowering (DIBL) of 14.91 mV/V and a threshold voltage roll-off of 0.05 V for 0.7 V change in drain voltage. The compact analytical model developed in this work successfully tracks t he t ransport ch aracteristics of t he monolayer WS e<sub>2</sub> device as well. The model estimates the inversion charge distribution in the channel and calculates the drain current using the drift-diffusion transport equation. To simplify the analytical expression, the model also makes Gradual Channel Approximation and assumes that the electrostatic potential in the channel is limited to quadratic variations only. The model also uses a Field Dependent Mobility M odel s uggested by the A LTAS s imulation f ramework and considers the E-K diagram obtained from the Density Functional Theory (DFT) to calculate the Density of States for monolayer W Se<sub>2</sub>. Results obtained from this physically a ccurate compact model are used for quick characterization of the proposed monolayer WSe<sub>2</sub> channel transistor. With the help of a gate voltage dependent "Fitting Function", this model successfully estimates the transport characteristics and threshold voltage of monolayer the WSe<sub>2</sub> FET, which are in reasonable agreement with the numerical simulation.

# **Contents**

|     |         |                                                 | Page |

|-----|---------|-------------------------------------------------|------|

| Ap  | prov    | al                                              | ii   |

| De  | clara   | tion                                            | iii  |

| Ac  | knov    | rledgement                                      | v    |

| Ab  | strac   | t                                               | vi   |

| Co  | nten    | ts                                              | vii  |

| Lis | st of ] | Figures                                         | X    |

| Lis | st of ' | Γables                                          | xiii |

| Lis | st of A | Abbreviations                                   | xiv  |

| Lis | st of S | Symbols                                         | xvi  |

| 1.  | Intr    | oduction                                        | 1    |

|     | 1.1.    | Current Trend and Challenges of CMOS Technology | 1    |

|     | 1.2.    | Two Dimensional Material Channel MOSFETs        | 5    |

|     |         | 1.2.1. Motivation for Choosing TMDCs            | 5    |

|     |         | 1.2.2. Motivation for Choosing WSe <sub>2</sub> | 6    |

|     | 1.3.    | Thesis Objectives                               | 7    |

|     | 1.4.    | Thesis Organization                             | 8    |

| 2.  | Exp     | loration of the Monolayer WSe <sub>2</sub> FET  | 9    |

|     | 2.1.    | Simulation                                      | 9    |

|     |         | 2.1.1. Material Level Simulation                | 9    |

|     |         | 2.1.2. Device Level Simulation                  | 11   |

|     |         | 2.1.2.1. Simulation of Electrostatics           | 12   |

|     |         | 2.1.2.2. Simulation of Transport Properties     | 12   |

|     | 2.2.    | Analytical and Compact Modeling                 | 14   |

|     | 23      | Fabrication and Testing                         | 15   |

|    |      | 2.3.1.    | Deposition                                                                | 16 |

|----|------|-----------|---------------------------------------------------------------------------|----|

|    |      | 2.3.2.    | Choice of Top Gate Oxide                                                  | 19 |

|    |      | 2.3.3.    | Choice of S/D Metal                                                       | 19 |

|    |      | 2.3.4.    | Doping                                                                    | 19 |

|    |      | 2.3.5.    | Characterization and Testing                                              | 20 |

| 3. | Qua  | ntum N    | Mechanical Electrostatics and Transport Simulation                        | 21 |

|    | 3.1. | I         | Device Structure                                                          | 21 |

|    | 3.2. | S         | Simulator Development                                                     | 22 |

|    |      | 3.2.1.    | Self-consistent Electrostatic Simulation                                  | 22 |

|    |      |           | 3.2.1.1. Self-Consistent Charge Calculation                               | 22 |

|    |      |           | 3.2.1.2. C-V Characterization                                             | 23 |

|    |      | 3.2.2.    | Transport S imulation Using First U nooupled M ode S pace Approach        | 24 |

|    |      | 3.2.3.    | COMSOL Multiphysics                                                       | 26 |

|    |      |           | 3.2.3.1. Solving Poisson Equation                                         | 26 |

|    |      |           | 3.2.3.2. Solving Schrödinger's Equation                                   | 27 |

|    |      | 3.2.4.    | Material Parameters                                                       | 28 |

|    | 3.3. | I         | Results and Discussions                                                   | 30 |

|    |      | 3.3.1.    | Simulator Validation                                                      | 30 |

|    |      | 3.3.2.    | Electrostatic and Transport Characteristics                               | 31 |

|    |      |           | 3.3.2.1.Effect of Gate Voltage on 1 <sup>st</sup> Subband Energy Profile  | 31 |

|    |      |           | 3.3.2.2.Effect of Drain Voltage on 1 <sup>st</sup> Subband Energy Profile | 31 |

|    |      |           | 3.3.2.3.Capacitance-Voltage and Current-Voltage Characteristics           | 31 |

|    |      |           | 3.3.2.4. Transfer Characteristics and Transconductance                    | 31 |

|    |      | 3.3.3.    | Parameter Extraction                                                      | 36 |

|    |      |           | 3.3.3.1.Extraction of Threshold Voltage (V <sub>th</sub> )                | 36 |

|    |      |           | 3.3.3.2.Extraction of Drain Induced Barrier Lowering (DIBL)               | 36 |

|    |      |           | 3.3.3.Extraction of Subthreshold Slope (SS)                               | 36 |

|    |      |           | 3.3.3.4.Extraction of On/Off Current Ratio                                | 36 |

|    |      |           | 3.3.3.5.Extraction of Effective Mobility ( $\mu_{eff}$ )                  | 36 |

|    |      | 3.3.4.    | Transport Properties below Threshold Voltage                              | 39 |

|    |      | 3.3.5.    | Transport Properties above Threshold Voltage                              | 43 |

|    |      | 3.3.6.    | Device Performance Parameters                                             | 47 |

| 4. | Ana  | lytical l | Modeling of Drain Current                                                 | 48 |

|    | 4.1. | I         | Differential System Establishment                                         | 49 |

|    | 4.2. | I         | Evaluating the Constants $C_1$ and $C_2$                                  | 55 |

|    | 4.3.  | Drain Current Modeling                                      | 57 |

|----|-------|-------------------------------------------------------------|----|

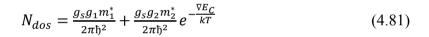

|    | 4.4.  | Calculation of Effective Density of States N <sub>dos</sub> | 60 |

|    | 4.5.  | Model Verification                                          | 61 |

|    |       | 4.5.1. Device Dimension Used                                | 61 |

|    |       | 4.5.2. Device Materials Used                                | 61 |

|    |       | 4.5.3. Material Parameters Used                             | 62 |

|    |       | 4.5.4. Benchmarking and Fitting Parameters Selection        | 62 |

|    | 4.6.  | Results and Discussions                                     | 64 |

|    |       | 4.6.1. Transport Characteristics of the Analytical Device   | 64 |

|    |       | 4.6.2. Threshold Voltage Extraction                         | 67 |

|    |       | 4.6.3. Limitations of the Analytical Model                  | 68 |

| 5. | Con   | nclusion                                                    | 69 |

|    | 5.1.  | Summary                                                     | 69 |

|    | 5.2.  | Suggestions for Future Work                                 | 70 |

| Bi | bliog | raphy                                                       | 71 |

| ΑĮ | pend  | lix                                                         | 78 |

|    | A.    | Journal Article Published                                   | 78 |

# **List of Figures**

|      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | Page |

|------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|

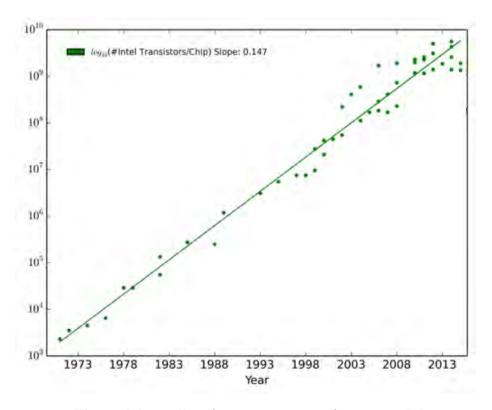

| 1.1  | Intel's Microprocessor transistor count [2].                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 1    |

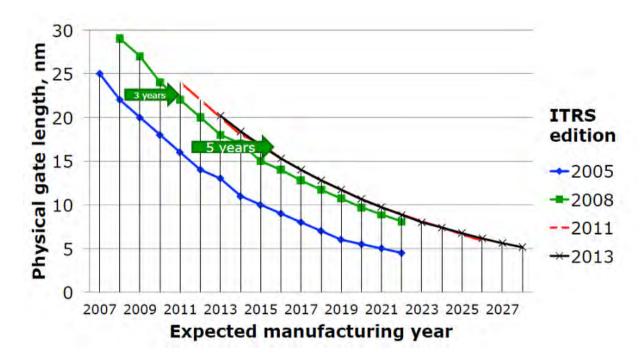

| 1.2  | ITRS roadmap [3] for transistor scaling in terms of physical channel length.                                                                                                                                                                                                                                                                                                                                                                                                                                        | 3    |

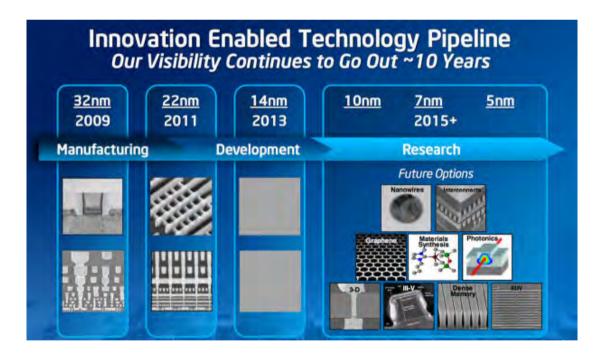

| 1.3  | Intel's i nnovation e nabled t echnology pi peline i nfographic (Courtesy Intel [2]).                                                                                                                                                                                                                                                                                                                                                                                                                               | 4    |

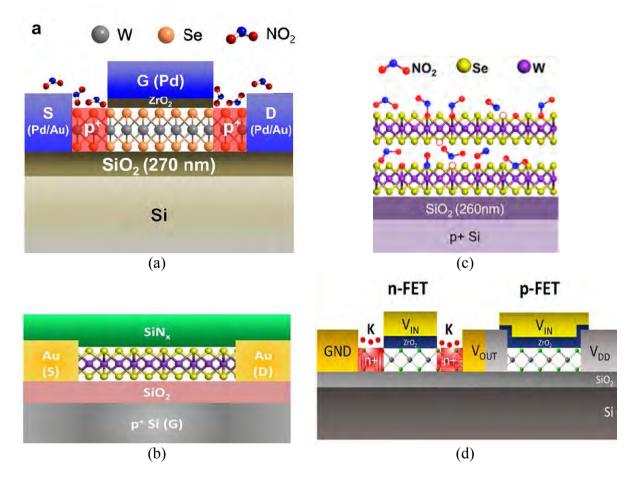

| 1.4  | (a) Monolayer WSe <sub>2</sub> based p-FET by Fang et al. [26] (b) Air stable p-doped WSe <sub>2</sub> FET by Chen et al. [44] (c) n-doped WSe <sub>2</sub> FET by Zhao et al. [45] (d) CMOS inverter implemented on same WSe <sub>2</sub> flake by Tosun et al. [46].                                                                                                                                                                                                                                              | 7    |

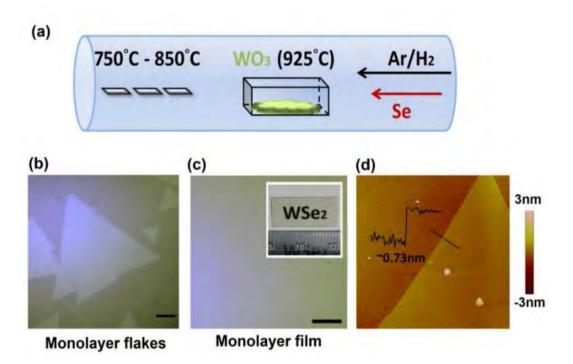

| 2.1  | Synthetic large scale growth of monolayer W Se <sub>2</sub> . (a) CVD growth of WSe <sub>2</sub> in the process of Selenization of WSe <sub>2</sub> powers in a hot-wall CVD furnace. (b) M onolayer W Se <sub>2</sub> flakes on Sapphire substrate at 850°C (optical microscope i mage). (c) M onolayer W Se <sub>2</sub> films on Sapphire substrate at 750°C (optical microscope image). (d) AFM image of monolayer W Se <sub>2</sub> on a Sapphire substrate grown at 850°C. (Image courtesy Huang et al. [54]) | 17   |

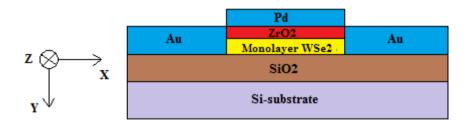

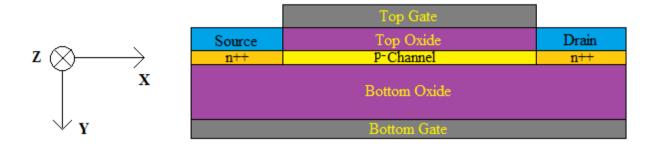

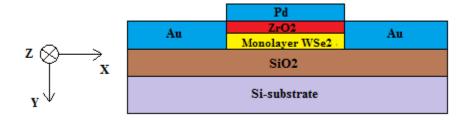

| 3.1  | 2D c ross s ection of the monolayer W Se <sub>2</sub> channel FET with channel length of 20 nm and top and bottom oxide thickness of 3 nm and 5 nm respectively.                                                                                                                                                                                                                                                                                                                                                    | 21   |

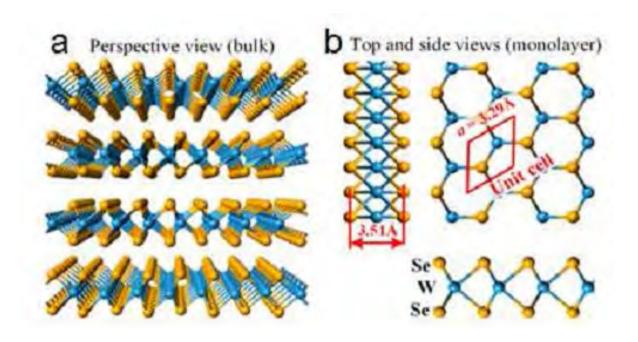

| 3.2  | (a) Bulk WSe <sub>2</sub> and (b) monolayer sheet of WSe <sub>2</sub> [101].                                                                                                                                                                                                                                                                                                                                                                                                                                        | 29   |

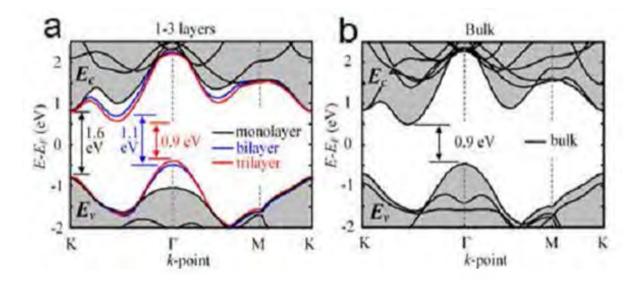

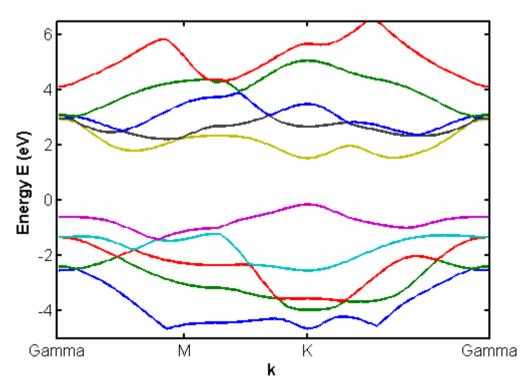

| 3.3  | E-k diagram of (a) few layers of W Se <sub>2</sub> and (b) bulk W Se <sub>2</sub> obtained from the atomistic simulation of W Se <sub>2</sub> [101] using DFT simulation in ATK [52]. It is to be noted that, the bulk bandgap shown here is slightly underestimated than the actual bulk bandgap of 1.2 eV, which is an inherent limitation of DFT simulations.                                                                                                                                                    | 29   |

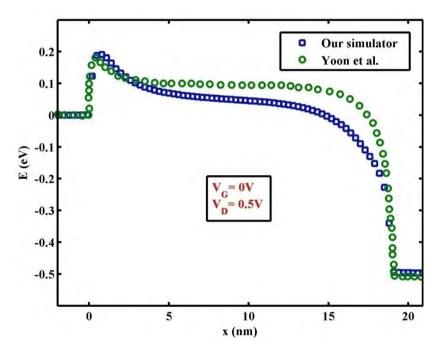

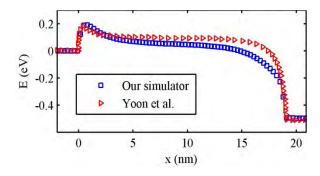

| 3.4  | First s ubband energy across the channel f or the monolayer M oS <sub>2</sub> channel device by Yoon et al. [27] at $V_G$ =0 and $V_D$ =0.5 V. Simulator described in this section gives similar results.                                                                                                                                                                                                                                                                                                           | 30   |

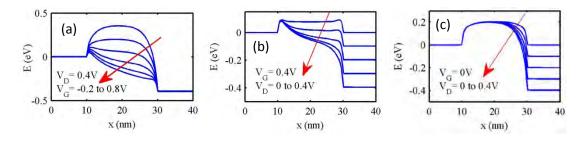

| 3.5  | First subband energy profile across the channel with different gate bias conditions and fixed drain voltage of (a) 0V and (b) 0.4V.                                                                                                                                                                                                                                                                                                                                                                                 | 32   |

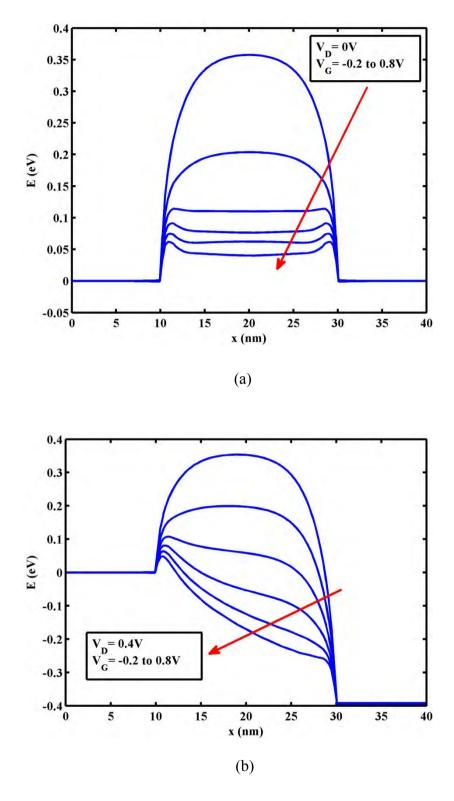

| 3.6  | First s ubband energy p rofile a cross the channel with different drain bias conditions and fixed gate voltage of (a) 0V and (b) 0.4V.                                                                                                                                                                                                                                                                                                                                                                              | 33   |

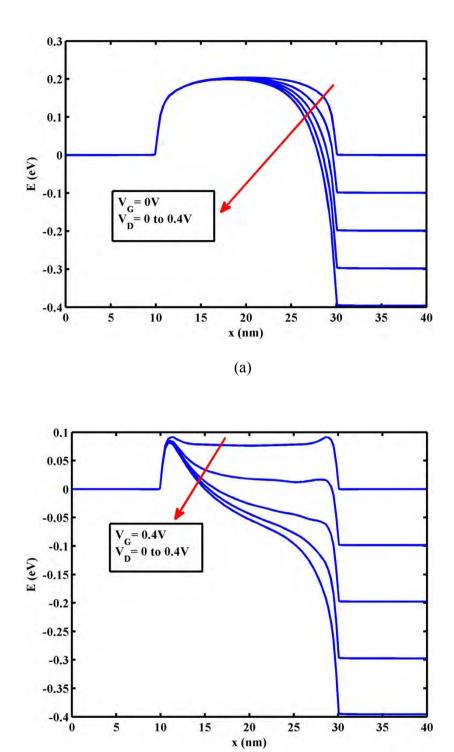

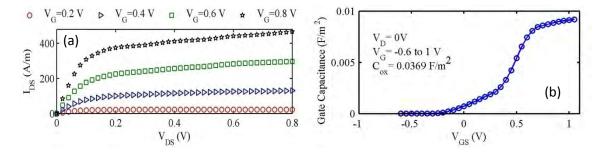

| 3.7  | (a) Drain current-voltage characteristics at different gate biases (b) gate capacitance-voltage characteristics at zero drain voltage.                                                                                                                                                                                                                                                                                                                                                                              | 34   |

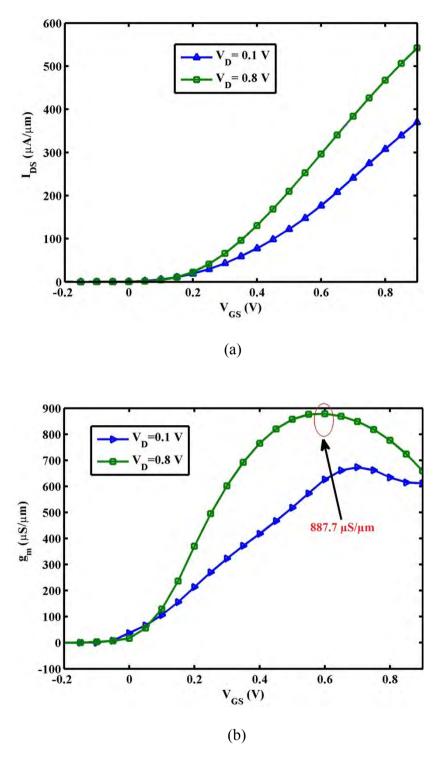

| 3.8  | (a) Transfer characteristics (b) transcoductance profile at different drain voltages.                                                                                                                                                                                                                                                                                                                                                                                                                               | 35   |

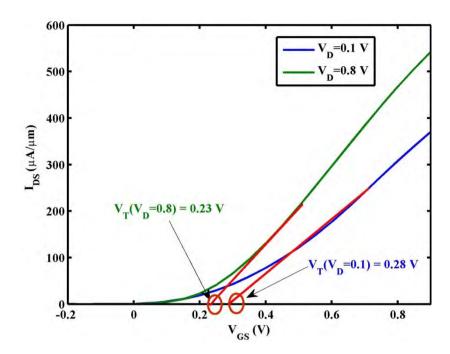

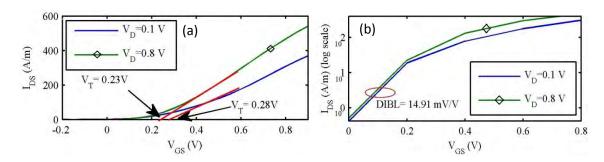

| 3.9  | Threshold voltage extraction at different drain biases. For drain voltage of 0.8V threshold voltage is found to be 0.23 V and for drain bias voltage of 0.1V it is 0.28V.                                                                                                                                                                                                                                                                                                                                           | 37   |

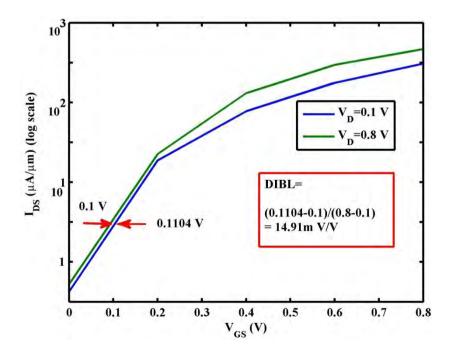

| 3.10 | Drain Induced Barrier Lowering (DIBL) e xtraction f rom t he                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 37   |

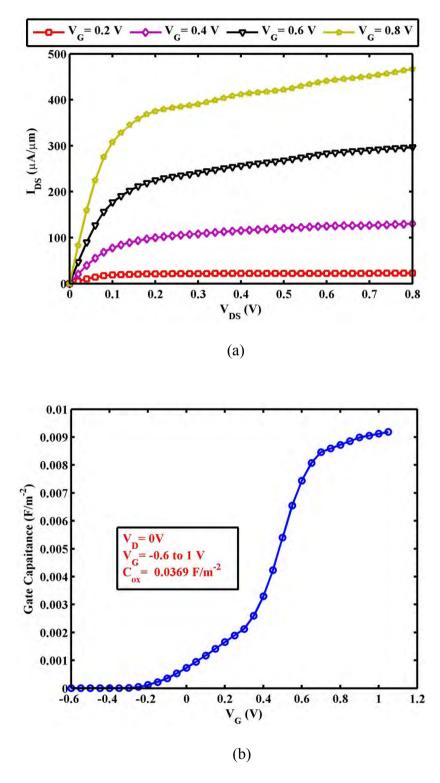

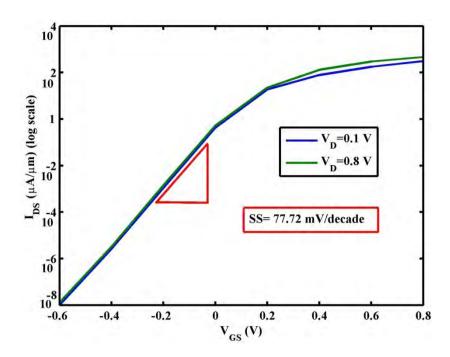

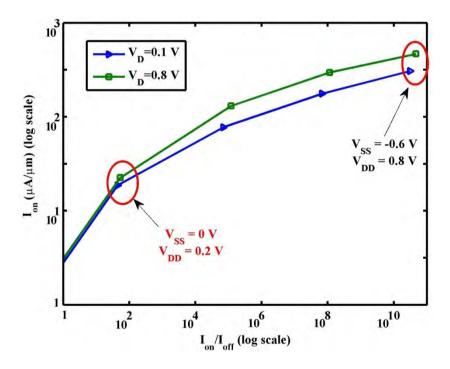

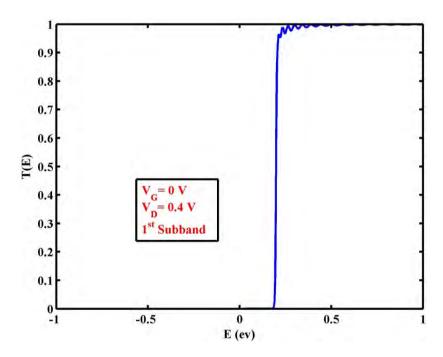

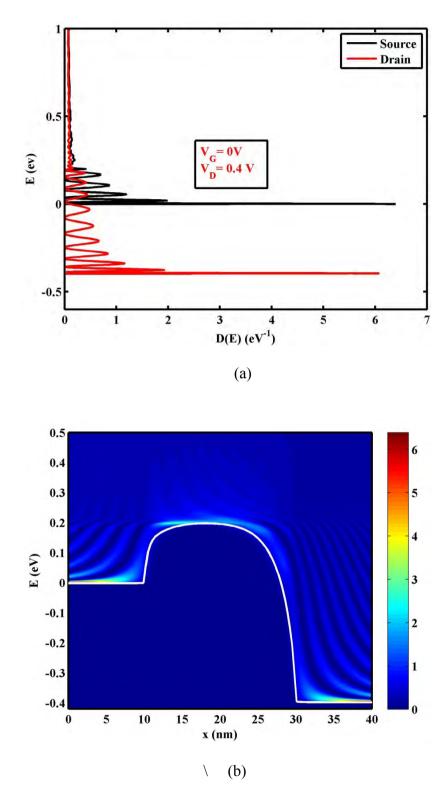

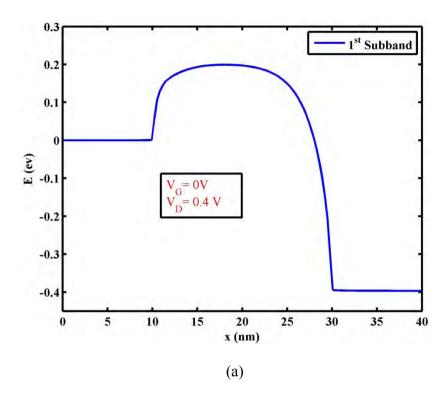

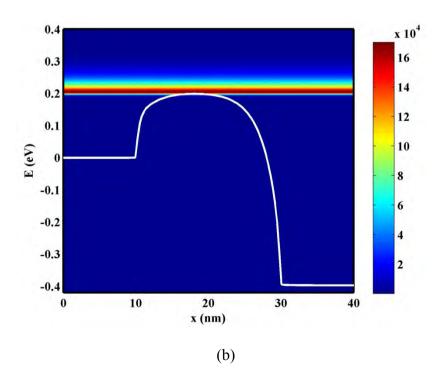

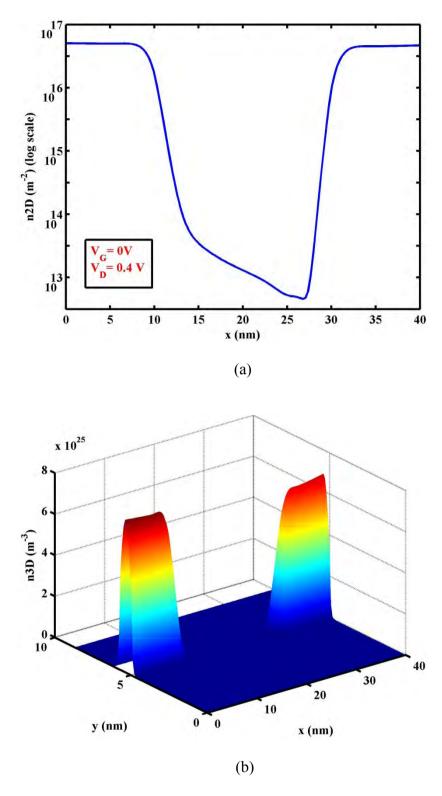

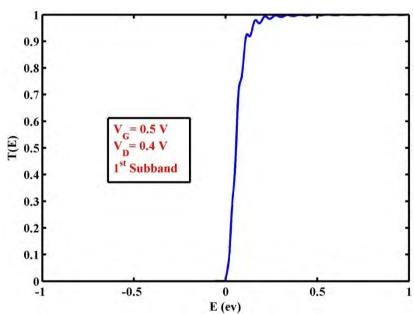

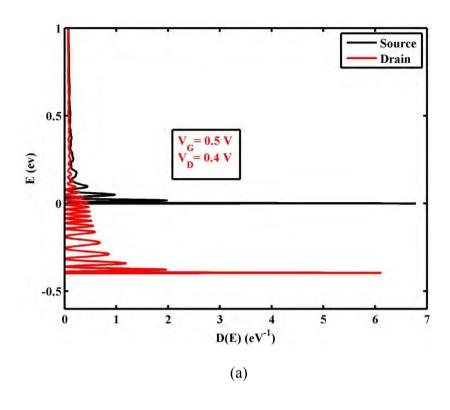

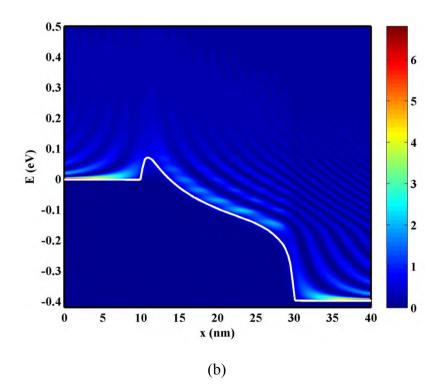

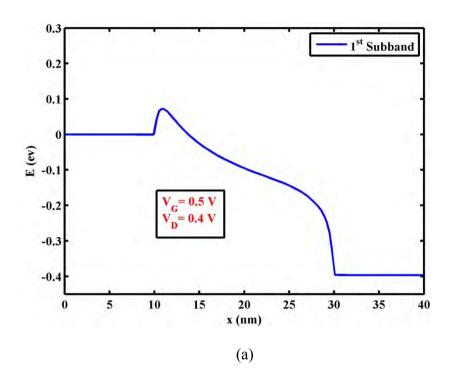

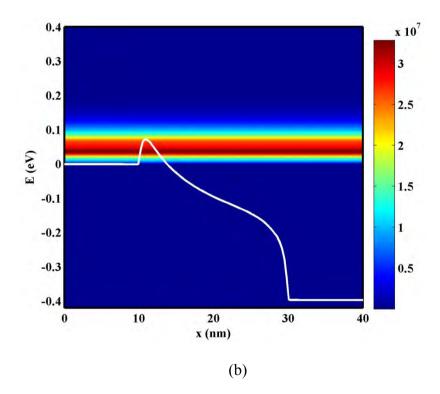

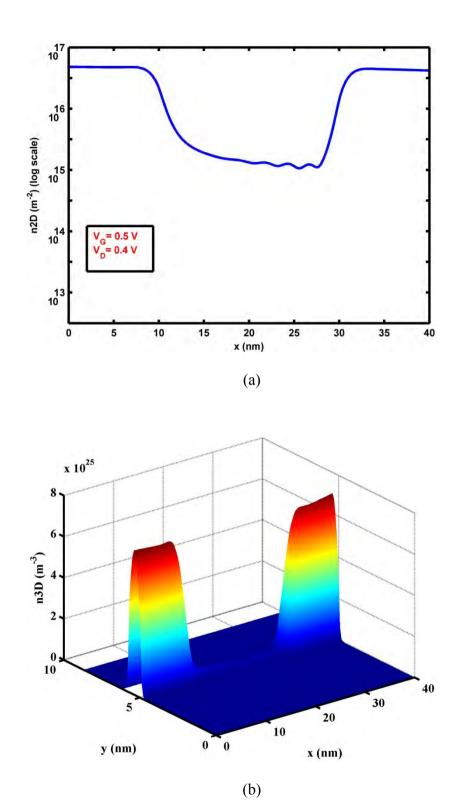

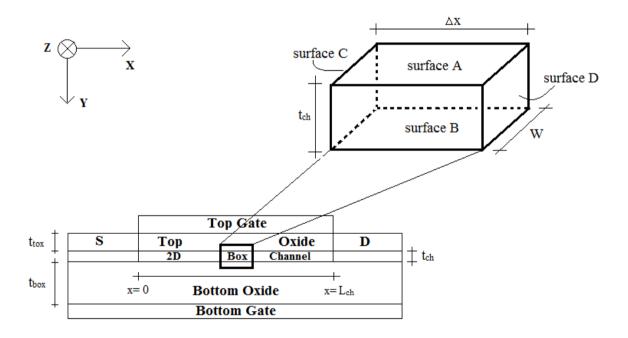

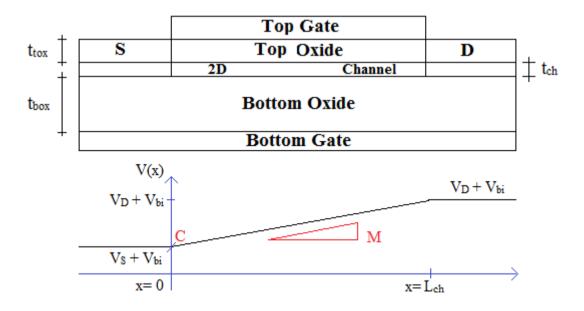

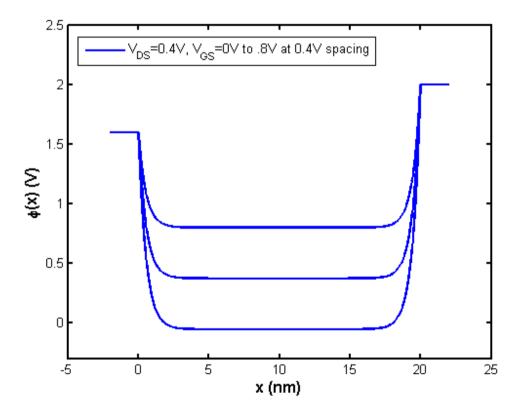

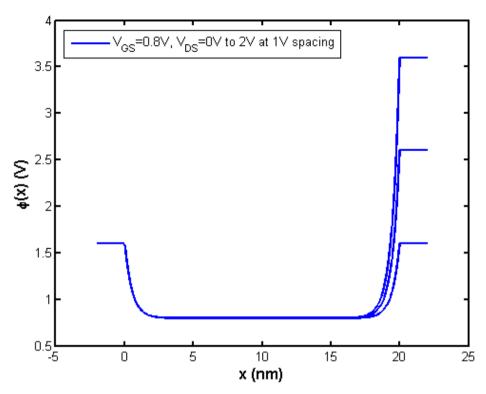

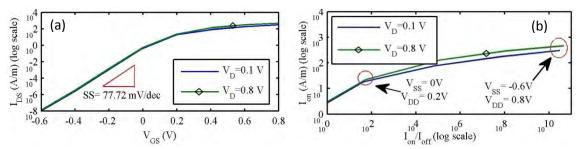

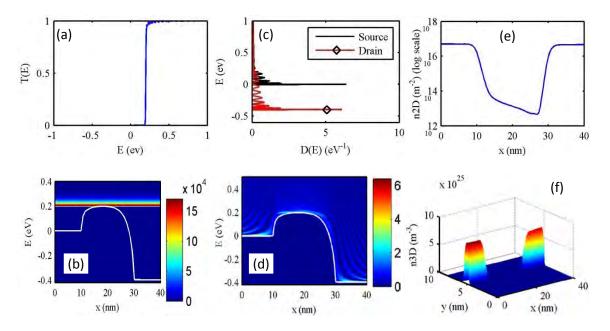

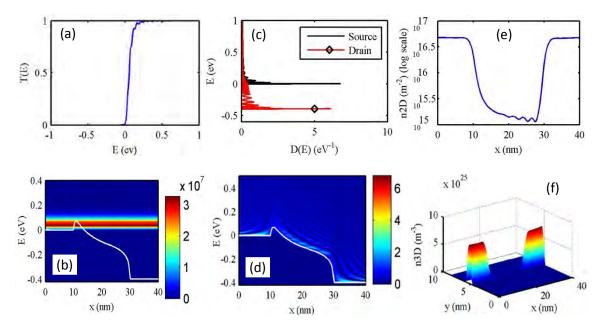

$\log_{10}(I_{ds}) - V_{gs}$  curve at drain voltages of 0.1V and 0.8V. 3.11 Subthreshold Swing (SS) extraction from the  $\log_{10}(I_{ds}) - V_{as}$  curve at 38 drain voltages of 0.1V and 0.8V. Extraction of ON/OFF current ratio at drain voltages of 0.1V and 0.8V. 3.12 38 The maximum ON/OFF current ratio obtained is in the order of  $\sim 10^{10}$ . 3.13 Transmission co-efficient for the device for gate and drain voltages of 39 0V and 0.4V respectively. (a) LDOS at source and drain end (d) LDOS along the channel for gate 3.14 40 and drain voltages of 0V and 0.4V respectively. (a) First subband energy profile (b) Energy resolved current density of 3.15 41 the device for gate and drain voltages of 0V and 0.4V respectively. 3.16 (a) 2-D electron density (b) 3-D electron density across the device for 42 gate and drain voltages of 0V and 0.4V respectively. 3.17 Transmission co-efficient for the device for gate and drain voltages of 43 0.5V and 0.4V respectively. (a) LDOS at source and drain end (d) LDOS along the channel for gate 3.18 44 and drain voltages of 0.5V and 0.4V respectively. (a) First subband energy profile (b) Energy resolved current density of 3.19 45 the device for gate and drain voltages of 0.5V and 0.4V respectively. (a) 2-D electron density (b) 3-D electron density across the device for 3.20 46 gate and drain voltages of 0.5V and 0.4V respectively. 4.1 The M OSFET's tructure under c onsideration. It has a 2D m aterial 48 channel sandwiched between top and bottom oxides and corresponding top and bottom gates. The channel is p-doped. The source and drain are highly n-doped regions of the same 2D material. 4.2 To e stablish th e d ifferential s ystem f or th e 2 D M OSFET a n 49 infinitesimal box is considered to which Gauss's Law  $(\oint_{\mathcal{E}} \varepsilon \vec{E} \cdot \vec{ds} = Q)$ is applied. The directions of the surface vectors are outward positive. 4.3 Approximation of potential V(x) inside the 2D channel. 57 4.4 E-k diagram of WSe<sub>2</sub> obtained from first-principle DFT simulations in 60 Quantum E spresso s oftware [51]. The di agram s hows l owest conduction va lley a t K -point. T he ne arsst l ow point i s somewhere between K and  $\Gamma$  point. The energy difference be tween those two lowest valleys is approximately 8 meV. 4.5 Current from the analytical model is matched with the simulated results 63 by using appropriate fitting parameters. 4.6 Field dependent mobility used to evaluate the analytical current. 63 4.7 Channel pot ential  $\varphi(x)$  under di fferent t op ga te bi as c onditions. 64 Bottom gate is fixed at 0V. Drain voltage is fixed at 0.4V. Gate voltage is varied from 0 to 0.8V. 4.8 Channel pot ential  $\varphi(x)$  under different dr ain bi as c onditions. B ottom 65 gate is fixed at 0V. Top gate voltage is fixed at 0.8V. Drain voltage is varied from 0 to 2V.

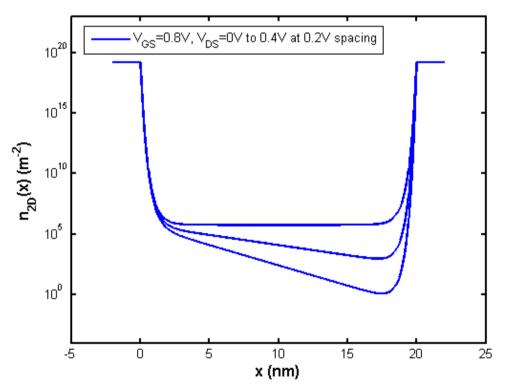

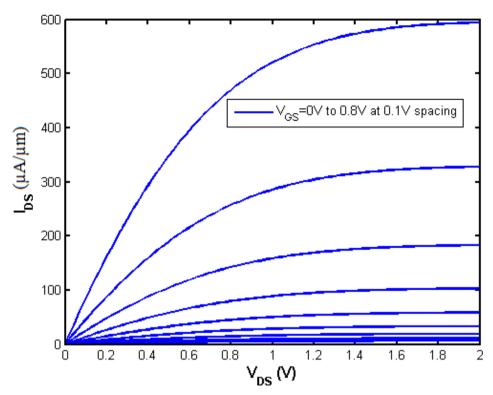

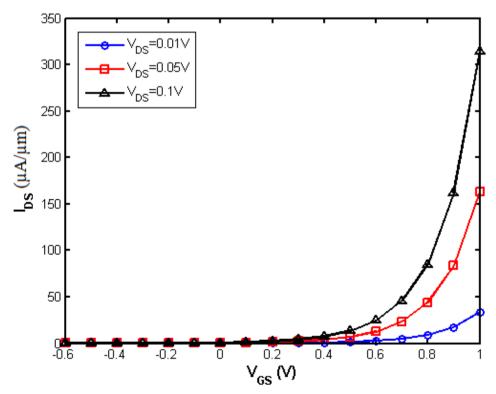

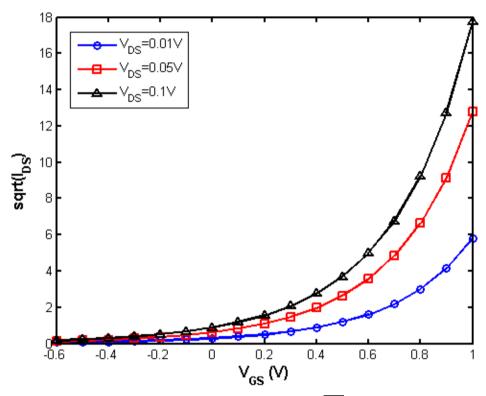

4.9 Channel i nversion c arrier (electron) de nsity  $n_{2D}(x)$  under di fferent 65 drain bias conditions. Top gate voltage is fixed at 0.8V. Drain voltage is varied from 0 to 0.4V. Output c haracteristics (I<sub>d</sub>-V<sub>ds</sub>) of the device under different top g ate 66 4.10 voltage. Bottom gate is fixed at 0V. 4.11 Transfer ch aracteristics ( $I_{d}$ - $V_{gs}$ ) of the device under different drain 66 voltage. Bottom gate is fixed at 0V. 4.12 Threshold vol tage extraction from the  $\sqrt{I_{ds}} - V_{gs}$  curve for different 67

drain voltages. Bottom gate is fixed at 0V.

# **List of Tables**

|     |                                                                   | Page |

|-----|-------------------------------------------------------------------|------|

| 3.1 | Monolayer WSe <sub>2</sub> Parameters Extracted from Literature   | 28   |

| 3.2 | Device Performance Parameters Obtained from Simulation            | 47   |

| 4.1 | Physical Dimension of the Analytical Device                       | 61   |

| 4.2 | Material Used in the Analytical Device                            | 61   |

| 4.3 | Material Parameters for the Analytical Device                     | 62   |

| 4.4 | Fitting Parameters for the Compact Analytical Drain Current Model | 62   |

# **List of Abbreviations**

**1D** One-Dimensional

**2D** Two-Dimensional

**3D** Three-Dimensional

**AFM** Atomic Force Microscope

**ALD** Atomic Layer Deposition

**ATK** Atomistix Toolkit

**CMOS** Complementary Metal Oxide Semiconductor

**C-V** Capacitance-Voltage

**CVD** Chemical Vapor Deposition

**DFT** Density Functional Theory

**DIBL** Drain Induced Barrier Lowering

**FEM** Finite Element Method

**FUMS** Fast Uncoupled Mode Space

**GAA** Gate-All-Around

**GGA** Generalized Gradient Approximation

**ITRS** International Technology Roadmap of Semiconductors

**LDA** Local Density Approximation

**LDOS** Local Density of States

**MOCVD** Metal Organic Chemical Vapor Deposition

**MOSFET** Metal Oxide Semiconductor Field Effect Transistor

**NCFET** Negative Capacitance Field Effect Transistor

**NEGF** Non Equilibrium Green's Function

**PAW** Projector Augmented Wave

**PDE** Partial Differential Equation

**PECVD** Plasma Enhanced Chemical Vapor Deposition

**PL** Photoluminescence

**PMMA** Polymethyl Methacrylate

QM Quantum Mechanical

**Q-V** Charge-Voltage

**SBH** Schottky Barrier Height

**SCE** Short Channel Effect

**SOC** Spin Orbit Coupling

**SOI** Silicon on Insulator

SS Subthreshold Slope

**TEM** Transmission Electron Microscope

**TFET** Tunnel Field Effect Transistor

**TMDC** Transition Metal Dichalcogenides

**UMS** Uncoupled Mode Space

**UTB** Ultra Thin Body

VASP Vienna Ab-initio Simulation Package

**XAS** X-Ray Absorption Spectroscopy

**XPS** X-Ray Photoelectron Spectroscopy

**XRD** X-Ray Diffraction

# **List of Symbols**

| $\boldsymbol{q}$                 | Elementary Charge                                |

|----------------------------------|--------------------------------------------------|

| k                                | Boltzmann Constant                               |

| h                                | Plank's Constant                                 |

| ħ                                | Reduced Plank Constant                           |

| T                                | Kelvin Temperature                               |

| $L_{ch}$                         | Gate Length                                      |

| $t_{ch}$                         | Channel Thickness                                |

| $t_{tox}$                        | Top Gate Oxide Thickness                         |

| $t_{box}$                        | Bottom Gate Oxide Thickness                      |

| W                                | Channel Width                                    |

| $oldsymbol{arepsilon}_{ch}$      | Dielectric Permittivity of WSe <sub>2</sub>      |

| $\varepsilon_{tox}$              | Dielectric Permittivity of Top Gate Oxide        |

| $\boldsymbol{\varepsilon}_{box}$ | Dielectric Permittivity of Bottom Gate Oxide     |

| $N_A$                            | Uniform Doping Concentration in the Channel      |

| $N_{sd}$                         | Uniform Doping Concentration in Source and Drain |

| $N_{2D}$                         | Inversion Charge Density in the Channel          |

| $N_{dos}$                        | Effective Density of States                      |

| $n_i$                            | Intrinsic Carrier Concentration                  |

| $oldsymbol{\Phi}_{mt}$           | Work-Function of Top Gate Electrode              |

| $\Phi_{mb}$                      | Work-Function of Bottom Gate Electrode           |

| $V_{Gt}$                         | Top Gate Bias                                    |

| $V_{Gb}$                         | Bottom Gate Bias                                 |

| $V_{Gt}'$                        | Effective Top Gate Bias                          |

| $V_{Gb}'$                        | Effective Bottom Gate Bias                       |

| $V_{S}$                          | Source Bias Voltage                              |

| $V_D$                            | Drain Bias Voltage                               |

| $V_{bi}$                         | Built-in Potential                               |

| V <sub>ED</sub> ,                | Flat-Band Voltage of Ton Gate Flectrode          |

Flat-Band Voltage of Bottom Gate Electrode  $V_{FBb}$ Electron Affinity  $\chi_{ch}$  $\boldsymbol{E}_{\boldsymbol{g}}$ Bandgap Energy  $m^*$ Effective Mass Effective Carrier (Electron) Mobility  $\mu_n$ Low Field Carrier (Electron) Mobility  $\mu_{n0}$  $C_{ox}$ Gate Oxide Capacitance  $\boldsymbol{E}_{||}$ Lateral Electric Field from Source to Drain

$g_s$  Spin Degeneracy

$g_i$  Valley Degeneracy

**VSATN** Saturated Carrier (Electron) Velocity

# Chapter 1

# Introduction

## 1.1 Current Trend and Challenges of CMOS Technology

In 1965 Intel's co-founder Gordon Moore famously predicted that the number of components per integrated chip will be doubled every year. He revised his prediction in 1975 [1] stating that the doubling will happen approximately in every two years. This prediction, known as "Moore's Law", has been acting as a guideline for the semiconductor industry to set their goals and made them push harder to break the technological boundaries through constant innovation.

As shown in Figure 1.1, number of transistors per chip grew steadily every year so far, as per Moore's Law. To sustain this growth the semiconductor industry had to face many challenges over the years. The first major blow came in early 2000 w hen the technology node shrunk below 90 nm. The high clock speed and smaller device dimension caused heat to get trapped inside the chips and gradually make them too hot to use. To counter the heating problem the industry halted the increase in clock speed and introduced multi-core processors to keep up with the Moore's law.

**Figure 1.1:** Intel's Microprocessor transistor count [2].

As technology node got smaller, gate length and oxide thickness got smaller as well, leading to Short Channel Effects (SCEs) and gate leakage current. The most common short channel effects are Channel Length Modulation, Drain Induced Barrier Lowering (DIBL), Threshold Voltage R oll-off and Velocity S aturation. O ver the years, the semiconductor industry had came up with various modifications to the basic Si-based MOSFET structure to keep those non-ideal effects in check and continue scaling.

Channel Length Modulation, first observed in long channel MOSFETs, shortens the effective channel length of t he d evice with t he a pplication of drain bi as. B ut t his effect is most prominent with short channel devices where it acts as one of the reasons for the finite positive slope of MOSFET's  $I_{ds}$ - $V_{ds}$  curve in the saturation region. Shorter effective channel length causes v arious other S CEs and disrupts the constant electric field's caling approach. This effect can be countered by increasing the channel doping concentration.

Drain Induced B arrier Lowering (DIBL) is caused when device length is so small that the source to drain lateral electric field is no longer insignificant compared to the vertical electric field due to the gate voltage. This results in lowering of the top of the conduction band barrier with the drain voltage and gives an  $I_{ds}$ - $V_{ds}$  curve with positive slope in the saturation region. Because of this effect the threshold voltage of the device becomes a function of the applied drain voltage. Increased gate control over the channel, either by means of thinner cannel or increased gate confinement, can get rid of this problem.

Another m ajor s hort c hannel e ffect i s Hot Carrier Effect or Impact I onization, where increased lateral electric field due to shorter channel length causes the carrier electrons to gain much higher energies than average electrons in an n-MOSFET. These "Hot Electrons" hits Silicon a toms and creates electron-hole pairs due to impact i onization, which in turn creates a channel-to-substrate current. If the "Hot Electrons" gain enough energy it may even overcome the channel-oxide barrier and damage the gate oxide material. A physical isolation of the channel from the substrate and a thick high- $\kappa$  oxide can prevent this effect.

Increased I ateral el ectric field i n t he ch annel al so cau ses Velocity Saturation, w here t he average v elocity o f ch arge c arriers n o l onger increases I inearly w ith the el ectric field. Velocity saturation is c aused b y i ncreased s cattering o f h ighly energetic e lectrons and i t eventually increases the transit time of carriers through the channel.

Another implication of the increased lateral electric field is avalanche breakdown, which occurs in the channel at the drain end. Avalanche breakdown causes current to flow from drain to source through the substrate underneath the channel, which results in channel breakdown at a lower drain voltage. Silicon-on-insulator (SOI) and Ultra Thin Body (UTB) channel MOSFET can reduce this problem significantly.

Gate Oxide Breakdown is another non-ideal effect associated with the aggressive scaling of transistors. With the reduction of the feature length of a transistor generation, gate oxide thickness gets smaller as well, making it more prone to electrostatic breakdown. This is major

reason of modern day transistor failure and poses a severe challenge to the device reliability. Use of thick high-κ gate oxides can improve the breakdown problem while keeping the gate capacitance at the level demanded by the constant scaling. Thicker gate oxides also reduce the Quantum Mechanical tunneling at the channel-oxide interface and minimize the gate leakage current. Intel is already u sing high-κ gate oxide in their transistors for 45 nm technology node and beyond.

Random Dopant Fluctuation is another major issue with shorter device dimension. A 10 nm channel Si-MOSFET has only 20 to 23 Silicon atoms in between the source and drain, which makes uni form dopi ng of the channel very difficult and threshold vol tages vary from transistor to transistor in a process.

Subthreshold Current is one of the important factors affecting the scaling of transistors. Since the operating voltage is very low for present day devices, the threshold voltage is not much higher than the of f-voltage. This gives rise to a significant drain current even be low the threshold voltage and is one of the major reasons of heating in off-state devices. The severity of this unwanted current is represented by Subthreshold Slope (SS) which indicates the voltage required in milivolt to reduce the drain current by a factor of ten below the threshold voltage. Unfortunately traditional MOSFET structure cannot go below a SS of 60 m V/dec. Transistor structures with higher degree of gate control like Gate-all-round (GAA) FET and FinFET c anh ardy reach that theoretical limit of SS. Only viable option to reduce the SS below 60 mV/dec is the use of Negative Capacitance FET (NCFET) or Tunnel FET (TFET), which is technologically not feasible yet.

**Figure 1.2:** ITRS roadmap [3] for transistor scaling in terms of physical channel length.

The s emiconductor i ndustry c oped w ith t he S CEs a nd ot her non-ideal ef fects m entioned above by using strained S i-Ge channel for 90 nm and hi gh-κ gate ox ides be yond 45 nm technology nodes. From 2011, Intel started to use Tri-gate Silicon transistors in their 22 nm technology nodes, allowing them to have better gate control on the device channel and reduce the S CEs. Intel w ill b e u sing th e s ame T ri-gate S ilicon transistors te chnology in their upcoming processors beyond the 22 nm node. Intel's latest 'Kaby Lake' microprocessors are scheduled to be released by the end of 2016 which will have 14 nm transistors [4]. The 14 nm technology node will be using Silicon Tri-gate transistors as well, with a physical fin-length of 8 nm [5].

As technology node goes down to 10 nm, 7 nm and eventually to 5 nm, to keep up with the Moore's law the physical gate length of the transistors needs to be shrunk as well. According to ITRS 2013 roadmap [3], by the year 2028 the physical gate length of transistors will be 5 nm (Figure 1.2) which means only around 10 S ilicon atoms in the channel. B eyond 10 nm node Tri-gate S ilicon channel transistors will not suffice to overcome the power dissipation and s caling challenges and new material and s tructures will be needed. Intel's Innovation Enabled Technology Pipeline (Figure 1.3) a lso s upports the need f or alternate channel materials and novel structures for future generation transistors.

**Figure 1.3:** Intel's innovation enabled technology pipeline infographic (Courtesy Intel [2]).

To o vercome the electrostatics and power challenges global research efforts have been devoted by researchers to innovate new materials for semiconductor application. These materials range from Organic Materials, III-V Compound Materials, Graphene and other 2D

materials. Along this line of e ffort came the innovation of Monolayer Transition Metal Dichalcogenides (TMDCs) as prospective candidates for the next generation of transistors.

#### 1.2 Two Dimensional Material Channel MOSFETs

Traditional tr ansistor s tructures h ave a lready to uched th eir s caling limit a nd o nly v iable solution to uphold Moore's law lies in 3D structure like Fin-FET and Gate-all-around FET or Ultra Thin Body (UTB) C hannel FETs. Although in extreme s caling limits UTB channel FETs easily outsmart 3D devices, it is not easy to deposit a defect free UTB channel in sub-5 nm g ate le ngth r egime w hen the s emiconductor ma terial h as Zinc-blende or D iamond structure. U se of s ingle l ayered 2D semiconductors [6] like G raphene or m onolayer Transition Metal Dichalcogenides (TMDCs) [7-11], Phosphorine [12-13] and S ilicene [14] as UTB channel solves that problem, as despite being only an atomic layer thick, they exhibit minimal roughness, dangling bonds and defect states.

## 1.2.1 Motivation for Choosing TMDCs

Among the single layered semiconductors, Graphene is not suitable as transistor because of the absence of intrinsic bandgap in Graphene. Although methods of opening bandgap in Graphene like forming Nano Ribbons [15-17], applying strain [18-21] and/or electric field [22-25] have been explored, sufficient bandgap for getting a suitable on/off current ratio is yet to achieve. As an immediate solution to this problem comes the monolayer TMDCs, as they have a very high bandgap in addition to their single layered hexagonal unit cell like Graphene [26-28].

In r ecent years, a mong t he m onolayer TMDCs, Molybdenum Disulphide (MoS<sub>2</sub>) a nd Tungsten Diselenide (WSe<sub>2</sub>), have gained broad interest as transistor channel materials [29-31]. Their high bandgaps and sub-1 nm thickness makes them the most suitable candidate for next generation low pow er transistors. Apart from the application in memory devices and microprocessors, flexibility, transparency, and pristine interfaces made TMDCs ideal candidates for display electronics [32] and bio/gas sensors [33-34]. The TMDC based FET has matured quite a lot over the years with the demonstration of large scale CVD growth technique [35] and demonstration of both n-type and p-type FETs based on MoS<sub>2</sub> and WSe<sub>2</sub> [26, 36-37] FETs with record on-state and off-state performances. In addition, tremendous research efforts are being given to improve the performance of TMDC FETs addressing the residual is sues like high contact resistances with source/drain metals, high interface trap density, low electron and hole mobility and inefficient air-stable doping methods [38].

Other recent 2 D ma terials li ke Phosphorine and Silicene is at el ementary stages of development at present and their transport and scaling performances are not established yet.

This makes TMDCs like  $MoS_2$  and  $WSe_2$  the best possible solution to the ultimate scaling obligations of future transistors for the time being.

#### 1.2.2 Motivation for Choosing WSe<sub>2</sub>

Despite of s howing p romise f or l ow pow er a pplication, M oS<sub>2</sub> based t ransistors ar e l ess suitable for high performance operation since monolayer MoS<sub>2</sub> has a high electron and hole effective mass and low carrier mobility [39].

Recent studies indicates that  $MoS_2$  FETs with high- $\kappa$  dielectric has very low carrier mobility of about  $60 \text{ cm}^2/\text{V} \cdot \text{s}$  due to remote phonon scattering [30, 40]. According to Liu et al. [41] phonon scattering limits the ballistic performance of monolayer  $MoS_2$  FET even at sub-10 nm technology nodes. Moreover, monolayer  $MoS_2$  FETs are yet to demonstrate the scaling performance required to comply with the ITRS roadmap [27, 41-42].

In search of high mobility monolayer channel material which conforms to ITRS roadmap, many other Transition Metal Dichalcogenides are being explored [28] and as a result of that endeavor monolayer WSe<sub>2</sub> based p-FET has been fabricated (Figure 1.4a) [26].

Bulk WSe<sub>2</sub> is quite stable and ox idation resistant than its Sulphide counterpart in case of a humid environment [37, 43]. Bulk WSe<sub>2</sub> crystal also demonstrated carrier mobilities around 500 c m<sup>2</sup>/V.s [9]. The ex perimental monolayer WSe<sub>2</sub> device by Fang et al. [26] with high band gap (1.6 eV) showed higher effective carrier mobility (250 cm<sup>2</sup>/V.s) than monolayer MoS<sub>2</sub> based devices. In recent literature methods of n-type (Figure 1.4b) [44] and p-type (Figure 1.4c) [45] doping of monolayer WSe<sub>2</sub> FET have been demonstrated, which led to fabrication of high performance CMOS inverter (Figure 1.4d) [46] solely based on monolayer WSe<sub>2</sub> channel.

In 2011 Y oon et al. [27] published rigorous Quantum Mechanical (QM) simulation study of short channel ( $L_G$ = 19 n m) monolayer MoS<sub>2</sub> transistor using Fast Uncoupled Mode Space (FUMS) [47-48] based Non-equilibrium Green's Function (NEGF) [49] approach, to predict the performance of such devices. In this thesis similar approach has been followed to perform an extensive QM simulation analysis of monolayer WSe<sub>2</sub> channel transistors.

Besides experimental and physical modeling, compact analytical modeling of monolayer TMDCs is of paramount importance in order to explore the full potential of these materials for ultra-scaled device applications. Cao et al. [38] recently proposed a generalized compact transport model for 2D TMDCs that takes into various non-ideal device effects into account. However, this model is not specific to WSe<sub>2</sub> FETs and the assumptions and simplifications utilized to develop this model deserve some attention specific to WSe<sub>2</sub>. In this work a better model specific to monolayer W Se<sub>2</sub> has be en developed which correctly predicts the performance and transport properties for WSe<sub>2</sub>.

**Figure 1.4:** (a) Monolayer W Se<sub>2</sub> based p-FET by F ang et al. [26] (b) Air stable p-doped WSe<sub>2</sub> FET by Chen et al. [44] (c) n-doped WSe<sub>2</sub> FET by Zhao et al. [45] (d) CMOS inverter implemented on same WSe<sub>2</sub> flake by Tosun et al. [46].

## 1.3 Thesis Objectives

The primary objectives of this work can be divided into following four parts-

- we First, to develop a 1D self-consistent Schrödinger-Poisson solver for simulating the Electrostatics of monolayer WSe<sub>2</sub> channel Field Effect Transistor.

- Second, to develop a F ast U noupled M ode S pace (FUMS) a pproach based 2D numerical transports imulator using Non-equilibrium G reen's F unction (NEGF) Formalism for fully depleted monolayer WSe<sub>2</sub> channel Field Effect Transistor.

- π Third, to de velop a compact current-voltage model for monolayer W Se<sub>2</sub> channel Field Effect Transistor considering different secondary effects.

Fourth a nd final, to a ssess the viability of monolayer W Se<sub>2</sub> channel Field E ffect Transistors f or f uture e lectronic a pplications by evaluating various p erformance parameters like threshold voltage, on c urrent, on/off c urrent r ation, dr ain i nduced barrier lowering and subthreshold swing.

## 1.4 Thesis Organization

The entire thesis is organized into five chapters. A brief outline of each chapter is described below.

The first chapter discusses the current technological status of transistors and briefly sheds lights on the scaling issues and need for futuristic innovations in every aspect of semiconductor devices to uphold the technological progression professed by Moore's law. It also introduces the context of the innovation behind monolayer Transition Metal Dichalcogenide (TMDC) channel MOSFETs.

The second chapter summarizes the research and technological progress achieved so far to make monolayer W Se<sub>2</sub> channel M OSFETs a reality. It presents a brief overview of the literature r elated to d evice s imulation, ma terial d evelopment, f abrication and d evice characterization of monolayer WSe<sub>2</sub> FETs.

The third chapter describes the development of a numerical quantum mechanical Electrostatic and Transport simulator for the monolayer WSe<sub>2</sub> device. At the first part of this chapter the device structure is defined along with governing equations and theoretical discussions on the electrostatic a nd tr ansport c haracteristics is p erformed. T his s ection is followed by configuration m ethods of r elated s oftware pl atform f or t he s imulator. Then ext s ection presents s ome k eyr esults obtained f rom the s imulator developed and be nchmarks the accuracy of the s imulator. F inally v arious p erformance p arameters are extracted from the simulated results to evaluate the feasibility of the proposed s tructure in terms of transport characteristics.

The fourth chapter introduces a s implified compact an alytical drain current-voltage model from fundamental treatment of charge-potential system of the device. This chapter rigorously studies the mathematical f ormulation of the device system and in troduces physically justifiable assumptions to simplify the problem. This chapter gradually develops a closed form analytical model of the current-voltage problem and defines few fitting parameters to benchmark its output. Finally, few key results from the analytical model have been demonstrated at the last part of this chapter.

The fifth and last chapter of this thesis outlines the conclusion of this thesis work. It also briefly describes prospective fields of future improvements and modifications to this work.

# Chapter 2

# Exploration of the Monolayer WSe<sub>2</sub> FET

## 2.1 Simulation

#### 2.1.1 Material Level Simulation

Monolayer WSe<sub>2</sub> has very different properties than their bulk form. For example, bulk WSe<sub>2</sub> has an indirect bandgap of 1.2 eV, whereas monolayer WSe<sub>2</sub> has a 1.6 eV direct bandgap [39, 50]. To seek for the suitable T MDC with desired property, material level simulation is necessary. Solving the band structure using first principle DFT simulation can provide that valuable insight to the material properties of monolayer TMDCs. Open source softwares like Quantum E spresso [51] can perform such simulations. Commercial to ols like A tomistix ToolKit (ATK) [52] are also available.

In 2014 Zhao et al. [45] utilized First Principle Density Functional Theory (DFT) [53-54] calculations to study their experimental p-doped W Se<sub>2</sub> transistor. For the simulation, they have considered p lane w ave b asis s ets and P rojector A ugmented W ave (PAW) pseudopotentials [54-55] in the Vienna Ab-initio Simulation Package (VASP) [53, 56-57].

In 2013 Liu e t al. [37] studied r ole of m etal c ontacts i n designing high p erformance monolayer n -type W Se<sub>2</sub> Transistors us ing A b-initio DFT calculations. The s imulation indicated that the d-orbitals of the contact metal play a vital role in creating low resistance ohmic contacts with monolayer WSe<sub>2</sub>. In addition to the presence of d-orbitals, smaller work function of the contact metal compared to WSe<sub>2</sub> affinity is necessary for the best possible n-WSe<sub>2</sub>-metal contact.

In 2014 K ang et al. [58] computationally studied metal contacts to monolayer Transition Metal Dichalcogenide semiconductors. Their work employed the Kohn-Sham DFT [55] to compute the band structure of Monolayer WSe<sub>2</sub> because it offers significant computational advantages over ot her Ab-initio m ethods. Although, K ohn-Sham D FT sometimes underestimates the b andgap of the m aterials for most common exchange-correlation potentials like the generalized gradient a pproximation (GGA) [59] and the local density approximation (LDA) [60], this work revealed that LDA alone is sufficient to get the theoretically and experimentally accurate bandgap of 1.6eV [61].

In 2012 K ang et al. [28] performed numerical DFT calculations using A tomistix T oolKit (ATK) [52]. This work calculated optimized geometries, PDOS, electron densities and tunnel

barriers of metal-TMDC contacts using DFT to discover that Pd is the best source(drain)-contact metal for monolayer intrinsic WSe<sub>2</sub> and forms p-type contact.

In 2013 Liu et al. [39] performed Ab-initio DFT calculations on metal-WSe<sub>2</sub> system to study the performance of monolayer WSe<sub>2</sub> FET. For metal they have chosen Ag (111) since it has a small-work-function which forms good contacts for n-type devices. Calculation revealed that although natural WSe<sub>2</sub> is intrinsic, it can be n-doped by depositing Ag onto the monolayer.

In 2015 S engupta et a l. [62] showed the ef fects of el ectron-phonon s cattering on t he performance of monolayer n-WSe<sub>2</sub> MOSFET using material parameters obtained from LDA-DFT calculations. They concluded that the performance of the monolayer WSe<sub>2</sub> FET is less prone to phonon s cattering and has a ballisticity of 83% for a 10 nm channel. On the other hand, in the presence of scattering there can be a 21–36% increase in the intrinsic time delay as well.

In 2016 Su et al. [63] employed the Vienna Ab-initio DFT calculations to study the electronic properties of  $MoS_2/WSe_2$  heterobilayers and the effect of both the external in-plane biaxial strain and out-of-plane compressive strain on it.

In 2015 H osseini e t a l. [64] cal culated t he bandstructure of W Se<sub>2</sub> using LDA-DFT mechanism in the S IESTA c ode [65] and s tudied the effect of s train on the electronic bandstructure and low field mobility. The study revealed sharp increase in the mobility of WSe<sub>2</sub> with relatively small tensile strain. Whereas, a relatively small increase in compressive strain r esults in initial decrement of the mobility, which then increases again with further increase in compressive strain.

In 2014 D esai et al. [66] studied the strain-induced indirect to direct bandgap transition in multilayer WSe<sub>2</sub>. T heir ex perimental results d emonstrated a d rastic en hancement in Photoluminescence intensity f or multilayer W Se<sub>2</sub> under uni axial t ensile strain, w hich i s attributed to a n in direct to direct bandgap t ransition. D FT c alculation s upported t he experimental results and revealed very small energy difference exists between the direct and indirect bandgaps of WSe<sub>2</sub> and the transition is easily controllable u sing p ractically achievable stain on the channel.

In 2016 Wang et al. [67] made a comparative study of the interfacial properties of monolayer and bilayer WSe<sub>2</sub> with different metals using the DFT band structure calculation. The study found that, in the absence of the spin-orbital coupling (SOC) Pd contact has the minimum hole Schottky Barrier Heght (SBH). Whereas with SOC, WSe<sub>2</sub>-Pt interface has the minimum hole SBH and thus acts as a p-type Ohmic contact.

In 2013 D uerloo e t a l. [68] e mployed D FT calculations to e stimate the piezoelectric coefficients WSe<sub>2</sub> along w ith f ew ot her m onolayer T MDCs. T he s tudy r evealed t hat monolayer TMDCs possesses greater piezoelectric coefficients compared to commonly used Wurtzite piezoelectrics.

In 2015 A llain et al. [69] us ed DFT calculations to show that, due to orbital overlap and reduced tunnel barriers, edge contacts lead to a shorter bonding distance than top contacts for both the monolayer and multi-layer TMDs.

In 2014 Y uan e t a l. [70] s tudied t he s pin-valley-coupled circular pho togalvanic c urrent generation i n WSe<sub>2</sub> using V ASP D FT p ackage. They h ave demonstrated a s pin-coupled valley photocurrent in a WSe<sub>2</sub> electric-double-layer transistor and found that the direction and magnitude of the current is dependent on the degree of circular polarization and external electric field.

In 2013 Liang et a l. [71] r eported Q uasiparticle b and-edge e nergy a nd ba nd of fsets of monolayer WSe<sub>2</sub> using first-principle DFT calculations. In addition to bandgap calculations, absolute band-edge energies with respect to the vacuum level have been estimated.

In 2015 Zhou et al. [72] investigated the phonon t ransport of monolayer  $WSe_2$  employing DFT with the phonon Boltzmann transport equation. The study found that, compared to other 2D ma terials the monolayer  $WSe_2$  has relatively lower thermal conductivity, which is attributed to its Debye frequency and heavy atom mass.

In 2015 J iang e t al. [73] us ed Ab-initio quantum simulation to e stimate the t ransport performance and scaling limit of the sub-10 nm monolayer TMDC TFETs. They found that, in terms of high-performance and low-operating-power WTe<sub>2</sub>-TFET offers the them ost promising results compared to WSe<sub>2</sub> and other TMDC TFETs.

In 2015 Dai et al. [74] used DFT computations to study bandgap tunability of the multilayer  $WSe_2$  sheets with the application of external electric fields. The study concluded that the bandgap of  $WSe_2$  sheet decreases with the increment of the vertical electric field and gradually turns it metallic at about of 0.6–2.0 V/nm electric field, depending on the number of layers present in the sheet.

In 2013 M ishra et al. [42] studied the dependence of the performance of TMDC FETs on materials and number of layers, using V ienna Ab-initio S imulation P ackage (VASP) and ballistic quantum transport calculations. The study of 5 nm channel TMDC FET with a 2 nm underlap at both side of the gate revealed excellent switching performance but lacked the peak current required by ITRS roadmap at this level of scaling.

#### 2.1.2 Device Level Simulation

Once the material parameters are in hand the performance of the device to be made with that material can be evaluated. Different p hysical parameters and dimensions need to be optimized for better performance of the device. These are done by device level simulation of

monolayer T MDC FETs. A s an el ectron d evice, both t he e lectrostatics a nd t ransport properties of monolayer TMDC FETs are required to be studied to get the optimal structure with greatest performance.

#### 2.1.2.1 Simulation of Electrostatics

To obtain the Electrostatics of the device, 1-D Schrödinger and Poisson equations is solved self-consistently in the direction perpendicular to the channel. This is done by coupling COMSOL Multiphysics [75] and MATLAB [76]. Introduction of COMSOL Multiphysics allows dealing with complex geometry. Only the partial differential equations of Schrödinger and Poisson are solved in COMSOL environment. The numerical data are exported to MATALB in real time at every iteration and all the numerical coupling and calculations are done inside MATLAB. Upon convergence this simulation gives complete electrostatics of the device including C-V characteristics, surface-potential, charge profile, effect of  $D_{it}$  and fixed oxide charge etc. So far no work in the literature investigates the detailed electrostatics of the monolayer WSe<sub>2</sub>.

#### 2.1.2.2 Simulation of Transport Properties

Transport simulation can be done using FUMS [47-48] approach. Here, Poisson equation is to be solved for a 2D cross section along the channel. Schrödinger equation is to be solved only for one 1D cross section perpendicular to the channel, from which the solution of the Schrödinger equation across the channel can be approximated applying Perturbation Theory. The channel is treated as fully depleted and channel charge is calculated using N EGF Formalism. U pon convergence, the simulator can provide B allistic drain current-voltage characteristics, Threshold Voltage, Transconductance profile, Subthreshold Swing and other performance parameters. This simulator can accurately model S CEs like D rain Induced Barrier Lowering (DIBL) and Threshold V oltage S hifting. Here also, the differential equations can be solved by COMSOL and coupling and calculations can be done in MATLAB environment.

In 2013 Chang et al. [77] compared ballistic transport characteristics of monolayer WSe<sub>2</sub> with other T MDCs using atomistic full-band N EGF simulations with T ight B inding potentials obtained from DFT. They considered n-type TMDCs with channel length of 15 nm deposited on a 50 nm t hick S iO<sub>2</sub> substrate, 2.8 nm t hick H fO<sub>2</sub> as t op ox ide and n -type doping concentration of  $7\times10^{13}$  cm<sup>-2</sup> at source and drain. The NEGF simulations revealed excellent off-state and short channel performances of the TMDC FETs in terms of SS and DIBL.

In 2013 M ishra et a1. [42] studied the transport performances of TMDC devices by using Non-equilibrium Green's Function (NEGF) formalism to calculate the charge and then self-consistently solving the Poisson's equation. Their an alysis r evealed s caling p otential of TMDC FETs up to 5 nm channel length with excellent on/off current ratio of 10<sup>6</sup>, SS of 65

mV/dec and transconductance of 150  $\mu$ S/ $\mu$ m. The study also revealed that, increasing the number of layers in TMDC FETs does not increase the on c urrent as the channel loses the gate control with the increasing number of channel layer.

In 2014 Cao et al . [30] p resented dissipative q uantum t ransport s imulations us ing Non-equilibrium Green's Function (NEGF) formalism to study the scalability and performance of monolayer/multilayer 2D FETs. The study covered the effects of gate underlap, scattering strength and c arrier effective mass and c oncluded that the high mobility and low effective mass of WSe<sub>2</sub> is suitable for bot h high-performance and low-standby-power transistor applications up to 5.9 nm technology node. The work used HfO<sub>2</sub> as both the top and bottom gate ox ide and ensured a high source/drain dop ing of  $6.5 \times 10^{13}$  cm<sup>-2</sup> in order to ma intain ohmic source/drain contacts. According to this study, 2D FETs has the potential to follow the ITRS roadmap up to the year 2026.

In 2015 Ilatikhameneh et a l. [78] d eveloped a s caling t heory f or electrically d oped 2 D transistors using full band atomistic NEGF simulations that revealed that for  $WSe_2$  TFET the same EOT but different oxide thicknesses can result in three order of magnitude difference in on-current. The work also revealed that both physical thickness of the oxides and spacing between the gates are major performance parameters for electrically doped 2D TFETs, with the former being most important.

In 2014 M ajumdar e t al. [79] simulated a non-planar double ga te F ET structure w ith monolayer T MDC channel u sing an effective mass b ased H amiltonian (H) and N EGF formalism. The proposed F in FET-compatible n on-planar s tructure has  $SiO_2$  as f in ox ide surrounding the TMDC channel. The source/drain doping, EOT of the oxide and monolayer thickness of the channel are considered  $9 \times 10^{12}$  cm<sup>-2</sup>, 0.7nm and 0.65 nm r espectively. Simulation revealed that, both over-the-barrier thermionic and direct source-drain tunneling currents govern the characteristics of such ultra scaled devices.

In 2013 K umar et al. [80] investigated the electron transport properties of layered T MDC FETs with non-equilibrium Green's Function (NEGF) formalism u sing D FT H amiltonian. The transport characteristics are calculated using the well known Landauer-Buttiker formula [81].

In 2014 Zhang et al. [82] performed a simulation study on valley-polarized current generation and transport in monolayer W Se<sub>2</sub> transistors. To simulate the TMDC transistor, this work used D FT calculations carried out within the K eldysh non equilibrium Green's function (NEGF) formalism [83–85]. It was estimated that to make WSe<sub>2</sub> valley transistors with perfect valley polarization at least 50-100 nm channel length is required depending on the applied gate bias voltage.

## 2.2 Analytical and Compact Modeling

Analytical and compact modeling can give better insight into the operation of a device. For monolayer TMDCs classical transport models will not be appropriate because of the presence of high degree of confinement. The quantum model can be easily formulated by assuming that the potential drop at the ultrathin channel in the confinement direction is negligible. Also, the potential across the channel can be accurately approximated as a quadratic function of the dimension. U sing t his a pproximation and solving S chrödinger and P oisson e quation analytically can give the surface potential profile and hence the current transport across the channel. For modeling threshold voltage only semiclassically approximated charge can be used to obtain simplified c losed form equation. Once the primary analytical model is developed various secondary effects like Mobility Degradation and Interface Traps etc. can also be incorporated into the model.

In 2012 J iménez et al. [86] presented a physics-based model for the surface potential and drain current for monolayer T MDC FET. The work took the 2D density-of-states of the monolayer TMDC and its impact on the quantum capacitance into account and modeled the surface pot ential. The authors further developed an expression for the drain current considering the drift-diffusion mechanism. The analytical expressions of surface potential and drain current derived in this work are applicable for both the subthreshold and above threshold regions of operation. Although the analytical model is be nchmarked a gainst a prototype TMDC transistor, it has some major limitations like non-scalability due to lumped capacitor network based intrinsic device characteristics and in sufficient differentiation between Fermi potential (voltage) and electrostatic potential in the model.

In 2014 Cao et al. [38] presented an analytical I-V model for 2D TMDC FETs as well. The model takes physics of monolayer TMDCs into a count and of fers a single closed form expression for all three i.e. linear, saturation, and subthreshold regions of operation. The authors also incorporated various non-ideal secondary effects like interface traps, mobility degradation, and inefficient doping in the model, although that resulted in current equations having an integral form instead of closed form. The compact analytical model has been benchmarked against both numerical device simulation and experimental result.

In 2015 N ajam et a l. [87] i ntroduced a surface p otential-based l ow-field d rain cu rrent compact model for 2D TMDC FET taking dielectric interface traps into account. In this work, the de rived dr ain current m odel is cap able of self-consistently c alculating t he s urface potential of t he de vice and i nterface t rap charge  $Q_{it}$  with the help of an ex perimentally reported interface trap distribution. The final current equation has a closed form and works well for all regions of operation.

## 2.3 Fabrication and Testing

Over the year many groups have experimentally demonstrated monolayer W Se<sub>2</sub> channel transistors. These work ranges from basic W Se<sub>2</sub> MOSFETs to advanced devices like W Se<sub>2</sub> based TFET, TMDC Heterostructure FET and so on. In this section few of those works have been introduced from the literature.

In 2012 Fang e t a l. [26] reported high performance p -type monolayer WSe<sub>2</sub> FET with chemically dop ed source and drain contacts and high- $\kappa$  gate dielectrics. The FET had a S i substrate with 270 nm SiO<sub>2</sub> bottom oxide, 17.5 nm ZrO<sub>2</sub> top gate dielectric and Pd metal gate. At room temperature, the monolayer transistors exhibited an effective hole mobility of ~250 c m²/V.s, s ubthreshold s wing of ~60 m V/dec, and on -off c urrent r atio of 10  $^6$  with a channel length of 9.4  $\mu$ m.

In 2015 M ovva et al. [88] demonstrated dual-gated p-type few-layer W Se<sub>2</sub> FET with high work-function Pt source/drain contacts, Pd top gate and a hexagonal boron nitride top-gate dielectric. The devices achieved hole mobility and on-off current ratio of 140 cm<sup>2</sup>/V.s and  $10^7$  respectively at room temperature. The W Se<sub>2</sub> layer is deposited on a SiO<sub>2</sub>/Si substrate with a effective channel length of 6  $\mu$ m and supported a maximum drive current of 5  $\mu$ A/ $\mu$ m at -5 V top gate bias voltage.

In 2014 Tosun et al. [46] demonstrated a CMOS inverter by implementing both n and p-type inverter on the same WSe<sub>2</sub> flake for the first time. In the p-FET, high work function Pt is used to inject hole at the source contact of WSe<sub>2</sub>. Whereas, the n-FET is formed by degenerately doping the Pt-WSe<sub>2</sub> contact by Potassium (K). Both the n and p-type FETs achieved an onoff current ratio of  $10^4$  and the DC gain of the inverter was measured to be greater than 12. The inverter h ad  $ZrO_2$  top g ate di electric and 10 nm thick W Se<sub>2</sub> flake g rown on S iO<sub>2</sub>/Si substarte. The effective channel length was 2  $\mu$ m with a gate underlap and overlap at the source/drain contacts of n and p-FET respectively.

In 2013 Banerjee et al. [39] demonstrated a back gated monolayer WSe<sub>2</sub> n-FET on a 72 nm Al<sub>2</sub>O<sub>3</sub>/Si s ubstrate. The d evice u tilized Ag (10 nm)/Au (100 nm) for s ource/drain contact which provides excellent contact resistances with doped monolayer WSe<sub>2</sub>. The fabricated n-FET had channel length and width of 1.5  $\mu$ m and 1  $\mu$ m respectively and displayed on-current of 110  $\mu$ A/ $\mu$ m and mobility of 48 cm<sup>2</sup>/V.s.

In 2014 Zhao et a l. [45] demonstrated a ir s table p-type doped WSe<sub>2</sub> FET u sing c ovalent functionalization. The p-FET had a 7 nm thick WSe<sub>2</sub> flake grown on 260 nm thick SiO<sub>2</sub> on Si substrate using mechanical exfoliation with a varying channel length from 500 nm -2  $\mu$ m. P-doping of WSe<sub>2</sub> was achieved through the chemical absorption of NO<sub>x</sub> at 150 °C leading to a maximum hole concentration of  $10^{19}$  cm<sup>-3</sup>. This degenerate p-type doping enabled 5 orders of magnitude contact resistance reduction at Pd-WSe<sub>2</sub> source/drain contacts.

In 2014 C hen et a l. [44] demonstrated airs table n-doped 2  $\mu$ m channel WSe<sub>2</sub> FET using positively charged SiN<sub>x</sub> films at 150°C. The top SiN<sub>x</sub> and bottom SiO<sub>2</sub> gate dielectrics had thicknesses of 50 m and 260 nm respectively. The SiN<sub>x</sub> film with positive charge centers is deposited on the WSe<sub>2</sub> surface using P lasma Enhanced C hemical Vapor D eposition (PECVD) which electrostatically induced electrons at the WSe<sub>2</sub> channel. The fixed positive charge is controllable by flows and ratios of NH<sub>3</sub> and SiH<sub>4</sub> gases used to form the SiN<sub>x</sub>. Highest fixed positive charge at SiN<sub>x</sub> top layer and electron mobility in the WSe<sub>2</sub> channel achieved is this device are  $1.75 \times 10^{12}$  cm<sup>-2</sup> and 70 cm<sup>2</sup>/V.s respectively.

In addition t o t hose de vices de scribed a bove, MoS<sub>2</sub>/WSe<sub>2</sub> [89-90] a nd SnS<sub>2</sub>/WSe<sub>2</sub> [91] heterojunction transistors have been demonstrated recently by Prof. Palacios's group in MIT. The same group demonstrated high performance WSe<sub>2</sub> CMOS devices in 2015 [92]. In 2015 Li et al. [93] proposed a WSe<sub>2</sub>/SnSe<sub>2</sub> heterojunction Thin-TFET structure which displayed a remarkable 14 mV/dec subthresold swing and 300 μA/μm on current.

## 2.3.1 Deposition

Deposition of M onolayer WS  $e_2$  can be done on a  $SiO_2/Si$ , G raphene or B N substrate by 'Mechanical E xfoliation' of bulk T MDC crystal or Chemical V apor D eposition (CVD) process. Over the year several methods have been introduced in the literature to deposit the height quality monolayer  $WSe_2$  in an easily controllable and scalable manner.

In 2012 Fang et al. [26] applied 'Mechanical Exfoliation' method to deposit monolayer  $WSe_2$  from bulk  $WSe_2$  crystals on a 270 nm thick  $SiO_2/Si$  substrate. Atomic F orce M icroscope (AFM) measurements revealed the thickness of the monolayer to be around 0.7 nm, which agrees with the crystallographic data of  $WSe_2$ . The growth process is described below-

- 1. Using mechanical ex foliation v ia scotch t ape WSe<sub>2</sub> layers are t ransferred onto a Si/SiO<sub>2</sub> substrate.

- 2. Transferred WSe<sub>2</sub> is submerged in acetone for 1 hour to remove the tape residues.

- 3. Source/drain metal contacts is deposited by lithography and metallization of Pd/Au of length 20-30 nm.

- 4. Gate electrodes is then patterned by E-beam Lithography using PMMA positive resist and keeping 300 500 nm underlap near the source/drain contacts.

- 5. As the top g ate di electric, 17.5 nm thick Z rO<sub>2</sub> is de posited a t 120 °C us ing ALD process.

- 6. Pd top gate is deposited using metallization.

- 7. Device is exposed to a NO<sub>2</sub> to p-dope the underlapped S/D regions for better contact resistances. Channel remains almost intrinsic but can be p-doped by exposing it to NO<sub>2</sub> environment before the ZrO<sub>2</sub>/Pd is placed.

In 2013 Huang et al. [94] demonstrated synthesis of large-area and highly crystalline W Se<sub>2</sub> monolayers for device application using gas phase selenization of W O<sub>3</sub> in a hot-wall C VD chamber. The process of WSe<sub>2</sub> synthesis (as shown in Figure 2.1) is described below-

- 1. WO<sub>3</sub> powder is placed in hot-wall CVD furnace.

- 2. Sapphire substrate is placed inside the deposition chamber in the direction of the flow.

- 3. Furnace is heated up to 950°C.

- 4. Selenium (Se) and Ar/H<sub>2</sub> gas mixture is passed through the hot CVD furnace over the sapphire substrates. H<sub>2</sub> plays an important role in activating the Selenization process.

- 5. Near the furnace where temperature is around 850°C, triangular WSe<sub>2</sub> flakes with lateral domain dimension from 10 μm and to 50 μm is deposited on the Sapphire substrates. These large flakes are mostly monolayer, with o ccasional presence of bilayer WSe<sub>2</sub> as well.

- 6. On the Sapphire substrates slightly distant from the furnace have temperatures around  $750^{\circ}$ C. On these substrates, monolayer WSe<sub>2</sub> film with relatively small domain size (lateral dimension < 5  $\mu$ m) is grown. The thicknesses of these films are 0.73 nm, which is in agreement with the thickness of mechanically exfoliated monolayer WSe<sub>2</sub>.

**Figure 2.1:** Synthetic large scale growth of monolayer WSe<sub>2</sub>. (a) CVD growth of WSe<sub>2</sub> in the process of Selenization of WSe<sub>2</sub> powers in a hot-wall CVD furnace. (b) Monolayer WSe<sub>2</sub> flakes on Sapphire substrate at 850°C (optical microscope image). (c) Monolayer WSe<sub>2</sub> films on Sapphire substrate at 750°C (optical microscope image). (d) AFM i mage of monolayer WSe<sub>2</sub> on a Sapphire substrate grown at 850°C. (Image courtesy Huang et al. [94])

In 2014 Eichfeld et al. [95] demonstrated a scalable synthesis method of large-area, mono and few-layer WSe<sub>2</sub> using Metal Organic Chemical Vapor Deposition (MOCVD). This method allows better control of the vapor-phase chemistry unlike the WO<sub>3</sub> powder vaporization CVD technique described earlier. In addition, a wide range of substrates including Epitaxial and CVD Graphene, Sapphire, and Boron Nitride are acceptable in this method. This work also studied the impact of temperature, pressure, Se:W ratio, and substrate on the atomic structure and properties of the deposited WSe<sub>2</sub>. The growth process is described below-

- 1. The deposition process starts with the placement of Tungsten Hexacarbonyl (W(CO)<sub>6</sub>) and Dimethylselenium ((CH3)<sub>2</sub>Se) precursors in a v ertical cold wall reactor with an induction heated susceptor.

- 2. The precursors are transported into reactor using a bubbler manifold which allows independent control over each precursor concentration.

- 3. H<sub>2</sub>/N<sub>2</sub> mixtures are used as carrier gas.

- 4. The sample precursors are heated to 500°C and kept at this temperature for 15 min to remove any water vapor. The temperature was increased at a rate of 80°C/min.