# PHYSICS BASED 2-D ANALYTICAL MODEL OF TRIPLE MATERIAL DOUBLE GATE TUNNEL FIELD EFFECT TRANSISTOR

by

Samia Safa Student ID: 0413062208

A thesis submitted in partial fulfillment for the degree of **Master of Science**

in the

Department of Electrical and Electronic Engineering Bangladesh University of Engineering and Technology

August, 2016

# **Approval Certificate**

The thesis titled "PHYSICS BASED 2-D ANALYTICAL MODEL OF TRIPLE MATERIAL DOUBLE GATE TUNNEL FIELD EFFECT TRANSISTOR" submitted by Samia Safa, Student ID: 0413062208 P, Session: April 2013 has been accepted as satisfactory in partial fulfillment of the requirement for the degree of MASTER OF SCIENCE IN ELECTRICAL AND ELECTRONIC ENGINEER-ING on August 3, 2016.

#### **Board of Examiners**

1

Chairman (Supervisor)

Dr. Md. Ziaur Rahman Khan Professor, Department of EEE, BUET, Dhaka-1205, Bangladesh

Dr. Quazi Deen Mohd Khosru Professor and Head, Department of EEE, BUET, Dhaka-1205, Bangladesh

Dr. Md. Shafiqul Islam Professor, Department of EEE, BUET, Dhaka-1205, Bangladesh

Act

4.

Dr. Muhibul Haque Bhuyan Professor and Chairman, Department of EEE & ICE, Southeast University, Dhaka, Bangladesh. Member (Ex-Officio)

Member

Member (External)

# Declaration

It is hereby declared that this thesis or any part of it has not been submitted elsewhere for the award of any degree or diploma.

JUN コカマひり

(Samia Safa)

Dedicated to

My beloved family.....

# Acknowledgements

I would first like to thank Almighty Allah for His continuous blessings upon me, especially in my educational life, and for bringing me to the position where I am at this very moment.

My completion of this thesis could not have been accomplished without the ceaseless guidance and support of my thesis supervisor, Dr. Md. Ziaur Rahman Khan. He was inspirational in making me come up with the idea of working with Tunnel Field-Effect Transistor. From the very beginning of my thesis work and throughout the last few months, he guided me thoroughly. I consider myself very lucky to have a thesis supervisor like him. And I earnestly hope to maintain an active relation with him for our future research works in the days to come.

Next, I would like to express my gratitude to my fellow researcher, Samantha Lubaba Noor for her continuous support and help for the last one year. I am also very grateful to the Department of EEE, East West University, Bangladesh for letting me use their resources for my simulations.

Finally, my deepest gratitude to my caring, loving, and supportive family. Your encouragement when the times got rough is much appreciated and duly noted.

# Abstract

Tunnel FETs are attractive new devices for low-power applications due to their low off-current and their potential for a small subthreshold swing. In this work, analytical models of potential, electric field, drain current and gate threshold voltage have been proposed for Triple Material Double Gate (TMDG) TFET structure. Surface potential and electric field are formulated by exploiting Gauss's law in the lightly doped body region. A closed form expression of band-to-band tunneling current is developed by utilizing tunneling generation rate and the derived electric field model. An analytical model of gate threshold of TMDG TFET is derived from the surface potential equation based on its physical definition for TFETs. The developed models are then generalized for single and multiple material gate TFET structures. A numerical model of TMDG TFET structure is developed using ATLAS, Silvaco device simulator. The device parameters are chosen carefully based on the literature, so that the structure can provide high ON current, low leakage current and can suppress the ambipolar behavior of the device. The proposed models are then verified against the TCAD simulation results. The effects of varying device parameters and bias conditions on device performance are also analyzed. Based on the analysis, the validity range of the proposed models are defined and a solution to extend this validity range is suggested. The effect of Si film thickness on device's electrical characteristics is also studied, the physics governing it is detailed and an optimum value of Si film thickness is suggested. Analytical models are crucial in understanding the characteristics of a device and the proposed models will be helpful for designing circuits containing single material gate and multiple material gate TFET devices.

# Contents

| Aţ | prov        | al Certificate                                 | i   |  |

|----|-------------|------------------------------------------------|-----|--|

| De | Declaration |                                                |     |  |

| De | edicat      | tion                                           | iii |  |

| Ac | cknow       | vledgements                                    | iv  |  |

| Ał | ostrac      | et                                             | v   |  |

| Ta | ble of      | f Contents                                     | vi  |  |

| Li | st of l     | Figures                                        | ix  |  |

| 1  | Intr        | oduction                                       | 1   |  |

|    | 1.1         | CMOS Solid State Switching Devices             | 1   |  |

|    | 1.2         | Proposed Alternatives to CMOS-based Logic      | 5   |  |

|    |             | 1.2.1 Electromechanical Devices                | 7   |  |

|    |             | 1.2.2 Tunneling Field Effect Transistor (TFET) | 9   |  |

|    | 1.3         | Motivation and Objectives                      | 11  |  |

|    | 1.4         | Thesis Organization                            | 12  |  |

| 2 | TM                       | DG TFI    | ET                                      | 14 |

|---|--------------------------|-----------|-----------------------------------------|----|

|   | 2.1                      | Introdu   | uction                                  | 14 |

|   | 2.2                      | Histor    | y and State-of-the-art of the TFET      | 14 |

|   | 2.3                      | Device    | e Structure                             | 19 |

|   | 2.4                      | Operat    | ting Principle of TFETs                 | 20 |

| 3 | Ana                      | lytical N | Model of TMDG TFET                      | 22 |

|   | 3.1                      | Introdu   | uction                                  | 22 |

|   | 3.2                      | Electri   | c Potential Distribution                | 23 |

|   |                          | 3.2.1     | Surface Potential                       | 23 |

|   |                          | 3.2.2     | 2D Potential Model                      | 28 |

|   | 3.3                      | Electri   | c Field                                 | 30 |

|   | 3.4                      | Drain     | Current: Band-to-Band Tunneling         |    |

|   |                          | Curren    | ıt                                      | 31 |

|   | 3.5                      | Gate T    | Threshold Voltage                       | 35 |

|   |                          | 3.5.1     | Definition of $V_{TH}$ for TMDG TFET    | 35 |

|   |                          | 3.5.2     | $V_{TH}$ Modeling                       | 37 |

| 4 | Nun                      | nerical I | Model of TMDG TFET                      | 39 |

|   | 4.1                      | Introdu   | uction                                  | 39 |

|   | 4.2                      | Overvi    | iew of Silvaco Atlas                    | 40 |

|   | 4.3 Numerical Simulation |           | rical Simulation                        | 41 |

|   |                          | 4.3.1     | Defining The Structure                  | 41 |

|   |                          | 4.3.2     | Defining Material Parameters and Models | 42 |

|   |                          | 4.3.3     | Selecting Numerical Methods             | 46 |

|   |                          | 4.3.4     | Obtaining Solutions                     | 47 |

|    |                 | 4.3.5 Result Interpretation        | 48 |  |  |

|----|-----------------|------------------------------------|----|--|--|

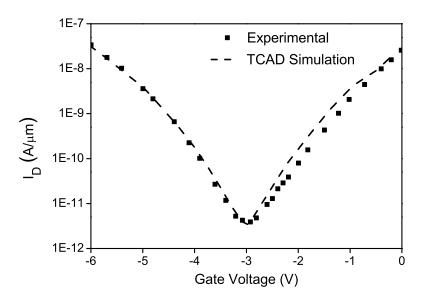

|    | 4.4             | Extraction of Tunneling Parameters | 49 |  |  |

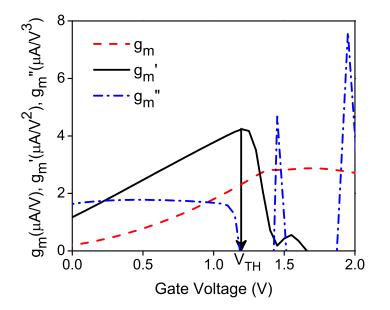

|    | 4.5             | Extraction of Threshold Voltage    | 50 |  |  |

| 5  | Resi            | Ilts and Discussion                | 52 |  |  |

|    | 5.1             | Introduction                       | 52 |  |  |

|    | 5.2             | Device parameter                   | 52 |  |  |

|    | 5.3             | Analytical Model Validation        | 53 |  |  |

|    |                 | 5.3.1 Electric Potential           | 53 |  |  |

|    |                 | 5.3.2 Electric Field               | 59 |  |  |

|    |                 | 5.3.3 Tunneling Current            | 64 |  |  |

|    |                 | 5.3.4 Gate Threshold Voltage       | 68 |  |  |

|    | 5.4             | Si Film Thickness Optimization     | 73 |  |  |

| 6  | Con             | clusion and Future Work            | 78 |  |  |

|    | 6.1             | Conclusion                         | 78 |  |  |

|    | 6.2             | Future Works                       | 80 |  |  |

| Bi | Bibliography 81 |                                    |    |  |  |

# **List of Figures**

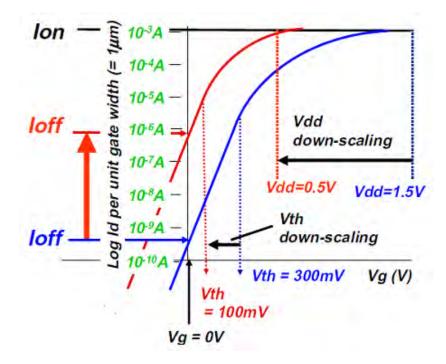

- 1.2 Two MOSFET  $I_D V_{GS}$  curves operated at a high supply voltage (blue) and low supply voltage (red). To maintain the same  $I_{ON}$ , the threshold voltage of the red curve must decrease. This results in exponentially increased  $I_{OFF}$  because of the constant SS [6].

3

4

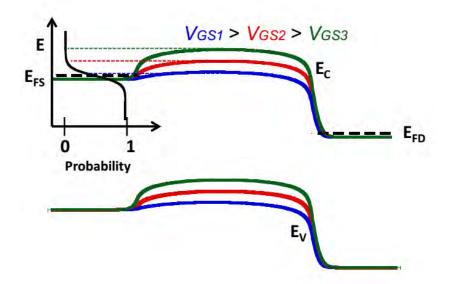

- 1.3 Energy band diagram along the channel of a MOSFET with three different gate voltages applied. The Fermi-Dirac distribution function is sketched with respect to the source Fermi level to illustrate the electron occupation as a function of energy in the source. . . .

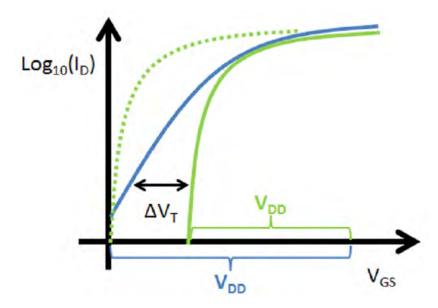

- 1.4 A steeply switching device proves a compelling goal for a MOS-FET replacement. The blue curve represents a traditional MOS-FET *I V* transfer characteristic. The solid green curve comparatively highlights the main benefit of a steeper transfer characteristic: a reduction in the power supply voltage, *V*<sub>DD</sub>. Presumably, a steeper SS characteristic can be threshold-voltage shifted (as depicted in the dashed green curve) [8]. . . . . . . . . . . . . 6

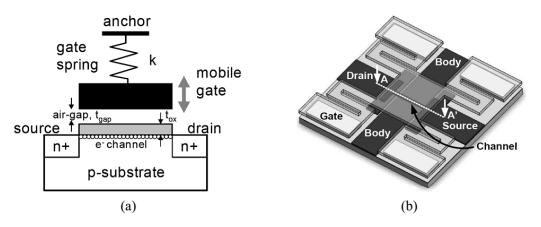

1.5 Two possible designs for MOSFET-like MEMS relays, with a

- source, drain, and gate. (a) From [17]. (b) From [23]. . . . . . . . 8

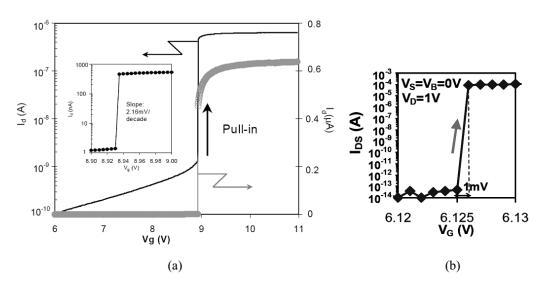

| 1.6 | Measured $I_{DS} - V_{GS}$ characteristics for the MEMS switches shown |    |

|-----|------------------------------------------------------------------------|----|

|     | in Fig. 1.5(a) and (b), respectively, demonstrating extremely small    |    |

|     | subthreshold swings. The swing in this type of device is set by        |    |

|     | the voltage step size, has no fundamental limit, and can approach      |    |

|     | zero. (a) Junction leakage is still present for this relay design      |    |

|     | [17]. (b) Off-state current is much lower for a design in which        |    |

|     | the source and/or drain is physically separated from the MOSFET        |    |

|     | channel [23]                                                           | 8  |

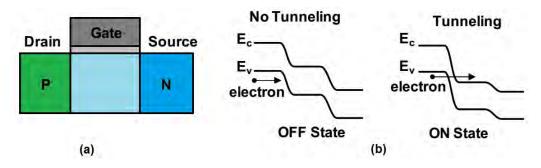

| 1.7 | (a)Schematic diagram of a tunneling field effect transistor and (b)    |    |

|     | its energy band diagram in the off and on states                       | 9  |

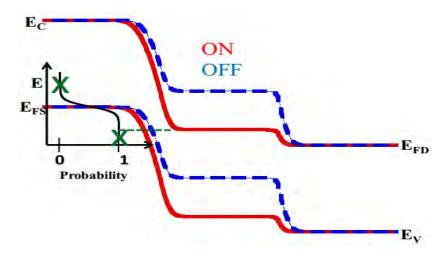

| 1.8 | Energy band diagram along the channel of a representative lateral      |    |

|     | TFET. ON state is shown in solid red and OFF state in dashed           |    |

|     | blue. The Fermi-Dirac distribution function is overlaid on the         |    |

|     | source Fermi level. In the ON state, the upper tail is cut off by      |    |

|     | the band gap and the lower tail suppressed by the large tunnel         |    |

|     | barrier across the channel. (green x's) [25].                          | 10 |

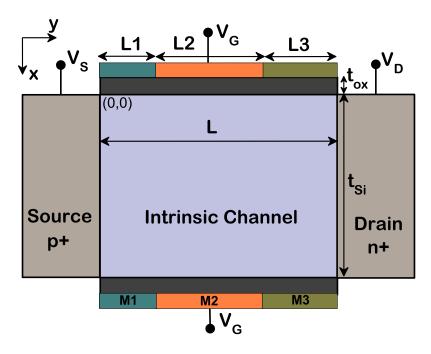

| 2.1 | Schematic diagram of TMDG TFET                                         | 19 |

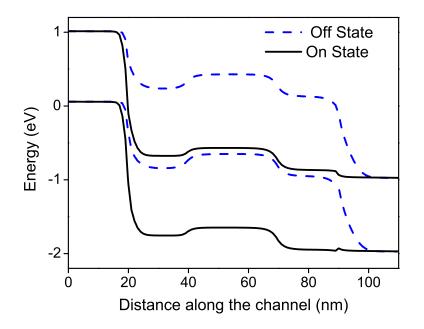

| 2.2 | Energy band diagram of TMDG TFET at OFF-state ( $V_{GS} = 0V$          |    |

|     | and $V_{DS} = 1V$ ) and ON-state ( $V_{GS} = 1V$ and $V_{DS} = 1V$ )   | 21 |

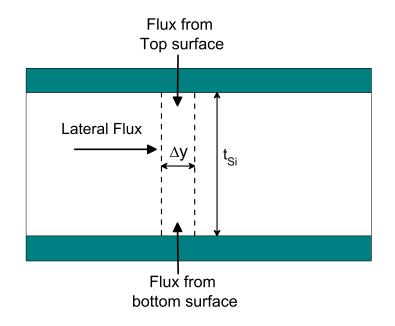

| 3.1 | Gaussian box in the channel region of TMDG TFET                        | 23 |

| 3.2 | Electric potential distribution in TMDG TFET                           | 28 |

| 3.3 | Tunnel path between the valence band of the source and the con-        |    |

|     | duction band of the channel region                                     | 32 |

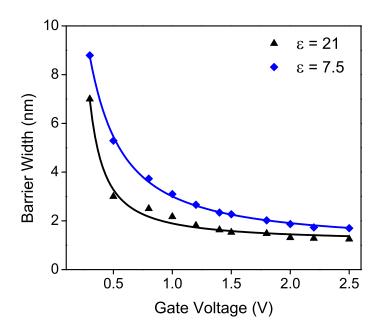

| 3.4 | Variation of energy barrier width with applied gate bias for $\epsilon_{ox}$ = |    |

|-----|--------------------------------------------------------------------------------|----|

|     | 21, 7.5 at $V_{DS} = 1V$                                                       | 35 |

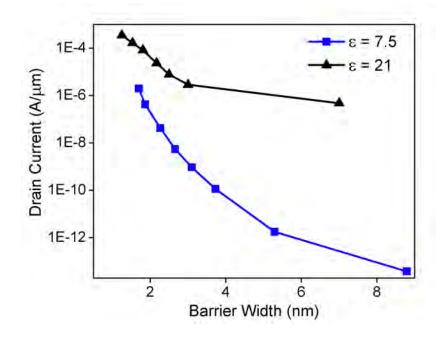

| 3.5 | Drain current vs. energy barrier width, $w_b$ for different values of          |    |

|     | the gate dielectric permittivity at $V_{DS} = 1V.$                             | 36 |

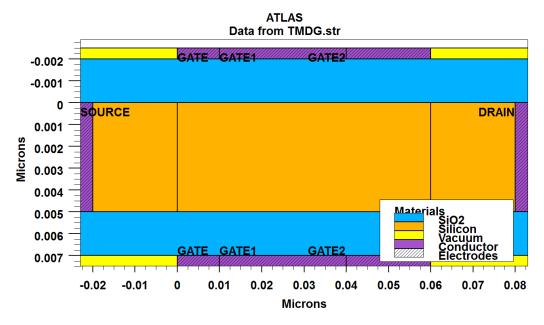

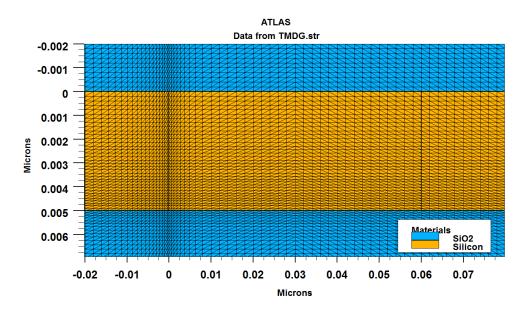

| 4.1 | TMDG TFET structure created using ATLAS device simulator                       | 43 |

| 4.2 | TMDG TFET structure with meshing.                                              | 43 |

| 4.3 | Reproduction of experimental result from [69].                                 | 49 |

| 4.4 | Extraction of $V_{TH}$ using TC method                                         | 50 |

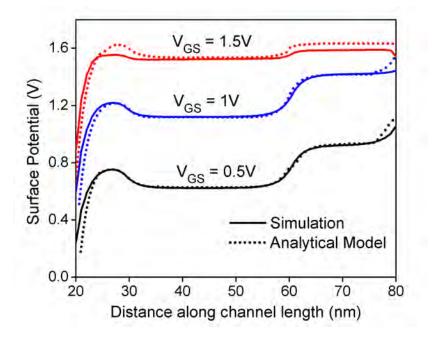

| 5.1 | Surface potential along channel length for $V_{GS} = 0.5$ , 1, and 1.5V        |    |

|     | with $V_{DS} = 1V$ and $\epsilon_{ox} = 21$ . Dotted lines shows the surface   |    |

|     | potentials from analytical model                                               | 54 |

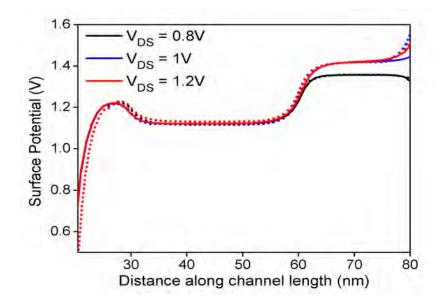

| 5.2 | Surface potential along channel length given by analytical model               |    |

|     | (dotted lines) and TCAD simulations (solid lines) for $V_{DS} = 0.8, 1,$       |    |

|     | and 1.2 <i>V</i> with $V_{GS} = 1V$ and $\epsilon_{ox} = 21$                   | 55 |

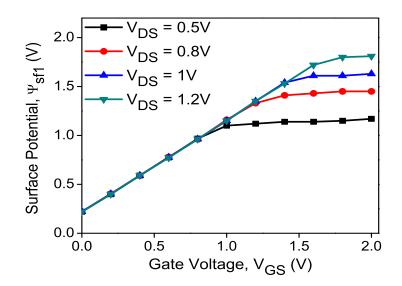

| 5.3 | Variation of Surface potential with $V_{GS}$ for $V_{DS} = 0.5, 0.8, 1$ , and  |    |

|     | 1.2 <i>V</i> and $\epsilon_{ox} = 21$                                          | 55 |

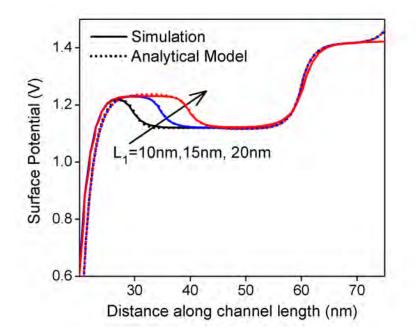

| 5.4 | Surface potential along channel length for $L_1 = 10$ , 15, and $20nm$         |    |

|     | with $V_{GS} = 1V$ , $V_{DS} = 1V$ and $\epsilon_{ox} = 21$                    | 56 |

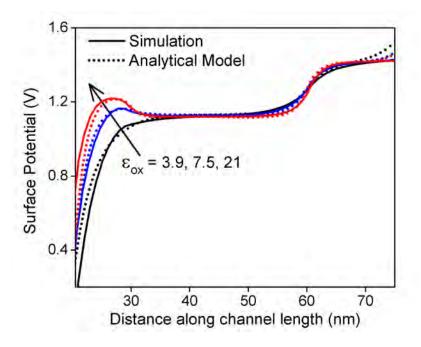

| 5.5 | Surface potential along channel length for $\epsilon_{ox} = 3.9$ , 7.5, and 21 |    |

|     | with $V_{GS} = 1V$ and $V_{DS} = 1V$                                           | 57 |

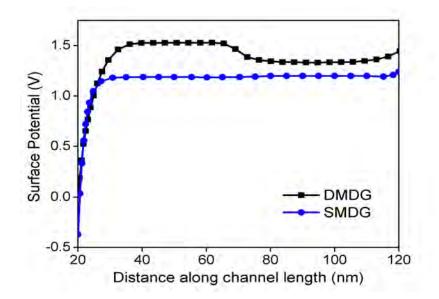

| 5.6 | Surface potential along channel length for DMDG and SMDG                       |    |

|     | TFET structure given by the developed model (symbols) and ana-                 |    |

|     | lytical models from [74] and [75] (solid lines)                                | 58 |

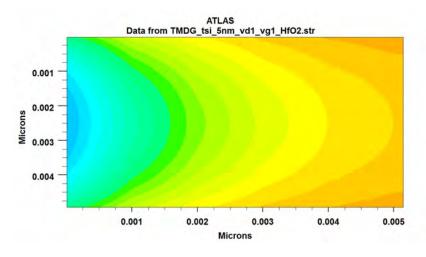

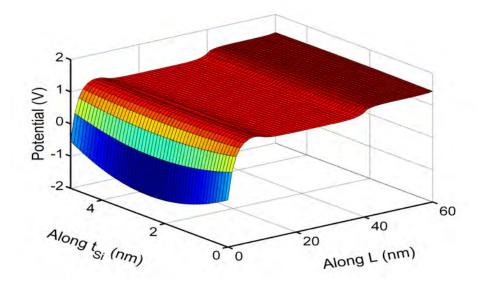

| 5.7                  | 2-D electric potential from developed model for $V_{GS} = 1V$ , $V_{DS} =$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                |

|----------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------|

|                      | $1V$ and $\epsilon_{ox} = 21$ .                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 58             |

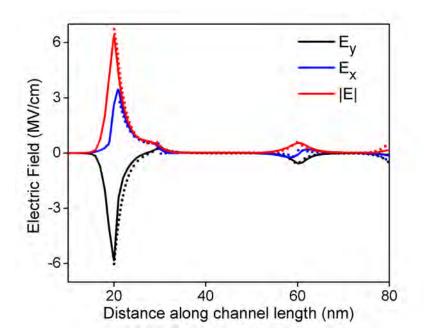

| 5.8                  | Horizontal field $(E_y)$ , vertical field $(E_x)$ and resultant electric field                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                |

|                      | ( E ) along channel length given by the developed model (dotted                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |                |

|                      | lines) and the TCAD simulation (solid lines) with $\epsilon_{ox} = 21$ , $V_{GS} =$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                |

|                      | $1V$ and $V_{DS} = 1V$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 59             |

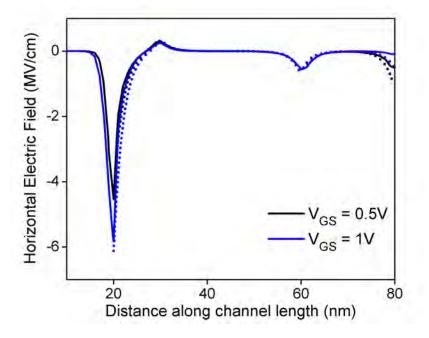

| 5.9                  | Horizontal field $(E_y)$ along channel length from the developed                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                |

|                      | model (dotted lines) and the TCAD simulation (solid lines) for                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                |

|                      | $V_{GS} = 0.5$ and $1V$ with $V_{DS} = 1V$ and $\epsilon_{ox} = 21. \dots \dots$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 60             |

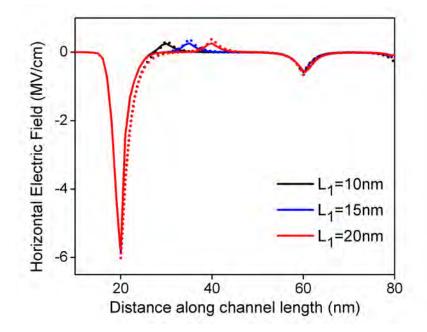

| 5.10                 | Variation of horizontal field $(E_y)$ along channel length from the                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                |

|                      | developed model (dotted lines) and the TCAD simulation (solid                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |                |

|                      | lines) for $L_1 = 10$ , 15, and $20nm$ with $V_{GS} = 1V$ , $V_{DS} = 1V$ and                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |                |

|                      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |                |

|                      | $\epsilon_{ox} = 21$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 61             |

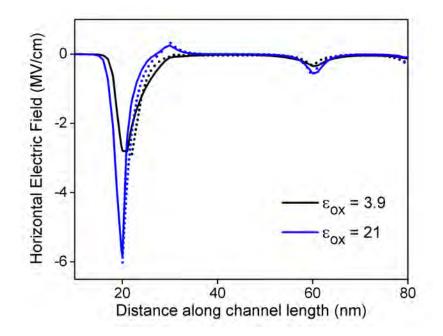

| 5.11                 | $\epsilon_{ox} = 21$<br>Horizontal field ( $E_y$ ) along channel length from the developed                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 61             |

| 5.11                 |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 61             |

| 5.11                 | Horizontal field $(E_y)$ along channel length from the developed model (dotted lines) and the TCAD simulation (solid lines) for                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 61<br>62       |

|                      | Horizontal field $(E_y)$ along channel length from the developed model (dotted lines) and the TCAD simulation (solid lines) for                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |                |

|                      | Horizontal field $(E_y)$ along channel length from the developed<br>model (dotted lines) and the TCAD simulation (solid lines) for<br>$\epsilon_{ox} = 3.9, 7.5, \text{ and } 21 \text{ with } V_{GS} = 1V \text{ and } V_{DS} = 1V. \dots \dots$                                                                                                                                                                                                                                                                                                                                                                                       | 62             |

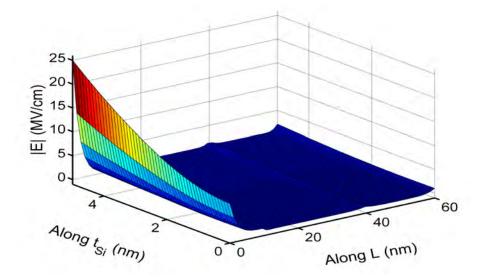

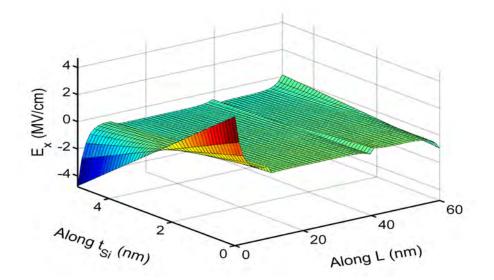

| 5.12                 | Horizontal field $(E_y)$ along channel length from the developed<br>model (dotted lines) and the TCAD simulation (solid lines) for<br>$\epsilon_{ox} = 3.9, 7.5, \text{ and } 21 \text{ with } V_{GS} = 1V \text{ and } V_{DS} = 1V. \dots \dots$<br>2-D average electric field from the derived analytical model for                                                                                                                                                                                                                                                                                                                   | 62             |

| 5.12                 | Horizontal field $(E_y)$ along channel length from the developed<br>model (dotted lines) and the TCAD simulation (solid lines) for<br>$\epsilon_{ox} = 3.9, 7.5, \text{ and } 21 \text{ with } V_{GS} = 1V \text{ and } V_{DS} = 1V. \dots$<br>2-D average electric field from the derived analytical model for<br>$V_{GS} = 1V, V_{DS} = 1V \text{ and } \epsilon_{ox} = 21. \dots$                                                                                                                                                                                                                                                    | 62<br>63       |

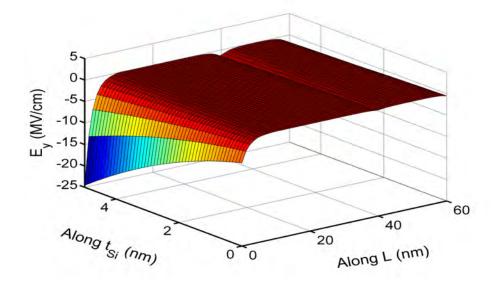

| 5.12<br>5.13         | Horizontal field $(E_y)$ along channel length from the developed<br>model (dotted lines) and the TCAD simulation (solid lines) for<br>$\epsilon_{ox} = 3.9, 7.5, \text{ and } 21 \text{ with } V_{GS} = 1V \text{ and } V_{DS} = 1V. \dots \dots$<br>2-D average electric field from the derived analytical model for<br>$V_{GS} = 1V, V_{DS} = 1V$ and $\epsilon_{ox} = 21. \dots \dots \dots \dots$<br>2-D horizontal field given by the developed model for $V_{GS} = 1V$ ,                                                                                                                                                          | 62<br>63       |

| 5.12<br>5.13         | Horizontal field $(E_y)$ along channel length from the developed<br>model (dotted lines) and the TCAD simulation (solid lines) for<br>$\epsilon_{ox} = 3.9, 7.5, \text{ and } 21 \text{ with } V_{GS} = 1V \text{ and } V_{DS} = 1V. \dots \dots$<br>2-D average electric field from the derived analytical model for<br>$V_{GS} = 1V, V_{DS} = 1V$ and $\epsilon_{ox} = 21. \dots \dots \dots \dots$<br>2-D horizontal field given by the developed model for $V_{GS} = 1V,$<br>$V_{DS} = 1V$ and $\epsilon_{ox} = 21. \dots \dots \dots \dots \dots \dots$                                                                            | 62<br>63       |

| 5.12<br>5.13<br>5.14 | Horizontal field $(E_y)$ along channel length from the developed<br>model (dotted lines) and the TCAD simulation (solid lines) for<br>$\epsilon_{ox} = 3.9, 7.5, \text{ and } 21 \text{ with } V_{GS} = 1V \text{ and } V_{DS} = 1V. \dots \dots$<br>2-D average electric field from the derived analytical model for<br>$V_{GS} = 1V, V_{DS} = 1V$ and $\epsilon_{ox} = 21. \dots \dots \dots \dots$<br>2-D horizontal field given by the developed model for $V_{GS} = 1V,$<br>$V_{DS} = 1V$ and $\epsilon_{ox} = 21. \dots \dots \dots \dots \dots \dots$<br>2-D vertical field from the developed model for $V_{GS} = 1V, V_{DS} =$ | 62<br>63<br>63 |

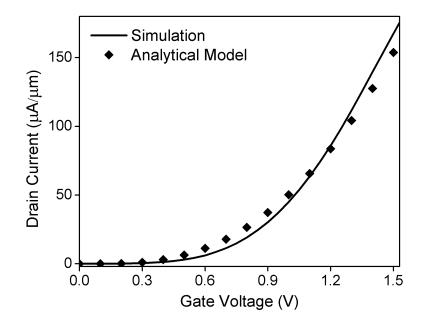

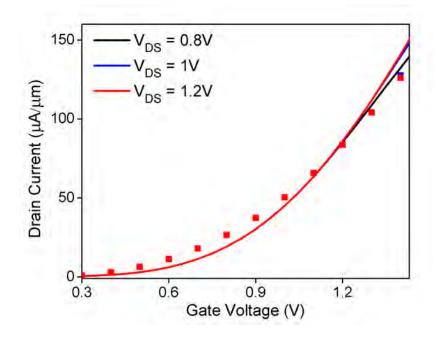

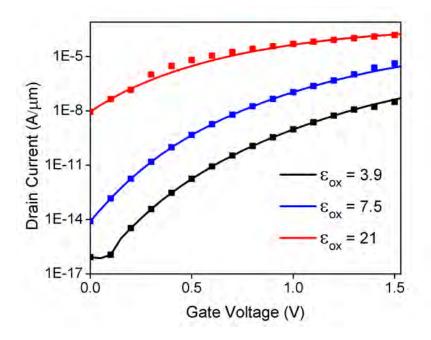

| 5.16 | $I_D$ vs $V_{GS}$ curve proposed by the analytical model (symbols) and                                                                                                                                                                 |    |

|------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

|      | TCAD simulation (solid lines) for $V_{DS} = 0.8$ , 1, and 1.2V with                                                                                                                                                                    |    |

|      | $\epsilon_{ox} = 21$                                                                                                                                                                                                                   | 66 |

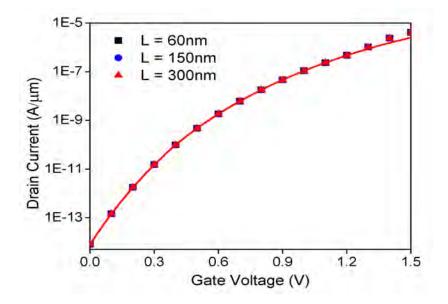

| 5.17 | Transfer characteristics (log scale) for varying channel length given                                                                                                                                                                  |    |

|      | by the analytical model (symbols) and TCAD simulation (solid                                                                                                                                                                           |    |

|      | lines) with $V_{DS} = 1V$ and $\epsilon_{ox} = 7.5$ .                                                                                                                                                                                  | 67 |

| 5.18 | Variation of $I_D$ with $V_{GS}$ given by the analytical model (symbols)                                                                                                                                                               |    |

|      | and TCAD simulation (solid lines) for $\epsilon_{ox} = 3.9$ , 7.5, and 21 with                                                                                                                                                         |    |

|      | $V_{DS} = 1V.\ldots\ldots\ldots\ldots\ldots\ldots\ldots\ldots\ldots\ldots\ldots\ldots\ldots\ldots\ldots\ldots\ldots\ldots\ldots\ldots\ldots\ldots\ldots\ldots\ldots\ldots\ldots\ldots\ldots\ldots\ldots\ldots\ldots\ldots\ldots\ldots$ | 67 |

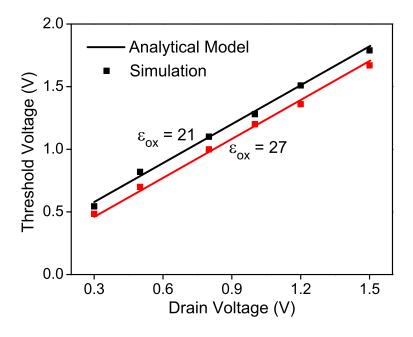

| 5.19 | $V_{TH}$ vs $V_{DS}$ for different $\epsilon_{ox}$ .                                                                                                                                                                                   | 68 |

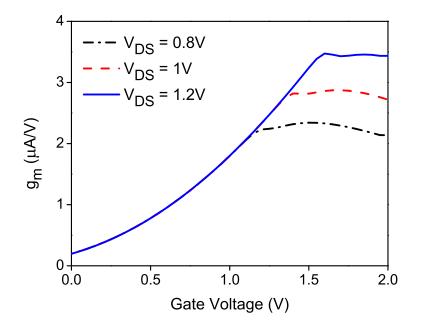

| 5.20 | Modulation of transconductance with gate voltage                                                                                                                                                                                       | 69 |

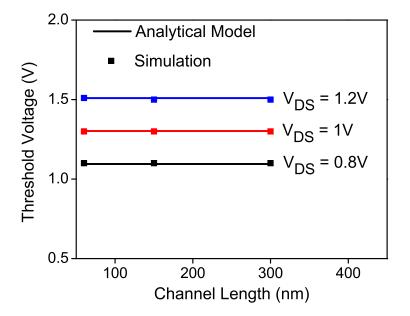

| 5.21 | Variation of $V_{TH}$ with channel length                                                                                                                                                                                              | 69 |

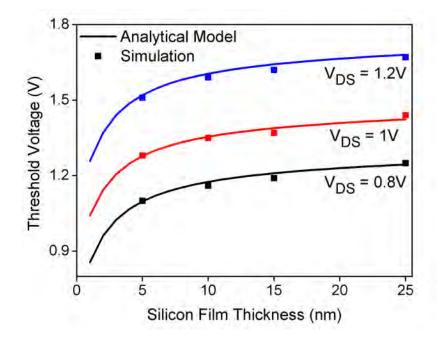

| 5.22 | Dependence of $V_{TH}$ on silicon film thickness at $V_{DS} = 1V$ and                                                                                                                                                                  |    |

|      | $\epsilon_{ox} = 21$                                                                                                                                                                                                                   | 70 |

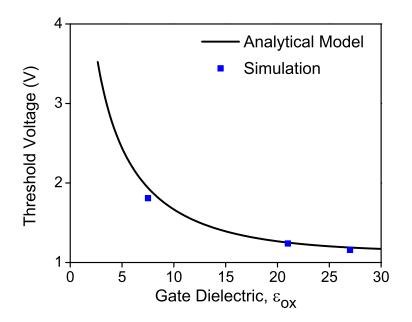

| 5.23 | Variation of $V_{TH}$ with changing gate dielectric for $V_{DS} = 1V$                                                                                                                                                                  | 71 |

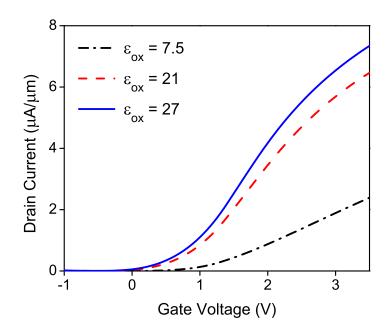

| 5.24 | Transfer characteristics curve for different gate dielectric                                                                                                                                                                           | 71 |

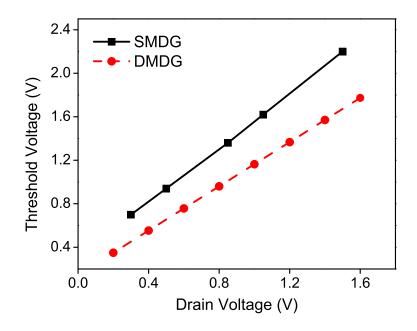

| 5.25 | $V_{TH}$ curve for SMDG and DMDG structures. Symbols represent                                                                                                                                                                         |    |

|      | analytical model of [75] for SMDG and [88] for DMDG structure.                                                                                                                                                                         | 72 |

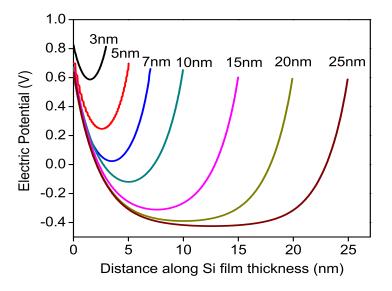

| 5.26 | Electric potential along x direction near source-channel tunneling                                                                                                                                                                     |    |

|      | junction                                                                                                                                                                                                                               | 73 |

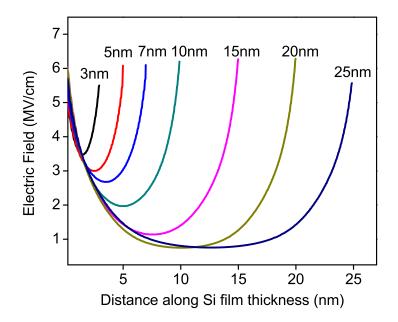

| 5.27 | Electric field along x direction near band-to-band tunneling region                                                                                                                                                                    |    |

|      | of source-channel interface                                                                                                                                                                                                            | 74 |

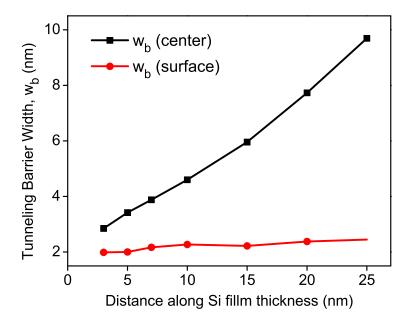

| 5.28 | Energy barrier width, $w_b$ at the surface and at the center ( $x =$                                                                                                                                                                   |    |

|      | $t_{Si}/2$ ) of Si film for different $t_{Si}$                                                                                                                                                                                         | 74 |

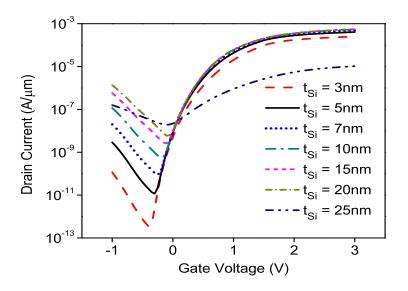

| 5.29 | Effect of $t_{Si}$ on Transfer characteristics.                                                                                                                                                                                        | 75 |

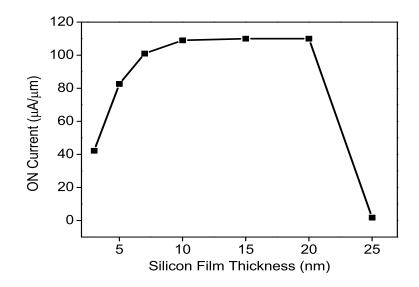

| 5.30 | Modulation of $I_{ON}$ by Si film thickness                 | 76 |

|------|-------------------------------------------------------------|----|

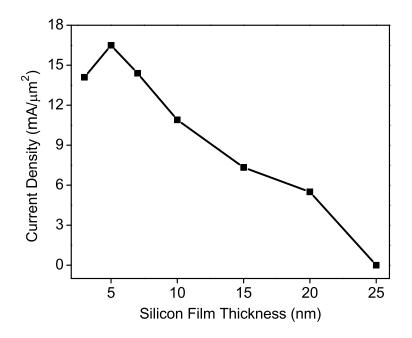

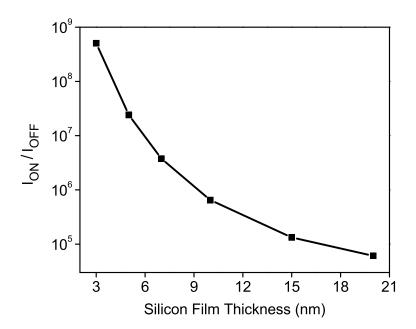

| 5.31 | Variation of average current density with Si film thickness | 77 |

| 5.32 | $I_{ON}/I_{OFF}$ for different Si film thickness.           | 77 |

# **Chapter 1**

# Introduction

Small swing devices are being researched intensively for the power crisis currently faced by conventional metal-oxide-semiconductor field-effect transistors (MOS-FETs), due to their ever-increasing static power consumption. The reasons behind this crisis are explained, and then some currently used solutions are presented.

### **1.1 CMOS Solid State Switching Devices**

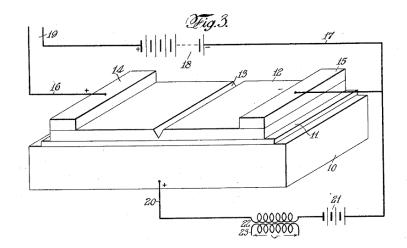

In 1928, a patent was filed for a "device for controlling current" shown in Fig. 1.1 [1], a variant of a device that is now known as the MOSFET. Because of the difficulty to get a good oxide-semiconductor interface, it took until 1959 before the first MOSFET was fabricated [2]. But now, after many years of research and development a single chip now contains up to 6.8 billion of these devices. Being almost 90 years old, the semiconductor industry and its products are now a landmark of human civilization.

At the heart of the success story behind the MOSFET is the concept of scal-

Fig. 1.1: Illustration from J.E. Lilienfeld's patent [1].

ing. For the past 50 years, the electronics industry has kept pace with Moore's Law [3], roughly doubling the number of transistors on a chip every two years. To maintain this trend, the size of individual transistors, known as MOSFETs, fabricated in complementary metal oxide semiconductor (CMOS) technology were reduced for each technology generation or node. The guidelines for reducing the dimensions of the transistor were originally developed by Dennard in 1974 [4] and were roughly followed for nearly three decades. In this "conventional scaling era", the reduction in size of each transistor increased speed while maintaining a constant power density. From a manufacturing perspective, adding more transistors for a given chip area lowered the cost per transistor. This threefold benefit to scaling CMOS revolutionized electronics and enabled technological advancement at a rapid pace.

Around the early-mid 2000's, conventional scaling ended and the industry moved to a power constrained scaling era [5]. In this era, the supply voltage  $(V_{DD})$  of devices has not scaled with the other device parameters and dimensions.

This is because the threshold voltage  $(V_{TH})$  must scale with the supply voltage in order to maintain a sufficient ON/OFF ratio. However, scaling of the threshold voltage results in an exponential increase in OFF state leakage. This is illustrated in Fig. 1.2 [6]. Two drain current vs. gate-source voltage  $(I_D - V_{GS})$  transfer curves are shown for a MOSFET device at a high supply voltage (blue) and low supply voltage (red). In order to maintain the same ON current  $(I_{ON})$ , the threshold voltage must decrease with the supply voltage. This reduction of threshold voltage exponentially increases the OFF current. This increase in OFF current is guaranteed because of the constant subthreshold swing (SS) of the MOSFET.

Fig. 1.2: Two MOSFET  $I_D - V_{GS}$  curves operated at a high supply voltage (blue) and low supply voltage (red). To maintain the same  $I_{ON}$ , the threshold voltage of the red curve must decrease. This results in exponentially increased  $I_{OFF}$  because of the constant SS [6].

Subthreshold swing is a measure of the inverse slope of the  $I_D - V_{GS}$  curve

Fig. 1.3: Energy band diagram along the channel of a MOSFET with three different gate voltages applied. The Fermi-Dirac distribution function is sketched with respect to the source Fermi level to illustrate the electron occupation as a function of energy in the source.

below threshold, defined by

$$SS = \left(\frac{d\ln I_D}{dV_{GS}}\right)^{-1} \tag{1.1}$$

Due to the thermionic nature of the drain current in a MOSFET, there is a theoretical minimum value for a MOSFET of (kT/q)ln(10) = 60mV/decade, where k is Boltzmanns constant, T is temperature in Kelvin, and q is the electron charge. Conceptually, this can be understood with the aid of the energy band diagram along the channel of a MOSFET as shown in Fig. 1.3. Here, the Fermi level in the source is shown schematically with the Fermi-Dirac distribution function superimposed, illustrating the probability of finding an electron in the source at a given energy. Since the function asymptotically approaches zero, there are always some electrons in the source with energy greater than the channel barrier. These high energy or hot electrons define the drain current in the OFF state and the distribution of electrons above the barrier varies exponentially as the surface potential is lowered. It is for this reason that SS is limited by kT and has a minimum of 60 mV/dec.

As a consequence of constant voltage scaling, power density increases if the circuit speed increases or if the transistor density increases. This is troubling particularly in today's world of mobile electronics where battery life and cooling constraints set limits on allowable power dissipation. These limitations have led to the industry's adoption of multi-core processors, which can increase the number of MOPS/mW (million operations per second per milliwatt). In order to continue scaling of CMOS devices, new innovations and device designs will be required to overcome the challenges reviewed above.

### **1.2 Proposed Alternatives to CMOS-based Logic**

To achieve good ON/OFF performance at a lower supply voltage, it is necessary to find a way to scale down the subthreshold swing. That is, overcome the 60mV/dec limit in SS of MOSFETs. In order to do this, a new current mechanism that does not involve carriers traveling over a potential barrier needs to be used. Fig. 1.4 qualitatively shows the benefit of a low SS for an alternative device. A steeply switching device allows for a lower threshold voltage (hence a lower power supply voltage,  $V_{DD}$ ) and the possibility of a lower  $I_{OFF}$  which decreases the passive power consumption.

There have been some revolutionary innovations already adapted into CMOS

Fig. 1.4: A steeply switching device proves a compelling goal for a MOSFET replacement. The blue curve represents a traditional MOSFET I - V transfer characteristic. The solid green curve comparatively highlights the main benefit of a steeper transfer characteristic: a reduction in the power supply voltage,  $V_{DD}$ . Presumably, a steeper SS characteristic can be threshold-voltage shifted (as depicted in the dashed green curve) [8].

devices in the most recent technology nodes. Mechanically-strained channels were introduced to increase mobility and enhance drive currents [7] around the 90*nm* node. At the 45*nm* node, high-*k* gate dielectrics and metal gates were introduced to improve electrostatics and suppress gate oxide leakage currents as the equivalent gate-oxide thickness decreased [9]. Most recently, Intel introduced Broadwell transistors at the 14*nm* node to improve energy efficiency [10]. Alternative transistor designs such as the tunneling based field-effect transistors [11, 12], impact ionization MOS [13, 14], ferroelectric FETs [15, 16] and electromechanical devices [17–23] have been proposed and demonstrated to achieve SS < 60mV/dec. Among these, the tunneling field effect transistor (TFET) and

electro-mechanical devices show the most promise for low power electronics applications.

#### **1.2.1** Electromechanical Devices

The abrupt "pull-in" effect in electromechanical systems has been harnessed to realize new switching device designs with higher  $I_{ON}/I_{OFF}$  ratio for a given gate voltage swing. These devices utilize a movable beam for switching, and they can roughly be divided into two categories: the nano-electro-mechanical system (NEMS) field effect transistor and the micro-electro-mechanical system (MEMS) relay. While some MEMS switches seem to be just two-terminal devices, which might have extremely small values of swing [24] but are limited in terms of applications in circuits, others are three-terminal devices that could potentially replace conventional MOSFETs. There are many possible designs for this type of switch. One possibility is to fabricate a flexible cantilever beam connected electrically to the source terminal, which is activated by a gate electrode underneath, and pulled down to touch the drain electrode in the on-state [21]. Another possibility is to use a more typical MOSFET layout, with source, channel, and drain, as in the two devices shown in Fig. 1.5. The Fig. 1.5(a) has an air gap between the gate dielectric and the gate contact and the gate itself moves up (off-state) and down (on-state) [17]. Fig. 1.5(b) has source and drain regions on the substrate, and a moving gate/channel which can be pulled down into contact with the source and drain in the on-state [23]. Fig. 1.6 shows the transfer characteristics of the device shown in Fig. 1.5.

MEMS and NEMS switches are interesting due to their potentially high ON-

Fig. 1.5: Two possible designs for MOSFET-like MEMS relays, with a source, drain, and gate. (a) From [17]. (b) From [23].

Fig. 1.6: Measured  $I_{DS} - V_{GS}$  characteristics for the MEMS switches shown in Fig. 1.5(a) and (b), respectively, demonstrating extremely small subthreshold swings. The swing in this type of device is set by the voltage step size, has no fundamental limit, and can approach zero. (a) Junction leakage is still present for this relay design [17]. (b) Off-state current is much lower for a design in which the source and/or drain is physically separated from the MOSFET channel [23].

currents, very low OFF-currents, and small subthreshold swings. Their disadvantages include lower speed [21] and reliability problems due to their mechanical nature, such as structural damage where the two pieces need to touch each other and then come back apart thousands or millions of times [24].

#### **1.2.2** Tunneling Field Effect Transistor (TFET)

Among all the alternative transistor designs, the tunnel field effect transistor (TFET) is the most promising due to its relative simplicity and resemblance to the conventional MOSFET. The TFET utilizes band-to-band tunneling (BTBT) current to achieve a more abrupt on-to-off transition than what is achievable through thermionic emission. Fig. 1.7 shows the energy band diagram of the TFET in on and off states.

Fig. 1.7: (a)Schematic diagram of a tunneling field effect transistor and (b) its energy band diagram in the off and on states.

In a TFET, the predominant current flow is by tunneling through a barrier rather than by thermionic emission over a barrier as in a MOSFET. Fig. 1.8 shows the TFET energy band diagram, with the Fermi-distribution function shown schematically, analogous to Fig. 1.3. In the source, the valence band edge acts as a filter, i.e. there are no electrons in the high energy tail of the Fermi-Dirac

Fig. 1.8: Energy band diagram along the channel of a representative lateral TFET. ON state is shown in solid red and OFF state in dashed blue. The Fermi-Dirac distribution function is overlaid on the source Fermi level. In the ON state, the upper tail is cut off by the band gap and the lower tail suppressed by the large tunnel barrier across the channel. (green x's) [25].

distribution function because there is no density of states in the band gap. Similarly, the conduction band edge in the channel suppresses electrons in the source below this energy from tunneling. This energy filtering effect of the band edges results in "cold" carriers contributing to the current and hence, SS in a TFET is not expected to be limited by T and it can potentially achieve lower SS values, which has already been experimentally demonstrated [11]. However, a TFET achieves SS< 60mV/dec only at low current levels and that SS increases as  $I_{DS}$ increases [26–28]. Consequently, at high  $V_{DD}$  (1V) values, a silicon TFET has a significantly lower on-state current  $I_{ON}$  (1 $\mu A/\mu m$  at 1V) than a silicon MOSFET (1 $mA/\mu m$  at 1V). This remains a principal challenge for TFET designers. Another major shortcomings of this device is ambipolar conduction which makes its application difficult as a switching device.

### **1.3** Motivation and Objectives

Analytical models are powerful tools which can provide fast results, together with further insight on the working principles of the device; it is useful to design, simulate and fabricate a new device. TFET is a promising device which has low OFFstate leakage currents, and a better immunity to SCE due to a built-in tunnel barrier, and can provide a steep SS. Therefore, modeling potential of triple material double gate (TMDG) TFET is of great interest. Only a few analytical models of electric potential and drain current have been developed for this structure [29–31]. In [29], potential model is derived utilizing variable separation technique by solving 2-D Poisssons equation. In [30], 2-D Poisssons equation is solved employing Young's approximation for the formulation of potential model. An equation of drain current is also developed in this literature. Similar approach is used in [31] to find equation of potential for surrounding gate triple material TFET structure. So far no analytical model is developed for TMDG TFET structure based on the device physics. Although models are derived for surface potential and drain current, no analytical model is reported for the gate threshold voltage of TMDG TFET structure.

The objectives of this work are:

- 1. To develop physics based analytical models of electric potential, electric field, drain current, and gate threshold voltage for TMDG TFETs.

- To develop 2D numerical simulation model of TMDG TFET using SIL-VACO ATLAS.

- 3. To verify the proposed analytical model with SILVACO ATLAS simulation

results.

To study and investigate the effects of model parameter variation on the performance of TMDG TFET and verify the results with SILVACO ATLAS simulation results.

The proposed analytical models of different useful device parameters of TMDG TFET can be used to investigate the circuit performance containing this device.

### **1.4 Thesis Organization**

This dissertation consists of six chapters. The first chapter focuses on the limitations faced by the popular MOSFET switching devices due to aggressive scaling. Most promising alternatives for MOSFET devices and their shortcomings are mentioned. Finally, the motivation and objectives of this work is presented in this chapter. The second chapter includes the state-of-art of TFETs which is then followed by the TMDG TFET structure considered in this work and the operating principle of this structure.

The third chapter discloses surface potential and electric field model formulation procedures of TMDG TFET structure by exploiting Gauss's law. The surface potential model is extended to a 2-D potential model by considering parabolic approximation. The expression of band-to-band tunneling current is developed by utilizing tunneling generation rate and the derived electric field model. An analytical model of gate threshold of TMDG TFET is formulated from the surface potential equation based on its physical definition for TFETs. The developed models are then generalized for single and multigate TFET structures. The fourth chapter gives a brief introduction to the Silvaco ATLAS simulator used for developing the numerical model of TMDG TFET considered in this study. The method of extracting the tunneling parameters of the device from the experimental data is described later. Threshold voltage extraction from the simulation results and necessary de-noising procedures are also included in this chapter.

The fifth chapter measures the accuracy of the developed models by comparing the results of analytical models with the TCAD simulation results. The effects of varying bias conditions and device parameters on surface potential, electric field, drain current and gate threshold voltage are analyzed. Based on these analysis, the validity conditions of the proposed models are extracted and a solution to extend the validity range of the models is suggested. Finally, the effect of Si film thickness on electrical characteristics of the device is studied, the physics governing it is detailed and an optimum value of Si film thickness for optimized device performance is suggested for future fabrication of TMDG TFET structures.

The last chapter marks the end of the dissertation with a summary of the work done. It also mentions the scopes for further improvement of the work and provides a suggestion of the possible areas which can be explored in future.

# **Chapter 2**

# TMDG TFET

## 2.1 Introduction

As technology and scientific insight move forward, new possibilities open themselves to mankind. In this section, the working principle of an electronic switch exploiting the quantum mechanical tunneling process is investigated. The electronic device under investigation in this work is called the triple material double gate (TMDG) tunnel field-effect transistor (TFET) and could provide a big improvement over existing MOSFET technology.

### 2.2 History and State-of-the-art of the TFET

Quinn *et al.* at Brown University [32] were the first to propose the gated p-i-n structure of a Tunnel FET in 1978, and suggested the usefulness of this device for spectroscopy. Banerjee *et al.* at Texas Instruments [33] studied the behavior of a three-terminal silicon tunnel device using a  $p^-$ -region instead of an i-region under

the gate. Takeda et al. at Hitachi [34] created a band-to-band tunneling MOS device on silicon that they called the  $B^2T$ -MOSFET, and showed the lack of  $V_{TH}$  roll-off when scaling, and the temperature dependence of the device characteristics. Baba at NEC [35] fabricated Tunnel FETs which he called Surface Tunnel Transistors, using MBE to create mesa structures in III-V materials. In 1995, Reddick and Amaratunga at Cambridge [36] published measured characteristics of silicon Surface Tunnel Transistors. They were motivated by the desire for devices that would be faster than conventional MOSFETs, as tunneling devices are, and that could be scaled down more easily without running into problems such as punchthrough. They are sometimes erroneously given credit for being the first to make silicon Tunnel FETs. In 1997, Koga and Toriumi at Toshiba [37] proposed a post-CMOS three-terminal silicon tunneling device with the same structure as a Tunnel FET, though the experimental results which were presented showed a device that was forward-biased.

In 2000, Hansch *et al.* at the University of the German Federal Armed Forces in Munich [38] showed experimental results from a reverse-biased vertical silicon tunneling transistor made with MBE, with a highly-doped boron delta-layer to create an abrupt tunnel junction, and noted the saturation behavior in the  $I_D - V_G$ characteristics. Aydin and Zaslavsky at Brown Univ., along with their collaborators in New York and France [26] fabricated Lateral Interband Tunneling Transistors on SOI in 2004. These devices used a different Tunnel FET structure without an intrinsic region, instead placing the gate over a p-n junction, claiming that this would reduce gate capacitance and therefore increase speed. The authors also claim that there should be no current saturation for these devices. Similar devices on bulk silicon had already been investigated by Grove and Fitzgerald in 1965 [39].

In 2004, band-to-band tunneling was demonstrated in carbon nanotube (CNT) FETs by Appenzeller *et al* [40]. In order to create the energy bands necessary for tunneling, a back gate and a top gate were used. The researchers claimed that the one-dimensionality of the CNTs led to extremely different band bending conditions than those in 3-D semiconductors. A subthreshold swing smaller than the 60mV/dec limit of conventional MOSFETs was reported for the first time, which was a momentous occasion, even if the low swing value was only between a couple of points at very low current values. A year later, Appenzeller *et al.* [41] published a comparison of several CNT transistors, and concluded that the Tunnel FET, now with only one gate, was the superior device and showed conventional looking  $I_{DS} - V_{DS}$  output characteristics while still achieving a subthreshold swing of less than 60mV/dec.

Bhuwalka *et al.* at the University of the German Federal Armed Forces in Munich [12] published the first of many articles about their vertical Tunnel FET on silicon with a SiGe delta layer, grown by MBE in 2004. The SiGe replaced the silicon delta layer already used by Hansch, and in theory, the smaller bandgap should have reduced the tunnel barrier width and increased tunneling current in the on-state as well as lowering the subthreshold swing. In 2006, the same group proposed a lateral Tunnel FET on SiGe on insulator [42], and showed through simulation that on-current would increase with the percentage of Ge in the SiGe. No experimental results have been published to date by this group for these devices. In 2006, Zhang *et al.* at Notre Dame [43] remarked once again what others before them had noticed that theoretically, it is indeed possible for Tunnel FETs to have a subthreshold swing lower than 60mV/dec. The structure they studied was

a gated p-n diode, but the general equations they put forth, and the band-to-band tunneling behavior, would be the same as for a gated p-i-n structure.

In 2007, Verhulst *et al.* at IMEC showed by simulation that shortening Tunnel FET gate length, so that the gate covers the source-side junction where tunneling takes place, but does not cover the majority of the intrinsic region, has the benefits of decreasing off-current (tunneling through the drain-side junction) and reducing speed, with a small or no reduction in the on-current, depending on the device design [44]. In the same year, Toh at the National University of Singapore published a study of double-gate Tunnel FET silicon body thickness optimization, in which he showed an optimal device thickness for maximum on-current [45]. Nagavarapu *et al.* at UCLA suggested a pnpn device design in 2008, in which a narrow region of the opposite doping is introduced into the Tunnel FET source just under the gate edge. This narrow region acts as a source of electrons, and increases the band bending and the electric field at the tunnel junction, thus increasing on-current [46].

2009 had been a busy year for the Tunnel FETs. Schlosser *et al.* at the University of the German Federal Armed Forces in Munich studied the simulated advantages of putting an extremely high-k dielectric on a Tunnel FET, and the benefits of the fringing fields when the dielectric is only over the intrinsic region [47]. Vadizadeh *et al.* at the University of Tehran presented a simulation study of Tunnel FETs in which a high-k dielectric covered the tunnel junction, and the rest of the intrinsic region was covered by a low-k dielectric [48]. This technique led to little improvement in device characteristics, however; most of the shown improvement actually came from a shift in the gate work function which shifted their I-V curves along the voltage axis. Patel *et al.* at UC Berkeley simulated an

interesting device whose band-to-band tunneling takes place perpendicularly to the gate dielectric surface, and showed that it would have a very small subthreshold swing and a high on-current [49]. Their device has an ultra-shallow n+ pocket at the surface of the p+ drain (for an n-type device), and the gate overlaps this pocket. When gate voltage is applied, carriers tunnel upward from the p+ source into the n+ pocket, and then drift to the drain.

There were also some fabricated Tunnel FET results in 2009. Sandow *et al.* from Forschungszentrum Jülich published experimental data for p-type Tunnel FETs on SOI, showing the effects of varying source and drain doping levels, gate dielectric thickness, and device length [50]. Kazazis *et al.*, with his colleages at Brown University and in France, fabricated Tunnel FETs on thin GeOI that showed very high leakage, with  $I_{ON}/I_{OFF} < 100$  [51]. Moselund *et al.* at IBM's Zurich Research Laboratory fabricated Tunnel FETs on silicon nanowires with a wrap-around gate, using two different gate dielectrics:  $SiO_2$  and  $HfO_2$  [52]. The nanowires were grown vertically and doped *in-situ*, and then deposited on a prepatterned substrate where the gate dielectric was deposited and the drain, source, and gate contacts were made. Improvements in subthreshold swing and on-current were seen with the use of a high-*k* dielectric.

In order to enhance the ON current, various design improvements in terms of band gap engineering, hetero junction TFETs strained silicon, novel architectures like P+N+I-N, gate all around structure have been proposed [53–58]. Effect of gate material on energy band profile and overall performance of TFET has been studied in [59, 60]. In 2011, Saurabh *et al.* introduced the idea of dual material double gate TFETs and showed that it is possible to achieve better ON current, smaller leakage current and improved SS with this structure [61]. Unfortunately,

the ambipolar effect cannot be completely inhibited using this configuration. In the same year, Liang *et al.* proposed a novel triple material gate (TMG) TFET structure which shows a higher on current, a reduced SS, a suppressed ambipolar conduction and better switching characteristics [62]. In 2015, Saraswathi *et al.* showed that a gate-all-around TMG TFET structure shows better immunity to short channel effects and hot carrier effects [31].

### 2.3 Device Structure

Fig. 2.1: Schematic diagram of TMDG TFET.

The schematic of TMDG TFET structure considered in this work is shown in Fig. 2.1. Source is highly p-type doped with doping concentration of  $N_{source}$  and drain region is n-type doped with doping concentration of  $N_{drain}$ . The channel is

lightly n-type doped with doping concentration of  $N_{Ch}$ . Three metals M1, M2, and M3 with different workfunctions  $\phi_{m1}$ ,  $\phi_{m2}$ , and  $\phi_{m3}$  respectively form the gate. To improve the ON-current to OFF-current ratio,  $\phi_{m2}$  is kept higher compared to  $\phi_{m1}$  and  $\phi_{m3}$  [30]. The total gate length of the device is  $L = L_1 + L_2 + L_3$  where  $L_1$ ,  $L_2$ , and  $L_3$  are length of metal gate M1, M2, and M3 respectively. The thickness of oxide film is  $t_{ox}$  and silicon film thickness is  $t_{si}$ .

### 2.4 Operating Principle of TFETs

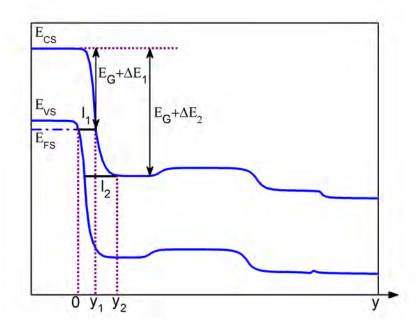

Current conduction mechanism in Tunnel FET devices is solely based on tunneling process. The gate near the source region is responsible for tunneling mechanism between source/body junctions. Conduction band and valence bands of the TMDG TFET during on-state and off-state are shown in Fig. 2.2. The electric field in the source-channel junction increases due to increase in band bending in that region because of less value of  $\phi_{m1}$ . A higher value of  $\phi_{m2}$  creates a barrier in the channel and a lower value of  $\phi_{m3}$  creates a bandpass filter structure [71]. The height of this barrier is tunable by the gate voltage. During OFF-state  $(V_{GS} = 0V \text{ and } V_{DS} = 1V)$ , no overlap occurs between the occupied band of the source and the unoccupied band of the channel, so the tunneling process will not take place and also the barrier in the channel region blocks the reverse tunneling of the carriers; therefore, the OFF-current is very low. When gate voltage is large enough, the conduction band of channel region goes below the valence band of source region and a sufficiently high lateral electric field is created at the sourcechannel junction. In the ON-state ( $V_{GS} = 1V$  and  $V_{DS} = 1V$ ), the barrier width is small enough to allow tunneling and the electric field forces the electrons to tun-

Fig. 2.2: Energy band diagram of TMDG TFET at OFF-state ( $V_{GS} = 0V$  and  $V_{DS} = 1V$ ) and ON-state ( $V_{GS} = 1V$  and  $V_{DS} = 1V$ ).

nel from valence band of source region to the conduction band of channel region. The tunneled electrons then move towards the drain end through drift diffusion mechanism.

# **Chapter 3**

# **Analytical Model of TMDG TFET**

## 3.1 Introduction

Analytical models are important to predict the behavior of devices. The formulation of analytical models of fundamental TMDG TFET characteristics are exihibited in this chapter. The derivation of 1-D surface potential is carried out by exploiting Gauss's law in the lightly doped channel region. The 1-D model is then extended to 2-D potential model by using parabolic approximation which is followed by the development of electric field model. The expression of electric field is used to calculate the band-to-band tunneling current by extracting tunneling generation rate. Finally, the physical definition of gate threshold voltage of TFETs is addressed and an analytical model is developed based on that definition.

# **3.2 Electric Potential Distribution**

## **3.2.1** Surface Potential

Surface potential is defined as the electrostatic potential energy of surface confined charges. To find the surface potential, Gauss's law can be applied to a Gaussian box of height  $t_{Si}$  and width  $\Delta y$  in the lightly doped body region as shown in Fig. 3.1. Neglecting mobile charges and source-channel, drain-channel depletion regions, the following equation can be derived [72]:

$$\frac{\epsilon_{si}t_{si}}{\eta}\frac{\partial E_{sf(i)}(y)}{\partial y} + \epsilon_{ox}\frac{V'_{GS(i)} - \psi_{sf(i)}(y)}{t_{ox}} + \epsilon_{ox}\frac{V'_{GS(i)} - \psi_{sb(i)}(y)}{t_{ox}} = qN_{Ch}t_{si} \quad (3.1)$$

where,  $E_{sf(i)}(y)$  is electric field at top oxide-semiconductor interface and i = 1, 2,

Fig. 3.1: Gaussian box in the channel region of TMDG TFET.

and 3 delimit three channel region under M1, M2, and M3 respectively.  $\psi_{sf(i)}(y)$ and  $\psi_{sb(i)}(y)$  are potential at top and bottom oxide-semiconductor interface respectively.  $\eta$  is the channel spreading parameter which is weakly dependent on channel thickness and doping. The value of  $\eta$  is constant varying between 1 and 1.3 [73] and can be extracted from simulation or experiment. In this work,  $\eta = 1$ is used.  $V'_{GS(i)}$  is calculated as

$$V_{GS(i)}' = V_{GS(i)} - V_{FB(i)}$$

$V_{FB(i)}$  is the flatband voltage which is a function of metal and semiconductor workfunction:

$$V_{FB(i)} = \phi_{m(i)} - \phi_S$$

where,  $\phi_{m(i)}$  is metal workfunction and  $\phi_S$  is semiconductor workfunction.  $\phi_S$  can be expressed as

$$\phi_S = \chi_{si} + \frac{E_G}{2}$$

Here,  $\chi_{si}$  is electron affinity and  $E_G$  is semeconductor bandgap.

The right-hand side of Eq. (3.1) represents the net charge in the Gaussian box. The electric flux entering the Gaussian box in lateral direction is represented by the first term on the left-hand side of (3.1). The second and third term of Eq. (3.1)on the left-hand side represent the electric flux entering the Gaussian box from top and bottom surface.

The bottom interface potential,  $\psi_{sb(i)}(y)$  can be expressed in terms of  $\psi_{sf(i)}(y)$

by solving 1-D Poisson's equation in x-direction of Fig. 2.1.

$$\psi_{sb(i)}(y) = \psi_{sf(i)}(y) - E_{sf(i)}(y)t_{si} - \frac{qN_{Ch}t_{si}^2}{\epsilon_{si}}$$

(3.2)

Surface electric field can be obtained by applying electric displacement vector continuity condition at top oxide-semiconductor interface.

$$E_{sf(i)}(y) = \frac{\epsilon_{ox}}{\epsilon_{si}} \frac{(V'_{GS(i)} - \psi_{sf(i)}(y))}{t_{ox}}$$

(3.3)

Substituting (3.2), (3.3) in (3.1) a simple second order non-homogeneous differential equation of surface potential is obtained,

$$\frac{\partial^2 \psi_{sf(i)}(y)}{\partial y^2} - \alpha^2 \psi_{sf(i)}(y) = \beta_{(i)}$$

(3.4)

with

$$\begin{aligned} \alpha^2 &= \eta \, \frac{C_{ox}}{t_{si}^2 C_{si}} \left( 2 + \frac{C_{ox}}{C_{si}} \right) \\ \beta_{(i)} &= \eta \, \frac{q N_{Ch}}{2\epsilon_{si}} \left( 2 + \frac{C_{ox}}{C_{si}} \right) - \alpha^2 V_{GS(i)}' \end{aligned}$$

where,  $C_{ox}$  and  $C_{si}$  are oxide capacitance and silicon film capacitance respectively calculated as

$$C_{ox} = \frac{\epsilon_{ox}}{t_{ox}}$$

,  $C_{si} = \frac{\epsilon_{si}}{t_{si}}$

The solution of (3.4) for channel region under M1, M2 and M3 can be ex-

pressed as,

$$\psi_{sf1}(y) = A_1 \exp(\alpha y) + B_1 \exp(-\alpha y) - \frac{\beta_1}{\alpha^2}, \qquad 0 \le y \le L_1$$

(3.5)

$$\psi_{sf2}(y) = A_2 \exp(\alpha y) + B_2 \exp(-\alpha y) - \frac{\beta_2}{\alpha^2}, \qquad L_1 \le y \le L_2$$

(3.6)

$$\psi_{sf3}(y) = A_3 \exp(\alpha y) + B_3 \exp(-\alpha y) - \frac{\beta_3}{\alpha^2}, \qquad L_2 \le y \le L_3$$

(3.7)

To determine the values of  $A_1$ ,  $B_1$ ,  $A_2$ ,  $B_2$ ,  $A_3$ , and  $B_3$  the following boundary conditions are applied at source edge, drain edge of the channel and at the point where the metals contact with each other:

$$\psi_{sf1}(0) = -\frac{KT}{q} \ln \frac{N_{source}}{N_{Ch}} = -V_{bi}$$

(3.8)

$$\psi_{sf3}(L) = \frac{KT}{q} \ln \frac{N_{drain}}{N_{Ch}} + V_{DS} = V'_{bi} + V_{DS}$$

(3.9)

$$\psi_{sf1}(L_1) = \psi_{sf2}(L_1) \tag{3.10}$$

$$\psi_{sf2}(L_1 + L_2) = \psi_{sf3}(L_1 + L_2) \tag{3.11}$$

$$\frac{\partial \psi_{sf1}(L_1)}{\partial y} = \frac{\partial \psi_{sf2}(L_1)}{\partial y}$$

(3.12)

$$\frac{\partial \psi_{sf1}(L_1 + L_2)}{\partial y} = \frac{\partial \psi_{sf2}(L_1 + L_2)}{\partial y}$$

(3.13)

The first two boundary conditions ensure that potential at source and drain interface of the channel will be equal to the Fermi level of source and drain region respectively. The remaining boundary conditions ensure the continuity of potential and electric displacement at the points where the metals contact. The constants of (3.5), (3.6) and (3.7) are obtained as,

$$A_{1} = \frac{\sigma_{1} - \sigma_{2}exp(-\alpha L) - \gamma}{2sinh(\alpha L)}$$

$$B_{1} = \frac{-\sigma_{1} + \sigma_{2}exp(\alpha L) + \gamma}{2sinh(\alpha L)}$$

$$A_{2} = A_{1} + \frac{\Delta V_{FB}}{2exp(\alpha L_{1})}$$

$$B_{2} = B_{1} + \frac{\Delta V_{FB}}{2exp(-\alpha L_{1})}$$

$$A_{3} = A_{2} + \frac{\Delta V'_{FB}}{2exp(\alpha L')}$$

$$B_{3} = B_{2} + \frac{\Delta V'_{FB}}{2exp(-\alpha L')}$$

where,

$$L' = L_1 + L_2$$

$$\sigma_1 = V'_{bi} + V_{DS} + \frac{\beta_3}{\alpha^2}, \quad \sigma_2 = \frac{\beta_1}{\alpha^2} - V_{bi}$$

$$\Delta V_{FB} = V_{FB2} - V_{FB1}, \quad \Delta V'_{FB} = V_{FB3} - V_{FB2}$$

$$\gamma = \Delta V_{FB} \cosh(\alpha(L - L_1)) + \Delta V'_{FB} \cosh(\alpha(L - L'))$$

Replacing the values of the constants in (3.5), (3.6) and (3.7) the surface potential under three metal gates can be found.

The derived analytical model of  $\psi_{sf(i)}$  can be used for dual material double gate TFETs [74] by considering either  $\phi_{m1} = \phi_{m2}$  or  $\phi_{m2} = \phi_{m3}$ . If we consider  $\phi_{m1} = \phi_{m2} = \phi_{m3}$  in the derived model of  $\psi_{sf(i)}$ , the model reduces to the surface potential model of single material gate TFETs [75]. Therefore, this surface potential model can be used as a generalized model for single and multiple material gate TFET structures.

## 3.2.2 2D Potential Model

Fig. 3.2: Electric potential distribution in TMDG TFET.

Electric potential profile of TMDG TFET is shown in Fig. 3.2 during ONstate. The potential profile is parabolic and therefore, the two-dimensional potential is assumed to be a second-order polynomial [76], i.e.,

$$\psi_1(y,x) = \psi_{sf1}(y) + C_1(y)x + D_1(y)x^2, \qquad 0 \le y \le L_1$$

(3.14)

$$\psi_2(y,x) = \psi_{sf2}(y) + C_2(y)x + D_2(y)x^2, \qquad L_1 \le y \le L_2$$

(3.15)

$$\psi_3(y,x) = \psi_{sf3}(y) + C_3(y)x + D_3(y)x^2, \qquad L_2 \le y \le L_3$$

(3.16)

In the channel, the following boundary conditions at the top and bottom oxide

interface can be applied to find the value of  $C_i(y)$  and  $D_i(y)$  [i = 1, 2, and 3].

$$\left. \frac{\partial \psi_1(y,x)}{\partial x} \right|_{x=0} = \frac{C_{ox}}{\epsilon_{Si}} [\psi_{sf1}(y) - V'_{GS1}]$$

(3.17)

$$\frac{\partial \psi_2(y,x)}{\partial x}\Big|_{x=0} = \frac{C_{ox}}{\epsilon_{Si}} [\psi_{sf2}(y) - V'_{GS2}]$$

(3.18)

$$\frac{\partial \psi_3(y,x)}{\partial x}\bigg|_{x=0} = \frac{C_{ox}}{\epsilon_{Si}} [\psi_{sf3}(y) - V'_{GS3}]$$

(3.19)

$$\left. \frac{\partial \psi_1(y,x)}{\partial x} \right|_{x=t_{Si}} = -\frac{C_{ox}}{\epsilon_{Si}} [\psi_{sf1}(y) - V'_{GS1}]$$

(3.20)

$$\frac{\partial \psi_2(y,x)}{\partial x} \bigg|_{x=t_{Si}} = -\frac{C_{ox}}{\epsilon_{Si}} [\psi_{sf2}(y) - V'_{GS2}]$$

(3.21)

$$\frac{\partial \psi_3(y,x)}{\partial x}\bigg|_{x=t_{Si}} = -\frac{C_{ox}}{\epsilon_{Si}}[\psi_{sf3}(y) - V'_{GS3}]$$

(3.22)

The values of  $C_i(y)$  and  $D_i(y)$  are obtained as

$$C_1(y) = \frac{C_{ox}}{\epsilon_{Si}} [\psi_{sf1}(y) - V'_{GS1}]$$

$$C_2(y) = \frac{C_{ox}}{\epsilon_{Si}} [\psi_{sf2}(y) - V'_{GS2}]$$

$$C_3(y) = \frac{C_{ox}}{\epsilon_{Si}} [\psi_{sf3}(y) - V'_{GS3}]$$

$$D_1(y) = -\frac{C_{ox}}{\epsilon_{Si}t_{Si}}[\psi_{sf1}(y) - V'_{GS1}]$$

$$D_2(y) = -\frac{C_{ox}}{\epsilon_{Si}t_{Si}}[\psi_{sf2}(y) - V'_{GS2}]$$

$$D_3(y) = -\frac{C_{ox}}{\epsilon_{Si}t_{Si}}[\psi_{sf3}(y) - V'_{GS3}]$$

# 3.3 Electric Field

Electric field is defined as the electric force per unit charge. The electric-field distribution along the channel length can be obtained by differentiating the surface potential. The lateral electric field can be written as,

$$E_{y1}(y) = -\frac{\partial \psi_1(y, x)}{\partial y} \bigg|_{x=0} = -\alpha [A_1 \exp(\alpha y) - B_1 \exp(-\alpha y)], \ 0 \le y \le L_1$$

(3.23)

$$E_{y2}(y) = -\frac{\partial \psi_2(y, x)}{\partial y} \bigg|_{x=0} = -\alpha [A_2 \exp(\alpha y) - B_2 \exp(-\alpha y)], \ L_1 \le y \le L_2$$

(3.24)

$$E_{y3}(y) = -\frac{\partial \psi_3(y, x)}{\partial y} \bigg|_{x=0} = -\alpha [A_3 \exp(\alpha y) - B_3 \exp(-\alpha y)], \ L_2 \le y \le L_3$$

(3.25)

The vertical electric field can be written as,

$$E_{x1}(y) = -\frac{\partial \psi_1(y, x)}{\partial x} = -[C_1(y) + 2xD_1(y)], \qquad 0 \le y \le L_1 \qquad (3.26)$$

$$E_{x2}(y) = -\frac{\partial \psi_2(y, x)}{\partial x} = -[C_2(y) + 2xD_2(y)], \qquad L_1 \le y \le L_2 \qquad (3.27)$$

$$E_{x3}(y) = -\frac{\partial \psi_3(y, x)}{\partial x} = -[C_3(y) + 2xD_3(y)], \qquad L_2 \le y \le L_3$$

(3.28)

# 3.4 Drain Current: Band-to-Band Tunneling Current

TFET is a reverse biased p-i-n diode and the current is small if no BTBT is present, in which case the current is referred as the off-current. As soon as BTBT occurs, the resulting on-current will dominantly exceed the off-current. In semi-classical simulators, BTBT is modeled by the introduction of an extra generation term (G) in the drift-diffusion equation. When the BTBT current contribution is dominant, the TFET current can be computed as the sum over all charge generated in the device:

$$I_{DS} = q \int G \, \mathrm{d}V$$

with dV an elementary volume in the device and G the generation rate expressed in number of carriers per unit volume per unit time. The tunneling current per unit width can be calculated as

$$I_{DS} = q \iint G \, \mathrm{d}x \mathrm{d}y \tag{3.29}$$

The most popular model to calculate the generation rate is Kane's Model [77,78], which determines the BTBT generation rate of carrier tunneling from the valence band of the source to the conduction band of the channel, as

$$G = A_k E^D \exp\left(-\frac{B_k}{E}\right) \tag{3.30}$$

where *E* is the local electric field; *D* is 2.5 for the indirect and 2 for the direct tunneling processes;  $A_k$  and  $B_k$  are the tunneling process-dependent parameters.

Fig. 3.3: Tunnel path between the valence band of the source and the conduction band of the channel region.

In this work, silicon based TMDG TFETs are considered, hence D = 2.5 is used. Although analytical model for indirect tunneling process is developed, it can be easily extended to the direct tunneling process and the drain current can be computed as [79]