# A SIGNAL REFORMING ALGORITHM BASED THREE-PHASE PLL UNDER UNBALANCED AND DISTORTED CONDITIONS IN THE GRID

A thesis submitted in partial fulfillment of the requirement for the degree of Masters of Science in Electrical and Electronic Engineering

by

Fahmid Sadeque Student ID: 1014062105P

Under the supervision of Dr. Md. Shamim Reza Assistant Professor, Department of EEE, BUET

Department of Electrical and Electronic Engineering BANGLADESH UNIVERSITY OF ENGINEERING AND TECHNOLOGY Dhaka, Bangladesh August, 2017

## Approval

The thesis titled **"A SIGNAL REFORMING ALGORITHM BASED THREE-PHASE PLL UNDER UNBALANCED AND DISTORTED CONDITIONS IN THE GRID",** submitted by Fahmid Sadeque, Student No: 1014062105P, Session: October 2014, has been accepted as satisfactory in partial fulfillment of the requirement for the degree of Master of Science in Electrical and Electronic Engineering on 20 August, 2017.

### **Board of Examiners**

| 1                                                   |              |

|-----------------------------------------------------|--------------|

| Dr. Md. Shamim Reza                                 | Chairman     |

| Assistant Professor                                 | (Supervisor) |

| Department of Electrical and Electronic Engineering |              |

| Bangladesh University of Engineering and Technology |              |

| Dhaka – 1205, Bangladesh                            |              |

|                                                     |              |

|                                                     |              |

| 2                                                   |              |

| Dr. Taifur A. Chowdhury                             | Member       |

| Professor and Head                                  | (Ex-officio) |

| Department of Electrical and Electronic Engineering |              |

| Bangladesh University of Engineering and Technology |              |

| Dhaka – 1205, Bangladesh                            |              |

|                                                     |              |

|                                                     |              |

| 3                                                   |              |

| Dr. Mohammad Jahangir Alam                          | Member       |

| Professor                                           |              |

| Department of Electrical and Electronic Engineering |              |

| Bangladesh University of Engineering and Technology |              |

| Dhaka – 1205, Bangladesh                            |              |

|                                                     |              |

|                                                     |              |

| 4                                                   |              |

| Dr. Muhammad Quamruzzaman                           | Member       |

| Professor                                           | (External)   |

| Department of Electrical and Electronic Engineering |              |

| Chittagong University of Engineering and Technology |              |

| Chittagong – 4349, Bangladesh                       |              |

### Declaration

It is hereby declared that this thesis or any part of it has not been submitted elsewhere for the award of any degree or diploma.

Signature of the Candidate

(Fahmid Sadeque)

### Acknowledgement

All praise goes to the Almighty for giving me the patience and drive required to complete my M.Sc. research and finish the dissertation in due time.

I would begin by heartily thanking my thesis supervisor Dr. Md. Shamim Reza, Assistant Professor, Department of Electrical and Electronic Engineering (EEE), Bangladesh University of Engineering and Technology (BUET), for his generous help, edifying suggestions and well-defined guidance throughout the thesis work. I feel grateful to him for giving me sufficient freedom and having faith in my capabilities, which made the research work very much enjoyable for me. His passion and dedication to academic research has motivated me to push my boundaries harder and excel at my research work, which I believe, will inspire me to be a better researcher in future.

I want to express my special gratitude to Dr. Md Maruf Hossain, Assistant Professor, Department of Electrical Engineering Technology, University of Wisconsin, USA, for his kind help with the discussion on different types of PLL algorithms and their applications.

I would like to thank my parents as well as my sister and dedicate my thesis to them. They have been the encouragement behind my every successful endeavor. This thesis work is not an exception and this would not have been completed without their constant support and inspiration.

Finally, I put forward my humble gratitude to all my colleagues, friends and well-wishers for their help, support and words of encouragement during my research work.

### Abstract

Fast and accurate estimation of the grid voltage phase angle is crucial for grid synchronization of power converters, flexible AC transmission systems (FACTS) devices, power line conditioners, regenerative drives, uninterrupted power supplies, distributed generations and energy storage systems. Several phase-angle estimation methods, such as- Fourier analysis, frequency locked loop, notch filter, least-error squares, and demodulation, have been developed for phase-angle estimation. Although these methods are accurate at nominal frequency, they require modification of design when the frequency is altered. Synchronous reference frame phase-locked loop (SRF-PLL) is the simplest and the fastest in phase-angle estimation of purely sinusoidal balanced three-phase voltage system. But its accuracy decreases when the system is not balanced or is affected by the presence of harmonics.

In this thesis, a signal reforming algorithm based three-phase phase-locked loop (PLL) has been developed to estimate the phase angles of an unbalanced and harmonics affected threephase voltage system by combining a harmonics attenuation algorithm, a signal reforming algorithm and the conventional SRF-PLL algorithm into a single PLL system. This technique attenuates the harmonic components from the three-phase signal and then reforms the unbalanced three-phase signal into a balanced one. This makes the conventional synchronous reference frame PLL (SRF-PLL) suited for accurate estimation of the phase angle of one phase. The phase angles of the other two unbalanced phases are also calculated accurately without using additional PLLs. The developed PLL works perfectly even when the frequency of the system is varied. The developed PLL has been tested in MATLAB/Simulink environment for different types of imbalances and distortions. The harmonics attenuation technique is simpler and faster. The signal reforming algorithm is effective in all unbalanced conditions. The developed PLL algorithm not only solves the phase estimation difficulties of the conventional SRF-PLL working under harmonics affected unbalanced grid conditions, but also avoids the use of three single-phase PLLs to estimate the phase angles of a three-phase voltage system.

## Table of Contents

| Approval                                      | iii  |

|-----------------------------------------------|------|

| Declaration                                   | iv   |

| Acknowledgement                               | v    |

| Abstract                                      | vi   |

| Table of Contents                             | vii  |

| List of Figures                               | xi   |

| List of Tables                                | xix  |

| List of Abbreviations                         | XX   |

| List of Symbols                               | xxii |

| Chapter 1: Introduction                       | 1    |

| 1.1: Importance of Phase-Angle Estimation     | 1    |

| 1.2: Literature Review                        | 3    |

| 1.3: Objectives of the Thesis                 | 6    |

| 1.4: Thesis Methodology                       | 7    |

| 1.5: List of Publications                     | 8    |

| 1.6: Thesis Organization                      | 9    |

| Chapter 2: Phase-Locked Loops                 | 10   |

| 2.1: The Basic Structure of Phase-Locked Loop | 10   |

| 2.2: Commonly Used PLL Algorithms             | 12   |

| 2.2.1: Single-Phase Inverse Park PLL          | 12   |

| 2.2.2: Single-Phase Second Order Generalized Integrator Based PLL                 | 13 |

|-----------------------------------------------------------------------------------|----|

| 2.2.3: Single-Phase Transport Delay PLL                                           | 14 |

| 2.2.4: Single-Phase Enhanced PLL                                                  | 15 |

| 2.2.5: Three-Phase SRF-PLL                                                        | 15 |

| 2.2.6: Decoupled Double SRF-PLL                                                   | 16 |

| 2.2.7: Dual Second Order Generalized Integrator PLL                               | 17 |

| 2.2.8: Three-Phase Enhanced PLL                                                   | 18 |

| 2.3: The Conventional Three-Phase SRF-PLL and Its Performance                     | 19 |

| Chapter 3: The Developed Phase-Locked Loop                                        | 27 |

| 3.1: Block Diagram of the Developed PLL                                           | 27 |

| 3.2: Attenuation of Harmonics                                                     | 28 |

| 3.3: Determination of Phase-Angle Deviation                                       | 33 |

| 3.4: Signal Reformation by Amplitude & Phase-Angle Correction                     | 37 |

| 3.5: Selection of $K_p$ and $K_i$ for the PLL                                     | 39 |

| Chapter 4: Simulation Results                                                     | 41 |

| 4.1: Simulation Environment                                                       | 41 |

| 4.2: Case-A: Three-Phase Grid Voltage without Harmonics                           | 43 |

| 4.2.1: Case-A1: Voltage Sag at All the Phases                                     | 43 |

| 4.2.2: Case-A2: Voltage Swell at All the Phases                                   | 44 |

| 4.2.3: Case-A3: Simultaneous Voltage Sag and Voltage Swell at Different<br>Phases | 45 |

| 4.2.4: Case-A4: Phase Shift of One Phase                                                                                      | 46 |

|-------------------------------------------------------------------------------------------------------------------------------|----|

| 4.2.5: Case-A5: Phase Shift of Two Phases                                                                                     | 48 |

| 4.2.6: Case-A6: Simultaneous Amplitude Imbalance and Phase-Shift of All the Phases                                            | 49 |

| 4.2.7: Case-A7: Balanced System at Frequency Other Than Nominal Value                                                         | 50 |

| 4.2.8: Case-A8: Amplitude Imbalance at Frequency Other Than Nominal Value                                                     | 52 |

| 4.2.9: Case-A9: Phase-Shift of the Phases at Frequency Other Than<br>Nominal Value                                            | 54 |

| 4.2.10: Case-A10: Simultaneous Amplitude Imbalance and Phase-Shift of<br>All the Phases at Frequency Other Than Nominal Value | 56 |

| 4.3: Case-B: Three-Phase Grid Voltage with Harmonic Distortion                                                                | 58 |

| 4.3.1: Case-B1: Balanced System Distorted by Harmonics                                                                        | 58 |

| 4.3.2: Case-B2: Voltage Sag at All the Phases with Harmonic Distortion                                                        | 60 |

| 4.3.3: Case-B3: Voltage Swell at All the Phases with Harmonic Distortion                                                      | 61 |

| 4.3.4: Case-B4: Simultaneous Voltage Sag and Voltage Swell at Different<br>Phases with Harmonic Distortion                    | 62 |

| 4.3.5: Case-B5: Phase Shift of One Phase with Harmonic Distortion                                                             | 63 |

| 4.3.6: Case-B6: Phase Shift of Two Phases with Harmonic Distortion                                                            | 65 |

| 4.3.7: Case-B7: Simultaneous Amplitude Imbalance and Phase-Shift of All<br>the Phases with Harmonic Distortion                | 66 |

| 4.2.8: Case-B8: Harmonics Affected Balanced System at Frequency Other<br>Than Nominal Value                                   | 67 |

| 4.2.9: Case-B9: Amplitude Imbalance with Harmonic Distortion at<br>Frequency Other Than Nominal Value                         | 69 |

ix

| 4.2.10: Case-B10: Phase-Shift of the Phases with Harmonic Distortion at | 71 |

|-------------------------------------------------------------------------|----|

| Frequency Other Than Nominal Value                                      |    |

| 4.3.11: Case-B11: Simultaneous Amplitude Imbalance and Phase-Shift of   | 73 |

| All the Phases Accompanied by Harmonic Distortion at Frequency          |    |

| Other than Nominal Value                                                |    |

| Chapter 5: Conclusions                                                  | 75 |

| 5.1: Summary                                                            | 75 |

| 5.2: Future Work                                                        | 76 |

| References                                                              | 77 |

| Appendix A: MATLAB/Simulink Block Diagrams                              | 89 |

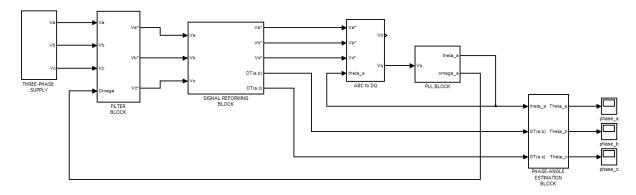

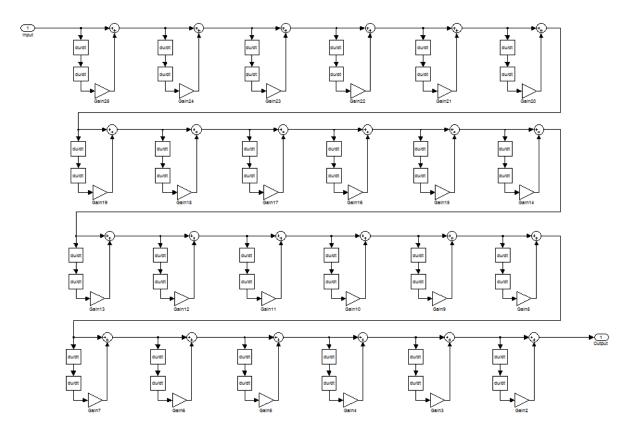

| A.1: Block Diagram of the Whole System for Simulation                   | 89 |

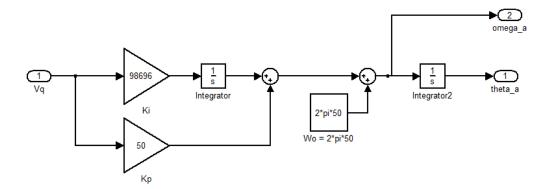

| A.2: Block Diagram of the PLL Block                                     | 89 |

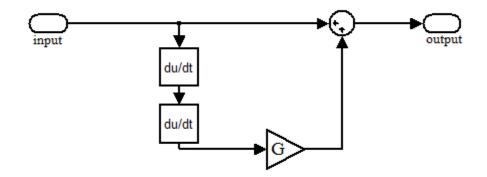

| A.3: Block Diagram of the Filter Block                                  | 90 |

| Appendix B: MATLAB Codes                                                | 91 |

| <b>B.1: MATLAB Code for Three-Phase Grid Voltage</b>                    | 91 |

| <b>B.2: MATLAB Code for Signal Reforming Block</b>                      | 93 |

| <b>B.3: MATLAB</b> Code for abc to dq Transformation                    | 97 |

# List of Figures

| Fig. 2.1  | Block diagram of a Phase-Locked Loop.                                                                                                                                                                                                  | 10 |

|-----------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

| Fig. 2.2  | Block diagram of a Single-Phase PLL.                                                                                                                                                                                                   | 12 |

| Fig. 2.3  | Block diagram of the single-phase SOGI based PLL                                                                                                                                                                                       | 13 |

| Fig. 2.4  | Block diagram of single-phase transport delay PLL.                                                                                                                                                                                     | 14 |

| Fig. 2.5  | Block diagram of single-phase enhanced PLL.                                                                                                                                                                                            | 15 |

| Fig. 2.6  | Block diagram of three-phase DDSRF-PLL.                                                                                                                                                                                                | 16 |

| Fig. 2.7  | Block diagram of three-phase DSOGI-PLL.                                                                                                                                                                                                | 17 |

| Fig. 2.8  | Block diagram of three-phase EPLL.                                                                                                                                                                                                     | 18 |

| Fig. 2.9  | Block diagram of the conventional SRF-PLL.                                                                                                                                                                                             | 19 |

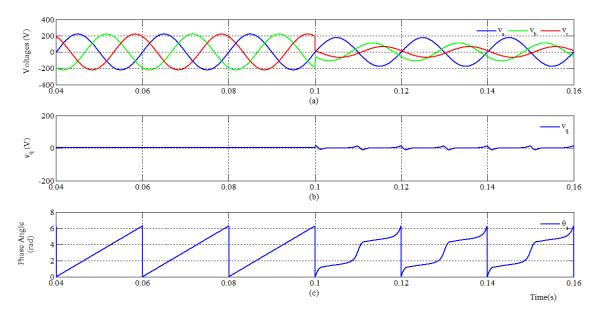

| Fig. 2.10 | Performance of the conventional SRF- PLL under symmetrical fault conditions (50% amplitude step, $\pi/2$ phase jump) at high bandwidth. (a) three-phase voltage waveforms; (b) $v_q$ versus time; (c) estimated phase angle of $v_a$ . | 20 |

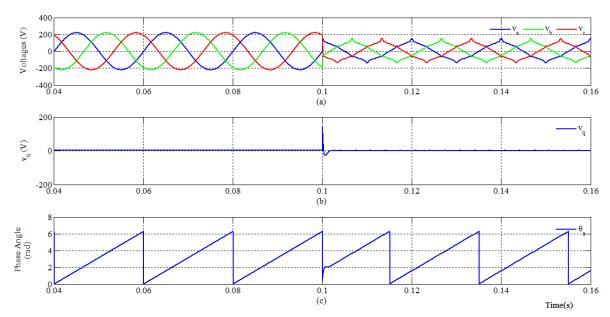

| Fig. 2.11 | Performance of the conventional SRF- PLL under only unequal amplitudes of the phases at high bandwidth (a) three-phase voltage waveforms; (b) $v_q$ versus time; (c) estimated phase angle of $v_a$ .                                  | 21 |

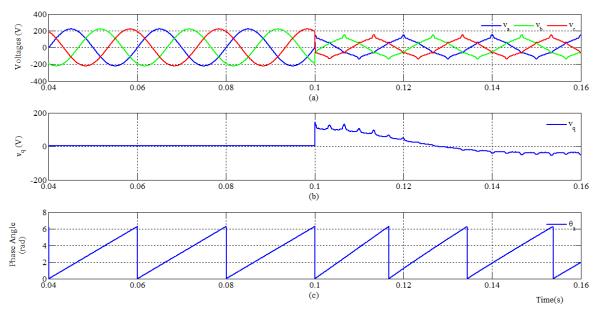

| Fig. 2.12 | Performance of the conventional SRF- PLL under only unequal phase difference between the phases at high bandwidth (a) three-phase voltage waveforms; (b) $v_q$ versus time; (c) estimated phase angle of $v_a$ .                       | 22 |

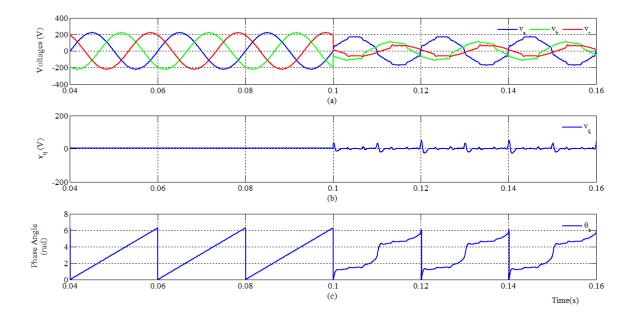

| Fig. 2.13 | Performance of the conventional SRF-PLL under both unequal amplitude and unequal phase differences between the phases at high bandwidth (a) three-phase voltage waveforms; (b) $v_q$ versus time; (c) estimated phase angle of $v_a$ . | 23 |

- Fig 2.14 Performance of the conventional SRF- PLL under symmetrical fault 24 conditions with harmonics (50% amplitude step, π/2 phase jump) at high bandwidth. (a) three-phase voltage waveforms; (b) v<sub>q</sub> versus time;

(c) estimated phase angle of v<sub>a</sub>.

- **Fig. 2.15** Performance of the conventional SRF- PLL under symmetrical fault 24 conditions with harmonics (50% amplitude step,  $\pi/2$  phase jump) at very low bandwidth. (a) three-phase voltage waveforms; (b)  $v_q$  versus time; (c) estimated phase angle of  $v_a$ .

- Fig. 2.16 Performance of the conventional SRF- PLL in the presence of harmonics 25 under both unequal amplitude and unequal phase differences between the phases at high bandwidth. (a) three-phase voltage waveforms; (b)  $v_q$  versus time; (c) estimated phase angle of  $v_a$ .

- Fig. 2.17 Performance of the conventional SRF- PLL in the presence of harmonics 26 under both unequal amplitude and unequal phase differences between the phases at low bandwidth (a) three-phase voltage waveforms; (b)  $v_q$ versus time; (c) estimated phase angle of  $v_a$ .

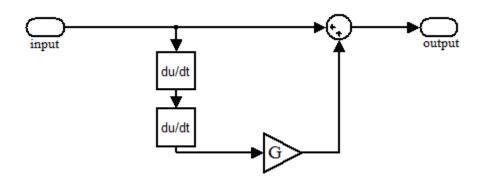

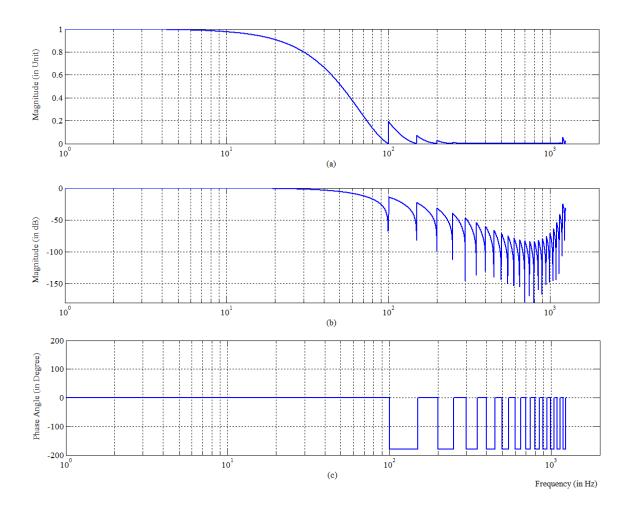

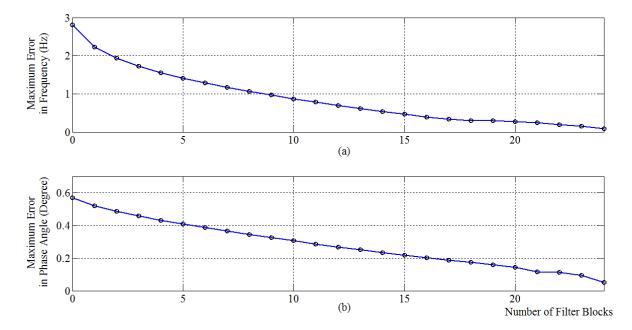

- **Fig. 3.2** Block diagram of a single unit for the harmonics attenuation technique. 30

- Fig. 3.3 Performance of the designed harmonics attenuation algorithm (a) 31

Frequency (Hz) vs Magnitude (in Unit), (b) Frequency (Hz) vs

Amplitude (in dB), (c) Frequency vs Phase Angle (in Degree).

- Fig. 3.4 Performance of the proposed technique. (a) Estimated maximum 32 frequency error versus number of filter blocks. (b) Estimated maximum phase error versus number of filter blocks.

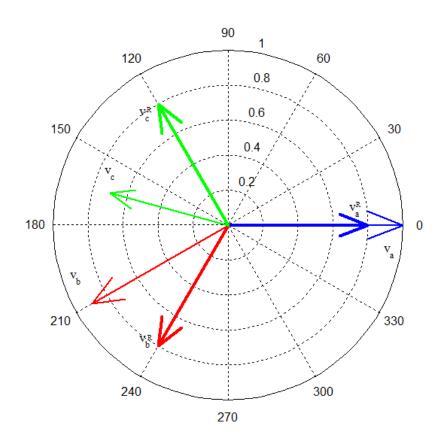

- Fig. 3.5 Phase diagram of the system. The thin line represents the unbalanced 34 three-phase system and the thick line represents the reformed balance system. Phase *a*, *b* and *c* are represented by blue, red and green color respectively.

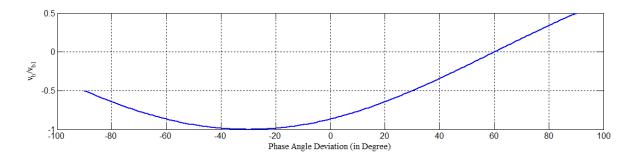

| Fig. 3.6 | Phase Angle Deviation vs $v_b/v_{b1}$ curve.                                                                                                                                                                                                | 35 |

|----------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

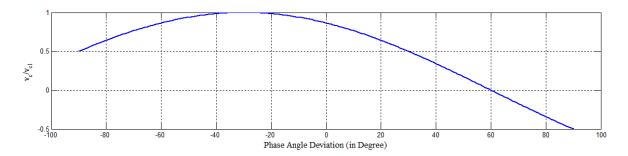

| Fig. 3.7 | Phase Angle Deviation vs $v_c/v_{c1}$ curve.                                                                                                                                                                                                | 36 |

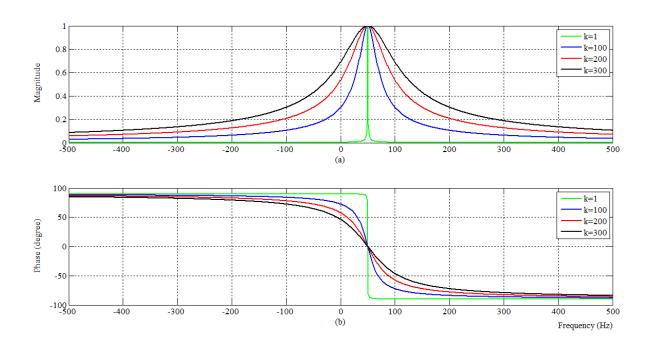

| Fig. 3.8 | Frequency response of $G_{SRF-PLL}(s)$ for $\omega_e = 2\pi 50$ rad/s at different values of k. (a) Magnitude vs Frequency plot, (b) Phase vs Frequency plot.                                                                               | 39 |

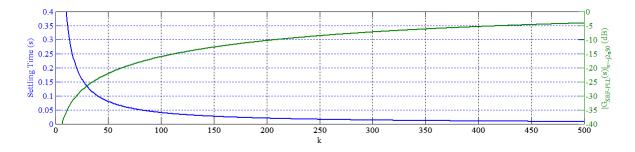

| Fig. 3.9 | SRF-PLL settling-time in extraction of FFPS component as a function of $k$ (labeling on the left); Attenuation provided by the SRF-PLL at the fundamental frequency of negative sequence as a function of $k$ (labeling on the right).      | 40 |

| Fig. 4.1 | Performance of the developed PLL with voltage sag at all the phases. (a) three-phase voltage waveforms; (b) three-phase voltage waveforms after reformation; (c) $v_q$ versus time; (d) estimated phase angles of $v_a$ , $v_b$ and $v_c$ . | 43 |

| Fig. 4.2 | Performance of the developed PLL with voltage swell at all the phases.                                                                                                                                                                      | 44 |

- (a) three-phase voltage waveforms; (b) three-phase voltage waveforms after reformation; (c)  $v_q$  versus time; (d) estimated phase angles of  $v_a$ ,  $v_b$  and  $v_c$ .

- **Fig. 4.3** Performance of the developed PLL with voltage sag and voltage swell 45 at different phases. (a) three-phase voltage waveforms; (b) three-phase voltage waveforms after reformation; (c)  $v_q$  versus time; (d) estimated phase angles of  $v_a$ ,  $v_b$  and  $v_c$ .

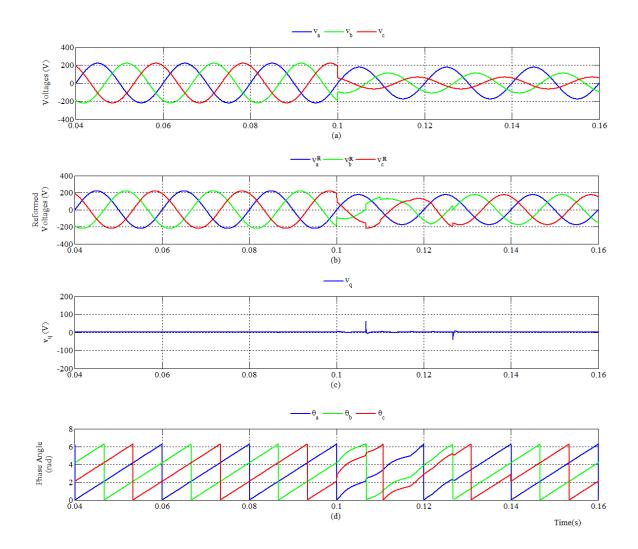

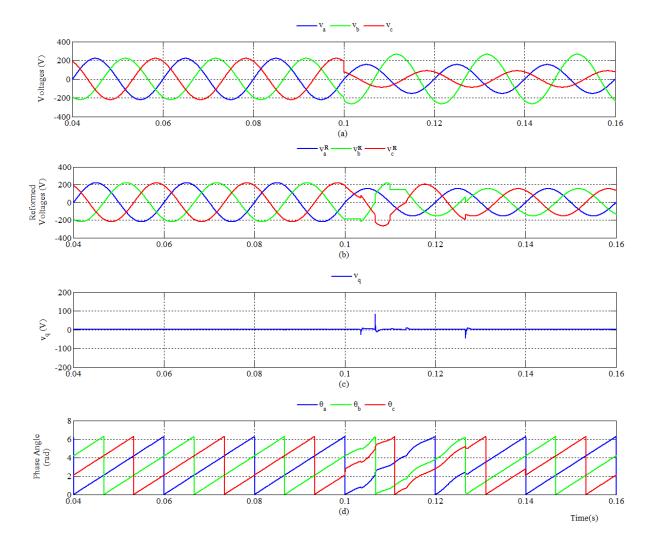

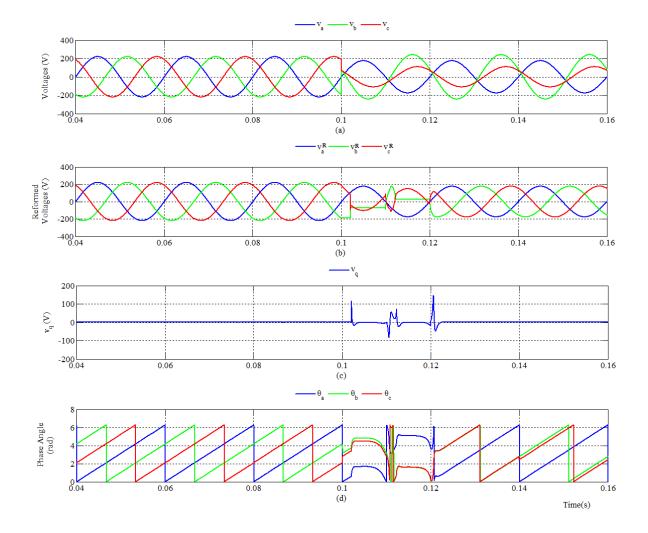

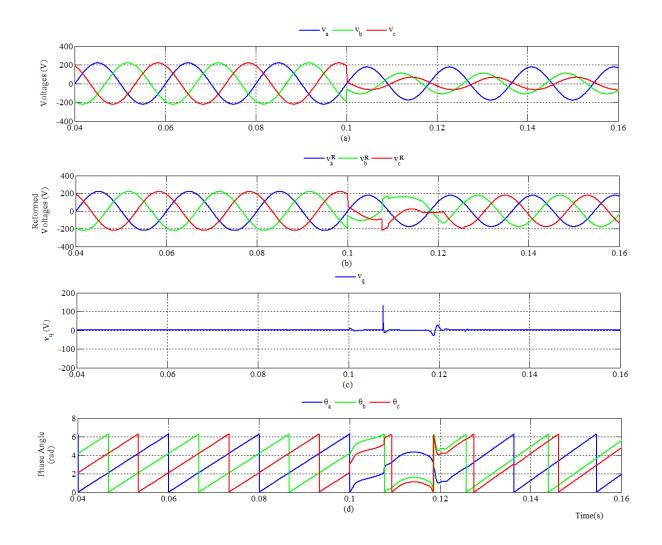

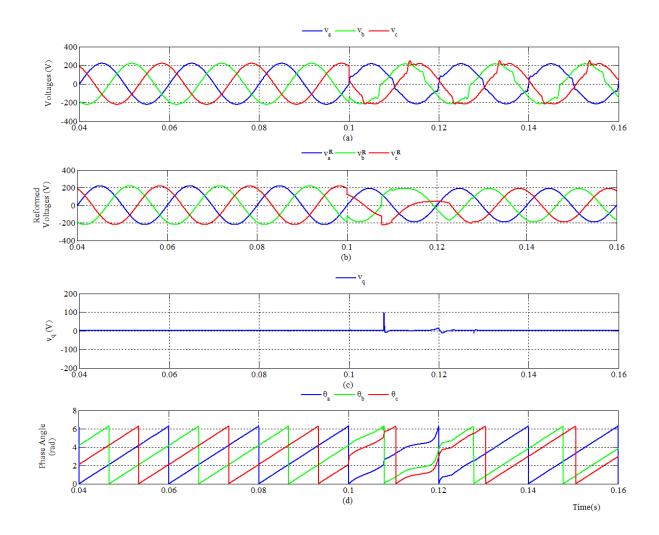

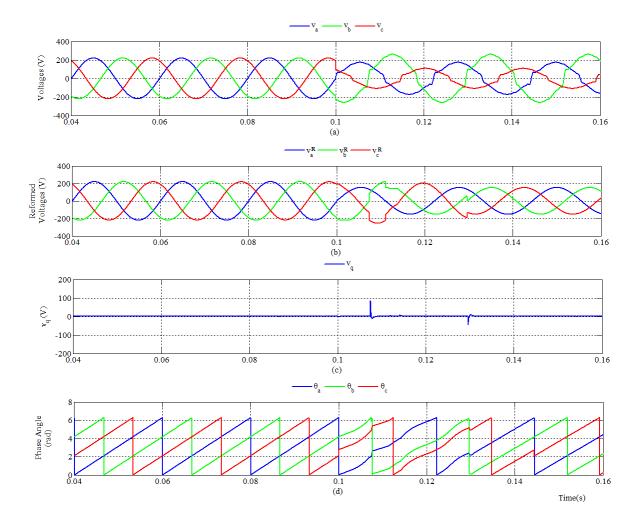

- **Fig. 4.4** Performance of the developed PLL with sudden phase-shift of phase-*b*. 46 (a) three-phase voltage waveforms; (b) three-phase voltage waveforms after reformation; (c)  $v_q$  versus time; (d) estimated phase angles of  $v_a$ ,  $v_b$  and  $v_c$ .

- **Fig. 4.5** Performance of the developed PLL with sudden phase-shift of phase-c. 47 (a) three-phase voltage waveforms; (b) three-phase voltage waveforms after reformation; (c)  $v_q$  versus time; (d) estimated phase angles of  $v_a$ ,  $v_b$  and  $v_c$ .

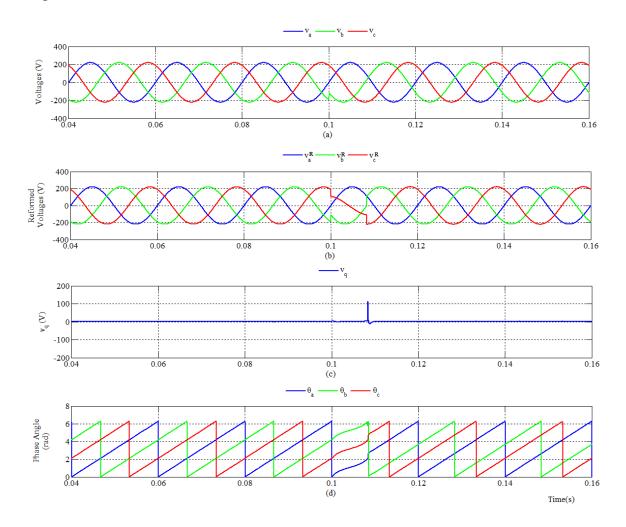

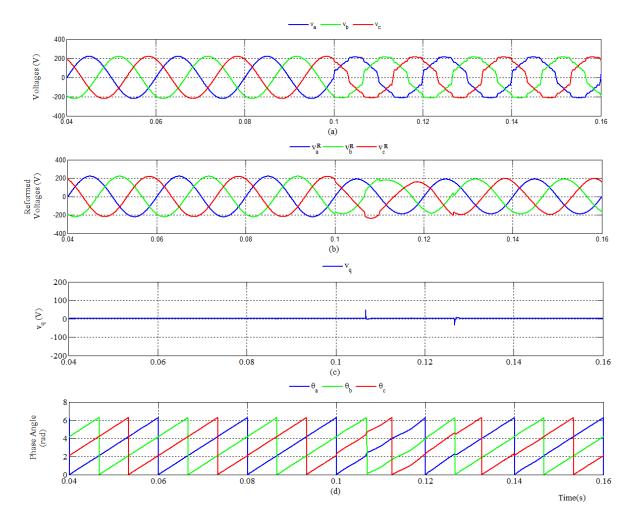

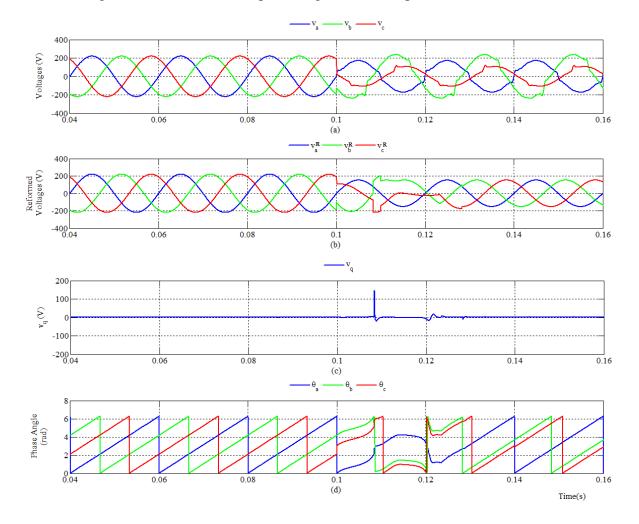

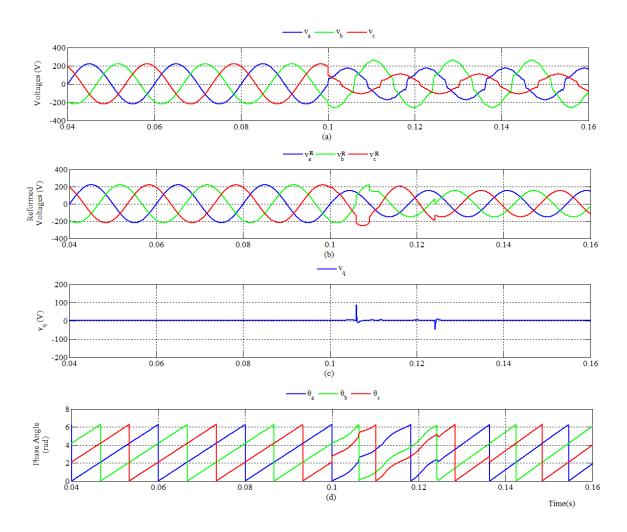

- **Fig. 4.6** Performance of the developed PLL with sudden phase-shift of both 48 phase-*b* and phase-*c*. (a) three-phase voltage waveforms; (b) three-phase voltage waveforms after reformation; (c)  $v_q$  versus time; (d) estimated phase angles of  $v_a$ ,  $v_b$  and  $v_c$

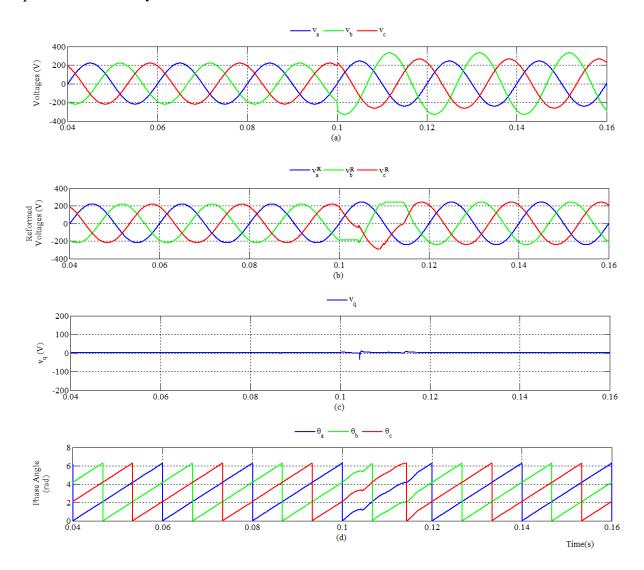

- **Fig. 4.7** Performance of the developed PLL under unequal amplitude and 49 unequal phase-angle differences of the phases (a) three-phase voltage waveforms; (b) three-phase voltage waveforms after reformation; (c)  $v_q$  versus time; (d) estimated phase angles of  $v_a$ ,  $v_b$  and  $v_c$ .

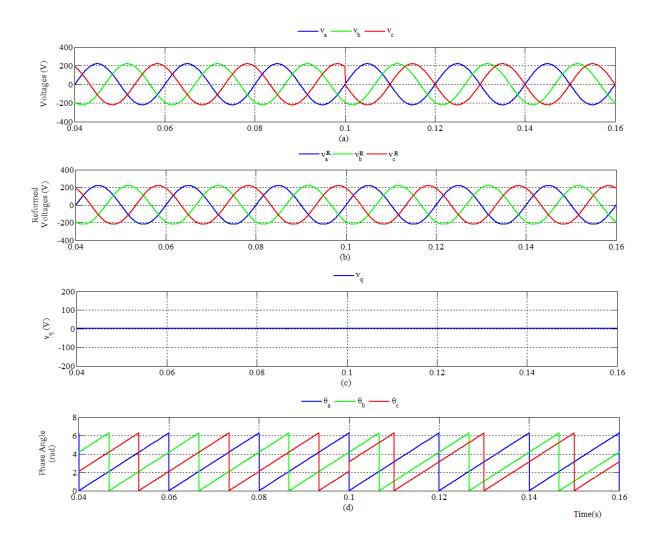

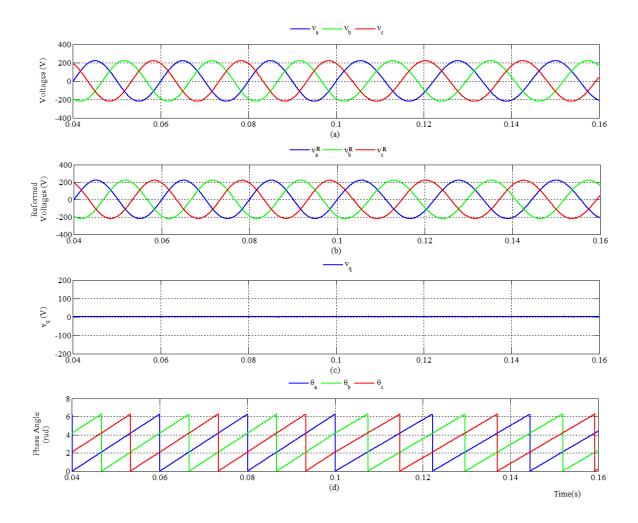

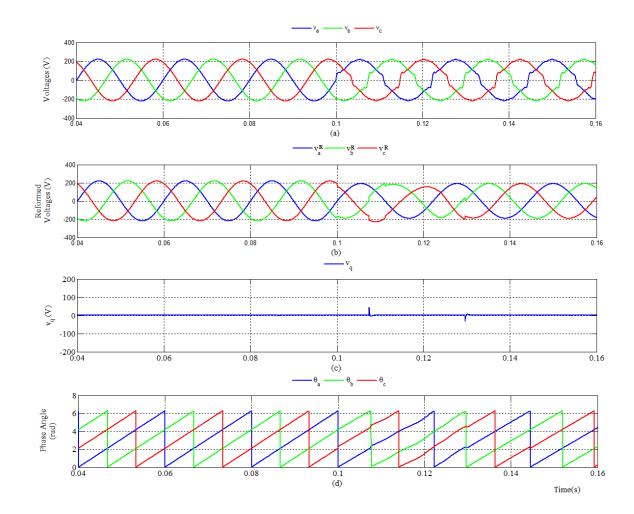

- **Fig. 4.8** Performance of the developed PLL under balanced amplitude and equal 50 phase-angle differences of the phases at 45 Hz. (a) three-phase voltage waveforms; (b) three-phase voltage waveforms after reformation; (c)  $v_q$  versus time; (d) estimated phase angles of  $v_a$ ,  $v_b$  and  $v_c$ .

- **Fig. 4.9** Performance of the developed PLL under balanced amplitude and equal 51 phase-angle differences of the phases at 55 Hz. (a) three-phase voltage waveforms; (b) three-phase voltage waveforms after reformation; (c)  $v_q$  versus time; (d) estimated phase angles of  $v_a$ ,  $v_b$  and  $v_c$ .

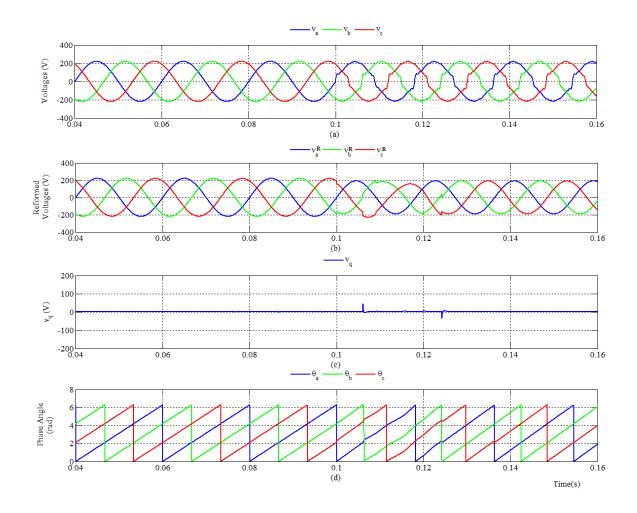

- **Fig. 4.10** Performance of the developed PLL under amplitude imbalance but equal 52 phase-angle differences of the phases at 45 Hz. (a) three-phase voltage waveforms; (b) three-phase voltage waveforms after reformation; (c)  $v_q$  versus time; (d) estimated phase angles of  $v_a$ ,  $v_b$  and  $v_c$ .

- **Fig. 4.11** Performance of the developed PLL under amplitude imbalance but equal 53 phase-angle differences of the phases at 55 Hz. (a) three-phase voltage waveforms; (b) three-phase voltage waveforms after reformation; (c)  $v_q$  versus time; (d) estimated phase angles of  $v_a$ ,  $v_b$  and  $v_c$ .

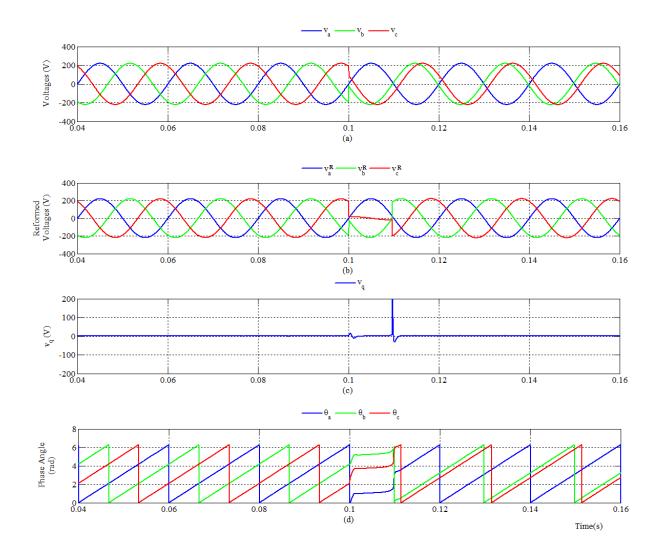

- **Fig. 4.12** Performance of the developed PLL under balanced amplitudes of the 54 phases but with unequal phase-angle differences at 45 Hz. (a) three-phase voltage waveforms; (b) three-phase voltage waveforms after reformation; (c)  $v_q$  versus time; (d) estimated phase angles of  $v_a$ ,  $v_b$  and  $v_c$ .

- **Fig. 4.13** Performance of the developed PLL under balanced amplitudes of the 55 phases but with unequal phase-angle differences at 55 Hz. (a) three-phase voltage waveforms; (b) three-phase voltage waveforms after reformation; (c)  $v_q$  versus time; (d) estimated phase angles of  $v_a$ ,  $v_b$  and  $v_c$ .

- **Fig. 4.14** Performance of the developed PLL under unequal amplitude and 56 unequal phase-angle differences of the phases at 45 Hz (a) three-phase voltage waveforms; (b) three-phase voltage waveforms after reformation; (c)  $v_q$  versus time; (d) estimated phase angles of  $v_a$ ,  $v_b$  and  $v_c$ .

- **Fig. 4.15** Performance of the developed PLL under unequal amplitude and 57 unequal phase-angle differences of the phases at 55 Hz (a) three-phase voltage waveforms; (b) three-phase voltage waveforms after reformation; (c)  $v_q$  versus time; (d) estimated phase angles of  $v_a$ ,  $v_b$  and  $v_c$ .

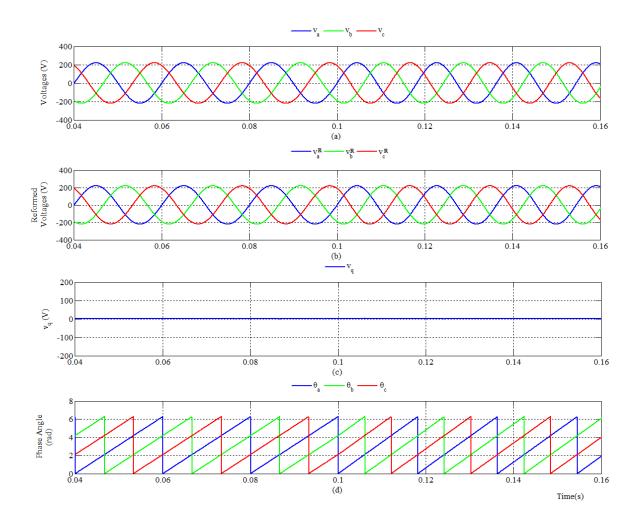

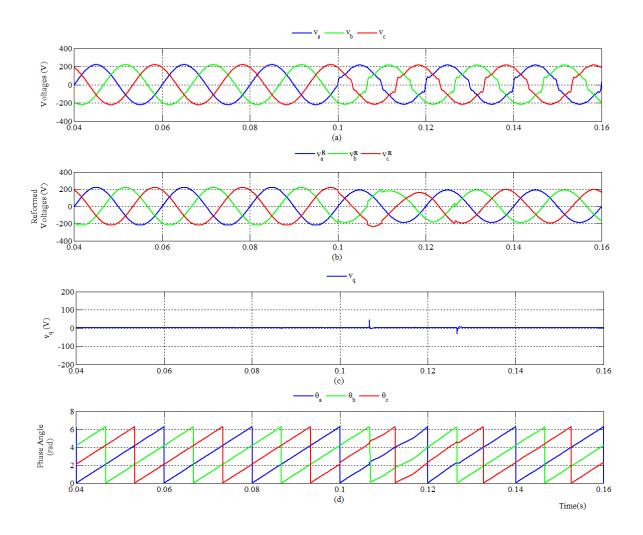

- **Fig. 4.16** Performance of the developed PLL under harmonics affected condition 58 (EN 50160 Standard) with a balanced system (a) three-phase voltage waveforms; (b) three-phase voltage waveforms after reformation; (c)  $v_q$  versus time; (d) estimated phase angles of  $v_a$ ,  $v_b$  and  $v_c$ .

- **Fig. 4.17** Performance of the developed PLL under harmonics affected condition 59 (IEEE 519-2014 Standard) with a balanced system (a) three-phase voltage waveforms; (b) three-phase voltage waveforms after reformation; (c)  $v_q$  versus time; (d) estimated phase angles of  $v_a$ ,  $v_b$  and  $v_c$ .

- **Fig 4.18** Performance of the developed PLL under harmonics affected condition 60 (IEEE 519-2014 Standard) with a voltage sag at all the phases (a) three-phase voltage waveforms; (b) three-phase voltage waveforms after reformation; (c)  $v_q$  versus time; (d) estimated phase angles of  $v_a$ ,  $v_b$  and  $v_c$ .

- **Fig. 4.19** Performance of the developed PLL under harmonics affected condition 61 (IEEE 519-2014 Standard) with a voltage swell at all the phases (a) three-phase voltage waveforms; (b) three-phase voltage waveforms after reformation; (c)  $v_q$  versus time; (d) estimated phase angles of  $v_a$ ,  $v_b$  and  $v_c$ .

- **Fig. 4.20** Performance of the developed PLL under harmonics affected condition 62 (IEEE 519-2014 Standard) with different amplitudes at all the phases (a) three-phase voltage waveforms; (b) three-phase voltage waveforms after reformation; (c)  $v_q$  versus time; (d) estimated phase angles of  $v_a$ ,  $v_b$  and  $v_c$ .

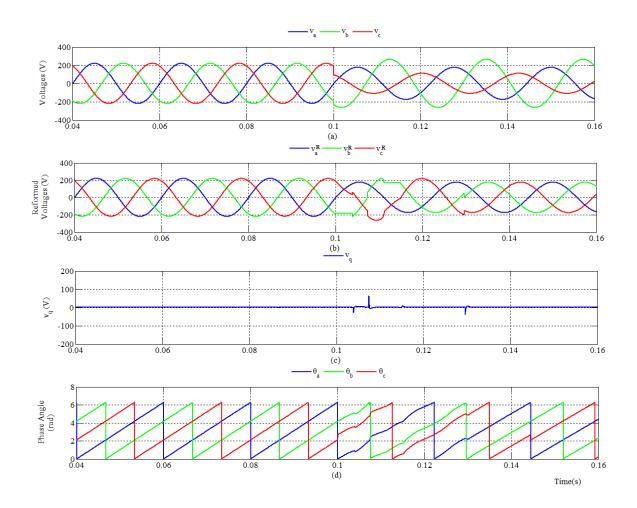

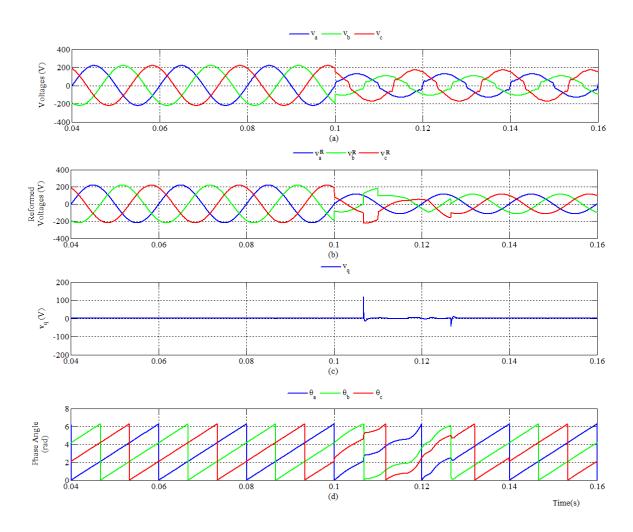

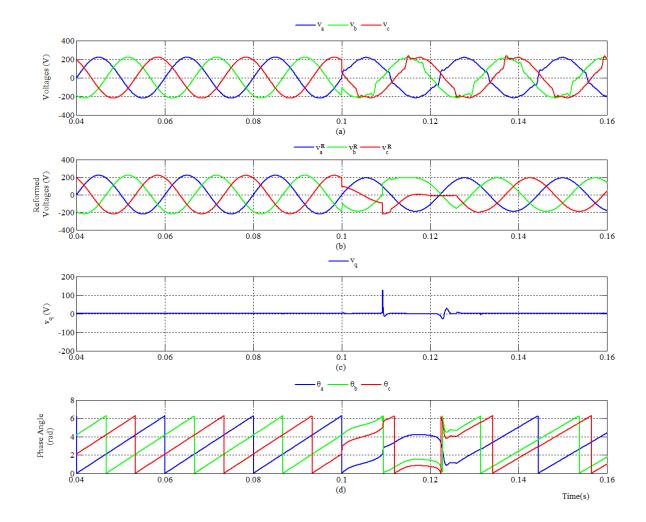

- **Fig. 4.21** Performance of the developed PLL under harmonics affected condition 63 with phase shift of phase-*b* (a) three-phase voltage waveforms; (b) threephase voltage waveforms after reformation; (c)  $v_q$  versus time; (d) estimated phase angles of  $v_a$ ,  $v_b$  and  $v_c$ .

- **Fig. 4.22** Performance of the developed PLL under harmonics affected condition 64 with phase shift of phase-*c* (a) three-phase voltage waveforms; (b) three-phase voltage waveforms after reformation; (c)  $v_q$  versus time; (d) estimated phase angles of  $v_a$ ,  $v_b$  and  $v_c$ .

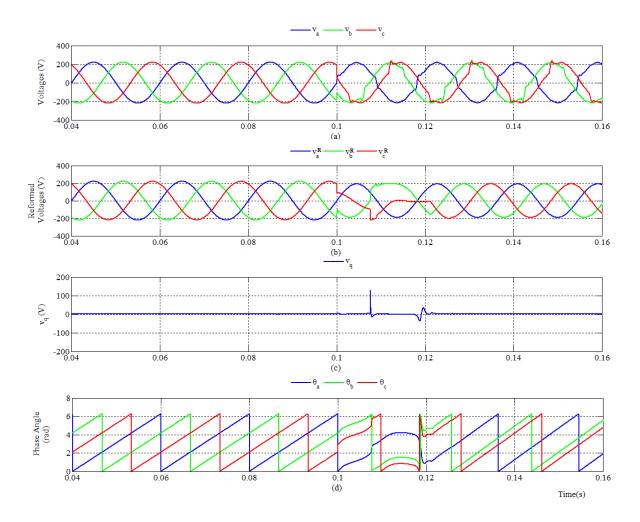

- **Fig. 4.23** Performance of the developed PLL under harmonics affected condition 65 with phase shift of all the phases. (a) three-phase voltage waveforms; (b) three-phase voltage waveforms after reformation; (c)  $v_q$  versus time; (d) estimated phase angles of  $v_a$ ,  $v_b$  and  $v_c$ .

- **Fig. 4.24** Performance of the developed PLL under harmonics affected condition 66 with both amplitude imbalance and phase shift of all the phases. (a) three-phase voltage waveforms; (b) three-phase voltage waveforms after reformation; (c)  $v_q$  versus time; (d) estimated phase angles of  $v_a$ ,  $v_b$  and  $v_c$ .

- **Fig. 4.25** Performance of the developed PLL under harmonics affected condition 67 with balanced three-phase system and at 45 Hz. (a) three-phase voltage waveforms; (b) three-phase voltage waveforms after reformation; (c)  $v_q$ versus time; (d) estimated phase angles of  $v_a$ ,  $v_b$  and  $v_c$ .

- **Fig. 4.26** Performance of the developed PLL under harmonics affected condition 68 with balanced three-phase system and at 55 Hz. (a) three-phase voltage waveforms; (b) three-phase voltage waveforms after reformation; (c)  $v_q$  versus time; (d) estimated phase angles of  $v_a$ ,  $v_b$  and  $v_c$ .

- **Fig. 4.27** Performance of the developed PLL under amplitude imbalance but equal 69 phase-angle differences of the phases at 45 Hz accompanied by harmonic distortion. (a) three-phase voltage waveforms; (b) three-phase voltage waveforms after reformation; (c)  $v_q$  versus time; (d) estimated phase angles of  $v_a$ ,  $v_b$  and  $v_c$

- **Fig. 4.28** Performance of the developed PLL under amplitude imbalance but equal 70 phase-angle differences of the phases at 55 Hz accompanied by harmonic distortion. (a) three-phase voltage waveforms; (b) three-phase voltage waveforms after reformation; (c)  $v_q$  versus time; (d) estimated phase angles of  $v_a$ ,  $v_b$  and  $v_c$

- **Fig. 4.29** Performance of the developed PLL under balanced amplitudes of the 71 phases but with unequal phase-angle differences at 45 Hz accompanied by harmonic distortion. (a) three-phase voltage waveforms; (b) three-phase voltage waveforms after reformation; (c)  $v_q$  versus time; (d) estimated phase angles of  $v_a$ ,  $v_b$  and  $v_c$ .

- **Fig. 4.30** Performance of the developed PLL under balanced amplitudes of the 72 phases but with unequal phase-angle differences at 55 Hz accompanied by harmonic distortion. (a) three-phase voltage waveforms; (b) three-phase voltage waveforms after reformation; (c)  $v_q$  versus time; (d) estimated phase angles of  $v_a$ ,  $v_b$  and  $v_c$ .

- **Fig. 4.31** Performance of the developed PLL under unbalanced and distorted 73 condition at lower than nominal frequency. (a) three-phase voltage waveforms; (b) three-phase voltage waveforms after reformation; (c)  $v_q$  versus time; (d) estimated phase angles of  $v_a$ ,  $v_b$  and  $v_c$ .

- **Fig. 4.32** Performance of the developed PLL under unbalanced and distorted 74 condition at higher than nominal frequency. (a) three-phase voltage waveforms; (b) three-phase voltage waveforms after reformation; (c)  $v_q$  versus time; (d) estimated phase angles of  $v_a$ ,  $v_b$  and  $v_c$ .

| Fig. A.1 | Block diagram of the whole system for simulation. | 89 |

|----------|---------------------------------------------------|----|

| Fig. A.2 | Expanded block diagram of the PLL block.          | 89 |

| Fig. A.3 | Block diagram of the developed filter.            | 90 |

| Fig. A.4 | Block diagram of a unit filter block.             | 90 |

## List of Tables

| Table I  | Harmonics based on European Standard EN 50160 | 42 |

|----------|-----------------------------------------------|----|

|          |                                               |    |

| Table II | Harmonics based on IEEE 519-2014 Standard     | 42 |

## List of Abbreviations

| <b>Abbreviation</b> | Description                             |

|---------------------|-----------------------------------------|

| AC                  | Alternating Current                     |

| CBF                 | Complex Band-pass Filter                |

| DC                  | Direct Current                          |

| DDSRF-PLL           | Decoupled DSRF-PLL                      |

| DSC-PLL             | Delayed Signal Cancellation based PLL   |

| DSOGI-PLL           | Dual SOGI-PLL                           |

| DSRF-PLL            | Double SRF-PLL                          |

| DVR                 | Dynamic Voltage Restoration             |

| EPLL                | Enhanced PLL                            |

| FACTS               | Flexible AC Transmission System         |

| FFPS                | Fundamental Frequency Positive Sequence |

| FIFO                | First-In-First-Out                      |

| ISC                 | Instantaneous Symmetrical Component     |

| LPN                 | Low-Pass Notch                          |

| LVRT                | Low Voltage Ride Through                |

| OSG                 | Orthogonal Signal Generator             |

| PI                  | Proportional Integral                   |

| PLL                 | Phase-Locked Loop                       |

| PSC                 | Positive Sequence Calculation           |

| <b>Abbreviation</b> | Description                         |

|---------------------|-------------------------------------|

| PV                  | Photo Voltaic                       |

| PWM                 | Pulse-Width Modulation              |

| SOGI                | Second-Order Generalized Integrator |

| SRF                 | Synchronous Reference Frame         |

| STATCOM             | Static Synchronous Compensator      |

| THD                 | Total Harmonic Distortion           |

| UPS                 | Uninterrupted Power Supply          |

| VCO                 | Voltage-Controlled Oscillator       |

# List of Symbols

| <u>Symbol</u>                        | Nomenclature                                                                                            |

|--------------------------------------|---------------------------------------------------------------------------------------------------------|

| $v_a, v_b, v_c$                      | Instantaneous voltage of the $a$ , $b$ , and $c$ phase respectively                                     |

| <i>va1</i> , <i>vb1</i> , <i>vc1</i> | Maximum amplitude of <i>v</i> <sub>a</sub> , <i>v</i> <sub>b</sub> , <i>v</i> <sub>c</sub> respectively |

| $v_a^R$ , $v_b^R$ , $v_c^R$          | Reformed instantaneous voltage of the $a, b$ , and $c$ phase respectively                               |

| $v_{\alpha}, v_{\beta}$              | Voltage components on $\alpha$ - $\beta$ orthogonal axis respectively                                   |

| $v_d, v_q$                           | Direct axis and quadrature axis voltage components                                                      |

| A, B, q, c                           | Multiplication factors                                                                                  |

| t                                    | Time                                                                                                    |

| Wo                                   | Nominal value of the grid voltage fundamental frequency                                                 |

| (U) <sub>VCO</sub>                   | Free running frequency of the Voltage Controlled Oscillator                                             |

| $\Delta \boldsymbol{\omega}$         | Fundamental frequency deviation from nominal value                                                      |

| $\omega_i$                           | Angular frequency of the input                                                                          |

| (I)e                                 | Estimated value of the grid voltage fundamental frequency                                               |

| $arphi_o$                            | Phase of the signal at nominal frequency                                                                |

| φe                                   | Phase error                                                                                             |

| θ                                    | Phase-angle of the grid voltage                                                                         |

| $\Delta \theta_I$                    | Phase-angle deviation from the balanced phase-angle between phase $a$ and phase $b$                     |

| $\Delta \theta_2$                    | Phase-angle deviation from the balanced phase-angle between phase $a$ and phase $c$                     |

| <u>Symbol</u>           | Nomenclature                                                                                                                     |

|-------------------------|----------------------------------------------------------------------------------------------------------------------------------|

| $e_o(t)$                | Phase error signal                                                                                                               |

| Τ                       | Combined transfer function of Clarke and Park transformation                                                                     |

| H(s)                    | Transfer function of the loop filter of the PLL                                                                                  |

| K                       | Gain parameter of the loop filter                                                                                                |

| $K_p$                   | Proportional gain of the loop filter                                                                                             |

| Ki                      | Integral gain of the loop filter                                                                                                 |

| h                       | Order of the harmonics                                                                                                           |

| <i>h</i> <sub>max</sub> | Maximum order of the harmonic component prevailing at the voltage signal                                                         |

| Ν                       | Sampling index                                                                                                                   |

| $T_s$                   | Sampling period                                                                                                                  |

| $v_a^k$                 | Voltage signal of the <i>a</i> phase after <i>k</i> -th stage of filtering                                                       |

| $a_1^k$                 | Amplitude of the fundamental component of the voltage signal at $a$ phase after $k$ -th stage of filtering                       |

| $a_h^k$                 | Amplitude of the <i>h</i> -th harmonic component of the voltage signal at $a$ phase after <i>k</i> -th stage of filtering        |

| $v_a^{k''}$             | Double derivative of the voltage signal of the $a$ phase after $k$ -th stage of filtering                                        |

| $H_{h_{max}}(z)$        | Transfer function of a unit block of the harmonic attenuation system in <i>z</i> -domain to eliminate $h^{\text{th}}$ harmonics. |

| G                       | Gain constant of the unit block of harmonic attenuation system                                                                   |

| <u>Symbol</u>                                                                                 | Nomenclature                                                                                                  |

|-----------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------|

| H(z)                                                                                          | Transfer function of the harmonic attenuation system in z-domain.                                             |

| <i>x</i> <sub>b1</sub> , <i>x</i> <sub>b2</sub>                                               | Amplitudes of the reformed voltage of the <i>b</i> -phase calculated from the solution of quadratic equations |

| <i>x</i> <sub>c1</sub> , <i>x</i> <sub>c2</sub>                                               | Amplitudes of the reformed voltage of the <i>c</i> -phase calculated from the solution of quadratic equations |

| <i>e</i> <sub>1</sub> , <i>e</i> <sub>2</sub> , <i>e</i> <sub>3</sub> , <i>e</i> <sub>4</sub> | Error values of the sum of derived solution voltages of the three phases                                      |

This chapter starts by presenting the importance on phase-angle estimation in Section 1.1. Technical reviews of relevant works have been introduced in Section 1.2. Section 1.3 contains the objectives of this thesis work. The methodologies and the tools used for the research work have been presented in Section 1.4. Section 1.5 consists of the contribution of the research work and list of publications obtained from the thesis. Finally, the outline of the thesis is described in Section 1.6.

#### 1.1 Importance of Phase-Angle Estimation

The power system can be easily affected by the addition of non-linear loads [1]-[2]. The positive-sequence fundamental phase-angle of the utility voltage is a critical piece of information for the devices that are used in the operation of power conversion and conditioning applications. Hence, they need an accurate phase estimation scheme to work properly. The phase-angle information is often used to construct a reference carrier wave to synchronize the on/off commutations of power devices, calculate and control the flow of active/reactive power or transform the feedback variables to a reference frame suitable for control purpose.

Fast and accurate phase angle estimation is essential for the control of grid-connected power converters [3]-[6], flexible AC transmission systems (FACTS) [7]-[9], power line conditioners [10]-[12], regenerative drives [13]-[14], active power filters [15]-[16], uninterrupted power supplies [17]-[18], distributed generations [19]-[21] and energy storage systems [22]. The detected information of such a fundamental component, either in magnitude and phase angle or as a vector of the grid voltage and fundamental frequency, is used for the synchronization of converter output variables, for power flux calculations, and for the transformation of state variables into rotating frames.

Grid connected power converters convert DC current into AC current and provide real and reactive power to the grid [4],[6]. To calculate the amount of real power and reactive power to be injected into the power-grid by the power converters, the information on phase-angles of the phases of the power-system is required.

A power line conditioner improves the quality of the power that is delivered to electrical load/ equipment by refining the input signal and removing noise from the signal [11]. The information on the phase-angle of the signal is required in this regard.

In UPS system, it is necessary to guarantee proper synchronization between the inverter output voltage and the primary source voltage [18]. In parallel redundant UPS arrangements, a very precise synchronization is also required prior to each UPS connection to the protected bus in order to avoid catastrophic transients.

For applications involving load compensation, the DC to AC converter of the STATCOM is manipulated as a controlled current source [23]-[24]. The phase-angle information is required either to generate the reference current template or to synchronize the PWM voltage waveform with that of the utility.

Distributed generation system mainly includes wind and PV systems. These systems have some requirements and restrictions under faulty conditions in order to remain connected to the network. Such requirement are known as Low Voltage Ride Through (LVRT) [25]-[26]. Solutions based on the installation of STATCOMs and DVRs, as well as on advanced control functionalities for the existing power converters of distributed generation plants, have contributed to enhance their response under faulty and distorted scenarios and, hence, to fulfill these requirements. In order to achieve satisfactory results with such systems, it is necessary to count on accurate and fast grid voltage synchronization algorithm.

Weak, variable-frequency power system exists in small distributed generation island and in isolated mobile power systems [27]-[28]. Typically, multiple generators are attached to an AC bus and synchronized using phase detector that estimated the approximate system frequency and phase. Methods of synchronization similar to those used for generators are also applied to parallel power converters that are powered from DC sources. These AC power converters inherently rely heavily on phase detection to achieve and maintain synchronism since they do not have physical rotating inductance.

In all these applications, in order to maintain proper operation, the information on amplitude and phase-angle has to be obtained as fast and accurate as possible, which is even more challenging in the presence of disturbance in the utility voltage.

### 1.2 Literature Review

With the increasing applications of numerous grid-connected systems, phase-angle estimation has become a crucial aspect. A large number of researches have been conducted in this field, producing different techniques and methods.

Several open-loop based grid synchronization techniques are reported in the technical literature [29]-[32]. Some advanced techniques are based on Fourier transformation [10], [33], frequency locked loop [34]-[36], least-error squares [37]-[38], weighted least-square-estimation [39]-[41], notch filter [42]-[43], extended Kalman filter [44]-[46] and space vector filtering [47]-[48] etc. These techniques perform satisfactorily when the grid frequency is close to the nominal value. However, as the input frequency shifts, the deviation of frequency will deteriorate the performance of these techniques. Though, improvements are introduced and employed, the increase of dynamic recovery time and the too much computational complexity is always inevitable. A novel Fourier transformation based grid-synchronization method has been proposed in [10]. The grid phase-angle can be estimated properly and effectively by combining a frequency shifts, the LPN filter is to be modified accordingly. To incorporate with the adaptive regulation, a cascaded series of fourth-order LPN filters is needed, which is a complex system for grid synchronization and also requires very powerful processors.

Instead of open-loop based techniques, the closed-loop based phase-locked loops (PLL) are more preferable. Closed-loop based PLLs are the most widespread grid synchronization algorithms due to their simplicity and flexibility. Numerous PLLs have been proposed and developed. The basic scheme used in three-phase systems is the Synchronous Rotating Frame PLL (SRF-PLL) [49]–[55]. In SRF-PLL, the three-phase grid voltage is first transformed into synchronous rotating frame as direct axis and quadrature axis voltage component and then the phase-angle is estimated by feeding back and regulating the quadrature axis voltage component to zero. Under ideal sinusoidal grid conditions, the SRF-PLL performs effectively at a very high bandwidth, providing rapid and accurate phase angle estimation. However, if the input signal is distorted by three phase imbalances or harmonics, the bandwidth of the SRF-PLL needs to be reduced to perform proper filtering. Specially, to cancel the fundamental negative sequence from imbalances, which acts as a second order component and is located at the low frequency segment of  $v_q$ , the bandwidth should be dramatically reduced further to generate an acceptable result [62]-[65]. Advanced PLL schemes have been developed to achieve better performance. Most of these have been developed to extract the fundamental positive sequence from the primary voltage signal. In [62] and [63], double-SRF-PLL (DSRF-PLL) and decoupled DSRF-PLL (DDSRF-PLL) have been presented. The DDSRF-PLL applies two rotating synchronous reference frame, which have the same angular speed but in opposite directions for the rotation transformation and then a decoupling network is designed to extract the fundamental positive sequence of the grid voltage. SRF-PLL with a sinusoidal signal integrator have been proposed in [64] and a double second-order generalized integrator based PLL is proposed in [65]. These advanced PLLs have filtering stages within or before the control loop of SRF-PLL. Although, they exhibit excellent performances, these algorithms have too much computational complexity. Delayed signal cancellation based PLL (DSC-PLL) is documented in [66]-[70] to eliminate the negative-sequence component in unbalanced grids and also to cancel any given harmonics, but improper sampling rate or frequency shift of the system can result in error during estimation and also multiple digital signal processors are required to implement these complex algorithms.

Another important issue for the closed-loop based PLLs is system modeling. The scheme of advanced PLLs mostly put a specific filtering stage within or before the control loop of SRF-PLL, named in-loop filtering and pre-filtering. System modeling is always essential to design the filtering stage and to evaluate the performance of these PLLs. According to the reference frame, the system modeling can be carried out under natural (*abc*), stationary ( $\alpha\beta$ ) and synchronous (*dq*) reference frames. Modeling of these pre-filtering type PLLs mostly assume that the pre-filtering stage and the SRF-PLL as two independent entity. To improve the dynamic performance of these two segments, in [71] the author has developed an efficient approach to design the control parameters combining the SRF-PLL and the pre-filtering stage in a single entity. As to the in-loop filtering types, where the filtering stage is integrated, they are modeled as an entity.

A design oriented study of advanced SRF based in-loop filtering type PLLs has been demonstrated in [72]. Several PLLs are modeled and analyzed in detail, after which parameter design guidelines are provided. Similarly, on basis of system modeling, performance analysis and design guidelines of moving average filter based PLLs are illustrated in [73]. A PLL method consisting of a cascaded interconnection of two PLL schemes, named UH-PLL and conventional SRF-PLL is documented in [74]. A solution to eliminate the negative sequences of the three-phase unbalanced voltage waveforms is presented in [56]. It reforms the

unbalanced three-phase voltage system into a balanced one when only amplitudes are unbalanced. However, both the amplitude and phase imbalances may occur under unsymmetrical fault conditions [75]-[85] and the reported techniques are not suitable for accurate phase estimation in these conditions.

The presence of harmonics in grid-voltage is a major cause for inaccurate phase-angle estimation. Depending upon the phase-angle or frequency detection algorithm, harmonics are either completely eliminated or sufficiently attenuated. The use of active and passive low-pass filters are the conventional means of harmonics elimination. Several active filters [86]-[89] and passive filters [90]-[93] have been proposed for grid-connected converters and micro-grids to compensate for harmonics. But these filters will cause phase-delay of signal which is also dependent on the system frequency. Hence, these types of filters are not suitable for phase-angle or frequency estimation of harmonic affected signals. In [94], a delta-connected filtering winding has been used for harmonic elimination. An adaptive delay bank filter has been proposed in [95] for SRF-PLL. In [96], a PI controller based shunt active filter has been claimed useful for harmonic elimination. These filters cause phase-shift of their input signals. For accurate phase-angle detection under harmonic affected condition, it is necessary to develop a suitable algorithm to either eliminate or attenuate the harmonic components before they are processed for phase-angle estimation.

### 1.3 Objectives of the Thesis

The primary objective of this thesis is develop a new PLL algorithm based on three-phase SRF-PLL under the amplitude and phase imbalances in the three-phase grid voltage including harmonics. A conventional SRF-PLL is not able to estimate the phase-angle accurately if any form of distortion and imbalance is present. This thesis aims at increasing the over-all performance under such circumstances.

This thesis aims at developing a signal reforming algorithm that can reform the three-phase unbalanced grid-signal with amplitude and phase imbalances into the three-phase balanced signal without discarding the information on amplitude and phase-angle of the original voltage signal. By reforming the unbalanced signal into a balanced one, the reformed signal can be made suitable for ordinary SRF-PLL.

The thesis also aims at developing a relatively simple algorithm for harmonics attenuation suitable for the SRF-PLL. Use of traditional filter for harmonics elimination alters the phase-angle of the filtered signal, which causes error in phase-angle estimation. On the other hand, if it is possible to reduce the amount of harmonics without altering the phase-angle, it can assist the signal reforming algorithm. Hence, it has become another objective of this thesis.

In a summary, this thesis aims at improving the performance of the three-phase PLL by developing a signal reforming and a harmonics attenuating algorithm and combining them with a conventional SRF-PLL.

#### 1.4 Thesis Methodology

The thesis has been conducted by following a step by step set of methodologies. At first, a three-phase SRF-PLL has been developed in MATLAB/Simulink environment. Then, the frequency adaptive harmonics attenuation algorithm has been mathematically developed and implemented to reject the negative effects caused by the harmonics. The IEEE standard 519-2014 [97] has been followed for setting up the specification for the harmonics. European standard EN50160 [98] has also been followed for some cases. The signal reforming algorithm has been mathematically derived and simulated to obtain a balanced three-phase voltage system from an unbalanced one. The phase angle imbalance information between two phases has also been extracted using this algorithm. The phase detector of the PLL has been implemented based on the Clark and Park transformations [99]. A proportional and integral controller has been used as the loop filter. The fundamental frequency obtained from the output of the loop filter has been integrated to obtain the phase angle of the reference phase voltage. One sine and one cosine function have been used as the oscillators. The performance of the PLL has been investigated under different grid events such as voltage sag, voltage swell, frequency step, frequency jump, phase jump etc. The outputs at different stages of the PLL have been measured and error analyses have been performed. A conventional SRF-PLL reported in the technical literature has also been developed and the performance of it has been compared with the developed one.

### 1.5 List of Publications

The contributions of this research work have been published in peer reviewed international conferences. The list of these papers is as follows-

- [1] F. Sadeque, M. S. Reza and M. M. Hossain, "A signal reforming algorithm based threephase PLL under unbalanced grid conditions", in *Proceedings of IEEE International Conference on Renewable Energy Research and Applications (ICRERA)*, Birmingham, UK, 20-23 November, 2016, pp. 940-945.

- [2] F. Sadeque, M. S. Reza and M. M. Hossain, "Three-phase phase-locked loop for grid voltage phase estimation under unbalanced and distorted conditions", in *Proceedings* of *IEEE Power and Energy Conference at Illinois (PECI)*, Illinois, USA, 23-24 February, 2017, pp. 1-7.

### 1.6 Thesis Organization

The thesis entitled, 'A Signal Reforming Algorithm Based Three-Phase PLL under Unbalanced and Distorted Conditions in the Grid', is organized as follows-

*Chapter 1* introduces the necessity of phase angle estimation in the field of power system analysis and grid synchronization by presenting its significant contribution in numerous power system devices and utilities. The chapter also discusses some widely used and conventional means of phase-angle estimation introduced in different research works. Finally, it briefly discusses the objective of this thesis and the methodologies that have been carried out.

*Chapter 2* starts with the basic principle of phase-locked loop. Then, it briefly discusses on several PLL algorithms that are commonly used. A detailed discussion on conventional three-phase SRF-PLL has also been introduced here. Some simulation results have been provided here to demonstrate the performance of this PLL under different grid circumstances.

*Chapter 3* contains the detailed analysis of the developed PLL. The analysis includes basic design of the PLL structure, signal reforming and harmonics attenuation algorithm and the selection of proportional and integral gain parameters.

*Chapter 4* provides the simulation results to support the accuracy, efficiency and robustness of the developed PLL under different adverse grid voltage conditions.

*Chapter 5* concludes the thesis work by summarizing the achievement from this thesis work and providing suggestion on future work.

This chapter starts with the basic structure of phase-locked loop in Section 2.1. In Section 2.2 some commonly used single-phase and three-phase PLL algorithms have been discussed. The basic structure and working principle of the conventional three-phase SRF-PLL has been elaborately described and its performance under various circumstances have been demonstrated in Section 2.3.

### 2.1 The Basic Structure of Phase-Locked Loop

The Phase-locked loop (PLL) is one of the most efficient techniques for tracking phase-angle and frequency of a signal. It is widely used in power system devices and communication devices for phase-angle and frequency estimation. A PLL has three basic components-

- A voltage-controlled oscillator (VCO),

- A multiplier serving as phase detector or phase comparator, and

- A loop filter

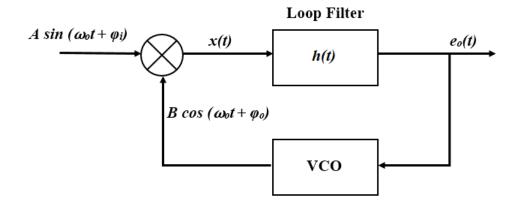

Figure 2.1: Block diagram of a Phase-Locked Loop.

Fig. 2.1 shows the block diagram of a typical PLL [100]. The operation of the PLL is similar to that of a feedback system. The signal fed back tends to follow the input signal. If the signal fed back is not equal to the input signal, a difference, known as error, will change the signal fed back until it is close to the input signal. In a PLL, the phase angle is fed back and compared

with the input signal. The VCO adjusts its own frequency until it is equal to that of the input signal. At that point, the frequency and the phase of the input and output signals are in synchronism, with or without a constant phase difference.

The voltage-controlled oscillator is an oscillator whose frequency can be controlled by an external voltage. In a VCO, the oscillation frequency varies linearly with the input voltage. If a VCO input voltage is  $e_o(t)$ , its output is a sinusoid of frequency  $\omega$  given by,

$$\omega(t) = \omega_{vco} + ce_o(t) \tag{1}$$

where, *c* is a constant of the VCO and  $\omega_{vco}$  is the free-running frequency of the VCO. The multiplier output is further low-pass-filtered by the loop filter and then applied to the input of VCO. This voltage changes the frequency of the oscillator and keeps the loop locked.

Let the input signal to the PLL be  $Asin(\omega_o t + \varphi_i)$ , and let the VCO output be a sinusoid  $Bcos(\omega_o t + \varphi_o)$ . The multiplier output x(t) is given by,

$$x(t) = ABsin(\omega_o t + \varphi_i)cos(\omega_o t + \varphi_o)$$

(2)

$$x(t) = \frac{AB}{2}\sin(\varphi_i - \varphi_o) + \frac{AB}{2}\sin(2\omega_o t + \varphi_i + \varphi_o)$$

(3)

$$e_o = \frac{AB}{2}\sin(\varphi_i - \varphi_o) \tag{4}$$

The last term on the right-hand side of (3) is suppressed by the loop filter of the PLL. Hence the other term is the value of  $e_o$ , which is an input to the VCO, where  $(\varphi_i - \varphi_o)$  is the phase error,  $\varphi_e$ . This phase error governs the locking of the two signals. The PLL tracks the input sinusoid and when the phase error is 0, the PLL is said to have locked the input signal and the output of VCO. The frequency and the phase angle can be directly derived from the output [101]-[103].

### 2.2 Commonly Used PLL Algorithms

Phase-Lock Loops are the most widely used algorithms for phase-angle and frequency estimation. Due to its increased popularity for fast operation, reliability and accuracy, numerous PLL algorithms have been developed. These PLLs can be categorized into two groups – single-phase PLLs and three-phase PLLs. Some commonly used PLL algorithms developed for power system parameter estimation are follows-

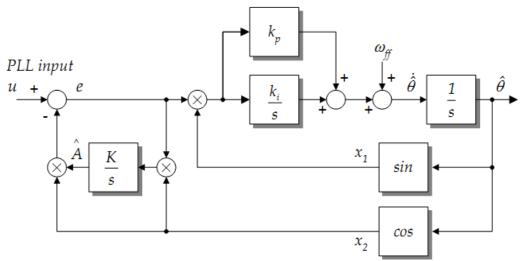

#### 2.2.1: Single-Phase Inverse Park PLL

Single phase inverse park PLL [104] is the most efficient phase-angle detection PLL algorithm. Fig. 2.2 shows the block diagram of a single phase PLL. The single phase inverse Park PLL transforms a voltage signal into two orthogonal components, commonly knowns as alpha-beta  $(\alpha - \beta)$  transformation on a stationary reference frame. The task is performed by the Orthogonal Signal Generator (OSG) block.

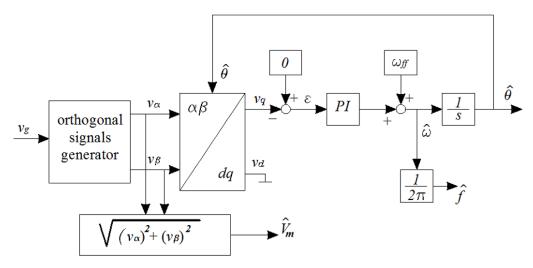

Figure 2.2: Block diagram of a single-phase PLL.

For the input signal  $v_g$ , the orthogonal components are,

$$v_{\alpha} = v_{g} \sin\theta; \ v_{\beta} = v_{g} \cos\theta \tag{5}$$

where,  $\theta = \omega_o t + \varphi_o$  is the phase-angle and  $\omega_o$  is the nominal angular frequency.

Then Park transformation [105] is applied on it to convert the stationary reference frame to a rotating reference frame. The direct axis (d) or quadrature axis (q) is then fed to a Proportional and Integral (PI) controller having a reference of zero. The PI controller output is integrated to get the estimated instantaneous phase-angle for the PLL output signal. The estimated phase angle gets synchronized with the instantaneous phase-angle of the utility grid once the q axis component is driven to zero.

There are various method to design the loop PI filter. The second-order loop is commonly used as good trade-off between the filter performance and the system stability. A filter with lower value of bandwidth produces a longer synchronization time. On the other hand, with a higher value of bandwidth, the filter is able to synchronize quickly, but with a possibility of distortions being added.

Although the single-phase PLL is accurate in phase-angle estimation, its algorithm is quite complex. Specially, the orthogonal signal generator require the use of transport delay to introduce a phase shift of 90 degree with respect to the fundamental frequency, which is a difficult to develop.

### 2.2.2: Single-Phase Second Order Generalized Integrator Based PLL

The structure of Second Order Generalized Integrator (SOGI) based PLL [106] differs from the Inverse Park based PLL in the way the orthogonal signal is produced. Fig. 2.3 shows the diagram of a single-phase SOGI based PLL. It has a simple structure based on the use of a double integrator and requires not only the grid voltage but also an angular frequency.

Figure 2.3: Block diagram of the single-phase SOGI based PLL.

The integrators represents two second-order filters with an adjustable bandwidth and resonance frequency equal to the frequency of the input signal. If the grid frequency is at the resonance frequency of the SOGI, the signal  $v_{\alpha}$  has the same phase and amplitude as the fundamental of the input signal and  $v_{\beta}$  is orthogonal to  $v_{\alpha}$ .

Therefore, the SOGI requires an adaptive tuning with respect to its resonance frequency. This can be achieved by using the frequency provided by the feedback control loop of the PLL structure; but in this way, the behavior of the whole PLL structure will be affected by the transients of the SOGI and the feedback control loop.

#### 2.2.3: Single-Phase Transport Delay PLL

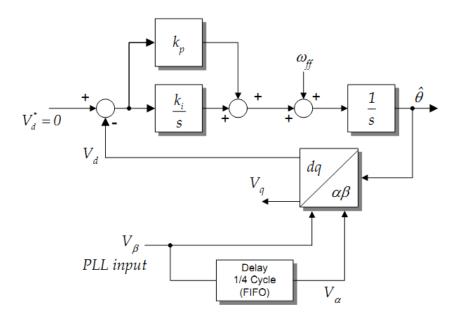

Fig. 2.4 shows the block diagram of the PLL-dq-FIFO [107]. It uses a first-in-first-out (FIFO) register to build the quadrature component for the dq transformation. Due to its fixed length delay, it is not able adjust the input voltage frequency during off-nominal condition, leading to phase angle estimation errors. An alternative way to generate the quadrature component is the Hilbert transformation. But it is very difficult to develop within the frequency range of 50-60 Hz.

Figure 2.4: Block diagram of single-phase transport delay PLL.

#### 2.2.4: Single-Phase Enhanced PLL

Fig. 2.5 shows the block diagram of the single-phase Enhanced PLL (EPLL). This PLL is based on adaptive filter theory [108]-[109]. Basically, it reconstructs, in real time, the fundamental component of the input signal by estimating its amplitude, phase and frequency through the steepest descent algorithm. In other words, this PLL has a non-linear phase detector. The gain K controls the convergence speed of the estimated amplitude.

Figure 2.5: Block diagram of single-phase enhanced PLL.

The adaptive filter theory is based on the idea that an output signal of a system can be reconstructed (or estimated) modifying the gains of a linear combiner as a function of an error, which in turn is the difference between the estimated signal and the systems output. In the EPLL context, the desired signal is the grid voltage, and the estimated signal is built with the estimated phase angle, as well as the inputs to the filter.

### 2.2.5: Three-Phase SRF-PLL

The three-phase synchronous reference frame PLL transforms the three-phase voltage signal into direct voltage component and quadrature voltage component by Clarke's and Park's Transformation [91] and then its phase angle is estimated by regulating the quadrature component to zero. Under ideal sinusoidal grid conditions, the SRF-PLL performs effectively at a very high bandwidth, providing rapid and accurate phase angle estimation. However, if the signals are distorted by phase imbalance or harmonics, the bandwidth of the SRF-PLL needs to be reduced to perform proper filtering. The details of SRF-PLL will be discussed at a later section.

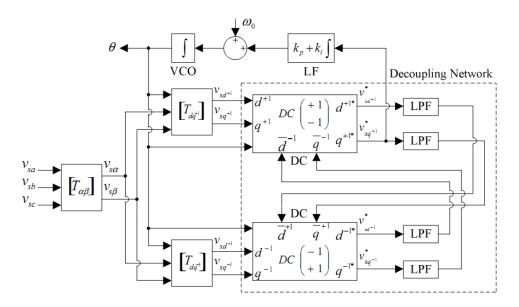

#### 2.2.6: Decoupled Double SRF-PLL

The DDSRF-PLL, published in [62]-[63], has been developed for improving the conventional SRF-PLL. Fig. 2.6 shows the block diagram. This synchronization system exploits two synchronous reference frames rotating at the fundamental utility frequency, one counter-clockwise and another one clockwise, in order to achieve an accurate detection of the positive and negative sequence components of the grid voltage vector when it is affected by unbalanced grid faults.

Figure 2.6: Block diagram of three-phase DDSRF-PLL.

When the three-phase grid voltage is unbalanced, the fundamental positive-sequence voltage vector appears as a DC voltage on the  $dq^{+1}$  axes of the positive-sequence SRF and as AC voltages at twice the fundamental utility frequency on the  $dq^{-1}$  axes of the negative-sequence SRF. In contrast, the negative-sequence voltage vector will cause a DC component on the negative-sequence SRF and an AC oscillation on the positive-sequence SRF. Since the amplitude of the oscillation on the positive-sequence SRF matches to the DC level on the negative-sequence SRF, and vice versa, a decoupling network is applied to signals on the dq positive/negative SRF axes in order to cancel out such ac oscillations. Low-pass filters (LPF) are used for extracting the DC component from the signal on the decoupled SRFs axes. These DC components collect information about the amplitude and phase-angle of the positive- and negative-sequence components of the grid voltage vector.

The PI controller of the DDSRF-PLL works on the decoupled *q*-axis signal of the positivesequence SRF and performs the same function as in a SRF-PLL, aligning the positive-sequence voltage with the *d*-axis. This signal is free of AC components due to the effect of the decoupling networks and the bandwidth of the loop controller can be consequently increased [21].

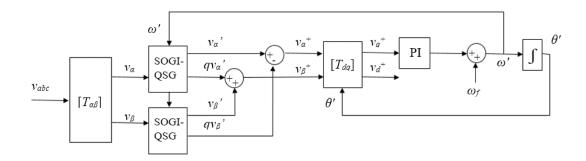

### 2.2.7: Dual Second Order Generalized Integrator PLL

The operation of the DSOGI-PLL for estimating the positive and negative-sequence components of the grid voltage vectors is based on using the Instantaneous Symmetrical Components (ISC) method on the  $\alpha\beta$  stationary reference frame, as explained in [93]. The ISC method is developed by the positive sequence calculation (PSC) block.

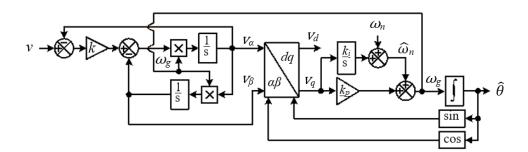

Figure 2.7: Block diagram of three-phase DSOGI-PLL.

To apply the ISC method, it is necessary to have a set of signals,  $v_{\alpha}$ - $v_{\beta}$ , representing the input voltage vector on the  $\alpha\beta$  stationary reference frame together with another set of signals,  $qv_{\alpha}$  and  $qv_{\beta}$ , which are in-quadrature and lagged with respect to  $v_{\alpha}$  and  $v_{\beta}$ . In the DSOGI-PLL, the signals to be supplied to the ISC method are obtained by using a dual second order generalized integrator (DSOGI). At its output, the DSOGI provides four signals, which are the filtered version of  $v_{\alpha}$ ,  $v_{\beta}$ ,  $qv_{\alpha}$ , and  $qv_{\beta}$ . A conventional SRF-PLL estimates the positive-sequence voltage vector,  $v^+_{\alpha\beta}$ , to make this synchronization system frequency adaptive. This voltage is translated to the rotating SRF and the signal on the *q*-axis is applied at the input of the loop controller and the fundamental grid frequency and phase-angle of the positive sequence voltage are estimated.

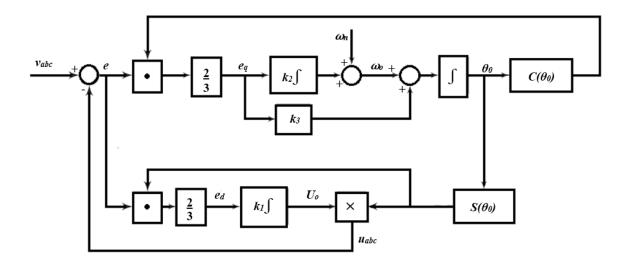

#### 2.2.8: Three-Phase Enhanced PLL

Fig. 2.8 shows the block diagram of a three-phase enhanced PLL (3EPLL). There are multiple extensions of the three-phase EPLL. An ordinary 3EPLL is equivalent to the SRF-PLL with the capability of accommodating various modifications due to its outer closed-loop feedback structure [110]. It can address the direct current component and harmonics within its loop structure.

Figure 2.8: Block diagram of three-phase EPLL.

Each phase voltage is processed independently by the EPLL. This block filters the input signal and generates two sinusoidal outputs of the same amplitude and frequency, where the later one is led by 90 degree. The resulting signals constitute the input for the computational unit. Finally, the instantaneous positive-sequence voltage component can be estimated by means of using the ISC method.

### 2.3 The Conventional Three-Phase SRF-PLL and Its Performance

The conventional SRF-PLL transforms the three-phase sinusoidal voltage signal, denoted by  $v_a$ ,  $v_b$  and  $v_c$  and expressed as in (6), into the direct axis component and quadrature axis component,  $v_d$  and  $v_q$ , under synchronous rotating reference frame through the rotating transformation. The transfer function, T is the combination of Clarke Transformation and Park Transformation [91] relating  $v_a$ ,  $v_b$  and  $v_c$ , with  $v_d$  and  $v_q$  through (7) and is defined in (8).

$$\begin{bmatrix} v_a \\ v_b \\ v_c \end{bmatrix} = \begin{bmatrix} \sin(\omega_o t + \varphi_o) \\ \sin(\omega_o t + \varphi_o - \frac{2\pi}{3}) \\ \sin(\omega_o t + \varphi_o + \frac{2\pi}{3}) \end{bmatrix}$$

(6)

$$\begin{bmatrix} v_q \\ v_d \end{bmatrix} = [T] \begin{bmatrix} v_a \\ v_b \\ v_c \end{bmatrix}$$

(7)

$$T = \frac{2}{3} \begin{bmatrix} \cos(\theta) & \cos\left(\theta - \frac{2\pi}{3}\right) & \cos\left(\theta + \frac{2\pi}{3}\right) \\ -\sin(\theta) & -\sin\left(\theta - \frac{2\pi}{3}\right) & -\sin\left(\theta + \frac{2\pi}{3}\right) \end{bmatrix}$$

(8)

$\theta = \omega_o t + \varphi_o \tag{9}$

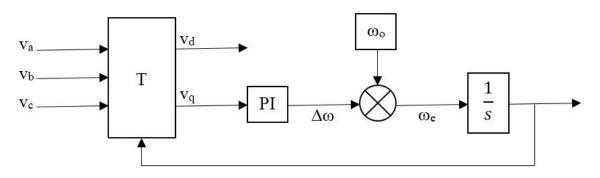

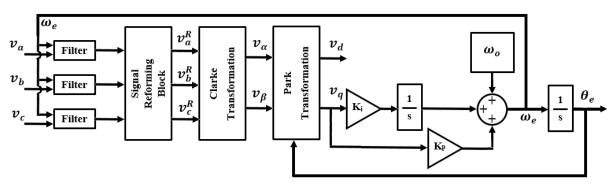

Figure 2.9: Block diagram of the conventional SRF-PLL.

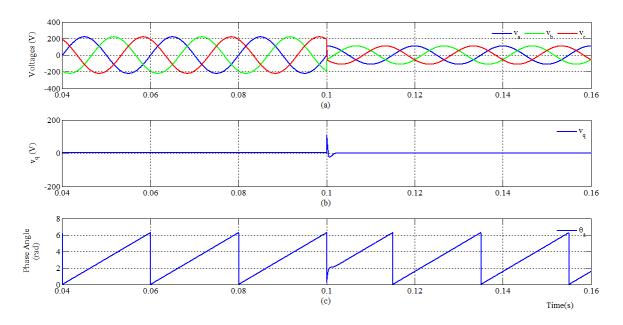

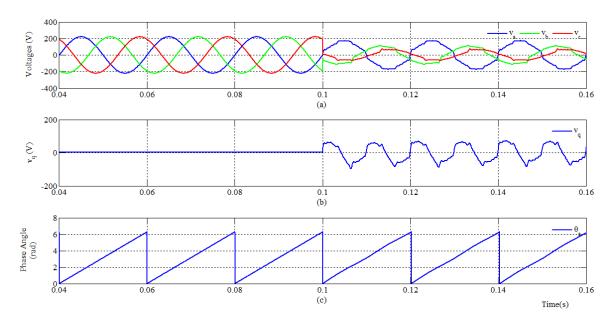

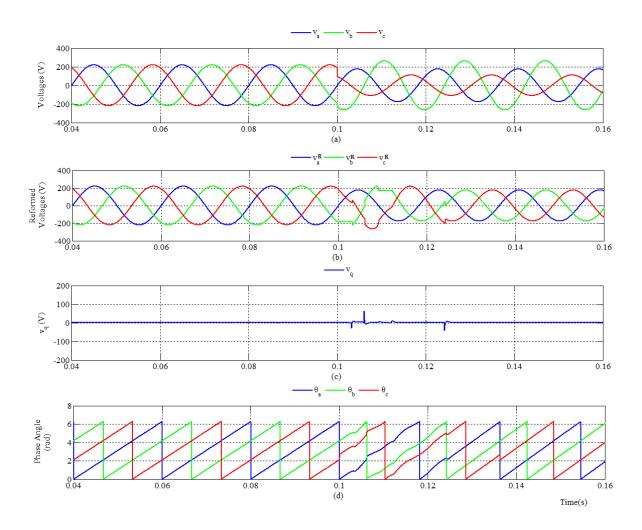

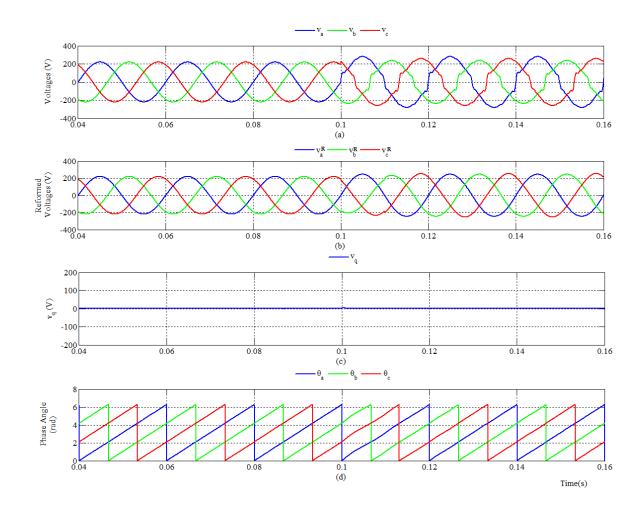

Fig. 2.9 shows the block diagram of the conventional SRF-PLL, where  $\omega_0$  is the nominal value of the grid voltage fundamental frequency,  $\Delta \omega$  is the fundamental frequency deviation from its nominal value and  $\omega_e$  is the estimated value of the grid voltage fundamental frequency. Eventually,  $\omega_e$  becomes equal to the fundamental frequency of the grid voltage at steady state. The value of  $v_q$  is regulated to zero and the phase angle of the grid voltage,  $\theta$  is estimated. It is also the phase angle for rotating transformation in (8) and is expressed as in (9). The conventional SRF-PLL can track the phase-angle of a three-phase system quickly and accurately at a very high bandwidth under balanced sinusoidal grid condition. It can estimate the phase-angle properly even when there is a sudden amplitude step or/and phase-angle shift. Fig. 2.10 shows the performance of the conventional SRF-PLL under 50% amplitude step and  $\pi/2$  radian phase-angle shift of all the three phases at 0.1 second. The gain parameters of the proportional integral (PI) controller have been adjusted to maintain a higher value of bandwidth. The proportional gain,  $K_p$  has been set to 50 and the integral gain,  $K_i$  has been set to 98696. The  $v_q$  versus time curve in Fig. 2.10(b) shows that the value of quadrature component suddenly became unstable at the time of fault and then quickly became stabilized to zero within 3ms. It means, the response time of the conventional SFR-PLL is around 3ms. The estimated phase angle of phase-a is shown in Fig. 2.10(c).

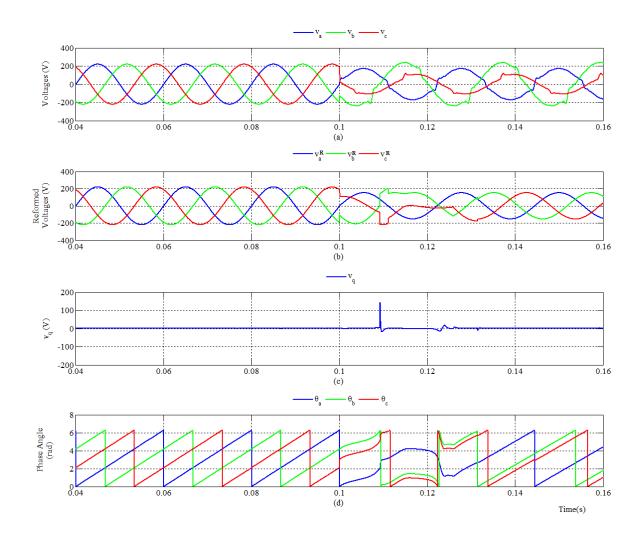

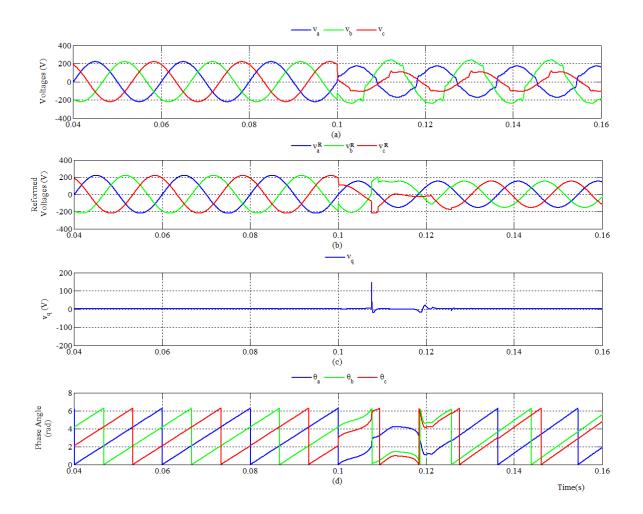

Figure 2.10: Performance of the conventional SRF- PLL under symmetrical fault conditions (50% amplitude step,  $\pi/2$  phase jump) at high bandwidth. (a) three-phase voltage waveforms; (b)  $v_q$  versus time; (c) estimated phase angle of  $v_a$ .

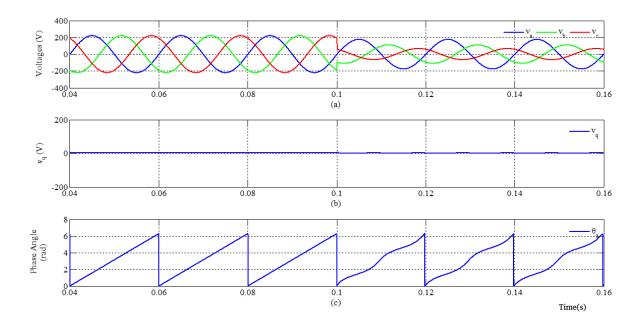

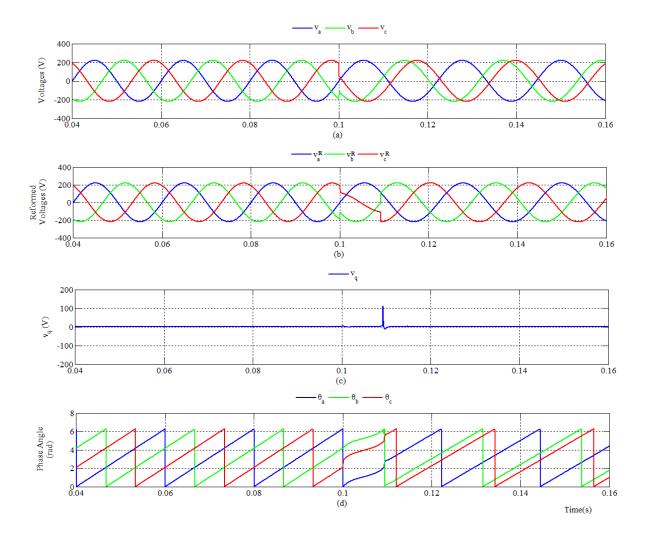

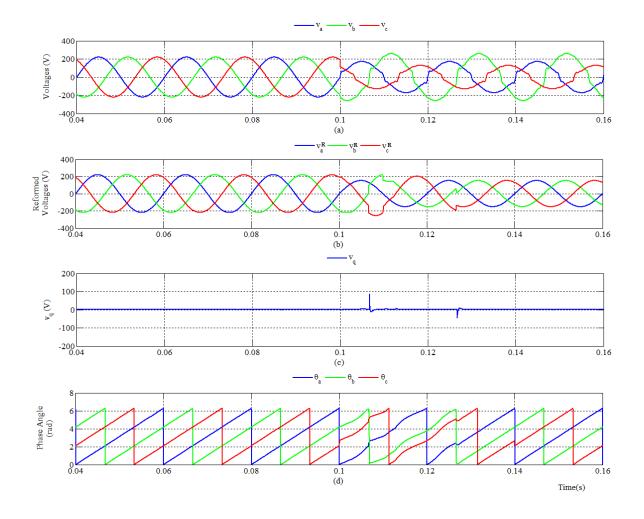

Fig. 2.11 shows the performance of the conventional SRF-PLL at high bandwidth when the amplitudes of the three-phases have different amplitude jumps. In this simulation the amplitudes of the three-phases,  $v_a$ ,  $v_b$  and  $v_c$  have changed to 80%, 50% and 30% of their original values respectively at 0.1 second. However, the phase angle differences between the three phases have been kept unaltered as in their balanced state. The phase-difference between them remained  $2\pi/3$  radian. Fig. 2.11(b) shows the value of  $v_q$  has become slightly unstable after the fault. The effect is also displayed on Fig. 2.11(c). It shows that the conventional SRF-PLL cannot estimate the phase-angle of a three-phase system when the amplitudes of the phases are not equal despite being the phase-angle differences have been unaltered.

Figure 2.11: Performance of the conventional SRF- PLL under only unequal amplitudes of the phases at high bandwidth (a) three-phase voltage waveforms; (b)  $v_q$  versus time; (c) estimated phase angle of  $v_a$ .

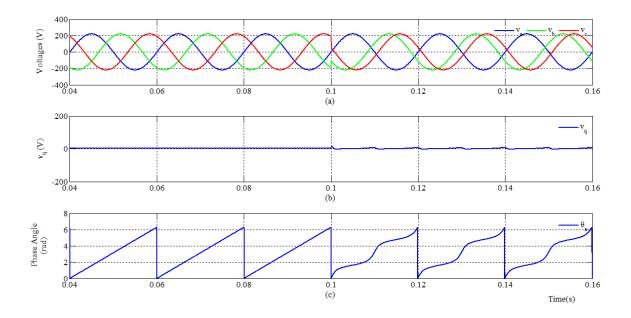

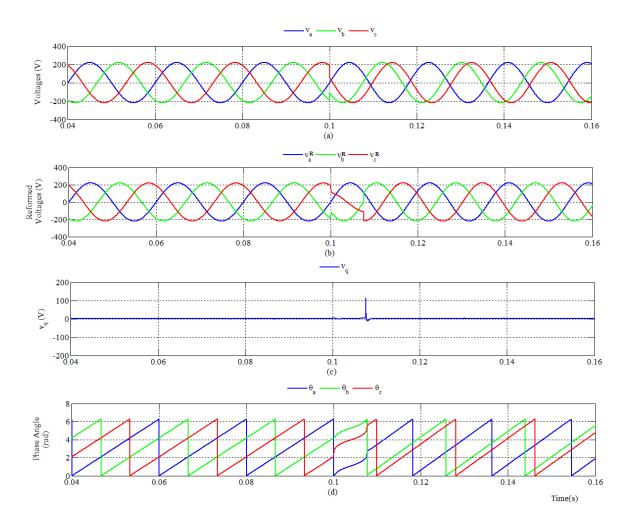

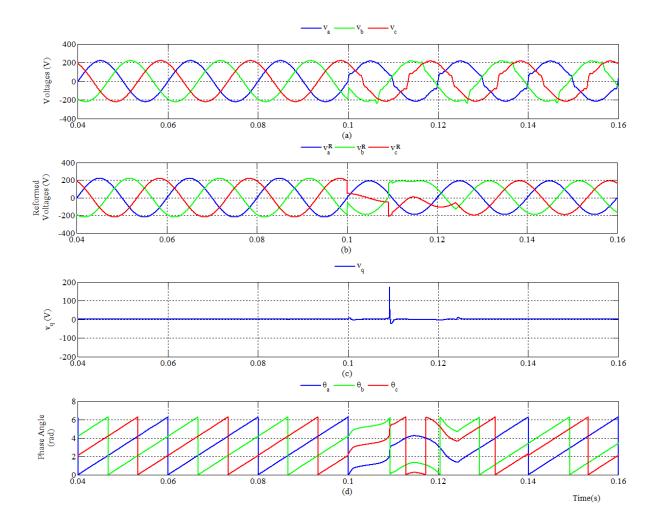

The conventional SRF-PLL has been tested for the unbalanced conditions when the amplitudes of the three-phases are equal while the phase-angle differences between the phases have been altered. Fig. 2.12 gives the outcome of the same SRF-PLL operated under such unbalanced condition. Here, the phase-*b*, denoted by  $v_b$  suffers a clockwise phase shift of  $\pi/6$  radians and the phase-*c*,  $v_c$ , suffers a counter-clockwise phase-shift of  $\pi/4$  radians. Meanwhile, the amplitudes of the three-phases have remain equal. This unbalanced conditions have been triggered at 0.1 second of simulation. Fig. 2.12(b) shows the  $v_q$  vs time curve, which has a noticeable amplitude variation of  $v_q$ . The phase-angle estimation is shown in Fig. 2.12(c).

Figure 2.12: Performance of the conventional SRF- PLL under only unequal phase difference between the phases at high bandwidth (a) three-phase voltage waveforms; (b)  $v_q$  versus time; (c) estimated phase angle of  $v_q$ .

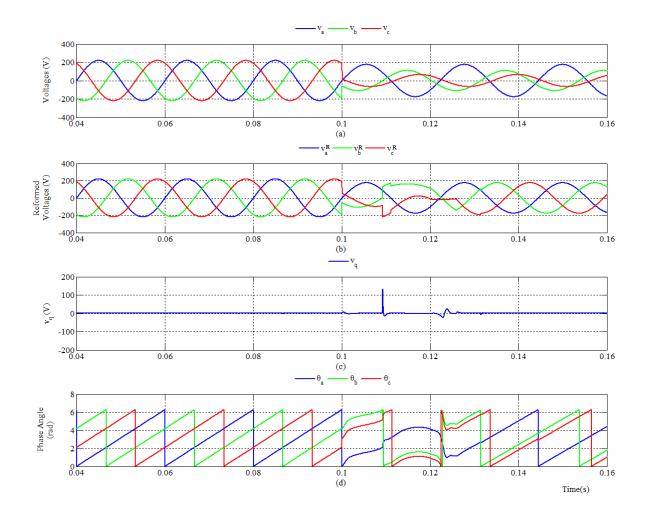

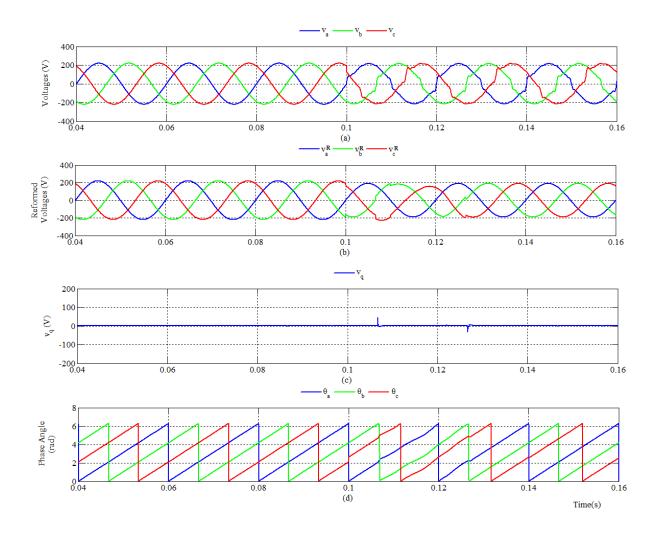

Fig. 2.13 shows the performance of the conventional SRF-PLL under both unequal amplitudes and unequal phase angle differences in between the three phases. Here, the amplitude of  $v_a$ ,  $v_b$ and  $v_c$  have become 80%, 50% and 30% of their original values respectively at 0.1 second. Also, the two phases have shifted away by  $\pi/6$  and  $\pi/4$  radians respectively from phase-*a*. Fig 2.13 show that, the amplitude of  $v_q$  is not stabilized to zero and the estimated phase angle is also incorrect.

Figure 2.13: Performance of the conventional SRF-PLL under both unequal amplitude and unequal phase differences between the phases at high bandwidth (a) three-phase voltage waveforms; (b)  $v_q$  versus time; (c) estimated phase angle of  $v_a$ .

Although the conventional three-phase SRF-PLL is not successful in any form of imbalances in the three phases (either amplitude or/and phase angle difference imbalance), the PLL works perfectly under undistorted grid condition at high bandwidth. However, three-phase systems are often affected by harmonics. Even with a balanced system, the harmonic components are responsible for the failure of its phase-angle estimation process. Under such distorted conditions, the SRF-PLL can still be developed to accurately estimate the phase-angle at reduced bandwidth to perform proper filtering by the PI controller of the PLL. Fig 2.14 and Fig 2.15 show the performance of the SRF-PLL under harmonics affected conditions at high and at reduced bandwidth respectively. For both the cases, the values of the harmonics components are set from the limit of IEEE 519-2014 standard. Also, for both the cases, the three phases have 50% amplitude step and  $\pi/2$  radian phase jump.

Figure 2.14: Performance of the conventional SRF- PLL under symmetrical fault conditions with harmonics (50% amplitude step,  $\pi/2$  phase jump) at high bandwidth. (a) three-phase voltage waveforms; (b)  $v_q$  versus time; (c) estimated phase angle of  $v_a$ .