Development of a Simulator for Transition Metal Dichalcogenide Channel Field Effect Transistors Incorporating Quantum Mechanical Effects

A thesis submitted to the

Department of Electrical and Electronic Engineering (EEE)

of

Bangladesh University of Engineering and Technology (BUET)

In partial fulfillment of the requirement for the degree of

MASTER OF SCIENCE IN ELECTRICAL AND ELECTRONIC ENGINEERING

by

Md. Shafiqul Islam

(Roll No.: 1015062210 P)

DEPARTMENT OF ELECTRICAL AND ELECTRONIC ENGINEERING (EEE)

BANGLADESH UNIVERSITY OF ENGINEERING AND TECHNOLOGY (BUET)

APRIL 2018

The thesis titled "Development of a Simulator for Transition Metal Dichalcogenide Channel Field Effect Transistors Incorporating Quantum Mechanical Effects" submitted by Md. Shafiqul Islam, Roll No.: 1015062210 P, Session: October 2015, has been accepted as satisfactory in partial fulfillment of the requirement for the degree of MASTER OF SCIENCE IN ELECTRICAL AND ELECTRONIC ENGINEERING on April 07, 2018.

#### **Board of Examiners**

1. Chairman Dr. Quazi Deen Mohd Khosru (Supervisor) Professor & Head Department of EEE, BUET, Dhaka. 2. Member Dr. Quazi Deen Mohd Khosru (Ex-officio) Professor & Head Department of EEE, BUET, Dhaka. 3. Member Dr. Md. Kawsar Alam Associate Professor Department of EEE, BUET, Dhaka. navid 4. Member Dr. Md. Zunaid Baten Assistant Professor Department of EEE, BUET, Dhaka. Tall to Me 5. Member Dr. Zahid Hasan Mahmood (External) Professor Department of EEE University of Dhaka Dhaka-1000.

Declaration

It is hereby declared that this thesis or any part of it has not been submitted elsewhere for the award of any degree or diploma.

Signature of the candidate

Md. Shafiqul Islam

(Roll No.: 1015062210 P)

## Dedication

to my Family

### Acknowledgements

All praise goes to the Almighty for giving me the patience and drive required to complete my M.Sc. research and finish the dissertation in due time.

I would like to convey my heart-felt gratitude and thanks to my thesis supervisor Dr. Quazi Deen Mohd Khosru, Professor & Head of the Department of Electrical and Electronic Engineering, Bangladesh University of Engineering and Technology, for his generous help, edifying suggestions and well-defined guidance throughout the thesis work. He was there with his kind help and direction anytime I was in need of them. His passion and dedication to academic research has motivated me to push my boundaries harder and excel at my research work, which I believe will inspire me to be a better researcher in future days to come. It was a great pleasure to be a part of his research group and work under his supervision.

I would also like to express my appreciation to the members of my thesis committee, Dr. Md. Kawsar Alam, Dr. Md Zunaid Baten and Dr. Zahid Hasan Mahmood, for taking the time to evaluate my work and provide insightful suggestions.

I want to express my gratitude to all the faculty members and my course teachers for their continuous help and guidance throughout the course of my M.Sc. program. I also thank my family members, without whose support and encouragement, it would be impossible to carry on with my study smoothly.

Finally, I want to express my gratitude to the Almighty for all the favors, material and nonmaterial, He has provided me with.

### Abstract

In recent years, Transition Metal Dichalcogenides (TMDs) have gained broad interest as the channel materials of Field Effect Transistors (FETs) after the development of fabrication and growth of two dimensional (2D) materials. Suitable bandgap, dangling bond free interfaces and atomic scale thickness make TMD materials, like Molybdenum disulphide (MoS<sub>2</sub>) and Tungsten diselenide (WSe<sub>2</sub>), attractive for switching and logic devices. A robust simulator with quantum mechanical effects of 2D FETs will be a promising addition to the existing literature and will pave the way to explore the sub-10nm technology in near future. In this thesis work a computationally efficient simulator considering the quantum mechanical effects of TMD FETs has been developed by using only MATLAB. Schrödinger-Poisson equations are solved self-consistently using material parameters extracted from literature. The numerical simulator has been used to study the transport performance of a monolayer WSe<sub>2</sub> FET structure with 20 nm of channel length. The performance analysis revealed excellent on and off state performances of the device with an impressive ON/OFF current ratio of ~ $10^6$ , on current of 547  $\mu$ A/ $\mu$ m, and subthreshold swing of 85.27mV/dec. To show the compatibility with circuit level simulation performance, analysis of monolayer MoS<sub>2</sub> channel TMD FETs has also been presented. Finally, the optimal structure with greatest performance for the device has been proposed.

## **Table of Contents**

| Declarationii                                                       |

|---------------------------------------------------------------------|

| Dedicationiv                                                        |

| Acknowledgementsv                                                   |

| Abstractvi                                                          |

| Table of Contentsvii                                                |

| List of Figuresix                                                   |

| List of Tablesxi                                                    |

| Chapter 1 Introduction1                                             |

| 1.1 Transition Metal Dichalcogenide channel FETs                    |

| 1.2 Motivation for choosing WSe <sub>2</sub> and MoS <sub>2</sub> 4 |

| 1.3 Atomistic Simulation of WSe <sub>2</sub> and MoS <sub>2</sub> 4 |

| 1.4 Analytical Modeling                                             |

| 1.5 Fabrication7                                                    |

| 1.6 Objectives of the Thesis                                        |

| 1.7 Thesis Overview                                                 |

| Chapter 2 Quantum Mechanical Simulation10                           |

| 2.1 Device Structure                                                |

| 2.2 Self-Consistent Simulator                                       |

| 2.2.1 Poisson Solver11                                              |

| 2.2.2 Schrödinger Equation Solver14                                 |

| 2.2.2.1 System Hamiltonian Matrix [H]15                             |

| 2.2.2.2 Eigen States                                                |

| 2.2.3 NEGF Formalism for the Transport Simulation                   |

| Chapter 3 Results and Discussion                            |    |

|-------------------------------------------------------------|----|

| 3.1 WSe <sub>2</sub> Channel FET                            | 22 |

| 3.1.1 Parameter Extraction for WSe <sub>2</sub> channel FET | 26 |

| 3.2 Simulator Validation and Efficiency                     |    |

| 3.3 MoS <sub>2</sub> channel FET                            |    |

| 3.3.1 Parameter Extraction for MoS <sub>2</sub> channel FET |    |

| Chapter 4 Conclusion and Future Works                       |    |

| 4.1 Conclusion                                              |    |

| 4.2 Limitations and Suggestion for Future Works             |    |

| References                                                  |    |

## **List of Figures**

| Fig. 1.1  | The transistor count of each major Intel x86 chip family [2] 1                           |

|-----------|------------------------------------------------------------------------------------------|

| Fig. 1.2  | ITRS roadmap [6] for transistor                                                          |

| Fig. 2.1  | 2D cross section of the monolayer WSe <sub>2</sub> channel FET [68] 11                   |

| Fig. 2.2  | Simple 1D structure of the atom in the solid. The basis function is localized            |

|           | around a particular atom 16                                                              |

| Fig. 2.3  | Dispersion Relation 17                                                                   |

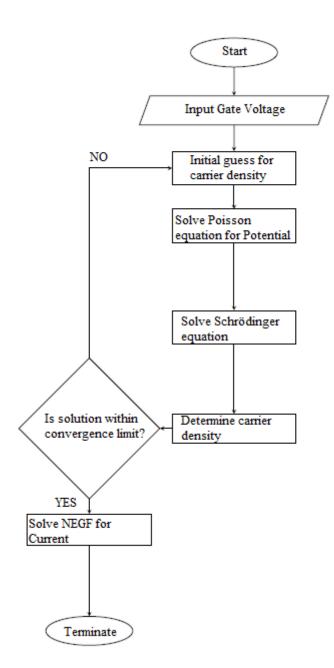

| Fig. 2.4  | Algorithm for self-consistent solution 24                                                |

| Fig. 3.1  | First subband energy profile across the channel at a fixed gate bias of $V_{gs}$ =       |

|           | 0.4 V with $V_{ds} = 0.0$ V to 0.4 V with an interval of 0.1 V 23                        |

| Fig. 3.2  | First subband energy profile across the channel at a fixed drain bias of $V_{\text{ds}}$ |

|           | = 0.4 V with $V_{gs}$ = 0.2 V to 1.0 V with an interval of 0.2 V 23                      |

| Fig. 3.3  | 2D electron density along the device                                                     |

| Fig. 3.4  | 3D electron density for $V_{ds} = 0.4$ V and $V_{gs} = 0$ V                              |

| Fig. 3.5  | I-V characteristics                                                                      |

| Fig. 3.6  | I <sub>DS</sub> vs V <sub>GS</sub>                                                       |

| Fig. 3.7  | V <sub>th</sub> calculation                                                              |

| Fig. 3.8  | Determination of ON/OFF current ratio                                                    |

| Fig. 3.9  | Determination of Subthreshold Swing 27                                                   |

| Fig. 3.10 | Drain current of Monolayer WSe2 channel FET by our simulator, Khan et                    |

|           | al [83] and Yoon et al [84] at the gate bias from 0.2 V to 0.6 V with an                 |

|           | interval of 0.2 V                                                                        |

| Fig. 3.11 | Drain current of Monolayer MoS2 channel FET by our simulator, Yadav et                   |

|           | al [85] at the gate bias from 0.2 V to 0.8 V with an interval of 0.2 V 29                |

| Fig. 3.12 | Sparsity of Jacobian Matrix                                                              |

| Fig 3.13  | Convergence Profile                                                                      |

| Fig 3.14  | I-V characteristics of MoS <sub>2</sub> channel FET31                                    |

| Fig. 3.15 | V <sub>th</sub> calculation for MoS <sub>2</sub> channel FET32                           |

| Fig. 3.16 | ON/OFF current ratio of MOS <sub>2</sub> channel FET 32                                  |

| Fig. | 3.17 | SS for the $MoS_2$ | channel FET3 | 3 |

|------|------|--------------------|--------------|---|

|------|------|--------------------|--------------|---|

## **List of Tables**

| Table 4.1 Device Parameters obtained from the Simulator         3 |

|-------------------------------------------------------------------|

|-------------------------------------------------------------------|

# Chapter 1 Introduction

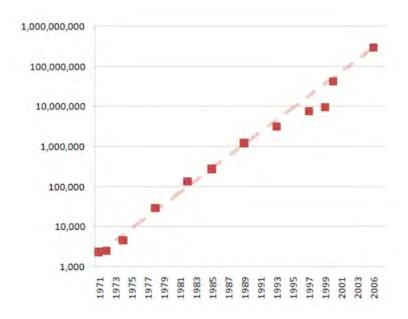

Ever since the pristine era of metal oxide semiconductor field effect transistor (MOSFET), scaling has been the primary driving force behind its unprecedented success. According to the figure 1.1, the prediction of "Moor's Law" [1], number of components per integrated chip will be doubled in every two years. This prediction was the guideline for the semiconductor industry to set their goals and made them push harder to break the technological boundaries through constant innovation.

Figure 1.1: The transistor count of each major Intel x86 chip family [2]

From 1975 to 2005, the early era of scaling, both dimension scaling and voltage scaling were the characteristics features. Dimension scaling allows the number of transistor per chip to increase by 1000000x and consequently their speed to increase by 1000x, and voltage scaling keeps the power density practically constant throughout this scaling regime [3]-[4]. However, around 2005, the voltage scaling almost stopped as further reduction in the supply voltage and hence the threshold voltage was leading to exponential increase in the OFF state current [5]. As a result the high clock speed and smaller device dimension caused heat to get trapped into the chip. To counter the heating problem the industry halted

the increase in clock speed and introduced multi-core processors to keep up with the Moore"s law.

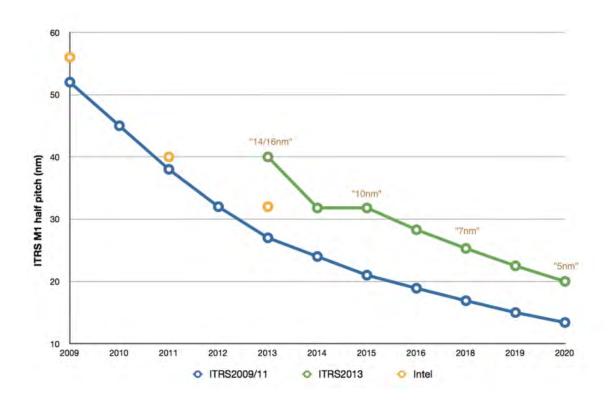

Figure 1.2: ITRS roadmap [6] for transistor.

With technology node goes down to 10 nm, 7 nm and eventually to 5 nm, to keep up with the Moore's law the physical gate length of the transistors needs to be shrunk as well. According to both ITRS 2009 and ITRS 2013 roadmap [6], by the year 2028 the physical gate length of transistors will be 5 nm (Figure 1.2) or below which means only around 10 Silicon atoms in the channel. Beyond 10 nm node Silicon channel transistors will not suffice to overcome the power dissipation and scaling challenges and new material and structures will be needed.

To overcome the requirement of small channel length and electrostatic and power challenges low dimensional nanotubes [7-8], nanowires [9-10], and very recently nanosheets [11-17], tunneling FETs [18-19], Si FinFETs [20], negative capacitance ferroelectric FETs [21], excitonic FETs [22], spin based FETs [23-24] are considered as the promising replacement of Si-CMOS devices. Among all these, monolayer Transition Metal Dichalcogenide (TMD) materials are receiving significant attention as possible candidates for post-Si electronics owing to their ultra-thin body nature that allows aggressive channel length scaling and hence high performance.

#### **1.1 Transition Metal Dichalcogenide channel FETs**

After the successful preparation of grapheme, two dimensional (2D) materials have been examined intensively to obtain new stable 2D materials beyond graphene. Researches on 2D material include real world experiments where 2D materials have been prepared and analyzed, as well as computational and theoretical works where the stability and band structure of existing and hypothetical 2D materials have been computed. Demonstration of isolated 2D atomic plane crystals [25] from bulk crystals paves the way for experimental work on monolayer 2D materials. Both experiments and theoretical effort confirm that variety of 2D materials beyond graphene does or should exist and their electronic properties span the full range from metallic to insulating.

Single-layer materials consisting of atoms of one single element arranged in a hexagonal lattice are designated as X-enes. So far, graphene as well as its Si-, Ge-, and P-based counterparts silicone [26], germanene [27], and phosphorene [28] have been experimentally realized, and the band structure of stanene, the X-ene based on tin (Sn), has been calculated [29]. The crystallographic structure of the X-anes is closely related to that of the X-enes. They also possess a hexagonal lattice of carbon (graphane), silicon (silicane), germanium (germanane), or tin (stanane) atoms. However, their lattice atoms are additionally out of plane bonded to hydrogen atoms - this is frequently called hydrogenated. Graphane was predicted to exist in 2007 [30] and was produced experimentally shortly afterwards [31]. Recently, germanane could also be realized experimentally [32]. Most relevant for electronic applications is the fact that graphane, silicane, and germanane possess sizeable bandgaps. The Transition Metal Dichalcogenides (TMDs) constitute a group of materials consisting of a transition metal (elements of groups 4, 5, and 6 of the periodic table of elements) and a chalcogen i.e., sulfur (S), selenium (Se), or tellurium (Te). These transition metal and chalcogen elements form covalently bonded 2D layers of the type TMD (e.g., MoS<sub>2</sub>) with a hexagonal lattice. Single-layer TMDs consist of three atomic layers where a layer of transition metal atoms is sandwiched between two layers of chalcogen atoms. For example, single-layer MoS2 is composed of one layer of molybdenum atoms and two layers of sulfur atoms. Today, more than 40 different types of TMDs are known [33]. While many of them are metallic, those containing Mo and W (i.e., MoS<sub>2</sub>, WSe<sub>2</sub>, etc.) as well as several of the Hf-, Pd-, Pt-, and Zr-based TMDs are semiconductors with bandgaps of the order of 1-2 eV.10,45 It should be noted that TMDs occur in different polytypes 1T, 1T', 2H, and 3R, where T means trigonal, T'

distorted trigonal, H hexagonal, and R rhombohedral, and 1, 2, or 3 indicates the number of TMD layers in the unit cell [34-35] which have different properties. For example, the common 2H polytypes of the Mo- and W-based TMDs are semiconducting while their metastable counterparts of the 1T type are metallic [36].

#### **1.2 Motivation for choosing WSe<sub>2</sub> and MoS<sub>2</sub>**

In recent years, among the monolayer TMDCs, Molybdenum Disulphide (MoS<sub>2</sub>) and Tungsten Diselenide (WSe<sub>2</sub>), have gained broad interest as transistor channel materials [37-48]. Their high bandgaps and sub-1 nm thickness makes them the most suitable candidate for next generation low power transistors. Apart from the application in memory devices and microprocessors, flexibility, transparency, and pristine interfaces made TMDCs ideal candidates for display electronics [49] and bio/gas sensors [50-51]. The TMDC based FET has matured quite a lot over the years with the demonstration of large scale CVD growth technique [52] and demonstration of both n-type and p-type FETs based on MoS2 and WSe2 [53-54] FETs with record on-state and off-state performances. In addition, tremendous research efforts are being given to improve the performance of TMDC FETs addressing the residual issues like high contact resistances with source/drain metals, high interface trap density, low electron and hole mobility and inefficient air-stable doping methods [55].

#### **1.3** Atomistic Simulation of WSe<sub>2</sub> and MoS<sub>2</sub>

Monolayer WSe<sub>2</sub> and MoS<sub>2</sub> have different properties than bulk form. For example, monolayer sheet has different bandgap than the bulk one. So to get the desired TMDs with required properties atomistic simulation is necessary. Band structure of these materials provide necessary material properties. Density-Functional Theory (DFT) method can provide the properties of the material by determining the band diagram of the material. Simulation tools like Quantum Espresso [56] and Atomistix ToolKit (ATK) [57] can be used for the DFT simulation.

In 2013 Ramasubramaniam et al. [58] studied MoS<sub>2</sub> by using a combination of DFT and Monte Carlo simulations. They demonstrated the potential for engineering a new class of atomically thin dilute magnetic semiconductors based on Mn-doped MoS<sub>2</sub> monolayers.

In 2013 Duerloo et al. [59] employed DFT calculations to estimate the piezoelectric coefficients WSe<sub>2</sub> along with few other monolayer TMDCs. The study revealed that monolayer TMDCs possesses greater piezoelectric coefficients compared to commonly used Wurtzite piezoelectrics.

In 2014 Chang et al. [60] used an *ab initio* density functional theory based electronic structure method, they studied the effects of adatoms on the electronic properties of monolayer transition metal dichalcogenide  $MoS_2$ . For the most stable adatom positions, they characterized the emergence of adatom-induced electronic states including any dopant states.

In 2014 Yuan et al. [61] studied the spin–valley-coupled circular photogalvanic current generation in WSe<sub>2</sub> using VASP DFT package. They have demonstrated a spin-coupled valley photocurrent in a WSe<sub>2</sub> electric-double-layer transistor and found that the direction and magnitude of the current is dependent on the degree of circular polarization and external electric field.

In 2015 Allain et al. [62] used DFT calculations to show that, due to orbital overlap and reduced tunnel barriers, edge contacts lead to a shorter bonding distance than top contacts for both the monolayer and multilayer TMDs.

In 2015 Zhou et al. [63] investigated the phonon transport of monolayer WSe<sub>2</sub> employing DFT with the phonon Boltzmann transport equation. The study found that, compared to other 2D materials the monolayer WSe<sub>2</sub> has relatively lower thermal conductivity, which is attributed to its Debye frequency and heavy atom mass.

In 2015 Dai et al. [64] used DFT computations to study bandgap tunability of the multilayer WSe<sub>2</sub> sheets with the application of external electric fields. The study concluded that the bandgap of WSe<sub>2</sub> sheet decreases with the increment of the vertical electric field and gradually turns it metallic at about of 0.6–2.0 V/nm electric field, depending on the number of layers present in the sheet.

In 2016 Wang et al. [65] studied the detailed bond reconstructions that occur in S vacancies within monolayer MoS<sub>2</sub> using a combination of aberration-corrected transmission electron microscopy, DFT and multislice image simulations. Removal of a single S atom causes little perturbation to the surrounding MoS<sub>2</sub> lattice, whereas the loss of two S atoms from the same atomic column causes a measureable local contraction.

#### 1.4 Analytical Modeling

Analytical and compact modeling can give better insight into the operation of a device. For monolayer TMDCs classical transport models will not be appropriate because of the presence of high degree of confinement. The quantum model can be easily formulated by assuming that the potential drop at the ultrathin channel in the confinement direction is negligible. Also, the potential across the channel can be accurately approximated as a quadratic function of the dimension. Using this approximation and solving Schrödinger and Poisson equation analytically can give the surface potential profile and hence the current transport across the channel. For modeling threshold voltage only semiclassically approximated charge can be used to obtain simplified closed form equation. Once the primary analytical model is developed various secondary effects like Mobility Degradation and Interface Traps etc. can also be incorporated into the model.

In 2012 Jiménez et al. [66] presented a physics-based model for the surface potential and drain current for monolayer TMDC FET. The work took the 2D density-of-states of the monolayer TMDC and its impact on the quantum capacitance into account and modeled the surface potential. The authors further developed an expression for the drain current considering the drift-diffusion mechanism. The analytical expressions of surface potential and drain current derived in this work are applicable for both the subthreshold and above threshold regions of operation. Although the analytical model is benchmarked against a prototype TMDC transistor, it has some major limitations like non-scalability due to lumped capacitor network based intrinsic device characteristics and insufficient differentiation between Fermi potential (voltage) and electrostatic potential in the model.

In 2014 Cao et al. [67] presented an analytical I-V model for 2D TMDC FETs as well. The model takes physics of monolayer TMDCs into account and offers a single closed form expression for all three i.e. linear, saturation, and subthreshold regions of operation. The

authors also incorporated various non-ideal secondary effects like interface traps, mobility degradation, and inefficient doping in the model, although that resulted in current equations having an integral form instead of closed form. The compact analytical model has been benchmarked against both numerical device simulation and experimental result.

#### **1.5** Fabrication

Over the year many groups have experimentally demonstrated monolayer WSe<sub>2</sub> channel transistors. These work ranges from basic WSe<sub>2</sub> MOSFETs to advanced devices like WSe<sub>2</sub> based TFET, TMDC Heterostructure FET and so on. In this section few of those works have been introduced from the literature.

In 2012 Fang et al. [68] reported high performance p-type monolayer WSe<sub>2</sub> FET with chemically doped source and drain contacts and high- $\kappa$  gate dielectrics. The FET had a Si substrate with 270 nm SiO<sub>2</sub> bottom oxide, 17.5 nm ZrO<sub>2</sub> top gate dielectric and Pd metal gate. At room temperature, the monolayer transistors exhibited an effective hole mobility of ~250 cm<sup>2</sup>/V-s, subthreshold swing of ~60 mV/dec, and on-off current ratio of 106 with a channel length of 9.4  $\mu$ m.

In 2015 Movva et al. [69] demonstrated dual-gated p-type few-layer WSe<sub>2</sub> FET with high work-function Pt source/drain contacts, Pd top gate and a hexagonal boron nitride top-gate dielectric. The devices achieved hole mobility and on-off current ratio of 140 cm<sup>2</sup>/V-s and  $10^7$  respectively at room temperature. The WSe<sub>2</sub> layer is deposited on a SiO<sub>2</sub>/Si substrate with a effective channel length of 6 µm and supported a maximum drive current of 5 µA/µm at -5 V top gate bias voltage.

In 2014 Tosun et al. [70] demonstrated a CMOS inverter by implementing both n and ptype inverter on the same WSe<sub>2</sub> flake for the first time. In the p-FET, high work function Pt is used to inject hole at the source contact of WSe<sub>2</sub>. Whereas, the n-FET is formed by degenerately doping the Pt-WSe<sub>2</sub> contact by Potassium (K). Both the n and p-type FETs achieved an on-off current ratio of 104 and the DC gain of the inverter was measured to be greater than 12. The inverter had ZrO<sub>2</sub> top gate dielectric and 10 nm thick WSe<sub>2</sub> flake grown on SiO<sub>2</sub>/Si substarte. The effective channel length was 2 µm with a gate underlap and overlap at the source/drain contacts of n and p-FET respectively. In 2017 Zeng et al. [71] prepared exfoliated MoS<sub>2</sub> dispersions through a two-step liquid phase exfoliation process with N-methyl-pyrrolidone (NMP) and Isopropanol (IPA). The quality of the obtained MoS<sub>2</sub> flakes was characterized by transmission electron microscopy, scanning electron microscopy, UV–Vis spectroscopy and Raman spectroscopy. For charge transport analysis, bottom-gate thin film transistors (TFTs) based on exfoliated MoS<sub>2</sub> films were fabricated via spray coating technique.

#### **1.6 Objectives of the Thesis**

The objectives of this work are:

- i. To develop a self-consistent simulator for TMD FETs.

- ii. To present a comparative study of device parameters by considering different TMD materials using the developed simulator.

#### **1.7 Thesis Overview**

This thesis is divided into four chapters.

Chapter 1 provides general introduction followed by necessary background, motivation, literature review and the objectives of the work.

Chapter 2 presents detailed mathematical analysis of the Self-consistent Simulator. Poisson's equation is solved by performing a variable change to make the simulator computationally efficient. Schrödinger's equation is solved by using Non Equilibrium Green Function. Upon the convergence of the self-consistent simulator device drain current is determined.

The results obtained from the developed simulator is presented in chapter 3. Drain current for different gate bias is determined for  $WS_2$  channel FET. Simulator is verified by referring the obtained result to already existing literature. More than one reference is considered. Then by using the developed simulator the drain current for  $MoS_2$  channel transistor is determined. A comparative study of the device parameters is also presented and a better channel material for the structure considered is proposed in this chapter.

Chapter 4 contains the concluding remarks along with suggestions for future work on the topic.

#### **Chapter 2**

### **Quantum Mechanical Simulation**

In this chapter, the 2D transport simulator for TMD FETs is developed by implementation of two components in MATLAB: a Poisson solver and a self-consistent solver. In the first section, the Poisson's equation is solved for a 2D cross section along the channel. A variable change from potential to quasi-Fermi energy will be performed and solved using the Newton-Raphson method. For the second section, the Schrödinger's equation is solved for a 1D cross section perpendicular to the channel by using the Non Equilibrium Green's Function (NEGF) method. From this result, the solution of Schrödinger's equation across the channel is approximated by applying the Perturbation Theory. The NEGF method is mathematically equivalent to solving the Schrödinger's equation with open boundary conditions. Upon convergence, the computationally efficient self-consistent solver is able to determine ballistic drain current, threshold voltage and sub-threshold swing for the TMD FETs. These parameters will be used to measure the device performance in the next chapter. To show the compatibility with circuit level simulation, performance analysis of monolayer MoS<sub>2</sub> channel and WSe<sub>2</sub> channel TMD FETs will also be presented in the result section.

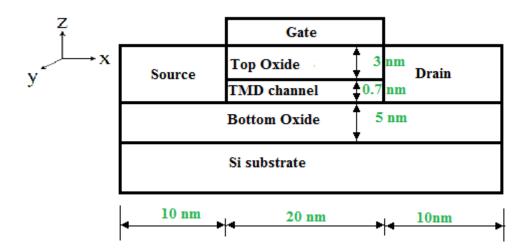

#### 2.1 Device Structure

The device structure considered in this work has a 0.7 nm thick monolayer WSe<sub>2</sub> channel of length 20 nm deposited on a 5 nm thick layer of SiO<sub>2</sub>. A 3 nm thick layer of ZrO<sub>2</sub> serves as the top oxide of the device as shown in Figure 2.1. The metallic source/drain length is taken as 10 nm and Au is used as the source material. Above the top oxide a metallic top gate of Palladium (Pd) is placed. The channel doping density is  $1 \times 10^{25}$  m<sup>-3</sup>.

Figure 2.1 2D cross section of the monolayer WSe<sub>2</sub> channel FET [68]

#### 2.2 Self-consistent Simulator

#### 2.2.1 Poisson Solver

The numeric solution to the Poisson equation is obtained by making use of Gauss's law.

$$\oint [\varepsilon \bar{E}(x,y)] d\bar{S} = \int_{\Omega} q[-n+N_D-N_A] d\Omega \qquad 2.1$$

Where  $\overline{E}$  is the electric field, n is the electron concentration,  $N_D$  and  $N_A$  are the donor and acceptor concentrations, q is the electron charge and  $\varepsilon$  is the dielectric constant. For the numerical solution there are N<sub>x</sub> and N<sub>y</sub> number of lattice mode considered along the X and Y directions. A 2D numerical solution to the Poisson equation is composed of  $N_x \times N_y$  potential values throughout the device region. To attain the  $N_x \times N_y$  unknowns, same number of equations are needed. The equations are obtained either by applying equation 3.1 at all the internal nodes. We have considered m nodes for the row and n nodes for the column. Using a central difference approximation for the spatial derivatives, we express  $\overline{E}$  in terms of potential V. The linearized finite difference form of equation 2.1 is,

$$\frac{a}{b}V_{m-1,n} + \frac{b}{a}V_{m,n-1} - 2\left(\frac{a}{b} + \frac{b}{a}\right)V_{m,n} + \frac{b}{a}V_{m,n+1} + \frac{a}{b}V_{m+1,n}$$

=  $-q\frac{ab}{\varepsilon}(N_D - N_A - n)_{m,n}$  2.2 a

Where a and b are the mesh spacing in the X and Y directions. Since the oxide thickness is very small, to obtain a finer grid the spacing b is typically chosen smaller than the spacing a. Now the dielectric constant should be modified according to the region of interest. If the node is in silicon then  $\varepsilon = \varepsilon_{Si}$  or if the node is in the oxide region then  $\varepsilon = \varepsilon_{ox}$ . If the top and bottom oxides are different then the dielectric constant should be changed accordingly. For the node in the Silicon oxide interface, the discontinuity of  $\varepsilon$  is considered as,

$$\frac{a}{b}V_{m-1,n} + \frac{b}{2a}\left(1 + \frac{\varepsilon_{bot}}{\varepsilon_{top}}\right)V_{m,n-1} - \left(\frac{a}{b} + \frac{b}{a}\right)\left(1 + \frac{\varepsilon_{bot}}{\varepsilon_{top}}\right)V_{m,n} + \frac{b}{2a}\left(1 + \frac{\varepsilon_{bot}}{\varepsilon_{top}}\right)V_{m,n+1} + \frac{a}{b}\frac{\varepsilon_{bot}}{\varepsilon_{top}}V_{m+1,n}$$

$$= -q\frac{ab}{\varepsilon_{top}}(N_D - N_A - n)_{m,n}$$

2.2 b

Where  $\varepsilon_{top}$  and  $\varepsilon_{bot}$  are the dielectric of the top and bottom materials of the interface respectively. Now, rest of the equations is determined from boundary conditions. At the external boundaries of the gates Dirichlet i.e. fixed voltage boundary condition is used and Neumann i.e. continuous electric flux boundary condition is used at the source and drain contacts. So the equations are,

$V_{m,n} = V_G$  for the gate contact

$V_{m,n} - V_{m,n+1} = 0$  for the top and bottom edges of drain/source

$V_{m,n} - V_{m,+1,n} = 0$  for the left and right edges of drain/source 2.2 c

$2V_{m,n} - V_{m+1,n} + V_{m,n+1} = 0$  for the corner nodes of the top edge of drain/source

$2V_{m,n} - V_{m-1,n} + V_{m,n+1} = 0$  for the corner nodes of the bottom edge of drain/source

Now these  $N_x \times N_y$  equations is to be solved for  $V_{m,n}$ . However, for the set of coupled equation the solution of current node depends on the solution of previous node. So it requires a huge amount of time to determine the solution of theses coupled equation. To make our solver computationally efficient we have used a different algorithm [72-74] for Poisson equation solver. In this algorithm, upon the availability of electron density, a variable change from electron density to quasi-fermi energy is performed by using the old potential,

$$(F_n)_{m,n} = -q(V_{old})_{m,n} + k_B T \mathfrak{I}_{1/2}^{-1}(\frac{(n_{2D})_{m,n}}{N_C})$$

2.3

Where  $\mathfrak{I}_{1/2}^{-1}$  is the inverse Fermi-Dirac integral of order  $\frac{1}{2}$  [75],  $n_{2D}$  is the 2D electron density and N<sub>c</sub> is the effective density of states in the conduction band. Now the density of states can be determined from the above equation,

$$(n_{2D})_{m,n} = N_C \mathfrak{I}_{1/2} \left[ \frac{(F_n)_{m,n} - qV_{m,n}}{k_B T} \right]$$

2.4

Once the Quasi-Fermi level variable change is achieved, it is substituted into the nonlinear Poisson equation,

$$\nabla \left( \varepsilon \, \nabla V_{m,n} \right) = N_C \left[ \Im_{1/2} \left( \frac{(F_n)_{m,n} - qV_{m,n}}{k_B T} \right) - \frac{N_D - N_A}{N_C} \right]$$

2.5

This non-linear equation is solved by using Newton-Raphson method [76-77] by rewriting it in the form of F(V)=0 where  $\alpha$  varies from 1 to  $N_x \times N_y$ . The Jacobian matrix of the solution is obtained by,

$$F_{\alpha,\beta} = \frac{\partial F_{\alpha}(V)}{\partial V_{\beta}}$$

2.6

Where  $V_{\beta}$  is the 1D representation of  $V_{m,n}$ . For the new values of potential we use the equation,  $V_{new} = V_{old} + \Delta V$ . Using the Taylor expansion of the first order,

$$F_{\alpha}(V_{new}) \cong F_{\alpha}(V_{old}) + F_{\alpha,\beta,[}(V_{old}). [\Delta V] = 0$$

2.7

So the change in the potential is obtained by simply the matrix operation,

$$[\Delta V]_{\beta} = -F_{\alpha,\beta,[}(V_{old}) \setminus F_{\alpha}(V_{old})$$

2.8

This inner iteration will solve for the potential of the device.

#### 2.2.2 Schrödinger Equation Solver

Schrödinger Equation (SE) allows to calculate the energy levels for any confining atomic potential  $U(\bar{r})$ . The basic time independent Schrödinger equation can be described as,

$$i\hbar\frac{\partial\psi(\bar{r})}{\partial t} = \left[-\frac{\hbar^2}{2m}\nabla^2 + U(\bar{r})\right]\psi(\bar{r})$$

<sup>2.9</sup>

This equation can be modified as Equation 2.10 and the system Hamiltonian is given in Equation 2.11,

$$i\hbar \frac{\partial \psi(\bar{r})}{\partial t} = \widehat{H_{op}} \,\psi(\bar{r})$$

2.10

$$\widehat{H_{op}} = -\frac{\hbar^2}{2m}\nabla^2 + U(\bar{r})$$

2.11

For solving this equation numerically the wave function,  $\psi(\bar{r})$  is converted into a column vector  $\{\psi\}$  and the deferential operator  $\widehat{H_{op}}$  into a matrix [H], then the partial deferential equation into a matrix for is obtained,

$$i\hbar \frac{d}{dt} \{\psi\} = [H]\{\psi\}$$

2.12

If we assume transport direction along x axis and apply Schrödinger equation along that direction, then by using finite difference technique we can convert differential equation into a difference equation,

$$\left(\frac{\partial^2 \psi}{\partial x^2}\right)_{x=x_n} \to \frac{1}{a^2} \left[\psi(x_{n-1}) - 2\psi(x_n) + \psi(x_{n+1})\right]$$

2.13

$$U(x)\psi(x) \to U(x_n)\psi(x_n)$$

2.14

Where a is the difference between two consecutive nodes or the lattice spacing. Now, the system Hamiltonian matrix elements have to calculate.

#### 2.2.2.1 System Hamiltonian Matrix [H]

The system Hamiltonian describes the contact effects of the device in matrix. If N is the total number of grid points of the device in transport direction then the Hamiltonian will be of  $N \times N$  blocks. Hamiltonian matrix size and element will depend on the device structure. The time dependent Schrödinger equation can be written in the matrix form as,

$$E\{\psi\} = [H]\{\psi\}$$

2.15

From the concept of effective mass we can say that electrons in a solid behaves like electrons in the vacuum but with mass different from the electron mass, that is effective mass m\*. So we can replace the SE with the Effective Mass Equation in simple one dimension along the x axis,

$$E\psi(\bar{r}) = \left[-\frac{\hbar^2}{2m^*}\nabla^2 + E_c\right]\psi(\bar{r})$$

2.16

Here the atomic potential is replaced by some constant  $E_c$  that indicates the conduction band energy. Now we will explain the method to represent Equation (2.16) in a matrix from like Equation (2.15) and choose the matrix elements of [H] so that it becomes equal to the Equation (2.15). The solution of the differential equation with constant value can be written in exponential form as,

$$\psi(x) = e^{ikx} \qquad 2.17$$

From Equation 2.16,

$$E = \frac{\hbar^2 k^2}{2m^*} + E_c = \frac{p^2}{2m^*} + E_c$$

2.18

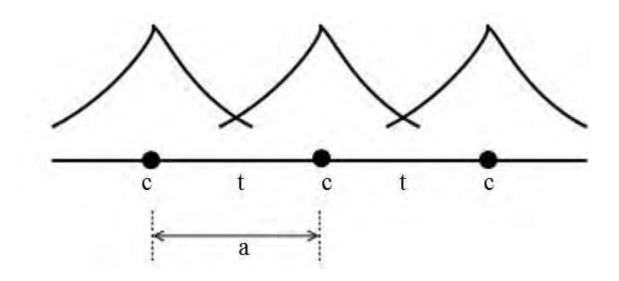

Figure 2.2: Simple 1D structure of the atom in the solid. The basis function is localized around a particular atom

For a matrix of homogeneous system like the Equation (2.15), again the solution can be written in exponential form and the dispersion relation obtained should be match with Equation (2.18). We will use nearest neighbor tight binding model and so the wave function will be a column vector and [H] will be square matrix with nonzero value only at diagonal, upper and lower diagonal.

Since we have considered a homogeneous system all the diagonal elements will be same and the upper and lower diagonal elements will also be same. We can write Equation (2.15) as,

$$E \begin{cases} \psi_1 \\ \psi_2 \\ \vdots \\ \psi_N \end{cases} = \begin{bmatrix} c & t & \dots & 0 \\ t & c & \dots & 0 \\ \vdots & \vdots & \ddots & \vdots \\ 0 & 0 & \dots & c \end{bmatrix} \begin{pmatrix} \psi_1 \\ \psi_2 \\ \vdots \\ \psi_N \end{cases}$$

2.19

From this equation for the n<sup>th</sup> atom,

$$E\psi_n = t\psi_{n-1} + c\psi_n + t\psi_{n+1}$$

2.20

For this type of homogeneous system we can represent the solution in terms of exponential functions,

$$\psi_{n-1} = e^{ik(n-1)a}$$

$$\psi_n = e^{ikna}$$

$$\psi_{n+1} = e^{ik(n+1)a}$$

2.21

From Equation 2.20 the dispersion relation will be,

$$E = te^{-ika} + c + te^{ika}$$

$$= c + 2tcos(ka)$$

2.22

$$E + \frac{1}{\pi/a} + \frac{1}{\pi$$

Figure 2.3: Dispersion Relation

If the parameters are chosen properly this two dispersion relation will match for a certain limit. For electron flow property the electrons around the conduction band have to be considered and for our case this cosine and parabolic function match quite well. Electrons will occupy the conduction band energy level over a few K<sub>BT</sub> plus the applied voltage. We determine the limit by using Taylor series expansion,

$$\cos(x) = 1 - \frac{x^2}{2!} + \frac{x^4}{4!} - \frac{x^6}{6!} \dots$$

$$\approx 1 - \frac{x^2}{2!}$$

2.23

So Equation 2.22 becomes,

$$E = (c + 2t) - ta^2 k^2 2.24$$

Since Equation 2.24 and 2.18 are equal, so  $U(x_n)=U_n$  and  $\frac{\hbar^2}{2m^*a^2}=t_0$ . We can write the system Hamiltonian matrix, [H] as,

$$[H] = \begin{bmatrix} U_0 + 2t_0 & -t_0 & \dots & 0 \\ -t_0 & U_1 + 2t_0 & \dots & 0 \\ \vdots & \vdots & \ddots & \vdots \\ 0 & 0 & \dots & U_N + 2t_0 \end{bmatrix}$$

2.25

#### 2.2.2.2 Eigen States

Since Equation Eigenvalues of [H] are the energy levels and Eigenvectors of [H] are the corresponding wave functions associated with those levels. Now for time dependent Schrödinger equation we can write from Equation 2.12 as,

$$i\hbar \frac{d\psi_n}{dt} = -t_0 \psi_{n-1} + (U_0 + 2t_0)\psi_n - t_0 \psi_{n+1}$$

=  $\sum_m -t_0 \delta_{n,m-1} + (U_0 + 2t_0)\delta_{n,m} - t_0 \delta_{n,m+1}$  2.26

Where  $\delta_{n,m}$  is the Kronekar delta, which is equal to 1 if n = m and 0 if  $n \neq m$ . So the elements of the Hamiltonian can be expressed as,

$$H_{n,m} = -t_0 \delta_{n,m-1} + (U_0 + 2t_0) \delta_{n,m} - t_0 \delta_{n,m+1}$$

2.27

If the initial state is given then  $\{\psi(t)\}\$  can be calculated from eigenvalues  $E_{\alpha}$  and eigenvectors  $\{\alpha\}$  of the matrix [H],

$$[H]\{\alpha\} = E_{\alpha}\{\alpha\}$$

2.28

Wave functions can be defined as,

$$\{\psi(t)\} = \sum_{\alpha} C_{\alpha} e^{-\frac{iE_{\alpha}t}{\hbar}} \{\alpha\}$$

2.29

As a result  $\psi\psi^* = |\psi^2|$  is the probability distribution of the charge.

#### **2.2.3 NEGF Formalism for the Transport Simulation**

First Uncoupled Mode Space (FUMS) [78-79] has been used for this 2D simulator. By using the initially approximated Poisson equation is solved and the potential, V is determined at each node of the device. Then potential energy U(x,y) is calculated. Average

potential energy along the confinement direction is determined by using the following equation,

$$\overline{U(y)} = \frac{1}{L_x} \int_0^{L_x} U(x, y) dx$$

2.30

Where,  $L_x$  is the length of the device in the transport direction. This average potential energy is substituted into the Schrödinger equation and by solving the equation average subband energy,  $\overline{E_{sub}^m}$  and the wave function  $\overline{\psi^m(y)}$  for the m<sup>th</sup> subband is determined. This wave function is considered as a constant along the transport direction according to the FUMS [28] approach. For the Eigen energies, First Order Perturbation Theory [29] is considered and the calculated energy the system Hamiltonian, H is formed.

Non-equilibrium Green's Function is used to calculate ballistic electron density and hence the current in the device. The properties of the channel material is considered in the Hamiltonian matrix [H]. So the retarded Green's function with potential matrix [U] at a specific energy E,

$$G^{m}(E) = (EI - H - \sum_{S}^{m}(E) - \sum_{D}^{m}(E))^{-1}$$

2.31

Where, I is the identity matrix,  $\sum_{S}^{m}(E)$  and  $\sum_{D}^{m}(E)$  are the self-energy matrices representing the interaction of channel with source and drain. The spectral function, A for the source and drain can be determined as,

$$A_{S}^{m}(E) = G^{m}(E)\Gamma_{S}^{m}(E)G^{m_{\dagger}}(E)$$

2.32

$$A_D^m(E) = G^m(E)\Gamma_D^m(E)G^{m_{\dagger}}(E)$$

2.33

Where  $\Gamma_S^m$  and  $\Gamma_D^m$  are the coupling matrices for the source and the drain and they are described by the spectral broadening as,

$$\Gamma_S^m = i(\Sigma_S^m(E) - \Sigma_S^{m\dagger}(E))$$

2.34

$$\Gamma_S^m = i(\Sigma_S^m(E) - \Sigma_S^{m\dagger}(E))$$

2.35

The 2D electron density is determined by the equation,

$$n_x^m = \frac{1}{\hbar a} \sqrt{\frac{m^* k_B T}{2\pi^3}} \int_{-\infty}^{\infty} [\mathfrak{F}_{-\frac{1}{2}} \left(\frac{\mu_s - E}{k_B T}\right) diag \left(A_S^m(E)\right) + \mathfrak{F}_{-\frac{1}{2}} \left(\frac{\mu_D - E}{k_B T}\right) diag \left(A_S^m(E)\right)] dE$$

$$2.36$$

3D electron density can be determined by multiplying  $n_x^m$  with the wave function  $|\psi^m(y)^2|$ . Total electron density,  $n_x$  is determined by summing the above equation for all the subband considered in the simulation. Then the total ballistic current is determined by,

$$I = \frac{q}{\hbar a} \sum_{m=1}^{n} \sqrt{\frac{m^* k_B T}{2\pi^3}} \int_{-\infty}^{\infty} [\mathfrak{F}_{-\frac{1}{2}} \left(\frac{\mu_s - E}{k_B T}\right) diag \left(A_s^m(E)\right) + \mathfrak{F}_{-\frac{1}{2}} \left(\frac{\mu_D - E}{k_B T}\right) diag \left(A_s^m(E)\right)] T(E) dE$$

$$2.37$$

Where T(E) is the transmission coefficient which is obtained by summing the transmission coefficient,  $T^m(E)$  for all the subband considered,

$$T^{m}(E) = Trace\left(\Gamma_{S}^{m}G^{m}(E)\Gamma_{D}^{m}G^{m\dagger}(E)\right)$$

2.38

The whole simulation process is presented below with a flow diagram,

Figure 2.4: Algorithm for self-consistent solution

#### Chapter 3

### **Results and Discussion**

In this chapter, we present a comprehensive study of the device parameters of the TMD channel FETs with WSe<sub>2</sub> and MoS<sub>2</sub> as the channel material. First of all, device parameters of WSe<sub>2</sub> is presented. For this simulation, 1.6 eV bandgap, 3.9 eV electron affinity and  $0.33m_0$  effective mass are considered [80-81] [57]. Simulator verification is provided in this chapter. Later in this chapter, device parameters of MoS<sub>2</sub> channel based FET are provided.

#### 3.1 WSe<sub>2</sub> channel FET

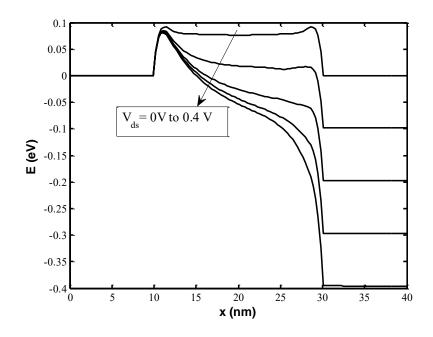

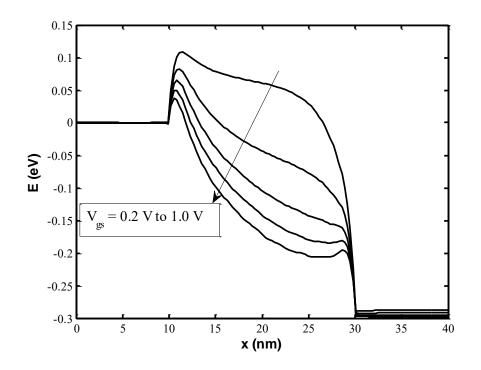

In this section, different characteristic properties of WSe<sub>2</sub> channel FET are presented. Figure 3.1 shows the first subband energy profile at fixed gate bias of  $V_{gs}$ =0.4 V. Drain bias is considered from 0V to 0.4V in an interval of 0.1V. Little variation in the top of the barrier confirms the strong gate control of the device. Figure 3.2 shows the first subband energy at fixed drain bias of V<sub>ds</sub>=0.4V and the gate bias varies from 0.2V to 1.0V in an interval of 0.2V. Rapid top barrier change at lower voltage confirms stable threshold voltage. Three subbans are considered in our work.

Figure 3.1: First subband energy profile across the channel at a fixed gate bias of  $V_{gs}$  = 0.4 V with  $V_{ds}$  = 0.0 V to 0.4 V with an interval of 0.1 V

Figure 3.2: First subband energy profile across the channel at a fixed drain bias of  $V_{ds}$  = 0.4 V with  $V_{gs}$  = 0.2 V to 1.0 V with an interval of 0.2 V

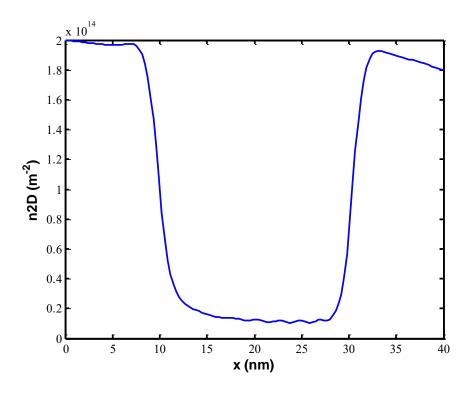

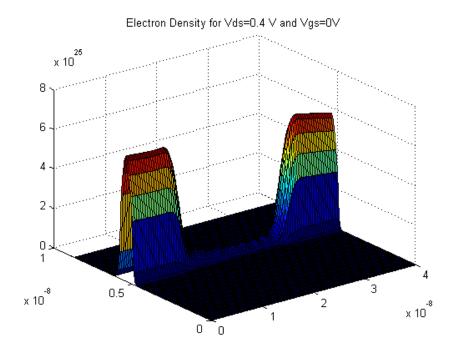

Figure 3.3 shows the 2D electron density along the device and in middle of the channel region the value is approximately $10^{13}m^{-2}$ . Figure 3.4 is the 3D electron density across the device for  $V_{ds} = 0.4$  V and  $V_{gs} = 0$  V.

Figure 3.3: 2D electron density along the device

Figure 3.4 : 3D eletron density for  $V_{ds}$  = 0.4 V and  $V_{gs}$  = 0 V

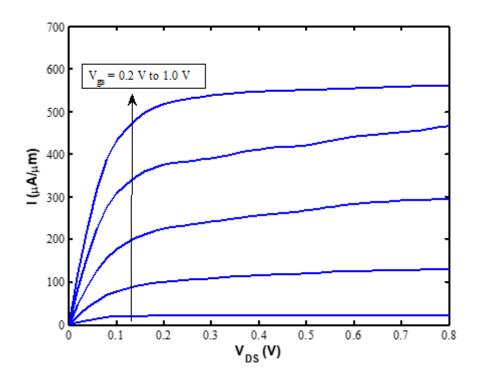

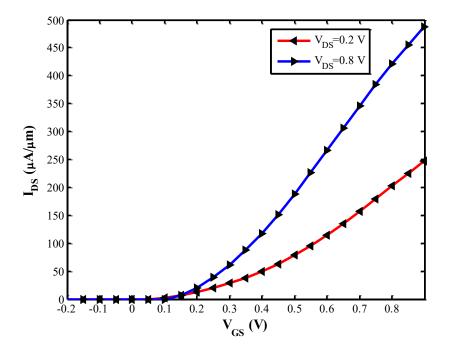

Figure 3.5 shows the transfer characteristics of the device. Drain current of the device at different gate voltage is presented in the I-V characteristics. Figure 3.6 shows the drain current at different gate bias.

Figure 3.5: I-V characteristics

#### Figure 3.6: IDS vs VGS

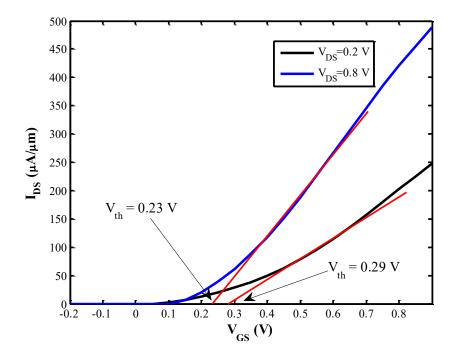

### 3.1.1 Parameter Extraction for WSe<sub>2</sub> channel FET

Threshold voltage,  $V_{th}$  of the device is the minimum source to gate voltage required to create the conducting path between source and drain terminals. This important device parameter is extracted from the extrapolated  $I_{DS}$ vs  $V_{GS}$  curve. X-intercept of the rising region of the curve or the tangent of that curve indicates the V<sub>th</sub>. From Figure 3.7 V<sub>th</sub> for the device structure considered is 0.23 V for V<sub>ds</sub> =0.2 V and 0.29 V for V<sub>ds</sub> =0.8 V.

Figure 3.7: Vth calculation

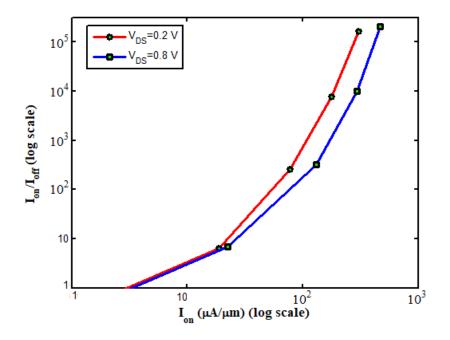

The ON/OFF ratio of the drain current is determined from Figure 3.8 and the maximum obtained ON/OFF ratio is  $\sim 10^6$  for both the drain bias of 0.2 V and 0.8 V. The gate bias of 0.1V is considered as OFF state and 0.8 V as the ON state of the device.

Figure 3.8: Determination of ON/OFF current ratio

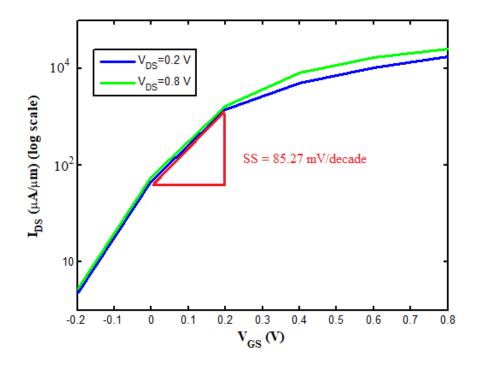

Subthreshold Swing (SS) is determined from the Figure 3.8. Slope of the  $log_{10}(I_{ds})$ -  $V_{gs}$  curve denotes the SS [82]. SS of the device is 85.27 mV/decades which is very close to the theoretical limit of 60 mV/decade of these type of devices.

Figure 3.9: Determination of Subthreshold Swing

### 3.2 Simulator Validation and Efficiency

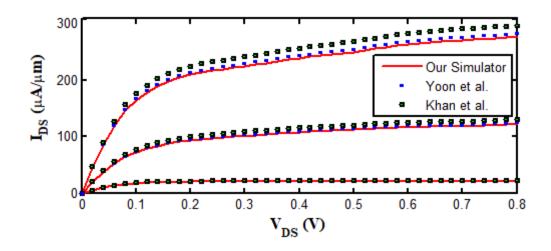

The simulator is validated by comparing the device current with the existing reported simulator by Khan et al [83]. The device simulated by Khan et al is a monolayer WSe<sub>2</sub> channel Field Effect Transistor. They have used COMSOL multiphysics tool for their simulation and Fast Uncoupled Mode Space (FUMS) approach for their device current calculation. The reported result is in complete affirmation with our result. Again, monolayer TMD transistor reported by Yoon et at [84] is also taken as the reference for the validation of our simulator.

Figure 3.10: Drain current of Monolayer WSe<sub>2</sub> channel FET by our simulator, Khan et al [83] and Yoon et al [84] at the gate bias from 0.2 V to 0.6 V with an interval of 0.2 V.

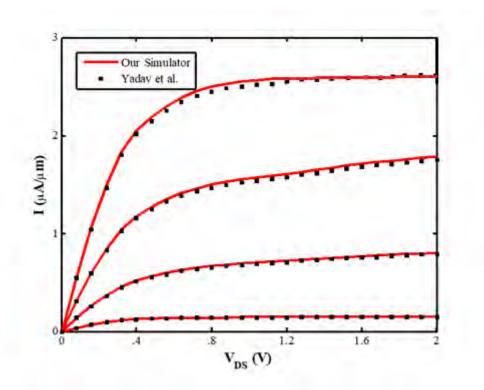

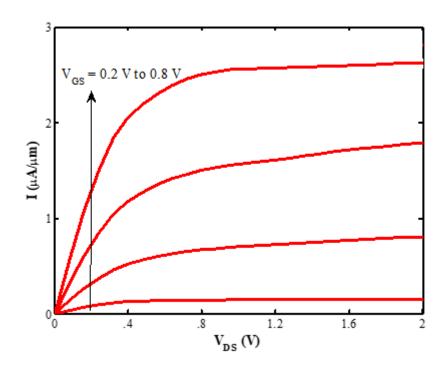

The simulator is also validated for MoS<sub>2</sub> channel material. Monolayer TMD based transistor reported by Yadav [85] et al has used 20nm as the channel length of the device. Figure 3.11 shows that our simulation are compatible with the reported result of MoS<sub>2</sub> channel material transistor.

Figure 3.11: Drain current of Monolayer MoS<sub>2</sub> channel FET by our simulator, Yadav et al [85] at the gate bias from 0.2 V to 0.8 V with an interval of 0.2 V.

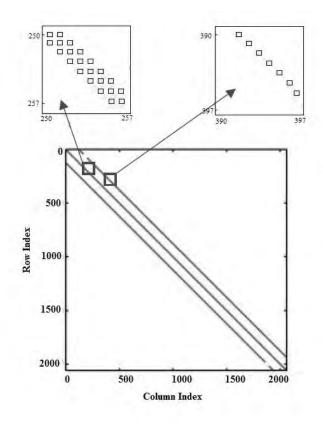

In our algorithm, Poisson equation makes the simulator computationally efficient. To illustrate the solution process of Poisson equation, we present the sparsity of the Jacobian matrix in Figure 3.12. The pattern shows that the Jacobian is very sparse matrix. The five diagonal lines indicate that each node is only coupled to its four neighbourings in the finite difference approximation. The sparsity of the Jacobian give rise to large savings in memory and computational time.

Figure 3.12: Sparsity of Jacobian Matrix

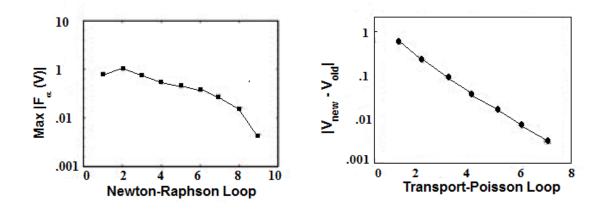

In the convergence profile of Newton-Raphson Loop shown in Figure 3.13, the first few points indicate that the trial potential is away from the solution. After that quadratic convergence is seen. Due to the variable in Poisson-Transport coupled system, The Transport-Poisson convergence is smooth.

Figure 3.13: Convergence profile of Newton-Raphson Loop and Transport-Poisson Loop

### 3.3 MoS<sub>2</sub> channel FET

For this simulation of MoS<sub>2</sub> channel FET, 1.8 eV bandgap, 4.07 eV electron affinity and 0.56m<sub>0</sub> effective mass are considered [36-37]. Same simulator has been used for this simulation. Thickness of the monolayer MoS<sub>2</sub> channel is considered as 0.6 nm [38]. Top oxide of thickness 2nm, bottom oxide of thickness 4nm and 20nm channel length are considered in this simulation. Both drain and source lengths are considered as 10nm. Figure 3.14 shows the final result of this simulation. Drain current at different gate bias is presented in this figure.

Figure 3.14: I-V characteristics of MoS<sub>2</sub> channel FET

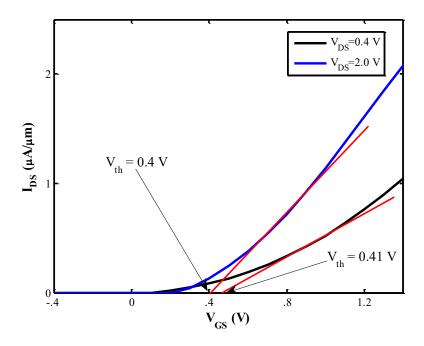

### 3.3.1 Parameter Extraction for MoS<sub>2</sub> channel FET

Figure 3.15 shows the threshold voltage,  $V_{th}$  for MoS<sub>2</sub> channel FET. For this device  $V_{th}$  is 0.4 V for  $V_{DS} = 0.4$  V and 0.41 V for  $V_{DS} = 2.0$  V.

Figure 3.15:  $V_{th} \mbox{ calculation for } MoS_2 \mbox{ channel FET}$

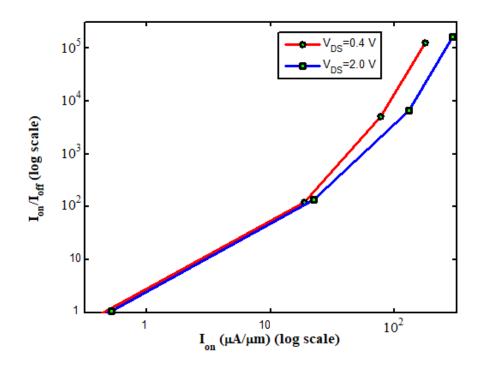

Figure 3.16 shows the ON/OFF current ratio for this device structure and the ratio is  $\sim 3 \times 10^5$ .

Figure 3.16: ON/OFF current ratio of MOS<sub>2</sub> channel FET

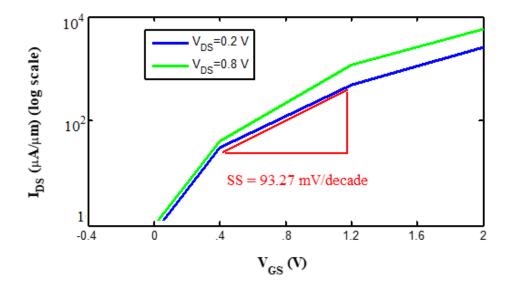

Figure 3.17 shows the subthreshold swing for this device structure and the value is 93.27 mV/decade.

Figure 3.17: SS for the MOS<sub>2</sub> channel FET

## **Chapter 4**

# Conclusion

This chapter presents the whole work in a nutshell. Some unexplored facts of this work which can be put under extensive research.

## 4.1 Conclusion

In this work a computationally efficient Simulator for TMD channel FET is developed. For the simulator development, Poisson's equation is solved by using a faster method. Schrödinger's equation is solved and this self-consistent simulator is used to determine the device current by using NEGF method. We have studied the effect of channel material for the device structure we have considered. In our work, we used WSe<sub>2</sub> and MoS<sub>2</sub> as our channel material. Different device parameters are determined. According to our study the device parameters are given below,

| Channel material | Threshold Voltage | ON/OFF Current   | Sub-threshold Swing |

|------------------|-------------------|------------------|---------------------|

|                  | (in Volt)         | Ratio            | (in mV/decade)      |

|                  |                   |                  |                     |

| WSe <sub>2</sub> | .2                | ~10 <sup>6</sup> | 85.27               |

|                  |                   |                  |                     |

| MoS <sub>2</sub> | .4                | $\sim 10^{5}$    | 93.27               |

|                  |                   |                  |                     |

Table 4.1: Device Parameters obtained from the Simulator

For faster switching the FET devices should have a lower threshold voltage and higher ON/OFF current ratio. From our study it can be inferred that for this type of FET structure monolayer WSe<sub>2</sub> is a better choice as the channel material than the monolayer MoS<sub>2</sub>. However, the fabrication facility is not considered in our study. Fabrication facility of these devices most be considered for the commercial production of this device.

## 4.2 Limitations and Suggestion for Future Works

- The fabrication facility of a device is the main concern for the commercial availability of the device. So, first of all fabrication process for this device should be developed.

- Experimental results for 20nm channel length FETs are still not available in the literature. As a result the simulator is validated with existing simulation results. So, validity of the device parameters should be done by developing an analytical model.

- In the numerical simulation, the 2D material channel is considered fully depleted under all gate bias condition. Although this assumption is true for strong inversion region, it introduces error in subthreshold current calculation. In future this limitation can be addressed by using a dynamic depletion width with applied gate voltages.

- The simulator determines only the ballistic current of the device structure. To determine more accurate current profile of this device, scattering can be introduced.

For the introduction of scattering Butikker probes can be considered inside the channel region.

- The approach of the simulator can also be applied for other types of device structures.

# References

- G. E. Moore. "Progress in digital integrated electronics," *Electron Devices Meeting*, vol. 21, pp. 11-13, 1975.

- [2] Available online: http://www.intel.com/content/www/us/en/homepage.html

- [3] R. H. Dennard, V. Rideout, E. Bassous, and A. LeBlanc, "Design of ion-implanted MOSFET's with very small physical dimensions," *IEEE Journal of Solid-State Circuits*, vol. 9, no. 5, pp. 256–268, 1974.

- [4] D. J. Frank, R. H. Dennard, E. Nowak, P. M. Solomon, Y. Taur, and H. S. P. Wong,

"Device scaling limits of Si MOSFETs and their application dependencies,"

*Proceedings of the IEEE*, vol. 89, no. 3, pp. 259-288, 2001.

- [5] W. Haensch, E. J. Nowak, R. H. Dennard, P. M. Solomon, A. Bryant, O. H. Dokumaci, A. Kumar, X. Wang, J. B. Johnson, and M. V. Fischetti, "Silicon CMOS devices beyond scaling," *IBM Journal of Research and Development*, vol. 50 no. 4, pp. 339-361, 2006.

- [6] ITRS Roadmap 2013, Available online: http://www.itrs2.net/2013-itrs.html.

- [7] P. Avouris, Z. Chen, and V. Perebeinos, "Carbon-based electronics," *Nature nanotechnology*, vo. 2, no. 10, p. 605, 2007.

- [8] A. D. Franklin, and Z. Chen, "Length scaling of carbon nanotube transistors," *Nature nanotechnology*, vol. 5, no. 12, p. 858, 2010.

- [9] J. Appenzeller, J. Knoch, M. T. Bjork, H. Riel, H. Schmid, and W. Riess, "Toward nanowire electronics," *IEEE Transactions on electron devices*, vol. 55, no. 11, pp. 2827-2845, 2008.

- [10] Y. Li, F. Qian, J. Xiang, and C. M. Lieber, "Nanowire electronic and optoelectronic devices," *Materials today*, vol. 9, no. 10, pp. 18-27, 2006.

- [11] S. Das, J. A. Robinson, M. Dubey, H. Terrones, and M. Terrones, "Beyond graphene: progress in novel two-dimensional materials and van der Waals solids," *Annual*

Review of Materials Research, vol. 45, no. 1, pp. 1-27,2015.

- [12] B. Radisavljevic, A. Radenovic, J. Brivio, I. V. Giacometti, and A. Kis, "Singlelayer MoS<sub>2</sub> transistors," *Nature nanotechnology*, vol. 6, no. 3, p. 147, 2011.

- [13] S, Das, H. Y. Chen, A. V. Penumatcha, and J. Appenzeller, "High performance multilayer MoS<sub>2</sub> transistors with scandium contacts," *Nano letters*, vol. 13, no. 1, pp. 100-105, 2012.

- [14] S. Das, and J. Appenzeller, "WSe<sub>2</sub> field effect transistors with enhanced ambipolar characteristics," *Applied physics letters*, vol. 103, no. 10, p. 103501, 2013.

- [15] S. Das, M. Demarteau, and A. Roelofs, "Ambipolar phosphorene field effect transistor," ACS nano, vol. 8, no. 11, pp. 11730-11738, 2014.

- S. Z. Butler, S. M. Hollen, L. Cao, Y. Cui, J. A. Gupta, H. R. Gutiérrez, T. F. Heinz,

S. S. Hong, J. Huang, A. F. Ismach, and E. J. Halperin, "Progress, challenges, and opportunities in two-dimensional materials beyond graphene," *ACS nano*, vol. 7, no. 4, pp. 2898-2926, 2013.

- [17] I. Meric, M. Y. Han, A. F. Young, B. Ozyilmaz, P. Kim, and K. L. Shepard, "Current saturation in zero-bandgap, top-gated graphene field-effect transistors," *Nature nanotechnology*, vol. 3, no. 11, p. 654, 2008.

- [18] H. Lu, and A. Seabaugh, "Tunnel field-effect transistors: State-of-the-art," *IEEE Journal of the Electron Devices Society*, vol. 2, no. 4, pp. 44-49, 2014.

- [19] S. Das, A. Prakash, R. Salazar, and J. Appenzeller, "Toward low-power electronics: tunneling phenomena in transition metal dichalcogenides," *ACS nano*, vol. 8, no. 2, pp. 1681-1689, 2014.

- [20] T. van Hemert, and R. J. E. Hueting, "Piezoelectric strain modulation in FETs." *IEEE transactions on electron devices*, vol. 60, no. 10, pp. 3265-3270, 2013.

- [21] S. Salahuddin, and S. Datta, "Use of negative capacitance to provide voltage amplification for low power nanoscale devices," *Nano letters*, vol. 8, no. 2, pp. 405-410, 2008.

- [22] G. I. Bourianoff, P. A. Gargini, and D. E. Nikonov, "Research directions in beyond CMOS computing," *Solid-State Electronics*, vol. 51, no. 11-12, pp. 1426-1431, 2007.

- [23] B. B. Aein, D. Datta, S. Salahuddin, and S. Datta, "Proposal for an all-spin logic device with built-in memory," *Nature nanotechnology*, vol. 5, no. 4, p. 266, 2010.

- [24] S. K. Banerjee, L. F. Register, E. Tutuc, D. Reddy, and A. H. MacDonald, "Bilayer pseudospin field-effect transistor (BiSFET): A proposed new logic device," *IEEE Electron Device Letters*, vol. 30, no. 2, pp. 158-160, 2009.

- [25] K. S. Novoselov, D. Jiang, F. Schedin, T. J. Booth, V. V. Khotkevich, S. V. Morozov, and A. K. Geim, "Two-dimensional atomic crystals," *Proceedings of the National Academy of Sciences of the United States of America*, vol. 102, no. 30, pp. 10451-10453, 2005.

- [26] P. Vogt, P. D. Padova, C. Quaresima, J. Avila, E. Frantzeskakis, M. C. Asensio, A. Resta, B. Ealet, and G. L. Lay, "Silicene: compelling experimental evidence for graphenelike two-dimensional silicon," *Physical review letters*, vol. 108, no. 15, p. 155501, 2012.

- [27] M. E. Dávila, L. Xian, S. Cahangirov, A. Rubio, and G. L. Lay, "Germanene: a novel two-dimensional germanium allotrope akin to graphene and silicene," *New Journal* of *Physics*, vol. 16, no. 9, p. 095002, 2014.

- [28] S. V. Suryavanshi, and E. Pop, "S2DS: Physics-based compact model for circuit simulation of two-dimensional semiconductor devices including non-idealities" *Journal of Applied Physics*, vol. 120, no. 22, p. 224503, 2016.

- [29] B. V. D. Broek, M. Houssa, E. Scalise, G. Pourtois, V. V. Afanas'ev, and A. Stesmans, "Two-dimensional hexagonal tin: ab initio geometry, stability, electronic structure and functionalization," 2D Materials, vol. 1, no. 2, p. 021004, 2014.

- [30] J. O. Sofo, A. S. Chaudhari, and G. D. Barber, "Graphane: A two-dimensional hydrocarbon," *Physical Review B*, vol. 75, no. 15, p. 153401, 2007.

- [31] D. C. Elias, R. R. Nair, T. M. G. Mohiuddin, S. V. Morozov, P. Blake, M. P. Halsall,

A. C. Ferrari, D. W. Boukhvalov, M. I. Katsnelson, A. K. Geim, and K. S. Novoselov, "Control of graphene's properties by reversible hydrogenation: evidence for graphane," *Science*, vol. 323, no. 5914, pp. 610-613, 2010.

- [32] E. Bianco, S. Butler, S. Jiang, O. D. Restrepo, W. Windl, and J. E. Goldberger, "Stability and exfoliation of germanane: a germanium graphane analogue," ACS Nano, vol. 7, no. 5, pp. 4414-4421, 2013.

- [33] K. K. Liu, W. Zhang, Y. H. Lee, Y. C. Lin, M. T. Chang, C. Y. Su, C. S. Chang, H. Li, Y. Shi, H. Zhang, and C. S. Lai, "Growth of large-area and highly crystalline MoS2 thin layers on insulating substrates," *Nano Letter*, vol. 12, No. 3, pp. 1538-1544, 2012.

- [34] F. Schwierz, J. Pezoldt, and R. Granzner, "Two-dimensional materials and their prospects in transistor electronics," *Nanoscale*, vol. 7, no. 18, pp. 8261-8283, 2015.

- [35] A. P. Nayak, T. Pandey, D. Voiry, J. Liu, S. T. Moran, A. Sharma, C. Tan, C. H. Chen, L. J. Li, M. Chhowalla, and J. F. Lin, "Pressure-dependent optical and vibrational properties of monolayer molybdenum disulfide," *Nano letters*, vol. 15, no. 1, pp. 346-353, 2014.

- [36] G. Eda, T. Fujita, H. Yamaguchi, D. Voiry, M. Chen, and M. Chhowalla, "Coherent atomic and electronic heterostructures of single-layer MoS<sub>2</sub>," *Acs Nano*, vol. 6, no. 8, pp. 7311-7317, 2012.

- [37] B. Radisavljevic, M. B. Whitwick, and A. Kis, "Integrated circuits and logic operations based on single-layer MoS2," ACS nano, vol. 5, no. 12, pp. 9934-9938, 2011.

- [38] W. Cao, J. Kang, D. Sarkar, W. Liu, and K. Banerjee, "Performance evaluation and design considerations of 2D semiconductor based FETs for sub-10 nm VLSI," in *Proc. IEEE International Electron Devices Meeting (IEDM) 2014*, pp. 30.5.1– 30.5.4, 2014.

- [39] W. Cao, J. Kang, S. Bertolazzi, A. Kis, and K. Banerjee, "Can 2D-nanocrystals extend the lifetime of floating-gate transistor based nonvolatile memory?" *IEEE Trans. Electron Devices*, vol. 61, no. 10, pp. 3456–3464, 2014.

- [40] X. Wang, C. Liu, Y. Chen, G. Wu, X. Yan, H. Huang, P. Wang, B. Tian, Z. Hong,

Y. Wang, and S. Sun, "Ferroelectric FET for nonvolatile memory application with

two-dimensional MoSe2 channels," 2D Materials, vol. 4, no. 2, p. 025036, 2017.

- [41] T. Korn, S. Heydrich, M. Hirmer, J. Schmutzler, and C. Schüller, "Low-temperature photocarrier dynamics in monolayer MoS2," *Applied Physics Letters*, vol. 99, no. 10, p. 102109, 2011.

- [42] K. F. Mak, C. Lee, J. Hone, J. Shan, and T. F. Heinz, "Atomically thin MoS2: a new direct-gap semiconductor," *Physical review letters*, vol. 105, no. 13, p. 136805, 2010.

- [43] V. Podzorov, M. E. Gershenson, C. Kloc, R. Zeis, and E. Bucher, "High-mobility field-effect transistors based on transition metal dichalcogenides," *Applied Physics Letters*, vol. 84, no. 17, pp. 3301-3303, 2004.

- [44] J. Pu, Y. Yomogida, K. K. Liu, L. J. Li, Y. Iwasa, and T. Takenobu, "Highly flexible MoS2 thin-film transistors with ion gel dielectrics," *Nano letters*, vol. 12, no. 8, pp. 4013-4017, 2012.

- [45] D. Sarkar, W. Liu, X. Xie, A. C. Anselmo, S. Mitragotri, and K. Banerjee, "MoS2 field-effect transistor for next-generation label-free biosensors," ACS nano, vol. 8, no. 4, pp. 3992-4003, 2014.

- [46] Y. J. Zhang, T. Oka, R. Suzuki, J. T. Ye, and Y. Iwasa, "Electrically switchable chiral light-emitting transistor," *Science*, vol. 344, no. 6185, p. 725-728, 2014.

- [47] Q. He, Z. Zeng, Z. Yin, H. Li, S. Wu, X. Huang, and H. Zhang, "Fabrication of Flexible MoS2 Thin-Film Transistor Arrays for Practical Gas-Sensing Applications," *Small*, vol. 8, no. 19, pp. 2994-2999, 2012.

- [48] C. Tan, and H. Zhang, "Two-dimensional transition metal dichalcogenide nanosheet-based composites," *Chemical Society Reviews*, vol. 44, no. 9, pp. 2713-2731, 2015.

- [49] S. Kim, A. Konar, W.-S. Hwang, J. H. Lee, J. Lee, J. Yang, C. Jung, "High-mobility and low-power thin-film transistors based on multilayer MoS2 crystals," *Nature*

communications, vol. 3, no. 1, p. 1011, 2012.

- [50] S. Najmaei, Z. Liu, W. Zhou, X. Zou, G. Shi, S. Lei, B. I. Yakobson, J.-C. Idrobo, P. M. Ajayan, and J. Lou, "Vapour phase growth and grain boundary structure of molybdenum disulphide atomic layers," *Nature materials*, vol. 12, no. 8, pp. 754-759, 2013.

- [51] W. Liu, J. Kang, W. Cao, D. Sarkar, Y. Khatami, D. Jena, and K. Banerjee, "Highperformance few-layer-MoS2 field-effect-transistor with record low contactresistance." In *IEEE International Electron Devices Meeting (IEDM) 2013*, pp. 19-4, 2013.

- [52] W. Liu, J. Kang, D. Sarkar, Y. Khatami, D. Jena, and K. Banerjee, "Role of metal contacts in designinghigh-performance monolayer n-type WSe2 field effect transistors," *Nano Lett.*, vol. 13, no. 5, pp. 1983–1990, 2013.

- [53] W. Cao, J. Kang, W. Liu, and K. Banerjee, "A compact current–voltage model for 2D semiconductor based field-effect transistors considering interface traps, mobility degradation, and inefficient doping effect," *IEEE Transactions on Electron Devices*, vol. 61, no. 12, pp. 4282-4290, 2014

- [54] K. Banerjee, W. Liu, and J. Kang, "High-Performance Field-Effect-Transistors on Monolayer-WSe2," In *The Electrochemical Society Meeting Abstracts*, no. 31, pp. 2182-2182, 2013.

- [55] N. Ma, and D. Jena, "Charge scattering and mobility in atomically thin semiconductors," *Physical Review X*, vol. 4, no. 1, p. 011043, 2014.

- [56] Availale online: http://www.quantum-espresso.org/

- [57] Availale online: http://quantumwise.com/products/atk

- [58] A. Ramasubramaniam, and D. Naveh, "Mn-doped monolayer MoS<sub>2</sub>: an atomically thin dilute magnetic semiconductor," *Physical Review B*, vol. 87, no. 19, p. 195201, 2013.

- [59] K.-A. N. Duerloo, M. T. Ong, and E. J. Reed, "Piezoelectricity in Monolayers and Bilayers of Inorganic Two-Dimensional Crystals," *In MRS Proceedings*, vol. 1556,

pp. mrss13-1556, 2013.

- [60] J. Chang, S. Larentis, E. Tutuc, L. F. Register, and S. K. Banerjee, "Atomistic simulation of the electronic states of adatoms in monolayer MoS<sub>2</sub>," *Applied physics letters*, vol. 104, no. 14, p. 141603, 2014.

- [61] H. Yuan, X. Wang, B. Lian, H. Zhang, X. Fang, B. Shen, G. Xu, "Generation and electric control of spin–valley-coupled circular photogalvanic current in WSe<sub>2</sub>," *Nature nanotechnology*, vol. 9, no. 10, pp. 851-857, 2014.

- [62] A. Allain, J. Kang, K. Banerjee, and A. Kis, "Electrical contacts to two-dimensional semiconductors," *Nature Materials*, vol. 14, no. 12, pp. 1195-1205, 2015.

- [63] W. X. Zhou, and K. Q. Chen. "First-Principles Determination of Ultralow Thermal Conductivity of monolayer WSe<sub>2</sub>," *Scientific Reports*, vol. 5, 2015.

- [64] X. Dai, W. Li, T. Wang, X. Wang, and C. Zhai, "Bandstructure modulation of twodimensional WSe<sub>2</sub> by electric field," *Journal of Applied Physics*, vol. 117, no. 8, p. 084310, 2015.

- [65] S. Wang, G. D. Lee, S. Lee, E. Yoon, and J. H. Warner, "Detailed Atomic Reconstruction of Extended Line Defects in Monolayer MoS<sub>2</sub>." ACS nano, vol. 10, no. 5, pp. 5419-5430, 2016.

- [66] D. Jiménez, "Drift-diffusion model for single layer transition metal dichalcogenide field-effect transistors," *Applied Physics Letters*, vol. 101, no. 24, p. 243501, 2012.

- [67] H. Oughaddou, H. Enriquez, M. R. Tchalala, H. Yildirim, A. J. Mayne, A. Bendounan, G. Dujardin, M. A. Ali, and A. Kara, "Silicene, a promising new 2D material," *Progress in Surface Science*, vol. 90, no. 1, pp. 46-83, 2015.\

- [68] H. Fang, S. Chuang, T. C. Chang, K. Takei, T. Takahashi, and A. Javey, "Highperformance single layered WSe<sub>2</sub> p-FETs with chemically doped contacts," *Nano letters*, vol. 12, no. 7, pp. 3788-3792, 2012.

- [69] H. C. P. Movva, A. Rai, S. Kang, K. Kim, B. Fallahazad, T. Taniguchi, K. Watanabe,

E. Tutuc, and S. K. Banerjee, "High-Mobility Holes in Dual-Gated WSe<sub>2</sub> Field-Effect Transistors," ACS nano, vol. 9, no. 10, pp. 10402-10410, 2015.

- [70] M. Tosun, S. Chuang, H. Fang, A. B. Sachid, M. Hettick, Y. Lin, Y. Zeng, and A Javey, "High-gain inverters based on WSe<sub>2</sub> complementary field-effect transistors," *ACS nano* 8, no. 5, pp. 4948-4953, 2014.

- [71] X. Zeng, H. Hirwa, S. Metel, V. Nicolosi, and V. Wagner, "Solution Processed Thin Film Transistor from Liquid Phase Exfoliated MoS<sub>2</sub> Flakes," *Solid-State Electronics*, Dec 2017.

- [72] G. W. Brown and B. W. Lindsay, "The numerical solution of Poisson's equation for two-dimensional semiconductor devices," *Solid-State Electronics*, vol. 19, pp. 991-992, 1976.

- [73] T. Conklin, T. Naugle, S. Shi, S. Frimel, S. M. Roenker, K. P. Kumar, T. Cahay and M. M. Stanchina, "Inclusion of tunneling and ballistic transport effects in an analytical approach to modeling of NPN InP based heterojunction bipolar transistors," *Superlattices and Microstructures*, vol. 18, pp. 21-32, 1995.

- [74] F. Venturi, R. K. Smith, E. C. Sangiorgi, M. Pinto, and B. Riccó, "A General Purpose Device Simulator Coupling Poisson and Monte Carlo Transport with Applications to Deep Submicron MOSFETs," *IEEE Transaction on Electron Devices*, vol. 8, pp. 360-369, 1989.

- [75] W.B. Joyce and R. W. Dixon, "Analytic approximations for the Fermi energy of an ideal Fermi gas," *Applied Physics Letter*, vol. 31, pp. 354-356, 1977.

- [76] D. J. Rose and R. E. Bank, "Global approximate Newton methods," Numerische Mathematik, pp. 279-295, 1981.

- [77] W. H. Press, B. P. Flannery, S. A. Teukolsky and W. T. Vetterling, "Numerical Recipes: the art of scientific computing," *Cambridge University Press*, Cambridge, New York, 1989.

- [78] Z. Ren, R. Venugopal, S. Goasguen, S. Datta, and M. S. Lundstrom, "nanoMOS 2.5: A two-dimensional simulator for quantum transport in double-gate MOSFETs," *IEEE Transactions on Electron Devices*, vol. 50, no. 9, pp. 1914-1925, 2003.

- [79] O. Kurniawan, P. Bai, and E. Li, "Ballistic calculation of nonequilibrium Green's

function in nanoscale devices using finite element method," *Journal of Physics D: Applied Physics*, vol. 42, no. 10, p. 105109, 2009.

- [80] L. C. Upadhyayula, J. J. Loferski, A. Wold, W. Giriat, and R. Kershaw, "Semiconducting Properties of Single Crystals of n-and p-Type Tungsten Diselenide (WSe<sub>2</sub>)," *Journal of Applied Physics*, vol. 39, no. 10, pp. 4736-4740, 1968.

- [81] G. H. Yousefi. "Optical properties of mixed transition metal dichalcogenide crystals." *Materials Letters*, vol. 9, no. 1, pp. 38-40, 1989.

- [82] S. M. Sze, and K. Ng. Kwok. *Physics of semiconductor devices*. John Wiley & Sons, 2006.

- [83] S. U. Z. Khan, and Q. D. M. Khosru. "Quantum mechanical electrostatics and transport simulation and performance evaluation of short channel monolayer WSe<sub>2</sub> field effect transistor." *ECS Transactions*, vol. 66, no. 14 pp. 11-18, 2015.

- [84] Y. Yoon, K. Ganapathi and S. Salahuddin, Nano Lett., vol. 11, no. 9, p. 3768, 2011.

- [85] C. Yadav, A. Agarwal, and Y. S. Chauhan, "Compact modeling of transition metal dichalcogenide based thin body transistors and circuit validation," *IEEE Transactions on Electron Devices*, vol. 64, no. 3, pp. 1261-1268, 2017.