Surface Potential Based Analytical Modeling of Electrostatic and Transport Characteristics of GaN Junctionless Nanowire MOSFET

A thesis submitted to the

Department of Electrical and Electronic Engineering (EEE)

of

Bangladesh University of Engineering and Technology (BUET)

In partial fulfillment of the requirement for the degree of

MASTER OF SCIENCE IN ELECTRICAL AND ELECTRONIC ENGINEERING

by Md. Irfan Khan Roll No : 1017062249 P

Department of Electrical and Electronic Engineering Bangladesh University of Engineering and Technology

September, 2020

## Approval

The thesis titled "Surface Potential Based Analytical Modeling of Electrostatic and Transport Characteristics of GaN Junctionless Nanowire MOS-FET" submitted by Md. Irfan Khan, Roll No.: 1017062249 P, Session: October 2017, has been accepted as satisfactory in partial fulfillment of the requirements for the degree of MASTER OF SCIENCE IN ELECTRICAL AND ELECTRONIC ENGINEERING on September 22, 2020.

**Board of Examiners**

1. Dr. Quazi Deen Mohd Khosru Chairman Professor (Supervisor) Department of Electrical and Electronic Engineering Bangladesh University of Engineering and Technology, Dhaka THE Zommy 27 2. Dr. Md. Kamrul Hasan Member Professor and Head (Ex-officio) Department of Electrical and Electronic Engineering Bangladesh University of Engineering and Technology, Dhaka 3. Dr. Md. Kawsar Alam

Professor Department of Electrical and Electronic Engineering Bangladesh University of Engineering and Technology, Dhaka

4.

地中北 ?

Dr. Md Zunaid Baten Assistant Professor Department of Electrical and Electronic Engineering Bangladesh University of Engineering and Technology, Dhaka

5.

Dr. Jiban Podder Professor **Department of Physics** Bangladesh University of Engineering and Technology, Dhaka

2

Member (External)

Member

Member

ii

## Declaration

It is hereby declared that this thesis or any part of it has not been submitted elsewhere for the award of any degree or diploma.

Signature of the candidate

MD. IRFAN KHAN

(Md. Irfan Khan) Roll No: 1017062249 P

# To my beloved parents

## Acknowledgement

I would like to express my earnest gratitude and heartfelt appreciation to my thesis supervisor Dr. Quazi Deen Mohd Khosru, Professor, Department of Electrical and Electronic Engineering, BUET for his invaluable assistance, guidance and encouragement while pursuing my Master of Science thesis. I would hardly be able to achieve success in my endeavor if I did not receive his consistent support.

I also express my gratitude to Dr. Md. Kamrul Hasan, Head, Department of Electrical and Electronic Engineering (EEE), BUET, for endowing me with a perfect ambiance for continuing my research. My gratitude also extends to EEE department for granting the required tools and guidance for my research.

I would like to express my gratitude to the members of my thesis committee, Prof. Dr. Md. Kamrul Hasan, Prof. Dr. Md. Kawsar Alam, Dr. Md Zunaid Baten and Prof. Dr. Jiban Podder for their thoughtful review and constructive suggestion on my work.

I want to express my gratitude to I. K. M. Reaz Rahman, Lecturer, Department of EEE, BUET, for his kind and sincere helps and discussions in solving various problems pertaining to the thesis work.

I would like to thank my parents, Md. Abdul Jalil Khan and Razia Khatun. I also want to dedicate my thesis to them. They have helped me in every possible way throughout this journey. This thesis work would not have been possible without their help.

Finally I owe my sincere gratitude to all of my teachers, as well as friends, classmates and seniors for their valuable inputs and constant encouragement.

### Abstract

Since tradition planar Metal Oxide Semiconductor Field Effect Transistors (MOSFETs) has reached their scaling limit, further miniaturization, without degradation of device performance, has become very difficult due to sever short channel effect and high complexity of fabrication process resulted from ultra sharp source and drain junction requirement. Junctionless (JL) nanowire (NW) MOSFETs are considered promising for the sub-20 nm era due to their constant doping profile from source to drain. They provide a great scalability without the need for rigorously controlled doping and activation techniques as well as reduced short channel effects (SCEs) compared to the conventional MOSFETs. With its superior electronic properties compared to Si, GaNhas shown its potential as a viable alternative of Si as a channel material in ultra scaled devices. Though a number of experimental studies for GaN JL NW MOSFET have been carried out over the past few years, rigorous and accurate analytical study of this device is yet to be reported. This work presents a physically based comprehensive analytical investigation of electrostatic and transport phenomena of GaN JL NW MOSFET. The evolution of the proposed model involves the solution of quasi 2-D Poisson's equation with appropriate boundary condition to obtain effective surface potential as a function of gate voltage. The mobile carrier density derived from the surface potential is used to formulate the core transport model as well as to analyze the electrostatic characteristics for various physical device parameters. Short channel effects and certain non-ideal effects including velocity saturation, mobility degradation, channel length modulation have been incorporated in the core transport model. The impact of physical device parameters including channel length, NW radius and oxide thickness on the performance metrics of the device such as subthreshold slope (SS), drain induced barrier lowering (DIBL) and threshold voltage has been rigorously investigated. Upon analyzing the transport properties of the device, steep SS of 68 mV/dec, DIBL of 27 mV/V and switching figure of merit  $Q(=~g_m/SS)$  of 0.16  $(\mu S/\mu m/(mV/dec)$ have been attained which makes the GaN NW JL MOSFET a promising candidate for emerging low power application. The results of this work exhibit very good agreement with 3D TCAD simulation and reported experimental results and thereby enhancing the reliability of the proposed model.

# Contents

| $\mathbf{A}$ | ppro  | val    |                                         | ii   |  |  |  |  |  |  |  |  |

|--------------|-------|--------|-----------------------------------------|------|--|--|--|--|--|--|--|--|

| Declaration  |       |        |                                         |      |  |  |  |  |  |  |  |  |

| A            | cknov | wledge | ment                                    | v    |  |  |  |  |  |  |  |  |

| Abstract     |       |        |                                         |      |  |  |  |  |  |  |  |  |

| C            | onter | nts    |                                         | vii  |  |  |  |  |  |  |  |  |

| Fi           | gure  | S      |                                         | x    |  |  |  |  |  |  |  |  |

| Ta           | ables |        |                                         | xiii |  |  |  |  |  |  |  |  |

| 1            | Intr  | oducti | on                                      | 1    |  |  |  |  |  |  |  |  |

|              | 1.1   | Currer | nt Trend of CMOS Scaling                | 1    |  |  |  |  |  |  |  |  |

|              | 1.2   | CMOS   | S Scaling Challenges                    | 2    |  |  |  |  |  |  |  |  |

|              |       | 1.2.1  | Short Channel Effect (SCE)              | 3    |  |  |  |  |  |  |  |  |

|              |       | 1.2.2  | Hot Carrier Effects                     | 3    |  |  |  |  |  |  |  |  |

|              |       | 1.2.3  | Channel Length Modulation (CLM)         | 4    |  |  |  |  |  |  |  |  |

|              |       | 1.2.4  | Drain Induced Barrier Lowering (DIBL)   | 4    |  |  |  |  |  |  |  |  |

|              |       | 1.2.5  | Gate Oxide Leakage                      | 5    |  |  |  |  |  |  |  |  |

|              |       | 1.2.6  | Velocity Saturation                     | 5    |  |  |  |  |  |  |  |  |

|              |       | 1.2.7  | Gate Induced Drain Leakage (GIDL)       | 5    |  |  |  |  |  |  |  |  |

|              |       | 1.2.8  | Impact Ionization                       | 6    |  |  |  |  |  |  |  |  |

|              |       | 1.2.9  | Surface Scattering                      | 6    |  |  |  |  |  |  |  |  |

|              | 1.3   | Altern | ative Solution to Continue CMOS Scaling | 6    |  |  |  |  |  |  |  |  |

7

|          |                                                                | 1.3.2 Alternative Channel Material                                  | 9                                                                                  |

|----------|----------------------------------------------------------------|---------------------------------------------------------------------|------------------------------------------------------------------------------------|

|          | 1.4                                                            | Junctionless Transistor                                             | 9                                                                                  |

|          |                                                                | 1.4.1 Basic Device Structure                                        | 10                                                                                 |

|          |                                                                | 1.4.2 Operating Principal of the Device                             | 14                                                                                 |

|          |                                                                | 1.4.3 Advantages of the Device                                      | 19                                                                                 |

|          | 1.5                                                            | Literature Review of Junctionless Transistor                        | 23                                                                                 |

|          | 1.6                                                            | Objective of the Thesis                                             | 30                                                                                 |

|          | 1.7                                                            | Organization of the Thesis                                          | 31                                                                                 |

| <b>2</b> | Elec                                                           | ctrostatic Model Development                                        | 33                                                                                 |

|          | 2.1                                                            | Surface Potential Model                                             | 34                                                                                 |

|          |                                                                | 2.1.1 Channel in Accumulation Mode                                  | 35                                                                                 |

|          |                                                                | 2.1.2 Channel in Depletion Mode                                     | 36                                                                                 |

|          |                                                                | 2.1.3 Continuous Surface Potential from Depletion to Accumulation . | 38                                                                                 |

|          | 2.2                                                            | Capacitance-Voltage Characteristics                                 | 39                                                                                 |

|          | 2.3                                                            | Threshold Voltage Calculation                                       | 39                                                                                 |

| 3        | Tra                                                            | nsport Model Development                                            | 41                                                                                 |

|          | 3.1                                                            | SCE Correction                                                      | 41                                                                                 |

|          |                                                                |                                                                     |                                                                                    |

|          | 3.2                                                            | Velocity Saturation                                                 | 45                                                                                 |

|          | 3.2<br>3.3                                                     | Velocity Saturation                                                 |                                                                                    |

|          |                                                                | •                                                                   | 45                                                                                 |

|          | 3.3                                                            | Channel Length Modulation                                           | 45<br>46                                                                           |

|          | 3.3<br>3.4                                                     | Channel Length Modulation                                           | 45<br>46<br>46                                                                     |

| 4        | <ol> <li>3.3</li> <li>3.4</li> <li>3.5</li> <li>3.6</li> </ol> | Channel Length Modulation                                           | 45<br>46<br>46<br>46                                                               |

| 4        | <ol> <li>3.3</li> <li>3.4</li> <li>3.5</li> <li>3.6</li> </ol> | Channel Length Modulation                                           | 45<br>46<br>46<br>46<br>47                                                         |

| 4        | 3.3<br>3.4<br>3.5<br>3.6<br>Sim                                | Channel Length Modulation                                           | <ul> <li>45</li> <li>46</li> <li>46</li> <li>46</li> <li>47</li> <li>48</li> </ul> |

| 4        | 3.3<br>3.4<br>3.5<br>3.6<br>Sim                                | Channel Length Modulation                                           | 45<br>46<br>46<br>47<br><b>48</b><br>48                                            |

| 4        | 3.3<br>3.4<br>3.5<br>3.6<br>Sim                                | Channel Length Modulation                                           | 45<br>46<br>46<br>47<br><b>48</b><br>48<br>50                                      |

| 4        | 3.3<br>3.4<br>3.5<br>3.6<br>Sim                                | Channel Length Modulation                                           | 45<br>46<br>46<br>47<br><b>48</b><br>48<br>50<br>51                                |

| 4        | 3.3<br>3.4<br>3.5<br>3.6<br>Sim                                | Channel Length Modulation                                           | 45<br>46<br>46<br>47<br><b>48</b><br>48<br>50<br>51<br>57                          |

| 5             | $\operatorname{Res}$                                                                                                                             | ults and Discussions       | 60 |  |  |  |  |  |  |

|---------------|--------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------|----|--|--|--|--|--|--|

| 6             | Con                                                                                                                                              | clusion                    | 72 |  |  |  |  |  |  |

|               | 6.1                                                                                                                                              | Summary                    | 72 |  |  |  |  |  |  |

|               | 6.2                                                                                                                                              | Suggestion for Future Work | 73 |  |  |  |  |  |  |

| $\mathbf{Li}$ | 6.1       Summary       Summary       Summary         6.2       Suggestion for Future Work       Suggestion         List of Publications       ' |                            |    |  |  |  |  |  |  |

| Bi            | Bibliography                                                                                                                                     |                            |    |  |  |  |  |  |  |

# List of Figures

| 1.1  | Scaling trend of high performance logic technologies with year [3]. $\ldots$ $\ldots$        | 2  |

|------|----------------------------------------------------------------------------------------------|----|

| 1.2  | Schematic illustration of hot carrier effects in MOSFETs                                     | 3  |

| 1.3  | Schematic illustration of channel length modulation effect                                   | 4  |

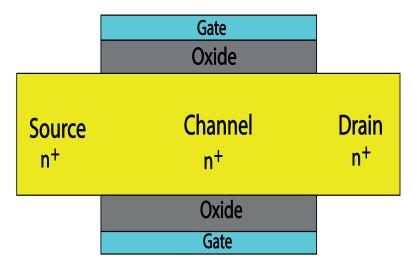

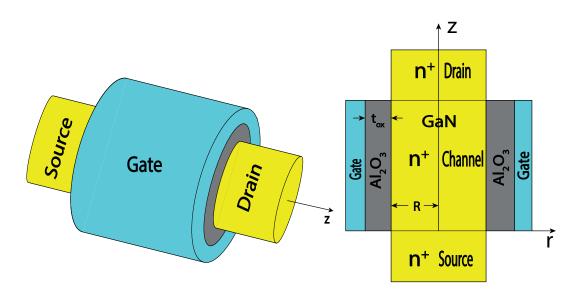

| 1.4  | Three Dimensional Schematic View of JL NW MOSFET                                             | 11 |

| 1.5  | 2D Schematic Cutout along Channel of a NW JL MOSFET                                          | 13 |

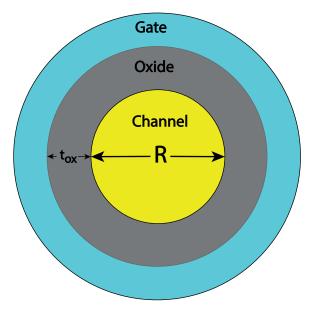

| 1.6  | Radial Cross Section of a NW JL MOSFET                                                       | 13 |

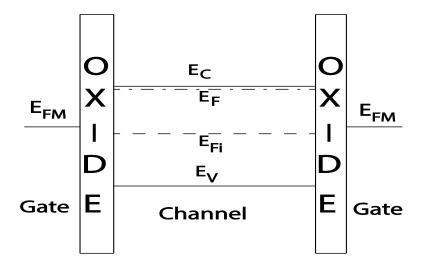

| 1.7  | Energy Band Diagram of n-channel NW JL MOSFET before Junction For-                           |    |

|      | mation                                                                                       | 15 |

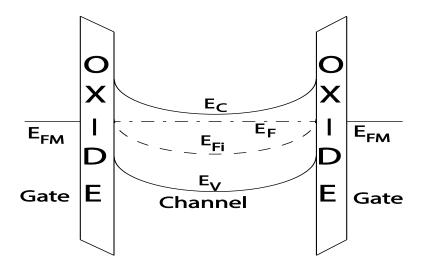

| 1.8  | $Energy \ Band \ Diagram \ of \ n-channel \ NW \ JL \ MOSFET \ in \ Full \ Depletion  .$     | 16 |

| 1.9  | $Energy \ Band \ Diagram \ of \ n-channel \ NW \ JL \ MOSFET \ in \ Partial \ Depletion \ .$ | 17 |

| 1.10 | Energy Band Diagram of n-channel NW JL MOSFET in Flat Band $\ldots$                          | 18 |

| 1.11 | I/V Characteristic of n-channel (a) IM-FET (b) AMFET (c) GAA-JL FET                          |    |

|      | Showing Relative Positions of Threshold and Flat Band Voltage. Figure ex-                    |    |

|      | tracted from [40]                                                                            | 18 |

| 1.12 | Energy Band Diagram of n-channel NW JL MOSFET in Accumulation                                | 19 |

| 2.1  | Schematic view of an N-channel GaN NW JL MOSFET (a) and its longitu-                         |    |

|      | dinal cross section $(b)$                                                                    | 33 |

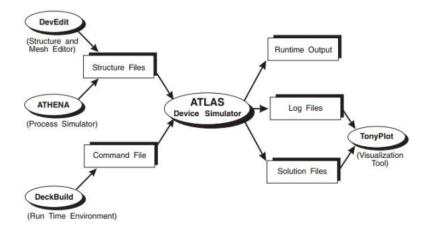

| 4.1  | ATLAS inputs and outputs                                                                     | 49 |

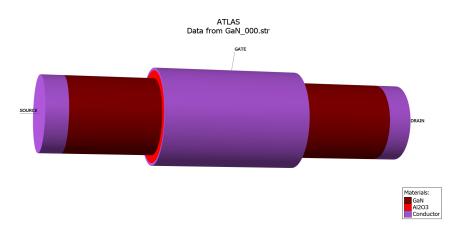

| 4.2  | GaN NW JL MOSFET 3D structure for TCAD simulation                                            | 51 |

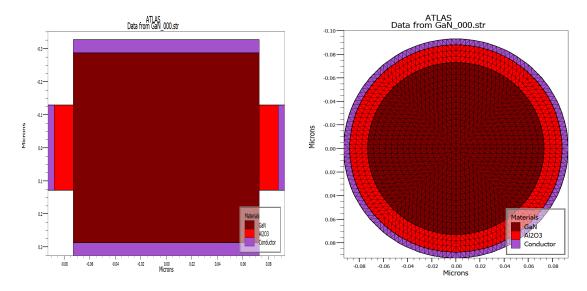

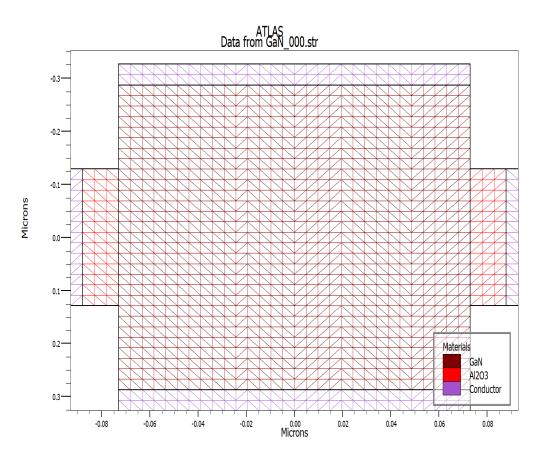

| 4.3  | 2D Cross-section of GaN NW JL MOSFET along (a)transport direction                            |    |

|      | (b)radial direction                                                                          | 51 |

| 4.4  | Mesh points of GaN NW JL MOSFET                                                              | 52 |

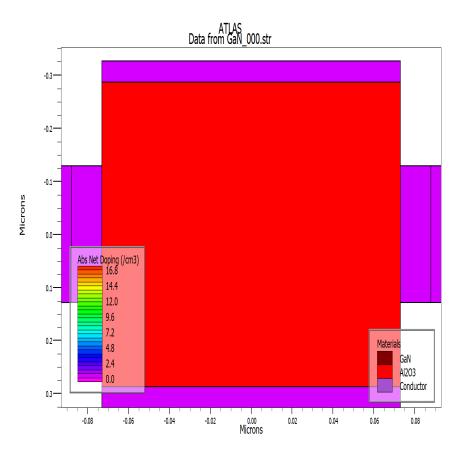

| 4.5  | Net doping in different regions for GaN NW JL MOSFET                                         | 55 |

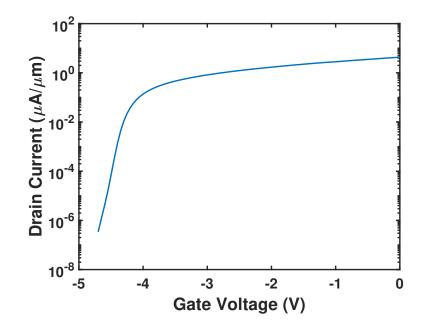

| 4.6  | Transfer characteristics of GaN NW JL MOSFET extracted from Silvaco                                                |    |

|------|--------------------------------------------------------------------------------------------------------------------|----|

|      | ATLAS simulation for $V_{ds} = 0.5V$ , $N_D = 1e18cm^{-3}$ , $R = 73nm$ and $t_{ox} =$                             |    |

|      | 16 nm                                                                                                              | 58 |

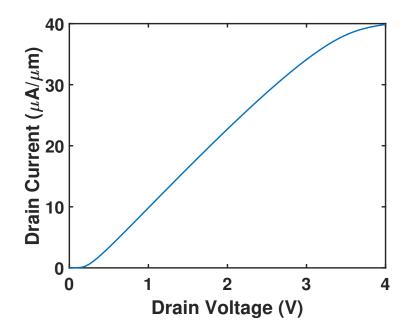

| 4.7  | Output characteristics of GaN NW JL MOSFET extracted from Silvaco AT-                                              |    |

|      | LAS simulation for $V_{gs} = 0$ , $N_D = 1e18cm^{-3}$ , $R = 73nm$ and $t_{ox} = 16 nm$ .                          | 59 |

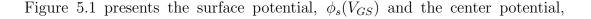

| 5.1  | Electrostatic potential at the surface and the symmetry axis of GaN NW JL                                          |    |

|      | MOSFET                                                                                                             | 60 |

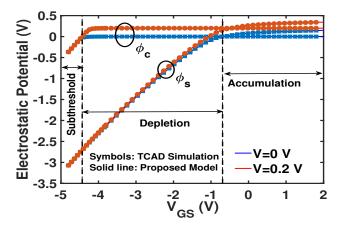

| 5.2  | Conduction band potential profile along radial coordinate for gate voltage val-                                    |    |

|      | ues (a) below threshold and (b) above threshold $\ldots \ldots \ldots \ldots \ldots \ldots$                        | 61 |

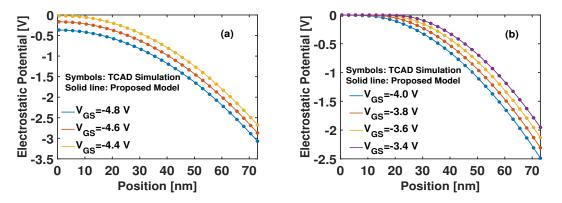

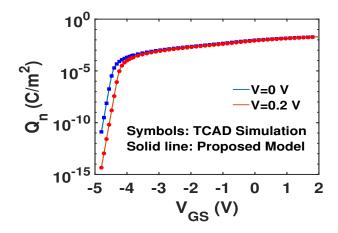

| 5.3  | Comparison between simulated and modeled space charge density per unit of                                          |    |

|      | area as a function of $V_{GS}$                                                                                     | 61 |

| 5.4  | Variation of mobile carrier density per unit of area as a function of $V_{GS}$                                     | 62 |

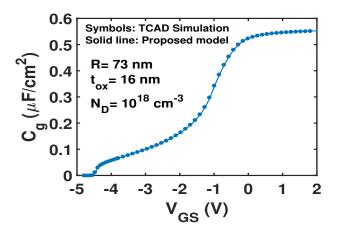

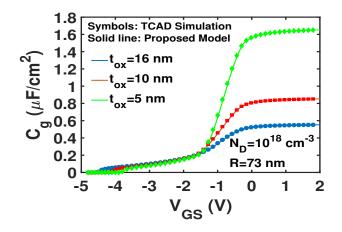

| 5.5  | Gate capacitance per unit area as a function of $V_{GS}$                                                           | 62 |

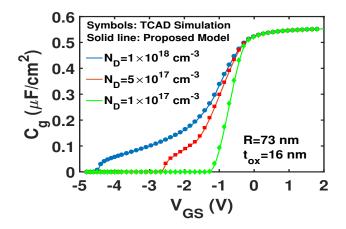

| 5.6  | Comparison between simulated and modeled gate capacitance as a function of                                         |    |

|      | the $V_{GS}$ for different doping concentrations $\ldots \ldots \ldots \ldots \ldots \ldots \ldots$                | 63 |

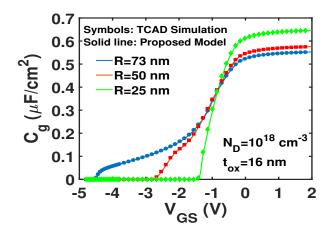

| 5.7  | Comparison between simulated and modeled gate capacitance as a function of                                         |    |

|      | the $V_{GS}$ for different nanowire radius $\ldots \ldots \ldots \ldots \ldots \ldots \ldots \ldots \ldots$        | 63 |

| 5.8  | Comparison between simulated and modeled gate capacitance as a function of                                         |    |

|      | the $V_{GS}$ for different oxide thickness $\ldots \ldots \ldots \ldots \ldots \ldots \ldots \ldots \ldots$        | 64 |

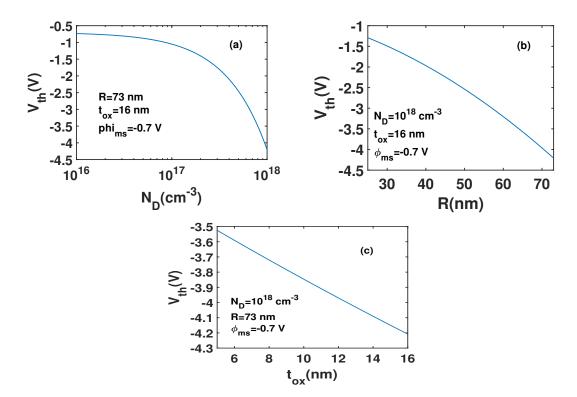

| 5.9  | Threshold voltage variation with (a) doping concentration (b) NW radius (c)                                        |    |

|      | oxide thickness                                                                                                    | 65 |

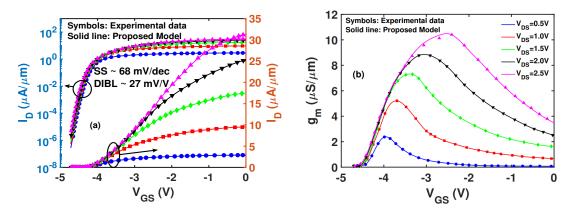

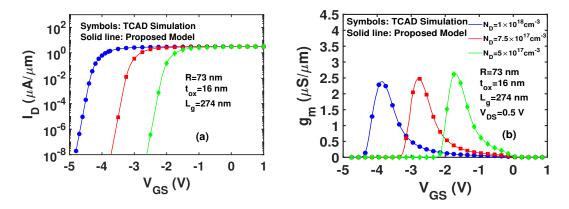

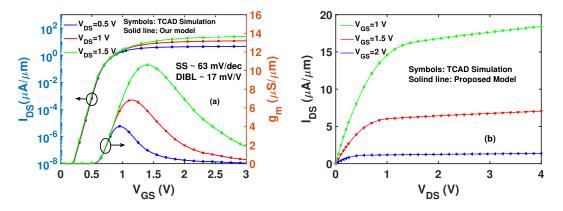

| 5.10 | (a) Transfer characteristics and (b) transconductance for different $V_{DS}$ . The                                 |    |

|      | device parameters are $N_D = 10^{18} \text{ cm}^{-3}$ , $R = 73 \text{ nm}$ , $t_{ox} = 16 \text{ nm}$ and $L_g =$ |    |

|      | 274 nm. The experimental data has been extracted from [71]                                                         | 66 |

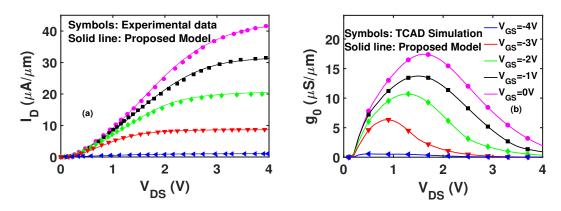

| 5.11 | (a) Output characteristics and (b) output conductance for different $V_{GS}$ . The                                 |    |

|      | device parameters are $N_D = 10^{18} \text{ cm}^{-3}$ , $R = 73 \text{ nm}$ , $t_{ox} = 16 \text{ nm}$ and $L_g =$ |    |

|      | 274 nm. The experimental data has been taken from [71]                                                             | 66 |

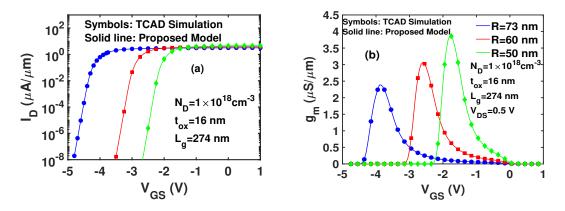

| 5.12 | (a) Transfer characteristics and (b) transconductance for different nanowire                                       |    |

|      | doping                                                                                                             | 67 |

| 5.13 | (a) Transfer characteristics and (b) transconductance for different nanowire                                       |    |

|      | radius.                                                                                                            | 67 |

|      |                                                                                                                    |    |

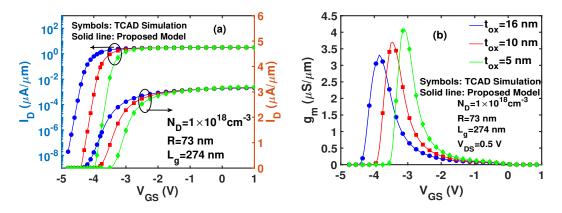

| 5.14 | (a) Transfer characteristics and (b) transconductance for different oxide thick-                               |    |

|------|----------------------------------------------------------------------------------------------------------------|----|

|      | ness                                                                                                           | 68 |

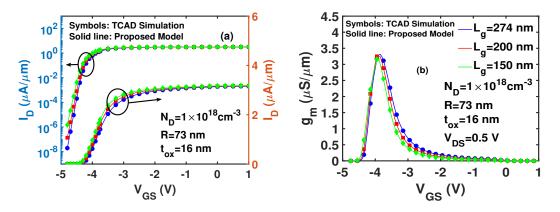

| 5.15 | (a) Transfer characteristics and (b) transconductance for different gate length.                               | 68 |

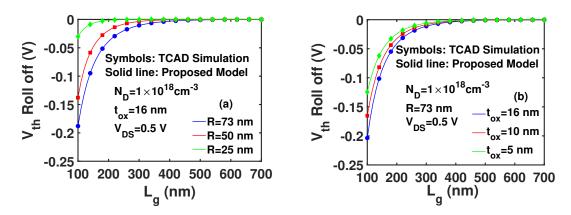

| 5.16 | Variation of threshold voltage roll off with channel length for various $(a)$                                  |    |

|      | nanowire radius and (b) oxide thickness                                                                        | 69 |

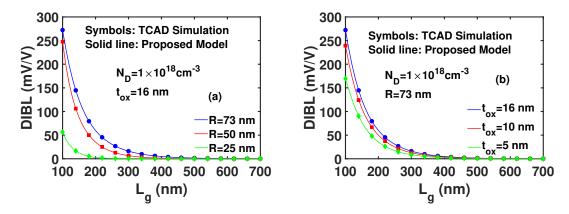

| 5.17 | Variation of DIBL with channel length for various (a) nanowire radius and                                      |    |

|      | (b) oxide thickness. $\ldots$ | 69 |

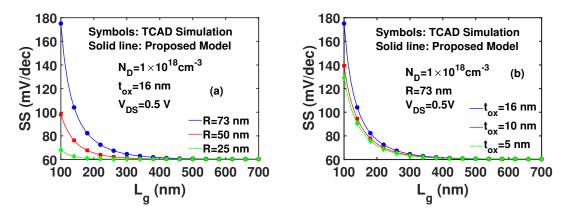

| 5.18 | Variation of subthreshold slope with channel length for various (a) nanowire                                   |    |

|      | radius and (b) oxide thickness.                                                                                | 70 |

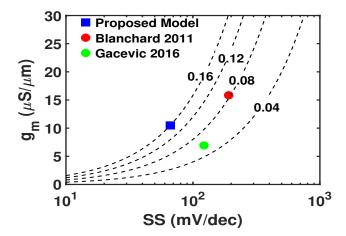

| 5.19 | Benchmark plot of $g_m$ versus SS for GaN NW JL MOSFET. The square                                             |    |

|      | represents the $g_m$ in this work which has been compared with Blanchard 2011                                  |    |

|      | [69] and Gacevic 2016 [70]. The dashed lines are the constant $g_m/SS$ contour.                                |    |

|      | The device parameters are $N_D = 10^{18} \text{ cm}^{-3}$ , $R = 73 \text{ nm}$ , $t_{ox} = 16 \text{ nm}$ and |    |

|      | $L_g = 274 \ nm.$                                                                                              | 70 |

| 5.20 | (a) Transfer characteristics and transconductance for different $V_{DS}$ and (b)                               |    |

|      | output characteristics for different $V_{GS}$ of GaN NW JL MOSFET in low                                       |    |

|      | voltage normally-off operation. The device parameters set for this operation                                   |    |

|      | are $N_D = 10^{18} \ cm^{-3}$ , $R = 50 \ nm$ , $t_{ox} = 10 \ nm$ and $L_g = 274 \ nm$ and                    |    |

|      | $\phi_{ms} = 1.3V.$                                                                                            | 71 |

# List of Tables

| 3.1 | Parameters used in this work | • | • | • | • | • | • | • | • | • | • | • | • | • | • | • | • | • | • | • | • | • | • | • | 45 |

|-----|------------------------------|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|----|

| 4.1 | ATLAS command groups         |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   | 50 |

## Chapter 1

## Introduction

This chapter elaborates on the fundamental concepts pertaining to technology scaling along with the origin and impact of non ideal effects in nanoscale Metal Oxide Semiconductor Field Effect Transistors (MOSFETs). It also presents a brief overview of Junctionless (JL) Field Effect Transistors followed by an rigorous study of existing literature. In addition, it covers the objectives and outline of the thesis.

### 1.1 Current Trend of CMOS Scaling

Over the past few decades, the computing and communication technologies have played as driving forces in the world economy. About more than 10% of the world economy is built on electronics market and this parcentage is continuously growing. This revolution in semiconductor technology commenced from the invention of the first solid-state device, a bipolar point contact transistor on Germaniun (Ge) substrate, invented by Bardeen, Brattain, and Shockly at Bell labs in 1947. Complementary metal-oxidesemiconductor (CMOS) field-effect-transistor has almost replaced bipolar transistor because the former offers lower power and technology advantages. The outstanding performance and scalability of CMOS have encouraged Intel's co-founder Gordon Moore to make a famous prediction about device scaling. In 1965, Gordon Moore predicted that the number of components per integrated chip will be doubled every year [1]. He revised his prediction in 1975 stating that the doubling will happen approximately in every two years [2]. This prediction, known as "moore's Law", has been acting as a guideline for the semiconductor industry to set their goals and made them push harder to break the frontier of technology through constant innovation.

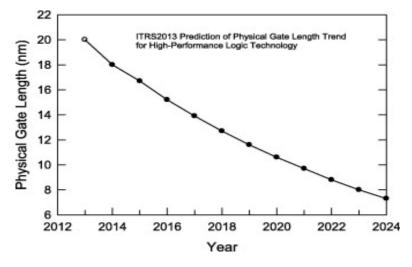

Figure 1.1: Scaling trend of high performance logic technologies with year [3].

cessfully reduced by more than two orders of magnitude according to Moore's law until now and International Technology Roadmap of Semiconductors 2012 (ITRS) recently foresaw that the minimum feature size will still decrease from 22 nm in 2011 to around 7 nm in 2024 as displayed in figure 1.1.

### **1.2 CMOS Scaling Challenges**

As the MOSFET dimensions are decreasing, it is difficult to keep long channel behavior due to the unwanted side effects [4]. With the continuous reduction of channel length in deep sub-micron region, some unavoidable effects namely, short channel effects, channel length modulation, drain induced barrier lowering, mobility degradation with vertical field, velocity saturation etc. come into play. We will discuss them qualitatively as below. Researchers have tried to reduce them through different techniques like gate engineering, channel engineering, implementing different device architecture with different working physics etc. Although they are able to reduce it to some extent, it is extremely difficult to nullify this effects in ultra short channel lengths with a single gate control on the silicon region.

#### **1.2.1** Short Channel Effect (SCE)

The short channel effect (SCE) is the decrease of threshold voltage of a MOSFET as the channel length is reduced. It is prominent when drain bias is equal to the power supply voltage. the important difference of long and short channel MOSFET is that, in a long channel MOSFET, the electrostatics of the channel region is controlled by the gate; however, for short channel MOSFET, besides gate, source and drain regions also try to control the channel electrostatics. Therefore, it is now a 2D problem instead of 1D that is valid for a long channel MOSFET. The charge sharing from source and drain regions decreases the threshold voltage of the device [5, 6].

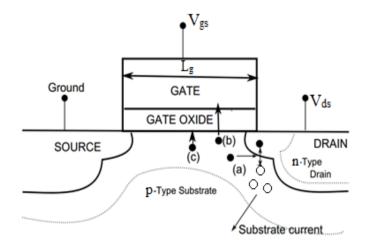

Figure 1.2: Schematic illustration of hot carrier effects in MOSFETs.

#### **1.2.2** Hot Carrier Effects

After fabricating a certain device there should not be a drift in performance of the device over time. But hot carrier effect leads to the drift over certain period of operation. This is more dominant in short channel devices where the electric field is higher. The three kind of possible hot carrier injection mechanisms are illustrated in figure 1.2 as mentioned below.

- Carriers generated due to impact ionization on the drain side can multiply and lead to a heavy substrate current.

- The carriers having energy higher than the silicon/gate dielectric conduction band offset can lead to a conduction current to the gate.

• The sufficient high energy electrons can damage the silicon/gate dielectric interface leading to degradation in important device parameters like drain current, threshold voltage etc. [7, 8]

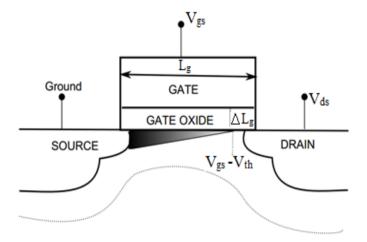

Figure 1.3: Schematic illustration of channel length modulation effect.

#### 1.2.3 Channel Length Modulation (CLM)

When drain to source voltage,  $V_{DS} > V_{GS} - V_T$ ,  $I_D$  is relatively constant and we say the device operates in saturation region. The local density of inversion layer charge  $(Q_d(x))$  is proportional to  $V_{GS} - V(x) - V_T$ , where V(x) is the channel potential at x (x is along the channel direction). Thus, if V(x) approaches  $V_{GS} - V_T$ , then  $Q_d(x)$  drops to zero. This implies that if  $V_{DS}$  is slightly greater than  $V_{GS} - V_T$ , the inversion layer stops at  $x \leq L$  and we say the channel is "pinched off". If  $V_{DS}$  is increased further, the point at which  $Q_d$  is equal to zero approaches towards source. Therefore, at some point along the channel, the local potential difference between the gate and the oxide-silicon interface is not sufficient to support an inverted channel (figure 1.3). That is, the actual length of the inverted channel gradually decreases as the potential difference between gate and drain increases. This effect is known as channel length modulation. This phenomena results in a nonzero slope in the saturation region of  $I_D/V_{DS}$  characteristics [9, 10, 11]

#### **1.2.4** Drain Induced Barrier Lowering (DIBL)

This phenomena occurs when gate voltage is less than the threshold voltage of the device. When drain and source voltages are equal, the depletion region beneath the

source and drain are equal as they are equally doped. Now, with increase in  $V_{DS}$ , the depletion region below the drain region is more to compensate with the extra potential connected to drain. For short channel length devices, the electrostatics is not only controlled by the gate but also by the source and drain region. The charges in the drain region contribute to the depletion potential and the barrier between source and channel region decreases. As a result, threshold voltage decreases. This phenomenon is called drain induced barrier lowering. It is determined as the threshold voltage different when  $V_{DS}$  changes from 50 mV to 1 V [12, 13].

#### 1.2.5 Gate Oxide Leakage

Silicon dioxide  $(SiO_2)$  is a good insulator to be used in the MOS structure. But when gate oxide thickness is reduced to less than 2 - 3nm, tunneling probability increases and results in an increase of oxide leakage current [14, 15]. High- $\kappa$  dielectric is used to solve this problem to some extent, as high- $\kappa$  dielectric can provide a similar gate electric field even with a physically thick gate dielectric. This can reduce the direct tunneling leakage.

#### 1.2.6 Velocity Saturation

The mobility of the carriers depend on the lateral electric field as well. It begins to drop as the field reaches a value of 1  $v/\mu m$ . Thus, the carrier velocity,  $v(=\mu E)$  reaches a saturated value (  $10^7 \ cm/s$ ) for sufficiently high fields along the channel at some point. The parameters,  $\mu$  and E are the carrier mobility and low electric field respectively. The current thus produced is linearly proportional to overdrive voltage and does not depend on length [16, 17].

#### 1.2.7 Gate Induced Drain Leakage (GIDL)

With a high drain bias and a low gate voltage, the electric field in the gate/drain overlap region is high. Therefore, if the band bending of the gate/drain overlap region at the oxide interface is greater than or equal to the energy band gap  $E_g$  of the drain material, band to band tunneling will take place. The electron in the valance band of the drain will tunnel through the thinned band gap into the conduction band and they will be collected at the drain contact to be a part of the drain current, whereas the remaining holes will be collected at the substrate contact and will contribute to substrate leakage. This phenomenon, first elucidated and modeled in 1987 [18], discerns a potential major contributor to the off-state leakage current and is called the gate induced drain leakage (GIDL) current [19].

#### **1.2.8** Impact Ionization

In the transistor on state, because of the high electric field near the drain end of the channel, carriers in this region can gain enough kinetic energy to ionize the lattice atoms when they collide. This collision frees an electron from the valance-band and leaves a hole behind. The generated hole will drift to the substrate and it will increase the substrate leakage. The released high-energy electron (hot carrier) is collected by the drain and it will be a part of the drain current [20, 21].

#### **1.2.9** Surface Scattering

As the channel length becomes smaller, due to lateral extension of the depletion layer in to the channel region, the longitudinal electric field increases and the surface mobility becomes field-dependent. In the saturated or strong inversion region, the carriers are confined within the narrow inversion layer in a MOSFET. The carriers experience collision suffered by the electrons that are accelerated toward the interface and drain by the vertical electric field. This is called surface scattering which causes reduction of the mobility and this in turn affects both the drain current and transconductance [22, 23].

## 1.3 Alternative Solution to Continue CMOS Scaling

The increasing difficulties in Si CMOS scaling has created the need of investigation of alternative channel materials and device architectures. Many improvements , in terms of including channel doping profile, gate stack, source/drain design, mechanical strain engineering, three-dimensional architectures with multi-gates and alternate channel material have been proposed to overcome the scaling challenges of Si CMOS and enhance device performance.

#### **1.3.1** Alternative Device Architecture

In the 90's, retrograde channel doping profiles in the channel allowed punch-through and other SCEs to be better controlled. It also reduced the junction capacitance and threshold voltage sensitivity to substrate bias.

MOS transistor require high gate capacitance to attract charge to the channel. This results into very thin  $SiO_2$  gate dielectric. As a gate leakage current increases unacceptably with decrease of gate oxide thickness in each technology node. To circumvent this issue, high- $\kappa$  gate dielectric, such as  $Al_2O_3$ ,  $HfO_2$ ,  $ZrO_2$ ,  $Y_2O_3$ ,  $La_2O_3$ ,  $Ta_2O_5$  and  $TiO_2$  have been introduced, since they ensure same capacitance with a thicker physical thickness compared to  $SiO_2$ .

The Lightly Doped Drain (LDD) was introduced to enhance performance of ultra-scaled device. In the LDD structure, narrow, self-aligned,  $n^-$  regions are introduced between the channel and the  $n^+$  source-drain diffusion. This structure increase breakdown voltage and reduces impact ionization (and thus hot-electron emission) by spreading the high electric field at the drain pinch-off region into the  $n^-$  region. This allows either an increase in power supply voltage or a reduction in channel length at a given voltage to achieve a performance enhancement [24, 25].

Silicon on insulator (SOI) based devices have less difficulty in controlling SCEs compared to planar bulk Complementary MOS (CMOS) devices. A thin channel body the SOI substrate can successfully remove most problems regarding current leakage through the substrate and punch through effect [26, 27]. It also allows the channel to be lightly doped, giving rise to higher speed. However, there are disadvantages of SOI such as expensive wafer cost, the kink effect due to floating body effect and worse heat conduction.

Strain engineering can give the improvement of device mobility, since the Si crystal

lattice constant altered by external applied stress causes the changing of the band structure, the density of states and the effective mass of the carriers. For instance, embedded SiGe source/drain produces a compressive stress in the channel due to its larger lattice constant than Si. This improves holes mobility in pMOS devices. SiC source/drain structures can also lead to the electron mobility.

As the channel length of tradition bulk MOSFET became smaller in each technology node, the short channel effect induced device degradation became severe. To overcome this problem multiple gate device architecture was introduced. The most simple structure among different multi-gate architectures is the double gate (DG) MOSFET which was first reported in 1984 [28]. Compare to bulk single gate MOSFET, DG MOSFET has two insulated gates known as upper gate and lower gate. Due to presence of two gate, DG MOSFET ensures better electrostatic control over the channel and showcases stronger immunity to short channel related issues compared to single gate device [29]. Three dimensional MOSFET structures was considered several decades ago to be very important for the achievement of superior performance in ultra scaled. But the problems arisen due to floating substrate impeded the integration of 3-D devices in practical circuit. To eliminate the floating substrate issue, a novel structure called fully depleted lean-channel transistor (DELTA) was proposed [30]. The key feature of this device structure include induction of ultra thin SOI effects, formation of bulk single crystal SOI so that neither re-crystallization technology nor SIMOX was required, and channel formation on a vertical surface. This revolutionary device structure paved the way to the proposition of novel self-aligned double-gate MOSFET, popularly known as FinFET [31]. FinFET has not only suppressed the short channel effect, but also solved the complexity of DG MOSFET fabrication process due to incompatibility of gate-channel-gate structure with Si-planar technology.

Among all multigate device structure the gate all around (GAA) MOSFET has been the most attractive since it guarantees the best electrostatic control. The first GAA device, published in 1990, was in reality a double-gate transistor although the gate electrode did wrap around all sides of the channel region [32]. Nowadays the term "GAA" is preferentially used to describe a nanowire-like MOSFET where the gate is wrapped around the channel region. Using such gate architectures, it is even possible to fabricate MOSFET devices without introducing pn junctions for the source and drain [33] .Such "junctionless" (JL) multigate transistors have a great potential for greatly simplifying the MOSFET fabrication process at the nanometer length scale. It is also possible to insert electron trap layers or nanocrystals in the gate dielectric to create nanowire flash memory transistors [34].

#### 1.3.2 Alternative Channel Material

New channel materials like germanium (Ge) [35] and III-V compound semiconductor [36] have introduced an era of ultra-low-power and high-speed devices. Recently, two dimensional (2D) layered materials (bilayer graphene, bilayer  $MoS_2$ ) have supported field-controlled bandgap tuning [37]. It gives a new platform to design new electronic and optoelectronic devices. However, a high quality gate dielectric is required to apply large vertical electric fields in such devices. Such attempts for high mobility materials are facing fabrication challenges, as these materials can support either n type (III-V compound semiconductor) or p type (Ge) devices but not both, which are required for CMOS circuit designs. The quantum confinement effects, which are dependent on material thickness scaling can be used as a powerful techniques to optimize the material properties, because materials having different thicknesses can be viewed as different materials with entirely different properties. This sets a new platform for electronics and optoelectronic applications.

### 1.4 Junctionless Transistor

Since its inception, Junctionless(JL) MOSFET, also called gate resistor has emerged as a strong candidate for future technology node. The device has showcased significant potential in the Nanoscale transistor industry due to its reduced short channel effects and fabrication constraints. Many research groups are focusing on this device as it might become a breakthrough to the frontiers of nanoscale MOSFETs.

#### **1.4.1** Basic Device Structure

The nanowire (NW) JL MOSFET device structure contains two major regions : The channel and the gate.

The primary element of the JL device is the channel. It indicates the major path for current flow in the transistor. It is usually fabricated from lightly doped p or n type semiconductor material. No distinct p-n junction is present in the channel region in the path of current flow. The device properties change polarity along with dopant material. That is, the applied voltage polarity for activation and direction of current flow switches side along with dopant polarity. For simplicity, the n-channel JL FET can be compared with the NMOS structure, while p-channel JL FET is to be compared against PMOS.

The channel consists of two terminals along two distinct edges: the drain terminal and the source terminal. Like normal FET structures, the terminals are completely identical and interchangeable, even during device operations. In case of n-channel JL MOSFET, the terminal with higher voltage is known as the drain terminal and the lower is referred to the source. With switching of terminal voltage during operation, the terminal polarity switches sides. However, in case of p-channel device, the lower voltage terminal is referred to the drain and the higher one is source, to comply with the PMOS notations. As a result, channel current in n-channel device flows from drain to source, and hence it is termed as the Drain current.

The channel can be made using any existing semiconductor device suitable for fabrication. Even recently, a novel JL transistor structure with polysilicon nanowire channel is proposed by Su et al. [38]. However, due to the unique device structure and operating principles, the effective mobility of JL device is lowered compared to inversion mode device. As a result, high mobility semiconductor is preferred as channel material for JL MOSFET. However, considering the cost and feasibility, initial investigation of the device has been constrained within Silicon based channel structure. Recently, III-V materials, especially GaN has shown great potential to be an alternative channel material for JL NW MOSFET. The second significant device element is the Gate. It is often referred to the Gate

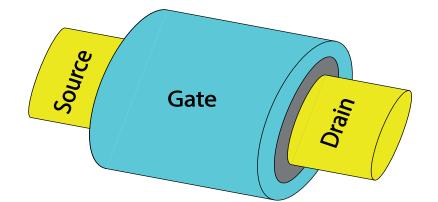

Figure 1.4: Three Dimensional Schematic View of JL NW MOSFET

terminal of the device, which combined with the Drain and Source terminals, complete the three-terminal structure of the transistor. The gate of JL MOSFET performs similar function as the Gate terminal of tradition inversion mode FET. That is, the gate acts as the switching regulator of the transistor. When a significant voltage is applied at the gate terminal, the device is turned on, and constant current flows through the channel. The limiting value is generally termed as the threshold voltage of the device. In addition, for JL MOSFET, flat band voltage acts as the Corner Voltage of the device.

The JL MOSFET is a basically a multi-gate device, which means, by definition, there is more than one gate structures present in the device. There are three major configuration of JL MOSFET can be found in the literature:

- The gate-all-around (GAA) structure/ The  $\Theta$  structure

- The Triple-Gate (TG) structure /The Π structure

- The Double-Gate (DG) structure / The  $\Xi$  structure

The GAA structure encloses the device in all four directions. The TG structure basically has 3 directional encapsulations, similar to a doorway arch, as the channel passes through the door. The DG structure, on the other hand, encloses the channel from only two directions, opposite to each other. Hence, for all acts and purposes, the gates and the channel can be viewed as a sandwich structure. In a Double-Gate structure, the channel is covered from two opposite directions with the gate structures. However, although the gate structures are physically isolated, they are electrically coupled together. That is, both gate structures are connected to the same voltage source, so that both ends of the channel are induced with the same gate voltage. The gates are placed along an axis perpendicular to current flow i.e. if current flow is considered to be along Z axis, the gates are placed along X axis. With variation of gate voltage, the channel surface charge density along YZ plane varies, turning the device ON or OFF or keeping in between. However, more complex variation occurs for TG or GAA structure.

The multigate device structure possesses several improvements over tradition single gate structure. Multi-gate device structure can be used to improve gate control over the channel and hence alleviate the short channel effect. The GAA structure provide the best utilization of the advantages of multigate structure due to the complete encapsulation of the channel region.

To fabricate the gate, various materials are available. Classic metal gate structure is still feasible, while current trend of polysilicon gates are well suited in fabrication perspective.

An insulator layer distinguishes the channel region from the gate material in JL MOS-FET, just like in tradition FET. To ensure proper device operation, the insulator should have low conductivity. In addition, to reduce lattice mismatch during fabrication, the lattice constant of insulator and channel material should be closely matched. Traditionally, the Oxide and Nitride layer of the native channel semiconductor is used as the insulator material.

Figure 1.4 portrays a simplified 3D model of the NW JL MOSFET under discussion. As it can be observed in the figure, the gate encloses the device, while the channel has source and drain terminals. The oxide layer separate the channel from the gates, preventing gate current flow.

The effective device model can be better understood for the 2D cross section of

Figure 1.5: 2D Schematic Cutout along Channel of a NW JL MOSFET

the device exhibited in figure 1.5. This figure highlights the respective position of the gate terminal, oxide layer and the channel in the NW JL MOSFET structure. Figure 1.6 displays the cross sectional view across the channel of the nanowire.

The device structure can be scaled up or down along a very extensive range. The reduction in the doping gradient maintenance constraints allows it to construct far smaller devices possible compared to current FET fabrication technology.

The standard doping density of n-channel region of the JL MOSFET device can

Figure 1.6: Radial Cross Section of a NW JL MOSFET

be varied as well. Usually, as no high doped diffusion area has to be fabricated, the

usual doping density of JL FET is higher compared to standard FETs. The usual studies contain the doping density in the range of  $2 \times 10^{19} a toms/cm^3$  to  $5 \times 10^{19} a toms/cm^3$  [33].

#### 1.4.2 Operating Principal of the Device

The device operation of NW JL MOSFET significantly varies from the tradition inversion type FET devices. In the inversion mode device, gate voltage is used to attract or repulse carriers in order to construct an inversion layer near the oxide/semiconductor interface to facilitate current flow through the channel. On the contrary, in the JL device, the gate voltage is used to free already existing channel from the chokehold of junction fermi level mismatch.

The operation of JL device can be well comprehended by analyzing its energy band diagram for different gate voltage conditions. It is already known from the fundamental knowledge of electronics, that during formation of junction, the different materials present in the structure attempt to match their Electrochemical Potentials, also referred to as Fermi Levels along the same energy level. In case of a p-n junction, as seen in traditional electronic devices, the p-type material is doped using Group-III materials with electron deficiency. Hence the fermi level exists closer to the valance band. On the contrary, due to being doped with Group-V materials, the n-type material has its fermi level near the conduction band. Now, during the formation of junction, the levels tend to match along the junction region, resulting in a bending of the conduction band, valance band and intrinsic Fermi level of the materials along the area. The region of band bending, i.e. the depletion or space-charge region, is less n-type inside the n-region due to presence of static positive charge within it. The opposite is true for the p-region.

Now in the case of Gate-Oxide-Semiconductor combination, as observed for both inversion mode and JL FET, the gate is either metal or heavily doped polysilicon. Although no direct junction is formed between gate and channel, the excess charges of the gate and channel regions attract each other through the oxide layer, often with the assistance of trapped oxide charges present in the oxide, but no current can flow. Hence, energy band bending can be observed in the conduction and valance band of the channel region as space charge region is formed.

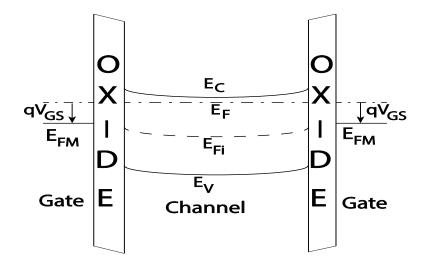

Figure 1.7 presents the energy band structure that would have been present in the de-

Figure 1.7: Energy Band Diagram of n-channel NW JL MOSFET before Junction Formation

vice in absence of electrochemical equilibrium. The n-channel, considered here, has its fermi level near the conduction band, as a large energy gap exists between the channel Fermi level and the gate work function.

In reality, with the formation of contact, the Fermi levels would align, and space charge region would be produced. The trapped charge in oxide layer would also create bending in the conduction and valance band of the oxide layer. Figure 1.8 portrays the energy band diagram that would be present under the assumption of zero gate voltage.

As it can be observed from the figure, the conduction band and valance band bending occur by the amount of  $\Delta E$  along the surface of the channel-oxide interface. So, potential varies from  $\phi_c$  to  $\phi_s$  from the core of the channel to the surface regions. Hence, a space charge region exists almost throughout the channel cross-section. This is known as the Full Depletion mode of the device operation [39].

Now, with application of gate voltage, the energy band profile varies accordingly. The electrochemical potential decreases as positive electric potential is increased along a material axis. Hence, if a positive gate voltage is applied along the gate terminal, the gate fermi level would decrease, i.e. move toward the valance band. Moreover, since

Figure 1.8: Energy Band Diagram of n-channel NW JL MOSFET in Full Depletion

potential decreases with distance from source, the channel would experience an effective negative voltage according to Kirchhoff's Voltage Law. As a result, the channel Fermi Level would tend to move upward nearer to the conduction band.

The fermi level matching in thermal equilibrium occurs due to the tendency of materials to maintain equilibrium charge density throughout the surface. But, when a voltage is applied, the equilibrium condition is no longer persists. Hence there would be a mismatch of Fermi levels present in the device, resulting in straightening out of the conduction and valance bands.

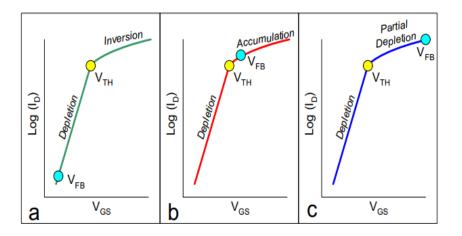

Figure 1.9 displays the band diagram under positive gate voltage biasing condition. With the increase of gate bias, the Fermi level drifts apart, and  $\Delta E$  reduces. Hence, the band bending declines and so the depletion region width decrease with increasing gate voltage. This is known as the Partial Depletion mode of device operation [39].

Now, let's review the device structure to delve into device operation. The channel from drain to source is the active region of the device, which is expected to allow ample current flow under proper gate biasing constraints. When the device has no input gate voltage present, the induced space charge region almost completely covers the channel region. It can be visualized as the gate choking the channel such that little to no current can flow.

Figure 1.9: Energy Band Diagram of n-channel NW JL MOSFET in Partial Depletion

As gate voltage is increased, the space charge region reduces in area, and moves further away from the center. Hence, current now has better potential of flowing than before. As said before, the chokehold of the gate on the channel lessens as current flow path cross section area increases. As a result, drain current flow initiates [33].

After reaching a certain gate voltage, current flow commences. A certain gate voltage can be marked as the "Threshold Voltage" of the device. Up to this point no current can flow through the channel, since sufficient mobile charge density cannot muster up for current flow. At the threshold, finally the current flow can begin.

Another significant bias point of the device can be marked as the "Corner Voltage". Since space charge region diminishes at the "Flat-Band Voltage", The depletion conditions die out as band structure straightens similar to the pre-connection status. Hence, At Flat-band, the band diagram closely resembles Figure 1.10, as conduction and valance band both are completely straightened.

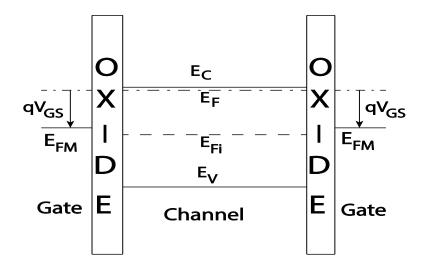

Figure 1.11 shows standard I/V relations of GAA-JL FET compared to inversion and accumulation type MOSFETs. In case of IM MOSFET devices, the band bending is minuscule, as flat-band lies close to zero voltage. On the other hand, for accumulation, flat band is very close to threshold voltage. But, as it can be clearly seen that unlike MOSFET, the flat-band voltage is situated far higher than threshold voltage for JL FET [33].

Figure 1.10: Energy Band Diagram of n-channel NW JL MOSFET in Flat Band

For voltages higher than the Flat Band voltage, band bending begins again, in the

Figure 1.11: I/V Characteristic of n-channel (a) IM-FET (b) AMFET (c) GAA-JL FET Showing Relative Positions of Threshold and Flat Band Voltage. Figure extracted from [40]

upward direction, since now accumulation layer of electron is created near the channel surface, which increases surface current carrying capability. Now, current flow occurs due to the accumulation layer of charge present near the junction, similar to AM-MOSFET devices, as opposed to IM devices.

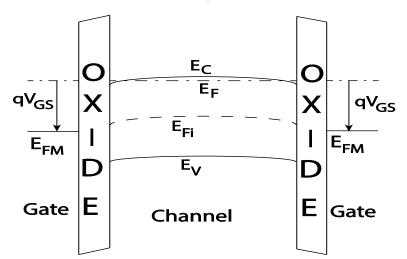

Figure 1.12 Shows the band diagram under a positive gate voltage biasing condition for over the Flat Band Voltage limit. This is the Accumulation Mode of the device operations [39]. The Drain Voltage-Drain Current related I/V Relationship of the NW JL FET device

Figure 1.12: Energy Band Diagram of n-channel NW JL MOSFET in Accumulation

closely resembles MOSFET I/V relationship. For gate voltage higher than threshold, the drain current increases linearly with drain voltage, as channel current flow path can be considered as resistive. The largest contribution of such resistance comes from impurity scattering of carrier free electrons [33].

However, for sufficiently large input drain to source voltage, the channel charge density varies significantly from drain to source. At a certain high voltage the channel is pinched off, and incremental resistance is nullified. Hence, drain current remains constant for higher voltage constraints. This operation is hence same as FET characteristics.

#### 1.4.3 Advantages of the Device

Since its inception, JL MOSFET has been the center of major study and analysis for its overwhelming potential of near future industrial fabrication and day-to-day applications in electronics sector. The device even has the potential of dethroning MOSFET as the principal supply of transistors, which are the building blocks of modern electronic circuitry. Moreover, the potential of the device in device scaling can even overcome the predictions of Moore's Law. The major advantages of the device are explained in brief as follows.

The junctionless nanowire transistor (JL FET), unlike MOSFET or BJT, contains

no distinct pn junctions in its channel region or any part of the current carrying path of the device. This is a significant departure from the FET based device characteristics, where a pnp or npn junction is a major element of device operations.

The junctions present in a FET based device results in several severe complications in fabrication process. with increasing scaling of the device size, the junctions in the device channel needs to be scaled as well. However, for proper and better device operations, it is expected that abrupt junction ending assumptions can hold up reasonably. To ensure that, very steep doping gradient must be maintained. Even in the deca-nanometer regime, abrupt ending of dopant concentration must be simulated as closely as possible, which results in extremely high doping density gradients near the junctions [9]. The doping gradient increases further with device scaling, which is increasing fast as predicted by Moore's law [1]. This problem is worsened by increased doping density in scaled Nanowire devices for ensuring enhanced properties.

For current fabrication technology, maintaining such intricate slope is proving more and more difficult. The diffusion characteristics and statistical nature of dopant and semiconductor prohibits the formation of ultra-shallow junctions with extremely high doping concentration gradients. This constraint is holding up scaling industry all by itself. Most modern fabrication techniques use novel doping techniques and ultrafast annealing techniques, which must be constantly improved, making evolution increasingly difficult. Even, a tradeoff between device scale and quality is fast prevailing.

The JL FET device, on the other hand, does not contain any explicit pn junctions. In fact, the channel present in the device is uniformly doped p or n type semiconductor with no doping gradient present whatsoever. Hence, the intricacies involved with doping gradient are of little to no consequence for the device at hand. Such freedom, makes it easier to design further scaled down transistors with reduced performance tradeoff.

Ideal FET based devices are supposed to perform as a simple switch, or at least a linear gates resistor, where the gate acts as a switching controller, turning ON or OFF the drain to source channel. However, in reality, several non-linear effects affect the device operations. Usually, enhanced device design techniques are used to reduce such complication to such an extent as possible, while device operations and characteristics are modeled via equations and diagrams, and appropriate approximations are made in order to simulate ideal device characteristics.

However, with further scaling of the device, several non-ideal factors are becoming more and more significant, which were considered trivial previously. Among them Short-Channel Effects is of major concern.Such non-ideal effects are detrimental to the proper gate control of MOSFETs. However, recent studies show that multi-gate nanowire structure can be used to improve gate control against short channel effects to the highest degree [41]. According to the term proposed by Yan et al. (1992), the Natural Length ( $\lambda$ ) of the dual gate device is defined as [42]:

$$\lambda = \sqrt{\frac{\epsilon_s}{2\epsilon_{ox}} \left(1 + \frac{\epsilon_{ox}t_s}{4t_{ox}\epsilon_s}\right) t_s t_{ox}} \tag{1.1}$$

Where  $t_s$  and  $t_{ox}$  are the semiconductor and oxide thicknesses and  $\epsilon_s$  and  $\epsilon_{ox}$  are the permittivity of semiconductor and oxide, respectively.

In case of multi-gate nanowire structure a term called Effective Number of Gates (n) can be introduced which also depends on threshold voltage on silicon film thickness, which in turn decreases the effective natural length of the device. According to improved relations by Suzuki et al. (1993) for the n-gate MuGFETs [43]:

$$\lambda = \sqrt{\frac{\epsilon_s}{2\epsilon_{ox}} \left(1 + \frac{\epsilon_{ox}t_s}{4t_{ox}\epsilon_s}\right) t_s t_{ox}} \tag{1.2}$$

A device can be considered free of short-channel effects if the gate length is at least 6-10 times larger than the Natural Length ( $\lambda$ ). Hence multi-gate devices show drastically reduced short-channel effects. The GAA-JL FET structure displays especially significant reductions in such effects. For example, highly improved DIBL constraints can be viewed for JL FET devices [43].

Traditional FET devices show aggravated device characteristics with increased temperature. In conventional MOSFET devices, the threshold voltage decreases with temperature, which in turn increases the drain current. However, carrier mobility decreases with increased temperature due to increased phonon scattering. The two variations counteract each other. At a certain temperature, these two effects cancel out one another. The gate bias for which such effects counteract each other is denoted as the Temperature Coefficient (ZTC) point [44].

However, in case of JL FET devices, the reduction of mobility is significantly less than traditional FET devices. Hence, there is no JL FET, resulting in monotonic increase of current with temperature. The use of the MuGFET structure can further reduce the temperature dependence of the threshold voltage when narrow silicon wires are used due to the reduction in the surface potential variation with the temperature [45]. As a result, better I/V characteristics can be observed at high voltage and higher temperatures. Also, the usual nonideal effects found for MOSFET at high temperature is less significant for GAA-JL FET.

The subthreshold conditions of a transistor are defined as the device characteristics and I/V relations observed for voltage under the threshold limit for the device. Under this condition, usual I/V relations of the device does not hold up. Gate leakage and other non-ideal factors prevail as significantly higher current can be observed for reduced bias voltage.

Such non-idealities constitute the OFF current of the device. The ON-OFF current ration of the device has a high significance as it marks device operation efficiency to some extent. The ratio can be improved by limiting the Subthreshold Slope of the device, i.e. rate of increase of OFF current, and hence reducing the OFF current considerably.

The subthreshold slope of a device limits the on-off current ratio of a device, which has the theoretical minima at 60 mV/decade for MOSFETs. However, that is no longer sufficient with increased device scaling along with gate voltage reduction. Positive feedback loop from increased current due to impact ionization can be used to limit the slope further down. However, multi-gated JL FET structure can be used to find better characteristics [46]. The device displays increased electron temperature but decreased ionization rate for similar slope, resulting in increased slope efficiency. At voltage under threshold, i.e. under subthreshold conditions, both JL FET and MOSFET are turned off, and a high electric field is found at the drain junction of the MOSFET, which holds the bulk of the applied drain bias which peaks in the channel region. But In the junctionless device, the drain potential drop is found inside the drain electrode, outside of the region covered by the gate, since current blocking is caused by pure electrostatic pinch-off of the heavily doped nanowire structure. Hence the entire channel region is pinched off, and bulk of the drain potential drop is found in the drain, near the gate electrode. The region over which impact ionization takes place is found to be much larger in the junctionless devices than a MOSFET, reducing Drain to Source voltage considerably. Hence JL MOSFET can support an improved subthreshold slope.

### 1.5 Literature Review of Junctionless Transistor

NW JL MOSFET has gained significant attention in the research community since its introduction. Jean-Pierre Colinge and Lee Chi Woo are considered as the pioneer in the race of unfolding novel attributes and innovations in the field of JL MOSFET.

J. Lilienfeld first proposed and patented JL MOSFET structure in 1930 [47]. His proposed device, also known as "Lilienfeld Transistor" in USA, was patented under the title "Device for controlling electric current". The Lilienfeld transistor is a field effect device, much like modern MOS device. It consists of a thin semiconductor film deposited on a thin insulator layer, itself deposited on a metal electrode [48]. The latter metal electrode serves as the gate of the device. in operation, the current flows in the resistor between two contact electrodes, in much the same way that drain current flows between the source and drain in a modern MOSFET. The Lilienfeld device is a simple resistor, and the application of a gate voltage allows the semiconductor film of carriers to be depleted, thereby modulating its conductivity. ideally, it should be possible to completely deplete the semiconductor film of carriers, in which case the resistance of the device becomes quasi-infinite.

Recently, Lee et al. first proposed and analyzed the characteristics of JL multigate

MOSFET [49]. They investigated the first model of a triple gate JL MOSFET via 3D simulation in ATLAS. Their proposed device structure enclosed n type Si channel with no effective p-n junction. The study performed detailed analysis of JL FET device properties and relative merits and demerits. Due to its junctionless structure, doping gradient related problems were eliminated. They also studied the non-ideal properties and compared it against inversion type MOSFET. In this the JL MOSFET exhibited improved DIBL and subthreshold slope compared to its inversion mode counterpart which indicate the excellent turn-off and short channel characteristics of JL MOSFET.

The first significant progress in the research of JL MOSFET came in 2010 when J. P. Colinge et al [33]. first demonstrated the multigate JL MOSFET experimentally. SOI technology was used for the device construction. The study showed that the current voltage characteristics of JL transistor, also coined as gated resistor, are remarkably similar to those of a regular MOSFET. They fabricated both the n type and p-type JL MOSFET and demonstrated full CMOS functionality of gated resistors. The absence of doping gradients in those devices ensured that the device were much less sensitive to thermal budget issues than regular CMOS devices. From the measurement they have obtained near-ideal subthreshold slope, close to  $60 \ mv/dec$  at room temperature in JL MOSFET and extremely low leakage current. In addition, their fabricated device exhibited less degradation of mobility with gate voltage increase compared to classical inversion mode MOSFET.

Colinge et al. elaborated on the theoretical aspects of JL multigate MOSFET in 2011 [40]. They explained the conduction mechanism in JL MOSFET and found that the device do not operate in inversion or accumulation, but only in full or partial depletion. They also illustrated the constraints of JL MOSFET- thin and narrow heavily doped semiconductor channel which are required for proper operation of the device. They also found that the threshold voltage depends on doping, equivalent oxide thickness (EOT) as well as on the width and thickness of the nanowire. In addition, they proposed the concept of a bulk multi-gate MOSFET without any lateral source-drain junction. They have demonstrated that JL MOSFET can exhibit low leakage current and excellent short channel behavior. Through simulation study, they have showcased

the potential of JL FET as a strong candidate for future CMOS.

Lee et al. (2010) studied the effect of High Temperature on JL MOSFET [44]. It was observed that the use of the MuGFET structure can reduce the temperature dependence of the threshold voltage when narrow silicon fingers are used due to the reduction in the surface potential variation with the temperature. The study observed the fact that in JL FET, no Zero Temperature Coefficient (ZTC) point exists, resulting in monotonic current increase. This phenomenon results in possible better JL FET operation under high temperature constraints. However, the off leakage current increases with temperature because of the increase of intrinsic carrier concentration, which increases both diffusion and generation currents. Here, DIBL at high temperature is dominated by Band-to-Band Tunneling (BBT), rather than Band-to-Defect Tunneling (BDT) as in the case of MOSFETs. Hence, the usual non-ideal effects at high temperature are less significant for GAA-JL FET as well.

In 2010, J. P. Colinge et al. investigated the variation of Electric field of JL transistor [50]. The effective oxide thickness (EOT) variation with scaling causes increase in the vertical electric field of a FET, resulting in high carrier scattering, and consequently mobility is decreased. When JL FET is turned on, it is in flat-band condition. As a result there is zero electric field in the direction perpendicular to current flow. Hence transconductance decreases less rapidly with applied voltage for JL FET compared to inversion mode device. Since high electric field is responsible for reduction of mobility, this provides and advantage to JL devices in terms of current drive.

Lee et al. compared the improvement of subthreshold slope between standard inversion type multigate NW MOSFET and JL NW MOSFET. It is established that on-off switching capability is represented by subthreshold slope and classical transistor has a theoretical best value limit of SS of 60 mV/dec at room temperature. The impact ionization has the potential to overcome this limit and achieve lower SS which is required for devices of future technology node. The positive feed facilitated by impact ionization results in the rapid on-off transition of device current and hence SS below  $60 \ mV/dec$  is observed. Under subthreshold conditions, in case of JL FET, the drain potential drop is found inside the drain electrode, outside of the region covered by the gate. Hence the entire channel region is pinched off, and bulk of the drain potential drop is found in the drain, near the gate electrode. The region over which impact ionization takes place is found to be much larger in the junctionless devices than a MOSFET, reducing Drain to Source voltage considerably. Hence JL MOSFET can support a much sharper subthreshold slope.

Ansari et al. reported a Si Nanowire GAA-JL FET with 3 nm gate length and 1 nm wire diameter in 2010 [51]. This study considered the GAA JL FET structure with 3.1 nm feature size, scaled down from 1  $\mu m$  one from previous studies, and hence shifting device properties to complete Nanoscale range. They also implanted a very high doping density in the scale of  $8 \times 10^{20} atoms/cm^3$ . The simulation was performed via full quantum mechanical treatment using Density Functional Tight-Binding  $(DFTB^+)$  Method, parameters calculated via Density Functional Theory (DFT) over an 800-atom supercell. Mulliken Population Analysis was performed to calculate the localized charge density. The analysis shows adequate carrier density even under undoped channel conditions, which is unlikely for both similar scale MOSFET and larger JL FET devices. However, de-localization would make the junctionless design more robust against dopant fluctuations. The observed I/V characteristics were in accordance with results obtained for larger feature size. Also, the positioning of the dopant in the wire cross section makes a difference in the band structure of the device, which results in steeper I/V relation at low bias.

In 2011, Su et al. proposed a novel junctionless structure with Polysilicon nanowire channel for the first time [38]. They experimentally investigated the feasibility of GAA polycrystalline silicon (poly-Si) nanowire transistors with junctionless configuration by utilizing only one heavily doped poly-Si layer to serve as source, channel, and drain regions in a GAA-JL FET structure. The formation of cavities was carried out by carefully controlling the lateral etching of the Tetraethyl Orthosilicate (TEOS) oxide layer in dilute HF solution. High Resolution Transmission Electron Microscopic (HRTEM) Image was obtained to study the designed model. Better I/V characteristics than a MOSFET structure was observed for this model. A very high transconductance was also observed compared to the IM device. Channel resistance also decreases considerably, which increases with channel length for obvious reasons. The device also shows very high on-off current ratio and low subthreshold slope.

Doria et al. investigated the analog parameters of JL MOSFET to analyze its feasibility in analog communication field applications [52]. They performed an in-depth comparison of the analog operation of JL and IM trigate devices aiming at low-power applications and attempt to explain the physical mechanisms behind the obtained results. JL transistors were found to exhibit both better Early voltage and larger intrinsic voltage gain than IM devices of similar dimensions at high values of transconductance. The JL transistors showed higher variation of conductance with voltage, which was addressed through 3-D numerical simulations. When the influence of the temperature is taken into consideration, JL transistors are able to provide a constant drain current over a wide temperature range, unlike IM devices. Hence, JL devices present better analog properties than IM transistors in low-moderate frequencies of operation.