# ADAPTIVE CLARKE TRANSFORMATION BASED THREE-PHASE PLL UNDER AMPLITUDE AND PHASE UNBALANCES IN PRESENCE OF HARMONICS

A thesis submitted in partial fulfillment of the requirement for the degree of Masters of Science in Electrical and Electronic Engineering

> *by* Md. Zahidul Islam Student ID: 1017062115 F

Department of Electrical and Electronic Engineering BANGLADESH UNIVERSITY OF ENGINEERING AND TECHNOLOGY Dhaka, Bangladesh

November, 2020

## Approval

The thesis titled "Adaptive Clarke Transformation Based Three-Phase PLL under Amplitude and Phase Unbalances in Presence of Harmonics", submitted by Md. Zahidul Islam, Student No: 1017062115 F, Session: October/2017, has been accepted as satisfactory in partial fulfillment of the requirement for the degree of Master of Science in Electrical and Electronic Engineering on 05/01/2021.

### **Board of Examiners**

1.

Dr. Md. Shamim RezaChairmanProfessor Department of Electrical and Electronic Engineering(Supervisor)Bangladesh University of Engineering and TechnologyDhaka – 1205, Bangladesh

2. Kin 20mm

Dr. Md. Kamrul Hasan Professor and Head Department of Electrical and Electronic Engineering Bangladesh University of Engineering and Technology Dhaka – 1205, Bangladesh Member (Ex-officio)

3.

Dr. Mohammad Jahangir AlamMemberProfessor Department of Electrical and Electronic EngineeringBangladesh University of Engineering and TechnologyDhaka – 1205, BangladeshEngineering

4. Dr. Nahid-Al-Masood Associate Professor Department of Electrical and Electronic Engineering Bangladesh University of Engineering and Technology Dhaka – 1205, Bangladesh

5. Oras/1/2021

Dr. Muhammad QuamruzzamanMemberProfessor Department of Electrical and Electronic Engineering(External)Chittagong University of Engineering and Technology-Chittagong – 4349, Bangladesh-

Member

## Declaration

It is hereby declared that this thesis or any part of it has not been submitted elsewhere for the award of any degree or diploma.

Signature of the Candidate

(Md. Zahidul Islam)

## Acknowledgement

First of all, I am grateful to the Almighty Allah for giving me the patience to do the research work and complete the dissertation in due time.

I want to express my gratitude to my thesis supervisor, Dr. Md. Shamim Reza, Professor, Department of Electrical and Electronic Engineering (EEE), Bangladesh University of Engineering and Technology (BUET), for his continuous support and edifying suggestions throughout the whole time. I have the opportunity to work closely with him during the research work. I realize his passion and dedication to academic research, which motivates me to explore my limitations and push the boundaries to come up with new research ideas. I am grateful to him for having faith in my capabilities and directing me towards right track to fulfil the dissertation.

I want to express my special thankfulness to Dr. Md Maruf Hossain, Assistant Professor, Department of Electrical Engineering Technology, University of Wisconsin, USA, for helping us to carry out the experimental results of the thesis. He took the risk during the COVID-19 to go to the university Lab to complete the experiments. I cannot express my gratitude in words for his such dedication.

I am also indebted to my parents and siblings for their continuous support in every step of my life and want to dedicate the thesis to them. They are the source of my energy for moving forward.

I am also grateful to my friends, colleagues and well-wisher for their support, suggestions and word of encouragement during the research work.

### Abstract

Precise and fast estimation of the phase information of grid voltages is crucial for grid synchronization of various power electronic devices, which is a research trend in modern smart grid technology. However, the task of instantaneous phase estimation has become difficult as the grid voltages may contain harmonics, DC offset, frequency variations, and voltage unbalances due to an increase in renewable energy penetration to grid, and domestic and industrial non-linear loads. In this dissertation, a fast and accurate instantaneous phase estimation technique is developed to overcome the present limitations in this field.

This dissertation proposes a three-phase phase locked loop (PLL) algorithm relying on adaptive Clarke transformation (ACT) for tracking the phase angle of unbalanced grid voltages associated with harmonics and DC offset. A meticulously tuned band pass filter (BPF) is inserted in each phase to remove harmonics and DC offset. Two separate algorithms are proposed to estimate the amplitudes and the phase-angle deviations of three-phase voltages. Using the estimated amplitudes and phase angle deviations, a set of analytical expressions is derived for the coefficients of Clarke transformation (CT) matrix to make them adaptive under both amplitude and phase unbalances, which is named as ACT. The ACT is capable of generating orthogonal signals from unbalanced three-phase voltages, whereas the conventional CT based on constant matrix fails to do so. After getting the orthogonal voltages, a conventional SRF-PLL is used to track the phase-angles of all three-phases. A phase-correction technique is also developed to make the PLL frequency adaptive without using any frequency feedback loop.

# Table of Contents

| Approv   | <i>al</i> iii                             |

|----------|-------------------------------------------|

| Declard  | <i>ation</i> iv                           |

| Acknow   | vledgementv                               |

| Abstrac  | c <i>t</i> vi                             |

| Table of | of Contentsvii                            |

| List of  | Figuresxii                                |

| List of  | Abbreviationsxix                          |

| List of  | Tables xviii                              |

| List of  | <i>Symbols</i> xxi                        |

| Chapte   | er 1 : Introduction1                      |

| 1.1      | Importance1                               |

| 1.2      | Background and Motivation2                |

| 1.3      | Objectives4                               |

| 1.4      | Methodology                               |

| 1.5      | Thesis organization                       |

| Chapte   | er 2 : PLL's Review7                      |

| 2.1      | The Basic Structure of Phase Locked Loop7 |

| 2.2      | Commonly Used PLL Algorithms9             |

| 2.3      | Review of Single Phase PLLs9              |

| 2.3      | 9.1 Power-based PLL (pPLL)                |

| 2.3.2   | 2.3.2 Transfer delay (TD) PLL10                        |  |  |

|---------|--------------------------------------------------------|--|--|

| 2.3.3   | 3 Inverse Park transformation-based PLL (IPT-PLL)11    |  |  |

| 2.3.4   | 4 Second Order Generalized Integrator (SOGI) based PLL |  |  |

| 2.4     | Review of Three Phase PLLs                             |  |  |

| 2.4.1   | Three Phase SRF-PLL                                    |  |  |

| 2.4.2   | 2 MAF based PLL                                        |  |  |

| 2.4.3   | Second Order Generalized Integrator based PLL          |  |  |

| 2.4.4   | Delayed Signal Cancellation PLL14                      |  |  |

| 2.4.5   | 5 Complex Coefficient Filter                           |  |  |

| 2.4.6   | 5 Decoupled SRF-PLL15                                  |  |  |

| 2.5     | The Performance of Conventional SRF-PLL Algorithm      |  |  |

| 2.6     | SRF-PLL without Harmonics17                            |  |  |

| 2.6.1   | Case1: Balanced17                                      |  |  |

| 2.6.2   | 2 Case 2: Amplitude Step                               |  |  |

| 2.6.3   | Case 3: Phase Step19                                   |  |  |

| 2.6.4   | Case 4: Frequency Step19                               |  |  |

| 2.6.5   | 5 Case 5: Amplitude and Phase Steps21                  |  |  |

| 2.6.6   | Case 6: Amplitude and Frequency Steps21                |  |  |

| 2.6.7   | 7 Case 7: Phase and Frequency Steps                    |  |  |

| 2.6.8   | Case 8: Amplitude, Phase and Frequency Steps23         |  |  |

| 2.6.9   | Case 9: DC Offset24                                    |  |  |

| 2.7     | SRF-PLL with Harmonics25                               |  |  |

| Chapter | 3 : The Developed PLL Algorithm27                      |  |  |

| 3.1     | Block Diagram of Proposed PLL                          |  |  |

| 3.2     | Attenuation of Harmonics: Design of Band Pass Filter   |  |  |

| 3.3    | Adaptive Clarke Transform for Unbalanced System                                 |

|--------|---------------------------------------------------------------------------------|

| 3.3    | .1 Amplitudes Estimation                                                        |

| 3.3    | .2 Estimation of Phase Angle Deviation:                                         |

| 3.4    | Instantaneous Phase Angles Estimation                                           |

| 3.5    | Tuning Parameters of the PLL                                                    |

| Chapte | r 4 : Simulation and Experimental Results                                       |

| 4.1    | Simulation Environments                                                         |

| 4.2    | Performance of Proposed PLL Without Disturbances                                |

| 4.2    | .1 Case 1: Balanced                                                             |

| 4.2    | .2 Case 2: Amplitude Step40                                                     |

| 4.2    | .3 Case 3: Phase Step41                                                         |

| 4.2    | .4 Case 4: Frequency Step                                                       |

| 4.2    | .5 Case 5: Amplitude and Frequency Steps                                        |

| 4.2    | .6 Case 6: Amplitude and Phase Steps                                            |

| 4.2    | .7 Case 7: Phase and Frequency Steps                                            |

| 4.2    | .8 Case 8: Amplitude, Phase and Frequency Steps                                 |

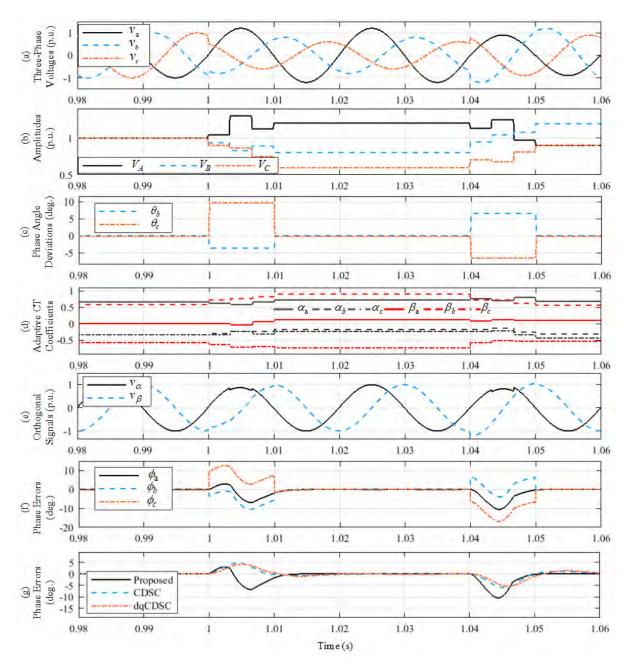

| 4.2    | .9 Case 9: Random Step Changes in Amplitudes50                                  |

| 4.3    | Performance of the Proposed Method in Presence of Harmonics and DC Offset 52    |

| 4.3    | .1 Case 1: Balanced System Distorted by Harmonics                               |

| 4.3    | .2 Case 2: Amplitude Unbalanced Signals Distorted by Harmonics                  |

| 4.3    | .3 Case 3: Phase Unbalanced Signals Distorted by Harmonics                      |

| 4.3    |                                                                                 |

| 4.2    | 5. Core 5. Dath Annality do and Phase Unhalanced Signals Distanted by Harmonics |

| 4.3    | .5 Case 5: Both Amplitude and Phase Unbalanced Signals Distorted by Harmonics   |

|        |                                                                                 |

| 4.3.6<br>Unbala | Case 6: Effects of Off-Nominal Frequencies and Harmonics in Amplitude need Signals |

|-----------------|------------------------------------------------------------------------------------|

| 4.3.7           | Case 7: Effects of Off-Nominal Frequencies and Harmonics in Phase Unbalanced       |

| 4.3.8           | Case 8: Effects of Off-Nominal Frequencies and Harmonics in Both Amplitude         |

| and Pha         | se Unbalanced Signals                                                              |

| 4.3.9           | Case 9: DC Offset                                                                  |

| 4.4 Ex          | perimental Results                                                                 |

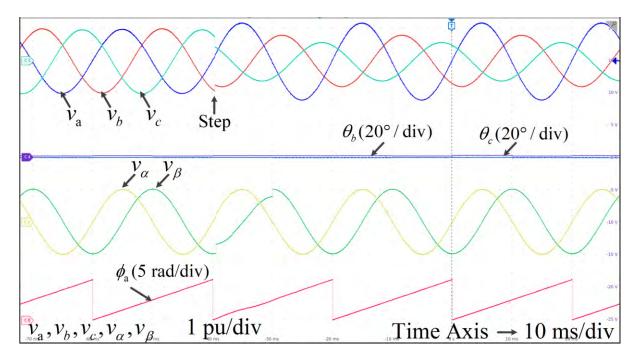

| 4.5 Ex          | perimental Performance without Harmonics70                                         |

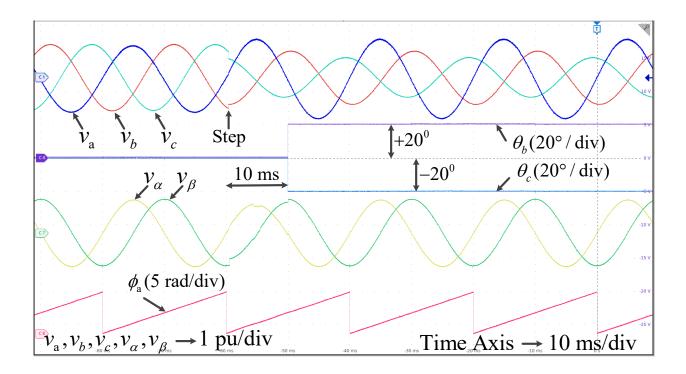

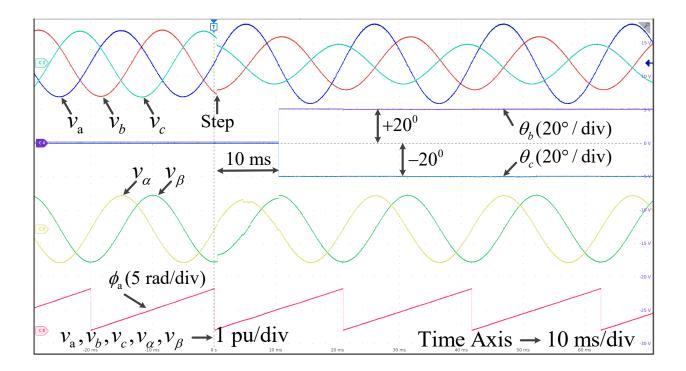

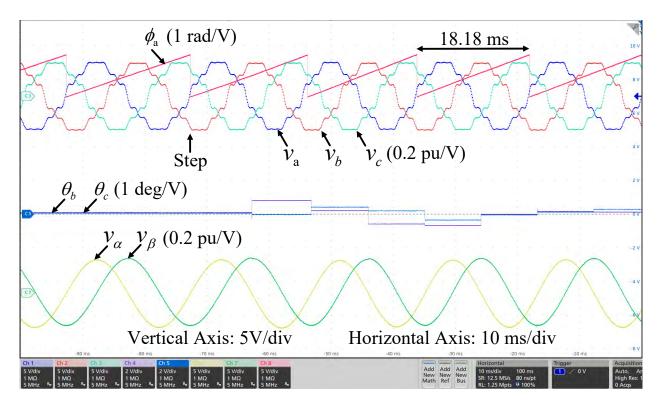

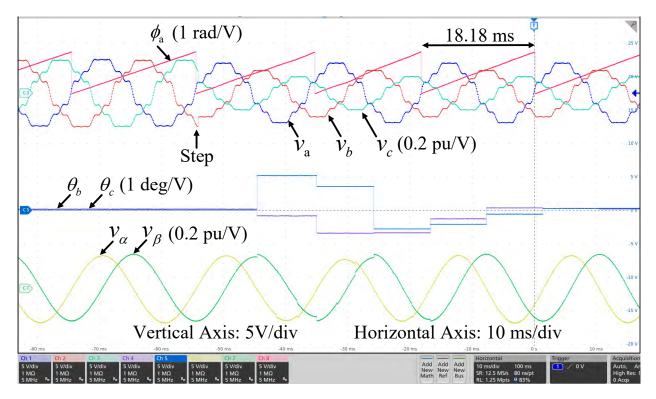

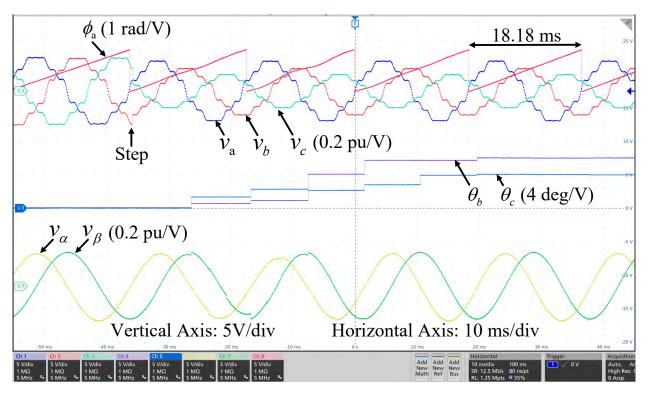

| 4.5.1           | Case 1: Amplitude Steps70                                                          |

| 4.5.2           | Case 2: Phase Steps71                                                              |

| 4.5.3           | Case 3: Amplitude and Phase Steps71                                                |

| 4.5.4           | Case 4: Amplitude, Phase and Frequency Steps72                                     |

| 4.6 Ex          | perimental Performance with Harmonics73                                            |

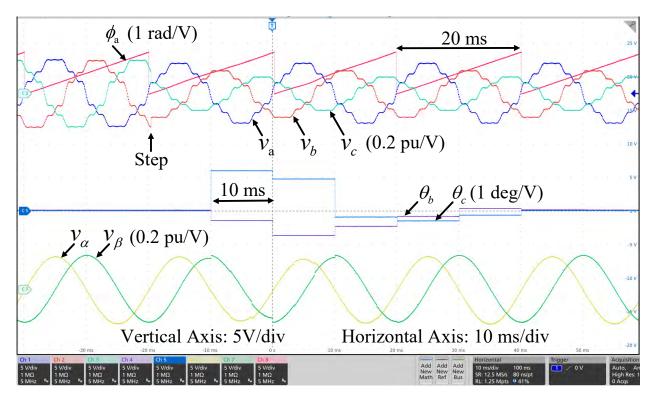

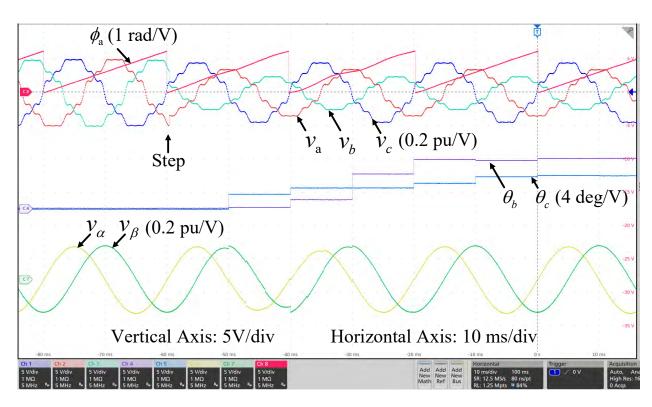

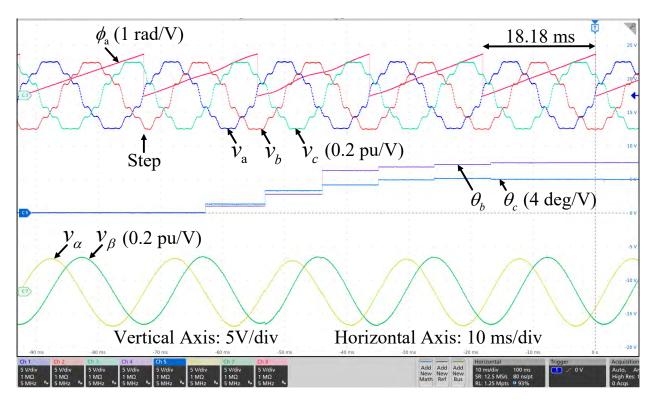

| 4.6.1           | Case 1: Amplitude Step                                                             |

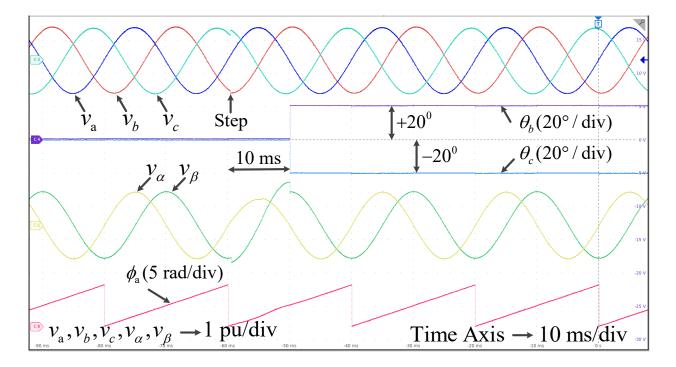

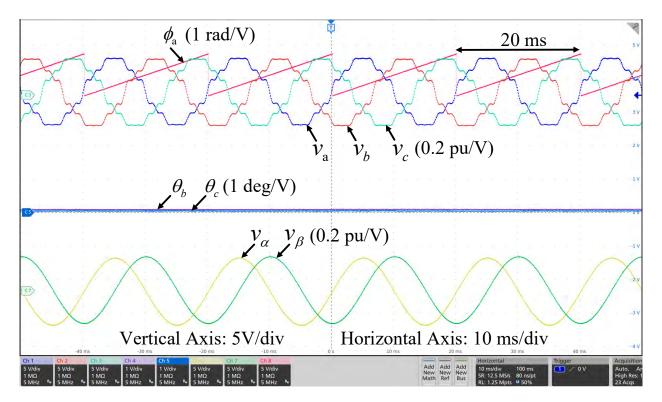

| 4.6.2           | Case 2: Phase Step73                                                               |

| 4.6.3           | Case 3: Frequency Step75                                                           |

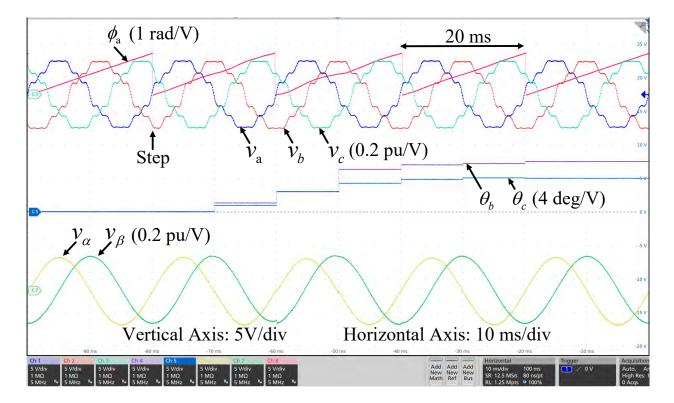

| 4.6.4           | Case 4: Amplitude and Phase Steps75                                                |

| 4.6.5           | Case 5: Amplitude and Frequency Steps76                                            |

| 4.6.6           | Case 6: Phase and Frequency Steps77                                                |

| 4.6.7           | Case 7: Amplitude, Phase and Frequency Steps78                                     |

| 4.6.8           | Case 8: DC Offset                                                                  |

| Chapter 5 :     | Conclusions                                                                        |

| 5.1 Co          | nclusions                                                                          |

| 5.2 Fu          | ture Works                                                                         |

| Reference       | 77                                                                                 |

# List of Figures

| Fig. 2.1 Basic PLL structure                                                                                                                                                                                                                                                    |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Fig. 2.2 Block diagram of pPLL9                                                                                                                                                                                                                                                 |

| Fig. 2.3 Modified block diagram of pPLL [71]10                                                                                                                                                                                                                                  |

| Fig. 2.4 Block diagram of Transfer Delay (TD) PLL [72]10                                                                                                                                                                                                                        |

| Fig. 2.5 Modified block diagram of Transfer Delay (TD) PLL [73]11                                                                                                                                                                                                               |

| Fig. 2.6 Block diagram of IPT based PLL                                                                                                                                                                                                                                         |

| Fig. 2.7 Modified block diagram of IPT based PLL [71]                                                                                                                                                                                                                           |

| Fig. 2.8 Block diagram of SOGI based PLL [75]12                                                                                                                                                                                                                                 |

| Fig. 2.9 Block diagram of MAF based PLL [76]13                                                                                                                                                                                                                                  |

| Fig. 2.10 Block diagram of SOGI based PLL [46]14                                                                                                                                                                                                                                |

| Fig. 2.11 Block diagram of CCF based PLL [46]15                                                                                                                                                                                                                                 |

| Fig. 2.12 Block diagram of Decoupled SRF-PLL [79]16                                                                                                                                                                                                                             |

| Fig. 2.13 Structure of Conventional SRF-PLL                                                                                                                                                                                                                                     |

| <ul> <li>Fig. 2.14 Simulation results of SRF-PLL for balanced input voltages. (a) Three-Phase Voltages</li> <li>(p.u.) (b) Orthogonal Signals (p.u.) (c) Quadrature Axis Component (p.u.) (d) Estimated Phase Error (deg.)</li></ul>                                            |

| Fig. 2.15 Simulation results of SRF-PLL, when amplitude steps ( $v_a = 20\%$ , $v_b = -10\%$ , $v_c = -20\%$ ) occur at t=1s. (a) Three-Phase Voltages (p.u.) (b) Orthogonal Signals (p.u.) (c) Quadrature Axis Component (p.u.) (d) Estimated Phase Error (deg.)               |

| <ul> <li>Fig. 2.16 Simulation results of SRF-PLL, when phase angle steps (θ<sub>b</sub>=30°, θ<sub>c</sub>=20°) occur at t=1s. (a) Three-Phase Voltages (p.u.) (b) Orthogonal Signals (p.u.) (c) Quadrature Axis Component (p.u.) (d) Estimated Phase Error (deg.)20</li> </ul> |

- Fig. 2.18 Simulation results of SRF-PLL, when amplitude steps ( $v_a = 20\%$ ,  $v_b = -10\%$ ,  $v_c = -20\%$ ) and phase angle steps ( $\theta_a=30^\circ$ ,  $\theta_b=20^\circ$ ) occur at t=1s. (a) Three-Phase Voltages (p.u.) (b) Orthogonal Signals (p.u.) (c) Quadrature Axis Component (p.u.) (d) Estimated Phase Error (deg.).

- Fig. 2.21 Simulation results of SRF-PLL, when amplitude steps ( $v_a = 20\%$ ,  $v_b = -10\%$ ,  $v_c = -20\%$ ), phase angle steps ( $\theta_b=30^\circ$ ,  $\theta_c=20^\circ$ ), and frequency step ( $\Delta f=-5$  Hz) occur at t=1s. (a) Three-Phase Voltages (p.u.) (b) Orthogonal Signals (p.u.) (c) Quadrature Axis Component (p.u.) (d) Estimated Phase Error (deg.)......24

- Fig. 2.22 Simulation results of SRF-PLL, when unequal DC offset steps ( $v_a = 15\%$ ,  $v_b = 40\%$ ,  $v_c = -20\%$ ) occur at t=1s. (a) Three-Phase Voltages (p.u.) (b) Orthogonal Signals (p.u.) (c) Quadrature Axis Component (p.u.) (d) Estimated Phase Error (deg.)....25

#### Fig. 3.1 Block Diagram Representation of the Proposed Technique......28

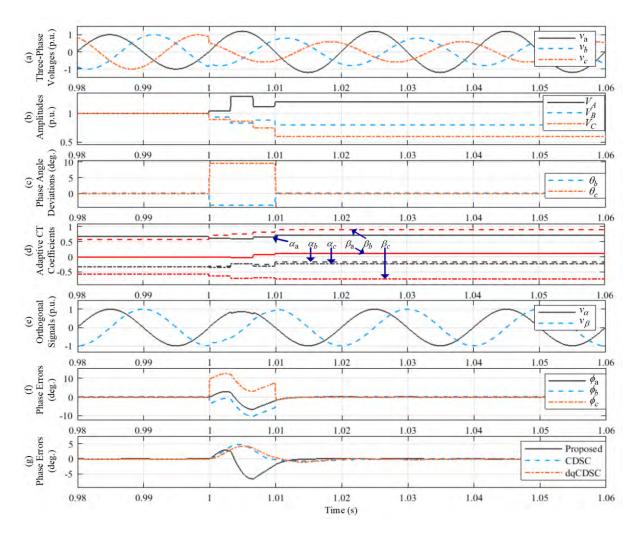

- Fig. 4.1 Simulated results for balanced inputs with 1p.u. amplitudes, zero phase deviations and 50 Hz frequency. (a) Three-Phase Voltages (p.u.) (b) Amplitudes (p.u.) (c) Phase Angle Deviations (deg.) (d) Adaptive CT Coefficients (e) Orthogonal Signals (p.u.) (f) Phase Errors (deg.) (g) Comparison of phase errors among Proposed, CDSC, and *dq*CDSC methods.

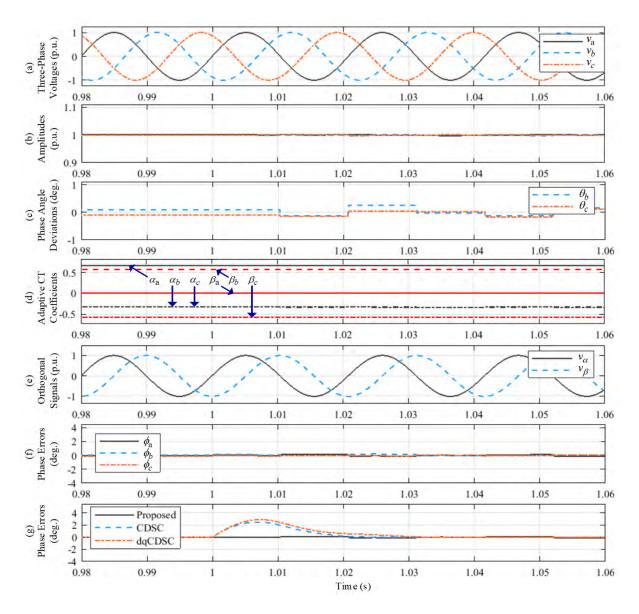

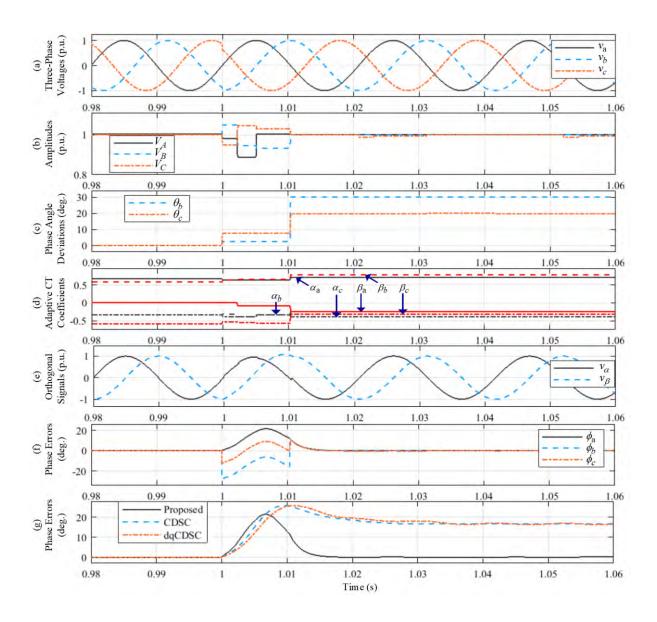

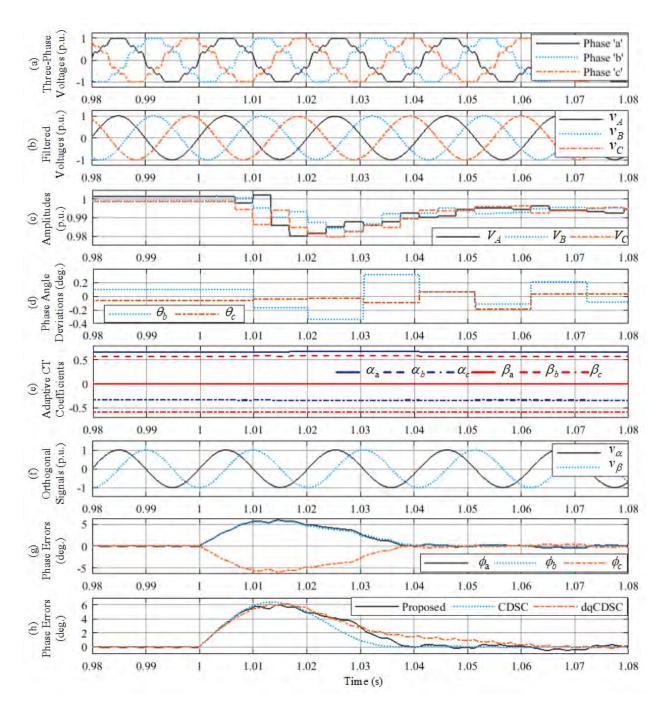

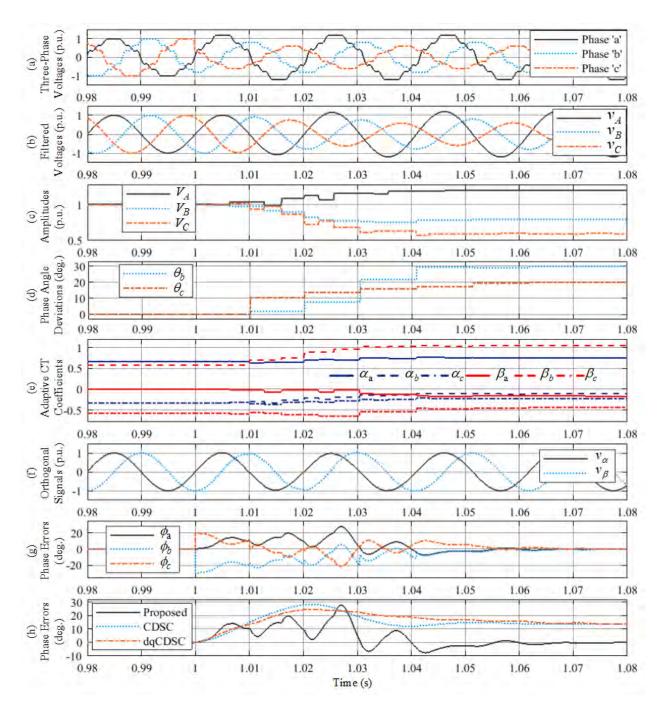

- Fig. 4.5 Simulated results when an amplitude steps ( $v_a = 20\%$ ,  $v_b = -20\%$ ,  $v_c = -40\%$ ) and frequency steps (-2 Hz) is created at t=1s from balanced condition. (a) Three-Phase Voltages (p.u.) (b) Amplitudes (p.u.) (c) Phase Angle Deviations (deg.) (d) Adaptive

CT Coefficients (e) Orthogonal Signals (p.u.) (f) Phase Errors (deg.) (g) Comparison of phase errors among Proposed, CDSC, and *dq*CDSC methods......45

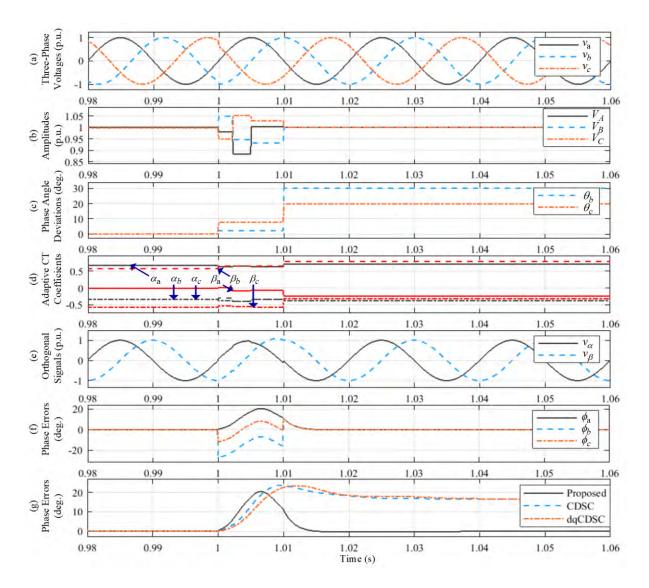

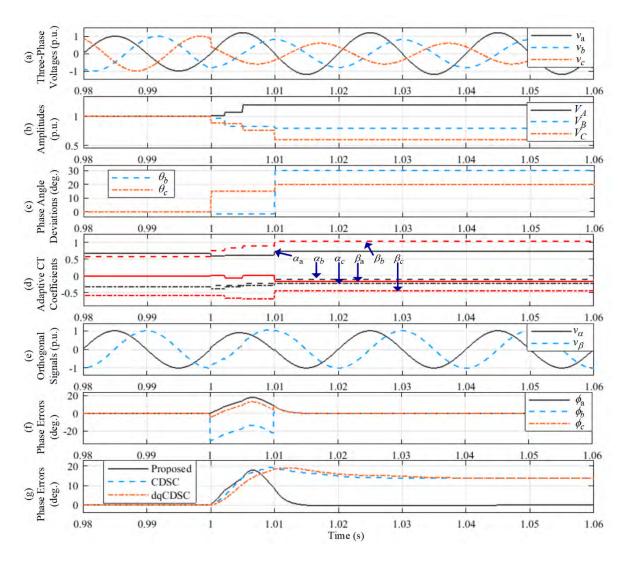

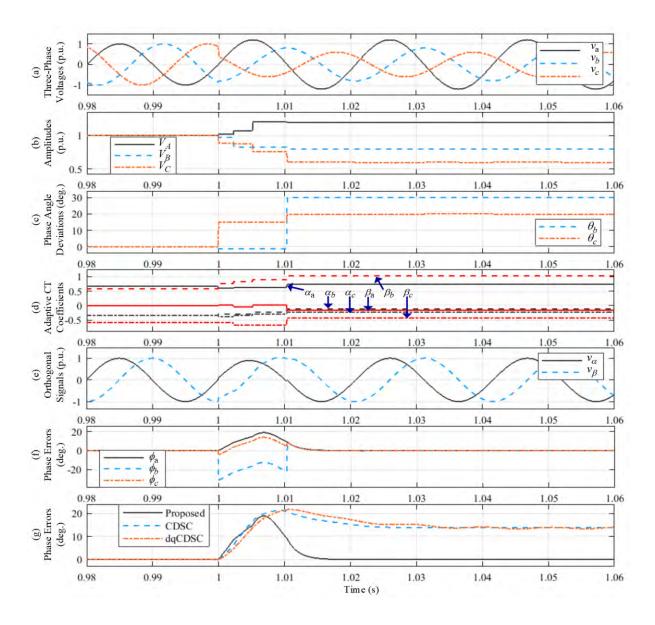

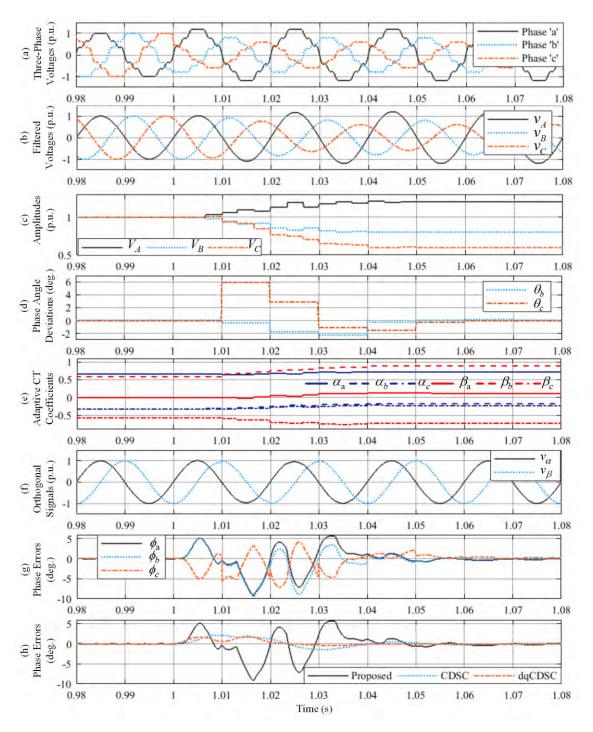

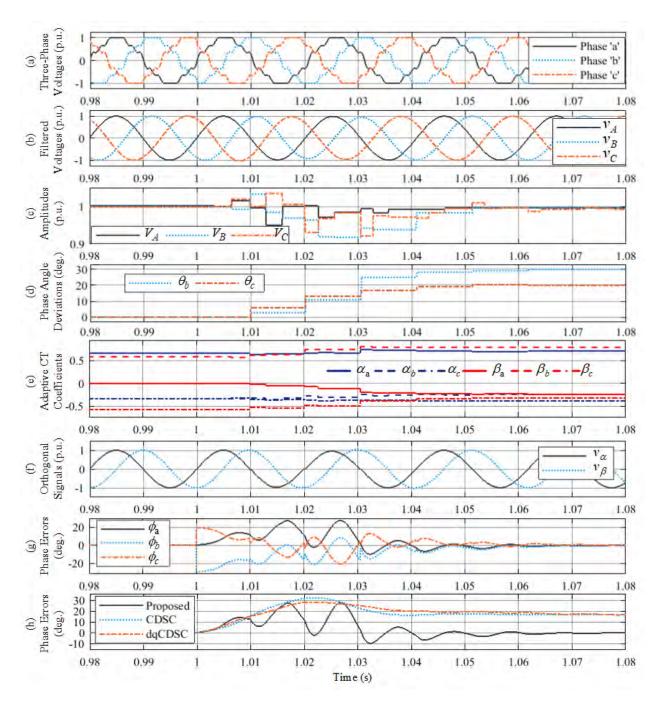

- Fig. 4.6 Simulated results when an amplitude steps ( $v_a = 20\%$ ,  $v_b = -20\%$ ,  $v_c = -40\%$ ) and phase steps ( $\theta_b = +30^\circ$ ,  $\theta_c = +20^\circ$ ) are created at t=1s from balanced condition. (a) Three-Phase Voltages (p.u.) (b) Amplitudes (p.u.) (c) Phase Angle Deviations (deg.) (d) Adaptive CT Coefficients (e) Orthogonal Signals (p.u.) (f) Phase Errors (deg.) (g) Comparison of phase errors among Proposed, CDSC, and *dq*CDSC methods.......47

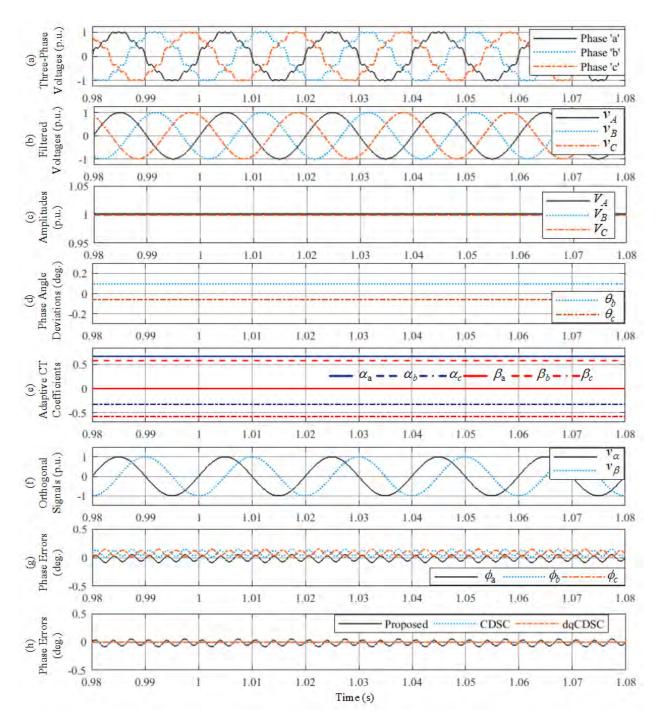

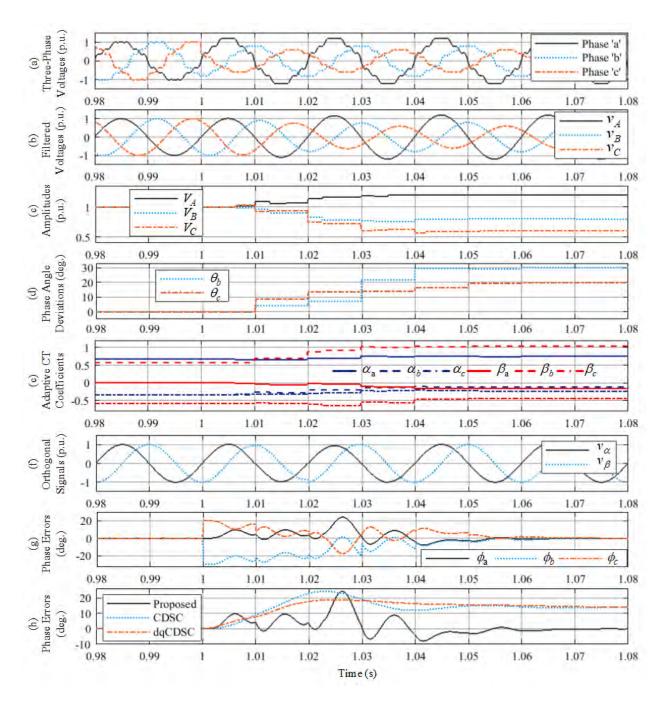

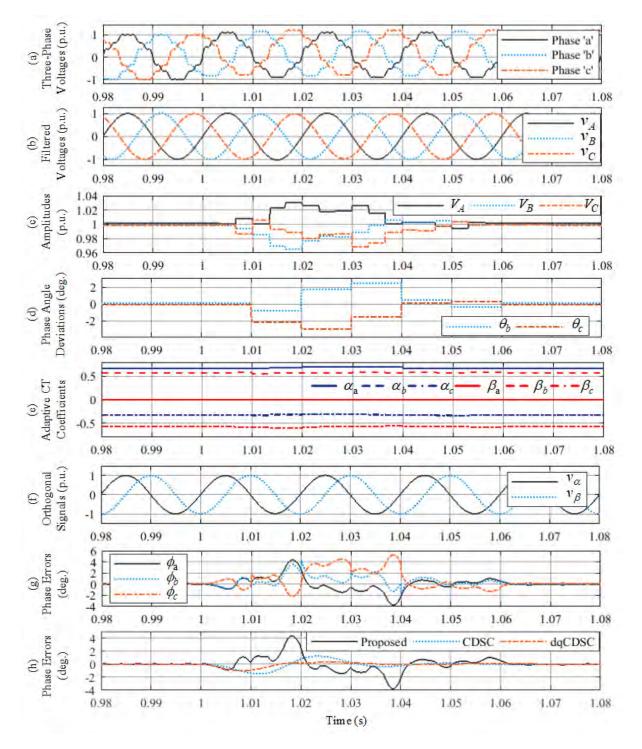

- Fig. 4.10 Simulated results for balanced inputs in presence of harmonics. (a) Three-Phase Voltages (p.u.) (b) Three-Phase Filtered Voltages (p.u.) (c) Amplitudes (p.u.) (d) Phase Angle Deviations (deg.) (e) Adaptive CT Coefficients (f) Orthogonal Signals (p.u.) (g) Phase Errors (deg.) (h) Comparison of phase errors among Proposed, CDSC, and *dq*CDSC methods.

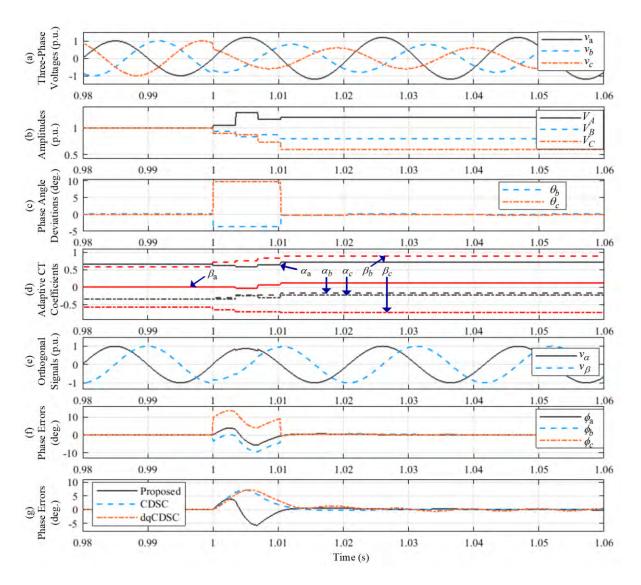

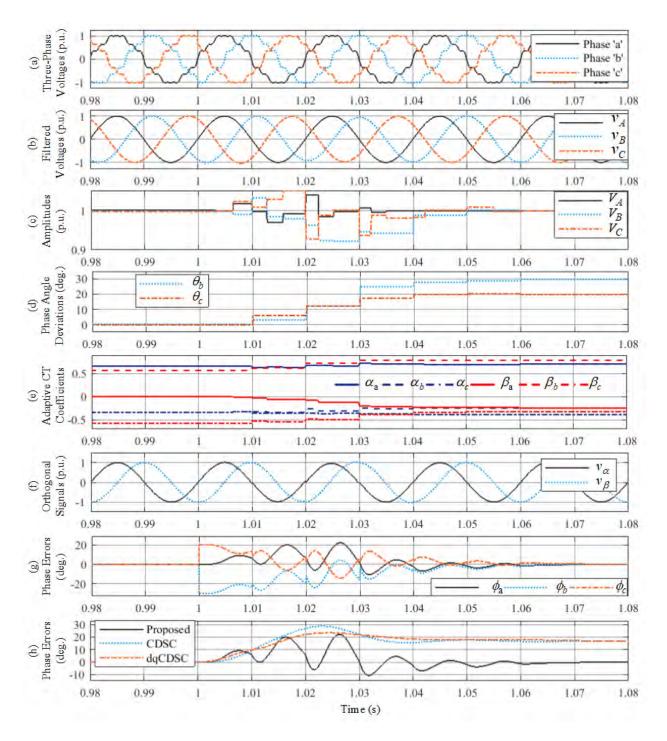

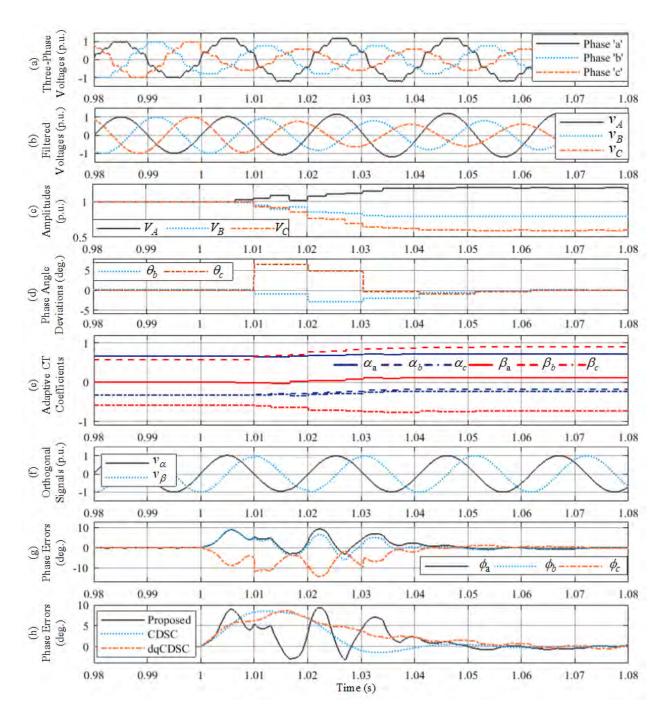

- Fig. 4.15 Simulated results when an amplitude step (v<sub>a</sub> = 20%, v<sub>b</sub> = -20%, v<sub>c</sub> = -40%) and frequency steps (-2 Hz) are created simultaneously at t=1s. (a) Input Voltages (p.u.) (b) Filtered Voltages (p.u.) (c) Amplitudes (p.u.) (d) Phase Angle Deviations (deg.) (e) Adaptive CT Coefficients (f) Orthogonal Signals (p.u.) (g) Phase Errors (deg.) (h) Comparison of phase errors among Proposed, CDSC, and *dq*CDSC methods.63

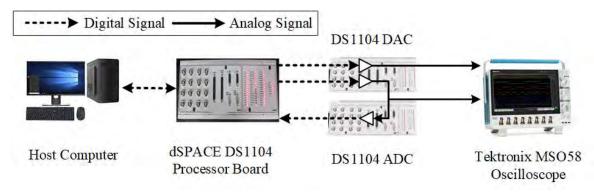

- Fig. 4.19 Experimental Setup......70

Fig. 4.26 Experimental results when frequency step (+5 Hz) is occurred from 50 Hz. ......75

- Fig. 4.29 Experimental results when a combination of phase ( $\theta_b$ =+30° and  $\theta_c$ =+20°) step, and frequency (+5 Hz) step are occurred from 0° and 50 Hz, respectively......78

- Fig. 4.31 Experimental results in presence of 10% DC offset in all phases......79

## List of Tables

Table 1: Grid-connected devices, employing power converters with grid synchronization.....2

# List of Abbreviations

| <u>Abbreviations</u> | <b>Description</b>                    |

|----------------------|---------------------------------------|

| PV                   | Photo Voltaic                         |

| DPGS                 | Distributed Power Generation System   |

| RES                  | Renewable Energy System               |

| DG                   | Distributed Generation                |

| AC                   | Alternating Current                   |

| DC                   | Direct Current                        |

| DVR                  | Dynamic Voltage Restorer              |

| APF                  | Active Power Filter                   |

| STATCOM              | Static Compensator                    |

| UPQC                 | Unified Power Quality Controller      |

| CUPS                 | Custom Power Systems                  |

| FACTS                | Flexible AC Transmission Systems      |

| SVC                  | Static Voltage Compensator            |

| SSSC                 | Static Synchronous Series Compensator |

| UPFC                 | Unified Power Flow Controller         |

| PLL                  | Phase Locked Loop                     |

| FLL                  | Frequency Locked Loop                 |

| SRF-PLL              | Synchronous Reference Frame-PLL       |

| MAF       | Moving Average Filter                             |

|-----------|---------------------------------------------------|

| QT1-PLL   | Quasi-Type-1 PLL                                  |

| CNF       | Complex Notch Filter                              |

| MCCF-PLL  | Multiple Complex Coefficient Filter based PLL     |

| SOGI-PLL  | Second Order Generalized Integrator based PLL     |

| CDSC-PLL  | Cascaded Delayed Signal Cancellation based<br>PLL |

| IPT-PLL   | Inverse Park Transformation-Based PLL             |

| DDSRF-PLL | Decoupled Double SRF-PLL                          |

| FFPS      | Fundamental Frequency Positive Sequence           |

| FFNS      | Fundamental Frequency Negative Sequence           |

| ACT       | Adaptive Clarke Transformation                    |

| VCO       | Voltage Controlled Oscillator                     |

| BPF       | Band Pass Filter                                  |

| PWM       | Pulse Width Modulation                            |

# List of Symbols

| <u>Symbol</u>                     | <u>Nomenclature</u>                                                                                    |

|-----------------------------------|--------------------------------------------------------------------------------------------------------|

| <i>V</i> a, <i>Vb</i> , <i>Vc</i> | Three-Phase Grid Instantaneous Voltages of Phase 'a', 'b', and 'c', Respectively                       |

| $v_A, v_B, v_C$                   | Three Phase Voltages Obtained from Each BPF                                                            |

| $V_{\rm a}, V_b, V_c$             | Amplitudes of Fundamental Voltages of Phases 'a', 'b', and 'c', Respectively                           |

| $V_{\rm A}, V_B, V_C$             | Amplitudes of Three Phase Filtered Voltages                                                            |

| $	heta_b, 	heta_c$                | Phase Angles of Phases 'b' And Phase 'c', Respectively                                                 |

| $v_{\alpha}, v_{\beta}$           | Stationary Frame Orthogonal Signals                                                                    |

| $\phi_A$                          | Instantaneous Phase of Phase 'a' Obtained from SRF-PLL                                                 |

| Δω                                | Frequency Deviation                                                                                    |

| $\phi_{\mathrm{a}}$               | Actual Instantaneous Phases of Phase 'a','b', and 'c', Respectively.                                   |

| $	heta_F$                         | Phase Error Due to BPF in Case of off-Nominal Frequencies                                              |

| $H_l$                             | Transfer Function of 2 <sup>nd</sup> Order BPF.                                                        |

| $T_s$                             | Sampling Time                                                                                          |

| Т                                 | Fundamental Time Period                                                                                |

| $v_B^A$ , $v_C^A$                 | Instantaneous Magnitude of Phase 'b' and 'c', Respectively at The Zero-Crossing Point of Phase 'a'     |

| $v_A^B, v_C^B$                    | Instantaneous Magnitude of Phase 'a' and 'c', Respectively at the Zero-<br>Crossing Point of Phase 'b' |

| $v_A^C, v_B^C$                                            | Instantaneous Magnitude of Phase 'a' and 'b', Respectively at the Zero-<br>Crossing Point of Phase 'c' |

|-----------------------------------------------------------|--------------------------------------------------------------------------------------------------------|

| $\alpha_A, \alpha_B, \alpha_C, \beta_A, \beta_B, \beta_C$ | Coefficients of the CT Matrix                                                                          |

| n                                                         | Index of Voltage Sample                                                                                |

| $ v_A(n) $                                                | Absolute Value of Instant Voltage Sample                                                               |

### **1.1 Importance**

The day-by-day increasing demand for energy and environmental issues of using fossil fuel yield in an increased development of distributed power generation units using renewable energies [1]. Distributed generation system mainly includes wind and PV systems, which are the most growing renewables in the world [2, 3]. The wind and PV systems have low efficiency and their dependency based on both wind and sun are their main drawback. As a consequence, their connection to the utility network can lead to grid instability or even failure without proper control strategies [4]. The distributed power generation system (DPGS) have some requirements and restrictions in order to run over short grid disturbances [5, 6]. Restrictions for renewable energy system (RES) and distributed generation (DG) power quality are given in each country in so called "grid codes" [7, 8]. Operation with certain power factor (close to unity), limited harmonic content of injected current, continuous operation under voltage distortions, etc. are some of the grid requirements for RES [9]. Most of these requirements can be satisfied with proper control of grid connected converter. Therefore, DG and RES are connected to the AC grid through power converters [10, 11].

In DPGS, there are two main control strategies- one is for the input-side converter (e.g., for wind turbines this is an AC-DC converter) and another is for grid-side converter (e.g., for wind turbines this is a DC-AC converter). The input-side controller ensures the maximum power extraction from the input source, generally achieved by using maximum power point tracking algorithm [12]. Moreover, input-side converter protects the input source in case of grid failure. The grid-side converter performs many jobs. It must ensure the quality of output power that is to mitigate voltage dips/swells, flicker, voltage unbalance, harmonics, and transients by controlling the output current. It must control the active power generated to the grid as well as the reactive power exchanged between the DPGS and the grid [13]. Finally, it must play a vital role to synchronize the DPGS with the grid voltage [14].

On the other hand, the power system network at distribution level faces many types of challenges, primarily related to load unbalance, reactive power and current harmonics etc. These issues must be addressed in order to generate and transmit quality power to the

consumers without any disturbance [15, 16]. With the development of sophisticated power electronics technology, lot of custom power devices like dynamic voltage restorer (DVR) [17, 18], active power filters (APF) [19, 20] may be series or shunt type, static compensator (STATCOM) [21, 22], unified power quality controller (UPQC) [23] are widely being used to mitigate power quality problem. Among them DVR, APF, D-STATCOM, UPS etc., known as CUPS (Custom Power Systems), are used to protect against voltage dips, higher harmonics or flicker. There are also devices installed for transmission system support, called flexible AC transmission systems (FACTS), like: STATCOM, SVC, SSSC, UPFC and others [24].

Each of the above-mentioned grid-connected devices has to be precisely synchronized with grid voltage and thus they need accurate control strategies [25]. The controller uses instantaneous phase angle of the grid voltage to produce synchronized reference signal that is used in pulse-width modulation process of the power converters [26]. Therefore, accurate phase angle information of grid voltage is indispensable for proper operation of every grid-connected power converter [27].

| Group of devices                         | Applications                                |

|------------------------------------------|---------------------------------------------|

| Renewable Energy Sources (RES)           | Wind power plants, Photovoltaic plants etc. |

| Custom Power Systems (CUPS)              | UPS, APF, DVR, D-STATCOM, etc.              |

| Flexible AC Transmission Systems (FACTS) | STATCOM, SVC, SSSC, etc.                    |

| Loads                                    | DC loads with AC/DC converters.             |

Table 1: Grid-connected devices, employing power converters with grid synchronization.

### **1.2 Background and Motivation**

Many useful methods are available for the estimation of grid phase information. Those methods can be separated into two categories. One is open loop estimation method and another is close loop estimation method. Some of the open loop algorithms are based on Fourier transformation [28-30], least-error squares [31], weighted least-square-estimation [32], gradient estimator [33], notch filter [34], extended Kalman filter [35, 36], demodulation technique [37], and space vector filtering [38, 39] etc. One advantage of the open loop method is that they can track the phase angle faster in comparison with close loop method as additional time delay in feedback system is absent in open loop methods. However, if the system frequency deviates from the

nominal frequency, these methods generate error in phase calculation. To make them frequency adaptive, some advanced methods have been proposed by modifying the existing methods [40-42]. But they add complexity and increase computational burden.

On the other hand, close loop methods such as phase locked loop (PLL), frequency locked loop (FLL) [43, 44] have better performance but slower response. Among the close loop estimation techniques, the most useful algorithm to track the phases is based on the synchronous reference frame PLL (SRF-PLL) for their simplicity and robustness. The conventional SRF-PLL has excellent phase tracking capability and dynamic performance under ideal grid conditions [45, 46]. However, when the grid voltage is unbalanced and distorted, the SRF-PLL can cause oscillation and accuracy problems [47]. Incorporating an in-loop filter or pre-filter in the SRF-PLL can improve the performances of the PLL.

Using a moving average filter (MAF) in the PLL control loop is suggested in [48, 49]. MAF works as low pass filter (LPF), which mitigates the influence of harmonics [50]. However, the open-loop bandwidth of a MAF incorporated PLL is drastically reduced that results in slower dynamic response [51]. To overcome the dynamic problem of MAF-PLL, some advanced MAF based structures are proposed. In [52], MAF-PLL with phase-lead compensator is proposed that reduces the settling time to 1.79 cycles of fundamental period. In [53], another MAF-based PLL named quasi-type-1 PLL (QT1-PLL) is proposed with a feed forward control path to compensate the phase tracking error, which achieves less settling time (1.75 cycles of fundamental period). However, the MAF-PLLs are unable to reject the DC offsets of the grid voltages. A CNF-QT1-PLL is proposed in [54], which adds a complex notch filter along with MAF to improve the PLLs performance. The settling time is further reduced in the CNF-QT1-PLL. However, MAF-PLLs become more complex to implement and produce error in phase estimation in case of frequency deviation, harmonics and DC offset of the grid voltages. In [48], a hybrid in-loop filter based on CNF and dqCDSC is used, which shows better dynamics during frequency deviation condition. Other in-loop filtering techniques are multiple complexcoefficient-filter-based PLL (MCCF-PLL) [55], the dq-frame delayed signal cancellation operator [56-58], the repetitive regulator [59], which are implemented by considering both filtering capability and dynamic response of the PLL.

Another method to improve the performance of the PLL is using the pre-filtering techniques, which add control strategies before the PLL loop, such as complex-coefficient filter (CCF) [60], multiple second-order generalized integrator based PLL (DSOGI-PLL) [61, 62], multiple

reference frame based PLL (MRF-PLL) [63], MAF [64], DSC operator [57, 58, 65-67]. In [55], a MCCF based SRF-PLL is presented that can extract fundamental positive and negative sequence signals adaptively, but it neglects the dynamic interaction between the SRF-PLL and CCF, which results in error in phase estimation. A solution to the problem is proposed in [60] to enhance the performance of MCCF without additional computational loads. Another effective method, Delayed signal cancellation PLL (DSC-PLL), is proposed recently in [67, 68] using multiple DSC operator that shows good capability in phase estimation. However, the cascading filters require complex calculation and affect the dynamic response. Recently, a signal reforming-based algorithm is used for removing the negative consequences caused by the unbalanced conditions in [69, 70]. The algorithm in [69] uses an amplitude balanced signal generator and a phase balanced signal generator to produce the amplitude and phase balanced FFPS from the unbalanced signals.

### **1.3 Objectives**

The main purpose of this thesis is to develop a phase estimation technique for three-phase voltages in both balanced and unbalanced conditions in presence of harmonics. A conventional SRF-PLL is unable to estimate the phase-angle accurately in presence of harmonics or voltage imbalances. This thesis aims at enhancing the over-all performance under such circumstances.

By using conventional Clarke transformation matrix, it is only possible to transform threephase balanced system to a stationary frame  $\alpha\beta$  system. As a result, conventional SRF-PLL that uses conventional Clarke transformation produces error in phase estimation in case of unbalanced condition. In the proposed method, coefficients of the Clarke transformation matrix have been adaptively updated so that it can directly transform three phase unbalanced voltages to a stationary frame  $\alpha\beta$  voltages. As it is known, if the stationary frame  $\alpha\beta$  voltages are available, phase angles of three-phase voltages can be easily tracked by using conventional SRF-PLL. The proposed method has also presented two separate algorithms for tracking the amplitudes and phase angle deviations of both amplitude and phase unbalanced three-phase system. The amplitudes and phase angle deviations are needed to calculate the adaptive coefficients of the Clarke transformation matrix.

The objectives of the proposed research are -

• To derive analytical expressions for the coefficients of Clarke transformation matrix for adaptively generating accurate orthogonal voltage signals under amplitude and/or phase unbalanced condition.

- To develop an algorithm for tracking the deviations of the amplitudes and phase angles from the balanced condition.

- To build up a three-phase PLL algorithm relying on adaptive Clarke transformation for tracking the phase angles of all three phases under harmonics and both balanced and unbalanced conditions.

### 1.4 Methodology

The thesis has been conducted by following several steps as follows.

Firstly, the proposed research has been carried out in MATLAB/Simulink environment. Threephase fundamental voltages have been produced using three sinusoidal blocks in Simulink. Additional sinusoidal harmonics have been generated based on the IEEE 519 standard [9]. Fundamental voltages and harmonics have been added up to create distorted voltages.

Secondly, three band-pass filters, each per phase, have been used for rejecting the unwanted voltages from the three-phase distorted voltages. An algorithm has been proposed for tracking the amplitudes of the three phases. An additional algorithm has been used to track the phase angle deviations in case of balanced or unbalanced voltages conditions. The estimated value of amplitudes and phase angle deviations have been used to compute the coefficients of the Clarke transformation matrix, which has been used to transform the unbalanced three-phase voltages to orthogonal stationary-frame  $\alpha\beta$  signals. The output of the Clarke transformation has been used as the input of a conventional SRF-PLL.

Finally, in the SRF-PLL block, a Park transformation (phase detector) has been used to generate direct and quadrature axis components from the stationary-frame  $\alpha\beta$  signals. Then, the *q*-axis component, which contains the phase error information, has been passed through a proportional-integral (PI) controller that acts as a low pass filter to generate frequency error. The output of the PI controller has been applied to a voltage-controlled oscillator (VCO) to estimate the phase angle of phase 'a' that is the reference phase. The phase angles of phase 'b' and phase 'c' are also estimated without any additional PLL. The performance of the proposed PLL has also been compared with conventional PLL algorithms reported in the technical literature.

### 1.5 Thesis organization

The thesis entitled "Adaptive Clarke Transformation Based Three-Phase PLL under Amplitude and Phase Unbalances in Presence of Harmonics" is divided into several chapters, which are organized as follows.

In chapter 1, the writing is started by mentioning the importance of estimating phase of three phase voltages and previous works on phase estimation. The objectives of this dissertation are also mentioned to summarize the whole thesis. After that, the methodology of the developed PLL algorithm is presented which describes about adaptive Clarke transformation, amplitude and phase angle deviation estimation, conventional SRF PLL, etc.

Chapter 2 focuses on the review of various common PLL techniques. At first, the basic structure of the PLL is described. Then, the two types of PLL, one is single phase PLL and another is three phase PLL techniques have been presented. Among the single phase PLLs, power based PLL, time delay based PLL, IPT-based PLL, SOGI based PLL are added. Similarly, SRF-PLL, MAF based PLL, SOGI based PLL, DSC-PLL, CCF-PLL, and decoupled SRF-PLL are defined from the three phase PLLs.

In chapter 3, the new developed PLL algorithm is presented in a block diagram to summarize the thesis. At first, a band pass filter is designed to remove harmonics from the input signals. Second, two separate algorithms are developed for amplitude estimation and phase angle deviation estimation of three phase voltages. Finally, a conventional SRF-PLL is constructed to estimate the instantaneous phase angles of all three phases.

The simulation results of the proposed PLL are described in Chapter 4. The results are presented in two categories- first, the performance of the proposed PLL is evaluated without presence of harmonics in input voltages and second, the performance is evaluated in presence of harmonics. The performance of the proposed PLL is also verified by performing some experimental results, which are also included in this chapter.

Chapter 5 concludes the thesis by summarizing the outcome from the thesis and suggesting the future work based on the thesis.

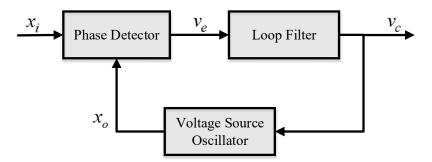

### 2.1 The Basic Structure of Phase Locked Loop

PLL consists of three parts.

- Phase Detector (PD)

- Loop Filter (LF)

- Voltage Controlled Oscillator (VCO)

The PLL works as basic feedback control system that helps to synchronize between the input and output signals. In this system, The PD tracks the difference in phase between the input and output signal of the PLL and the LF filters out the high order harmonics, disturbances from the error signal. The filtered signal is then forwarded toward the VCO, that generates the output of the PLL. Then, the output is feedbacked to the input of PLL.

The PD, as seen in Fig. 2.1 compares the phase of the input signal  $x_i(t)$  against the phase of the VCO output  $x_o(t)$  and produces an error signal  $v_e(t)$ . This error signal is then filtered in order to remove noise and other unwanted components of the input spectrum. The sum of filter output and an additive external control voltage controls the instantaneous VCO frequency. If a VCO input voltage is  $e_o(t)$ , its output is a sinusoid of frequency  $\omega$  given by  $\omega(t) = \omega_{vco} + ce_o(t)$ , where, c is a constant of the VCO and  $\omega_{vco}$  is the free-running frequency of the VCO. A nonzero output voltage must be provided by the PD, in order to tune the VCO frequency to the input one if the input frequency differs from the VCO center frequency. Consequently, the PLL tracks the phase of input signal with some phase error. However, this phase error can be kept very small in a well-designed PLL.

Fig. 2.1 Basic PLL structure.

Let,  $x_i$  and  $x_0$  are the input and VCO signals, which can be expressed as,

$$x_i(t) = A\cos(\omega_i t + \theta_i) \tag{2.1}$$

$$x_o(t) = B\cos(\omega_o t + \varphi_o) \tag{2.2}$$

$\omega_i$  and  $\omega_o$  are angular frequencies of the input and the VCO;  $\theta_i$  and  $\varphi_o$  are their phase constants. The PD is a single multiplier that perform multiplication between the input and VCO signals. The PD output can be written as,

$$v_e(t) = K_d \{ \cos[(\omega_i - \omega_o)t + \theta_i - \varphi_o)] + \cos[(\omega_i + \omega_o)t + \theta_i + \varphi_o)] \}$$

(2.3)

Where  $K_d$  is the gain of the PD. The higher frequency component of PD is eliminated by LF that is a low pass filter. The output of the LP is,

$$v_c(t) = K_d \cos[(\omega_i - \omega_o)t + \theta_i - \varphi_o)]$$

(2.4)

After transient period, the VCO signal synchronize with the input signal and can be expressed as

$$x_o(t) = B\sin(\omega_i t + \phi_o) \tag{2.5}$$

By comparing (2.2) and (2.5), the initial phase angle of VCO can be stated as below that is a linear function of time.

$$\varphi_o = (\omega_i - \omega_o)t + \phi_o \tag{2.6}$$

By substituting the value of  $\varphi_o$  in (2.4), the following expression is obtained

$$v_c(t) = K_d \cos(\theta_i - \phi_o) \tag{2.7}$$

The VCO is a frequency-modulated oscillator and instantaneous angular frequency is proportional to its input control signal ( $v_c(t)$ ) with an offset of central frequency ( $\omega_o$ ), that is

$$\omega_{inst} = \frac{d}{dt}(\omega_o t + \varphi_o) = \omega_o + K_v v_c(t)$$

(2.8)

$$\frac{d\varphi_o}{dt} = K_v v_c(t) \tag{2.9}$$

where  $K_v$  is the VCO sensitivity. From (2.6), (2.7), and (2.9)

$$\omega_{i} - \omega_{o} = K_{v}v_{c}$$

$$\Rightarrow \omega_{i} - \omega_{o} = K_{d}K_{v}\cos(\theta_{i} - \phi_{o})$$

$$\Rightarrow \phi_{o} = \theta_{i} - \cos^{-1}\frac{\omega_{i} - \omega_{o}}{K_{d}K_{v}}$$

(2.10)

(2.11)

From (2.8) and (2.10), it can be observed that the dc signal  $v_c$  is responsible for changing the VCO frequency from central frequency ( $\omega_o$ ) to the input signal angular frequency ( $\omega_i$ ). From eq (11), it can be observed that when  $\omega_i - \omega_o \approx 0$ , the phase difference between VCO and input signal become  $\pi/2$ , indicating that the VCO signal is in phase quadrature with the input signal when the loop is in lock. Letting output angle  $\theta_o = \phi_o + \pi/2$ , (2.7) becomes  $v_c = K_d \sin(\theta_i - \theta_o)$ . When the phase difference is small, the above  $v_c = K_d \sin(\theta_i - \theta_o)$  can be approximated as  $v_c \approx K_d$  ( $\theta_i - \theta_o$ ), which indicates that as far as VCO phase is unequal to input signal phase,  $v_c$  contributes to make them equal. When the phase difference is zero, it is said that the output voltage is locked with the input voltage.

### 2.2 Commonly Used PLL Algorithms

This section describes the most commonly used PLL techniques. The PLL algorithms are mainly two types, which are single phase PLL and three phase PLL algorithm. The single phase PLLs are used to track the instantaneous phase of a phase of the grid voltages, whereas three phase PLLs track the instantaneous phases of all three phases of grid voltages. The most commonly used PLLs are described in this section in detail.

### 2.3 Review of Single Phase PLLs

#### 2.3.1 Power-based PLL (pPLL)

Fig. 2.2 Block diagram of pPLL.

In Fig. 2.2 basic structure of power-based PLL (pPLL) is shown, where, v is the single-phase input signal,  $\omega_g$  and  $\theta$  are the estimated frequency and phase angle, respectively,  $\omega_n$  is the nominal value of the grid frequency, and  $k_p$ ,  $k_i$  are the proportional and integral gains of the PI controller, which acts as the LF. In the PLL, a product type PD is used to produce quadrature component of the input voltage. The model produces double frequency term which creates double frequency oscillatory error in the estimated phase. Another drawback is that grid amplitude information cannot be obtained from the pPLL model and so the pPLL dynamics may not be decoupled from the amplitude variation of the grid voltage. To overcome the drawbacks, double frequency and amplitude compensation (DFAC) method is used, which is shown in Fig. 2.3. In this method, double frequency terms in both quadrature and direct axis are nullified by multiplying equal but opposite double-frequency components. DFAC-pPLL method also decouples the amplitude variation effect on phase estimation as the quadrature axis component is being normalized.

Fig. 2.3 Modified block diagram of pPLL [71].

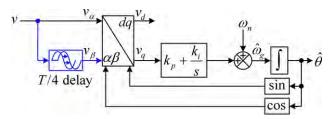

### 2.3.2 Transfer delay (TD) PLL

Fig. 2.4 Block diagram of Transfer Delay (TD) PLL [72].

In Fig. 2.4, the transfer delay (TD) PLLs structure is shown, which is a quadrature signal generation-based PLLs (QSG-PLLs). In TD-PLL, an orthogonal signal  $v_{\beta}$  is generated by introducing *T*/4 time delay to the original voltage, where *T* is the fundamental voltage period. Then, direct and quadrature signals are generated from the orthogonal signals by using Park

transformation. This is easily comparable to the conventional SRF-PLL, which will be discussed later. The shortcoming of the standard TD-PLL is that, it cannot generate orthogonal signals under distorted grid voltages that results in error in the phase estimation. To overcome this drawback, some advanced algorithms are proposed in literature.

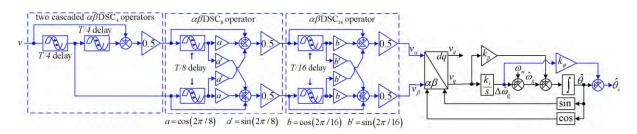

Mathematically, a single-phase system can be represented by two-phase system where a phase is equal to zero, which is mathematically equivalent to  $\alpha\beta$  frame delayed signal cancellation operator with the delay factor 4 (or briefly the  $\alpha\beta$ DSC4). By using two cascaded DSC4 operators, a wider notch around the fundamental voltage of the negative sequence is obtained, which results in better performance during frequency drift. The DC offset error in phase estimation in standard TD-PLL is due to phase shift in  $\alpha\beta$ DSC operators, that is also eliminated by subtracting the phase error from the actual estimation. A better performance can be obtained by cascading several DSCs. The modified structure is called enhanced TD-PLL that is shown in Fig. 2.5.

Fig. 2.5 Modified block diagram of Transfer Delay (TD) PLL [73].

2.3.3 Inverse Park transformation-based PLL (IPT-PLL)

Fig. 2.6 Block diagram of IPT based PLL.

The inverse Park transformation-based PLL (IPT-PLL) shown in Fig. 2.6 is a well-known and popular PLL in single-phase applications [74]. In this PLL, orthogonal signal is generated by using dq-to- $\alpha\beta$  transformation, that is inverse Park transformation. At first, Park transformation

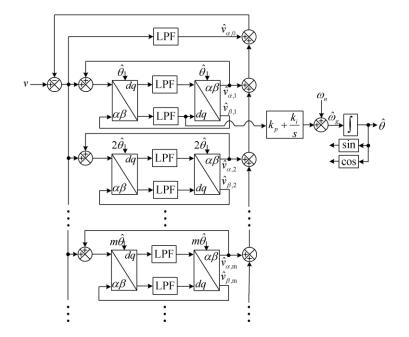

is used to generate dq-frame signals, then inverse Park transformation is used to generate  $\alpha\beta$  signals from dq-frame signals. When, in addition to the fundamental component, extracting the DC offset and some harmonic components are needed and/or for applications where a high filtering capability is required, the IPT-PLL can be extended as shown in Fig. 2.7. Obviously, selecting the number of filtering modules involves a tradeoff between the detection accuracy and the computational burden.

Fig. 2.7 Modified block diagram of IPT based PLL [71].

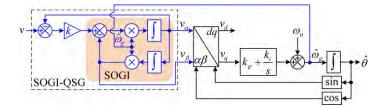

#### 2.3.4 Second Order Generalized Integrator (SOGI) based PLL

Fig. 2.8 Block diagram of SOGI based PLL [75].

Fig. 2.8 shows the diagram of a single-phase SOGI based PLL. SOGI has double integrator block and requires both grid voltage and angular frequency to produce orthogonal signals. The integrators represent two second-order filters with an adjustable bandwidth and resonance frequency equal to the frequency of the input signal. If the grid frequency is at the resonance frequency of the SOGI, the signal  $v_{\alpha}$  has the same phase and amplitude as the fundamental of the input signal and  $v_{\beta}$  is orthogonal to  $v_{\alpha}$ . The behavior of the whole PLL structure will be affected by the transients of the SOGI and the feedback control loop.

### 2.4 Review of Three Phase PLLs

#### 2.4.1 Three Phase SRF-PLL

In the SRF-PLL, Clarke and Park transformation (phase detector) is used to generate direct and quadrature axis components from the three phase voltages. Then, the *q*-axis component, which contains the phase error information, is passed through a proportional-integral (PI) controller that acts as a low pass filter to generate frequency error. The output of the PI controller is then applied to a voltage-controlled oscillator (VCO) to estimate the phase angle. The conventional SRF-PLL has excellent phase tracking capability and dynamic performance under ideal grid conditions. However, when the grid voltage is unbalanced and distorted, the SRF-PLL can cause oscillation and accuracy problems. To solve this problem, numerous advanced PLLs have been intensively studied [46]. Details about the SRF-PLL will be discussed later.

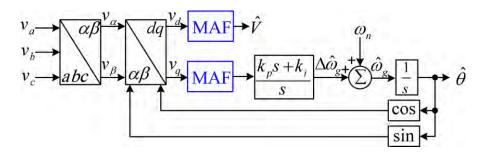

#### 2.4.2 MAF based PLL

Incorporating a moving average filter (MAF) in the SRF-PLL improves the performances of the SRF-PLL. The MAF block is placed before the PI filter block, as seen in Fig. 2.9. MAF works as low pass filter (LPF), which mitigates the influence of harmonics. However, the open-loop bandwidth of a MAF incorporated PLL is drastically reduced that results in slower dynamic response [51]. To overcome the dynamic problem of MAF-PLL, some advanced MAF based structures are proposed. In [52], MAF-PLL with phase-lead compensator is proposed that reduces the settling time to 1.79 cycles of fundamental period. In [53], another MAF-based PLL named quasi-type-1 PLL (QT1-PLL) is proposed with a feed forward control path to compensate the phase tracking error, which achieves less settling time (1.75 cycles of fundamental period). However, the MAF-PLLs are unable to reject the DC offsets of the grid voltages.

Fig. 2.9 Block diagram of MAF based PLL [76].

#### 2.4.3 Second Order Generalized Integrator based PLL

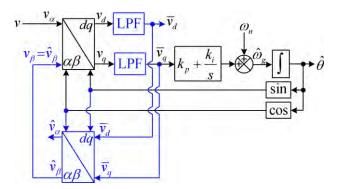

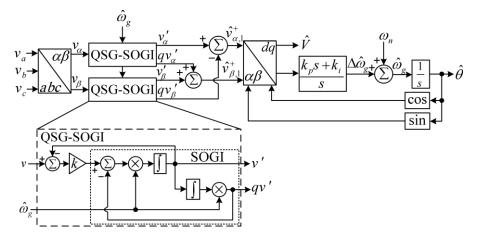

Fig. 2.10 Block diagram of SOGI based PLL [46].

A second-order generalized integrator (SOGI) is a useful tool for the extraction and separation of the FFPS and FFNS components of three-phase signals, which is shown in Fig. 2.10 [77]. As shown, two QSG-SOGIs are used to extract the filtered direct and quadrature versions of v'and qv'. The FFPS component is then calculated based on the instantaneous symmetrical components (ISC) method. This PLL structure, is often called the dual QSG-SOGI based PLL (DSOGI-PLL). Some improved SOGI such as third-order generalized integrator (TOGI) is also proposed for better performance [78].

#### 2.4.4 Delayed Signal Cancellation PLL

In delayed signal cancelation (DSC) method, FFPS and FFNS components of the grid voltage are separated. This procedure contains stationary reference frame voltage and a voltage vector delayed by a quarter of cycle. After the separation, the obtained positive-sequence and components are input to an SRF-PLL to calculate its amplitude and angular position. The DSC operators are cascaded to get better performance in presence of harmonics and voltage unbalances. The Cascaded DSC is two types. One is pre-filter based method, where the DSC operates before the loop-filter of the SRF-PLL. Another is in-loop filter based method, which is known as dqCDSC. Multiple CDSC operators can then be arranged in parallel to simultaneously track multiple harmonics. DSC is also used to cancel out the negative-sequence fundamental component in unbalanced grid voltage. By combining the original  $\alpha$  and  $\beta$  components of grid voltage and their quarter-cycle delayed versions, DSC-PLL can effectively eliminate the oscillatory errors resulted from voltage unbalance.

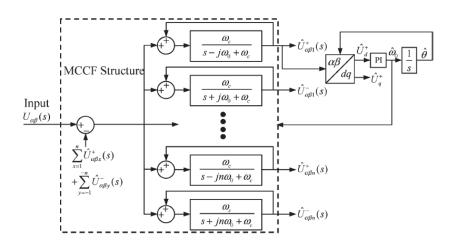

#### 2.4.5 Complex Coefficient Filter

Complex coefficient filters (CCFs) have an asymmetrical frequency response around zero frequency, which enables them to distinct between the positive and negative sequences (polarities) of the same frequency. By using this feature, fundamental positive, negative and other harmonics can be easily extracted from the distorted grid voltages. The Fig. 2.11 shows multiple CCFs based PLL (MCCF), which is popularly used in the literatures. To extract the positive sequence fundamental frequency component only two CCFs are used, which is referred as dual CCF-based PLL (DCCF-PLL). To make the model frequency adaptive, estimated frequency from the PLL is feedbacked to the CCFs.

Fig. 2.11 Block diagram of CCF based PLL [46].

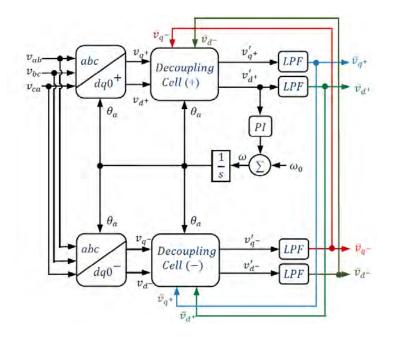

#### 2.4.6 Decoupled SRF-PLL

The decoupled double SRF (DDSRF)-PLL extracts both the positive and negative-sequence voltage components in the  $dq\theta$  reference frame from *abc* voltages. Fig. 2.12 shows the block diagram of DDSRF-PLL, where two transformation blocks are used for the positive- and negative sequence components. The decoupling cells cancels the oscillations in  $+dq\theta$  and  $-dq\theta$  components that improves the PLL performances during input voltages' unbalances. Like SRF-PLL, a closed-loop structure with a PI controller is used to obtain the signals' phase-angle and frequency. DDSRF-PLL eliminates the drawback of the classical SRF-PLL and can estimate the phase-angle of the distorted asymmetrical three-phase systems.

Fig. 2.12 Block diagram of Decoupled SRF-PLL [79].

# 2.5 The Performance of Conventional SRF-PLL Algorithm

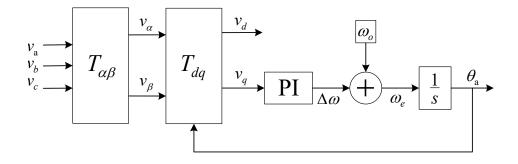

In conventional SRF-PLL, Clarke and Park transformation are used to obtain direct ( $v_d$ ) and quadrature ( $v_q$ ) axis components from three-phase input voltages. The quadrature component is then passed through a proportional-integral filter to filter out noises and high order components from the  $v_q$ . The output of the PI contains frequency deviation information, which is added with nominal frequency to get the actual frequency of the input voltages. Finally, the phase is attained by integrating the frequency component. However, coefficients of Clarke and Park transformation matrix are constant at conventional SRF-PLL. As a result, the conventional SRF-PLL results in error in case of unbalanced amplitude and/or phase angle deviations conditions.

Fig. 2.13 Structure of Conventional SRF-PLL.

In Fig. 2.13, three-phase input voltages are denoted by  $v_a$ ,  $v_b$ , and  $v_c$ . Clarke transformation matrix,  $T_{\alpha\beta}$  converts the input voltages to orthogonal voltages,  $v_{\alpha}$  and  $v_{\beta}$ . The park transformation function is symbolized by  $T_{dq}$ , which converts orthogonal voltages to the direct and quadrature axis components  $v_d$ , and  $v_q$ . The output of PI filter is marked as  $\Delta\omega$ , which is the frequency deviation from fundamental frequency  $\omega_o$ , and the estimated angular frequency is denoted by  $\omega_e$ . The integration block is shown as 1/s and  $\theta_a$  is the estimated phase of phase 'a'.

The following equations are necessary to estimate the phase by using conventional SRF-PLL.

$$\begin{bmatrix} v_{\alpha} \\ v_{\beta} \end{bmatrix} = T_{\alpha\beta} \cdot \begin{bmatrix} v_{a} \\ v_{b} \\ v_{c} \end{bmatrix}$$

$$\begin{bmatrix} v_{d} \\ v_{q} \end{bmatrix} = T_{dq} \cdot \begin{bmatrix} v_{\alpha} \\ v_{\beta} \end{bmatrix}$$

$$T_{\alpha\beta} = \sqrt{\frac{2}{3}} \cdot \begin{bmatrix} 1 & -\frac{v_{2}}{\sqrt{3}} & -\frac{v_{2}}{\sqrt{3}} \\ 0 & \sqrt{3}^{2} & -\sqrt{3}^{2} \end{bmatrix}$$

$$T_{dq} = \frac{2}{3} \begin{bmatrix} \sin \theta & -\cos \theta \\ \cos \theta & \sin \theta \end{bmatrix}$$

$$\theta = \int (\omega_{o} + \Delta \omega) dt$$

In the subsequent sections, the performance of SRF-PLL is demonstrated for both the balanced and unbalanced input voltages in absence or presence of harmonics.

# 2.6 SRF-PLL without Harmonics

#### 2.6.1 Case1: Balanced

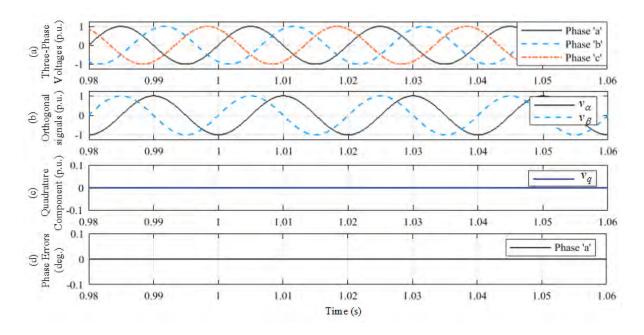

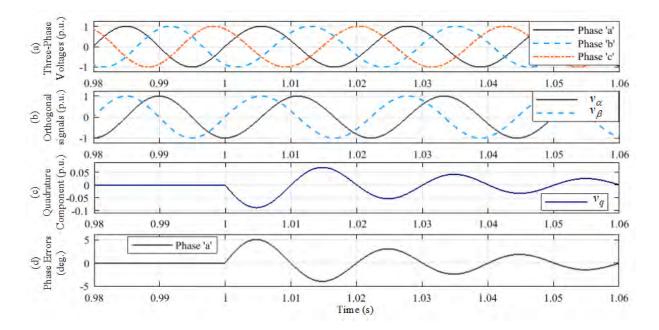

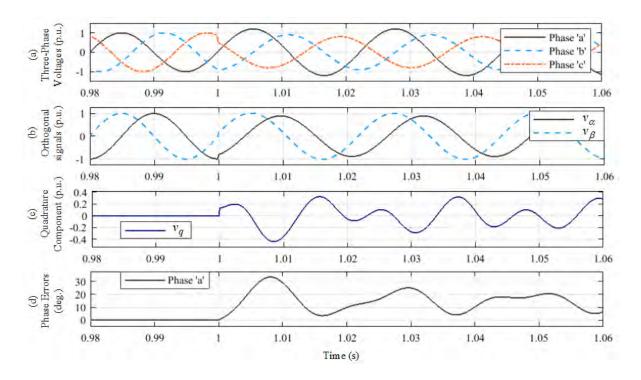

The performance of SRF-PLL is demonstrated in Fig. 2.14 for balanced three phase input voltages. Fig. 2.14(a) shows the balanced three phase input voltages with 1 p.u. amplitudes. In Fig. 2.14(b), stationary frame orthogonal voltages are shown. Fig. 2.14(c) illustrates the quadrature axis component of PD output, which contributes to lock the VCO phase to the input signal phase by controlling the VCO signal. In Fig. 2.14(d), the phase error, difference between the input and estimated phase, is shown, which depicts that SRF-PLL estimate the phase perfectly during the balanced condition.

Fig. 2.14 Simulation results of SRF-PLL for balanced input voltages. (a) Three-Phase Voltages (p.u.) (b) Orthogonal Signals (p.u.) (c) Quadrature Axis Component (p.u.) (d) Estimated Phase Error (deg.).

# 2.6.2 Case 2: Amplitude Step

Fig. 2.15 Simulation results of SRF-PLL, when amplitude steps ( $v_a = 20\%$ ,  $v_b = -10\%$ ,  $v_c = -20\%$ ) occur at t=1s. (a) Three-Phase Voltages (p.u.) (b) Orthogonal Signals (p.u.) (c) Quadrature Axis Component (p.u.) (d) Estimated Phase Error (deg.).

The performance of SRF-PLL is demonstrated in Fig. 2.15 for amplitude unbalanced three phase input voltages. Fig. 2.15(a) shows the input voltages with amplitude steps ( $v_a = 20\%$ ,  $v_b$

= -10%,  $v_c$  = -20%) at t=1s. As it can be seen in Fig. 2.15(b), SRF-PLL is unable to produce orthogonal signals of equal amplitudes after the step change. Fig. 2.15(c) illustrates the quadrature axis component, where almost 0.2 p.u. oscillation occurs after the step change. In Fig. 2.15(d), the phase error, difference between the input and estimated phase, is shown, which depicts that SRF-PLL produces almost 2° oscillatory error in phase estimation if amplitude unbalanced condition occurs.

### 2.6.3 Case 3: Phase Step

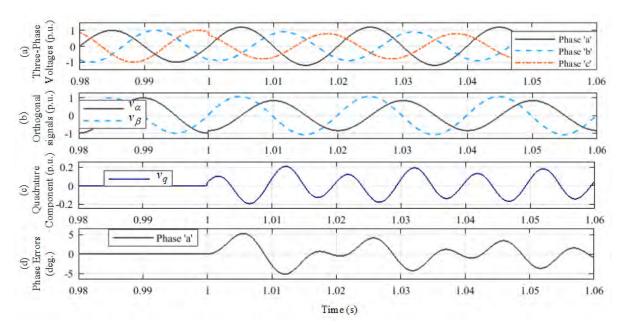

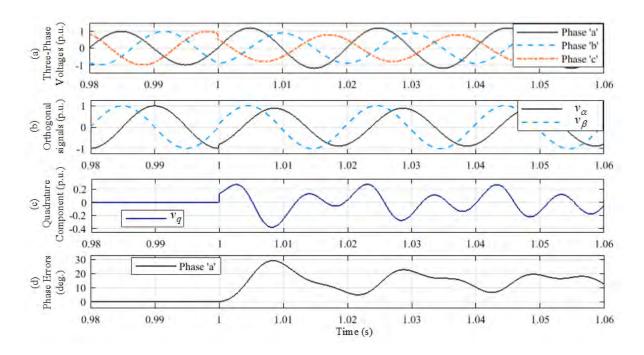

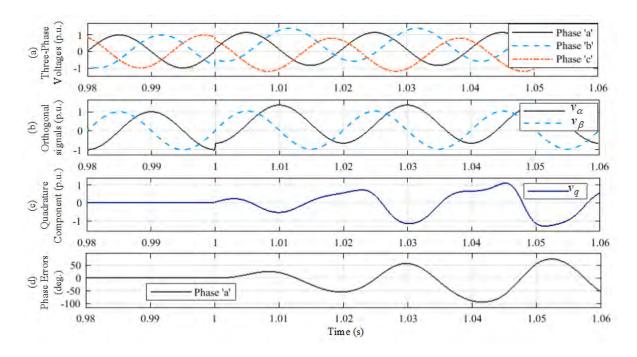

The performance of SRF-PLL is demonstrated in Fig. 2.16 for unbalanced phase angle condition. Fig. 2.16(a) shows the input voltages with phase angle steps ( $\theta_b=30^\circ$ ,  $\theta_c=20^\circ$ ) occur at t=1s. As it can be seen in Fig. 2.16(b), SRF-PLL produce unequal orthogonal signals after the step change. Fig. 2.16(c) illustrates the quadrature axis component, where almost 0.4 p.u. oscillation occurs after the step change. In Fig. 2.16(d), the phase error, difference between the input and estimated phase, is shown, which depicts that SRF-PLL produces almost 15° offset error and ±1.5° oscillatory error after the step change occurs.

## 2.6.4 Case 4: Frequency Step

The performance of SRF-PLL is demonstrated in Fig. 2.17 for frequency deviation of input signals from nominal frequency. Fig. 2.17(a) shows the input voltages with frequency step  $(\Delta f=-5 \text{ Hz})$  at t=1s. As it can be seen in Fig. 2.17(b), SRF-PLL produce non-orthogonal signals after the step change. Fig. 2.17(c) illustrates the quadrature axis component, where almost 0.05 p.u. oscillation occurs after the step change. In Fig. 2.17(d), the phase error, difference between the input and estimated phase, is shown, which depicts that SRF-PLL produces almost 1.5° oscillation in phase estimation after the step occurs.

Fig. 2.16 Simulation results of SRF-PLL, when phase angle steps ( $\theta_b=30^\circ$ ,  $\theta_c=20^\circ$ ) occur at t=1s. (a) Three-Phase Voltages (p.u.) (b) Orthogonal Signals (p.u.) (c) Quadrature Axis Component (p.u.) (d) Estimated Phase Error (deg.).

Fig. 2.17 Simulation results of SRF-PLL, when frequency step ( $\Delta f$ =-5 Hz) occur at t=1s. (a) Three-Phase Voltages (p.u.) (b) Orthogonal Signals (p.u.) (c) Quadrature Axis Component (p.u.) (d) Estimated Phase Error (deg.).

### 2.6.5 Case 5: Amplitude and Phase Steps

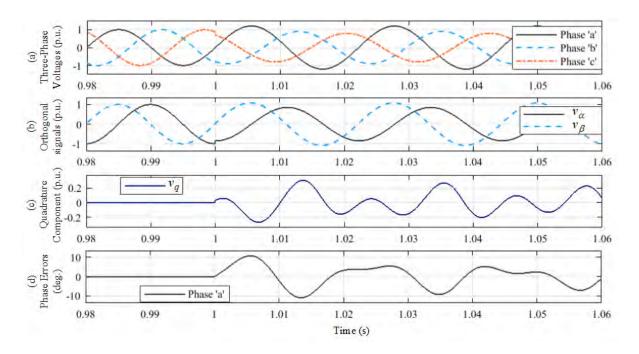

The performance of SRF-PLL is demonstrated in Fig. 2.18 for amplitude and phase angle unbalanced three phase input voltages. Fig. 2.18(a) shows the input voltages with amplitude steps ( $v_a = 20\%$ ,  $v_b = -10\%$ ,  $v_c = -20\%$ ) and phase angle steps ( $\theta_b=30^\circ$ ,  $\theta_c=20^\circ$ ) at t=1s. As it can be seen in Fig. 2.18(b), SRF-PLL is unable to produce orthogonal signals of equal amplitudes after the step change. Fig. 2.18(c) illustrates the quadrature axis component, where almost 0.3 p.u. oscillation occurs after the step change. In Fig. 2.18(d), the phase error, difference between the input and estimated phase, is shown, which depicts that SRF-PLL produces almost 12° offset error and  $\pm 4^\circ$  oscillatory error in phase estimation with 5 ms transient time.

Fig. 2.18 Simulation results of SRF-PLL, when amplitude steps ( $v_a = 20\%$ ,  $v_b = -10\%$ ,  $v_c = -20\%$ ) and phase angle steps ( $\theta_a=30^\circ$ ,  $\theta_b=20^\circ$ ) occur at t=1s. (a) Three-Phase Voltages (p.u.) (b) Orthogonal Signals (p.u.) (c) Quadrature Axis Component (p.u.) (d) Estimated Phase Error (deg.).

### 2.6.6 Case 6: Amplitude and Frequency Steps

The performance of SRF-PLL is demonstrated in Fig. 2.19, when amplitude unbalance and frequency deviation occur simultaneously. Fig. 2.19(a) shows the input voltages with amplitude steps ( $v_a = 20\%$ ,  $v_b = -10\%$ ,  $v_c = -20\%$ ) and frequency step ( $\Delta f = -5$  Hz) at t=1s. As it can be seen in Fig. 2.19(b), SRF-PLL is unable to produce orthogonal signals of equal amplitudes after the step change. Fig. 2.19(c) illustrates the quadrature axis component, where

almost 0.3 p.u. oscillation occurs after the step change. In Fig. 2.19(d), the phase error, difference between the input and estimated phase, is shown, which depicts that SRF-PLL produces almost 6° error in phase estimation with 2 ms transient time.

Fig. 2.19 Simulation results of SRF-PLL, when amplitude steps ( $v_a = 20\%$ ,  $v_b = -10\%$ ,  $v_c = -20\%$ ) and frequency step ( $\Delta f$ =-5 Hz) occur at t=1s. (a) Three-Phase Voltages (p.u.) (b) Orthogonal Signals (p.u.) (c) Quadrature Axis Component (p.u.) (d) Estimated Phase Error (deg.).

## 2.6.7 Case 7: Phase and Frequency Steps

The performance of SRF-PLL is demonstrated in Fig. 2.20, when phase angle unbalance and frequency deviation occur simultaneously. Fig. 2.20(a) shows the input voltages with phase angle steps ( $\theta_b$ =30°,  $\theta_c$ =20°) and frequency step ( $\Delta f$ =-5 Hz) at t=1s. As it can be seen in Fig. 2.20(b), SRF-PLL is unable to produce orthogonal signals of equal amplitudes after the step change. Fig. 2.20(c) illustrates the quadrature axis component, where almost 0.5 p.u. oscillation occurs after the step change. In Fig. 2.20(d), the phase error, difference between the input and estimated phase, is shown, which depicts that SRF-PLL produces almost 10° offset error and  $\pm$ 4° oscillatory error in phase estimation with 5 ms transient time.

Fig. 2.20 Simulation results of SRF-PLL, when phase angle steps ( $\theta_b=30^\circ$ ,  $\theta_c=20^\circ$ ) and frequency step ( $\Delta f=-5$  Hz) occur at t=1s. (a) Three-Phase Voltages (p.u.) (b) Orthogonal Signals (p.u.) (c) Quadrature Axis Component (p.u.) (d) Estimated Phase Error (deg.).

#### 2.6.8 Case 8: Amplitude, Phase and Frequency Steps

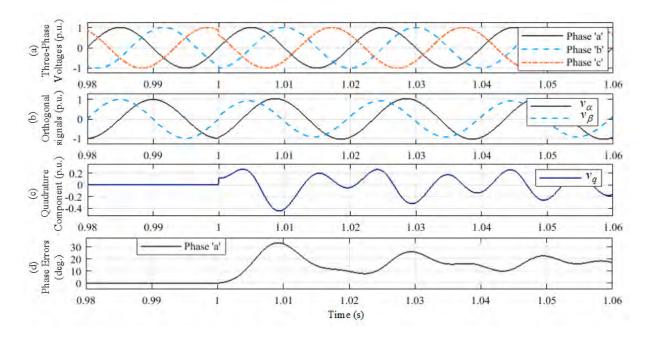

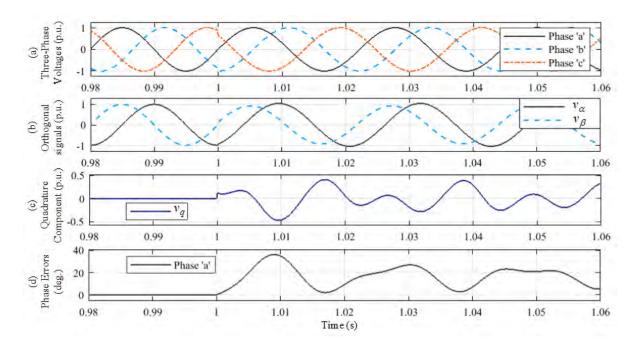

The performance of SRF-PLL is demonstrated in Fig. 2.21, when amplitude, phase angle unbalance and frequency deviation occur simultaneously. Fig. 2.21(a) shows the input voltages with amplitude steps ( $v_a = 20\%$ ,  $v_b = -10\%$ ,  $v_c = -20\%$ ), phase angle steps ( $\theta_b = 30^\circ$ ,  $\theta_c = 20^\circ$ ), and frequency step ( $\Delta f = -5$  Hz) at t=1s. As it can be seen in Fig. 2.21(b), SRF-PLL is unable to produce orthogonal signals of equal amplitudes after the step change. Fig. 2.21(c) illustrates the quadrature axis component, where almost 0.3 p.u. oscillation occurs after the step change. In Fig. 2.21(d), the phase error, difference between the input and estimated phase, is shown, which depicts that SRF-PLL produces almost 10° offset error and  $\pm 5^\circ$  oscillatory error in phase estimation with 5 ms transient time.

Fig. 2.21 Simulation results of SRF-PLL, when amplitude steps ( $v_a = 20\%$ ,  $v_b = -10\%$ ,  $v_c = -20\%$ ), phase angle steps ( $\theta_b=30^\circ$ ,  $\theta_c=20^\circ$ ), and frequency step ( $\Delta f=-5$  Hz) occur at t=1s. (a) Three-Phase Voltages (p.u.) (b) Orthogonal Signals (p.u.) (c) Quadrature Axis Component (p.u.) (d) Estimated Phase Error (deg.).

### 2.6.9 Case 9: DC Offset

The performance of SRF-PLL is demonstrated in Fig. 2.22 for unequal DC offset in three phase input voltages. Fig. 2.22(a) shows the input voltages with unequal DC offset steps ( $v_a = 15\%$ ,  $v_b = 40\%$ ,  $v_c = -20\%$ ) occur at t=1s. As it can be seen in Fig. 2.22(b), SRF-PLL is unable to produce orthogonal signals of equal amplitudes after the step change. Fig. 2.22(c) illustrates the quadrature axis component, where almost 1 p.u. oscillation occurs after the step change. In Fig. 2.22(d), the phase error, difference between the input and estimated phase, is shown, which depicts that SRF-PLL produces large error and becomes unstable with time.

Fig. 2.22 Simulation results of SRF-PLL, when unequal DC offset steps ( $v_a = 15\%$ ,  $v_b = 40\%$ ,  $v_c = -20\%$ ) occur at t=1s. (a) Three-Phase Voltages (p.u.) (b) Orthogonal Signals (p.u.) (c) Quadrature Axis Component (p.u.) (d) Estimated Phase Error (deg.).

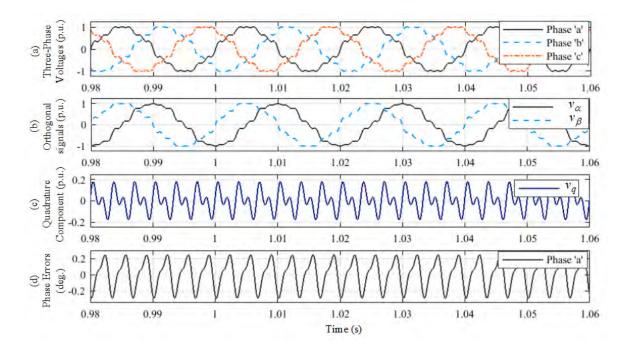

# 2.7 SRF-PLL with Harmonics

The performance of the SRF-PLL is shown in Fig. 2.23, when input balanced signals contain harmonics. In each phase, 5<sup>th</sup>, 7<sup>th</sup>, 11<sup>th</sup> and 13<sup>th</sup> harmonic components are considered and the amplitude of each harmonic is selected as 5% of input signals amplitudes to add harmonics. Fig. 2.23(a) shows the input balanced voltages with harmonics. The produced orthogonal  $\alpha\beta$  signals are depicted in Fig. 2.23(b), which shows that SRF-PLL is unable to produce orthogonal signals of equal amplitudes if the input signals contain harmonics. Fig. 2.23(c) illustrates the quadrature axis component, where almost 0.2 p.u. oscillation occurs from the beginning of simulation. In Fig. 2.23(d) the phase error, difference between the input and estimated phase, is shown, which depicts that SRF-PLL produces almost  $\pm 0.2^{\circ}$  error in phase estimation.

Fig. 2.23 Simulation results of SRF-PLL for balanced input voltages in presence of 5% harmonics. (a) Three-Phase Voltages (p.u.) (b) Orthogonal Signals (p.u.) (c) Quadrature Axis Component (p.u.) (d) Estimated Phase Error (deg.).

From the above analysis, it can be said that the SRF-PLL has limitations in instantaneous phase estimation in case of sudden changes in amplitudes, phases, frequencies of input voltages. This is because the conventional SRF-PLL depends on constant coefficients of Clarke transformation to produce orthogonal signals. Therefore, when the voltage parameters change but the coefficients of the transformation remain constant, the SRF-PLL fails to produce accurate orthogonal signals. Moreover, in presence of harmonics, though the input signals are balanced, the SRF-PLL produce large oscillation in phase estimation. In the next section, a three-phase phase-locked loop (PLL) algorithm relying on an adaptive Clarke transform (CT) is proposed to estimate instantaneous phases of three-phases under amplitude and/or phase angle unbalanced condition.

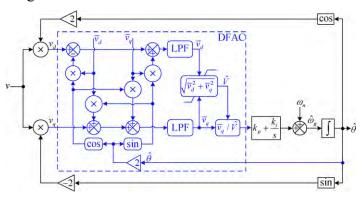

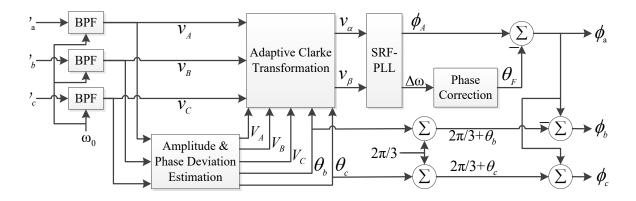

# **3.1 Block Diagram of Proposed PLL**

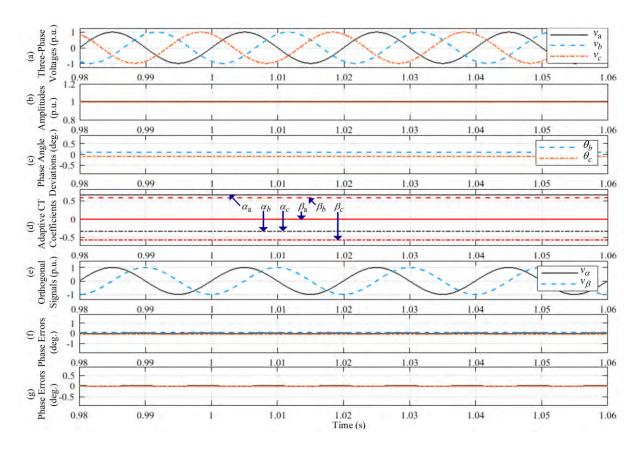

The block diagram representation of the proposed technique for phase estimation is shown in Fig. 3.1. As it can be seen, at first, three-phase grid instantaneous voltages of phase 'a', 'b', and 'c' incorporating with harmonics and dc offset are symbolized by  $v_a$ ,  $v_b$ , and  $v_c$ , respectively. Then, the distorted input voltage of each phase passes through a band-pass filter (BPF). The purpose of the BPF is to reject harmonics and dc voltages from the input voltages. The output of BPF contains three-phase fundamental voltages that is denoted by  $v_A$ ,  $v_B$ , and  $v_C$ , respectively. The fundamental voltages are then forwarded to amplitude and phase-deviation estimation block. This block is used to track  $V_A$ ,  $V_B$ , and  $V_C$ , amplitudes of the fundamental voltages of phases 'a', 'b', and 'c', respectively. The block also estimates phase deviations of phases 'b' and 'c' from 120° with respect to the reference phase 'a', which are denoted by  $\theta_b$ and  $\theta_c$ , respectively. Then, an Adaptive Clarke Transformation (ACT) is used. The ACT helps to generate orthogonal in-phase and quadrature voltages,  $v_{\alpha}$  and  $v_{\beta}$ , from the three-phase unbalanced/balanced voltages. The input of the ACT are the three-phase fundamental voltages, and their amplitudes and phase deviations information. The main feature of the ACT is that it can generate orthogonal in-phase and quadrature voltages in both amplitude and/or phase unbalanced condition of the phase voltages. At this stage, a conventional SRF-PLL is used to track the phase-angle,  $\phi_A$ , of phase 'a' from the orthogonal input signals. However, BPF introduces error in the estimated phase when frequency deviates from fundamental frequency. A phase correction block is added to estimate the error,  $\theta_F$ . The phase correction block uses the estimated frequency error,  $\Delta \omega$ , obtained from SRF-PLL to calculate the phase error. Finally, the phase error is subtracted from  $\phi_A$  to obtain actual phase angle ( $\phi_a$ ) of  $v_A$ . The phase angles  $(\phi_b \text{ and } \phi_c)$  of other two phase voltages is attained by processing  $\phi_a$ ,  $\theta_b$ , and  $\theta_c$ , as demonstrated in Fig. 3.1. The detail functions of each block shown in Fig. 3.1 is described in following subsections.

Fig. 3.1 Block Diagram Representation of the Proposed Technique.

The three phase grid voltages may include DC offset and harmonics due to non-linear loads, measurement devices, grid faults and can be expressed as follows.

$$v_{a}(n) = V_{a} \sin\{\phi_{a}(n)\} + DC \text{ offset+Harmonics} v_{b}(n) = V_{b} \sin\{\phi_{a}(n) - 2\pi/3 + \theta_{b}\} + DC \text{ offset+Harmonics} v_{c}(n) = V_{c} \sin\{\phi_{a}(n) + 2\pi/3 + \theta_{c}\} + DC \text{ offset+Harmonics}$$

(3.1)

where *n* is the sampling index,  $V_a$ ,  $V_b$ , and  $V_c$  are the amplitudes of fundamental voltages of phases 'a', 'b', and 'c', respectively,  $\phi_a(n)$ ,  $[\phi_a(n)-2\pi/3+\theta_b]$ , and  $[\phi_a(n)+2\pi/3+\theta_c]$  are instantaneous phase angles of phases 'a', 'b', 'c', respectively.

# 3.2 Attenuation of Harmonics: Design of Band Pass Filter

In order to reject harmonics from the grid voltages, a band pass filter (BPF) is tuned in this sub-section. The tuned BPF is based on the following transfer function [80],

$$H_1(s) = \frac{1-\alpha}{2} \frac{1-z^{-2}}{1-\beta(1+\alpha)z^{-1}+\alpha z^{-2}}$$

(3.2)

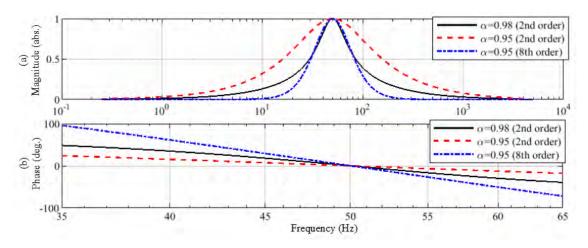

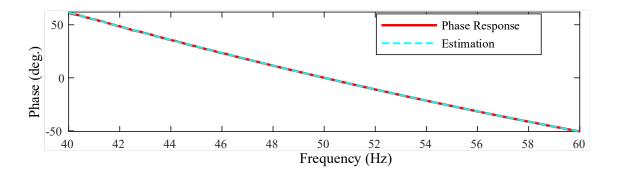

Where,  $\alpha$  and  $\beta$  are the tuning parameters of the filter. In Fig. 3.2, the magnitude and phase response of 2<sup>nd</sup> and 8<sup>th</sup> order filters are shown for  $\alpha$ =0.95, 0.98 and  $\beta$ =2 $\pi fT_s$ , where *f* is nominal frequency and  $T_s$  is sampling time. The 2<sup>nd</sup> order band-pass filter of (3.2) mitigates higher order harmonics perfectly. However, a significant portion of the lower order harmonics pass through the filter. Harmonics rejection capacity of filters can be increased by changing the tuning parameters,  $\alpha$  and  $\beta$ . In Fig. 3.2(a), it is seen that by changing the value of  $\alpha$  from 0.95 to 0.98 the bandwidth of the filter decreases. Though the harmonic rejection capacity increases with lower bandwidth, the speed of the filter decreases. To maintain higher harmonic rejection

capacity and higher speed, the order of the filter can be increased by cascading several 2<sup>nd</sup> order filters without changing the tuning parameters. In Fig. 3.2(a), it is observed that the same speed with better harmonic rejection capacity is achieved while using 8<sup>th</sup> order filter (four cascaded 2<sup>nd</sup> order filter) and  $\alpha$ =0.95. Therefore, in this article, an 8<sup>th</sup> order filter with  $\alpha$ =0.95 and  $\beta = \pi/100$  is used in each phase as BPF to reject harmonics and DC offset from the phase voltage. Now, the tuned BPF can remove the prominent grid harmonics efficiently.

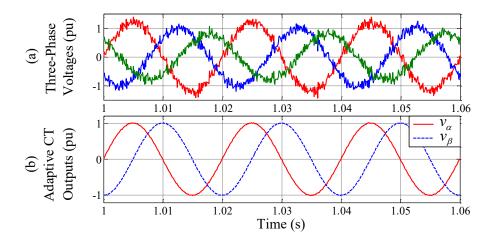

Fig. 3.2 Magnitude and Phase response of BPF.

From Fig. 3.2(b), it is seen that the BPF has zero phase response at 50 Hz frequency. As a result, if the grid's frequency deviates from the nominal frequency, BPF introduces error in phase estimation. The error can be corrected by using phase response of the filter, if frequency deviation is known, which will be discussed in section 3.4. The BPF is fixed tuned at 50 Hz (nominal frequency) under any conditions of grid voltages, that is why, there is no need to estimate system frequency at the filtering stage. After filtering out the harmonics and DC offset, the unbalanced three phase voltages are expressed as below.

$$\begin{array}{l} v_{A}(n) = V_{A} \sin\{\phi_{A}(n)\} \\ v_{B}(n) = V_{B} \sin\{\phi_{A}(n) - 2\pi/3 + \theta_{b}\} \\ v_{C}(n) = V_{C} \sin\{\phi_{A}(n) + 2\pi/3 + \theta_{c}\} \end{array}$$

(3.3)

# 3.3 Adaptive Clarke Transform for Unbalanced System

In this section, six analytical expressions are derived to calculate the six coefficients of 2x3 Clarke transformation (CT) matrix for generating accurate orthogonal voltage signals under amplitude and/or phase unbalanced condition.

The Clarke transformation can be expressed as follows,

$$\begin{bmatrix} v_{\alpha} \\ v_{\beta} \end{bmatrix} = \begin{bmatrix} \alpha_A & \alpha_B & \alpha_C \\ \beta_A & \beta_B & \beta_C \end{bmatrix} \begin{bmatrix} v_A & v_B & v_C \end{bmatrix}^*$$

(3.4)

where \* denotes transpose operation and  $\alpha_A$ ,  $\alpha_B$ ,  $\alpha_C$ ,  $\beta_A$ ,  $\beta_B$ ,  $\beta_C$  are the coefficients of the CT matrix. The matrix is elaborated by substituting  $v_A$ ,  $v_B$ , and  $v_C$  from (3.3) to get the following expressions.

$$v_{\alpha} = \{\alpha_{A}V_{A} - \alpha_{B}V_{B}\cos(\theta_{b} + \pi/3) - \alpha_{C}V_{C}\cos(\theta_{c} - \pi/3)\}\sin\{\phi_{A}(n)\} -\{\alpha_{B}V_{B}\cos(\theta_{b} - \pi/6) - \alpha_{C}V_{C}\cos(\theta_{c} + \pi/6)\}\cos\{\phi_{A}(n)\}$$

(3.5)