Analytical Modeling of Electrostatic and Transport Phenomena in Inversion-Type InGaAs Nanowire MOSFET

A thesis submitted to the

Department of Electrical and Electronic Engineering (EEE)

of

Bangladesh University of Engineering and Technology (BUET)

In partial fulfillment of the requirement for the degree of

MASTER OF SCIENCE IN ELECTRICAL AND ELECTRONIC ENGINEERING

by I.K.M. Reaz Rahman Roll No : 1017062205 P

Department of Electrical and Electronic Engineering Bangladesh University of Engineering and Technology

February, 2021

## Approval

The thesis titled "Analytical Modeling of Electrostatic and Transport Phenomena in Inversion-Type InGaAs Nanowire MOSFET " submitted by I.K.M. Reaz Rahman, Student No: 1017062205 P, Session: October 2017, has been accepted as satisfactory in partial fulfillment of the requirements for the degree of Master of Science in Electrical and Electronic Engineering on February 10, 2021.

**Board of Examiners**

1.

2.

3.

4.

Dr. Quazi Deen Mohd Khosru Chairman Professor (Supervisor) Department of Electrical and Electronic Engineering Bangladesh University of Engineering and Technology, Dhaka

Dr. Md. Kamrul Hasan Member Professor (Ex-officio) Department of Electrical and Electronic Engineering Bangladesh University of Engineering and Technology, Dhaka

Member

Dr. Md. Kawsar Alam Professor Department of Electrical and Electronic Engineering Bangladesh University of Engineering and Technology, Dhaka

maid

Dr. Md. Zunaid Baten Member Assistant Professor Department of Electrical and Electronic Engineering Bangladesh University of Engineering and Technology, Dhaka

5.

Dr. Jiban Podder Member Professor (External) **Department** of Physics Bangladesh University of Engineering and Technology, Dhaka

## Declaration

It is hereby declared that this thesis or any part of it has not been submitted elsewhere for the award of any degree or diploma.

Signature of the candidate

(I.K.M. Reaz Rahman) Roll No: 1017062205 P

# To my beloved parents

## Acknowledgement

All praise goes to the Almighty for giving me the patience and drive required to complete my M.Sc. research and finish the dissertation in due time. I would like to express my earnest gratitude and heartfelt appreciation to my thesis supervisor Dr. Quazi Deen Mohd Khosru, Professor, Department of Electrical and Electronic Engineering, BUET for his invaluable assistance, guidance and encouragement while pursuing my Master of Science thesis. His constant support was like the "North Star", guiding me in this journey without which it would not have been possible to conceive this endeavor.

I also express my gratitude to Dr. Md. Kamrul Hasan, Head, Department of Electrical and Electronic Engineering (EEE), BUET, for endowing me with a perfect ambiance for continuing my research. My gratitude also extends to EEE department for granting the required tools and guidance for my research.

I would like to thank the members of my thesis committee, Prof. Dr. Md. Kamrul Hasan, Prof. Dr. Md. Kawsar Alam, Dr. Md Zunaid Baten and Prof. Dr. Jiban Poddar for their thoughtful review and constructive suggestion to improve my work.

I want to express my gratitude to Md. Irfan Khan, Lecturer, Department of EEE, BUET, for the insightful prose and discussions in overcoming numerous impasse pertaining to the thesis work.

I would like to thank my parents, Md. Khalilur Rahman and Mrs. Rokshana Khatun. This thesis is dedicated as only a tinge of appreciation towards them. They have helped me in every possible way throughout this journey. This thesis work would not have been possible without their help. I am also indebted to my fiance for her inspiration at difficult times.

Finally I owe my sincere gratitude to all of my teachers, as well as friends, classmates and seniors for their valuable inputs and constant encouragement.

### Abstract

The prime motivation driving the semiconductor industry to fabricate devices of extremely reduced dimension is the innovation of novel technologies that enable manufacturers to create transistors in the sub 22-nm node, where short-channel effects (SCE) become a barrier for silicon technology in planar field effect transistors. Researchers are now moving to multi-gate structure that offer enhanced gate control over short channel effects to the highest degree. Particularly, gate-all-around (GAA) nanowire transistor have shown tremendous success in terms of improved electrostatic control but at the expense of mobility degradation at the surface due to oxide charges present at the oxide-semiconductor interface. Integration of III-V materials in the channel instead of silicon provides a viable solution for this dilemma, the bottleneck being the availability of a suitable native oxide unlike  $SiO_2$  on silicon. Previous reports on InGaAs nanowire MOSFETs include electrostatic characterization and transport modeling in uncoupled mode space (UMS) approach both of which rely on quantum mechanical simulation that is computationally expensive. This work presents an analytical investigation of the electrostatic and drain current model for symmetric short channel InGaAs gate-all-around MOSFET valid from depletion to strong inversion using a continuous expression. The development of the core model is facilitated by the solution of quasi 2-D Poisson equation in the doped channel, accounting for interface trap defects and fixed oxide charges. Correction to short channel effects such as threshold voltage roll-off, drain induced barrier lowering and subthreshold slope degradation are later introduced, complemented with channel length modulation, velocity saturation and mobility degradation from surface roughness, leading to an accurate mobile charge density for electrostatic capacitance-voltage and transport characterization. A threshold voltage model is presented for long channel gate-all-around device that utilizes the well-known double derivative method, which is crucial for determining threshold voltage roll-off with scaling of transistors. The effect of physical process parameters like fin width, oxide thickness and channel length scaling are thoroughly investigated in both on and off state of the transistor. The robustness of the model is reflected from the precise match with published experimental reports in the literature. An  $R_{\rm on}$  of 1160  $\Omega.\mu m$  is obtained from output characteristics and switching efficiency (ratio of maximum transconductance to subthreshold slope) improvement of 2.5 times is estimated from incorporating high- $\kappa$  dielectric into the GAA transistor. Numerical 3-D simulations from TCAD corroborates the validity of the proposed model in all regions of operation.

## Contents

| $\mathbf{A}$ | ppro  | val     |                                        |   |     | ii           |

|--------------|-------|---------|----------------------------------------|---|-----|--------------|

| Declaration  |       |         |                                        |   | iii |              |

| A            | cknov | wledge  | ment                                   |   |     | $\mathbf{v}$ |

| A            | bstra | nct     |                                        |   |     | vii          |

| C            | onter | nts     |                                        |   | ,   | viii         |

| Fi           | igure | s       |                                        |   |     | x            |

| Ta           | ables |         |                                        |   | :   | xvi          |

| 1            | Intr  | roducti | ion                                    |   |     | 1            |

|              | 1.1   | Motiva  | ation                                  |   |     | 1            |

|              | 1.2   | A Hist  | torical Perspective: Literature Review |   |     | 7            |

|              | 1.3   | Contri  | bution of the Thesis                   |   |     | 18           |

|              | 1.4   | Object  | tive of the Thesis                     |   |     | 20           |

|              | 1.5   | Organ   | ization of the Thesis                  | • |     | 22           |

| <b>2</b>     | Eleo  | ctrosta | tic Model Development                  |   |     | <b>24</b>    |

|              | 2.1   | Basic   | Device Structure                       |   |     | 25           |

|              | 2.2   | Charg   | e Modeling                             |   |     | 27           |

|              |       | 2.2.1   | Energy Band Diagram                    |   |     | 28           |

|              |       | 2.2.2   | Surface Potential and Mobile Charge    |   |     | 30           |

|              |       | 2.2.3   | Capacitance-Voltage Characteristics    |   |     | 37           |

|              | 2.3   | Thres   | hold Voltage Development               |   |     | 38           |

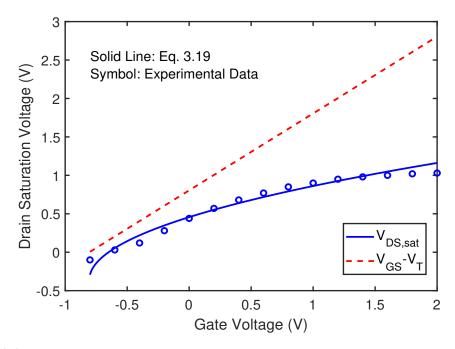

| 3                         | Tra                  | nsport Model Development                                                      | 40 |

|---------------------------|----------------------|-------------------------------------------------------------------------------|----|

|                           | 3.1                  | Short Channel Effect Correction                                               | 41 |

|                           | 3.2                  | Velocity Saturation                                                           | 44 |

|                           | 3.3                  | Mobility Degradation                                                          | 46 |

|                           | 3.4                  | Channel Length Modulation                                                     | 47 |

|                           | 3.5                  | Parasitic Resistance                                                          | 47 |

| 4                         | Sim                  | ulation Model Development                                                     | 49 |

|                           | 4.1                  | Sentaurus Device                                                              | 49 |

|                           | 4.2                  | Structure Creation                                                            | 50 |

|                           |                      | 4.2.1 Mesh Generation                                                         | 55 |

|                           |                      | 4.2.2 Simulation Flow                                                         | 56 |

|                           | 4.3                  | Script for SDevice                                                            | 57 |

|                           |                      | 4.3.1 The File Section                                                        | 58 |

|                           |                      | 4.3.2 The Electrode Section                                                   | 59 |

|                           |                      | 4.3.3 The Physics Section                                                     | 59 |

|                           |                      | 4.3.4 The Plot Section                                                        | 62 |

|                           |                      | 4.3.5 The Math Section                                                        | 62 |

|                           |                      | 4.3.6 The Solve Section                                                       | 64 |

| <b>5</b>                  | $\operatorname{Res}$ | ults and Discussions                                                          | 65 |

| 6                         | Con                  | clusion                                                                       | 85 |

|                           | 6.1                  | Summary                                                                       | 85 |

|                           | 6.2                  | Suggestions for Future Work                                                   | 86 |

| $\mathbf{A}_{\mathbf{j}}$ | ppen                 | dices                                                                         | 87 |

| $\mathbf{A}$              | Diff                 | erence of potential                                                           | 88 |

|                           | A.1                  | Difference of potential in deep subthreshold                                  | 88 |

|                           | A.2                  | Difference of surface-center potential in terms of Lambert function $\ . \ .$ | 89 |

|                           | A.3                  | Characteristic natural length of a symmetric GAA MOSFET $\ . \ . \ .$         | 90 |

| Bi                        | bliog                | raphy                                                                         | 92 |

## List of Figures

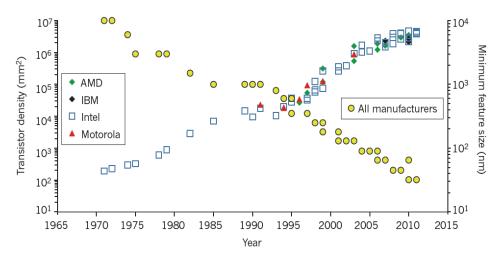

1.1 The evolution of transistor gate length (minimum feature size) and the density of transistors in microprocessor over time. Between 1970 and 2011, the gate length of the MOSFETs shrank from  $10\mu$ m to 28nm (yellow circles; y axis, right), and the number of transistors per square millimeter increased from 200 to over 1 million (diamonds, triangles and squares show data for the four main microprocessor manufacturers; y axis, left). AMD, Advanced Micro Devices; IBM, International Business Machines. [3] ....

2

4

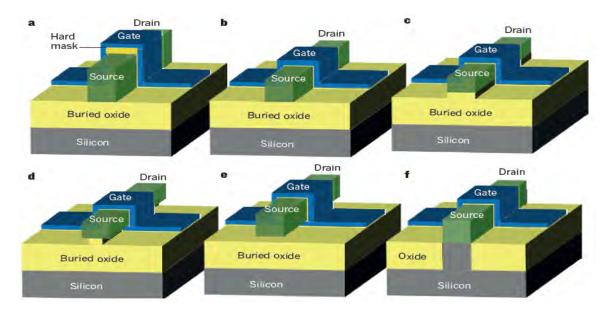

- 1.2 Types of multigate MOSFET. The different ways in which the gate electrode can be wrapped around the channel region of a transistor are shown. (a) A silicon-on-insulator (SOI) fin field-effect transistor (FinFET). Gate control is exerted on the channel from the lateral sides of the device. (b) SOI triple-gate (or tri-gate) MOSFET. Gate control is exerted on the channel from three sides of the device (the top, as well as the left and right sides). (c) SOI  $\pi$ -gate MOSFET. (d) SOI  $\Omega$ -gate MOSFET. Gate control of the bottom of the channel region is better than in the SOI  $\pi$ -gate MOSFET. (e) SOI gate-all-around MOSFET. Gate control is exerted on the channel from all four sides of the device. (f) A bulk tri-gate MOSFET. In this case, there is no buried oxide underneath the device. [3]

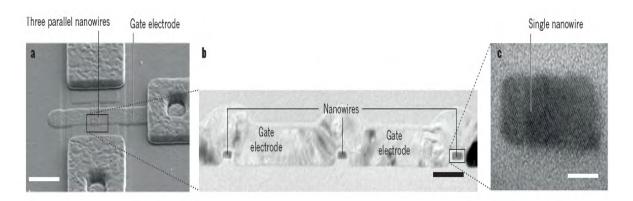

| 1.4 | A multi fingered (three-finger) nanowire transistor. (a) Scanning                                         |    |

|-----|-----------------------------------------------------------------------------------------------------------|----|

|     | electron microscopy image of a device with three parallel nanowires that have                             |    |

|     | a common gate electrode. Scale bar, $5\mu \mathrm{m.}$ (b) Transmission electron mi-                      |    |

|     | croscopy image of the three nanowires. Scale bar, 50 nm. (c) High resolution                              |    |

|     | transmission electron microscopy image of a nanowire. Scale bar, 5 nm. $\left[3\right]$ .                 | 10 |

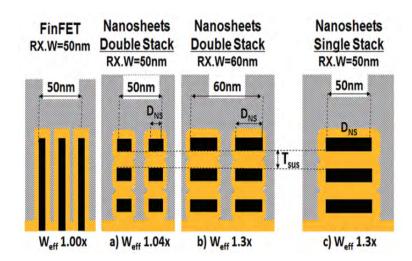

| 1.5 | Various configuration of nanosheet stacking. (a) Nanosheet double                                         |    |

|     | stack, W <sub>eff</sub> =1.04x (b) Nanosheet double stack, W <sub>eff</sub> =1.3x (c) [47]                | 10 |

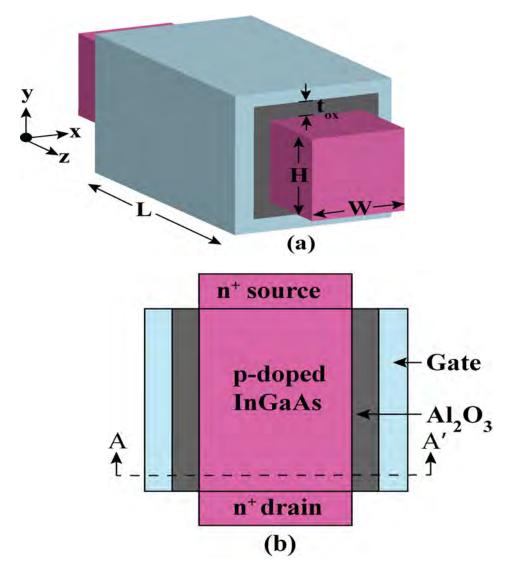

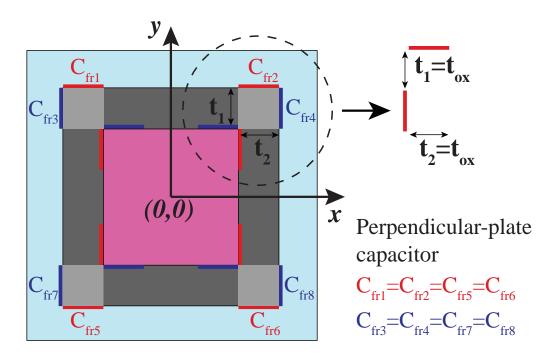

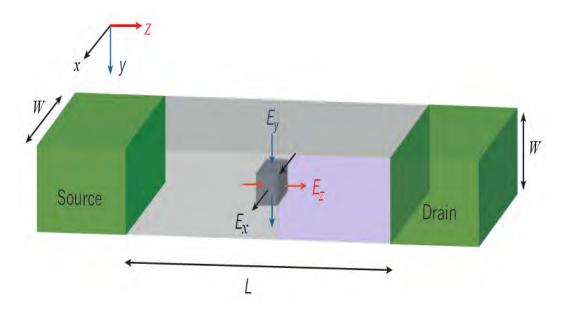

| 2.1 | Schematic view of a GAA MOSFET. The source/drain is heavily doped                                         |    |

|     | for ohmic contacts and the $In_{0.53}Ga_{0.47}As$ channel is p-doped. (a) Perspective                     |    |

|     | view. (b) Lateral view                                                                                    | 27 |

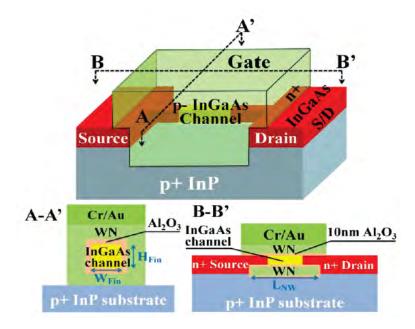

| 2.2 | Schematic view of an inversion mode GAA n-channel $In_{0.53}Ga_{0.47}As$                                  |    |

|     | $(2 \times 10^{16}/\mathrm{cm^{-3}})$ MOSFET with ALD 10nm Al <sub>2</sub> O <sub>3</sub> /20nm WN gate   |    |

|     | stack. A heavily doped wide bandgap InP lies underneather the bottom                                      |    |

|     | gate. [60]                                                                                                | 28 |

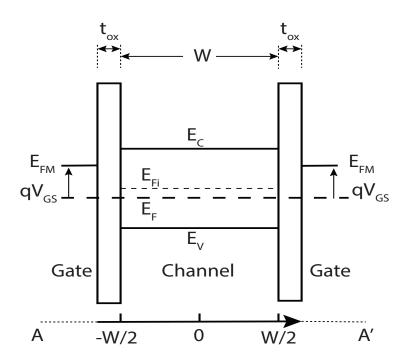

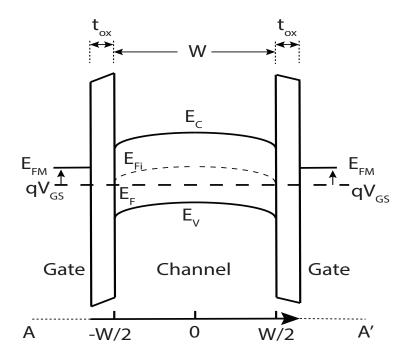

| 2.3 | Energy band diagram of a GAA MOSFET having p-doped channel                                                |    |

|     | in Flat band condition. The channel width is $W$ , oxide thickness $t_{ox}$ . $E_{\rm F}$ ,               |    |

|     | $E_{\rm Fi}$ and $E_{\rm Fm}$ are the Fermi level of the p-doped channel, intrinsic Fermi level           |    |

|     | and work function of the gate metal                                                                       | 29 |

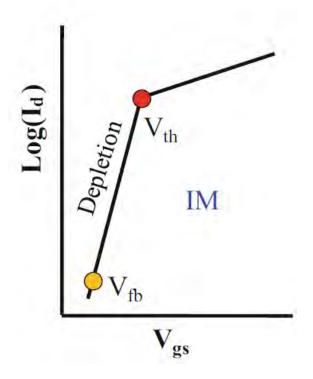

| 2.4 | Drain current as the function of $V_{\rm g}$ in an inversion-mode device. [109]                           | 31 |

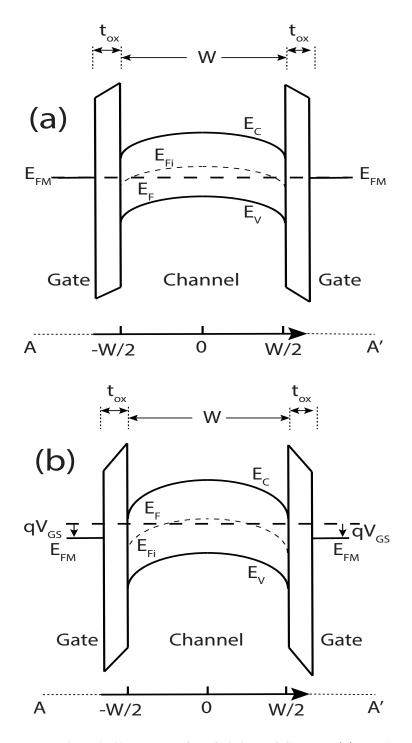

| 2.5 | Energy band diagram of a GAA MOSFET having p-doped channel                                                |    |

|     | <b>near threshold condition.</b> The channel width is $W$ , oxide thickness $t_{ox}$ .                    |    |

|     | $E_{\rm F},E_{\rm Fi}$ and $E_{\rm Fm}$ are the Fermi level of the p-doped channel, intrinsic Fermi       |    |

|     | level and work function of the gate metal                                                                 | 31 |

| 2.6 | <b>Energy band diagram of a GAA MOSFET.</b> (a) In thermal equilibrium.                                   |    |

|     | (b) At strong inversion. The mismatch in the gate Fermi level and that of                                 |    |

|     | the semiconductor results due to application of a large gate bias. $\ldots$ .                             | 32 |

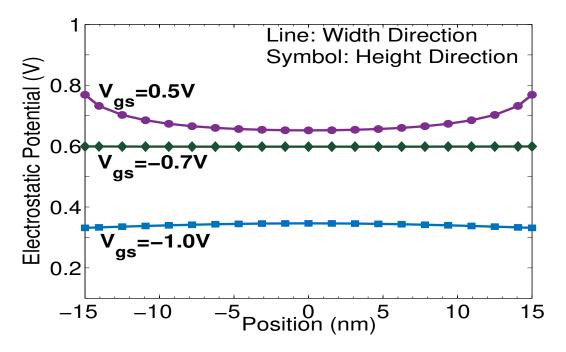

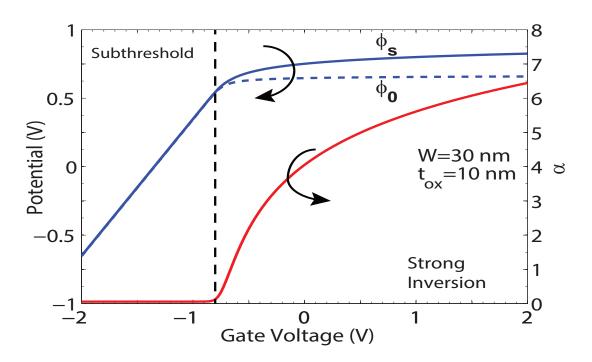

| 2.7 | Variation of electrostatic potential along width and height direc-                                        |    |

|     | tion at different gate voltages covering from subthreshold to strong                                      |    |

|     | <b>inversion.</b> The symmetry of the gradient of the electrostatic potential from                        |    |

|     | center to surface verifies the assumption $\frac{d\phi}{dx} = \frac{d\phi}{dy}$ made to simplify Equation |    |

|     | $(2.2)  \dots  \dots  \dots  \dots  \dots  \dots  \dots  \dots  \dots  $                                  | 34 |

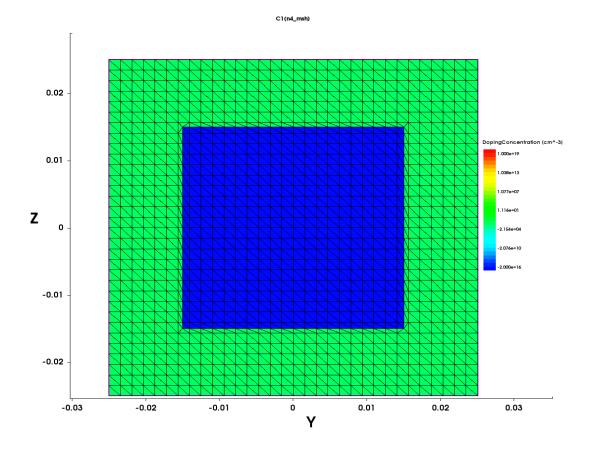

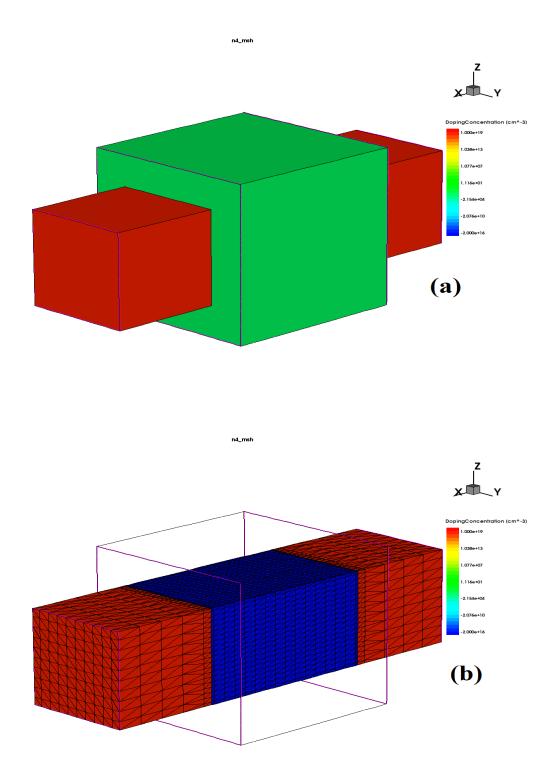

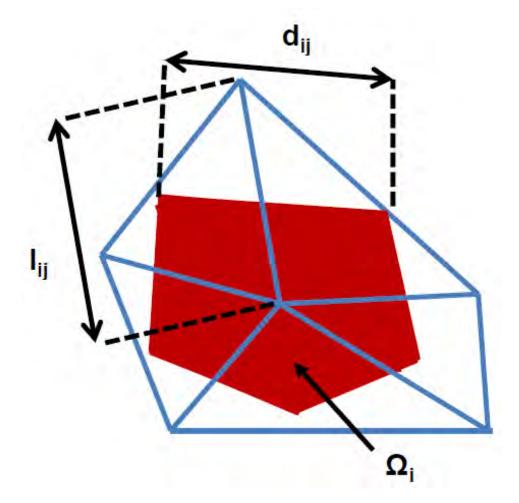

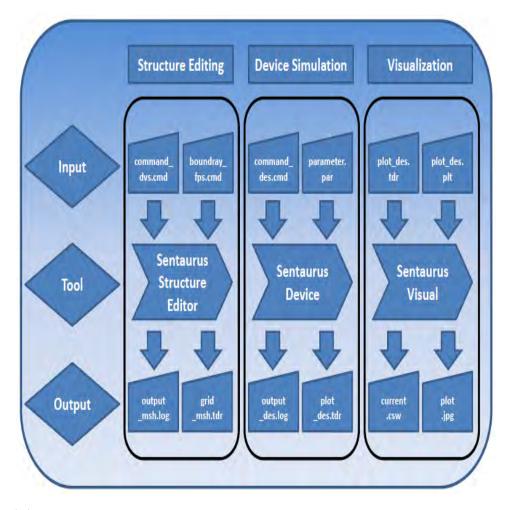

- 4.2 Completed structure of the GAA MOSFET created in Sentaurus Device Editor. (a) Schematic showing source/drain region with the wrap-around gate. (b) Schematic without the wrap-around gate, revealing the doping profile and mesh throughout the entire channel. It can be seen that dense mesh are formed near the oxide-semiconductor interface and near source/drain region to realize important physical effects in the active channel. 54

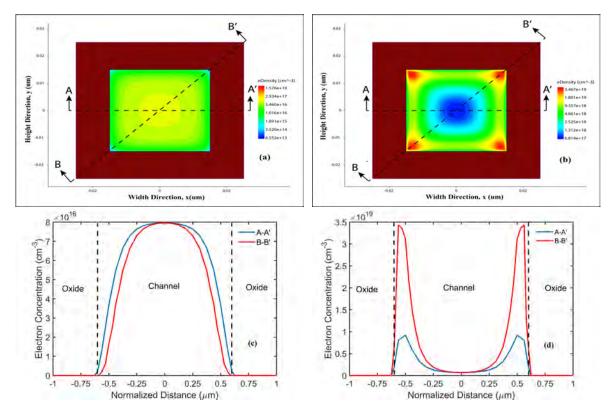

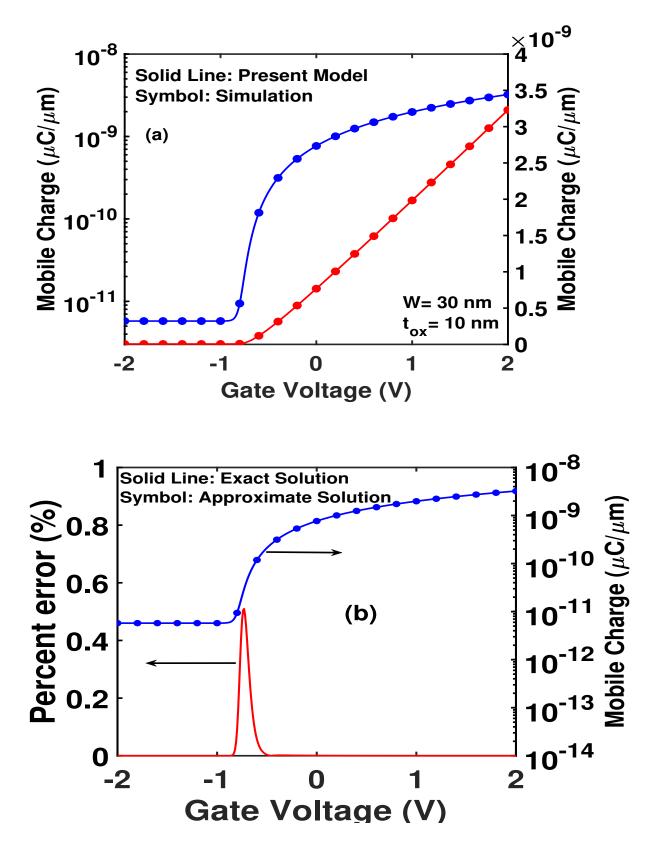

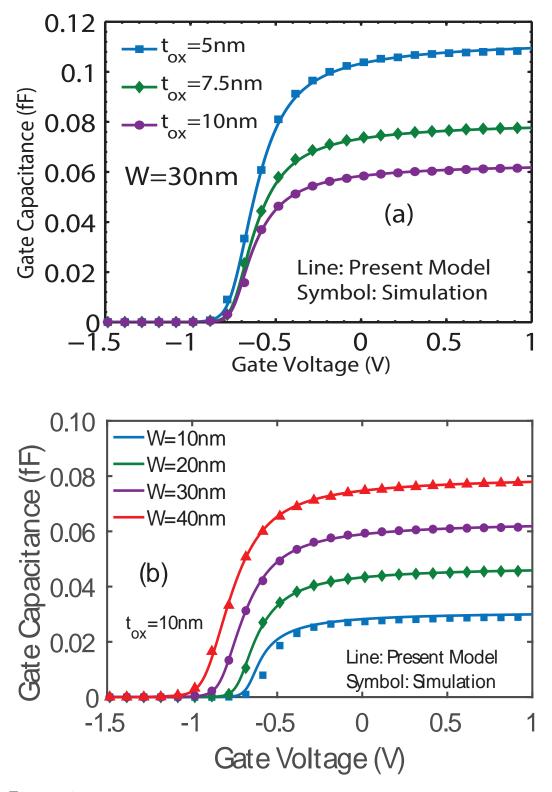

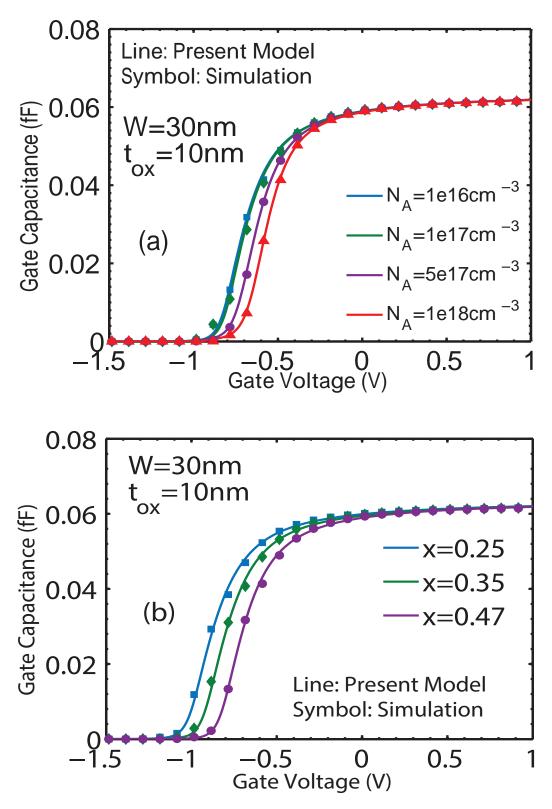

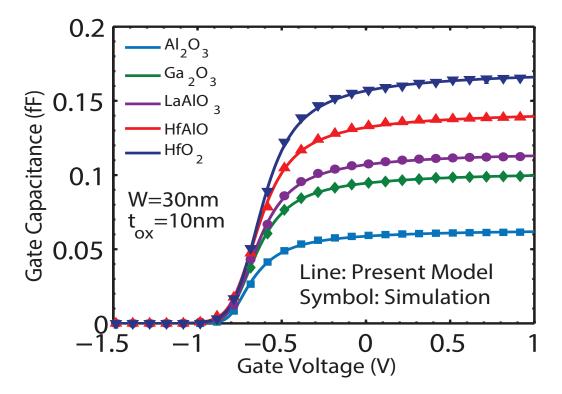

- Illustration of a 2D triangular mesh over a control area W (red) 4.3574.4Typical simulation flow diagram of Sentaurus Device, starting from the structure editing, device simulation and visualization of the 584.5Spatial carrier density of electrons taken at cross-section of the GAA MOSFET at mid-channel. (a) At low gate bias near threshold region. (b) At high gate bias in strong inversion regime. (c-d) The corresponding electron density along cutlines A-A' from gate-to-gate direction and along B-B' direction diagonally. The corner effect at strong gate bias in the GAA geometry is evident from (b) and (d), showing that TCAD simulation is successful in accounting for this effect. 63 5.1Mobile charge density as a function of gate bias for a GAA MOS-**FET at**  $N_{\rm A} = 2 \times 10^{16} \, cm^{-3}$ . (a) Comparison between model and simulated charge density in both linear and log scale at low  $V_{DS}$ . (b) Error in charge density from using (2.18) instead of Lambert function. Largest error occurs 66 near threshold region. Capacitance-voltage characteristics of a GAA nanowire MOSFET 5.2with  $N_{\rm A} = 2 \times 10^{16} \, {\rm cm}^{-3}$ . (a) For various oxide thickness. (b) For various fin width. The fin width has greater impact on C - V characteristics in comparison to oxide thickness which is reflected by a shift in threshold voltage.

- The impact of quantum effect on CV profile is seen for a fin width of 10nm where simulation results reflect a rightward shift in CV arising from threshold voltage shift in subthreshold region and gate capacitance degradation in strong inversion region.

67

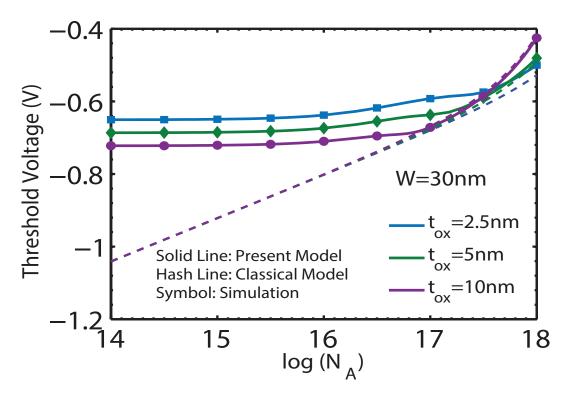

| 5.4  | Threshold voltage dependence on channel doping for different oxide                                                                                                                                                                                                                                                                                                                                                                   |    |

|------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

|      | thickness. The classical threshold voltage model based on critical band                                                                                                                                                                                                                                                                                                                                                              |    |

|      | bending in strong inversion deviates from the predicted result for lightly doped                                                                                                                                                                                                                                                                                                                                                     |    |

|      | transistor                                                                                                                                                                                                                                                                                                                                                                                                                           | 70 |

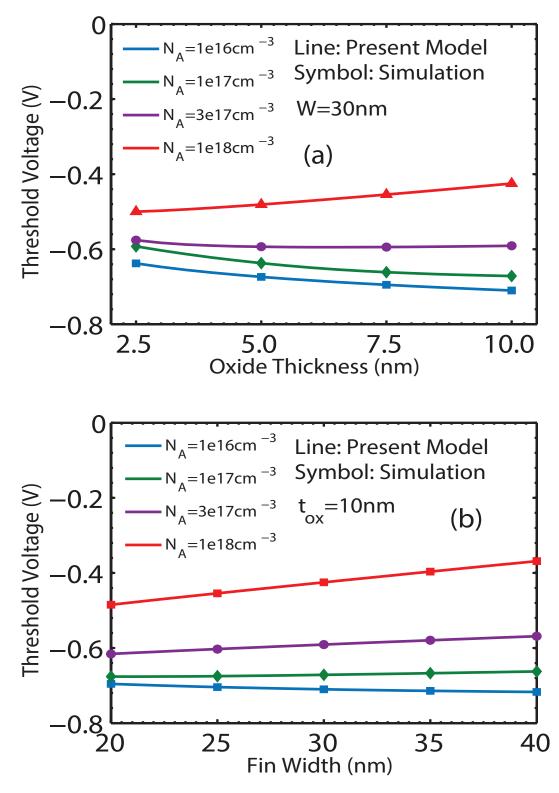

| 5.5  | Non-monotonic dependence of threshold voltage on: (a) $t_{ox}$ for various                                                                                                                                                                                                                                                                                                                                                           |    |

|      | channel doping. (b) fin width for various channel doping. $\ldots$ $\ldots$ $\ldots$                                                                                                                                                                                                                                                                                                                                                 | 71 |

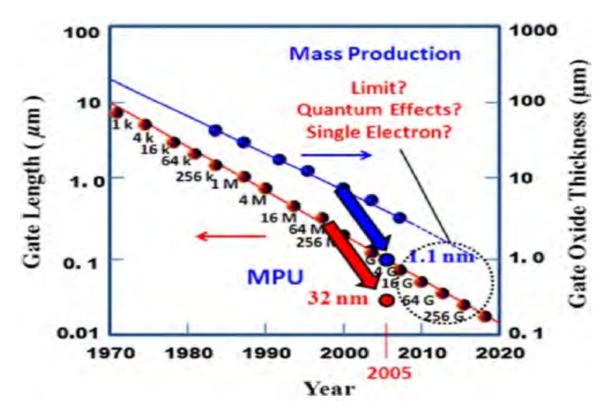

| 5.6  | The trend of MOSFET scaling from ITRS. Picture taken from ITRS                                                                                                                                                                                                                                                                                                                                                                       |    |

|      | Corp. [136]                                                                                                                                                                                                                                                                                                                                                                                                                          | 72 |

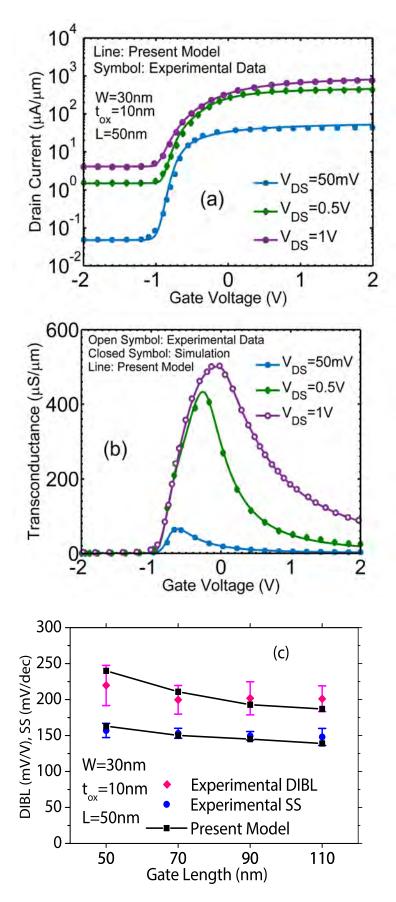

| 5.7  | Transfer characteristics of a 50nm GAA MOSFET. (a) Drain current                                                                                                                                                                                                                                                                                                                                                                     |    |

|      | as a function of gate voltage. (b) Extrinsic transconductance. (c) DIBL and                                                                                                                                                                                                                                                                                                                                                          |    |

|      | subthreshold slope extracted from the $I_D$ - $V_G$ plot. Experimental data has                                                                                                                                                                                                                                                                                                                                                      |    |

|      | been extracted from [60]                                                                                                                                                                                                                                                                                                                                                                                                             | 74 |

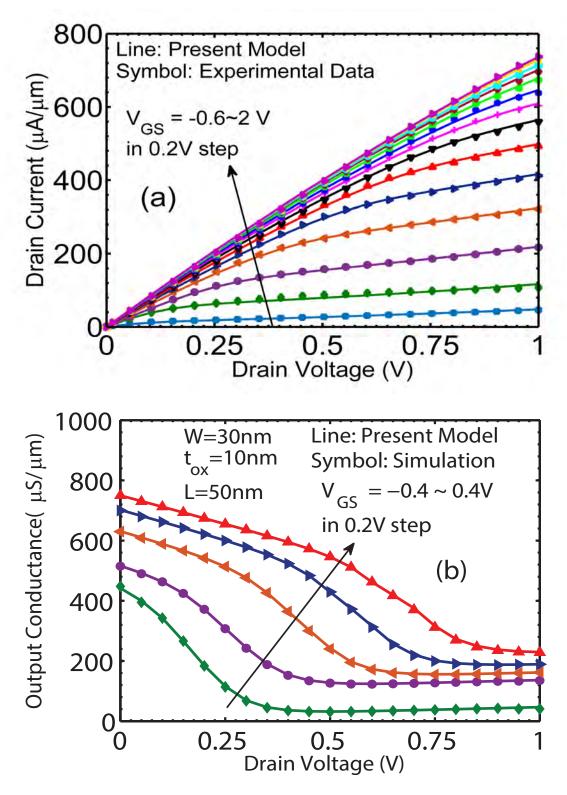

| 5.8  | (a) Output characteristics of a 50nm GAA MOSFET. An $\rm R_{on}$ of 1160 $\Omega\cdot\mu\rm m$                                                                                                                                                                                                                                                                                                                                       |    |

|      | is obtained from the slope at $V_{\rm GS}~=~2V$ (b) Output conductance of the                                                                                                                                                                                                                                                                                                                                                        |    |

|      | same device, showing that drain current remains continuous from linear to                                                                                                                                                                                                                                                                                                                                                            |    |

|      | saturation region. Experimental data has been extracted from [60]                                                                                                                                                                                                                                                                                                                                                                    | 75 |

|      |                                                                                                                                                                                                                                                                                                                                                                                                                                      |    |

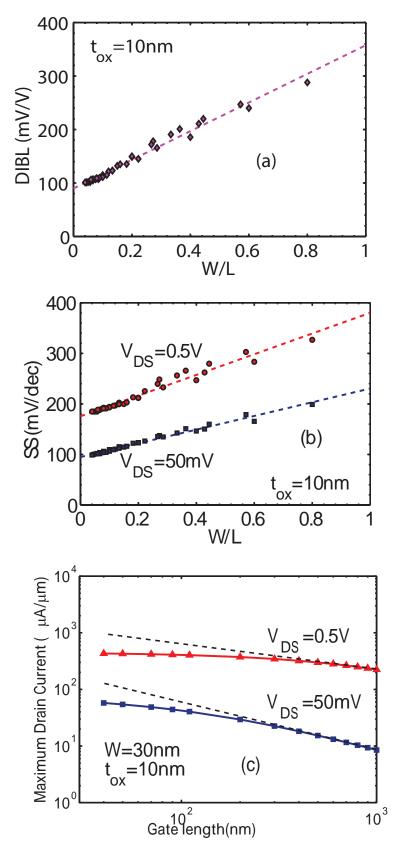

| 5.9  | On-state and off-state characteristics of an InGaAs GAA transistor.                                                                                                                                                                                                                                                                                                                                                                  |    |

| 5.9  | On-state and off-state characteristics of an InGaAs GAA transistor.<br>Variation of (a) DIBL (b) SS with W/L ratio. Best fit straight lines are also                                                                                                                                                                                                                                                                                 |    |

| 5.9  |                                                                                                                                                                                                                                                                                                                                                                                                                                      |    |

| 5.9  | Variation of (a) DIBL (b) SS with W/L ratio. Best fit straight lines are also                                                                                                                                                                                                                                                                                                                                                        |    |

| 5.9  | Variation of (a) DIBL (b) SS with W/L ratio. Best fit straight lines are also<br>plotted based on least square regression to highlight proportional relation                                                                                                                                                                                                                                                                         |    |

| 5.9  | Variation of (a) DIBL (b) SS with W/L ratio. Best fit straight lines are also<br>plotted based on least square regression to highlight proportional relation<br>with W/L. (c) Maximum ON-current as a function of gate length obtained                                                                                                                                                                                               |    |

| 5.9  | Variation of (a) DIBL (b) SS with W/L ratio. Best fit straight lines are also<br>plotted based on least square regression to highlight proportional relation<br>with W/L. (c) Maximum ON-current as a function of gate length obtained<br>at $V_{\rm GS} = 2V$ and different drain bias. For comparison, the dotted line shows                                                                                                       | 76 |

|      | Variation of (a) DIBL (b) SS with W/L ratio. Best fit straight lines are also<br>plotted based on least square regression to highlight proportional relation<br>with W/L. (c) Maximum ON-current as a function of gate length obtained<br>at $V_{\rm GS} = 2V$ and different drain bias. For comparison, the dotted line shows<br>when the drain current starts to saturate due to non-ideal effects in the short                    | 76 |

|      | Variation of (a) DIBL (b) SS with W/L ratio. Best fit straight lines are also<br>plotted based on least square regression to highlight proportional relation<br>with W/L. (c) Maximum ON-current as a function of gate length obtained<br>at $V_{\rm GS} = 2V$ and different drain bias. For comparison, the dotted line shows<br>when the drain current starts to saturate due to non-ideal effects in the short<br>channel MOSFET. | 76 |

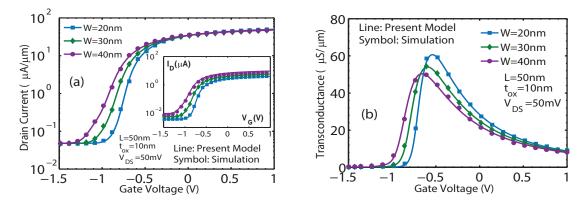

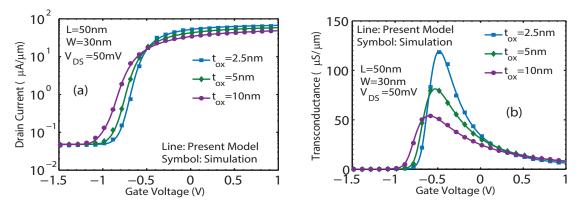

|      | Variation of (a) DIBL (b) SS with W/L ratio. Best fit straight lines are also<br>plotted based on least square regression to highlight proportional relation<br>with W/L. (c) Maximum ON-current as a function of gate length obtained<br>at $V_{\rm GS} = 2V$ and different drain bias. For comparison, the dotted line shows<br>when the drain current starts to saturate due to non-ideal effects in the short<br>channel MOSFET  | 76 |

|      | Variation of (a) DIBL (b) SS with W/L ratio. Best fit straight lines are also<br>plotted based on least square regression to highlight proportional relation<br>with W/L. (c) Maximum ON-current as a function of gate length obtained<br>at $V_{\rm GS} = 2V$ and different drain bias. For comparison, the dotted line shows<br>when the drain current starts to saturate due to non-ideal effects in the short<br>channel MOSFET  | 76 |

|      | Variation of (a) DIBL (b) SS with W/L ratio. Best fit straight lines are also<br>plotted based on least square regression to highlight proportional relation<br>with W/L. (c) Maximum ON-current as a function of gate length obtained<br>at $V_{\rm GS} = 2V$ and different drain bias. For comparison, the dotted line shows<br>when the drain current starts to saturate due to non-ideal effects in the short<br>channel MOSFET  |    |

| 5.10 | Variation of (a) DIBL (b) SS with W/L ratio. Best fit straight lines are also<br>plotted based on least square regression to highlight proportional relation<br>with W/L. (c) Maximum ON-current as a function of gate length obtained<br>at $V_{\rm GS} = 2V$ and different drain bias. For comparison, the dotted line shows<br>when the drain current starts to saturate due to non-ideal effects in the short<br>channel MOSFET  |    |

| 5.10 | Variation of (a) DIBL (b) SS with W/L ratio. Best fit straight lines are also<br>plotted based on least square regression to highlight proportional relation<br>with W/L. (c) Maximum ON-current as a function of gate length obtained<br>at $V_{\rm GS} = 2V$ and different drain bias. For comparison, the dotted line shows<br>when the drain current starts to saturate due to non-ideal effects in the short<br>channel MOSFET  |    |

| 5.10 | Variation of (a) DIBL (b) SS with W/L ratio. Best fit straight lines are also<br>plotted based on least square regression to highlight proportional relation<br>with W/L. (c) Maximum ON-current as a function of gate length obtained<br>at $V_{\rm GS} = 2V$ and different drain bias. For comparison, the dotted line shows<br>when the drain current starts to saturate due to non-ideal effects in the short<br>channel MOSFET  |    |

| 5.12 | (a) Threshold voltage roll-off (b) Drain induced barrier lowering and (c) Sub-                      |    |

|------|-----------------------------------------------------------------------------------------------------|----|

|      | threshold slope degradation due to gate length scaling at various fin width.                        |    |

|      | (d) Threshold voltage roll-off (e) Drain induced barrier lowering and (f) Sub-                      |    |

|      | threshold slope degradation due to gate length scaling at various oxide thick-                      |    |

|      | ness. The subthreshold properties are affected to greater extent due to fin                         |    |

|      | width variation.                                                                                    | 79 |

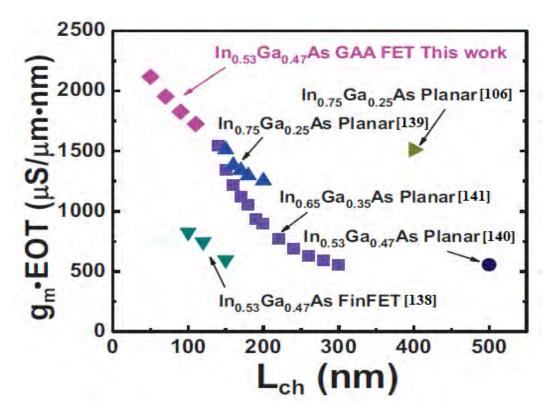

| 5.13 | Benchmarking $\mathrm{g}_{\mathrm{m}}{\cdot}\mathbf{EOT}$ of contemporary planar and non-planar In- |    |

|      | GaAs surface-channel MOSFETs. [60]                                                                  | 80 |

| 5.14 | Capacitance-voltage profile for different gate dielectric.                                          | 81 |

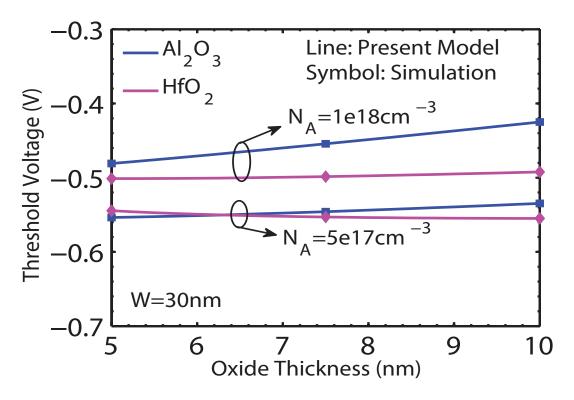

| 5.15 | Impact of high- $\kappa$ dielectric on threshold voltage of heavily doped                           |    |

|      | GAA transistor.                                                                                     | 82 |

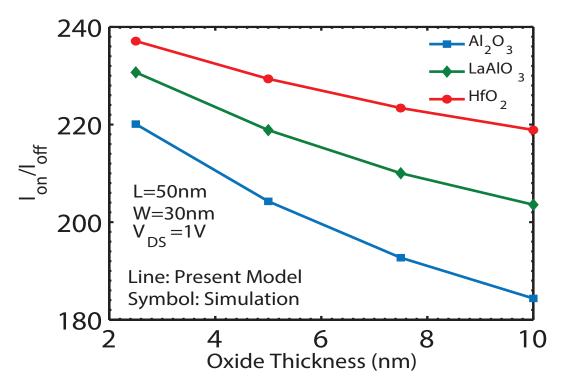

| 5.16 | $I_{\rm on}/I_{\rm off}$ ratio as a function of oxide thickness for various gate dielec-            |    |

|      | tric. $I_{\rm on(off)}$ is defined as the drain current at maximum (minimum) $V_{\rm GS}$ and       |    |

|      | high drain bias. The high drain junction leakage current of InGaAs GAA                              |    |

|      | MOSFETs result in a small on-off ratio                                                              | 83 |

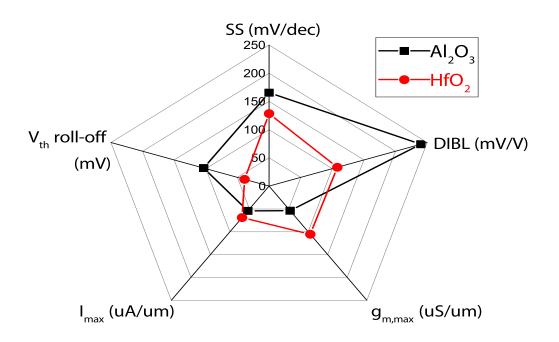

| 5.17 | Radar plot presenting a quantitative analysis between $Al_2O_3$ and                                 |    |

|      | $HfO_2$ as gate dielectric in 50nm InGaAs GAA MOSFET having                                         |    |

|      | fin width 30nm and $t_{ox}$ 10nm at $V_{\rm DS}$ = 50mV. A switching figure of                      |    |

|      | merit of 0.82 $(\mu S/\mu m)/(mV/dec)$ is obtained from using HfO <sub>2</sub> , resulting in       |    |

|      | an improvement of 2.5 times over using $Al_2O_3$                                                    | 84 |

|      |                                                                                                     |    |

# List of Tables

| 3.1 | Relevant parameters used in the transport model                          | 48 |

|-----|--------------------------------------------------------------------------|----|

| 4.1 | Box method coefficients for 1,2 and 3-D discretization.                  | 56 |

| 4.2 | Numerical approximation of the coupled differential equations, solved in |    |

|     | each vertex of the mesh                                                  | 56 |

| 5.1 | Process/device parameters used in this work                              | 70 |

## Chapter 1

### Introduction

This chapter expands on the motivation to search for alternative channel material in non-planar multi-gate device structure, mainly to overcome the limitations posed by single gate and double-gate transistor and how the industry has shifted to the adoption of gate-all-around (GAA) geometry from FinFET architecture in a seamless fashion, with an aim to perpetuate Moore's Law that has so long driven the semiconductor industry towards scaling of nanoscale Metal Oxide Semiconductor Field Effect Transistor (MOSFET). In addition, a brief overview of the experimental demonstrations realized for GAA transistors along with a rigorous study of the extant analytical models will be presented. Finally the object and outline of the thesis will be covered.

#### 1.1 Motivation

Scaling of MOSFET has continued over the past several decades without any major change in the basic planar structure. One of the many reasons for the predilection of the semiconductor industry towards a miniaturized MOSFET is the possibility of packing more transistors into a given area with smaller feature size. The apparent benefit is an improvement in the functionality of the chip with enormous cost-saving in manufacturing. In 1965, Gordon Moore made a famous prediction that the density of transistors on a chip would double every 18 months [1]. Despite the empirical nature of this prediction and the basis being only on six years' data, the law has upheld remarkably well in the past 50 years (Figure 1.1). In addendum, smaller transistor means faster switching speed resulting from the proportional down scaling of all the device

Figure 1.1: The evolution of transistor gate length (minimum feature size) and the density of transistors in microprocessor over time. Between 1970 and 2011, the gate length of the MOSFETs shrank from  $10\mu$ m to 28nm (yellow circles; y axis, right), and the number of transistors per square millimeter increased from 200 to over 1 million (diamonds, triangles and squares show data for the four main microprocessor manufacturers; y axis, left). AMD, Advanced Micro Devices; IBM, International Business Machines. [3]

dimensions. Doubling the density of transistors on a chip is equivalent to reducing the chip's linear dimensions, such as length and width, by a scaling factor of  $\sqrt{2}$ . Let this scaling factor be represented by 'l'. In 1974 Dennard *et al.* demonstrated the benefits of scaling in his seminal paper [2], where he showed that for a constant electric field inside the transistor, scaling the device by a factor of l increases the switching speed by l, reduces the power dissipation by  $l^2$  and improves the power-delay product by  $l^3$ . The gate capacitance is reduced, leading to minimum RC delay, thereby contributing to the enhance device switching speed. It is noteworthy to mention that Dennard's scaling law implies a reduction in the supply voltage and threshold voltage by 'l', although the latter has not been achieved due to the lack of feasibility in achieving a subthreshold slope value of less than 59.6 mV/decade in conventional MOSFETs.

The halcyon of the booming semiconductor industry was thwarted by the many challenges of simple down scaling in recent times. Dennard's scaling law was followed by the semiconductor industry until approximately 2005 when performance improvement due to scaling reached a saturation. Firstly, as MOSFET dimensions are shrunk, the designed gate voltage should also be smaller to maintain device reliability. In order to maintain performance, the threshold voltage must also decrease. This creates a bottleneck with the limitation of the device to turn off completely, making subthreshold conduction non-negligible in scaled devices. The down scaled MOSFET has thinner gate oxide layer which increases gate leakage, the sole factor with major contribution to static power dissipation and degraded reliability of logic and memory devices. Moreover, as gate length scaling reaches sub-nanometer domain, the source/drain junction depletion width becomes comparable to the short channel length, giving rise to new challenges known as short channel effect (SCE). The induced SCE results into device threshold voltage roll-off and increased junction leakage [4,5]. As can be seen in Figure 1.1, the gate length of microprocessors in the current timeline is close to 25 nm. In practice, accounting for the reduced distance between the source and drain in comparison to gate electrode yields an effective channel length of only 15 nm. It goes without saying that SCE will be more prominent in ultra-scaled devices.

To ameliorate some of these issues, researchers are exploring the prospect of high-  $\kappa$  dielectric to maintain the dielectric physical thickness while scaling down effective thickness, suppressing the static leakage current through the gate terminal due to quantum mechanical tunneling [6]. Hafnium oxide and lanthanum lutetium oxide have dielectric constants higher than that of silicon dioxide [7]. The use of these high- $\kappa$  dielectric results in improved control of the channel by the gate voltage and thus reduces SCEs.

Channel doping engineering is another viable solution to counteract SCE in the prevailing technological impasse. However, there is little room for further down scaling on planar geometry even with these new device design techniques.

The effort to maintain device down scaling trend needs some novel solution based on alteration of the device structure. In a bulk planar MOSFET, the gate electrode is positioned on top of an insulator to cover the active channel region between the source and drain. In such a configuration, the gate achieves electrostatic control of the channel region by capacitive coupling through gate insulator. The electrostatics of a long channel MOSFET are essentially one dimensional. The physics of the elementary device is governed by solving one-dimensional Poisson equation vertically from the gate towards the substrate direction. Short channel effects, where electric fields from the source to

Figure 1.2: **Types of multigate MOSFET.** The different ways in which the gate electrode can be wrapped around the channel region of a transistor are shown. (a) A silicon-oninsulator (SOI) fin field-effect transistor (FinFET). Gate control is exerted on the channel from the lateral sides of the device. (b) SOI triple-gate (or tri-gate) MOSFET. Gate control is exerted on the channel from three sides of the device (the top, as well as the left and right sides). (c) SOI  $\pi$ -gate MOSFET. (d) SOI  $\Omega$ -gate MOSFET. Gate control of the bottom of the channel region is better than in the SOI  $\pi$ -gate MOSFET. (e) SOI gate-all-around MOSFET. Gate control is exerted on the channel from all four sides of the device. (f) A bulk tri-gate MOSFET. In this case, there is no buried oxide underneath the device. [3]

the drain encroach laterally into the channel region adds a second dimension to this problem. Multi-gate transistors take the advantage of the third dimension to counteract the SCE. Figure 1.2 shows some of the advanced multigate architectures namely fin field-effect transistors (FinFETs), triple-gate (tri-gate) MOSFETs, gate-all-around (GAA) MOSFETs (in which the gate electrode wraps around the entire periphery of the channel region) and the  $\pi$ -gate and  $\Omega$ -gate structures (which are so named because of the shape of their gate electrodes [8,9]).

Multi-gate devices are lucrative for their ability to harness large on-state current in addition to better gate controllability. The improved gain and lower output resistance is desirable for circuit designers. With the ability to extend effective channel width into the third dimension, device miniaturization has been continued by shrinking the footprint on chip area. As the most promising multi-gate MOSFET, the FinFET has been in production by Intel since 2012 [10]. The GAA FET has a similar structure as the FinFET, but the gate material extends to surround the channel on all four sides. The GAA MOSFET is the ultimate successor, designed to eliminate SCE to the greatest extent. The GAA FET is expected to dominate the next generation nano-device industry [11–16].

The GAA FET has been successfully implemented based on the extant silicon nanowire technology. However, one of the central pitfalls of silicon-based MOSFETs is the increase in parasitic capacitance and resistance relative to their intrinsic counterparts as device dimensions decrease. As Dennard's scaling law dictates, voltage reduction is crucial in order to curtail power dissipation, otherwise increased parasitics translate into stagnation of performance in terms of current drive. A potential solution to circumvent this dilemma is to substitute the silicon channel by a new material, one that offers carrier with higher injection velocity and mobility. In this regard III-V compound semiconductor holds immense promise [17]. InGaAs for electrons and InGaSb for holes offer a good balance among the many requirements imposed on a MOSFET channel material: low contact resistance, high mobility, adequate interfacial quality with high- $\kappa$  dielectrics and bandgap energy. There has been an explosion in research on InGaAs-based MOSFET both in industry and academia, the ramification being massive progress in III-V semiconductor device design in planar geometry as well as 3D architectures such as FinFETs and nanowire FETs [18–20].

The high mobility of the channel carriers augmented with the low density effective mass has enabled planar InGaAs MOSFET to make great strides in recent times. For future high-speed low-power logic applications, inversion-type enhancement-mode III-V MOSFET holds the foreground amongst prevalent logic devices. Intense research effort expended in the past four decades behind the search for the "perfect" insulator suitable for III-V MOS system has solved a long standing problem that is Fermi level pinning at the oxide-semiconductor interface. This phenomenon is believed to be due to the formation of native oxides that create high concentration of defects at the semiconductor interface [21]. Fermi level pinning prevents modulation of the surface potential by the gate and the charge control that is essential for efficient operation of MOSFET. Until recently, a technological breakthrough has addressed this prevailing problem by finding the use of atomic layer deposition (ALD) to integrate thermodynamically stable high- $\kappa$  dielectric on III-V semiconductor to form gate oxide involving a "self-cleaning effect" that eliminates the native oxides and associated defects at the semiconductor surface [22, 23]. Subthreshold swings in MOSFETs with values approaching 60 mV/decade have been demonstrated [24–26], having excellent interface quality with trap densities in the range of 10<sup>11</sup> eV<sup>-1</sup>cm<sup>-2</sup> [27, 28].

Another key element contributing to the dramatic rise of the InGaAs MOSFET performance has been the development of self-aligned fabrication methodology. Selfalignment of contacts and gate is vital for manufacturability and to minimize parasitics and footprint. In essence, four different self-aligned designs have emerged in the last few years.

- A contact-first, gate last process in which the gate is located in an opening created in the ohmic contacts [25, 29, 30].

- Raised, self-aligned source and drain epitaxial regions selectively grown around a dummy gate [31,32].

- A thin Ni layer thermally reacted with InGaAs to give rise to a highly conducting and very shallow intermetallic compound with very low resistivity [33].

- A combination of self-aligned ion implanted source and drain extensions and in-situ doped raised source and drain regions around a gate [34].

In spite of these advancements in fabrication methodologies, planar MOSFETs are limited in their scaling potential. Since channel thickness has a strong correlation with device characteristics, a thick channel is beneficial to ON-state figures of merit, such as  $g_m$ , whereas a thin channel influences OFF-state metrics like subthreshold swing (SS) and drain-induced barrier lowering (DIBL). To reap the benefits provided by the multi-gate architecture in suppression of SCEs compounded by the advantages of the III-V channel carriers, InGaAs nanowire MOSFET has become the quintessential solution for ultra-scaled devices.

As a deeply scaled device, the GAA nanowire MOSFET behaves differently from the classical large scale transistors in many aspects such as volume inversion and quantization effects impacting carrier transport. The small device feature makes the device performance sensitive to fin width scaling and oxide thickness. A physics-based analytical modeling of InGaAs GAA MOSFET is imperative to study the behavior of the device, to serve as a guideline for optimization of process parameters and use in circuit simulation. Given the quality of interface trap states as the major detrimental factor, limiting performance of InGaAs nanowire MOSFET to subpar levels, the incorporation of these trap charges is essential to accurately determine the mobile charges responsible for carrier transport. A comprehensive understanding of the device physics is obtained from the core transport model. However, in keeping with the convention of the ITRS guidelines for device scaling, certain non-ideal effects need to be complemented into the core model to facilitate the accurate reflection of the device electrostatics and transport characteristics. As such, the impact of physical process parameters are vital for optimization of device design, for which their impact must also be studied under the scope of the analytical model outlined in this thesis.

### **1.2** A Historical Perspective: Literature Review

Humanity experienced a tremendous advancement in computational power in the second half of the last century. During the war, semiconductor diodes made of high-purity germanium were explored at Bell Labs with an aim for potential use in radar applications. Using this newfound gumption in semiconductors, William Shockley dedicated resources in the development of semiconductor amplifier. At the same period, John Bardeen and Walter Brattain began work on what would be the point-contact transistor at the AT&T Laboratories, which was demonstrated in December of 1947 (Figure 1.3). There were two closely spaced gold contacts on one side of a germanium crystal in this device positioned on a metal plate. On application of a small current to one of the gold contacts resulted into amplification of the current flowing from the other contact to the metal plate. This was the first experimental demonstration of a transistor that brought the Nobel Prize in Physics in 1956 for the three scientists.

In the 1950's, shortly after Shockley invented the bipolar junction transistor, tran-

Figure 1.3: First experimental demonstration of a transistor based on germanium crystal substrate placed on a metal plate with two gold contacts. (Photo by Jacopo Werther) [35]

sistors were commercialized. Primary applications of the then novel device included transistor radios and hearing aids. In 1958, IBM introduced the first transistor-based commercial computer which was the IBM 7070. Soon after, the first integrated circuit was built by Jack Kilby at Texas Instruments which incorporated all the circuit components on the same semiconductor crystal, making it feasible to create compact circuit designs.

Robert Noyce of Fairchild Semiconductor invented a similar circuit in 1959. Robert started Intel with his colleague Gordon Moore, initially manufacturing bipolar random access memory (SRAM) in 1968 and later adopting the commercial MOSFET SRAM based on silicon. Gordon Moore recapitulated the pursuit of the integrated circuit industry in the title of his famous paper from 1965 [1], "Cramming more components onto integrated circuits", which led to the vaunted prediction known as Moore's Law. In a nutshell the law states that the number of transistors in an integrated circuit doubles every year (later revised to double biennially) [1]. The pursuit for compact integration was upheld thanks to a number of fortuitous events including but not limited to vast technological possibilities as well as tremendous economical incentives driving the increase in transistor count in a typical central processing unit (CPU) from tens of thousands in 1970's to billions in 2020, ushering the next industrial revolution at the frontier of cutting edge technology.

The first report on multigate transistor was published in 1984 describing a double-gate MOSFET [36]. The device received the acronym XMOS because of the resemblance of the structure with the Greek letter  $\Xi$ . In this paper it was shown that the short-channel characteristics could be improved through implementation of a double-gate architecture instead of the conventional single-gate approach. Soon after, the transistor model went into fabrication in 1989, containing a vertically positioned silicon film which, for the orientation of the film, came to be known as the fully DEpleted Lean-channel TrAnsistor (DELTA) [37]. As a vertical ultra-thin SOI device, DELTA offered a high storage area with high packing density in DRAM cell.

With some modification, the vertical channel double-gate transistor took the form of a FinFET (Fig. 1.2a) [38] with successful implementation in the sub 50-nm channel length. High drive currents of 410  $\mu$ A/ $\mu$ m were obtained at V<sub>d</sub>=V<sub>g</sub>=1.2V owing to the use of doped poly-SiGe films for raised source/drain contacts. The quasi-planar nature of this variant allowed industries to adopt its fabrication using the conventional planar MOSFET process technologies.

The continued scaling of fully depleted SOI transistor brings additional challenge when scaling the dimensions of the active channel region. For a single-gate fully depleted channel, the silicon body thickness needs to be at least a third or one-half of the electrical gate length in order to ensure full depletion under the gate. Doyle *et al.* demonstrated that tri-gate MOSFET ensures fully depleted behaviour at thickness dimensions greater than those of double-gate transistors, making them excellent candidate for future scaled CMOS technologies [39]. Improved version of the tri-gate MOSFET feature a field-induced pseudo-fourth gate such as the  $\pi$ -gate MOSFET (Fig. 1.2c) [40] and the  $\Omega$ -gate devices (Fig. 1.2d) [41, 42], created to improve gate electrostatic control over the channel charges and consequently reduce the SCEs. Jean-Pierre Colinge and Xiong *et al.* provided a comparative study of the impact of radii of curvature in the cross-section on the electrical characteristics among these class of devices [8, 43]. In essence, it was demonstrated that fully cylindrical devices imposed the greatest control over the channel carriers in the subthreshold regime Such devices include the CYN-THIA device (circular-section device) [44] and the pillar surrounding-gate MOSFET

Figure 1.4: A multi fingered (three-finger) nanowire transistor. (a) Scanning electron microscopy image of a device with three parallel nanowires that have a common gate electrode. Scale bar,  $5\mu$ m. (b) Transmission electron microscopy image of the three nanowires. Scale bar, 50 nm. (c) High resolution transmission electron microscopy image of a nanowire. Scale bar, 5 nm. [3]

Figure 1.5: Various configuration of nanosheet stacking. (a) Nanosheet double stack,  $W_{eff}=1.04x$  (b) Nanosheet double stack,  $W_{eff}=1.3x$  (c) [47]

(square-section MOSFET) [45].

The first reported gate-all-around device dates back to 1990, where the gate electrode is wrapped around all the sides of the channel region [46]. Though the device was used as a double-gate transistor back then, GAA geometry gained popularity once the benefits obtained from FinFETs reached a saturation. Apart from the suppression of SCE to the greatest extent, the GAA MOSFET allows high current drive simply by increasing the number of fingers or parallel stacking of nanowires as depicted in Figure 1.4 and 1.5. Tremendous effort expended behind silicon nanowires and the incorporation of strain engineering reveal the potential of silicon as a favorable channel material for CMOS technology [48–50]. However, phonon scattering and surface roughness from wraparound gate configuration limits the mobility to subpar levels, impeding the performance of silicon nanowires to reach near ballistic limits. This opens room for further improvement in carrier transport by utilizing high mobility III-V semiconductor channel materials.

To this end InGaAs has attracted the attention of researchers as a viable candidate to provide superior drain current in both on and off-state [51–53]. On the one hand, intense research in the past four decades have ushered significant progress on the use of atomic layer deposition to integrate thermodynamically stable high- $\kappa$  dielectric on III-V semiconductor, which drastically reduces gate leakage current of InGaAs based transistors, offering better effective oxide thickness (EOT) for minimization of static power dissipation [54]. On the other hand, the inherent high mobility of III-V semiconductor as the active channel material truncates dynamic power dissipation in the transistor, offering the same drive current at a reduced supply voltage [55]. This favoured InGaAs gate-all-around MOSFETs to gain popularity in switching and logic applications [53].

Although III-V FETs could not decisively outperform industrial silicon FETs at the beginning, partly due to the lack of native gate oxide problem, when aluminum oxide (Al<sub>2</sub>O<sub>3</sub>) was discovered to be an excellent oxide on the InGaAs system, rapid progress began in this class of material devices and state-of-the-art gate stacks now exhibit defect densities similar to those of silicon FETs [22,56]. III-V multigate MOS-FETs received extensive consideration from the research community for potential use in digital application. Kim *et al.* demonstrated InGaAs tri-gate FETs with channel width and height of 20 nm, exhibiting on-current of  $410\mu A/\mu m$  (at V<sub>DD</sub>=0.5V and I<sub>OFF</sub>=100nA/ $\mu m$ ). Radosavljevic *et al.* also reported tri-gate InGaAs FETs, demonstrating good electrostatic control and relatively high-quality oxide interface [57–59]. Gu *et al.* demonstrated gate-all-around InGaAs FETs with superb electrostatic control [60]. Waldron *et al.* also demonstrated gate-all-around InGaAs devices fabricated on Si substrate with excellent performance [28]. In all these reports, the non-planar channel were created by etching using a mask for channel definition.

Other published works include non-etching methodologies. For instance, Schmid *et al.* used templated-assisted selective-epitaxy (TASE), allowing for integration on silicon substrates as well as implementation of heterostructure systems [61,62]. Lee *at al.* also used TASE along with a gate-last process to demonstrate a 39 nm-L<sub>g</sub> InGaAs GAA nanosheet whose peak  $g_{\rm m}$  was reported to be 1.37 mS/ $\mu$ m and an excellent subthreshold slope of 72 mV/decade. Vertical transistors characterized by the flow of carriers in the channel from source to drain in vertical direction have also gained attention in recent times.

State-of-the-art vertical transistors utilizing vapour-liquid-solid (VLS) catalyst-based growth to form the nanowire channel, have been reported by Berg *et al.*, demonstrating excellent performance [63], as well as Svensson *et al.*, demonstrating co-integration with gallium antimonide (GaSb) p-channel FET for CMOS circuits [64]. Contrary to the top-down approach, VLS is a bottom-up approach producing high-aspect ratio nanowires with atomically smooth sidewalls and uniform diameters along the axial directions. It is also convenient to scale down the diameter in this process, which is primarily determined by the size of the seed dots. Jung et al. recently demonstrated sub-10 nm InAs nanowire with a minimum diameter of 2 nm from Au seeded growth [65]. Also by defining Au dots in a lithographical method, ordered nanowires can be realized. The most attractive benefit of the VLS method is probably the direct integration of III-Vs on a lattice-mismatched substrate, such as silicon. Below a certain critical diameter [66], high-quality nanowires can be grown epitaxially on a foreign substrate without generating axial dislocations, which is an alluring prospect of III-V nanowires for CMOS application, requiring both n-channel and p-channel materials on one substrate. Other forms of bottom-up approach for growing III-V nanowire are outlined in [19], elaborating on the pros and cons of each fabrication viewpoint.

Nanowires with one-dimensional columnar shape has gained enormous attention, particularly for their ability to confine carriers in 2-dimensions, thereby allowing them to propagate freely in the third dimension [67–69]. Owing to the good optoelectronic properties of III-V semiconductor materials, a wide range of methods have been used to fabricate nanowires in photovoltaic applications, typically as solar energy harvesters, such as laser ablation, metal-organic vapor phase epitaxy, chemical beam epitaxy and molecular beam epitaxy to name a few [70–74]. Thus, III-V nanowires have a strong hold in the optoelectronic area as the successor of next generation photovoltaics.

Besides experimental demonstrations of the various forms of multigate transistors in the literature, there had been a concomitant progress in the analytical studies conducted by various luminaries to provide an in-depth analysis of the device physics undergirding each type of transistor in operation.

In 1994, Francis *et al.* proposed an analytical expression for the potential, charge and electric field within the channel region of a double-gate nMOS/SOI device [75]. Given the apparent simplicity of the model, the results were confined to weak inversion and below threshold operation of the device. In the subsequent year, the extent of the model was elaborated to moderate inversion regime with drain current and transconductance bearing strong resemblance with MEDICI simulations [76].

Taur *et al.* provided an analytical solution to double-gate MOSFET with undoped body by incorporating only the mobile charge term into the Poisson equation [77]. Four years later, the authors succeeded in devising a continuous drain-current model for the same device, derived directly from Pao-Sah integral without the necessity of charge sheet approximation [78]. Given the compact nature of the expression, this work gained popularity among the circuit designers for simulation of double-gate devices with undoped channel.

In 2002, Pei *et al.* conducted an extensive investigation for FinFET design consideration using three-dimensional (3-D) simulation [79]. Analytical solution of the 3-D Laplace's equation was employed to establish the design equations on the subthreshold behavior in the fully depleted silicon fins. The critical geometrical parameters considered for the FinFET were,

• Physical gate length of the FinFET defined by the spacer gap

- Height of the silicon fin, defined by the distance between top gate and buried oxide

- Thickness of silicon fin, defined by the distance between front and back gate oxides

- Effective channel length of FinFET estimated by the metallurgical junction for abrupt concentration gradient between the source (drain)-channel

- Geometrical channel width, defined at the net gated perimeter of the transistor

These guidelines also serve fruitful for the gate-all-around transistor utilizing III-V channel material.

Chen & Meindl devised a compact, physics-based, short-channel model of subthreshold swing and threshold voltage for undoped symmetric double-gate MOSFETs, the novelty of which includes quantum-mechanical and fringe-induced-barrier-lower effects [80]. In short-channel devices, the channel center has a higher electrostatic potential than anywhere else because of the influence of the source/drain and weakened gate control. Considering the most leakiest path inside the channel, a compact analytical subthreshold swing model was obtained under evanescent-mode analysis [81]. Moreover, it was shown that the conventional way of defining the threshold voltage by the surface band bending equal to  $2\phi_{\rm B}$  becomes irrelevant, where  $\phi_{\rm B}=({\rm kT/q}){\rm ln}(N_{\rm A}/n_{\rm i})$  with  $N_{\rm A}$  and  $n_{\rm i}$  being the doping concentration and intrinsic carrier concentration in the channel respectively. This issue was addressed by solving the 2-D Poisson equation with the inclusion of inversion charge term.

In 2004, Jiménez *et al.* derived a continuous analytic current-voltage model for cylindrical undoped (lightly doped) surrounding gate MOSFETs [82]. The model was shown to agree with three-dimensional numerical simulation from DESSIS-ISE in all operating regions (linear, saturation, subthreshold) and traces the transition between them without fitting parameters, being ideal for the kernel of SGT MOSFET compact models. The channel current was written as an explicit function of the applied voltage, based on a unified charge control model [83]. Ortiz-Conde *et al.* worked on a similar device to unfold the Lambert function-based analytic solution for the surface potential of the double-gate device. The works of Wei Bian *et al.* though similar to Jiménez *et al.*, differs from previous works in that the drain-current equation accounts for both drift and diffusion current components in terms of the potential at the oxide-semiconductor interface as well as at the center of the device body evaluated at the source and drain terminals [84]. This model allows room for inclusion of other second-order physical effects integrated in the form of add-on modules.

With much research on analytic reports of double-gate and surrounding gate MOS-FETs, Yu *et al.* suggested a unified explicit solution of drain current for multi-gate MOSFETs, based on the former two devices [85, 86]. The primary assumption underlying this union was that the inversion charge in subthreshold is proportional to the silicon cross-sectional area (volume inversion), whereas the inversion charge above threshold is proportional to the gated perimeter of the silicon body. Using Ward-Dutton linear charge partitioning, fully compact expression of all the nine capacitance coefficients were obtained directly based on the charge conservation law [87].

In 2007, Tsormpatzoglou *et al.* semi-analytically studied the short channel effects in silicon and germanium double-gate MOSFETs [88]. 2-D potential distribution is derived along the channel of the symmetric double-gate device in weak inversion regime. A semi-analytical expression for the subthreshold current is proposed along with extraction of other vital subthreshold performance metrics such as drain induced barrier lowering and threshold voltage roll-off. An analysis between Si and Ge as channel material reveals that Ge double-gate MOSFETs are more prone to SCEs.

Moldovan *et al.* studied a similar device with highly-doped channel which are more opted for baseband analog applications [89]. By this time, numerous analytic reports for undoped body double-gate MOSFETs were available in the literature. This work presents a unified charge control model for the first time for doped double-gate transistors. The difference of surface and center potential was assumed constant from subthreshold to well above threshold, an approximation that remains valid for highlydoped channel and expedites the solution of transcendental equation formed by the relation of surface potential with gate bias. In addition, fully compact expression for intrinsic capacitances were obtained, making the model highly desirable in circuit simulation.

The effect of body doping on threshold voltage and channel potential of double-gate MOSFET was only analyzed in the below threshold region. Liu *et al.* formulated a global continuous channel potential solution, valid for a wide range of doping concentrations from accumulation to strong inversion operation [90]. The study reveals that in the doped transistors, the geometric parameter dependence of the threshold voltage are different from that in intrinsic ones. The robustness of the model is verified from a good initial guess to facilitate the solution of channel potential.

Han *et al.* developed a continuous and analytic channel potential model for lightly doped GAA nanowire FET based on 6H-SiC [91]. The model adequately describes the inversion charge, incorporating the influence of incomplete dopant ionization, backed up by TCAD simulation. In spite of a unified drain current model in [87], the notion of equivalent capacitance was proposed by Chevillon *et al.* to generalize the so-called equivalent-thickness concept to model arbitrary shapes of lightly doped nonplanar multigate MOSFETs without adoption of any unphysical parameters [92]. The model merely maps any multigate geometry such as quadruple-gate, triple-gate, triangular gate, cylindrical gate-all-around and double-gate FinFET into the renowned double-gate MOSFET topology. The robustness of the model is verified for a range of temperatures without the need for any additional empirical parameters.

With strong motivation to reduce SCE in deeply scaled transistors, it was imperative to incorporate quantum mechanical effect into the physics based analytical reports. In this respect, an analytical model was proposed to calculate the potential and inversion charge of III-V cylindrical Surrounding-Gate MOSFET (SGT) by Marin *et al.* [93]. The developed model contains expression for the calculation of subband energies and their corresponding wavefunctions, taking into account their penetration into the gate insulator and the effective mass discontinuity in the semiconductor-insulator interface for this class of device, which is imperative to accurately devise the physics of loweffective-mass materials such as InGaAs. The model considers Fermi-Dirac statistics in conjunction with two-dimensional quantum confinement of the carriers. The solution of Poisson and Schrodinger equation is accompanied by the cylindrical symmetry of the device and the isotropic effective mass of  $\Gamma$  valley of the III-V material. Given the higher electron mobility in  $\ln_x \operatorname{Ga}_{1-x}$ As channel in comparison to silicon, and the superb control of the channel charge exerted by the surrounding gate configuration is well presented by the self-consistent analytical results, accurately mapping the spatial charge distribution within the channel in coherence with quantum confinement. This work is later expanded into a physically based gate capacitance and drain current model for III-V nanowires [94,95]. Different factors were explicitly accounted to reflect their contribution to gate capacitance. In this manner, the total gate capacitance is more meaningful in that it distinguishes between insulator and quantum capacitance exhibited by the short-channel device.

In a similar fashion Khosru et al. and Khan et al. studied the electrostatics and transport behavior in a gate-all-around InGaAs nanowire MOSFET with square crosssection [96, 97]. Finite element method was implemented to determine the solution of Poisson and Schrodinger equation in a coupled manner, taking wave function penetration, energy level splitting and other quantum effects into account. The impact of various physical/process parameters such as alloy composition, oxide thickness, finwidth and doping density on capacitance-voltage characteristics were explored. The prospect of utilizing high- $\kappa$  gate dielectric has long been favoured in the semiconductor industry. The effect of such high- $\kappa$  insulators on long channel threshold voltage were semi-analytically explored. The study reveals that for lower channel doping fin width mostly affects threshold voltage whereas in highly doped channel, the threshold voltage variation is prone to oxide thickness and permittivity. Transport characterization of experimentally demonstrated nanowire MOSFET in near-ballistic regime were performed using Uncoupled Mode Space approach [98]. As an appendage, ballistic transport characterization of the same device were carried out in axially composition graded  $In_{1-x}Ga_xAs$  channel, revealing an on-off current ratio of 10<sup>7</sup>, drain induced barrier lowering of 43.79 mV/V and near ideal subthreshold swing of 61.37 mV/dec [99].

Eventhough potential distribution were previous studied in the transport direction and

confinement direction separately, a precise modeling framework that spatially maps the potential variation in the three-dimensional space could only be obtained from the more computationally expensive numerical simulation. Borli *at al.* proposed a framework based on conformal mapping analysis of the potential distribution in the device body arising from the interelectrode capacitive coupling, combined with self-consistent procedure to include the effects of inversion charge [100]. The work relates the interelectrode coupling dominating the subthreshold behavior of double-gate device to cylindrical GAA MOSFET by means of a simple geometric scaling transformation, accounting for the difference in gate control of the two device. Moreno *et al.* provided an analytical description of the 2D inversion charge distribution function (ICDF) in square GAA MOSFET [101]. The ICDF is an effective robust formulation that successfully describes the inversion charge centroid and gate-to-channel capacitance, circumventing the complex self-consistent simulation process. From compact modeling viewpoint, this method is considered a good candidate for future scaled integrated circuit technologies.

#### **1.3** Contribution of the Thesis

Electrostatic control in three dimensions has become imperative to reduce the short channel effects (SCEs) in deeply scaled transistors beyond the 22nm technology node. Aggressive scaling of transistors to conform Moore's Law have eventually convinced researchers to investigate the prospects of multi-gate MOSFETs [5]. The gate-allaround (GAA) MOSFET has proven to provide greatest immunity to SCEs with the shortest natural length ( $\lambda$ ) and imposing stronger gate control over surface carriers. Although both cylindrical nanowires and rectangular GAA MOSFETs have exhibited excellent transport and subthreshold performance recently [28, 102], the rectangular geometry offers additional advantage in terms of fabrication viewpoint:

• Rectangular GAA MOSFET can be grown epitaxially into thin and wider nanosheets in stacked configuration unlike cylindrical nanowire MOSFETs which are grown by vapor-liquid-solid (VLS) method [19]. This enables precise control of nanowire height in rectangular geometry. One of the challenges in fabricating cylindrical nanowire is controlling the shape of the nanowire, since transport properties rely heavily on nanowire diameter [103]. This difficulty is circumvented in rectangular GAA MOSFET with etching techniques allowing exact control of nanosheet width.

- Monolithic 3D transistor stacking can be employed with ease for rectangular nanosheet. The use of interlayer dielectric has resulted into reduction of parasitic capacitance for a given active width, giving more W<sub>eff</sub> for the same footprint [47]. Even though pitch scaling allows cell height scaling, thereby rendering a viable path for density scaling in next generation transistors, it has been shown that a single wide nanosheet stack has superior intrinsic performance making it lucrative for use in 3D stacked configuration with monolithic heterogeneous integration through layer transfer technologies.

- The semiconductor industry is already reaping the advantages offered by Fin-FET transistor. Rectangular horizontal nanowires bear strong similarity with FinFET architecture, having minimal deviation. Thus fabrication of GAA MOS-FET could be easily adopted by the industry with little technology shift.

- Strain engineering is essential to improve short channel performances [104]. The extent of strain incorporated in the lateral or vertical rectangular GAA MOSFET depends on the orientation of nanowire growth. Integration of inner spacers and raised source/drain may induce strain relaxation or inject excess compressive strain in the InGaAs channel, thus offering the potential for process-induced strain modulation in 3D stacked nanowire devices.