### M.SC. ENGG. THESIS

# WIDE TUNING MULTIMODE SPLIT-LOAD RING OSCILLATOR FOR LEAKAGE-TOLERANT STUCK-ON FAULT DETECTION IN SUBMICRON CMOS CIRCUITS

by

S. M. Ishraqul Huq

Submitted to

Department of Electrical and Electronic Engineering in partial fulfillment of the requirements for the degree of Master of Science in Electrical and Electronic Engineering

Department of Electrical and Electronic Engineering

Bangladesh University of Engineering and Technology (BUET)

Dhaka 1000

October 2021

#### **Approval Certificate**

The thesis titled "Wide Tuning Multimode Split-Load Ring Oscillator for Leakage-Tolerant Stuck-On Fault Detection in Submicron CMOS Circuits", submitted by S. M. Ishraqul Huq, Roll No. 1017062277, Session: October-2017 has been accepted as satisfactory in partial fulfillment of the requirements for the degree of Master of Science in Electrical and Electronic Engineering on October 04, 2021.

#### **Board of Examiners**

1.

Dr. Apratim Roy Associate Professor Department of Electrical and Electronic Engineering Bangladesh University of Engineering and Technology, Dhaka

KA 8 200 2.

Dr. Md. Kamrul Hasan Professor and Head Department of Electrical and Electronic Engineering Bangladesh University of Engineering and Technology, Dhaka

3

Dr. Md. Shafiqul Islam Professor Department of Electrical and Electronic Engineering Bangladesh University of Engineering and Technology, Dhaka

4.

5.

Dr. Ahmed Zubair Associate Professor Department of Electrical and Electronic Engineering Bangladesh University of Engineering and Technology, Dhaka

Dr. Md. Anwarul Abedin Professor Department of Electrical and Electronic Engineering Dhaka University of Engineering and Technology (DUET), Gazipur (Supervisor)

Chairman

Member

Member

(Ex-Officio)

Member

Member (External)

## **Candidate's Declaration**

This is declared that the work entitled "Wide Tuning Multimode Split-Load Ring Oscillator for Leakage-Tolerant Stuck-On Fault Detection in Submicron CMOS Circuits" is the outcome of research carried out by me under the supervision of Dr. Apratim Roy, in the Department of Electrical and Electronic Engineering, Bangladesh University of Engineering and Technology, Dhaka 1000. It is also declared that this thesis or any part of it has not been submitted elsewhere for the award of any degree or diploma.

milling

S. M. Ishraqul Huq Candidate

# Acknowledgment

I would like to express my sincere gratitude to my supervisor, Dr. Apratim Roy for his supportive guidance and constructive suggestions throughout this research work. He is an amazing academician and I am blessed to work with him in my M.Sc. thesis. His constant encouragements and invaluable assistance motivated me to push my boundaries harder. Throughout my life, I will benefit from the experience and knowledge I gained working with Dr. Apratim Roy.

It is my pleasure to acknowledge Dr. Md. Kamrul Hasan, Dr. Md. Shafiqul Islam, Dr. Ahmed Zubair and Dr. Md. Anwarul Abedin for serving as members on my examination committee. I would like to formally thank them for reviewing this thesis and giving their valuable time and suggestions.

I owe more than words that can describe to my parents, S. M. Ihtishamul Huq and Salma Huq for their constant support, encouragement and faith which works as a positive reinforcement, especially during my failures. This work is dedicated to them.

Finally, all praise and glory to the Almighty for giving me the patience, strength, knowledge and capability to complete this research work successfully.

# Abstract

This thesis focuses on designing robust and reliable fault testing methods using oscillators to detect transistor stuck-on (TSON) faults in submicron CMOS circuits. Simulations are performed in Cadence Virtuoso platform using 90 nm technology models. There are several structures for voltage controlled oscillators (VCO), among which the single-ended ring oscillator (SERO) structure is utilized for its superiority in terms of power penalty and manufacturability. The conventional structure has been modified with split-load technique for dual-mode tuning to facilitate greater control in frequency regulation. Meanwhile, the low power requirement of the circuit is maintained through device sizing. While considering the effects of parasitic capacitances, the proposed architecture provided the maximum tuning range when compared with other presented works in literature. Next, the frequency response of the oscillator has been investigated as a function of the controlling parameters tuning voltages, number of stages in the ring, and transistor width ratio to derive an empirical model for the operating point. Unlike the existing approximate models which only apply for the conventional SERO circuit, the frequency model in this work will assist the designer to accurately set the desired operating point. Finally, the SERO architecture with its load adaptation has been utilized to propose two fault-testing methods where the oscillator functions as current- and voltage-controlled oscillators, respectively. The test schemes exploit triggered output oscillations during the presence of a fault in the circuit under test (CUT). Computational ease and system reliability are improved by avoiding average quiescent current calculation in the I<sub>DDQ</sub> method and indeterminate voltages of the logic voltage method. The proposed testing schemes remain more effective in high-leakage CMOS regime through threshold regulation achieved by multimode tuning of the split-load SERO and mirror device sizing, circumventing complex circuitry compared to built-in-currentsensor (BICS) protocols for on-chip fault detection.

# **Table of Contents**

| Ba | pard of Examiners                               | i    |

|----|-------------------------------------------------|------|

| Ca | Indidate's Declaration                          | ii   |

| Ac | cknowledgment                                   | iii  |

| Al | bstract                                         | iv   |

| Li | st of Figures                                   | viii |

| Li | st of Tables                                    | x    |

| Li | st of Abbreviations                             | xi   |

| Li | st of Symbols                                   | xii  |

| 1. | Introduction                                    | 1    |

|    | 1.1. Background                                 | 1    |

|    | 1.2. Motivation of the Thesis                   | 3    |

|    | 1.3. Objectives of the Thesis                   | 3    |

|    | 1.4. Thesis Organization                        | 4    |

| 2. | <b>Review of Voltage Controlled Oscillators</b> | 5    |

|    | 2.1. Fundamentals of Oscillator Operation       | 5    |

|    | 2.2. Important VCO Specifications               | 6    |

|    | 2.2.1. Phase Noise and Jitter                   | 7    |

|    | 2.2.2. Figure of Merit (FoM)                    | 8    |

|    | 2.2.3. Characteristics of Operating-Point       | 8    |

|    | 2.2.4. Power Consumption                        | 9    |

|    | 2.2.5. Manufacturability                        | 9    |

|    | 2.3. LC-based Oscillator                        | 9    |

|    | 2.4. Ring Oscillator (RO)                       | 10   |

|    | 2.5. RO vs. LC-VCO                              | 11   |

|    | 2.5.1. Phase Noise                              | 11   |

|    | 2.5.2. Maximum Operating-Point                  | 13   |

|    | 2.5.3. Tuning Range                             | 13   |

|    | 2.5.4. Power Consumption                        | 13   |

|    | 2.5.5. Manufacturability                        | 13   |

|    | 2.6. CMOS Inverter-based Single-Ended RO (SERO)                      | 14 |

|----|----------------------------------------------------------------------|----|

|    | 2.7. Adaptations of Single-Ended Ring Oscillators                    | 16 |

|    | 2.7.1. Current Starved RO                                            | 16 |

|    | 2.7.2. Negative-Skewed RO                                            | 18 |

|    | 2.7.3. Transmission gate (TG) RO                                     | 18 |

|    | 2.7.4. RO using Bulk Voltage Effect                                  | 19 |

|    | 2.7.5. Symmetrical Even-phase Outputs SERO                           | 20 |

|    | 2.7.6. NMOS-sink CS-VCO                                              | 21 |

|    | 2.7.7. RO using STSCL Load Devices                                   | 21 |

|    | 2.7.8. Hybrid SEROs                                                  | 22 |

|    | 2.7.8.1. Combined RO                                                 | 22 |

|    | 2.7.8.2. CS-Skewed RO                                                | 22 |

|    | 2.7.8.3. Combined-Skewed RO                                          | 23 |

|    | 2.7.9. LC based SEROs                                                | 24 |

|    | 2.7.9.1. RO using Inductor Peaking                                   | 24 |

|    | 2.7.9.2. Quadrature RO using Series LC Tank                          | 24 |

|    | 2.7.10. Summary                                                      | 25 |

|    | 2.8. Approximate Operating-Point Models                              | 25 |

|    | 2.8.1. Current Source (CS) Model and Delay at 50%                    | 26 |

|    | 2.8.2. CS Model and Delay at 90% Level                               | 27 |

|    | 2.8.3. CS Model and Delay at 100% Level                              | 28 |

|    | 2.8.4. RC Models                                                     | 28 |

|    | 2.8.5. Sources of Inaccuracy in Approximate Models                   | 30 |

|    | 2.9. Modeling of Parasitic Load Capacitance                          | 31 |

| 3. | Multimode Single-Ended Split-Load Ring Oscillator                    | 33 |

|    | 3.1. SERO with Active-Load                                           | 34 |

|    | 3.2. Single-Ended Split-Load Ring Oscillator (SESLRO) with Multimode |    |

|    | Tuning                                                               | 35 |

|    | 3.3. Simulation Environment                                          | 36 |

|    | 3.3.1. Wide Tuning with Multimode Operation                          | 37 |

|    | 3.3.2. Device Sizing                                                 | 37 |

|    | 3.4. Simul  | ation Results and Analysis                                | 37 |

|----|-------------|-----------------------------------------------------------|----|

|    | 3.4.1.      | Frequency-Voltage Characteristics                         | 37 |

|    | 3.4.2.      | Fine Tuning Frequency Response                            | 41 |

|    | 3.4.3.      | Empirical Model of Operating-Point                        | 42 |

|    | 3.4.4.      | Impact of PVT Variations                                  | 45 |

|    | 3.4.5.      | Layout                                                    | 47 |

| 4. | Leakage     | Folerant Transistor Stuck-ON Fault Detection using Ring   |    |

|    | Oscillator  | rs                                                        | 48 |

|    | 4.1. Trans  | istor Stuck-ON (TSON) Fault                               | 49 |

|    | 4.2. Conv   | entional Fault Detection Methods                          | 49 |

|    | 4.3. Fault  | Conditions and Test Vectors                               | 50 |

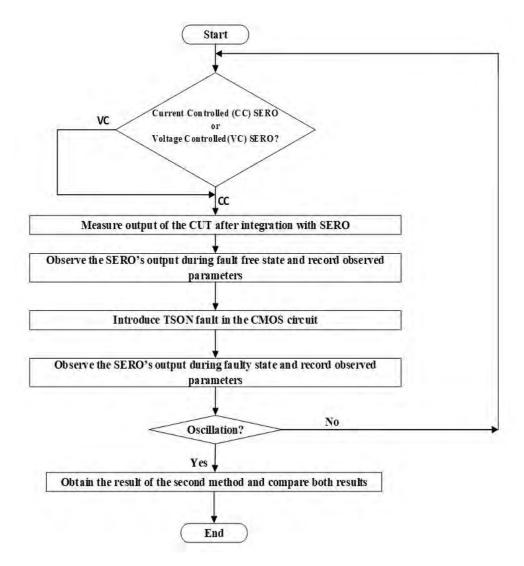

|    | 4.4. Propo  | sed Methodology of Testing Methods                        | 52 |

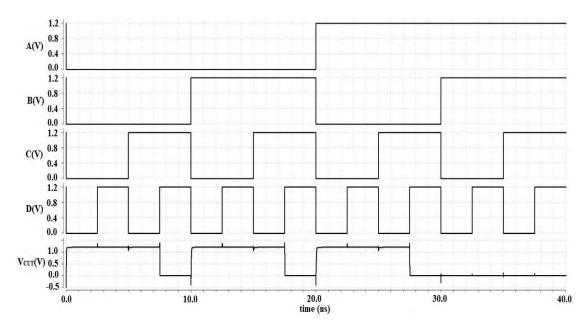

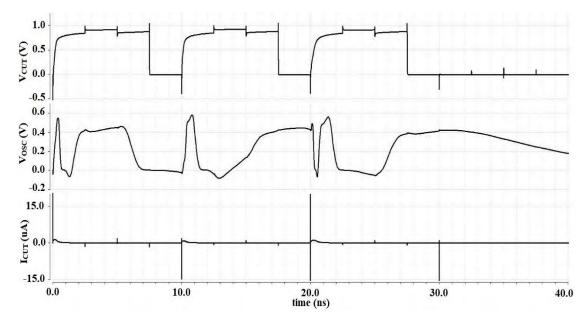

|    | 4.5. Simul  | ation Results and Analysis                                | 53 |

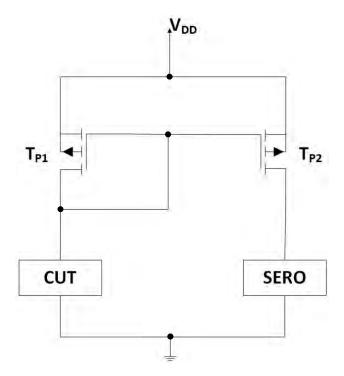

|    | 4.5.1.      | Method 1: using Current-Controlled SERO                   | 53 |

|    | 4.5.2.      | Method 2: using Voltage-Controlled SERO                   | 57 |

|    | 4.6. Leaka  | age Tolerant TSON Fault Detection                         | 59 |

|    | 4.6.1.      | Comparison between SESLRO-based Proposed Methods          | 62 |

|    | 4.7. Perfor | rmance Assessment                                         | 63 |

|    | 4.7.1.      | Power Penalty                                             | 64 |

|    | 4.7.2.      | Behavior of Oscillator and CUT Outputs                    | 64 |

|    | 4.7.3.      | Adaptable Threshold Regulation                            | 65 |

|    | 4.7.4.      | Built-in Current Sensor (BICS) Performance and Comparison |    |

|    | W           | vith Literature                                           | 66 |

| 5. | Conclusio   | ons and Future Scopes                                     | 69 |

|    | 5.1. Sumn   | nary                                                      | 69 |

|    | 5.2. Future | e Scopes                                                  | 71 |

|    | Bibliogra   | phy                                                       | 72 |

|    | List of Pu  | blications                                                | 79 |

# **List of Figures**

| Fig.<br>No. | Figure Caption                                                               | Page<br>No. |

|-------------|------------------------------------------------------------------------------|-------------|

| 1.1         | Block diagram of PLL                                                         | 2           |

| 1.2         | Spectrum growth versus traffic growth                                        | 2           |

| 2.1         | Simple feedback system                                                       | 5           |

| 2.2         | VCO frequency transfer function [4]                                          | 6           |

| 2.3         | Illustration of Phase Noise [4]                                              | 7           |

| 2.4         | RO with (a) single-ended, and (b) differential delay stages [14]             | 11          |

| 2.5         | Effect of noise impulse on oscillator output during peak and transition [14] | 12          |

| 2.6         | Conventional SERO                                                            | 14          |

| 2.7         | CS-VCO delay stage serving as the unit block of multistage structure [20]    | 17          |

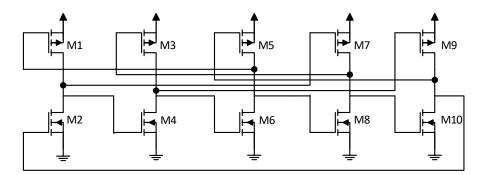

| 2.8         | Five-stage RO using negative skewed scheme [28]                              | 18          |

| 2.9         | Three-stage transmission gate supported RO [29]                              | 19          |

| 2.10        | Delay cell for symmetrical even-phase output SERO [33]                       | 20          |

| 2.11        | Multistage oscillator with source-coupled logic load [35]                    | 22          |

| 2.12        | Multistage skewed RO using three types of units [39]                         | 23          |

| 2.13        | Three-stage RO using peaking inductors [40]                                  | 24          |

| 2.14        | Quadrature RO using series LC tanks [41]                                     | 25          |

| 2.15        | Propagation delay calculation at 50% level [45]                              | 26          |

| 2.16        | RC model of CMOS inverter at $V_{in} = 0$ [47]                               | 29          |

| 2.17        | Components of parasitic capacitances in cascaded CMOS inverter               | 31          |

| 3.1         | SERO with active-load inverter                                               | 34          |

| 3.2         | Proposed SESLRO                                                              | 35          |

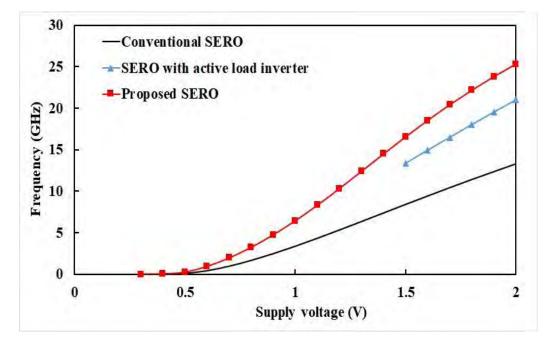

| 3.3         | Frequency response of three different SEROs                                  | 38          |

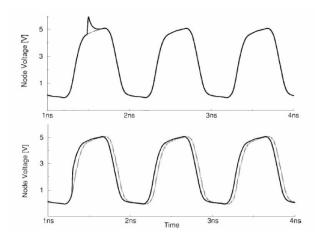

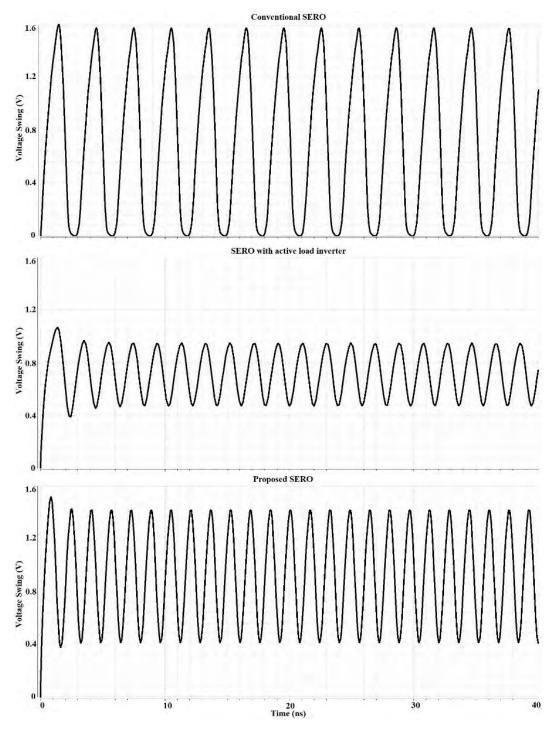

| 3.4         | Oscillator outputs of the three circuits at 2 V supply                       | 39          |

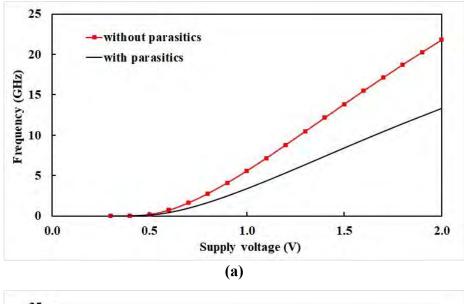

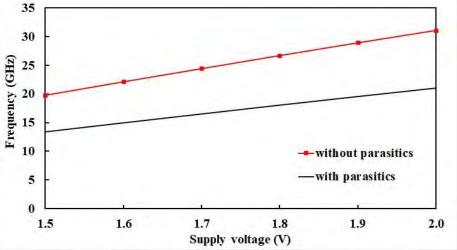

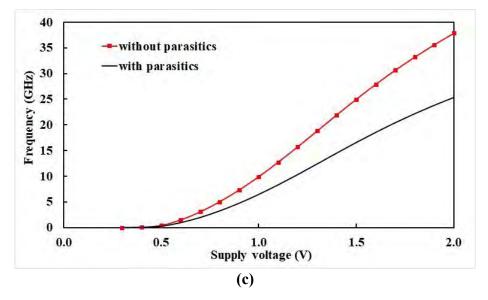

| 3.5         | Parasitic effect on frequency-voltage characteristics for (a) conventional   |             |

|             | SERO, (b) SERO with active-load inverter, and (c) proposed SERO              | 40          |

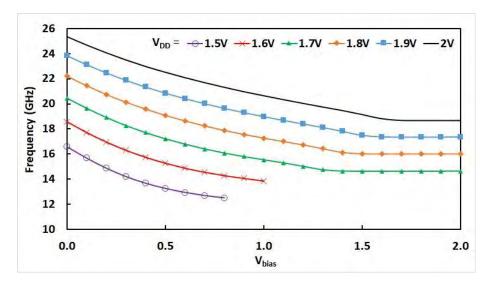

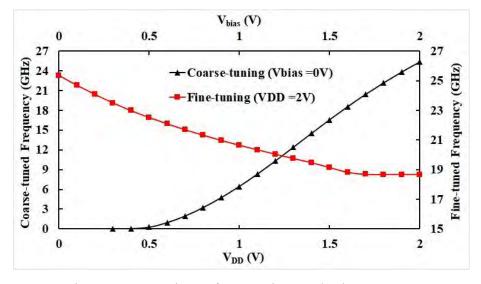

| 3.6         | Fine tuning frequency response of SESLRO                                     | 41          |

| 3.7  | Comparison of two tuning modes in SESLRO                                     | 41 |

|------|------------------------------------------------------------------------------|----|

| 3.8  | Frequency versus (a) N and (b) W <sub>R</sub>                                | 43 |

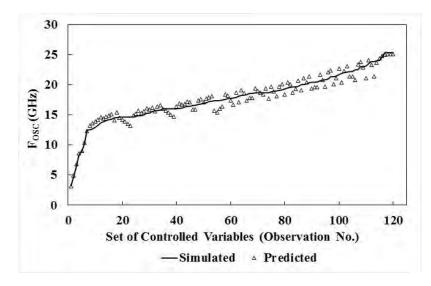

| 3.9  | Simulated data versus empirical model                                        | 45 |

| 3.10 | Impact of statistical variations of process parameters on (a) frequency, and |    |

|      | (b) power penalty                                                            | 46 |

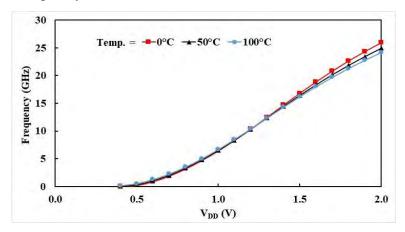

| 3.11 | Impact of temperature variation on frequency-voltage characteristic          | 47 |

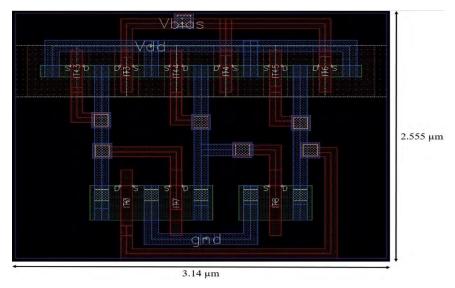

| 3.12 | Layout of proposed SESLRO                                                    | 47 |

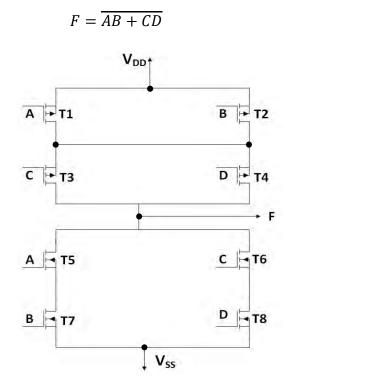

| 4.1  | Circuit Under Test (CUT)                                                     | 50 |

| 4.2  | Test method verification flowchart                                           | 53 |

| 4.3  | TSON fault test using current-controlled SERO                                | 54 |

| 4.4  | Input control signals and output of the standalone CUT                       | 55 |

| 4.5  | Output logic of CUT, oscillator ouput and current through the CUT during     |    |

|      | fault-free state using Method 1                                              | 55 |

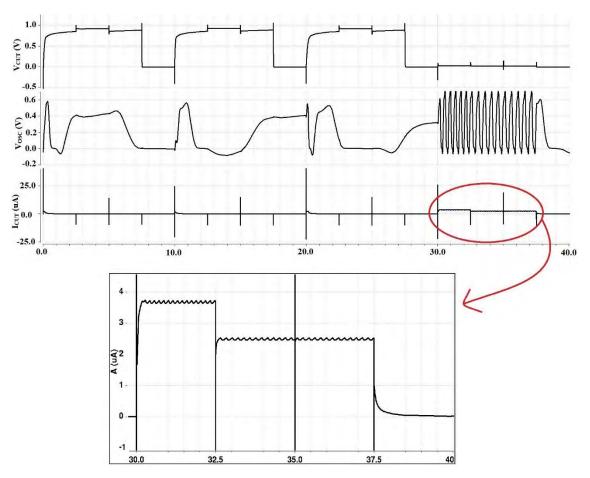

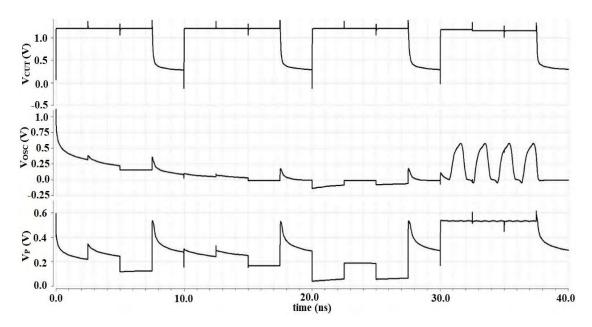

| 4.6  | Outputs for TSON fault at T1 using Method 1                                  | 56 |

| 4.7  | Outputs for TSON fault at T6 using Method 1                                  | 56 |

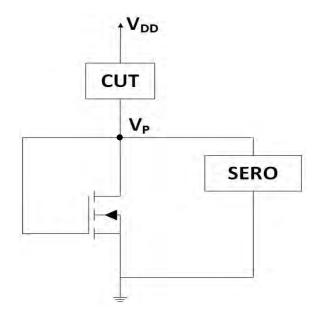

| 4.8  | TSON fault test using voltage-controlled SERO                                | 57 |

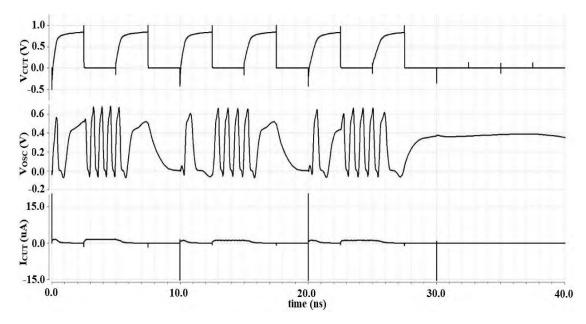

| 4.9  | Output logic of CUT, oscillator output and voltage VP during fault-free      |    |

|      | state using Method 2                                                         | 58 |

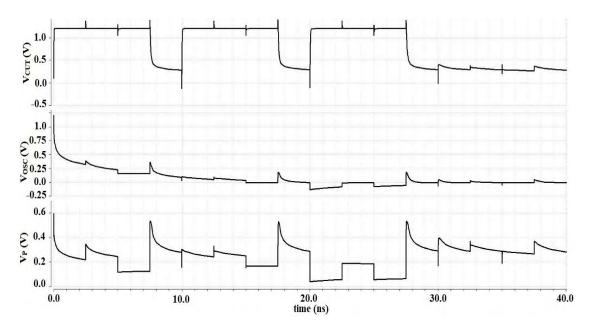

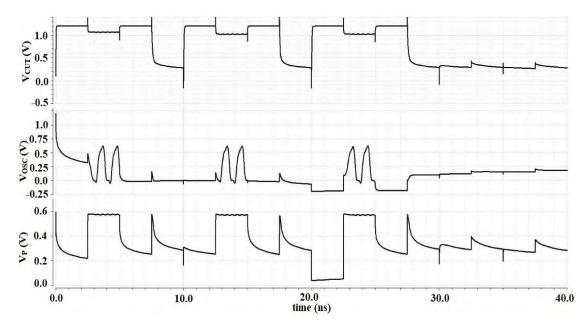

| 4.10 | Outputs for TSON fault at T1 using Method 2                                  | 59 |

| 4.11 | Outputs for TSON fault at T6 using Method 2                                  | 59 |

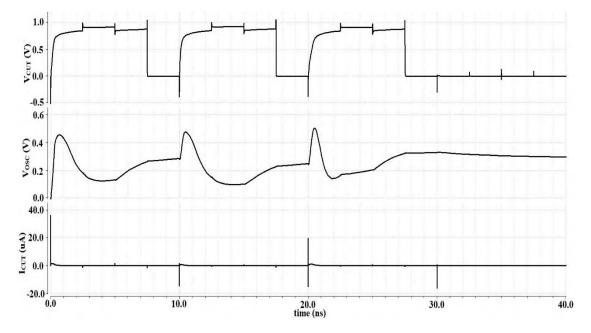

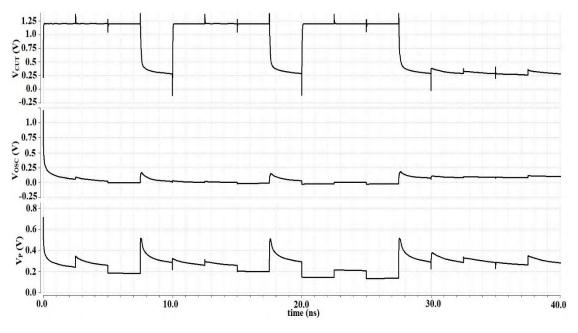

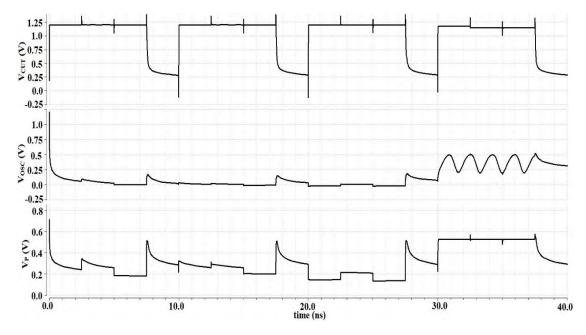

| 4.12 | Outputs for SESLRO-based Method 1 for fault-free state                       | 60 |

| 4.13 | Outputs of SESLRO-based Method 1 for fault in T1                             | 60 |

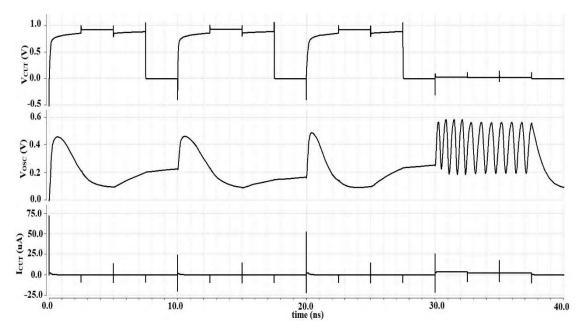

| 4.14 | Outputs of SESLRO-based Method 2 for fault-free state                        | 61 |

| 4.15 | Outputs of SESLRO-based Method 2 for fault in T1                             | 61 |

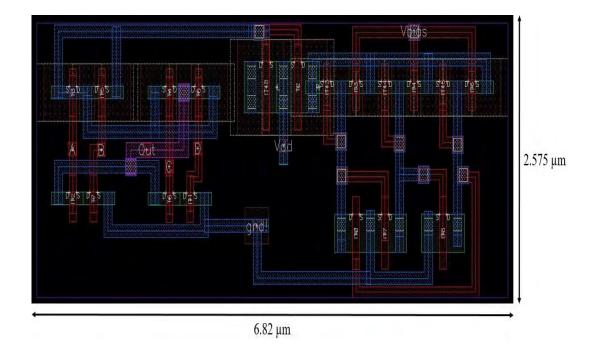

| 4.16 | Layout of SESLRO-based testing Method 1                                      | 62 |

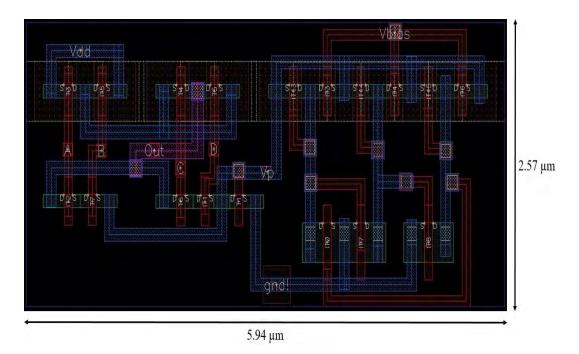

| 4.17 | Layout of SESLRO-based testing Method 2                                      | 62 |

| 4.18 | Threshold regulation at increased supply rating reflecting high leakage      | 66 |

# **List of Tables**

| Table<br>No. | Table Title                                                            | Page<br>No. |

|--------------|------------------------------------------------------------------------|-------------|

| 2.1          | Summary of Ring vs. LC oscillator                                      | 14          |

| 2.2          | Expressions of parasitic capacitance components                        | 32          |

| 2.3          | Definition of variables in parasitic components                        | 32          |

| 3.1          | Load capacitance of the three oscillators                              | 39          |

| 3.2          | Comparison with other works                                            | 42          |

| 3.3          | Coefficients and accuracies of the functions in the empirical model    | 44          |

| 3.4          | Performance of proposed oscillator at different technology nodes       | 46          |

| 4.1          | TSON faults and corresponding test vectors                             | 51          |

| 4.2          | Comparison between the two testing methods                             | 63          |

| 4.3          | Comparison of power penalty for CUT with and without integrated        |             |

|              | SERO                                                                   | 64          |

| 4.4          | Comparison with existing BICS circuits for oscillation based detection | 67          |

| 4.5          | Comparison with existing BICS circuits for IDDQ based detection        | 68          |

# **List of Abbreviations**

| Abbreviation | Description                                   |

|--------------|-----------------------------------------------|

| BICS         | Built-In Current Sensor                       |

| ССО          | Current Controlled Oscillator                 |

| CMOS         | Complementary Metal-Oxide Semiconductor       |

| CS-VCO       | Current Starved Voltage Controlled Oscillator |

| CUT          | Circuit Under Test                            |

| FoM          | Figure of Merit                               |

| FTR          | Frequency Tuning Range                        |

| LC           | Inductor-Capacitor                            |

| PDN          | Pull-Down Network                             |

| PLL          | Phase Locked Loop                             |

| PN           | Phase Noise                                   |

| PUN          | Pull-Up Network                               |

| RFIC         | Radio Frequency Integrated Circuits           |

| RO           | Ring Oscillator                               |

| SERO         | Single-Ended Ring Oscillator                  |

| SESLRO       | Single-Ended Split-Load Ring Oscillator       |

| STSCL        | Subthreshold Source Coupled Logic             |

| TG           | Transmission Gate                             |

| TSON         | Transistor Stuck-ON                           |

| TSV          | Through Silicon Via                           |

| VCO          | Voltage Controlled Oscillator                 |

# **List of Symbols**

| Symbol                  | Description                                     |

|-------------------------|-------------------------------------------------|

| H(s)                    | Transfer function of feedback system            |

| fvco                    | Frequency of VCO                                |

| fosc                    | Oscillation frequency                           |

| fo                      | Center or operating frequency                   |

| $\Delta f$              | Offset frequency                                |

| Kvco                    | Gain of VCO                                     |

| V <sub>ctrl</sub>       | Control voltage                                 |

| $\omega_{osc}$          | Oscillation frequency in radian                 |

| φ                       | Arbitrary phase reference                       |

| α                       | Switching factor                                |

| $C_L$                   | Parasitic load capacitance                      |

| V <sub>DD</sub>         | Supply voltage                                  |

| V <sub>bias</sub>       | Gate bias voltage of load transistor in SESLRO  |

| <i>t<sub>dHL</sub></i>  | Propagation delay during high to low transition |

| <i>t</i> <sub>dLH</sub> | Propagation delay during low to high transition |

| λ                       | Channel length modulation of MOSFET             |

| Ν                       | Number of stages in ring oscillator             |

| $W_R$                   | PMOS to NMOS width ratio                        |

# **Chapter 1**

# Introduction

## 1.1 Background

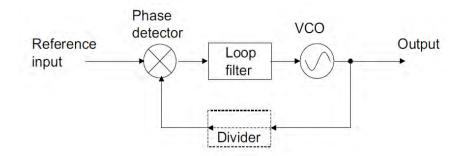

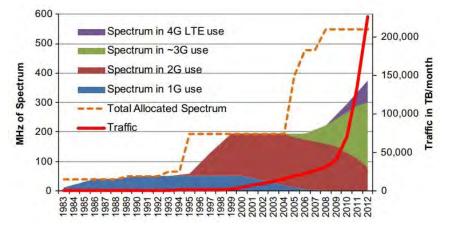

Oscillators represent one of the fundamental blocks in electronic systems that are employed for system-controlling operations such as clock generation, frequency synthesis and frequency translation [1]. Recent growth in wireless communication has demanded application-specific research to develop high quality phase locked loop (PLL) circuits which is an essential component in the radio frequency integrated circuits (RFICs). One of the driving blocks of the PLL segment is the voltage controlled oscillator (VCO) which is associated with signal processing tasks in the locked loop, mainly in frequency selection of the received signal. The block diagram of a typical PLL is shown in Fig. 1.1. An ideal VCO generates a signal whose frequency is a linear function of a controlled input voltage and its main characteristics in a PLL circuit include a wide tuning range to utilize maximum frequency spectrum in the communication channel [2] and a high operating-point to support increasing carrier frequency (in gigahertz range) [3]. Figure 1.2 shows the spectral growth for cellular communication in the United States of America (USA) over a span of 29 years due to the increase in traffic. In 2021, spectral occupancy has reached above the 21 GHz band.

Fig. 1.1: Block diagram of PLL

Fig 1.2: Spectrum growth versus traffic growth [2]

The current trend of VCO design categorizes it into two architectures: (i) inductorcapacitor (LC) oscillator and (ii) ring oscillator (RO) [4]. Compared to LC oscillators, RO takes smaller chip area and provides a larger tuning range at the cost of higher power consumption and phase noise (PN). The RO can be further classified into single-ended (SERO) and differential structures. With reduced cost due to smaller die area, improved utilization of the frequency spectrum due to wide tuning and easy integration, RO has proven to be a popular choice for the design of VCOs.

On the other hand, with aggressive scaling of semiconductor devices and higher circuit complexity, possibility of occurrence of predominant error-inducing circuit events like transistor stuck-on (TSON) faults increases [5]. A TSON fault is a permanent fault that may occur due to shorted connection or a voltage spike at the drain terminal causing the device to reach its breakdown condition. Such a fault always generates errors when the failing device is exercised. Therefore, testing of integrated circuits is a fundamental task to ensure high manufacturing yield.

### **1.2** Motivation of the Thesis

The study of RO is still being widely researched and studies on various architectures in literature reveal that a significant trade-off frequently exists between power overhead and operating-point. Therefore, there is a requisite to further investigate oscillator structures which provide wide flexible tuning with sensitivity to controlling parameters while maintaining a cap on power penalties.

Additionally, conventional logic method for TSON fault detection renders unreliable as it fails to detect the ambiguous logic level occurring at the output of static complementary metal-oxide semiconductor (CMOS) circuit. The alternative current measurement method typically involve device-heavy compound circuitry with high area overhead and limited functionality in sub-micron domain where fault current becomes difficult to distinguish from increased leakage current. Although ROs have been previously used to detect through-silicon-via (TSV) faults in 3D stacked ICs, their employment is logistically burdensome. Hence, there remains a scope to develop a homogeneous leakage-tolerant and area-efficient TSON detection scheme for CMOS circuits based on ROs.

## **1.3** Objectives of the Thesis

The objectives of this work are the following:

- 1. To devise a three-stage single-ended split-load ring oscillator (SESLRO) with multimode tuning leading to regulation of oscillator sensitivity.

- To propose two area-efficient reliable SESLRO based testing schemes which support a wide range of supply rails for accelerated TSON fault detection in submicron CMOS architectures.

- To develop a homogeneous leakage-tolerant TSON sensing method which achieves functionality in high leakage deep submicron regime with adaptable threshold regulation.

In brief, the aim of this thesis is to develop a multimode split-load ring oscillator architecture that will significantly curtail the circuit area and cost of TSON testing methods, support increased detection reliability, and help overcome the limitations of time-consuming quiescent current measurement approaches, making them compatible with leakage-heavy regimes.

## **1.4** Thesis Organization

The overall thesis is organized into five chapters. A brief abstract of the succeeding chapters are given below.

**Chapter 1** presents the background and motivation behind this research work. Additionally, the objectives of the thesis with specific aims are mentioned.

**Chapter 2** briefly provides a review of the theory of voltage controlled oscillators including VCO specifications and categories like LC and ring oscillators. Then, literature study is provided for single-ended ring oscillators and their adaptations. Finally, issues related with operating-point models necessary for oscillator design are addressed.

**Chapter 3** demonstrates the development of the proposed multimode single-ended splitload ring oscillator architecture with description of the simulation environment. Additionally, simulation results and analysis are presented in terms of frequency-voltage characteristics and fine tuning frequency response. Finally, the use of an empirical model of VCO operating-point is briefly described.

**Chapter 4** initially discusses conventional fault detection methods with regard to error inducing events like TSON faults. After that, it introduces the proposed methodology of fault-testing schemes based on SEROs. Simulation results and analysis are then provided for conventional and proposed SERO-fault detecting architectures with focus on leakage tolerant TSON fault detection, adaptable threshold regulation and built-in current sensor performances. Finally, the scheme is validated by making comparison with testing methods in literature.

**Chapter 5** finally concludes the outcome of this work providing insight for the scope of future work.

# Chapter 2

# **Review of Voltage Controlled Oscillators**

This chapter briefly provides a review of the theory of voltage controlled oscillators including VCO specifications and categories like LC and ring oscillators. Then, literature study is provided for single-ended ring oscillators and their adaptations. Finally, issues related with operating-point models necessary for oscillator design are addressed.

## 2.1 Fundamentals of VCO Operation

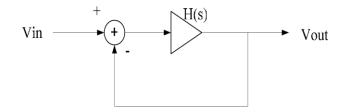

A simple oscillator produces a periodic output, usually a voltage. So how can a circuit oscillate? Consider a feedback system in Figure 2.1 with transfer function H(s). In order for steady oscillation to occur, the circuit must satisfy with Barkhausen criteria:

$$|\mathrm{H}(\mathrm{s})| \ge 1 \tag{2.1}$$

$$\angle H(s) = 180^{\circ}$$

(2.2)

These conditions are necessary but may not be sufficient to ensure oscillation [6]. Usually the loop gain of the system is twice to three times the required value [7].

Fig. 2.1: Simple feedback system

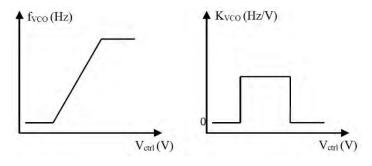

The VCO is a useful circuit because its oscillation frequency can be set to a desired value. The governing equation for a VCO is given in (2.3), where  $f_0$  is the center frequency (operating-point), K<sub>VCO</sub> is the gain of the VCO that controls how much a change in the control voltage will change the VCO's frequency. V<sub>ctrl</sub> is the input voltage to the VCO that sets it to the desired operating-point. The ideal relation of oscillating frequency and gain with the control voltage is shown in Fig. 2.2.

$$f_{VCO} = f_O + K_{VCO} V_{ctrl}$$

(2.3)

CMOS oscillators are typically implemented as ring oscillators or LC oscillators, though there are many other types of oscillators. One advantage of ring and LC oscillators is that they can be easily modified to be able to change the operating-point for a given control voltage, thus making them prime candidates for VCOs.

Fig. 2.2: VCO frequency transfer function [4]

## 2.2 Important VCO Specifications

When choosing a VCO architecture and topology, there are many important characteristics which must be taken into account. The relative importance of these characteristics usually depends on the target application. The characteristics can be placed into different categories. In the noise category, there are jitter, phase noise (PN) and figure of merit (FoM). In the frequency category, there are tuning range, the maximum operating-point and the effect of process and temperature variations on the operating-point. In the power category, there are static and dynamic power consumption. Finally in the manufacturing category: ease of integration with digital CMOS circuitry, and again, the effect of process variations.

#### 2.2.1 Phase Noise and Jitter

A vital design concern in VCOs is the PN in frequency domain, corresponding to jitter in the time domain. Phase noise is defined as the noise that is associated with phase fluctuations in the oscillating signal. The output of an ideal sinusoidal oscillator is of the form given in (2.4) where A is the amplitude,  $f_{VCO}$  is the oscillation frequency and  $\varphi$  is an arbitrary phase reference.

$$V_{out}(t) = A \cdot \cos(2\pi f_{VCO}t + \phi)$$

(2.4)

However, the output of a practical oscillator will be of the form given in (2.5), where A(t) and f(t) are now functions of time due to internal and external noise sources.

$$V_{out}(t) = A(t) \cdot \cos(2\pi f_{VCO}t + \varphi(t))$$

(2.5)

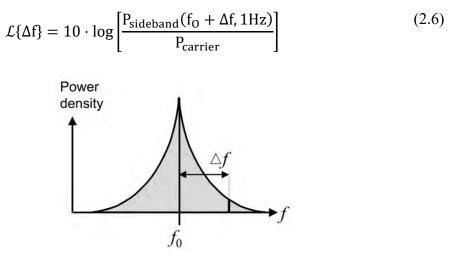

The PN is observed as a noise spectrum in the frequency domain, spreading out in either side of the oscillation frequency as sidebands as shown in Fig. 2.3. The single sideband (SSB) phase noise is measured in dBc/Hz at a given frequency offset (usually 1MHz) from the center or operating frequency of oscillation by equation (2.6) [4].

Fig. 2.3: Illustration of Phase Noise [4]

If the VCO is used in a wireless application, the phase noise can cause adjacent channels to be down-converted into the desired signal band. If the VCO is used to sample data, the jitter will affect the sample point and could degrade the signal-to-noise ratio (SNR).

#### 2.2.2 Figure of Merit (FoM)

The performance of VCOs is difficult to compare as they feature different operatingpoints, power consumption and phase noise over offset frequency. A widely accepted figure of merit has been introduced in [8]:

FoM = PN{

$$\Delta f$$

} - 20 log $\left(\frac{f_{VCO}}{\Delta f}\right)$  + 10 log $\left(\frac{P_{dc}}{1mW}\right)$  - 20 log $\left(\frac{FTR}{10}\right)$  (2.7)

where,  $PN{\Delta f}$  is the single sideband PN at offset frequency  $\Delta f$  from oscillation frequency  $f_{VCO}$ ,  $P_{dc}$  is the supply power and FTR is the frequency tuning range. The performance of a VCO is regarded to be better with a more negative value or higher absolute value of the FoM.

#### 2.2.3 Characteristics of Operating-Point

The characteristics related to the operating-point of a VCO are the tuning range, the maximum operating-point and the predictability of the operating-point over process and temperature variations. The tuning range of a VCO is the range within which the operating-point can be regulated for stable operation. For example, if the operating-point of a VCO can be varied from 1.8 GHZ to 2.0 GHz, it would have a tuning range of 0.2 GHz (or 10.5% with respect to the midpoint of the range). The tuning range can be important for two reasons. First, if the VCO is to be used in a system which has a large possible range of incoming frequencies, the tuning range should encompass them. This might occur in a chip which is designed to work with multiple standards. The second reason tuning range is important is related to the predictability of the VCO i.e. how close the actual operating-point will be with respect to the designed specification, as it can vary substantially due to process variations. Therefore, if the operating-point can vary substantially, a large tuning range is necessary so that the VCO will oscillate in the desired frequency range.

The maximum attainable operating-point of a VCO architecture is also important in high speed systems. As internet traffic increases, it is desirable to increase the serial data rate. Therefore, high-speed VCOs are needed for data recovery circuits.

#### **2.2.4 Power Consumption**

Another important characteristic of VCO circuits is the power consumption. The dynamic power of a CMOS circuit is directly related to the frequency as per (2.8) where  $\alpha$  is the switching factor, C<sub>L</sub> is the parasitic load capacitance and V<sub>DD</sub> is the supply voltage. Switching factor or switching activity is the measurement of signal value change in terms of probability and switching density.

Dynamic power =

$$\alpha C_L V_{DD}^2 f_{VCO}$$

(2.8)

Another major concern of power consumption is the static/leakage power of a digital circuit. The static power equation is given by (2.9) where  $I_{\text{Leakage}}$  is the steady state leakage current of the circuit. While static power remains relatively low in digital circuits, it is a major concern along with static power in analog circuits.

Static power =

$$I_{\text{Leakage}} V_{\text{DD}}$$

(2.9)

#### 2.2.5 Manufacturability

To reduce overall system cost and complexity, it is often desired to design an entire system, including analog and digital circuitry, on a single chip. Therefore, the ease with which the VCO can be integrated with other circuits is important. For example, the digital circuitry can create substrate and supply noise, so it is important that the VCO be able to reject this noise. Also, the physical size of the VCO is important, as a larger VCO will correspond to a larger die size, which will correspond to a higher cost.

#### 2.3 LC-based Oscillator

A general LC-VCO consists of a passive LC resonance tank and an active element to compensate for the losses of the resonator. The active element is constructed as an amplifier which can be configured in single-stage or differential mode, the latter being more popular [9]. The capacitor, which is dependent on the input voltage, is associated with tuning the oscillation of the circuit and the frequency of oscillation is given by

$$\omega_{\rm c} = \frac{1}{\sqrt{\rm LC}} \tag{2.10}$$

The inductor in LC oscillators has allowed the attainment of low levels of PN and power consumption over the years, but with several limitations when implemented with standard complementary metal-oxide-semiconductor (CMOS) processes [10]. It is very difficult to obtain a good quality factor (Q) for the inductor which is essential in determining the PN contributions. Quality factor of an inductor is defined as the ratio of its reactance to resistance for a given frequency and indicates the efficiency. Although inductance and resistance are constant at low frequencies, for high frequency, the Q degrades due to the ohmic loss of the spiral inductors [11].

## 2.4 Ring Oscillator (RO)

A ring oscillator consists of a chain of inverting amplifiers, or delay stages, in a ring structure where the output is fed back into the input. Its basic operation relies on the principle of propagation delay where the oscillating signal passes twice through the chain of a RO. To achieve oscillation, the ring must provide a phase shift of  $2\pi$  and have unity voltage gain at the frequency of oscillation. For a given structure with N number of stages, each delay stage must provide a phase shift of  $\pi/N$  and the remaining phase shift of  $\pi$  is provided by the DC inversion. If the propagation delay of a single stage is defined as  $t_{pd}$ , the total delay can be approximated as  $2Nt_{pd}$ . Therefore, the frequency of oscillation  $f_{osc}$  of the total RO is given by the following equation [12]:

$$f_{\rm osc} = \frac{1}{2Nt_{\rm pd}} \tag{2.11}$$

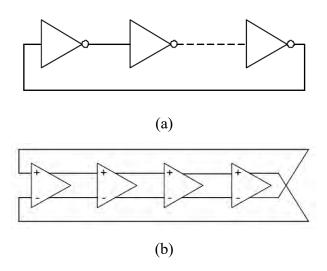

Depending on the design of the delay stage, the RO topology can be categorized into two types: (i) single ended ring oscillator (SERO) and (ii) differential ring oscillator (DRO) [13]. The SERO topology consists of a chain of odd number of inverters, whereas the DRO topology can have an odd or even number of differential amplifiers. The basic structure is shown in Fig. 2.4.

Fig. 2.4: RO with (a) single-ended, and (b) differential delay stages [14]

Based on the output voltage swing, the output of SERO compared to DRO is always saturated i.e. the output voltage always reaches the supply rail. As a result, the SERO shows better PN performance and power consumption compared to DRO for the same number of delay stages. The differential structure also adds complexity and space requirement to design compared to the single-ended structure. The use of SERO over DRO, therefore, is a better choice for vast number of applications.

### 2.5 RO vs. LC-VCO

When choosing a VCO architecture, one must determine the specifications related to the VCO characteristics described above and then decide whether a ring or LC VCO would better suit the application, as they each have their strengths and weaknesses.

#### 2.5.1 Phase Noise

Phase noise is often the most important specification that must be met when choosing a VCO architecture. If excellent phase noise characteristics are required, an LC VCO will usually be necessary. Two of the main parameters related to phase noise are the attainable quality factor (Q) of the oscillator and the oscillator's ability to reject supply and substrate noise. The quality factor, Q, of an oscillator is related to the loss of the circuit, and a common definition is given in (2.12) [14].

$$Q = 2\pi \frac{\text{energy stored}}{\text{energy dissipated/cycle}}$$

(2.12)

An LC oscillator will have a higher Q than RO. This is because in an ideal LC oscillator, the energy will transfer between the inductive and capacitance elements with no loss, resulting in an infinite Q. In a practical LC oscillator, there are losses associated with each element, such as series resistance losses in the inductor, but energy still switches between the two reactive elements. However, in a ring oscillator, the energy is stored in the equivalent capacitance of the next stage, and the energy is fully charged and then discharged every cycle. As shown by the denominator of (2.12), this characteristic substantially reduces the Q. Typical Q values for a ring oscillator are about 1.3 to 1.4 [15]. The Q of an LC tank can be about an order of magnitude higher [16].

A second reason why ROs have poor PN performance is observed by analyzing the oscillator output. The effect of injected noise on phase depends on the point in the cycle at which the noise is injected [17]. This is shown in Fig. 2.5. When the impulse is during the peak, there is a shift in the amplitude of the output signal while the phase remains the same. When the impulse is during the transition period, there is a phase shift that persists over time. This is a problem in ring VCOs because the device noise is the highest during transitions, which is the worst case scenario in terms of PN performance.

Fig. 2.5: Effect of noise impulse on oscillator output during peak and transition [14]

#### 2.5.2 Maximum Operating-Point

An LC tank has higher maximum attainable operating-point compared to a RO. As shown in (2.10), the oscillation frequency of an LC tank is inversely proportional to the square root of inductor and capacitor. The value of these parameters can be made extremely low, and hence, the frequency of the oscillator very high. The maximum operating-point of a CMOS RO is much lower.

#### 2.5.3 Tuning Range

A high tuning range is often required, whether to account for process variations or to work with multiple standards. A RO should be utilized to obtain high frequency tuning range. From (2.11), it can be seen that the RO frequency depends on the number of stages N and the propagation delay of each stage. A more detailed expression of the operating-point will be discussed in section 2.8 which will show that there are numerous parameters which can control the frequency of a RO. Meanwhile, the only parameter that is typically varied in a monolithic LC tank is the capacitance of the varactor. This tends to result in a lower tuning range percentage compared to RO [18].

#### 2.5.4 **Power Consumption**

The use of inductors in LC tanks results in a very high power demand by the oscillator compared to a RO. The leakage power of a CMOS RO is very low while the dynamic power exists only for the time period when both PMOS and NMOS transistor networks are ON to create a shorted path from supply to ground.

#### 2.5.5 Manufacturability

There are two issues related to the manufacturability of the VCO. These are how easily the VCO can be integrated into a monolithic solution, and how much the center frequency will vary over process parameters. A RO is preferred over LC oscillator if die area is a large concern. Monolithic inductors can occupy a large area, which corresponds to higher cost [19]. However, the center frequency of a RO can also vary more than an LC tank due to process variations. Despite of this larger variation, ROs are still more likely to be used at the desired frequency because of their wide tuning range.

Table 2.1 summarizes the relative strengths of ROs and LC oscillators by marking  $\checkmark$  to show the oscillator with the superior performance.

|                   | Ring Oscillator | LC Oscillator |

|-------------------|-----------------|---------------|

| Phase Noise       |                 | $\checkmark$  |

| Maximum Frequency |                 | $\checkmark$  |

| Tuning Range      | $\checkmark$    |               |

| Power Consumption | $\checkmark$    |               |

| Manufacturability | $\checkmark$    |               |

Table 2.1: Summary of Ring vs. LC oscillator

## 2.6 CMOS Inverter-based Single-Ended RO (SERO)

A basic 3-stage CMOS inverter based RO is shown in Fig. 2.6 where the parasitic output capacitances are included. It can be said on the basis of inverter controlled operation, when the input of the first stage is rising, the output of the third stage will be falling. Since the falling output is fed back to the input, it changes the input to falling, but not immediately because of the propagation delay incurred at every stage. After this first half cycle, the opposite scenario is realized when the input starts falling and in this way an oscillation is generated.

Fig. 2.6: Conventional SERO

The oscillation of a RO can be analyzed with respect to gain and transfer function of each stage. A typical RO consists of multiple gain stages within the loop. The minimum gain required in each stage can be easily derived from the transfer function of each stage and the Barkhausen criteria. The transfer function of each stage in the conventional SERO is given by (2.13), where A<sub>0</sub> is the minimum gain required per stage [7]. Neglecting the effect of the gate-drain overlap capacitance, the loop gain of the system is then obtained as in (2.14).

$$A(s) = -\frac{A_0}{1 + \frac{s}{\omega_0}}$$

(2.13)

$$H(s) = -\frac{A_0^3}{\left(1 + \frac{s}{\omega_0}\right)^3}$$

(2.14)

The system oscillates when the total phase shift equals 180°, where each stage contributes 60°. The frequency at which the oscillation occurs is given by:

$$\tan^{-1}\frac{\omega_{\rm osc}}{\omega_0} = 60^0 \tag{2.15}$$

Solving (2.15) for  $\omega_{osc}$ , the expression of the oscillating frequency obtained is:

$$\omega_{\rm osc} = \sqrt{3}\omega_0 \tag{2.16}$$

The minimum voltage gain per stage is then evaluated using the Barkhausen criteria in (2.17) where the magnitude of the loop gain at  $\omega_{osc}$  is equal to unity [7]. Using (2.16) and (2.17), the value of A<sub>0</sub> is approximately 2.

$$\frac{A_0^3}{\left[\sqrt{1^2 + \left(\frac{\omega_{\text{osc}}}{\omega_0}\right)^2}\right]^3} = 1$$

(2.17)

Therefore, a three stage RO can oscillate at  $\sqrt{3}\omega_0$ , where  $\omega_0$  is the 3-dB bandwidth of each stage, and requires a minimum gain of 2 per stage. Higher number of stage will result in a lower gain required per stage, but at the cost of lower frequency of oscillation.

## 2.7 Adaptations of Single-Ended Ring Oscillators

Several SERO architectures have been proposed over the years customized for specific applications, which can be divided into different categories based on their delay stage structure [20]. This section discusses their relative merits and compares their performances.

#### 2.7.1 Current Starved RO

A second conventional SERO topology suitable particularly for low power applications is the current starved VCO (CS-VCO). It consists of the basic inverter stages along with PMOS current sources and NMOS current sinks which are biased at the desired voltage. This bias voltage can be generated by a separate biasing circuit. Various CS architectures have been presented [20-24], each utilizing a different biasing technique. The single delay stage structure of a traditional CS-VCO is shown in Fig. 2.7 which serves as the unit block of cascaded architectures. Transistors M5-M7 form the bias circuit and the frequency is tuned by varying the gate voltage V<sub>ctrl</sub> of M7. Current mirror technique is used to provide the current generated by the bias circuit to all the stages. As the resulting current in the circuit is directly controlled by a separate voltage, it can be limited to a desired value to ensure low power consumption. Additional current source and current sink sections may also be employed to increase the equivalent resistance and further regulate the current. In this way, the circuit is starved of current and better management of power can be provided. However, the decrease in current eventually has a detrimental effect on frequency. Moreover, the topology also suffers from low and nonlinear tuning range.

Fig. 2.7: CS-VCO delay stage serving as the unit block of multistage structure [20]

The propagation delay of CS-VCO is derived in [25] and observed to be proportional to  $V_{DD}$ . Hence, compared to the basic inverter based RO, the frequency of CS topology is inversely proportional to  $V_{DD}$ . The CS architecture also faces a drawback in terms of non-linearity. The linear variation of bias current with respect to the control voltage depends on the region of operation of M5. Therefore in order to achieve a linear relation between  $f_{osc}$  and  $V_{ctrl}$ , M5 should be operated in the saturation region until the control voltage reaches  $V_{DD}$ . Rajahari et. al. [26] have provided a minimum width ratio for M6 and M5 to ensure that this condition is fulfilled. The equation is given by:

$$\frac{W_{M6}}{W_{M5}} = \frac{K_{M6}}{K_{M5}} \left[ \left( \frac{V_{DD} - V_t}{V_{bias(min)} - V_{DD} - V_t} \right)^2 - 1 \right]$$

(2.18)

where  $K = \frac{\mu C_{ox}}{L}$  and  $V_{bias(min)}$  is the minimum drain voltage of M6.

Several other CS-SEROs are presented in [27] which simplify the unit block to improve the area overhead of the circuit and analyze the performance in terms of key features. Comparison with existing circuit structures demonstrate significant trade-offs between frequency and power overhead, and between phase-noise and frequency bandwidth. While power-delay product (PDP) addresses the frequency-power trade-off, a new proposed parameter in [27] known as the phase-noise-bandwidth product (PNBP) addresses the trade-off between phase-noise performance and frequency tuning range.

#### 2.7.2 Negative-Skewed RO

Lee et. al. [28] have proposed a modified inverter based RO where the input of the PMOS device has a negative delay element placed in front of it. As a result, when the output of a stage changes from low to high, the PMOS of that stage turns on before the NMOS turns off. This speeds up the operation of the RO and achieves a higher maximum frequency compared to that of the conventional structure. Since the topology supports a larger period of time when both MOSFETs are on, there is an increased static current which raises the power consumption of this architecture. Additionally, the control of the delay demands deliberation because if it becomes significantly higher, the speed of the circuit eventually degrades. Unlike the basic CMOS structure, the input of the PMOS in the structure is not derived from adjacent cell outputs. For example, the PMOS of stage 4 is driven by the output of stage 1. The output of stages 1 and 3 are similar. So when input of stage 1 changes from high to low, output of stages 1 and 3 are rising. Since the output of stage 1 increases before that of stage 3 due to propagation delay, the PMOS of stage 4 is switched off prior to NMOS turn-on. Negative skewed scheme can also be implemented with NMOS gate inputs. To satisfy the requirements, the minimum number of stages for a negative skewed RO is determined to be 5. An example of a five-stage negative skewed VCO is demonstrated in Fig. 2.8 where the circuit offers a 62% higher operating frequency compared to the design point of basic SERO.

Fig. 2.8: Five-stage RO using negative skewed scheme [28]

#### 2.7.3 Transmission-Gate (TG) RO

Oscillators with a wide tuning range can fulfill a fundamental need often required in the communication world. Different methods exist to increase the range of frequency tuning, as mentioned in [29], but at the cost of greater power consumption and chip area. To tackle these challenges, Sheu et. al. [29] described a design of wide tuning range ring oscillator using TG at the output of each stage. The tuning of the frequency is achieved by varying the parasitic load capacitance through the control voltage V<sub>etrl</sub>, which is applied at the NMOS of the TG as shown in Fig. 2.9. Summation of the drive voltages being applied to NMOS and PMOS of the TG should be equal to the supply voltage. Compared to the transmission gate based design proposed in [30], the circuit provides symmetric paths for both charging and discharging cycles, eliminating the variation in duty cycle in response to the regulation of the TG scheme gives a wider and linear tuning range.

Fig. 2.9: Three-stage transmission gate supported RO [29]

#### 2.7.4 RO using Bulk Voltage Effect

The adjustment of supply and bias voltages have a direct impact on the power consumption of electronic circuits. Therefore, in order to operate in low voltages, one of the adopted techniques could be reducing the threshold voltage which can be achieved by applying a direct biasing voltage to the bulk terminal of MOSFETs. A quadrature output SERO is proposed in [32] which exploits the bulk voltage effect where a control voltage is applied to the bulk terminals of both PMOS and NMOS of the inverter circuit to manipulate the threshold voltages. This provides the best result in terms of low voltage requirements and achievement of a suitable FoM compared to a structure which uses biasing either one of the MOSFETs.

#### 2.7.5 Symmetrical Even-phase Outputs SERO

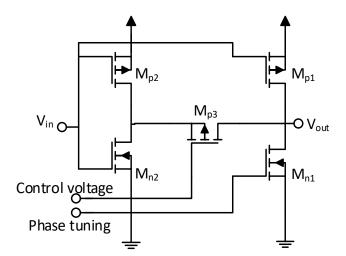

As mentioned before, the conventional SERO cannot provide symmetrical even-phase outputs since they consist of an odd number of inverting stages. The circuit proposed in [33] provides this feature with a four-stage SERO and its circuit is shown in Fig. 2.10. The transistor  $M_{n1}$  provides the required phase shift to get the desired quadrature output. Transistors M<sub>n1</sub> and M<sub>p1</sub> set the gain of the VCO and the frequency tuning is achieved by the control voltage driving the device M<sub>p3</sub>. By increasing the control voltage, the operating frequency of the circuit decreases i.e. the circuit has a negative linear relation between the control voltage and frequency. By replacing the PMOS M<sub>p3</sub> with an NMOS M<sub>n3</sub>, a positive linear relation can be obtained between the frequency and the control voltage. A modified circuit involving additional NMOS and PMOS switching transistors for a band switch technique is also proposed by the author which can operate at two different frequency modes (low and high) with the help of a control switch. Due to the band switch technique and full-swing characteristics, the circuit improves noise performance and signal to noise ratio (SNR) with a wide tuning range. SNR is the ratio of signal power to noise power and a high SNR means better noise performance i.e. low noise in the output signal. The topology is suggested to be beneficial in the field of consumer electronics, communication and medical appliances.

Fig. 2.10: Delay cell for symmetrical even-phase output SERO [33]

#### 2.7.6 NMOS-sink CS-VCO

Conventional CS-VCO uses both current sources and sinks where bias voltages, as mention earlier, are provided through current mirror circuits. Suhas et. al. in [34] adapts the basic CS circuit by using only the NMOS current sinks in a three-stage CS-RO. The control voltage is directly applied to the first NMOS sink instead of using current mirrors. The renovated topology simplifies the existing design and improves power consumption and area penalties significantly providing wide and linear frequency tuning. Keeping the control voltage fixed, the frequency is rather tuned by varying the supply voltage which contributes to the linear frequency versus voltage curve due to the smaller drain-source capacitance compared to gate-source capacitance. In relation to multiple reported oscillators in 180nm technology, the proposed circuit is observed to demand a low power rating of 0.598mW with 176.4% tuning range which was achieved when control voltage was fixed at 2.5V and the supply voltage was varied from 0.6V-2.5V. The properties of the oscillator is appropriate for microwave applications.

#### 2.7.7 RO using STSCL Load Device

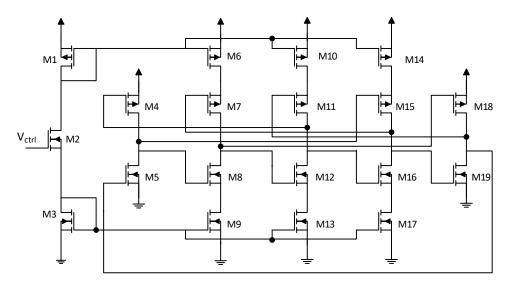

Goyal et. al. [35] describes a three-stage RO which implements a sub-threshold source coupled logic (STSCL) PMOS load device. STSCL allows MOS gates to operate with ultra-low voltages by placing them in the sub-threshold region where the current density is very low. As a result, the power dissipation is reduced and the circuit can be used for low power applications. However, it leads to the requirement of a scaled-down supply voltage which could result in a degradation of output voltage swing. To overcome this problem, the PMOS load is converted to a high resistance load by shorting bulk and drain terminals together. Additionally, the circuit uses a pseudo NMOS architecture [36] with a single NMOS sink. The bias voltages are provided by a current mirror technique as presented in Fig. 2.11. Drawbacks of this design involve a reduced frequency of oscillation and a subsequent curtailed tuning range. With a supply rail of 1V in 180nm technology, the STSCL-based design requires a power of only 6.75uW at 123.9MHz compared to the figure of 206uW at 1220.50MHz as achieved by a conventional CS-VCO. Such low power ROs are suitable for biomedical electronics.

Fig. 2.11: Multistage oscillator with source-coupled logic load [35]

#### 2.7.8 Hybrid SEROs

Hybrid ring oscillators entail the combination of basic inverter stages, CS schemes and negative skewed techniques which can be associated to combine their benefits and compensate for their limitations while making performance trade-offs.

#### 2.7.8.1 Combined RO

It was described in section I that the frequency of inverter based ROs is proportional to the supply rail and that of CS-VCOs has a reciprocal relationship with the supply voltage. Therefore, a variation in the supply voltage due to noise may alter the frequency of oscillation affecting the stability of the transceiver. In order to improve the frequency stability in this regard, multiple (3, 5 and 7) stages are combined in a hybrid oscillator which includes both of the aforementioned oscillator units [37]. The design ultimately consists of basic CMOS inverters for the odd stages and CS-inverters for the even stages. It leads to an improvement of reliability where frequency deviation of less than 2% was obtained with respect to variation in the power supply. The major drawback of the combined structure is the degradation of maximum oscillation frequency.

#### 2.7.8.2 CS-Skewed RO

Nayak et. al. in [38] adapts the CS and the negative skewed schemes simultaneously to propose the CS Skewed RO. Two seven-stage ROs were presented where one chain uses NMOS skewed units while the other uses PMOS skewed blocks. The structure has to make a calculated trade-off between frequency and power consumption, as the used chains have the possibility of adversely affecting these features. The authors measure a crucial parameter, the power delay product (PDP) of the circuit. PDP is the product of the power consumption and propagation delay of the circuit which is used in to analyze circuit performance in terms of energy efficiency. It measures the energy consumed by the circuit per switching event. The result shows more than 30 and 50% improvement in terms of PDP for NMOS skewed and PMOS skewed respectively, compared to the benchmark of individual CS and skewed topologies. Good performance was also observed against variations in operating conditions like temperature and supply voltage. The structure is useful in IoT system applications.

#### 2.7.8.3 Combined-Skewed RO

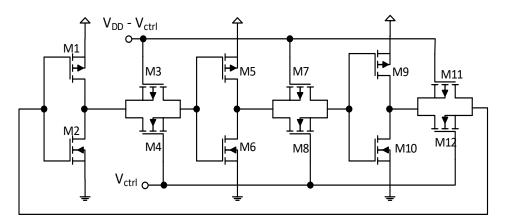

Simultaneous use of basic inverters, CS units and skewed stages can lead to a combined skewed RO as described in [39]. A five-stage RO is proposed, as presented in Fig. 2.12, where the front and the ultimate stage consists of the inverter units, the three stages in the middle consist of CS inverters, while gates of all the PMOS loads are negative skewed. The resulting circuit, in comparison with the combined RO structure, improves the frequency of oscillation significantly (3.31GHz compared to 960MHz) and also maintains good frequency stability with respect to supply voltage and temperature variations.

Fig. 2.12: Multistage skewed RO using three types of units [39]

#### 2.7.9 LC based SEROs

Although LC tuned oscillators and ROs belong to different categories offering unique advantages, inductors and capacitors can also be implemented in ring structures to attain their benefits. Ring architectures which also include load tanks and passive components are discussed in this section.

#### 2.7.9.1 RO using Inductor Peaking

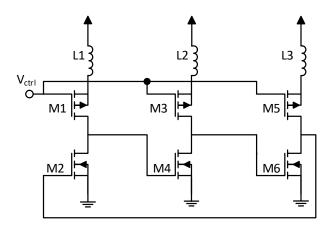

Four three-stage ROs with peaking inductors are described in [40] where the circuits employ inductive loads along with PMOS loads in each of the delay stages of a pseudo NMOS RO, as shown in Fig. 2.13. The modification is exploited to obtain an ultra-wide tuning range and good PN performance. It leads to the realization of two VCOs which show a tuning range of 189% and 196% along with 195.3 and 194.7 FoMs respectively. While the size of the inductor influences the frequency tuning, the quality factor plays the dominating role on the determination of PN. Additionally, the circuit is observed to give a significantly higher power consumption compared to other works.

Fig. 2.13: Three-stage RO using peaking inductors [40]

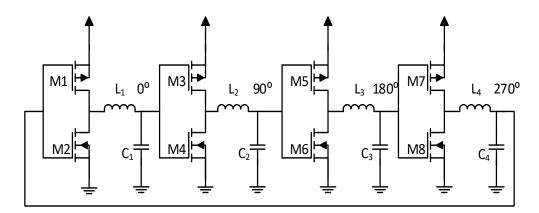

#### 2.7.9.2 Quadrature RO using Series LC Tank

A four-stage RO with series LC tank at the output node of the individual stages is described in [41]. Each inverter stage with the series LC tank produces a 90 degree phase shift, which results in the accumulation of the required phase shift for oscillation. The circuit, therefore, provides symmetrical even-phase outputs. With the inclusion of low-Q inductors, the chip area and PN performance are regulated while maintaining a good

tuning range. The frequency tuning of the topology is controlled by the capacitors in the output tanks ( $C_1$ - $C_4$ ) as shown in Fig. 2.14.

Fig. 2.14: Quadrature RO using series LC tanks [41]

#### 2.7.10 Summary

The choice of an SERO architecture for a specific application is dependent on its performance and so detailed analysis is important. Study demonstrates that few moderately modified SEROs can enhance the performance in terms of a single feature while degrading another characteristic. Hybrid oscillators were observed to improve the operating-point stability and LC based ring oscillators improved noise performance, operating-point and tuning range while sacrificing the performance in terms of power requirement.

# 2.8 Approximate Operating-Point Models

The expression of the operating-point in a RO is given by (2.11), which shows that the frequency is inversely proportional to the number of delay stages N and propagation delay  $t_{pd}$  at each stage. The propagation delay  $t_{pd}$  is an average of the high-to-low and low-to-high propagation delays,  $t_{dHL}$  and  $t_{dLH}$  respectively. Equation (2.11) can then be written as in (2.19).

$$f_{osc} = \frac{1}{N(t_{dHL} + t_{dLH})}$$

(2.19)

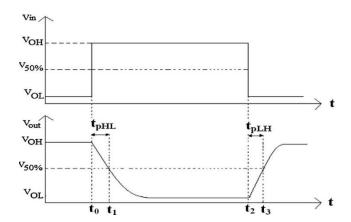

Therefore, in order to analyze and estimate the operating-point, it is essential to correctly model the propagation delays  $t_{dHL}$  and  $t_{dLH}$  [42]. Two conventional methods exist to determine an approximate delay equation, each modeling the CMOS inverter circuit differently. In the first method, the transistors are modeled as current sources with a constant current supply which charges and discharges the load capacitance  $C_L$  [43]. In the second method, the transistor is modelled as a resistor and an equivalent RC circuit is solved for the delay expression [44]. The point at which the delay is calculated can also vary and results in a similar equation with a different coefficient value. The propagation delay can be calculated when the output is at either 50%, 90% or 100% level of the supply voltage. Although the delay is calculated at the 50% level conventionally [45], as shown in Fig. 2.15, some equations mentioned in literature [14, 46] have considered the 90% and 100% levels.

Fig. 2.15: Propagation delay calculation at 50% level [45]

These analyses can lead to 5 different operating-point equations for a single circuit. Moreover, the equations are based on the assumption that the PMOS to NMOS width ratio,  $W_p/W_n$  is 2.

#### 2.8.1 Current Source (CS) Model and Delay at 50%

As mentioned before, one way to model the propagation delay is by assuming the transistors as current sources which charge and discharge the load capacitance. The charging and discharging current equations are then given by [42]:

$$C_{L} \int_{0}^{\frac{V_{DD}}{2}} dV_{out} = \int_{0}^{t_{dLH}} I_{p} dt \qquad (2.20)$$

$$C_{L} \int_{V_{DD}}^{\frac{V_{DD}}{2}} dV_{out} = -\int_{0}^{t_{dHL}} I_{n} dt \qquad (2.21)$$

where,  $I_n$  and  $I_p$  are saturation currents of NMOS and PMOS transistors, respectively. The propagation delays  $t_{dLH}$  and  $t_{dHL}$  are obtained as (2.22) and (2.23). Assuming the PMOS to NMOS width ratio  $W_p/W_n = 2$  and, hence,  $I_n = I_p = I_s$ , the resultant expression of operating-point is obtained in (2.23), where  $I_s$  is the current through each delay stage.

$$t_{dLH} = \frac{V_{DD}C_L}{2I_p}$$

(2.22)

$$t_{dHL} = \frac{V_{DD}C_L}{2I_n}$$

(2.23)

$$f_{\rm osc} = \frac{I_{\rm S}}{\rm NV_{\rm DD}C_{\rm L}}$$

(2.24)

### 2.8.2 CS Model and Delay at 90% Level

For the delay calculation at 90% level, the integral limits are changed from  $V_{DD}/2$  to 0.9 $V_{DD}$  and 0.1 $V_{DD}$  in (2.20) and (2.21), respectively. The two propagation delay expressions then obtained are given by (2.25) and (2.26). The resultant operating point expression is given by (2.27).

$$t_{dLH} = \frac{0.9V_{DD}C_L}{I_p}$$

(2.25)

$$t_{dHL} = \frac{0.9V_{DD}C_L}{I_n}$$

(2.26)

$$f_{osc} = \frac{I_S}{1.8NV_{DD}C_L}$$

(2.27)

#### 2.8.3 CS Model and Delay at 100% Level

For the 100% level, the delay is calculated when the output reaches the voltage rails,  $V_{DD}$  or 0. In a similar method as before, the integral limits are now from 0 to  $V_{DD}$  and  $V_{DD}$  to 0 in (2.20) and (2.21), respectively. The propagation delays then obtained are given by (2.28) and (2.29) which leads to the operating-point expression in (2.30). This is the most common equation in literature.

$$t_{dLH} = \frac{V_{DD}C_L}{I_p}$$

(2.28)

$$t_{dHL} = \frac{V_{DD}C_L}{I_n}$$

(2.29)

$$f_{osc} = \frac{I_S}{2NV_{DD}C_L}$$

(2.30)

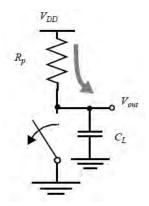

#### 2.8.4 RC Models

The inverter can also be modelled as an RC network to obtain the propagation delay. Suppose,  $C_L$  is being charged to a voltage  $V_{out}$  from supply voltage  $V_{DD}$  when  $V_{in} = 0$ , as shown in Fig. 2.16. The operation of the network is described by the following differential equation [47]:

$$C_{\rm L}\frac{dV_{\rm out}}{dt} + \frac{V_{\rm out} - V_{\rm in}}{R_{\rm p}} = 0$$

(2.31)

where,  $R_p$  is the equivalent PMOS resistance. The solution to the differential equation is given by:

$$V_{out} = \left(1 - e^{-\frac{t_{dLH}}{R_p C_L}}\right) V_{DD}$$

(2.32)

Fig. 2.16: RC model of CMOS inverter at  $V_{in} = 0$  [47]

For calculating delay at 50% voltage level,  $V_{out} = 0.5 V_{DD}$  and the expression of  $t_{dLH}$  obtained is given by (2.33). Similarly for the discharging scenario, the expression of  $t_{dHL}$  is given by (2.34), where  $R_n$  is the equivalent NMOS resistance.

$$t_{dLH} = \ln(2) R_p C_L \tag{2.33}$$

$$t_{dHL} = \ln(2) R_n C_L \tag{2.34}$$

The average on-resistances  $R_n$  and  $R_p$  can be calculated by integrating the I-V characteristic curves of the NMOS and PMOS, respectively, over the interval of interest. For example, for 50% delay calculation, the expression of  $R_p$  is given by (2.35) where  $\lambda$  is the channel length modulation constant for short channel devices. Assuming  $\lambda = 0$ , the approximate expressions of  $R_p$  and  $R_n$  are given by (3.36) and (2.37).

$$R_{p} = \frac{1}{-\frac{V_{DD}}{2}} \int_{V_{DD}}^{\frac{V_{DD}}{2}} \frac{V dV}{I_{p}(1 + \lambda V)}$$

$$\approx \frac{3V_{DD}}{4I_{p}} (1 - \frac{7}{9}\lambda V_{DD})$$

(2.35)

$$R_{p} = \frac{3V_{DD}}{4I_{p}}$$

(2.36)

$$R_n = \frac{3V_{DD}}{4I_n} \tag{2.37}$$

Substituting equations (2.36) and (2.37) in (2.33) and (2.34), the resulting expression of operating-point is given by (2.38) where  $I_s = I_n = I_p$ , assuming  $W_p/W_n = 2$ .

$$f_{\rm osc} = \frac{I_{\rm S}}{1.5\ln(2)\rm{NV}_{\rm DD}C_{\rm L}}$$

(2.38)

For calculating delay at 90% voltage level,  $V_{out} = 0.9V_{DD}$  in equation (2.32) and the delay expressions obtained are given by (2.39) and (2.40).

$$t_{dLH} = \ln(10) R_p C_L$$

(2.39)

$$t_{dHL} = \ln(10) R_n C_L \tag{2.40}$$

Following similar procedure, the resulting operating-point expression obtained is given by (2.41).

$$f_{osc} = \frac{I_{S}}{2\ln(10) \, \text{NV}_{\text{DD}} C_{L}}$$

(2.41)

Note that, using the RC model, the delay cannot be calculated at the 100% voltage level as the value of  $t_{dLH}$  from (2.32) evaluates to 0.

#### 2.8.5 Sources of Inaccuracy in Approximate Models

The equations discussed above for the operating-point of a RO are approximate equations with several assumptions where many details are neglected. Therefore, the equations are not very accurate. The following points mention the reasons of approximation and inaccuracy [42, 48]:

- i. The first order transistor equations are used which are not very accurate in the nanometer dimension.

- ii. The load capacitor of the transistor vary at different supply voltage and transistor regions.

- iii. The voltage swing is considered to be  $0 \rightarrow V_{DD}$  for the first method (integral method) which is not accurate. In practical, the integral limit is lower than  $V_{DD}$  and higher than 0.

- iv. The saturation currents of the transistors are considered in the equations. However, in the delay interval, the transistors may enter the linear region.

- v. The currents in the equations (2.20) and (2.21) are considered to be constant and got out of the integrals, whereas they are voltage dependent.

- vi. In the propagation delay equations, only the effect of one transistor is considered instead of both transistors.

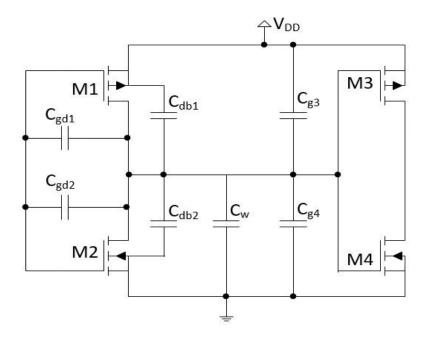

# 2.9 Modeling of Parasitic Load Capacitance

The oscillating frequency of an SERO is inversely proportional to the load capacitance of each stage, so it is important to analyze the different components which influence this parasitic load capacitance. Figure 2.17 shows a cascaded CMOS inverter pair and the various parasitic capacitances of the MOSFETs [47]. The total load capacitance of a conventional SERO at each stage is a summation of the following components: gate-drain capacitances ( $C_{gd1}$ ,  $C_{gd2}$ ), diffusion capacitances ( $C_{db1}$ ,  $C_{db2}$ ), gate capacitances of the load stage ( $C_{g3}$ ,  $C_{g4}$ ) and interconnect capacitance ( $C_w$ ). The expressions of these capacitances are given in Table 2.2. Table 2.3 defines the variables present in the expressions of these capacitor components.

Fig. 2.17: Components of parasitic capacitances in cascaded CMOS inverter

| Capacitance components | Expression                                  |

|------------------------|---------------------------------------------|

| C <sub>gd1</sub>       | $2C_{GDOp}W$                                |

| C <sub>gd2</sub>       | $2C_{GDOn}W$                                |

| C <sub>db1</sub>       | $K_{eqp}A_{Dp}C_J + K_{eqswp}P_{Dp}C_{JSW}$ |

| Cdb2                   | $K_{eqn}A_{Dn}C_J + K_{eqswn}P_{Dn}C_{JSW}$ |

| C <sub>g3</sub>        | $(C_{GDOp} + C_{GSOp})W_p + C_{OX}W_pL_p$   |

| Cg4                    | $(C_{GDOn} + C_{GSOn})W_n + C_{OX}W_nL_n$   |

| Cw                     | From extraction                             |

| CL                     | Σ                                           |

Table 2.2: Expressions of parasitic capacitance components

Table 2.3: Definition of variables in parasitic components

| Variable          | Definition                                                                                                                           |

|-------------------|--------------------------------------------------------------------------------------------------------------------------------------|

| C <sub>GDO</sub>  | Gate-drain overlap capacitance                                                                                                       |

| C <sub>GSO</sub>  | Gate-source overlap capacitance                                                                                                      |

| K <sub>eq</sub>   | Multiplication factor to relate the linearized capacitor value to the junction capacitance for bottom wall under zero bias condition |

| K <sub>eqsw</sub> | Multiplication factor to relate the linearized capacitor value to the junction capacitance for side-wall under zero bias condition   |

| AD                | Area of drain                                                                                                                        |

| P <sub>D</sub>    | Perimeter of drain area                                                                                                              |

| $C_{J}$           | Bottom junction capacitance                                                                                                          |

| C <sub>JSW</sub>  | Side-wall junction capacitance                                                                                                       |

| Cox               | Oxide capacitance                                                                                                                    |

# **Chapter 3**

# Multimode Single-Ended Split-Load Ring Oscillator

In this chapter, the development of the proposed multimode single-ended spit-load ring oscillator architecture is discussed with description of the simulation environment. Additionally, simulation results and analysis are presented in terms of frequency-voltage characteristics and fine tuning frequency response. Finally, the use of an empirical model of VCO operating-point is briefly described.

As discussed in the previous chapter, several SERO architectures have been proposed over the years customized for specific features such as low power consumption, low phase noise, wide tuning range or high operating frequency. It has been observed that transmission-gate and inductors have been used in the load section to increase frequency tuning range. However, the regulation of control voltage in the transmission-gate based oscillator remains a difficult design issue. On the other hand, the use of inductors results in high power penalty and affects the linearity of the frequency-voltage characteristics adversely. Hence, a modified SERO topology with split-load technique has been proposed in this work for wide tuning characteristic while maintaining a cap on power penalty.

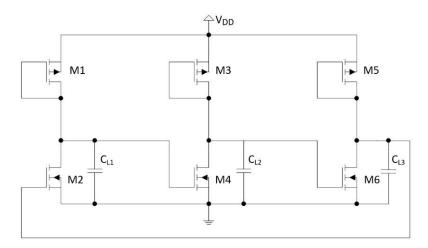

## **3.1 SERO with Active-Load**

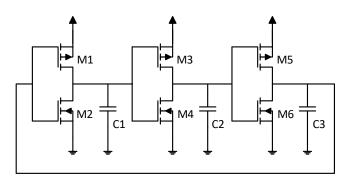

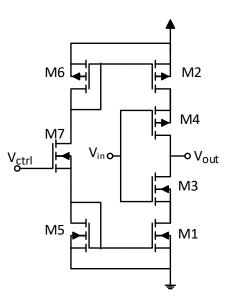

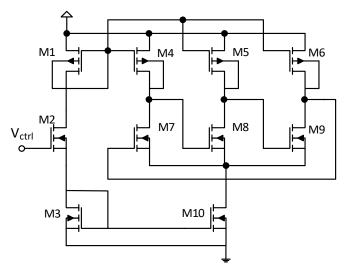

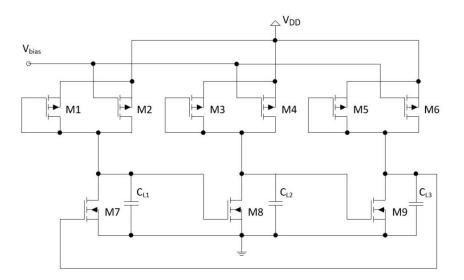

The proposed SERO circuit is developed by initially converting the CMOS inverter delay stage into an active-load inverter [36], where the PMOS is diode-connected and always operates in the saturation region. Diode-connected PMOS loads have been previously used in parallel symmetric loads arrangements in [20, 49, 50] to increase the oscillating frequency and improve the sinusoidal shape of the curve i.e. eliminate distortion at peaks. Transistors M1, M3 and M5 in Fig. 3.1 are the active loads of the circuit.

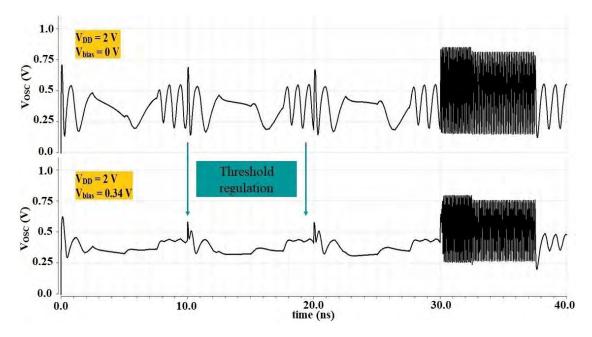

Fig. 3.1: SERO with active-load inverter