## DETECTION OF RECYCLED FIELD PROGRAMMABLE GATE ARRAYS USING CLUSTERING ALGORITHM

by TANVIR AHMAD TARIQUE 1017312012

## MASTER OF SCIENCE IN INFORMATION AND COMMUNICATION TECHNOLOGY (M.Sc. in ICT)

Institute of Information and Communication Technology (IICT) BANGLADESH UNIVERSITY OF ENGINEERING AND TECHNOLOGY (BUET) Dhaka, Bangladesh November 2022 The thesis titled "DETECTION OF RECYCLED FIELD PROGRAMMABLE GATE ARRAYS USING CLUSTERING ALGORITHM", submitted by Tanvir Ahmad Tarique, Student ID: 1017312012, Session: October 2017, has been accepted as satisfactory in partial fulfillment of the requirement for the degree of Master of Science in Information and Communication Technology (M.Sc. in ICT) held on 28<sup>th</sup> November 2022.

#### **BOARD OF EXAMINERS**

Dr. Md. Liakot Ali

Professor

Institute of Information and Communication Technology (IICT)

Bangladesh University of Engineering and Technology (BUET)

Dhaka-1000, Bangladesh.

Chairman (Supervisor)

Dr. Md. Rubaiyat Hossain Mondal Member Professor and Director (Ex-Officio) Institute of Information and Communication Technology (IICT) Bangladesh University of Engineering and Technology (BUET) Dhaka-1000, Bangladesh.

Dr. Md. Jarez Miah Member Assistant Professor Institute of Information and Communication Technology (IICT) Bangladesh University of Engineering and Technology (BUET) Dhaka-1000, Bangladesh.

Dr. Md. Fokhrul Islam Professor Department of Electrical and Electronic Engineering (EEE) Islamic University of Technology (IUT) Gazipur, Bangladesh.

Member (External)

#### **AUTHOR'S DECLARATION**

It is hereby declared that this thesis or any part of it has not been submitted elsewhere for the award of any degree, diploma, or other qualifications.

AA

**Tanvir Ahmad Tarique** ID: 1017312012

### **DEDICATION**

I dedicate my thesis work to my beloved parents (Late Zafar Ahmad and Sufia Jabeen), my dear sister Dr. Shazia Jabeen, and my dear wife Eumna Bushra along with my lovely 1 year 10 months old son Tauqir Ahmad Ayaan for giving me their generous love, care, support and enthusiasm to complete my Master of Science research.

# CONTENTS

| Title                   |                                  | Page No. |

|-------------------------|----------------------------------|----------|

| Board of Examiners      |                                  | i        |

| Author's Declaration    |                                  | ii       |

| Dedication              |                                  | iii      |

| Contents                |                                  | iv       |

| List of Figures         |                                  | vii      |

| List of Abbreviations   |                                  | ix       |

| List of Tables          |                                  | xi       |

| Acknowledgement         |                                  | xii      |

| Abstract                |                                  | xiii     |

| Chapter 1               | Introduction                     | 1        |

| 1.1 Introduction        |                                  | 1        |

| 1.2 Existing Works & G  | Challenges                       | 6        |

| 1.3 Motivation          |                                  | 9        |

| 1.4 Objective with Spe  | cific Aims                       | 10       |

| 1.5 Organization of the | Report                           | 10       |

| Chapter 2 P             | reliminaries and Fundamentals of | 12       |

|                         | <b>Recycled FPGA Detection</b>   |          |

| 2.1 Introduction        |                                  | 12       |

| 2.2 Counterfeit ICs     |                                  | 12       |

| 2.2.1 Classific         | ation of Counterfeit ICs         | 13       |

| 2.2.2 Recycled          | lICs                             | 16       |

| 2.3 Field Programmable Gate Arrays (FPGAs)         | 16 |

|----------------------------------------------------|----|

| 2.3.1 Basic Structure of FPGAs                     | 17 |

| 2.3.2 Applications of FPGAs                        | 19 |

| 2.3.3 FPGA Fingerprinting using ROs                | 21 |

| 2.4 Exhaustive Fingerprint Analysis (X-FP)         | 22 |

| 2.5 Virtual Probe (VP) Technique                   | 23 |

| 2.6 Clustering Analysis                            | 26 |

| 2.6.1 Cluster Analysis Algorithms                  | 26 |

| 2.6.2 K-means++                                    | 27 |

| 2.6.3 Applications of K-means++                    | 29 |

| 2.7 Anomaly Detection                              | 29 |

| 2.7.1 Anomaly scores                               | 31 |

| 2.8 Probability Density Function (PDF)             | 32 |

| 2.9 Symmetry Analysis                              | 33 |

| 2.10 uLSIF Method                                  | 35 |

| 2.11 Receiver Operating Characteristic (ROC) Curve | 35 |

| 2.11.1 Area Under the Curve (AUC)                  | 37 |

| 2.12 Understanding IC Cost                         | 38 |

|                                                    |    |

| Chapter 3 | Symmetry Analysis based Recycled | 40 |

|-----------|----------------------------------|----|

|           | <b>FPGA Detection</b>            |    |

| 3.1 Introduction                                             | 40 |

|--------------------------------------------------------------|----|

| 3.2 Methodology of the Work                                  | 40 |

| 3.3 Dataset Collection and Details of the Fingerprint Values | 41 |

| 3.4 Recycled FPGA Detection using Symmetric Path Analysis    | 41 |

| 3.5 Implementation of uLSIF Method                           | 43 |

| 3.6 Experimental Setup                                       | 44 |

| 3.7 Algorithm of the Proposed Method                         | 45 |

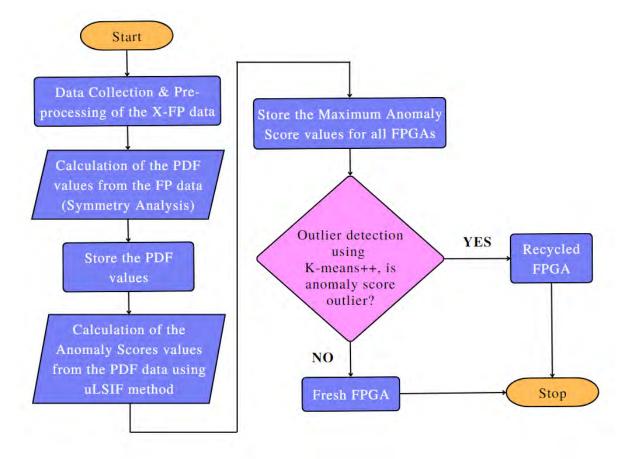

| 3.8 Flowchart of the Proposed Method                         | 46 |

|                                                              |    |

| 3.9 Required Hardwa   | re and Software               | 46 |

|-----------------------|-------------------------------|----|

| Chapter 4             | <b>Results and Discussion</b> | 48 |

| 4.1 Introduction      |                               | 48 |

| 4.2 Anomaly Score C   | omputation Details            | 48 |

| 4.3 Measurement Res   | sults                         | 49 |

| 4.4 Calculation of Co | mparison Computations         | 51 |

| 4.5 Recycled FPGA I   | Detection and Comparison      | 53 |

| 4.6 Discussion        |                               | 56 |

| Chapter 5             | Conclusion                    | 57 |

| 5.1 Conclusion        |                               | 57 |

| 5.2 Recommendation    | for Future Works              | 58 |

| References            |                               | 59 |

| Appendix I – Sampl    | e Snippet of Datasets         | 65 |

| Outcome of the The    | sis                           | 66 |

# List of Figures

| Figure No. | Figure Caption                                        | Page No. |

|------------|-------------------------------------------------------|----------|

| Fig. 1.1   | Rising demand for low-power FPGAs in portable devices | 3        |

|            | for high energy efficiency                            |          |

| Fig. 1.2   | Counterfeit incident report                           | 5        |

| Fig. 2.1   | Classification of counterfeit types                   | 14       |

| Fig. 2.2   | Typical structure of an FPGA                          | 17       |

| Fig. 2.3   | Basic idea of implementation of RO using LUTs in the  | 18       |

|            | FPGA                                                  |          |

| Fig. 2.4   | Applications of FPGAs                                 | 20       |

| Fig. 2.5   | 7-stage ring oscillator (RO) with enable signal       | 22       |

| Fig. 2.6   | An array of ROs in the Xilinx Artix-7 FPGA            | 23       |

| Fig. 2.7   | Virtual Probe Technique                               | 24       |

| Fig. 2.8   | K-means++ clustering algorithm                        | 28       |

| Fig. 2.9   | PDF curve of Normal Distribution                      | 32       |

| Fig. 2.10  | (a) Difference between symmetrical and asymmetrical   | 33       |

|            | shapes. (b) Some other symmetrical shapes             |          |

| Fig. 2.11  | Key idea of the Symmetry Analysis                     | 34       |

| Fig. 2.12  | ROC curve                                             | 36       |

| Fig. 2.13  | AUC calculation                                       | 38       |

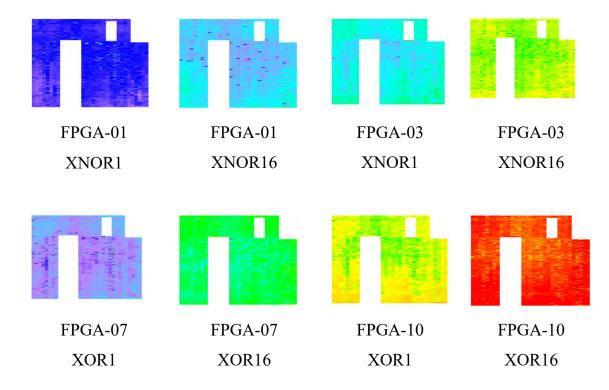

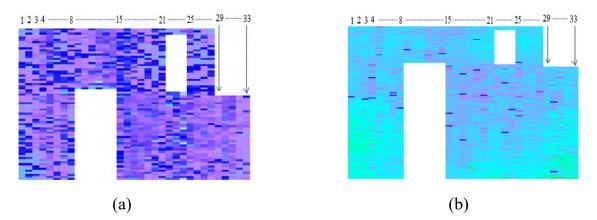

| Fig. 3.1   | Heatmaps of some paths of some fresh FPGAs            | 42       |

| Fig. 3.2   | Flowchart of the Program Code of the Proposed Method  | 46       |

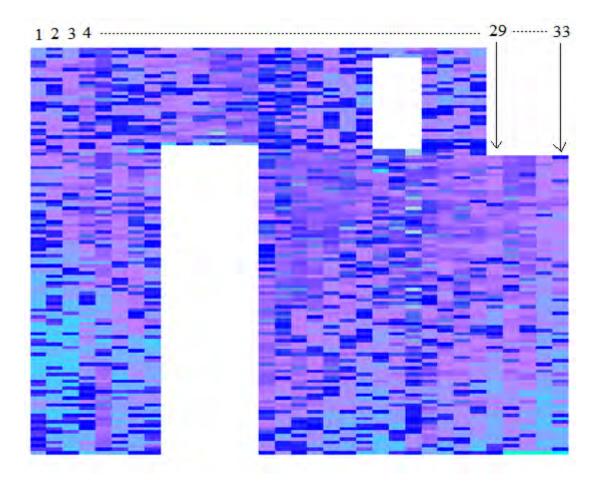

| Fig. 4.1   | A sample heatmap with 120 rows $\times$ 33 columns    | 48       |

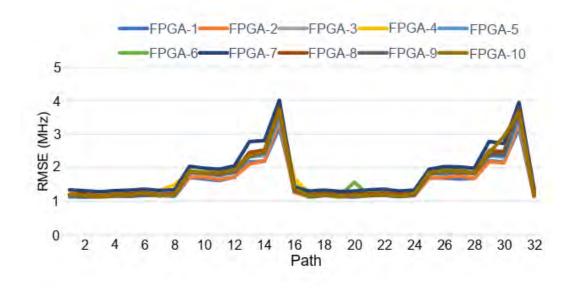

| Fig. 4.2   | RMSE of 10 fresh FPGAs 10% samples data               | 50       |

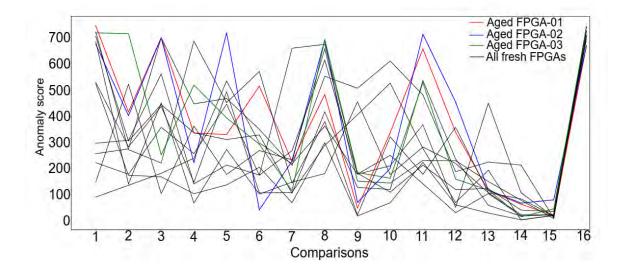

| Fig. 4.3   | Maximum anomaly scores of the 16 CPs using the        | 51       |

|            | proposed approach where used 10 fresh FPGAs and three |          |

|            | aged FPGAs                                            |          |

| Figure No. | Figure Caption                                        | Page No. |

|------------|-------------------------------------------------------|----------|

| Fig. 4.4   | Sample heatmaps with XNOR1 circuit in (a) and XOR1 in | 52       |

|            | (b)                                                   |          |

| Fig. 4.5   | ROC curve of the proposed recycled FPGA detection     | 53       |

|            | method using 10 fresh FPGAs and 3 aged FPGAs          |          |

## List of Abbreviations

| Abbreviation | Elaboration                                    |  |

|--------------|------------------------------------------------|--|

| FPGA         | Field-Programmable Gate Array                  |  |

| IC           | Integrated Circuits                            |  |

| KFF          | Known Fresh FPGA                               |  |

| RO           | Ring Oscillator                                |  |

| СР           | Comparisons                                    |  |

| FP           | Fingerprint                                    |  |

| X-FP         | Exhaustive Fingerprint                         |  |

| VP           | Virtual Probe                                  |  |

| uLSIF        | unconstrained Least-Squares Importance Fitting |  |

| AI           | Artificial Intelligence                        |  |

| ML           | Machine Learning                               |  |

| USD          | United States Dollar                           |  |

| CA           | Clustering Algorithm                           |  |

| ERAI         | Electronic Resellers Association International |  |

| HPC          | High-Performance Computing                     |  |

| DL           | Deep Learning                                  |  |

| CAGR         | Compound Annual Growth Rate                    |  |

| COVID        | Coronavirus Disease                            |  |

| SRAM         | Static Random-Access Memory                    |  |

| NLP          | Natural Language Processing                    |  |

| IoT          | Internet of Things                             |  |

| TV           | Television                                     |  |

| USICA        | U.S. Innovation and Competition Act            |  |

| FUT          | FPGA under test                                |  |

| SVM          | Support Vector Machine                         |  |

| CLB          | Combinational Logic Block                      |  |

| Abbreviation | Elaboration                                 |

|--------------|---------------------------------------------|

| LUT          | Look-Up Table                               |

| IP           | Intellectual Properties                     |

| ADAS         | Advanced Driver-Assistance System           |

| OCM          | Original Component Manufacturer             |

| SIA          | Semiconductor Industry Association          |

| ESD          | Electro-Static Discharge                    |

| PIN          | Part or Identifying Number                  |

| PCB          | Printed Circuit Board                       |

| ASIC         | Application Specific Integrated Circuits    |

| HDL          | Hardware Description Language               |

| VHDL         | Very High-Speed Integrated Circuit HDL      |

| CPU          | Central Processing Unit                     |

| ALM          | Adaptive Logic Module                       |

| LB           | Logic Block                                 |

| TPU          | Tensor Processing Unit                      |

| GPU          | Graphics Processing Unit                    |

| TDDB         | Time-dependent Dielectric Breakdown         |

| BTI          | Bias Temperature Instability                |

| PBTI         | Positive Bias Temperature Instability       |

| NBTI         | Negative Bias Temperature Instability       |

| HCI          | Hot Carrier Injection                       |

| EM           | Electromigration                            |

| OC-SVM       | One-Class SVM                               |

| XOR          | XOR logic gate                              |

| XNOR         | XNOR logic gate                             |

| JTAG         | Joint Test Action Group                     |

| PLL          | Phase-Locked Loop                           |

| UART         | Universal Asynchronous Receiver Transmitter |

| LFSR         | Linear Feedback Shift Register              |

|              |                                             |

| Abbreviation | Elaboration                       |

|--------------|-----------------------------------|

| ROC          | Receiver Operating Characteristic |

| AUC          | Area under the ROC Curve          |

| RMSE         | Root Mean Square Error            |

| GAN          | Generative Adversarial Network    |

# List of Tables

| Table No. | Table Caption                                         | Page No. |

|-----------|-------------------------------------------------------|----------|

| Table 2.1 | Top-5 Most Counterfeited Semiconductors in 2021       | 13       |

| Table 4.1 | Comparison Table of Different Paths for the Anomaly   | 50       |

|           | Scores                                                |          |

| Table 4.2 | Detection Results of the FPGAs                        | 54       |

| Table 4.3 | Comparison of the Proposed Method with Other Research | 55       |

|           | Results                                               |          |

#### ACKNOWLEDGEMENT

At first, I would like to thank and all praise to the Great Almighty Allah, the most merciful, the most gracious, the source of knowledge and wisdom endowed to mankind, who provided me with the power of mind, strength, patience and capability to carry me through the work and enable me to complete this thesis.

I would like to thank greatly to my Supervisor, **Prof. Dr. Md. Liakot Ali**, Institute of Information and Communication Technology (IICT), Bangladesh University of Engineering and Technology (BUET), Dhaka, Bangladesh for his kind, constant, and inspiring guidance, close encouragement, advice, and valuable suggestions at all stages for preparing this dissertation.

I am also very grateful to **Prof. Dr. Md. Rubaiyat Hossain Mondal**, Director of IICT, BUET for providing the great support of different facilities of IICT especially the **Embedded System Lab of IICT** to conduct my thesis research works. My special thanks to all the Faculty Members and Staffs of IICT, BUET.

In completing this work, I have been fortunate to get help, support and encouragement from many people. I would like to acknowledge all of them for their cooperation. Especially, I am greatly grateful to my ex-colleague, Dr. Foisal Ahmed, Postdoc Fellow at Department of Computer System, Tallinn University of Technology, Estonia. I am also thankful to the Dependable System Lab (DSL) at Nara Institute of Science and Technology (NAIST), Japan for providing their FPGA datasets to use them in my thesis research.

Finally, I would like to thank to my parents, my sister, my wife and my son for their continuous support and inspiration throughout the whole period of this research.

#### ABSTRACT

Field Programmable Gate Array (FPGA) is a popular electronic component used in many applications due to their cost-effectiveness, competitive performance, and power efficiency. However, some third-party vendors in the semiconductor industry collect used FPGAs and refurbish them to sell as a new, posing security and reliability issues for mission-critical systems. Researchers have proposed various methods to detect recycled FPGAs, including ring oscillator-based delay analysis or fingerprint (FP) analysis using supervised machine learning (ML) technique. However, these methods require a large amount of data and time, which is not practical due to the rapidly changing technology and large number of FPGAs in the industry. Unsupervised machine learning approaches require less data but still require a significant amount of comparison calculations to achieve high accuracy, which is costly and time-consuming. Finding a faster and cheaper solution to this problem is necessary. Fresh FPGAs have different FP patterns than that of recycled FPGAs. This property has been used by other researchers for classification of recycled FPGAs from fresh FPGAs. However huge computation is required in this case. This thesis has introduced a novel technique to reduce the computational complexities using the property of symmetricity of the structure of FPGAs. Due to systematic process variation within the FPGA, the neighboring combinational logic blocks (CLBs) of FPGAs have similar or symmetrical array structures, leading to similar FPs in the neighboring logic blocks. This symmetrical property has been exploited for detecting recycled FPGAs using Clustering Algorithm (CA)-based anomaly or outlier detection scheme with K-means++ technique which analyzes the neighboring ring oscillator (RO) frequencies' symmetrical or similarity information. The proposed symmetry analysis method efficiently detects all the recycled FPGAs through outlier detection, achieving 92% accuracy in a very short period of time with around 41% less computations compared to the previous unsupervised ML-based method. In future, research can be carried out to improve the accuracy using more reduced computations.

# Chapter 1 Introduction

#### **1.1 Introduction**

Nowadays, modern civilization inevitably relies on computer systems to improve our lives in every sector. The dependability of these systems is essential to ensure good functionality and performance in delivering the services to the systems. In general, the hardware dependability includes the attribute of availability, reliability, safety, integrity, maintainability, and confidentiality [1]. Specifically, hardware security is currently one of the most important reliability issues for the computer system.

Field-programmable gate arrays (FPGAs) have become highly prevalent among integrated circuits (ICs) due to their advantageous features such as low development expenses and quick time-to-market. Consequently, even reused FPGAs are frequently employed, considering the complex nature of contemporary electronics supply chains. As a result, FPGAs are now regarded as the most sought-after ICs. [2]. Moreover, there is a novel trend of using FPGAs as accelerators for artificial neural networks. [3]. PGAs offer multiple benefits, including cost-effective integration, superior performance, and energy efficiency, which are driving their adoption in edge AI devices, AI workstations, and High-Performance Computing (HPC) applications. AI-enabled FPGAs are employed in several data center devices, such as networking equipment, storage racks, and server systems, enabling users to manage high-speed data processing and monitor network traffic. Furthermore, the major data center operators' concerted efforts to enhance process efficiency will encourage market growth. [4].

The FPGA market has experienced growth in the healthcare industry since 2020, largely due to the COVID-19 pandemic. The heightened need for high-performance detection devices in hospitals has spurred developers to create infection detection systems based on FPGAs. For instance, ALDEC Inc. developed a COVID-19 lung infection detection system. The ongoing research and development and innovations in the healthcare sector are expected to foster market expansion in the years to come. [4].

To address the aforementioned challenge and explore new opportunities in the industry, FPGA market players are concentrating on developing cutting-edge SRAM memory solutions. For example, in February 2022, QuickLogic Corporation, a California-based semiconductor manufacturing company, launched a low-power FPGA based on SRAM technology to mitigate semiconductor supply and availability issues. These advancements are expected to foster market growth in the projected timeline. [4].

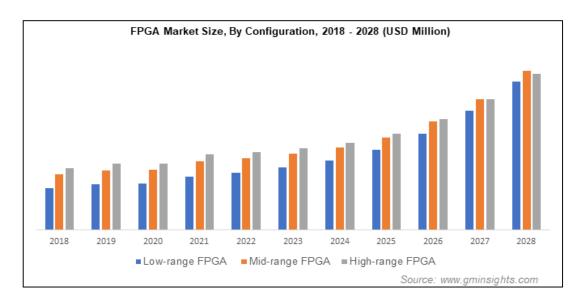

In Fig. 1.1, the low-range segment in the FPGA market is anticipated to exhibit a growth rate of approximately 15% until 2028, primarily driven by the numerous high-end features it offers, including low logic density, high power efficiency, and reduced complexity. These features have accelerated the adoption of low-range FPGAs in several portable electronic devices such as wearable devices, edge computing devices, and wireless gateways. [4]. The <28 nm segment of the FPGA market generated over USD 1.5 billion in revenue in 2021 and is expected to grow at a rate of 14% during the forecast period. The growth can be attributed to the various high-end features offered by this segment, such as high-speed processing, compact size, and improved efficiency, among others. These characteristics have accelerated the adoption of <28 nm FPGAs in multiple markets, including automotive electronics, high-performance computing, and telecommunications. [4].

Fig. 1.1: Rising demand for low-power FPGAs in portable devices for high energy efficiency [4]

In 2021, the consumer electronics sector accounted for approximately 9% of the FPGA market share. The growing disposable income in developing countries is driving the demand for new appliances, leading to an increasing market demand. FPGA solutions are integrated into various consumer electronics such as smartphones, laptops, digital cameras, game consoles, and tablets. Furthermore, the rising adoption of new technologies such as IoT, Natural Language Processing (NLP), and AI in smart speakers, smart TVs, and edge AI devices will fuel market growth in the future. [4].

The North American FPGA market is projected to grow at a CAGR of over 14% from 2022 to 2028, driven by the increasing government initiatives and funding activities to boost the regional semiconductor sector. For instance, in July 2021, the U.S. government passed the U.S. Innovation and Competition Act (USICA), which is an initiative aimed at boosting semiconductor manufacturing. The bill includes a total funding of USD 250 billion to launch innovative products and USD 52 billion for R&D activities in semiconductors, among other initiatives. [4].

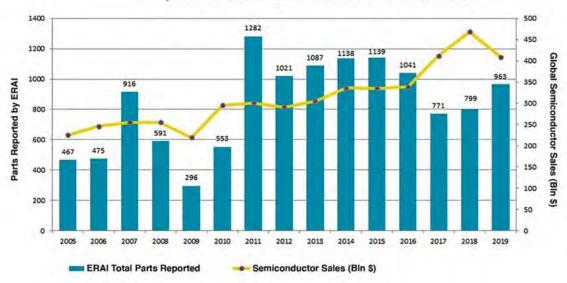

The security of the integrated circuits (ICs), which is the most essential part of any computer system, is now becoming a rising threat, especially the counterfeit ICs [5]. Counterfeited electronics components are now a deep-rooted problem that has created significant concern in the ICs supply chain, and are impacting the IC industries, computers, communication systems, medical, and telecommunication systems. Specifically, the problem of counterfeit ICs attracts a lot of attention not only to the private sectors but also the government because the global counterfeit market has grown significantly compared to the past history. Fig. 1.2 shows the recent data provided by Electronic Resellers Association International (ERAI) showing the scenarios of recent incidents of counterfeit material still exists in large numbers although some preventive measures have been taken.

Counterfeit ICs can be classified into several categories, including recycled, remarked, overproduced, defective, cloned, and more. Recycled components are the most common type of counterfeit ICs, accounting for over 80% of the total counterfeit components. Recycled components refer to those that have been previously used or recycled and are being sold as new, genuine products. This type of counterfeit ICs poses a significant risk to the electronics industry, as recycled components may not function as intended and can compromise the safety and reliability of electronic devices. [5].

Certainly, recycling of FPGAs is a significant concern given their increasing usage and the prevalence of recycled counterfeit components in the market. Using recycled FPGAs may compromise the performance, reliability, and safety of electronic devices. Therefore, it is crucial for the electronics industry to ensure the authenticity and quality of FPGAs and other semiconductor components to avoid the risks associated with using counterfeit or recycled components. This can be achieved through proper testing, inspection, and certification procedures, as well as by working with trusted suppliers and distributors. [7].

Reported Parts vs. Global Semiconductor Sales 2005-2019

Fig. 1.2: Counterfeit incident report [6]

Of course, recycled FPGAs pose significant risks to the reliability and performance of electronic devices. Due to their prior usage, recycled FPGAs may have already undergone wear and tear, leading to degradation in performance over time. Additionally, recycled FPGAs may be compromised and contain hidden defects or malicious code, which can cause serious reliability and security issues in critical applications.

Preventing the infiltration of recycled FPGAs is a challenging and costly task, as it requires stringent testing and verification procedures to ensure the authenticity and quality of the components. This is particularly important in critical applications, such as aerospace, defense, and medical devices, where the reliability and safety of the system are of utmost importance. To mitigate these risks, it is essential for the electronics industry to work with trusted suppliers and distributors and implement robust testing and inspection procedures to ensure the authenticity and quality of FPGAs and other semiconductor components. So, it can be understood that the importance and usages of the FPGAs in the current time are very huge. And so, as

the preparing and infiltrating of the recycled FPGAs are also booming for the many dishonest suppliers or third-party vendors. So, this is the concern of this work to tackle the infiltration of these recycled FPGAs in the supply chain of the FPGA market.

#### **1.2 Existing Works & Challenges**

It has been realized that the recycled FPGAs are a major concern in the IC supply chain due to the increasing number of third-party IC vendors, leading to a higher risk of counterfeit components. As mentioned earlier, recycled components account for more than 80% of the counterfeit components, which can pose a significant threat to the reliability and performance of critical applications. [5]. These recycled FPGAs may have reliability risks and trustworthiness issues due to the aginginduced performance degradation. As FPGAs are used, they may experience wear and tear, which can lead to degradation in performance over time. This aging process can impact the reliability and trustworthiness of recycled FPGAs, making them less suitable for critical applications. As a result, it is essential to take steps to prevent the infiltration of recycled FPGAs in the IC supply chain and ensure the authenticity and reliability of FPGAs used in critical applications. Meanwhile, presently FPGAs are extensively used in autonomous applications such as UAVs and self-driving cars owing to the excellent performance of AI implementation in safety and critical applications [8]. If untrusted FPGAs infiltrate these missioncritical systems, the system's reliability may suffer, causing significant incidents.

Several supervised machine learning (ML) based methods for detecting recycled FPGAs have been proposed in [9-13]. These methods use a combination of datadriven techniques and statistical analysis to identify recycled FPGAs. For instance, some researchers have proposed using Support Vector Machines (SVM), Decision Trees, Random Forests, and Neural Networks to detect recycled FPGAs by analyzing their electrical characteristics such as power consumption, delay, and power supply noise. These methods have shown promising results in detecting recycled FPGAs with high accuracy. The key idea behind these methods is to employ the ring oscillator (RO) frequency to analyze the deterioration of circuit characteristics caused by the aging process. Fresh FPGA's RO frequencies are measured and used to train the supervised ML models. As these frequencies degrade with use, the trained model can determine whether the FPGA under test (FUT) is new or recycled. These supervised ML methods [9, 11, 12, 14] are predicated on the presence of known fresh FPGAs (KFFs). But a very large number of FPGA datasets have been required for the supervised ML methods for the accurate classification [9-10]. As the FPGA manufacturing technology is improving very rapidly, so this vast dataset collection is very difficult as well as costlier. Besides, for the preprocessing of the datasets and the training of the supervised ML models with these large datasets will require a very large amount of time and huge amount of memory for the whole process of the detection for every FPGA, training requires a significant number of measurements for the ROs with these supervised ML models which is very time-consuming. This is time consuming because the KFF datasets are not readily available and also the recycled datasets are unavailable to the researchers. But the overall performance is not up to the mark.

Due to the lesser accuracy, exhaustive fingerprint (X-FP) analysis method, based on another supervised ML model, has been proposed for better detection of recycled FPGAs in [12]. Here, the frequencies for all paths of look-up tables (LUT) in all combinational logic blocks (CLB) are taken into account. This method correctly detected the aging issues, means it has detected all the recycled FPGAs. However, the X-FP method can lead to a large number of frequencies, which in turn increases the dimensionality of the feature-vector of the ML model. This can severely degrade the accuracy of the model. This is a problem because in real-life scenarios, hundreds of thousands of ICs or FPGAs have to be tested in a unit time (such like within 24 hours assuming) otherwise the testing cost will be increased, so it is required to find other ways in order to reduce this extra-cost.

These methods are unrealistic approaches to get desired the accuracy. Because, for accurate classification through supervised ML, FPGA manufacturers require the measurement of a significant number of KFFs, but this large volume of KFFs is unavailable due to many factors such as rapid upgradation of technology, costing etc. These methods do not work properly to get desired level of accuracy if there are fewer KFFs available. Another thing is that the recycled FPGA datasets are not available beforehand, because there are so many third-party vendors who are distributing FPGAs, whether those are fresh or recycled, and it is impossible to collect the FP data of those for the training and testing purpose as the rapid advancement of technologies, process variations etc. In order to tackle these problems, unsupervised ML algorithms based methods have been proposed in [16-17]. Unsupervised ML algorithms doesn't require too many datasets for the training. These methods [16-17] used clustering algorithm (CA) which is the widely used unsupervised ML algorithm. This algorithm is one kind of anomaly or outlier detection scheme, which can be used to detect the recycled FPGAs as the anomalous data. As mentioned above, CA's most intriguing characteristics is that it doesn't require so many KFFs for the accurate classifications, and also it can be used without the negative-class data.

There are different types of clustering algorithms available, among which Kmeans++ is one. To address the limitations of supervised methods, previous works [16-17] proposed unsupervised methods for detecting recycled FPGAs. However, the classification accuracies of these methods are limited due to process variation in the KFFs, which use the measured frequencies as input vectors for the K-means++ method. Choosing the correct logic blocks for RO measurement is crucial, as selecting the wrong or inadequate ones can significantly reduce classification accuracy. To detect recycled FPGAs, previous approaches exhaustively compared the frequencies of neighboring blocks using direct density ratio estimation technique, which is a lengthy process. Moreover, these methods require a large dataset to increase accuracy, which is not always feasible in real-life scenarios and also requires a significant amount of memory for the huge amount of computations comparisons of those ICs or FPGAs which increases the testing-time and testingcost. But it is required to achieve the desired accuracy faster and cheaper.

In brief it can be said that, the existing methods require a very large number of computations of neighboring RO FPs. And also, they require a large number of FPGA datasets in the supervised ML approaches which is impractical. As the technology is rapidly changing, the collection of these vast datasets not feasible. Meanwhile, the unsupervised methods don't require a very number of datasets for the whole work, but existing unsupervised methods require a large number of calculations to achieve desired accuracy. So, there are scopes for finding some different approaches for achieving desired accuracy with lesser amount of computations.

#### **1.3 Motivation**

It is already mentioned that FPGA is an electronic component that is widely used in many applications due to its competitive performance and power benefits, as well as low non-recurring engineering costs. However, the use of the recycled components in counterfeit FPGAs has threatened the security and reliability of critical systems such as those used in airplanes, automobiles, and medical equipment etc. Several research works have been conducted to detect those recycled FPGAs, including using ML approaches based on RO delay information. However, these methods require a large number of computation measurements and are time-consuming and memory-expensive. An alternative method is the exhaustive fingerprint (X-FP) analysis, which takes into account the frequencies for all paths of look-up tables in all CLB. This method accurately detects aging issues

but increases the dimensionality of the feature-vector of the ML model, which reduces accuracy. These issues have been addressed using with-in die (WID) modelling in literature [10]. However, accurate classification through supervised machine learning requires a large volume of known-fresh FPGAs (KFF), which may not be available due to various factors such as technology upgrades and cost. Also, the unsupervised ML methods addressed in [16-17] improves the accuracy but leaves one issue that is the huge comparison computations which leads to very time-consuming testing and costing. Recycled FPGAs exhibit distinct FP patterns compared to their fresh counterparts, which has been leveraged by previous researchers to differentiate between the two types in studies [16-17]. However, this approach requires extensive computation, and it is crucial to find a more efficient and cost-effective solution to address this issue.

This thesis has introduced a novel technique to reduce the computational complexities using the property of symmetricity of the structure of FPGAs that does not depend on KFFs or requires a low amount of KFFs [18]. Due to systematic process variation within the FPGA, the neighboring combinational logic blocks (CLBs) of FPGAs have similar or symmetrical array structures. This symmetrical property has been exploited for detecting recycled FPGAs using Clustering Algorithm (CA)-based anomaly or outlier detection scheme with Kmeans++ technique which analyzes the neighboring ring oscillator (RO) frequencies' symmetrical or similarity information. The proposed symmetry analysis method efficiently detects all the recycled FPGAs through outlier detection in a very short period of time with lesser computations compared to the previous unsupervised ML-based method. The proposed method eliminates the necessity of KFFs by exhaustively comparing all neighboring ROs, regardless of their frequency values [19-20]. This is because the assumption that the frequency distributions of neighboring columns ideally match due to the systematic component of process variation does not hold if there is any aging-induced

degradation on either side [21]. As this method will utilize the symmetry analysis, the number of computations will be reduced which in turn will yield lesser time and lesser memory requirement. So, there are the scope of research in this area.

### 1.4 Objective with Specific Aims

The objective of this research is to develop a technique for improving the recycled FPGA detection performance using unsupervised machine learning approach. To achieve this goal this research will have the following aims:

- i. To develop a CA-based unsupervised ML-model using with K-means++ method to solve the proposed research problem by exploring the symmetricity of the fingerprint (FP) data of the neighboring columns.

- ii. To train the model using available FP data of the KFFs by finding the PDF values and anomaly scores of their neighboring columns.

- iii. To test and verify the model by finding the best accuracy of that unsupervised K-means++ model.

#### **1.5 Organization of the Report**

In Chapter 1, the introductory information has been discussed. The common preliminaries used throughout the related works or topics and the fundamentals of the recycled FPGA detection are discussed in Chapter 2. The details of the proposed method have been discussed in Chapter 3. Simulation results and its discussions are provided in Chapter 4. Finally, the conclusions from this work along with the recommendations for the future works of this research are presented in Chapter 5.

# Chapter 2 Preliminaries and Fundamentals of Recycled FPGA Detection

#### **2.1 Introduction**

In this chapter, recycled FPGAs and various terminologies related to detecting recycled FPGAs are presented as preliminaries. In the related terms section, the topics regarding this research work and its previous works in fingerprint analysis to detect recycled FPGAs will be summarized.

#### 2.2 Counterfeit ICs

The global economic market has now reduced the cost of electronics due to a growing large horizontal business model that offers low-cost fabrications. As like ASIC, FPGA vendors similarly design and develop FPGA in their own lab, but fabricate them in offshore countries. This trend in the supply chain makes the backdoor for the corrupt market who instigate attacks like counterfeiting, malicious activities, or stealing of intellectual properties (IP) in real design etc. Specifically, the problem of counterfeiting of IC is now a major concern issue that drawn much attention to not only the media and industry but also government because of the global counterfeited market increasing exponentially over the past decades. Table 2.1 shows reports from 2021 of the five most commonly counterfeited electronic components. Among all incidents, the programmable logic IC is 8.3% of the counterfeited components [21].

The impact of counterfeited IC is more vulnerable in case of some critical applications like communication systems, medical equipment, aero-space etc. The

U.S. Department of Commerce reported over ten thousand occurrences relating to recycled ICs itself than other types of counterfeited components [22]. Moreover,

| Rank | <b>Commodity</b> Type | % of Reported Incidents |

|------|-----------------------|-------------------------|

| 1    | Analog IC             | 25.3                    |

| 2    | Microprocessor IC     | 13.4                    |

| 3    | Memory IC             | 13.1                    |

| 4    | Programmable logic IC | 8.3                     |

| 5    | Transistor            | 7.6                     |

Table 2.1: Top-5 Most Counterfeited Semiconductors in 2021 [21]

according to statistical reports, FPGAs are among the top five most counterfeited electronic components. [23]. Yes, that's correct. With the increasing adoption of advanced technologies like IoT, Artificial Intelligence (AI), and Advanced Driver-Assistance System (ADAS), the demand for FPGAs has been on the rise. As a result, the global FPGA market is expected to grow rapidly and reach a value of USD 9.50 Billion in 2022. This growth can be attributed to the unique benefits that FPGAs offer, such as flexibility, low power consumption, and high performance, which make them ideal for use in real-time applications. [24]. Due to the increasing popularity of FPGAs, they have become an even more attractive target for counterfeiters, which raises concerns about their reliability for both government and industry stakeholders.

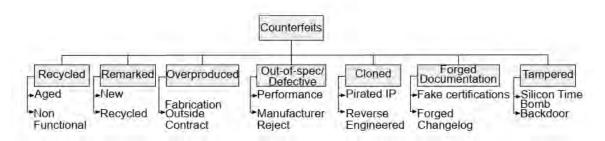

#### 2.2.1 Classification of Counterfeit ICs

The Semiconductor Industry Association (SIA) recommends that the best way to avoid counterfeit components is to purchase semiconductor products directly from the Original Component Manufacturer (OCM) or from authorized distributors or resellers. This ensures the authenticity of the components and helps to mitigate the risks associated with counterfeit components [25]. On the base of these points, the US Department of Commerce has marked some following points to classify a counterfeit component [22]:

- 1. Unauthorized copy: The component is not authorized or licensed by the original component manufacturer.

- 2. Non-conformance: The component does not meet the original design, model, and/or performance standards of the original component manufacturer.

- 3. Unauthorized production: The component is produced by unauthorized contractors or manufacturers, not by the original component manufacturer.

- 4. False representation: The component is misrepresented as new, working, or meeting specifications when it is actually off-specification, defective, or used. It may also have incorrect or false markings and/or documentation.

Fig. 2.1 shows a comprehensive classification of different types of counterfeiting components that are widely accepted in the community [26-27]. This expanded classification will help us understand the counterfeiting components more deeply and take potential techniques to measure and avoid counterfeited components in the supply chain.

Fig. 2.1: Classification of counterfeit types [26-27]

A brief idea of each of counterfeit parts is given as follows:

- 1. Recycled: Refers to electronic components that were previously used and recovered from a system, then transferred to the supply chain as new components from the Original Component Manufacturer (OCM).

- 2. Remarked: Counterfeiters remove the original marking from a recycled IC and add fake information to uniquely identify it.

- 3. Overproduced: An untrusted foundry illegally accesses the IC layout and fabricates more ICs than authorized, transferring them into the supply chain.

- 4. Out-of-spec/Defective: ICs that failed post-manufacturing tests are sold into the supply chain instead of being destroyed.

- 5. Cloned: Counterfeiters reproduce ICs using reverse engineering or pirated intellectual property.

- 6. Forged Documentation: Counterfeiters may ship ICs without documentation and then forge fake documentation before transferring them into the supply chain.

- 7. Tampered: Malicious alterations or insertions, such as hardware Trojans, or external factors like high temperature, are used to decrease the security and reliability of ICs.

Recycled ICs are one of the most common types of counterfeit components in the electronics supply chain, and it has been reported that they make up more than 80% of all reported counterfeit components. This is due to the fact that recycled ICs can be more difficult to detect and identify compared to other types of counterfeits, as they may look like genuine components and have similar markings. [24]. In the next subsection, the recycled ICs will be discussed more elaborately.

#### 2.2.2 Recycled ICs

Although recycled ICs show lower performance due to aging effects for their prior usage, the reliability issue will become more vulnerable as it undergoes very harsh environments during the recycling process. Initially, discarded printed circuit board (PCB) from different damaged or old systems is collected. The PCB is then heated to a specific high temperature so that soldering material begins to melt in order to collect used-ICs. Recycled ICs undergo a process of surface cleaning and polishing, following which a new set of markings such as PIN number, lot number, manufacturer logo, country of manufacture, etc. are printed on the surface. This gives the recycled ICs a fresh appearance, and they are then introduced into the supply chain as new components. [58].

Despite having good functionality initially, the performance of recycled ICs deteriorates rapidly due to the aging effects caused by their previous use. Furthermore, the recycling process subjects them to extreme electrical, mechanical, and temperature stresses, which contribute to a significant decrease in their performance. However, preventing the entry of recycled ICs into the IC market is challenging due to the increasingly complex supply chain. Therefore, it is crucial to have an effective method for detecting recycled ICs, especially recycled FPGAs.

#### 2.3 Field Programmable Gate Array (FPGA)

The FPGAs are reconfigurable ICs where any logic function can be performed by appropriately configuring logic elements. Unlike the ASICs, fabricated for a specific application, FPGAs can be reprogrammed for any desired applications. This versatility makes FPGAs more popular day-by-day. Specific hardware description languages (HDL) like Verilog HDL or VHDL (Very High-Speed Integrated Circuit HDL) can be used to configure the logic function on its own field; thus, it is called field-programmable. CLBs and complex routing interconnection make it possible to implement complex logic functions inside any part of the FPGAs. Presently, most of the FPGAs are SRAM-based and it is used to store information.

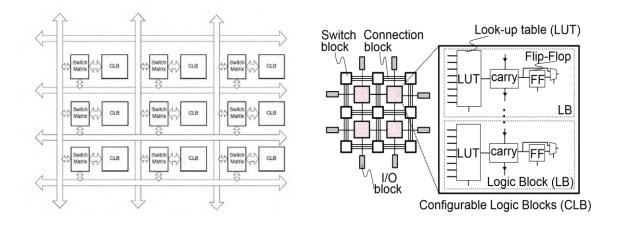

#### 2.3.1 Basic Structure of FPGAs

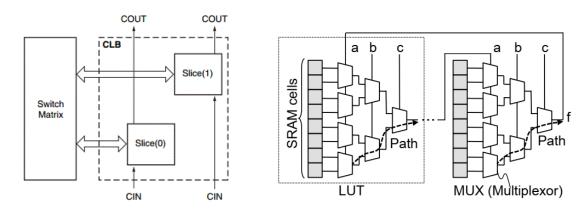

Fig. 2.2 depicts the basic structure of an FPGA. In an FPGA, the CLB (Configurable Logic Block), connection block, and switch block are arranged to form an array. The CLB is composed of one or more clusters of basic logic blocks (LB) that are interconnected within the cluster. Each LB is made up of several LUTs (Look-Up Tables), a carry chain, and flip-flops as shown in Fig. 2.2.

Fig. 2.2: Typical structure of an FPGA

An LUT, or Lookup Table, is a fundamental logic element that defines a function in an FPGA. It is capable of implementing an arbitrary i-input Boolean function through a chain of multiplexers (MUX), with n being the number of inputs. The input of the LUT is selected to utilize the value stored in a memory element with 2<sup>i</sup> bits as the input of the truth table for the function. In modern SRAM-based FPGAs, these memory element entries are represented by configuration bits stored in SRAM cells. Fig. 2.3 shows a 3-input LUT can be implemented using pass transistors or transmission gates. The inputs of the LUT are connected to the SRAM cells which store the configuration bits. Each input is connected to two pass transistors or transmission gates, and the gates of these transistors are connected to the corresponding configuration bit. The output of each pass transistor or transmission gate is connected to the input of a buffer. The output of the buffer is the output of the LUT. When the LUT is configured with a particular set of values, the pass transistors or transmission gates corresponding to those values are turned on, allowing the values to pass through to the output buffer [31]. The FPGA architecture consists of an array of CLBs, connection blocks, and switch blocks. Each CLB contains one or more clusters of basic logic blocks (LBs), which are made up of multiple LUTs, carry chains, and flip-flops. LUTs are the basic logic elements that determine the function of the FPGA. In modern SRAM-based FPGAs, each LUT is typically implemented as an n-input LUT using configuration bits stored in SRAM cells.

Fig. 2.3: Basic idea of implementation of RO in CLBs using LUTs in the FPGA

A 3-input LUT can be designed with pass transistors or transmission gates to transfer the value from SRAM cells to the output. This LUT requires eight SRAM bits to set the truth table value for any 3-input Boolean function. The direction of the LUT path can be changed by altering the input values of the LUTs. The FF logic circuit enables FPGAs to implement sequential circuits by storing the output

value obtained from the corresponding LUTs at each clock cycle. The CLBs are connected to the switch boxes via programmable interconnection blocks.

In order to implement specific logic functions, the signals between the CLBs and the I/O blocks are routed through the programmable interconnects, which are controlled by the switch box. In this way, the interconnects can be configured to create specific logic elements. For the purpose of detecting recycled FPGAs, this study uses a RO (Ring Oscillator) logic circuit, which collects frequency information from each CLB and uses it as a measure of aging.

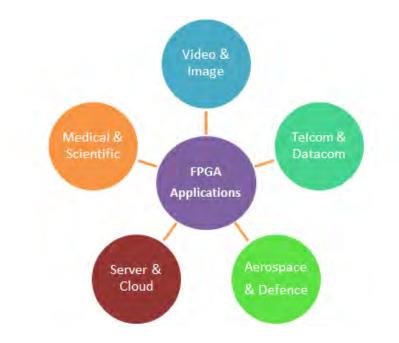

#### 2.3.2 Applications of FPGAs

FPGAs have a wide range of applications due to their reprogrammable and customizable nature. They are often used in low volume and high complexity projects where flexibility and performance are critical. Some of the main applications of FPGAs include medical and scientific equipment, video and image processing, telecommunications and data communications, aerospace and defense, and server and cloud computing. In medical and scientific applications, FPGAs are used in equipment such as MRI and CT scanners, as well as in research equipment for simulations and data analysis. In video and image processing, FPGAs are used for real-time video processing and image recognition. In telecommunications and data communications and deta sonar systems, as well as in navigation and guidance systems. In server and cloud computing, FPGAs are used for acceleration of specialized workloads such as machine learning and big data processing [36]. Fig. 2.4 shows some important applications of FPGAs.

FPGAs are commonly used in both wired and wireless communication systems. In wired communications, FPGAs are used in applications such as serial backplanes, network switches and routers, and high-performance computing systems. In

wireless communications, FPGAs are used for networking solutions and to address standards such as WiMAX, 5G/6G, and HSDPA. FPGAs are also used in the infrastructure side of communication systems to process and analyze data at high speeds [36].

Fig. 2.4: Applications of FPGAs

FPGA chips find applications in medical equipment for processing data and serving diagnostic and monitoring purposes [36].

FPGA chips also find extensive applications in the aerospace and defense industries, where they are utilized for image processing, generating waveforms, and for enabling partial reconfigurations in software-defined radios (SDRs) [36].

FPGA technology presents an option for ASIC companies to quickly prototype and test ideas and concepts without undergoing a lengthy process. This is helpful in improving time to market of various technological products and reducing engineering costs in several processes such as industrial automation and surveillance [36].

The reconfigurability of FPGA technology makes it an attractive option for reducing the long-term maintenance costs of a system. This flexibility also enables FPGA to keep up with modifications and changes, further reducing costs associated with system updates. Even developers at Microsoft have access to FPGA chips, and they use open source tools like the Microsoft Cognitive Toolkit. Microsoft utilizes Intel FPGA chips to increase their use of AI in their operations.

FPGAs have emerged as a key technology for the development of deep neural networks (DNNs), which are the foundation of artificially intelligent systems. When compared to GPUs, high-performance FPGAs can be even more beneficial in certain applications, making them the preferred choice for developing machine learning technology [36].

The recent acquisitions of Altera by Intel and Xilinx by AMD demonstrate the increasing importance of FPGAs in the server and computing market. This market segment is expected to show significant growth for the FPGA industry [36].

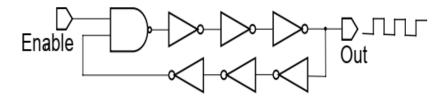

#### 2.3.3 FPGA Fingerprinting using ROs

Ring oscillators (ROs) are commonly used in the semiconductor industry for process control and characterization. They are simple to design and can provide valuable information about process variations, such as timing delays and device performance, which can impact the overall functionality of integrated circuits (ICs). ROs can also be used for frequency testing and calibration of various electronic systems. [32-33]. In addition, ROs are also extensively used in FPGAs for delay variation to use it as fingerprint in recycled FPGA detection [34-35]. The output of a ring oscillator (RO) is a periodic waveform with a frequency that depends on the delay of the inverters in the ring. A ring oscillator typically consists of an odd number of inverters (such as 3, 5, or 7) connected in a chain to form a closed loop, as you mentioned. When the output of the last inverter feeds back to

the input of the first inverter, the circuit can oscillate at a certain frequency determined by the delay of each inverter. The oscillation frequency is typically measured and used to extract information about the manufacturing process variation and delay characterization in ICs. Fig. 2.5 depicts a 7-stage inverter-based RO with an enable logic showing oscillation.

Fig. 2.5: 7-stage ring oscillator (RO) with enable signal

#### 2.4 Exhaustive Fingerprint Analysis (X-FP)

A new technique called X-FP has been introduced to enhance the efficiency of detecting recycled FPGAs. [12]. Using advanced RO design, the method X-FP can thoroughly analyze the aging deterioration of all paths in LUTs of all the CLBs, fully characterizing their frequencies. Results from experiments conducted on 10 commercially available FPGAs demonstrate that X-FP can effectively capture the degradation effects with high accuracy.

The main contributions of this method can be outlined as follows:

- To improve the detection of recycled FPGAs and effectively observe aging degradation, the proposed method utilizes X-FP. This technique enables the examination of the aging-induced delay characteristics of all paths in all LUTs of all the CLBs.

- The X-FP characterization of 10 commercial Xilinx Artix-7 FPGAs, including aging acceleration of 3 FPGAs, revealed various path differences between fresh and aged FPGAs, as demonstrated in the experiments.

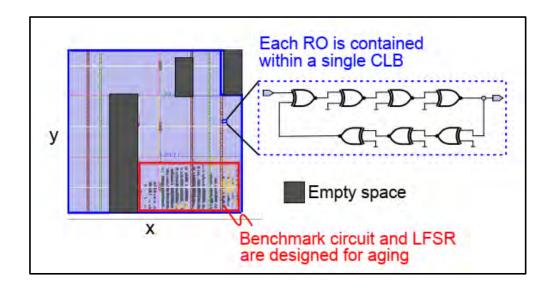

Fig. 2.6 shows the RO implementation within a single CLB for the capturing of the FP values of all paths in an FPGA. As the LUTs in the Xilinx Artix-7 are made of 6-input, thus there are total  $2^{6-1} = 32$  paths for a single FPGA. And every FPGA contains 3,173 CLBs, thus total 3,173 ROs were placed on a geometrical grid of  $33 \times 120$  (except the empty space of the layout) using Verilog HDL script. With the X-FP analysis, it becomes possible to observe the aging degradation of all paths in all LUTs within the FPGA. However, although X-FP analysis accurately captures aging information of recycled FPGAs, it raises two potential issues with ML-based detection. Firstly, to characterize the X-FP, a larger number of RO measurements are required which increases the testing cost considerably. Secondly, the X-FP technique generates a significant amount of measurement data, which cannot be effectively handled by typical machine learning algorithms for the purpose of detecting recycled FPGAs [12].

Fig. 2.6: An array of ROs in the Xilinx Artix-7 FPGA

#### 2.5 Virtual Probe (VP) Technique

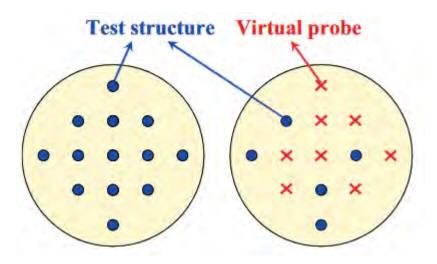

The main concept behind the virtual probe (VP) technique [41] is to strategically place and measure a small number of test structures at specific locations on a

wafer or chip. The parametric variations at other locations are not directly measured during hardware testing. Instead, virtual probes are virtually placed at these locations to predict the variation information using a numerical algorithm, as shown in Fig. 2.7. In contrast to the conventional approach that involves monitoring variability at many locations using numerous test structures, the virtual probe technique proposes to monitor variability at only a few specific locations and then employ an intelligent algorithm to predict the complete spatial variation accurately. This is made possible by leveraging the sparse structure in the spatial frequency domain.

Fig. 2.7 illustrates an example of the virtual probe technique. The left side shows the conventional approach, where a large number of test structures are deployed and measured to completely characterize process variations. On the right side, the virtual probe technique proposes to deploy and measure only a few test structures, while virtual probes are conceptually added to recover the spatial variation using a numerical algorithm.

Fig. 2.7: Virtual Probe Technique

To summarize, the virtual probe technique provides several key advantages over traditional techniques, such as [41]:

- 1. **Cost-effectiveness:** VP minimizes the number of required test structures, which reduces the cost of testing and measurements, such as area overhead, testing/characterization time, and yield loss during testing.

- 2. **High accuracy:** VP can accurately reconstruct the spatial variation with a probability close to 1. The accuracy can be verified in real time using efficient techniques such as cross-validation and Bayesian inference. Additional sampling points can be collected to further improve accuracy until the prediction error is sufficiently small.

- 3. Versatility: VP can predict the spatial pattern of both inter-die and spatially-correlated intra-die variations. The prediction is based on the measurement data from the current wafer/chip only.

The virtual probe (VP) technique has a wide range of potential applications in various fields beyond integrated circuits. It can be used in semiconductor manufacturing for testing and characterizing process variations, as well as in design verification and optimization. Additionally, VP can be applied in other fields such as biotechnology, environmental monitoring, and material science, where spatial variability measurements are critical. In summary, the versatility of the VP method makes it a valuable tool in various applications that require spatial variability measurements. Some important of them are listed below [41]:

- 1. Wafer-level Silicon Characterization

- 2. Chip-level Silicon Characterization

- 3. Speed-binning of the manufactured chips to determine their maximum operation frequency

- 4. Post-Silicon tuning technique to measure the presence of large-scale process variation

#### 2.6 Clustering Analysis

Clustering, also known as clustering analysis, is a process of organizing a collection of objects into groups or clusters, where objects within a cluster are more similar to each other than to objects in other clusters. Clustering is an essential component of exploratory data analysis and a widely used technique for statistical data analysis. It finds its application in several fields, including but not limited to pattern classification, recognition, image analysis and information retrieval. bioinformatics, data compression and processing, information encoding and decoding, computer graphics, and machine learning (ML) [44]. Clustering analysis is not a single algorithm, but rather a task that involves grouping objects together based on their similarities in a specific way. There are many algorithms available to perform clustering, each with their own understanding of what makes up a cluster and how to find them efficiently. Clusters can be defined as groups with small distances between members, dense areas in the data space, particular statistical distributions, or other criteria. Clustering can be thought of as a multi-objective optimization problem, with different algorithms and parameter settings suited to different datasets and intended uses. Cluster analysis is an iterative process that involves knowledge discovery and interactive optimization, often requiring adjustments to data preprocessing and model parameters until desired properties are achieved. [44].

#### 2.6.1 Cluster Analysis Algorithms

There have been approximately 100 types of clustering algorithms published so far, though not all provide models for their clusters and cannot be easily categorized. There is no objectively "correct" clustering algorithm, and the most appropriate one for a particular problem often needs to be chosen experimentally. Clustering is subjective and dependent on the individual's perspective. One cluster model may work well for a particular dataset, while another model may fail. Therefore, it is important to carefully consider the problem at hand and experiment with various algorithms until a satisfactory solution is achieved.

A list of some of the clustering algorithms is as follows: [45]

- 1. BFR algorithm

- 2. Canopy clustering algorithm

- 3. Cluster-weighted modeling

- 4. DBSCAN

- 5. K-means clustering

- 6. K-means++

- 7. K-medians clustering

- 8. Nearest-neighbor chain algorithm

K-means++ clustering algorithm has been chosen for this research purpose because of its advantages such as it is faster and provides a better performance. Not all clustering algorithms have their models or library codes because most of them are still theoretical, and also some of them are being used in the industries in recent time, and K-means++ has most advantages and least disadvantages in contrast to others. That's why it has been chosen for this research work.

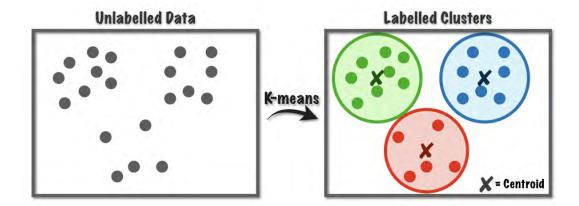

#### 2.6.2 K-means++

K-means++ is a widely used clustering algorithm that aims to partition a given set of observations into k clusters, where each observation is assigned to the cluster with the nearest mean. This algorithm is used for vector quantization, originally from signal processing, and is commonly used in data mining for choosing the initial values or "seeds" for the K-means clustering algorithm. The algorithm was proposed by David Arthur and Sergei Vassilvitskii in 2007 as an approximation algorithm for the K-means problem, and it addresses the limitations of the standard K-means algorithm that sometimes results in poor clusterings [46]. In Fig. 2.8, the basic idea of K-means++ scheme of clustering algorithm has been shown.

Fig. 2.8: K-means++ clustering algorithm

The standard approach to finding an approximate solution to the K-means problem is widely used due to its efficiency in finding reasonable solutions quickly. The algorithm works by randomly selecting k initial cluster centers, then assigning each data point to the nearest cluster center, and finally computing new cluster centers based on the mean of the data points assigned to each cluster. This process iterates until convergence, that is, until the cluster centers no longer change or a maximum number of iterations is reached.

To elaborate, the K-means++ algorithm starts by selecting a single data point as the first cluster center randomly from the given data set. Then, the algorithm selects the next cluster center from the remaining data points in such a way that the probability of choosing a data point as the next center is proportional to its squared distance from the closest existing center. This approach ensures that the new cluster centers are well separated from each other and have a high chance of representing different regions of the data. The remaining cluster centers are selected using the same probabilistic approach until k centers have been chosen. Finally, the standard K-means optimization iterations are performed starting from these initial cluster

centers to obtain the final cluster assignments. This initialization step often results in better clustering results than the random initialization used by the standard Kmeans algorithm.

By choosing the initial centers in a way that spreads them out across the data space, K-means++ aims to avoid getting stuck in suboptimal solutions that can occur when the initial centers are too close together or too far apart. The idea is to increase the chances of finding good starting points for the K-means algorithm that are representative of the overall data structure. This is achieved by selecting centers that are far from each other and from previously chosen centers, which is accomplished by assigning higher probabilities to data points that are farther from the nearest center [46].

#### 2.6.3 Applications of K-means++

K-means++ has been widely applied since its initial proposal. According to a review by Shindler [47], which covers various types of clustering algorithms, the K-means++ approach successfully overcomes some of the problems associated with other methods of defining initial cluster centers for K-means clustering. Lee et al. [48] used K-means++ to create geographical clusters of photographs based on latitude and longitude information attached to the photos. Howard and Johansen reported an application of K-means++ to financial diversification. Ongoing discussions and support for the method can also be found online.

#### **2.7 Anomaly Detection**

Anomaly detection is an important task in various fields, including data mining, machine learning, and computer security. It is used to detect unusual or suspicious behavior, which can be indicative of fraud, errors, or attacks. Anomalies can be detected by comparing data points to a statistical model of normal behavior, or by using unsupervised learning techniques to identify data points that are significantly

different from the majority of the data. Anomaly detection has applications in many areas, including fraud detection in finance, intrusion detection in computer networks, and fault detection in industrial processes [50].

Anomalies or outliers may represent critical events or rare occurrences that are of particular interest and value to the analyst. For example, in fraud detection, detecting an unusual pattern of financial transactions could help uncover fraudulent activity. Similarly, in medical diagnosis, identifying unusual symptoms or test results can aid in the detection of rare diseases or disorders. In these cases, anomaly detection techniques can be used to identify and highlight these rare or unusual events, allowing analysts to investigate further and take appropriate actions [50].

Anomaly detection is a critical task in many real-world applications where detecting rare and unusual events can provide valuable insights and prevent potentially dangerous or costly situations. For example, in cyber security, detecting anomalous network traffic patterns can help identify potential threats and prevent cyber-attacks. In the medical field, anomaly detection can help diagnose diseases by identifying abnormal patterns in medical images or patient data. In finance, detecting unusual patterns in financial transactions can help prevent fraud and financial crimes.

Anomaly detection can be performed using various techniques, including statistical methods, machine learning algorithms, and deep learning techniques. Statistical methods such as the Z-score or Mahalanobis distance are commonly used to detect anomalies based on the deviation from the mean or normal distribution. Machine learning algorithms such as k-nearest neighbors (k-NN) or support vector machines (SVM) can also be used to detect anomalies based on the distance from neighboring points or the separation of classes.

In recent years, deep learning techniques such as autoencoders and generative adversarial networks (GANs) have shown promising results in anomaly detection. Autoencoders can learn to reconstruct input data and detect anomalies based on the reconstruction error, while GANs can generate synthetic data that mimics the real data distribution and detect anomalies based on the difference between the real and generated data.

Despite the growing interest in anomaly detection, it remains a challenging task due to the inherent difficulty in defining what constitutes an anomaly and the high variability and complexity of real-world data. Anomaly detection algorithms often require careful tuning and domain-specific knowledge to achieve satisfactory results. However, with the increasing availability of large and diverse data sets and the development of more advanced algorithms, anomaly detection is becoming an increasingly important and powerful tool in many fields.

There are three main categories of techniques used in anomaly detection:

- 1. Supervised anomaly detection

- 2. Semi-supervised anomaly detection

- 3. Unsupervised anomaly detection

#### 2.7.1 Anomaly scores

Anomaly detection techniques involve identifying data points that are significantly different from the majority of the data. One approach involves developing a model of the normal behavior of the data and marking any data points that fall outside of the predicted range as anomalies. To provide a clear understanding of the results, an anomaly score is typically calculated for each time interval. According to [16], lower anomaly scores indicate positive-class or accepted data, while higher (even very high) scores indicate negative-class or not-acceptable data.

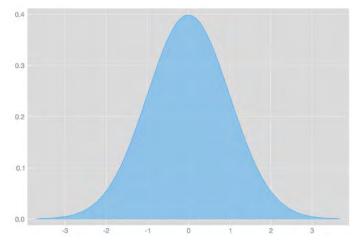

#### 2.8 Probability Density Function (PDF)

Probability distributions are a fundamental concept in probability theory and statistics. They are used to describe and analyze various phenomena in the real world, such as the distribution of heights or weights in a population, the frequency of certain types of weather events, or the likelihood of various outcomes in a game of chance. Different types of probability distributions are used to model different kinds of phenomena, depending on the characteristics of the data and the research question of interest. In Fig. 2.9, the PDF curve for the normal distribution case has been shown.

Fig. 2.9: PDF curve of Normal Distribution

The normal distribution is a very common probability distribution that is widely used in statistics and many other fields. It is also known as the Gaussian distribution, after the mathematician Carl Friedrich Gauss who first described it. The normal distribution has a bell-shaped curve, with the mean, median, and mode all being equal and located at the center of the curve. Many natural phenomena, such as measurements of physical properties, tend to follow a normal distribution, which makes it a useful tool for modeling and analysis. The general form of its probability density function (PDF) is,

$$f(x) = rac{1}{\sigma\sqrt{2\pi}} e^{-rac{1}{2}\left(rac{x-\mu}{\sigma}

ight)^2}$$

....(2.1)

In eq<sup>n</sup>. 2.1, The parameter  $\mu$  represents the mean or expected value of the distribution, and it also serves as its median and mode. On the other hand, the parameter  $\sigma$  corresponds to the distribution's standard deviation. The variance of the distribution is  $\sigma^2$ .

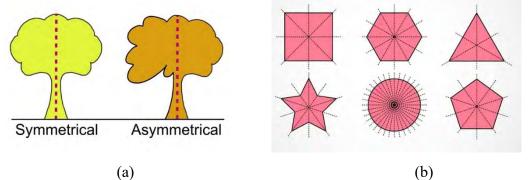

#### 2.9 Symmetry Analysis

Symmetry has a more precise definition in mathematics than in everyday language. It refers to an object that remains unchanged under certain transformations, such as translation, reflection, rotation, or scaling. In other words, a symmetric object looks the same before and after the transformation. Symmetry can be observed in various ways, including with respect to time, spatial relationships, geometric and other functional transformations, as well as in abstract objects like models, language, and music. Asymmetry, on the other hand, refers to the absence or violation of symmetry [49].

Fig. 2.10: (a) Difference between symmetrical and asymmetrical shapes. (b) Some other symmetrical shapes

In this work, symmetry analysis or symmetrical neighborhood means the FP data of the KFFs have symmetry because the FPGAs have the similar or symmetrical type of architecture. But this will not be held true for the recycled or aged FPGAs because after starting of the using of the FPGAs, their fingerprint will be changed. This indicates that, for the fresh FPGAs, there will be symmetricity, but for aged or recycled FPGAs these FP will be changed and thus there will be no symmetricity. Thus, if this symmetric property can be analyzed then the recycled FPGAs can be detected. This theory is explained below in the Fig. 2.11.

Fig. 2.11: Key idea of the Symmetry Analysis

In Fig. 2.11, fingerprints for two different paths of the same KFF have been analyzed, and it has been shown as the high values of the PDFs in Red and Blue curves. Both of them are having similar types of curves with almost in the same region. They are equivalent but not fully same due to the process variation of the IC chips. And again this process has been done with that FPGA but making it

artificially aged or recycled, and after analyzing it's PDF in small red curve in the left-side, we see that fresh and recycled FPGAs have different types of PDF curves which can be used to analyze the binary classification of fresh or recycled FPGAs.

#### 2.10 uLSIF Method

The least squares (LS) method is a type of mathematical regression analysis utilized to determine the line of best fit for a given set of data, which can visually illustrate the relationship between the data points. The data points represent the connection between a known independent variable and an unknown dependent variable [51]. In this study, the uLSIF (unconstrained Least-Squares Importance Fitting) method was employed, which is a variant of the LS method. The uLSIF-based approach to anomaly detection is computationally efficient, enabling it to be applied to large-scale datasets.

### 2.11 Receiver Operating Characteristic (ROC) Curve

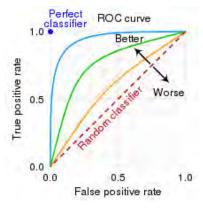

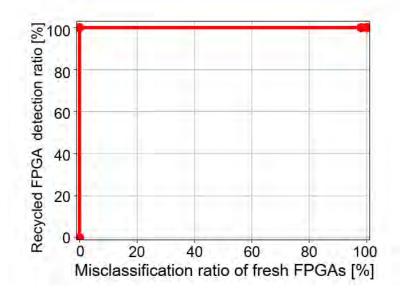

An ROC curve is a visualization tool that displays the performance of a binary classifier system across various discrimination thresholds. The name "ROC curve" originated from its use in military RADAR receiver operations during World War II. The curve is constructed by plotting the true positive rate (TPR) against the false positive rate (FPR) at different threshold values. TPR is also known as sensitivity, recall, or probability of detection, while FPR is also known as probability of false alarm. A true positive (TP) indicates a correct detection of the presence of a condition or characteristic, while a false positive (FP) indicates an incorrect detection of a condition or characteristic that is not present. In Fig.2.12, the ROC curve has been shown for more clarity.

Fig. 2.12: ROC curve

ROC curves are commonly used in medical research, machine learning, and other fields where binary classification is important. In medical research, for example, ROC curves are often used to evaluate the accuracy of diagnostic tests. In machine learning, ROC curves are used to evaluate the performance of binary classifiers, such as support vector machines (SVM) or neural networks.

A perfect classifier would have a TPR of 1 and an FPR of 0, meaning it would correctly identify all positive cases and never mistakenly identify a negative case as positive. In reality, however, most classifiers have limitations, and ROC curves help to illustrate the trade-off between sensitivity and specificity.

One way to summarize the diagnostic ability of a binary classifier using the ROC curve is to calculate the area under the curve (AUC). The AUC provides a single number that represents the overall performance of the classifier. An AUC of 1 indicates perfect discrimination, while an AUC of 0.5 indicates a classifier that is no better than random guessing.

ROC curves are a useful tool for selecting a threshold that balances sensitivity and specificity based on the needs of the application. For example, in medical research, a test with high sensitivity may be preferred if a false negative result could be life-threatening, while a test with high specificity may be preferred if false positives would lead to unnecessary treatments or procedures.

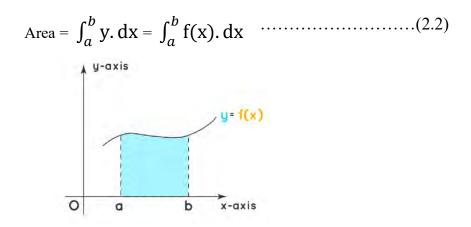

#### 2.11.1 Area Under the Curve (AUC)

It is worth noting that the area under the curve (AUC) can have various interpretations and applications in different fields. For example, in economics and finance, the area under the demand curve can represent the total revenue generated by a product, while in probability theory, the area under the probability density function curve represents the total probability of an event occurring. In addition, the area under the ROC curve, as mentioned earlier, is a common evaluation metric for binary classifiers in machine learning.

Overall, the concept of area under the curve and its calculation through integration is a fundamental concept in calculus and has many practical applications in different fields.