## ANALYTICAL MODELING OF THRESHOLD VOLTAGE AND DRAIN CURRENT OF GATE AND CHANNEL ENGINEERED DOUBLE GATE MOSFET

A thesis submitted to

the Department of Electrical and Electronic Engineering

of

Bangladesh University of Engineering and Technology

in partial fulfillment of the requirements

for the degree of

#### MASTER OF SCIENCE IN ELECTRICAL AND ELECTRONIC ENGINEERING

By,

MD. ARAFAT MAHMUD

Student ID: 0412062244 F

## BANGLADESH UNIVERSITY OF ENGINEERING AND TECHNOLOGY

December' 2014

## DECLARATION

It is hereby declared that this thesis or any part of it has not been submitted elsewhere for the award of any degree or diploma.

-----

(Md. Arafat Mahmud)

# DEDICATION

I would like to dedicate this work to my parents who have always been caring and supportive to me.

## **APPROVAL CERTIFICATE**

The thesis titled "ANALYTICAL MODELING OF THRESHOLD VOLTAGE AND DRAIN CURRENT OF GATE AND CHANNEL ENGINEERED DOUBLE GATE MOSFET" submitted by Md. Arafat Mahmud, Student ID: 0412062244F, Session: April 2012 has been accepted as satisfactory in partial fulfillment of the requirement for the degree of MASTER OF SCIENCE IN ELECTRICAL AND ELECTRONIC ENGINEERING on 24th December, 2014.

## **BOARD OF EXAMINERS**

| 1.<br>Dr. Samia Subrina<br>Associate Professor,<br>Department of EEE, Bangladesh University of Engineering and Technology,<br>Dhaka-1000         | Chairman<br>Supervisor |

|--------------------------------------------------------------------------------------------------------------------------------------------------|------------------------|

| 2.<br>Dr. Taifur Ahmed Chowdhury<br>Professor and Head,<br>Department of EEE, Bangladesh University of Engineering and Technology,<br>Dhaka-1000 | Member<br>(Ex-Officio) |

| 3.<br>Dr. Shaikh Asif Mahmood<br>Assistant Professor,<br>Department of EEE, Bangladesh University of Engineering and Technology,<br>Dhaka-1000   | Member                 |

| 4.<br>Dr. Md. Feroz Alam Khan<br>Professor,<br>Department of Physics, Bangladesh University of Engineering and Technology,<br>Dhaka-1000         | Member<br>(External)   |

# TABLE OF CONTENTS

| List of Figures       | ix   |

|-----------------------|------|

| List of Symbols       | xi   |

| List of Abbreviations | XV   |

| Acknowledgement       | xvi  |

| Abstract              | xvii |

| Chapter 1 | Introduction           | 1-8 |

|-----------|------------------------|-----|

| 1.1       | Literature Review      | 2   |

| 1.2       | Objectives of the Work | 6   |

| 1.3       | Thesis Outline         | 7   |

| Chapter 2 | Theoretical Background                 | 9-14 |

|-----------|----------------------------------------|------|

| 2.1       | Drain Induced Barrier Lowering (DIBL)  | 9    |

| 2.2       | Hot Carrier Effect (HCE)               | 10   |

| 2.3       | Threshold Voltage Roll-off             | 11   |

| 2.4       | Channel Length Modulation (CLM) Effect | 11   |

| 2.5       | Gate Engineering                       | 12   |

| 2.6       | Channel Engineering                    | 13   |

| 2.7 Effective Oxide Thickness (EOT) | 13 |

|-------------------------------------|----|

|-------------------------------------|----|

| Chapter 3 | Analytical Modeling of Proposed Device                                                               | 15-32 |

|-----------|------------------------------------------------------------------------------------------------------|-------|

| 3.1       | Physical Device Structure and Dimensions                                                             | 15    |

| 3.2       | Doping Concentration Profile                                                                         | 15    |

| 3.3       | Fringing Phenomena in Device                                                                         | 18    |

| 3.4       | Channel Potential                                                                                    | 20    |

| 3.5       | Threshold Voltage                                                                                    | 24    |

| 3.6       | Drain to Source Current                                                                              | 26    |

| 3.7       | Threshold Voltage Roll-off                                                                           | 32    |

| 3.8       | Drain Induced Barrier Lowering                                                                       | 32    |

|           |                                                                                                      |       |

| Chapter 4 | Results and Discussion                                                                               | 33-54 |

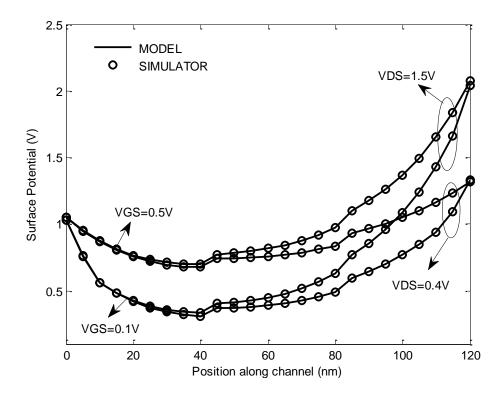

| 4.1       | Surface Potential along the Channel : Variation with Drain and Gate Bias                             | 33    |

| 4.2       | Electric Field along the Channel : Comparison among Various Device Structures                        | 34    |

| 4.3       | Threshold Voltage : Changes with Different<br>Channel Lengths and Substrate Doping<br>Concentrations | 35    |

| 4.4       | Threshold Voltage Roll-off : Contrast among Various Device Structures                                | 36    |

| 4.5       | Threshold Voltage Roll-off : Effect of Drain Bias                                                    | 37    |

| 4.6       | Drain Induced Barrier Lowering (DIBL) :                                                              | 38    |

|      | Comparison among Various Device Structures                                                         |    |

|------|----------------------------------------------------------------------------------------------------|----|

| 4.7  | Drain Induced Barrier Lowering (DIBL) : Effect of Halo Doping Concentration                        | 39 |

| 4.8  | Drain to Source Current: Variation with Gate Voltage for Different Drain Bias                      | 40 |

| 4.9  | Drain to Source Current: Variation with Drain Voltage for Different Gate Bias                      | 41 |

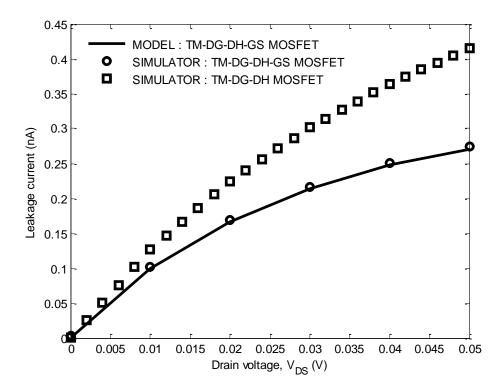

| 4.10 | Leakage Current: Contrast among Various Device Structures                                          | 43 |

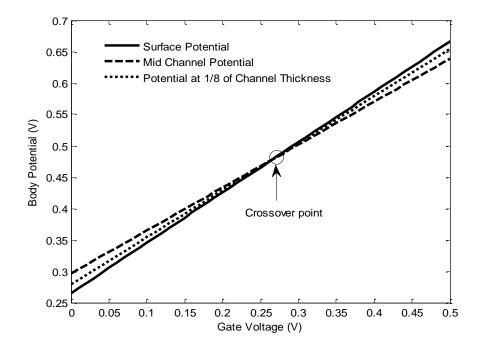

| 4.11 | Body Potential and Pseudo Flat Band Point (Crossover Point)                                        | 44 |

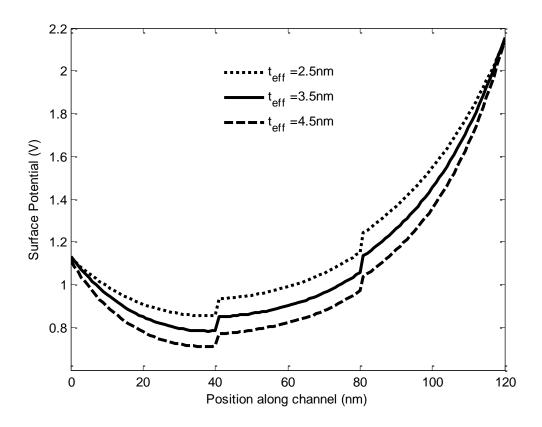

| 4.12 | Surface Potential along the Channel: Variation with Effective Oxide Thickness                      | 45 |

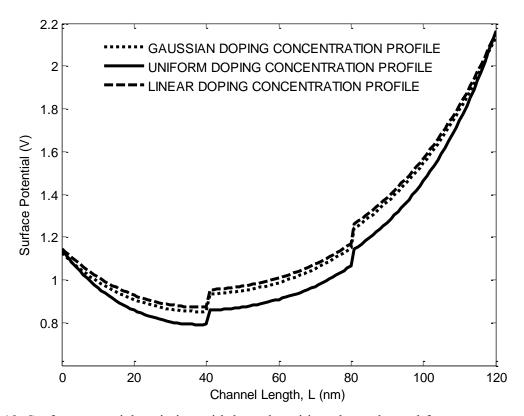

| 4.13 | Surface Potential along the Channel: Effect of Doping Concentration Profile                        | 46 |

| 4.14 | Surface Potential along the Channel: Variation with Silicon Channel Thickness                      | 47 |

| 4.15 | Threshold Voltage: Effect of Effective Oxide Thickness                                             | 48 |

| 4.16 | Threshold Voltage: Effect of Drain Bias                                                            | 48 |

| 4.17 | Threshold Voltage: Variation with Channel Thickness                                                | 49 |

| 4.18 | Threshold Voltage: Effect of Doping Concentration Profile                                          | 50 |

| 4.19 | Drain to Source Current: Effect of Effective Oxide<br>Thickness with Different Gate and Drain Bias | 51 |

| 4.20 | Drain to Source Current: Effect of Silicon Channel<br>Thickness with Different Gate and Drain Bias | 52 |

| 4.21 | Drain to Source Current: Variation with Doping Concentration Profile                               | 53 |

| Chapter 5 | Conclusion           | 55-57 |

|-----------|----------------------|-------|

| 5.1       | Conclusion           | 55    |

| 5.2       | Scope of Future Work | 56    |

|           |                      |       |

### References

59-61

# **LIST OF FIGURES**

| Fig. 2.1 | Drain Induced Barrier Lowering phenomena in Short Channel MOSFET                                                                                                                                       | 10 |

|----------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

| Fig. 2.2 | Channel Length Modulation (CLM) Effect in MOSFET device                                                                                                                                                | 12 |

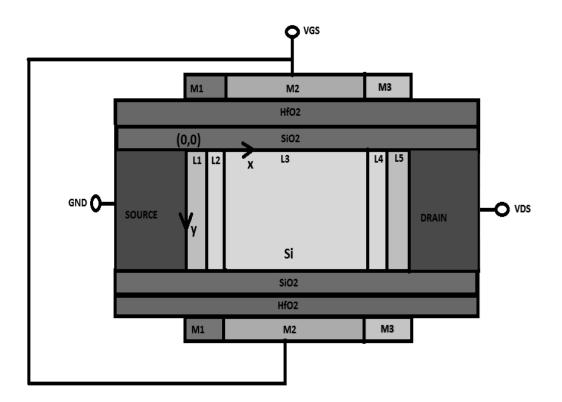

| Fig. 3.1 | Schematic cross sectional view of triple material double gate double halo gate stacked MOSFET                                                                                                          | 16 |

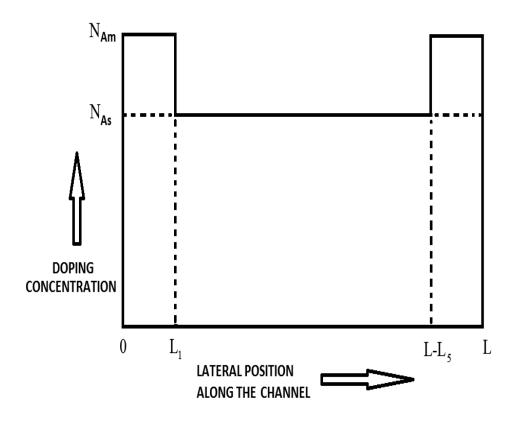

| Fig. 3.2 | Plot of doping concentration along the lateral position of the channel                                                                                                                                 | 17 |

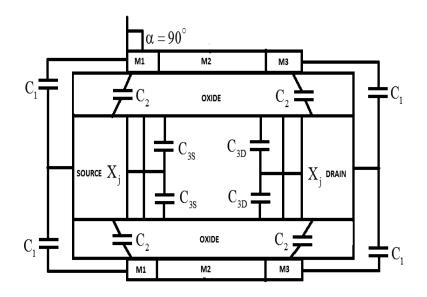

| Fig. 3.3 | Outer, inner and overlap fringing capacitance components                                                                                                                                               | 18 |

| Fig. 4.1 | Surface potential variation with lateral position along channel from source to drain for $V_{GS}$ =0.1V, 0.5V and $V_{DS}$ =0.4V, 1.5V                                                                 | 34 |

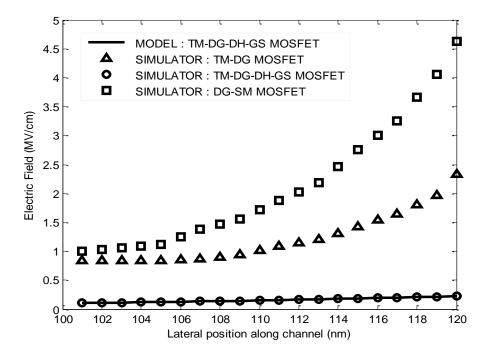

| Fig. 4.2 | Variation in electric field with lateral position along channel(100-120nm) for TM- DG- DH-GS MOSFET, TM-DG MOSFET and SM-DG MOSFET with $V_{GS}$ =0.1V and $V_{DS}$ =0.1V                              | 35 |

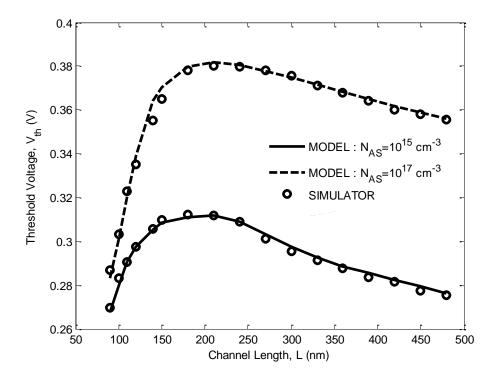

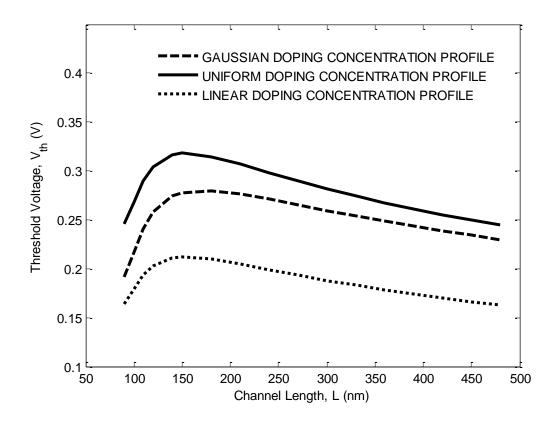

| Fig. 4.3 | Threshold voltage of the device along the channel length for $N_{Am} = 1.2 \times 10^{18}$ /cm <sup>3</sup> , $N_{As} = 10^{15}$ /cm <sup>3</sup> and $10^{17}$ /cm <sup>3</sup> with $V_{DS} = 0.5$ V | 36 |

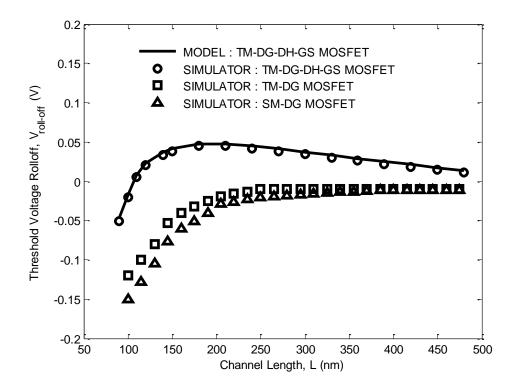

| Fig. 4.4 | Threshold voltage roll-off along the channel length for TM-DG-DH-GS MOSFET, TM-DG MOSFET and SM-DG MOSFET for $V_{DS} = 0.05V$                                                                         | 37 |

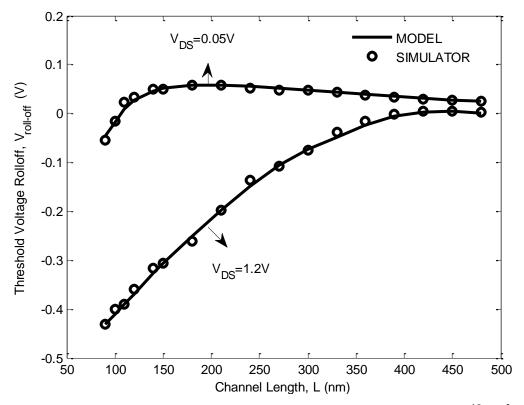

| Fig. 4.5 | Plot of threshold voltage roll-off vs channel length for $N_m = 1.2 \times 10^{18}$ /cm <sup>3</sup> and $N_s = 10^{15}$ /cm <sup>3</sup> for $V_{DS} = 0.05$ V and 1.2V                               | 38 |

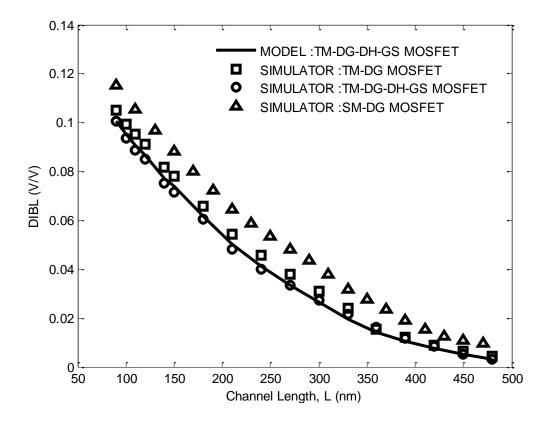

| Fig. 4.6 | Drain induced barrier lowering (DIBL) variation with channel length for TM-<br>DG-DH-GS MOSFET, TM-DG MOSFET and SM-DG MOSFET                                                                          | 39 |

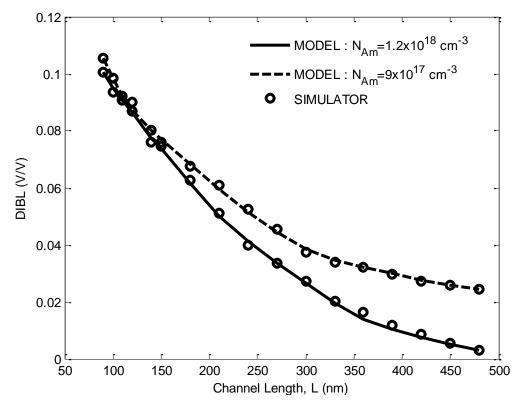

| Fig. 4.7 | Plot of Drain induced barrier lowering(DIBL) vs channel length, L for $N_{Am} = 1.2 \times 10^{18}$ /cm <sup>3</sup> , $9 \times 10^{17}$ /cm <sup>3</sup> and $N_{As} = 10^{15}$ /cm <sup>3</sup>     | 40 |

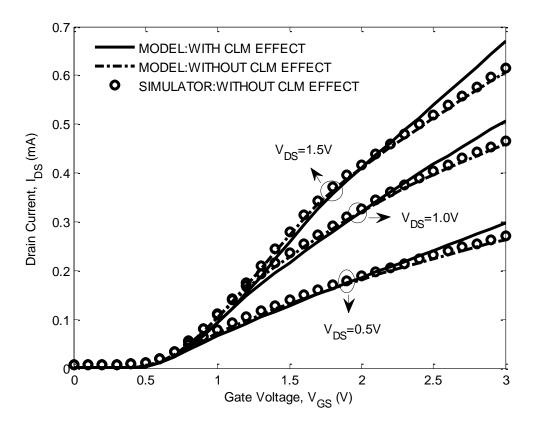

| Fig. 4.8 | Drain to source current, with and without Channel Length Modulation (CLM) effect, as a function of gate voltage for $V_{DS}$ =0.5V, 1V and 1.5V                                                        | 41 |

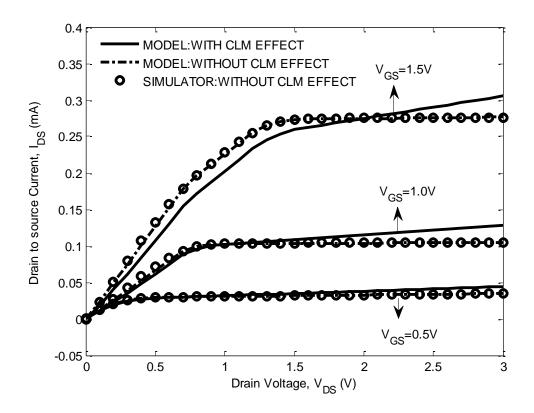

| Fig. 4.9 | Plot of Drain to source current, with and without Channel Length Modulation (CLM) effect, as a function of drain voltage for $V_{GS}=0.5$ V, 1V and 1.5V                                               | 42 |

- Fig. 4.10 Leakage current in TM-DG-DH-GS MOSFET and TM-DG-DH MOSFET as a 43 function of drain voltage with  $t_{eff}=3.5$ nm and  $V_{GS}=0$ V

- Fig. 4.11 Plot of body potential at x=30nm along with gate voltage with  $V_{DS} = 0.1V$  for 44  $t_{si} = 25nm$

- Fig. 4.12 Surface potential variation with lateral position along channel from source to 45 drain for effective oxide thickness,  $t_{eff} = 2.5$ nm, 3.5nm and 4.5nm with V<sub>GS</sub> =0.5V and V<sub>DS</sub>=1.5V

- Fig. 4.13 Surface potential variation with lateral position along channel from source to 46 drain for Gaussian, Uniform and Linear doping profile concentration with V<sub>GS</sub> = 0.5V and V<sub>DS</sub>=1.5V

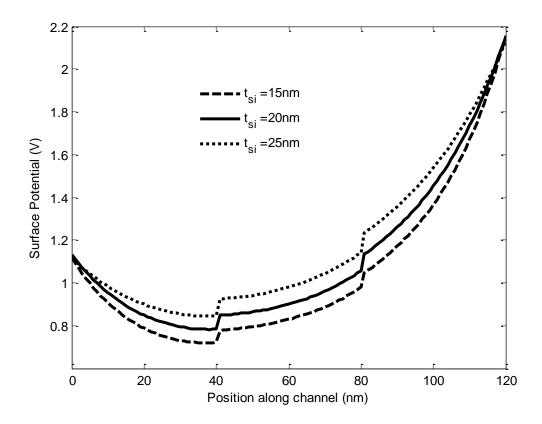

- Fig. 4.14 Surface potential variation with lateral position along channel from source to drain for channel thickness,  $t_{si} = 15$ nm, 20nm and 25nm with  $V_{GS} = 0.5$ V and  $V_{DS} = 1.5$ V

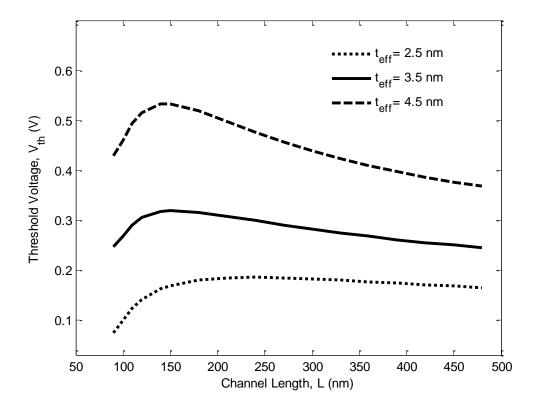

- Fig. 4.15 Threshold voltage of the device along the channel length for effective oxide 48 thickness,  $t_{eff}$ = 4.5nm, 3.5nm and 2.5nm with  $V_{DS}$ =1.5V

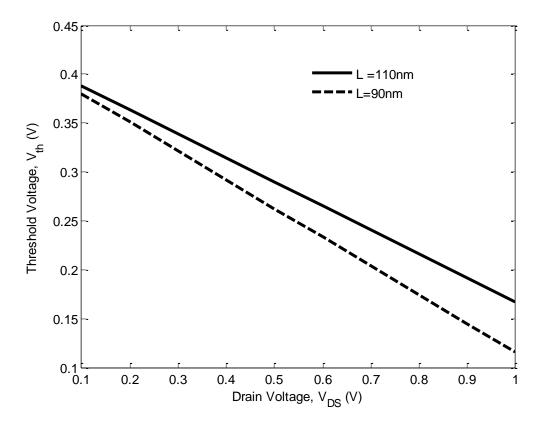

- Fig. 4.16 Plot of threshold voltage vs drain voltage for Channel length, L=120nm and 49 90nm

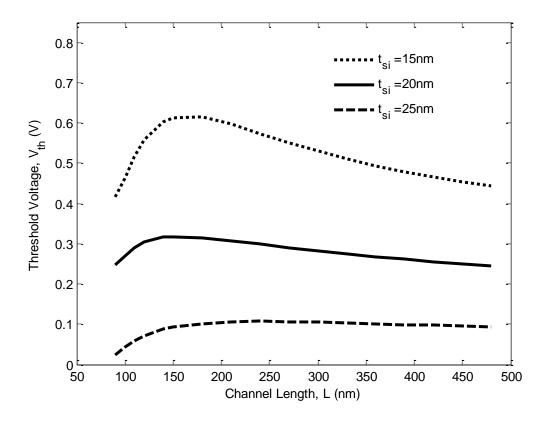

- Fig. 4.17 Threshold voltage of the device along the channel length for channel thickness, 50  $t_{si} = 15$ nm, 20nm and 25nm with  $V_{DS} = 1.5$ V

- Fig. 4.18 Threshold voltage of the device along the channel length Gaussian, Uniform 51 and Linear doping profile concentration with  $V_{DS}=1.5V$

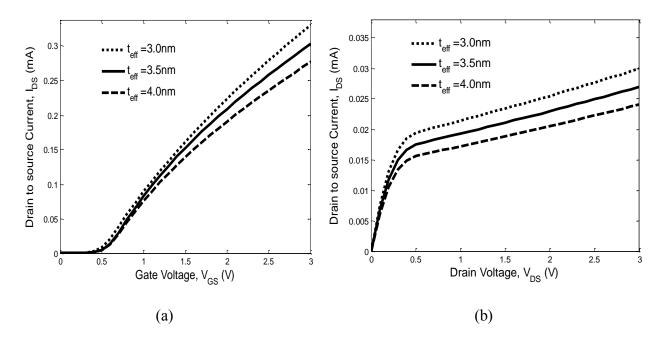

- Fig. 4.19 Plot of drain to source current, with Channel Length Modulation (CLM) effect 52 for effective channel thickness,  $t_{eff}$  =3.0nm, 3.5nm and 4.0nm as a function of (a) gate voltage for V<sub>DS</sub>=0.5V and of (b) drain voltage for V<sub>GS</sub>=0.5V

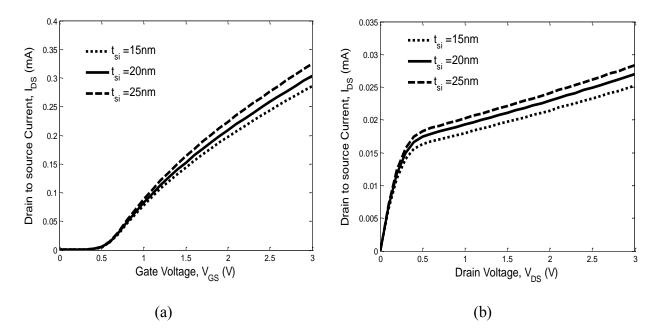

- Fig. 4.20 Plot of drain to source current, with Channel Length Modulation (CLM) effect 53 for channel thickness,  $t_{si}$  =15nm, 20nm and 25nm as a function of (a) gate voltage for  $V_{DS}$ =0.5V and of (b) drain voltage for  $V_{GS}$ =0.5V

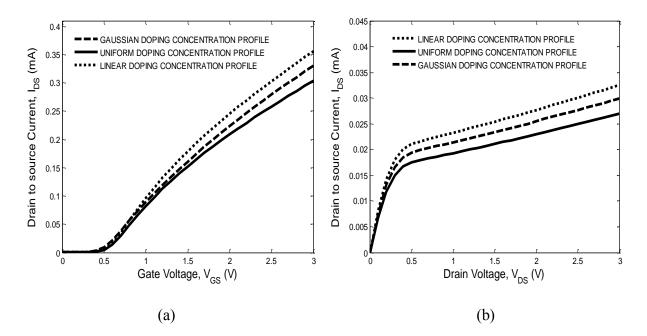

- Fig. 4.21 Plot of drain to source current, with Channel Length Modulation (CLM) effect 54 for uniform, gaussian and linear doping concentration profile as a function of (a) gate voltage for  $V_{DS}$ =0.5V and of (b) drain voltage for  $V_{GS}$ =0.5V

# LIST OF SYMBOLS

| Symbol                                                   | Meaning                                                                                                                  |

|----------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------|

| $\Phi_{\!_{m1}}$ , $\Phi_{\!_{m2}}$ and $\Phi_{\!_{m3}}$ | Work functions of the three materials in the gate electrode                                                              |

| L                                                        | Channel length                                                                                                           |

| $L_1, L_2, L_3, L_4 \text{ and } L_5$                    | Length of the five channel regions 1,2,3,4 and 5                                                                         |

| $t_{eff}$                                                | Effective oxide thickness                                                                                                |

| $t_{sio2}$                                               | SiO <sub>2</sub> layer thickness                                                                                         |

| t <sub>Hfo2</sub>                                        | HfO <sub>2</sub> layer thickness                                                                                         |

| € <sub>sio2</sub>                                        | Permittivity of SiO <sub>2</sub>                                                                                         |

| ∈ <sub>Hfo2</sub>                                        | Permittivity of HfO <sub>2</sub>                                                                                         |

| N <sub>Am</sub>                                          | Halo doping concentration near drain and source region                                                                   |

| $N_{As}$                                                 | Substrate doping concentration                                                                                           |

| $\mathbf{N}_{eff}$                                       | Average doping concentration for uniform doping concentration profile                                                    |

| ${ m N}_{ m eff,\ linear}$                               | Average doping concentration for linear doping concentration profile                                                     |

| ${ m N}_{ m eff,\ gaussian}$                             | Average doping concentration for gaussian doping concentration profile                                                   |

| $C_1$                                                    | Outer fringing capacitance component on each side of front and back gate between gate and source or gate and drain elect |

| C <sub>2</sub>                                           | Direct overlap capacitance between gate and source or gate and drain junction                                            |

| C <sub>3</sub>                          | Inner fringing capacitance between gate and source side junction or gate and drain side junction       |

|-----------------------------------------|--------------------------------------------------------------------------------------------------------|

| $C_{\mathrm{F}}$                        | Maximum value of inner fringing capacitance                                                            |

| $\mathbf{t}_{\text{gate}}$              | Gate electrode thickness                                                                               |

| W                                       | Channel width                                                                                          |

| α                                       | Slanting angle                                                                                         |

| $\mathbf{X}_{j}$                        | Source/drain junction depth                                                                            |

| $Q_{\text{DF}}$                         | Charge induced at drain end at each side of the front and back gate due to inner fringing capacitance  |

| $\boldsymbol{Q}_{\text{SF}}$            | Charge induced at source end at each side of the front and back gate due to inner fringing capacitance |

| $V_{\text{DS,eff}}$                     | Effective drain to source voltage                                                                      |

| $V_{fb}$                                | Flat band voltage                                                                                      |

| $V_{th}$                                | Threshold voltage                                                                                      |

| $\boldsymbol{\phi}_F$                   | Fermi potential                                                                                        |

| $V_{\rm T}$                             | Thermal voltage                                                                                        |

| n <sub>i</sub>                          | Intrinsic carrier concentration                                                                        |

| $V_{\scriptscriptstyle FD}$             | Fringing potential at drain end                                                                        |

| $V_{\rm FS}$                            | Fringing potential at source end                                                                       |

| Ψ                                       | Channel potential                                                                                      |

| $\chi_{si}$                             | Electron affinity of Si                                                                                |

| $\mathrm{E}_{\mathrm{g}_{\mathrm{si}}}$ | Energy band gap of Si                                                                                  |

| q                          | Electron charge                                        |

|----------------------------|--------------------------------------------------------|

| $Q_0$                      | Effective surface charge                               |

| $\mathbf{V}_{\mathrm{bi}}$ | Built-in potential                                     |

| $N_{\text{DS}}$            | Doping concentration at drain and source region        |

| t <sub>si</sub>            | Silicon channel thickness                              |

| λ                          | Characteristic length                                  |

| $\Psi_{c}$                 | Mid-channel potential                                  |

| $\Psi_{\rm S}$             | Surface potential                                      |

| $\Psi_{\text{s,min}}$      | Minimum surface potential                              |

| r <sub>oc</sub>            | Ratio of gate oxide capacitance to channel capacitance |

| $V_{\text{thL}}$           | Long channel threshold voltage                         |

| μ                          | Electron mobility                                      |

| $Q_{I}$                    | Inversion layer charge                                 |

| I <sub>DRIFT</sub>         | Drift current component in drain to source current     |

| $I_{\text{DIFF}}$          | Diffusion current component in drain to source current |

| $\mu_0$                    | Low carrier mobility                                   |

| E <sub>c</sub>             | Critical electric field                                |

| $Q_s$                      | Surface charge                                         |

| Q <sub>D</sub>             | Depletion layer charge                                 |

| Т                          | Temperature                                            |

| $I_{\text{DS,tot}}$   | Drain to source current without CLM effect |

|-----------------------|--------------------------------------------|

| $I_{\rm DS,CLM}$      | Drain to source current with CLM effect    |

| $V_{\text{DP}}$       | Pinch-off voltage                          |

| V <sub>A</sub>        | Early voltage                              |

| $V_{\text{roll-off}}$ | Threshold voltage roll-off                 |

# LIST OF ABBREVIATIONS

## Abbreviation

# **Full Form**

| SCE                | Short Channel Effect                                      |

|--------------------|-----------------------------------------------------------|

| HCE                | Hot Carrier Effect                                        |

| DIBL               | Drain Induced Barrier Lowering                            |

| MOSFET             | Metal Oxide Semiconductor Field Effect Transistor         |

| SOI MOSFET         | Silicon on Insulator MOSFET                               |

| SON MOSFET         | Silicon on Nothing MOSFET                                 |

| SM MOSFET          | Single Material MOSFET                                    |

| DM MOSFET          | Double Material MOSFET                                    |

| TM MOSFET          | Triple Material MOSFET                                    |

| SG MOSFET          | Single Gate MOSFET                                        |

| DG MOSFET          | Double Gate MOSFET                                        |

| TM-DG MOSFET       | Triple Material Double Gate MOSFET                        |

| SM-DG MOSFET       | Single Material Double Gate MOSFET                        |

| TM-DG-DH-GS MOSFET | Triple Material Double Gate Double Halo Gate Stack MOSFET |

| EOT                | Effective Oxide Thickness                                 |

| CLM                | Channel Length Modulation                                 |

## ACKNOWLEDGEMENT

I would like to express my sincere indebtedness to my thesis supervisor, Dr. Samia Subrina, Associate Professor, Department of Electrical and Electronic Engineering, Bangladesh University of Engineering and Technology, for her insightful suggestions, guidance and support throughout the thesis work. She inspired me to chase the desperate problems with patience and knowledge. It is because of her perceptive guidance and instructions, I have been able to complete the thesis work.

Thanks to my family members, well-wishers and friends who helped in various ways to complete the work. I would like to express my heartiest gratitude to my parents for whom I am standing at this position.

## ABSTRACT

Advancement of technology exerts enormous pressure on scaling of devices with a view of improved performance. The scaling of device technology faces significant challenges to control the short channel effects (SCE) and limits the further shrinkage of device size. A number of new architectures have been reported to mitigate these effects. Double gate MOSFET is a promising candidate because of its SCE handling capability. The gate electrodes with more than one material with the different work functions have better control over SCEs. In a Triple Material Double Gate MOSFET, both gate electrodes are composed of three different materials which screen the effect of drain on the source-channel barrier and suppress DIBL (Drain Induced Barrier Lowering). In device of sub-100 nm regime, charge sharing and DIBL effect become very severe. To overcome this issue, halo doping is used i.e., substrate doping is increased selectively near the depletion region. To deal with leakage current, inclusion of high k dielectric has been proved effective. The combined advantages of gate and channel engineering techniques can be achieved in symmetric halo doped gate stacked triple material double gate MOSFET. In this work, a two dimensional analytical model of channel potential, threshold voltage and drain to source current of a triple material double gate double halo gate stacked MOSFET has been developed. Two dimensional Poisson's equations with proper boundary conditions have been solved to obtain the channel potential considering parabolic approximation. For accurate modeling of the device, bias dependent inner fringing capacitance and effective surface charge have been considered. Basic drift-diffusion equation has been used to model the drain to source current. Mid-channel potential of the device has been used instead of surface potential in the current modeling considering the fact that the punch-through current is not confined only to the surface in a fully depleted MOSFET. Thus, an expression of pinch-off voltage has been derived for modeling the drain current in saturation region accurately. Channel length modulation effect has also been included in the model which lifts up the positive slope in the current voltage characteristics in the pinch off region of a MOS device in deep submicron level. The device performance has been analyzed with the variation in device parameters, such as channel length,

channel thickness, doping profile etc. Various short channel effects like drain induced barrier lowering, gate leakage, threshold voltage roll-off have also been investigated. This structure shows excellent ability in suppressing various short channel effects. The analytical model of the device will give a deeper insight of the device physics and characteristics. Finally, the proposed model results have been validated against the data obtained from a commercially available numerical device simulator.

## **CHAPTER ONE**

### INTRODUCTION

Continuous scaling of device technology originates significant difficulties and challenges to control the short channel effects (SCE) and hinders the further shrinkage of device size. A number of new architectures have been reported to mitigate these effects and improve device performance. Double gate (DG) MOSFET is advantageous over the traditional single gate (SG) structure because of its higher drive current capability and transconductance, lower off-current, better scaling capability, better Drain induced barrier lowering (DIBL) and effective SCE handling capability [1-9] as two gates control the channel from both sides.

Efficient gate as well as channel engineering contributes significantly to minimize various SCEs [5-8]. The gate electrodes with multiple materials with the different work functions can mitigate the effects of SCE. Some studies have dealt with dual material [10]-[14] and triple material [15]-[17] gate MOSFET. In a symmetric tripe material double gate (TM-DG) MOSFET, both the front and back gate electrodes are composed of three materials with different work functions and the material close to the source has the highest work function while that close to drain has the lowest (n-channel MOSFET). It gives a two-step surface potential profile that screens the effect of drain on the source-channel barrier and suppresses DIBL effectively. This gate engineering also allows to have the same threshold voltage for the device with a reduced doping concentration in the channel region resulting in better immunity against mobility degradation and hence higher transconductance. Some theoretical and experimental works on the TM gates have already been published.

To struggle against leakage associated with continual scaling of gate oxide, inclusion of high k dielectric over the traditional gate oxide  $(SiO_2)$  layer has been reported to be beneficial in the literatures [18-19]. The gate stack structure also improves SCEs, DIBL, hot carrier effects and channel length modulation.

In device of sub-100 nm regime, source and drain depletion region tend to approach each other and charge sharing effect becomes very severe. In addition, drain induced barrier lowering effect worsens the situation [20]. Therefore, depletion region width in a short-channel device must be restricted. But increasing substrate doping concentration everywhere is not a suitable solution to this problem, since this will increase the body effect co-efficient. Large value of body effect coefficient will cause large variation of threshold voltages with change in substrate bias which causes complication in circuit design. To overcome these effects, as a form of channel engineering, double halo doping is used i.e. substrate doping is increased selectively using ion implantation around source and drain region, where depletion region occurs. Triple material double gate double halo gate stacked (TM-DG-DH-GS) MOSFET incorporates the combined advantage of the gate engineering and the channel engineering techniques and is expected to provide further improvement in the performance with enhanced suppression of short channel effects.

#### **1.1 Literature Review**

Analytical and simulation works on double gate MOSFET have already been presented in some literatures [1]-[9]. Ernst *et al.* [1] have lifted up the superiority of DG MOSFETs compared to SG MOSFETs in terms of better subthreshold swing and improved transconductance. Quantum calculations have been combined with classical models in it to show the comparison. Suzuki *et al.* [2] have established a scaling theory for DG SOI MOSFET suggesting that a device can be designed with a gate length of less than 0.1 µm while maintaining the ideal subthreshold factor. Lu *et al.* [3] have presented an analytic potential model for long-channel symmetric and asymmetric double-gate MOSFETs. The model is derived rigorously from the exact solution to Poisson's and current continuity equation without the charge-sheet approximation. The resulting analytic expressions of the drain-current, terminal charges, and capacitances for long-channel DG MOSFETs in [3] are continuous in all operation regions, i.e., linear, saturation, and subthreshold, making it suitable for compact modeling. Ieong *et al.* [4] have explored the advantageous flexibility in a DG MOSFET by individual control of the two gates for low-power and mixed-signal applications. Chen *et al.* [5] have presented a compact, physical, short-channel

threshold voltage model for undoped symmetric double-gate MOSFETs based on an analytical solution of the two-dimensional (2-D) Poisson equation with the mobile charge term included. Taur *et al.* [6] and Tsormpatzoglou *et al.* [7] have put efforts on developing analytical model for undoped symmetrical DG MOSFETs, while Cerdeira *et al.* [8] have presented the analytical model for doped symmetrical DG MOSFETs. Young *et al.* [9] have investigated the conduction phenomena in fully depleted SOI DG MOSFET.

The advantages associated with gate engineering in the form of using multiple materials in the gate electrode in dealing with SCEs have been reported in some previous research works [10]-[17]. Among these works, some works [10]-[14] have dealt with dual material (DM) MOSFETs while the rest of them had their focus on triple material (TM) MOSFETs. Reddy et al. [10] have presented the analytical modeling of an asymmetrical DM-DG SOI MOSFET and it has been shown that SCEs in this structure are suppressed because of the perceivable step in the surfacepotential profile, which screens the drain potential. It has been further demonstrated that the DM-DG structure provides a simultaneous increase in the transconductance and a decrease in the drain conductance when compared with the DG structure. Sarkhel et al. [11] have lifted up the enhancement in the device scalability in a DM-DG SON MOSFET compared to a SM-DG SON MOSFET by means of the threshold control with multiple material electrode. Pal et al. [12] and Li et al. [13] have reported the role of double material in suppressing SCEs in a surrounding gate DM MOSFET. Sarker et al. [14] have developed an analytical subthreshold surface potential model of asymmetric pocket-implanted Double-Halo DM-SG-DH and DM-SG-SH MOSFET. The model is derived using the pseudo-2D analysis by applying the Gauss's law to an elementary rectangular box in the channel depletion region, considering the surface potential variation with the channel depletion layer depth. The asymmetric pocket-implanted model in this work takes into account the effective doping concentration of the two linear pocket profiles at the source and the drain ends. The inner fringing field capacitances are also considered in the model for accurate estimation of the subthreshold surface potential at the two ends of the MOSFET. Dhanaselvama et al. [15] presented a simulation based work on TM-DG MOSFET

and showed the improvement of SCEs such as DIBL, HCE and CLM effects compared to DM-DG MOSFET and Conventional DG MOSFET.

Razavi *et al.* [16] have developed an analytical model for the threshold voltage of fully depleted short-channel TM-DG MOSFET. In this work, lightly doped channel has been taken to enhance the device performance in terms of higher carrier mobility and minimum dopant fluctuation. The improved hot carrier effects over the double-material DG MOSFETs have been demonstrated. Different length ratios of three channel regions related to different gate materials have been optimized to minimize SCEs. However, it has not considered the inclusion of High-k dielectric for minimizing leakage current or halo doped channel for improved performance against DIBL. Besides, drain to source current model for the device structure has also not been developed in the work. Another limitation of the modeling of Razavi *et al.* [16] is that it has not considered effective surface charge and bias dependent fringing phenomena in its modeling which can give more accurate expression of surface potential. Similarly, Tiwari *et al.* [17] have dealt with analytical modeling of a TM-MOSFET, but they had their focus on surrounding gate structures and it has been demonstrated that notable enhancement in device performance against SCE is observed with their proposed device structure.

The benefit of using a gate stack MOSFET architecture to deal with leakage associated with downscaling of device has been reported in some of the earlier works [18]-[19]. Inani *et al.* [18] have discussed on the practical implications of the high-k dielectric materials on the device performance of a deep submicron MOSFET. Cheng *et al.* [19] have presented the potential impact of high- $\kappa$  gate dielectrics on device short-channel performance over a wide range of dielectric permittivities using a two-dimensional (2-D) simulator implemented with quantum mechanical models. It is shown in this work that the short-channel performance degradation is caused by the fringing fields from the gate to the source/drain regions which weaken the gate control. The gate stack architecture plays an important role in the determination of the device short-channel performance degradation. It is also presented in this work that using double-layer

gate stack structures and low- $\kappa$  dielectric as spacer materials well confine the electric fields within the channel thereby minimizing short-channel performance degradation.

Tsividis [20] lifted up the charge sharing effect severely present in a short channel MOSFET and discusses in details on halo doping process as a form of channel engineering to mitigate the very effect.

Pradhan *et al.* [21] have presented a simulation based work on TM-DG-DH-GS MOSFET, but has not presented any analytical modeling of the device structure. As such, it provides very limited insight of the device physics and phenomena; However, it unleashes the promises of the device structure in dealing with SCE to some extent.

Bentreia *et al.* [22] have studied the influence of hot-carrier degradation effects on the drain current of a DG-GS MOSFET device. The literature has used the idea of EOT (Effective Oxide Thickness) for modeling drain to source current. De et al. [23] have presented an quasi-Fermi potential based analytical subthreshold drain current model for linear and Gaussian doping profile based DHDMG MOSFET. Park *et al.* [24] have presented a charge sheet capacitance model for MOSFET. The bias dependent inner fringing phenomena have been included in this work. Young *et al.* [25] have dealt with the SCEs in a fully depleted SOI MOSFET and proposes the channel potential of such a MOSFET can be approximated by a  $2^{nd}$  order polynomial. The concept has been adopted in this work for modeling of channel potential and threshold voltage.

Yan *et al.* [26] explore an important fact regarding the calculation of characteristics length of a MOSFET. Characteristic length indicates how much electric field from drain region is penetrated into channel and hence how much it is controlled by drain. It has been reported at Yan *et al.* [26] that solving Poisson's equation at semiconductor-oxide interface does not give reasonable value of characteristic length and so cannot measure SCEs properly. Rather, solving Poisson's equation at mid-channel provides a better value of the parameter. This idea has been incorporated in this work.

Arora [27] indicates to the fact that for a fully-depleted DG MOSFET, the punch-through current is not confined only to surface. So, it is suggested in the work that the center potential should be considered instead of surface potential in drain to source current modeling for accurate values. Sodini *et al.* [28] and Akers *et al.* [29] have dealt with developing analytical expressions for low carrier mobility, electric field, critical electric field, surface charge and depletion layer charge of a fully depleted DG MOSFET. Merckel [30] has worked on CAD models of MOSFET. An empirical formula has been developed in his work for incorporating the CLM effect in drain to source current model.

Hamid *et al.* [31] and Kumar *et al.* [32] reveal the fact that QMEs (Quantum Mechanical Effects) become negligible for the channel thickness over 5nm. It is also reported that Ballistic transport is observed when the mean free path of the electron is longer than the dimension of the medium through which the electron travels [33]. Sverdrup *et al.* [34] report that it is known that at room temperature, the electron mean free path in heavily doped sample is~1-10 nm. The channel length used in this analytical modeling is 120nm. So, the ballistic transport effect has not been considered in this modeling.

#### **1.2 Objectives of the Work**

The Short Channel Effects (SCEs) are ever on the increase along with the advancement of the technology associated with super-shrunken device in deep submicron level for practical applications. Gate and Channel Engineering techniques can be efficiently applied in a downscaled device to mitigate SCEs. The advantages of gate as well as channel engineering technique can combinedly be incorporated in symmetric halo doped gate stacked triple material double gate MOSFET. To the best of our knowledge, no theoretical model of this device has been reported yet. Hence the purpose of the proposed work is to develop an analytical model of the device structure for having a deeper insight of the device physics and characteristics.

In this work, a two dimensional analytical model of channel potential, threshold voltage and drain to source current of a symmetric halo gate stacked triple material double gate MOSFET will be developed. The analytical model results will also be compared simultaneously with the

data from a commercially available numerical device simulator to validate the model. The expression of channel potential and surface potential of the device will be obtained by solving two dimensional Poisson's equations with appropriate boundary conditions with continuum of channel potential and electrical flux along the channel. Bias dependent inner fringing phenomena and oxide trapping phenomena will also be incorporated for better accuracy of the model. With a view of integrating these effects, inner fringing capacitance and effective surface charge will be included. The expression of drain to source current will be derived using basic drift-diffusion equations. Since the punch-through current is not confined only to the surface in a fully depleted MOSFET, center potential of the channel will be used instead of surface potential in the current modeling. Thus, an expression of pinch-off voltage will be deduced for modeling the drain current in saturation region accurately. However, in deep submicron level, the drain to source current actually does not become constant even after the pinch-off occurs. To depict this phenomenon through our modeling, the channel length modulation effect will also be included. The device performance will be examined with the variation in device parameters, such as channel length, channel thickness, doping profile etc. Several short channel effects like drain induced barrier lowering, leakage, threshold voltage roll-off will also be explored and compared with those of other already proposed device structures to point out the areas of improvement achieved through the application of gate and channel engineering in this device.

#### **1.3 Thesis Outline**

The thesis is organized as follows-

**Chapter One** introduces the topic of the thesis. The motivation behind this thesis work is written in this chapter. An outline of the specific objectives of the work is also included. It also lifts up the reviews of the related earlier literatures and how some of the concepts used in those literatures were adopted in our work.

**Chapter Two** presents the theoretical aspects of gate and channel engineered TM-DG-DS-DH MOSFET which are relevant to the device characteristics and device capability in dealing with

SCEs with continuous downscaling of device. The parameters which should be known to understand thestructure and performance of the device have been explained in this chapter.

**Chapter Three** explains the device structure and contains the development of the analytical modeling of channel potential, threshold voltage and drain to source current of the TM-DG-DH-GS MOSFET. Two dimensional Poisson's Equation with proper boundary conditions has been solved and basic drift-diffusion equation has been used to derive the mathematical expression of various device parameters and SCEs

**Chapter Four** lifts up the analysis and graphical representation of the results obtained from the proposed analytical model along with the simulation results extracted from professional 2D device simulator for model verification. Significant improvements in dealing with SCEs attained with TM-DG-DH-GS MOSFET compared to other device structures with no gate and channel engineering implemented in those, have also been presented in this chapter.

Chapter Five briefly summarizes the overall research work and suggests the scope of future work.

## **CHAPTER TWO**

#### THEORETICAL BACKGROUND

Practical applications demand ever decreasing chip sizes, which leads to reduced length of the channel in MOS devices. However, as the channel length, L is reduced to increase both the operation speed and the number of components per chip, the short-channel effects arise. Short-channel effect is an effect whereby a MOSFET in which the channel length is the same order of magnitude as the depletion-layer widths of the source and drain junction, behaves differently from other MOSFETs. The threshold voltage is modified due to the shortening of channel length. Some of the common SCEs are : Drain Induced Barrier Lowering (DIBL), Hot Carrier Effect (HCE), Threshold Voltage Roll-off and Channel Length Modulation (CLM) Effect etc.

#### 2.1 Drain Induced Barrier Lowering (DIBL) :

Drain-induced barrier lowering is a short-channel effect in MOSFETs refers originally to a reduction of threshold voltage of the transistor at higher drain voltages. In a classic planar field-effect transistor with long channel length, the bottleneck in channel formation occurs far enough from the drain contact and it is electrostatically shielded from the drain by the combination of the substrate and gate. Hence classically the threshold voltage of the long channel transistor is independent of drain voltage. In short-channel devices this phenomena is no longer true. The drain is close enough to gate the channel, and so a high drain voltage can open the bottleneck and turn on the transistor prematurely [20].

Normally, the combined charge in the depletion region of the device and that in the channel of the device are balanced by three electrode charges: the gate, the source and the drain. As drain voltage is increased, the depletion region of the p-n junction between the drain and body increases in size and extends under the gate, so the drain assumes a greater portion of the burden of balancing depletion region charge, leaving a smaller burden for the gate. As a result, the charge present on the gate retains charge balance by attracting more carriers into the channel, equivalent to lowering the threshold voltage of the device. In effect, the channel becomes more

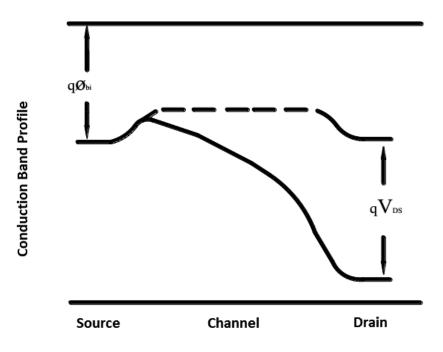

Fig. 2.1 Drain Induced Barrier Lowering phenomena in Short Channel MOSFET [20]

attractive for electrons. In other words, the potential energy barrier for electrons in the channel is lowered. Hence the term "barrier lowering" is used to describe these phenomena. Fig. 2.1 illustrates the DIBL effect with the conduction band profile in a short channel MOSFET. As the drain bias increases, fields emanating from the drain end up throughout the channel and the surface potential is raised. The electrons now find it easier to cross the barrier and their population in the channel increases. As a result, the threshold voltage is decreased and becomes a strong function of drain voltage in short channel device.

## 2.2 Hot Carrier Effect (HCE) :

Hot Carrier Effect is a phenomenon in solid-state electronic devices where an electron generated in the space charge region is attracted due to the electric field induced by a positive gate voltage and gains sufficient kinetic energy to overcome a potential barrier necessary to break an interface state. The term "hot" refers to the effective temperature used to model carrier density, not to the overall temperature of the device. Since the charge carriers can become trapped in the gate dielectric of a MOS transistor, the switching characteristics of the transistor can be permanently changed. Hot-carrier injection is one of the mechanisms that adversely affects the reliability of semiconductors in solid-state devices [32].

#### 2.3 Threshold Voltage Roll-off :

The decrease of threshold voltage with decrease in gate length is a well-known short channel effect called the "Threshold voltage roll-off". As the channel of the device is reduced to nanoscale region, the charge distribution in the channel is influenced by the field originating from the source/drain. Thus the value of threshold voltage in a short channel device decreases from the constant value maintained in a long channel device. Mathematically, threshold voltage roll-off is the difference between the threshold voltage of a short channel MOSFET and that of a long channel MOSFET.

### 2.4 Channel Length Modulation (CLM) Effect :

Channel Length Modulation (CLM) is a shortening of the length of the inverted channel region with increase in drain bias for large drain voltage. The result of CLM is an increase in current with drain bias and a reduction of output resistance.

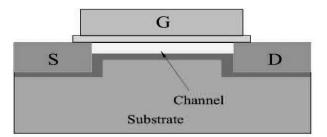

CLM effect is closely associated with pinch-off phenomena in the MOS Device. The channel in a MOS device is formed by attraction of carriers to the gate, and the current drawn through the channel is nearly a constant, independent of drain voltage in saturation mode. However, near the drain, the gate and drain jointly determine the electric field pattern. Instead of flowing in a channel, beyond the pinch-off point the carriers flow in a subsurface pattern made possible because the drain and the gate both control the current. The channel becomes weaker as the drain is approached, leaving a gap of uninverted silicon between the end of the formed inversion layer and the drain (the pinch-off region) [20].

As the drain voltage increases, its control over current toward the source extends further and hence the uninverted region expands toward the source, shorten the length of the channel region.

Before Pinch-off

After Pinch-off

Fig. 2.2 Channel Length Modulation (CLM) Effect in MOSFET device

This effect is termed as channel-length modulation. Fig. 2.2 shows the channel-length modulation phenomena in a MOS device. Before the pinch-off phenomenon occurs, the channel is extended to the drain end. However, once the pinch-off occurs, the channel length is decreased towards the source. Since resistance is proportional to length, shortening the channel length decreases its resistance, causes an increase in current with increase in drain bias for a MOSFET operating in saturation. The effect is more pronounced with shorter source-to-drain separation, deeper drain junction, and thicker oxide insulator [20].

## 2.5 Gate Engineering:

Gate Engineering is applied to mitigate SCEs in a MOSFET device. One form of Gate Engineering is to use metals having different work functions in the gate electrode with the one close to source having the highest work function and the lowest work function material being adjacent to the drain. Since, the work function of the metal close to drain is the highest of the all, the minimum surface potential will be found in the channel region under that metal. So, the energy barrier level will be the highest in this region. The channel will not conduct until this highest barrier is lowered irrespective of drain bias applied. Threshold voltage condition of the device is thus effectively screened from drain bias and the Drain Induced Barrier Lowering (DIBL) effect will be less.

Another form of Gate Engineering is the inclusion of High-k dielectric material along with the conventional  $SiO_2$  as gate oxide layer. With the continuous downscaling of the device, leakage current is ever on the increase. Including the High-k dielectric material in the gate oxide decreases leakage current effectively.

#### **2.6 Channel Engineering:**

Channel Engineering is applied in a MOSFET device in the form of Halo Doping. In the short channel MOSFET, the depletion regions associated with the source and the drain come into close proximity/contact with each other. It affects the device current-voltage characteristics adversely. The slope of  $log(I_{DS})$  vs  $V_{GS}$  becomes very small and the device cannot be turned off adequately even if  $V_{DS}$  is decreased significantly [20]. This is called Punch through effect. For avoiding the phenomena, depletion region width must be limited. Using higher substrate doping can limit depletion region width, but it is not desirable to increase the substrate doping concentration everywhere in the channel, as it will increase the body effect co-efficient which will impede the optimum device performance in many applications. So, the substrate doping concentration is increased locally, around the source or drain or both region using ion implantation. This processis called Halo doping. If the halo implantation is done around both source and drain regions, it is called Double Halo doping and if it is done around any of the two regions, it is

called Single Halo doping. The length of the halo regions is assumed to be fixed, independent of the channel length.

## 2.7 Effective Oxide Thickness (EOT):

Effective oxide thickness is a number used to compare performance of high-k dielectric MOSFET gates with performance of SiO<sub>2</sub> based MOSFET gates [22]. It shows the thickness of SiO<sub>2</sub> gate oxide needed to obtain the same gate capacitance as the one obtained with thicker than SiO<sub>2</sub> dielectric featuring higher dielectric constant, K. For example, EOT of 1 nm would result from the use a 10 nm thick dielectric featuring k=39 (k of SiO<sub>2</sub> is 3.9). Mathematically, EOT can be represented as :

$$EOT = t_{sio2} + \frac{t_{High,k} \times \epsilon_{sio2}}{\epsilon_{High,k}}$$

Where,  $t_{sio2}$ ,  $t_{High,k}$ ,  $\in_{sio2}$  and  $\in_{High,k}$  denote SiO<sub>2</sub> and high-k dielectric layer thickness, permittivity of SiO<sub>2</sub> and high-k dielectric respectively.

## **CHAPTER THREE**

## **ANALYTICAL MODELING OF PROPOSED DEVICE**

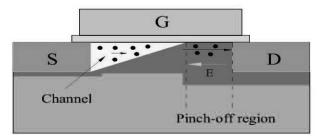

#### **3.1 Physical Device Structure and Dimensions:**

A schematic structure of the proposed device is shown in Fig. 3.1. The x- and y- axes of the 2D device structure are considered to be along the front oxide-semiconductor interface and the source terminal-channel interface, respectively. The total channel length, L is divided into 5 regions. L<sub>1</sub> and L<sub>5</sub> (L<sub>1</sub>=L<sub>5</sub>) denote the length of the regions with uniform halo doping near source and drain end, correspondingly. Doping concentration used in these regions is N<sub>Am</sub>=1.2x10<sup>18</sup> cm<sup>-3</sup>. Elsewhere in the channel, the doping concentration is N<sub>As</sub> = 10<sup>15</sup> cm<sup>-3</sup>. The doping concentration of drain and source region is N<sub>DS</sub>=10<sup>20</sup> cm<sup>-3</sup>. The front and the back gate electrodes of the device are symmetric and composed of three different materials having work functions of  $\Phi_{m1}$ ,  $\Phi_{m2}$  and  $\Phi_{m3}$  ( $\Phi_{m1} > \Phi_{m2} > \Phi_{m3}$ ) deposited over lengths (L<sub>1</sub>+L<sub>2</sub>),L<sub>3</sub> and(L<sub>4</sub>+L<sub>5</sub>) respectively. The front and the back gate terminals are shorted to a fixed potential, V<sub>G8</sub>. The drain bias is V<sub>D8</sub> and the source terminal is grounded. Two layers of oxides have been used with both front and back gate terminals. The first layer of the oxide is HfO<sub>2</sub> having high dielectric constant, k<sub>HfO2</sub> of SiO<sub>2</sub> is given by  $t_{eff} = t_{sio2} + \frac{t_{Hfo2} \times \epsilon_{sio2}}{\epsilon_{Hfo2}}$  [22], where,  $t_{sio2}$ ,  $t_{Hfo2}$ ,  $\epsilon_{sio2}$  and  $\epsilon_{Hfo2}$  denote SiO<sub>2</sub> and HfO<sub>2</sub> layer thickness, permittivity of SiO<sub>2</sub> and HfO<sub>2</sub> respectively.

## 3.2 Doping Concentration Profile:

Plot of doping profile along the channel is presented in Fig. 3.2. Doping concentration along the channel can be expressed as:

Fig. 3.1 Schematic cross sectional view of triple material double gate double halo gate stacked MOSFET

$$N(x) = \begin{cases} N_{Am}, 0 < x \le L_1 \\ N_{As}, L_1 < x \le (L - L_5) \\ N_{Am}, (L - L_5) < x \le L \end{cases}$$

(1)

Here, the halo doping concentration,  $N_{Am}$  has been used uniformly in the region  $L_1$  and  $L_5$ . So, it has been named as uniform halo doping concentration profile. Since, there is a non-uniform doping profile along the channel; the average effective concentration [14] as well as local doping concentration have been considered in the analytical modeling for mathematical simplicity. The average effective doping concentration for the uniform halo doping concentration profile can be found by:

$$N_{\rm eff} = N_{\rm As} + \frac{2L_1(N_{\rm Am} - N_{\rm As})}{L}$$

(2)

Unless otherwise stated, the abovementioned uniform halo doping profile has been used for result analysis in the work. We have also studied linear [14] and Gaussian [23] halo doping concentration profile in the work. For linear and Gaussian halo doping profile, the average effective doping concentration along the channel can be found by the following equations respectively:

Fig. 3.2 Plot of doping concentration along the lateral position of the channel

$$N_{\rm eff, \, linear} = N_{\rm As} + \frac{L_1 \left( N_{\rm Am} - N_{\rm As} \right)}{L}$$

(3)

$$N_{eff, gaussian} = N_{As} + N_{Am} \left\{ \frac{\sqrt{\pi} \operatorname{erf}\left(\frac{L}{L_{1}}\right)}{\left(\frac{L}{L_{1}}\right)} \right\}$$

(4)

## **3.3 Fringing Phenomena in Device:**

The bias dependent inner fringing phenomena in the device have been considered in our model. All the fringing and the overlap capacitance components in the device have been shown in Fig. 3.3.  $C_1$  is the outer fringing capacitance component on each side of front and back gate between gate and source or gate and drain electrode.  $C_2$  is the direct overlap capacitance between gate and source or gate and drain junction.  $C_3$  is the inner fringing capacitance between gate and source

Fig. 3.3 Outer, inner and overlap fringing capacitance components

side junction or gate and drain side junction.  $C_F$  is the maximum value of inner fringing capacitance,  $C_3$ . The capacitors are modeled as:

$$C_{1} = W \frac{\epsilon_{sio2}}{\alpha} \ln \left( 1 + \frac{t_{gate}}{t_{eff}} \right)$$

(3)

$$C_{2} = W \frac{\epsilon_{sio2}}{t_{eff}} \left[ 0.5 t_{eff} \left( \frac{1 - \cos \alpha}{\sin \alpha} + \frac{1 - \cos \delta}{\sin \delta} \right) \right]$$

(4)

$$C_{\rm F} = W \frac{\epsilon_{\rm sio2}}{\delta} \ln \left( 1 + \frac{X_{\rm j} \sin \alpha}{t_{\rm eff}} \right)$$

(5)

where  $\delta = 0.5\pi \frac{\epsilon_{sio2}}{\epsilon_{si}}$  and  $t_{gate}$ , W,  $\alpha$  and  $X_j$  are gate electrode thickness, channel width, slanting

angle and source/drain junction depth, respectively.

The charge induced at drain and source end at each side of the front and back gate due to inner fringing capacitance are,

$$Q_{DF} = -C_{F} \frac{V_{DS} - V_{DS,eff}}{1 + e^{-\frac{V_{GS} - V_{fb}}{30V_{T}}}} = -C_{F}V_{FD}$$

(6)

$$Q_{SF} = -C_{F} \frac{V_{th} + V_{fb} + 2\phi_{F} + \gamma \sqrt{2\phi_{F} - V_{GS}}}{1 + e^{-\frac{V_{GS} - V_{fb}}{30V_{T}}}} = -C_{F}V_{FS}$$

(7)

where,  $V_{tb}$  is flat band voltage,  $V_{th}$  is threshold voltage,  $\phi_F = V_T \ln\left(\frac{N_{eff}}{n_i}\right)$  is Fermi potential,  $n_i$

is intrinsic carrier concentration,  $\gamma = \frac{\sqrt{2q \in_{si} N_{eff}}}{C_{ox}}$  is body effect coefficient,  $V_T$  is thermal voltage and  $C_{ox} = \frac{\in_{sio2}}{t_{eff}}$  is oxide capacitance. The effective drain to source voltage,  $V_{DS,eff}$  is given

by Park et al. [24].  $V_{\mbox{\scriptsize FD}}$  and  $V_{\mbox{\scriptsize FS}}$  are inner fringing potential at drain and source end, respectively.

#### 3.4 Channel Potential :

Let  $\Psi_j(x,y)$ ; j=1, 2,3,4,5 be the channel potential in the channel region 1, 2, 3, 4 and 5 respectively. We solve the two dimensional Poisson's equation to obtain the channel potential,  $\Psi_j(x,y)$ :

$$\frac{\partial^2 \Psi_j(\mathbf{x}, \mathbf{y})}{\partial \mathbf{x}^2} + \frac{\partial^2 \Psi_j(\mathbf{x}, \mathbf{y})}{\partial \mathbf{y}^2} = \frac{q N_{\text{eff}}}{\epsilon_{\text{si}}}$$

(8)

To solve the equation the boundary conditions of potential and electrical flux continuity at different interfaces are required. At front and back semiconductor-oxide interfaces, boundary conditions are given by:

$$\frac{\partial \Psi_{j}(\mathbf{x}, \mathbf{y})}{\partial \mathbf{y}}\Big|_{\mathbf{y}=0} = \frac{\epsilon_{\text{sio2}} \left[ \Psi_{\text{sj}}(\mathbf{x}) - V_{\text{GS}} + V_{\text{fbj}} \right]}{\epsilon_{\text{si}} t_{\text{eff}}}$$

(9)

$$\frac{\partial \Psi_{j}(\mathbf{x}, \mathbf{y})}{\partial y}\Big|_{y=t_{si}} = -\frac{\epsilon_{sio2} \left[\Psi_{sj}(\mathbf{x}) - V_{GS} + V_{fbj}\right]}{\epsilon_{si} t_{eff}}$$

(10)

where,  $t_{si}$  is the channel thickness and  $V_{tbj}$  corresponds the flat band voltage of region 1,2,3,4 and 5 and is given by the expression :

$$V_{\rm fbj} = \varphi_{\rm mj} - \left[\chi_{\rm si} + \frac{E_{\rm g_{\rm si}}}{2q} + \varphi_{\rm F}\right] - \frac{Q_0}{C_{\rm ox}}; j = 1, 2, 3, 4, 5$$

(11)

here,  $\chi_{si}$ ,  $E_{g_{si}}$ ,  $\phi_F$  and  $Q_0$  are electron affinity , energy band gap of silicon, Fermi potential and effective surface charge, respectively. The value of effective surface charge,  $Q_0$  is  $1.6 \times 10^{-8}$  C/m<sup>2</sup>.

Due to the continuous behavior of potential and electrical flux throughout the channel, potential and electrical flux are continuous functions, hence at the interface of region 1 and 2, region 2 and 3, region 3 and 4 and region 4 and 5 we get,

$$\Psi_1(L_1, 0) = \Psi_2(L_1, 0) \tag{12}$$

$$\frac{\partial \Psi_1}{\partial x}\Big|_{x=L_1} = \frac{\partial \Psi_2}{\partial x}\Big|_{x=L_1}$$

(13)

$$\Psi_2(L_1 + L_2, 0) = \Psi_3(L_1 + L_2, 0) \tag{14}$$

$$\frac{\partial \Psi_2}{\partial x}\Big|_{x=L_1+L_2} = \frac{\partial \Psi_3}{\partial x}\Big|_{x=L_1+L_2}$$

(15)

$$\Psi_3(L_1 + L_2 + L_3, 0) = \Psi_4(L_1 + L_2 + L_3, 0)$$

(16)

$$\frac{\partial \Psi_3}{\partial x}\Big|_{x=L_1+L_2+L_3} = \frac{\partial \Psi_4}{\partial x}\Big|_{x=L_1+L_2+L_3}$$

(17)

$$\Psi_4(L_1 + L_2 + L_3 + L_4, 0) = \Psi_5(L_1 + L_2 + L_3 + L_4, 0)$$

(18)

$$\frac{\partial \Psi_4}{\partial x}\Big|_{x=L_1+L_2+L_3+L_4} = \frac{\partial \Psi_5}{\partial x}\Big|_{x=L_1+L_2+L_3+L_4}$$

(19)

Potentials at source-channel and drain channel interface can be expressed as,

$$\Psi_1(0,0) = V_{bi} + V_{FS}$$

(20)

$$\Psi_{5}(L_{1}+L_{2}+L_{3}+L_{4}+L_{5},0) = V_{bi} + V_{DS} + V_{FD}$$

(21)

where,  $V_{bi}$  is the built in potential and is given by:

$$\mathbf{V}_{\rm bi} = \mathbf{V}_{\rm T} \ln \left( \frac{\mathbf{N}_{\rm Am} \mathbf{N}_{\rm DS}}{\mathbf{n}_{\rm i}^2} \right) \tag{22}$$

here, N<sub>DS</sub> is the doping concentration at drain and source region. From [25], the solution of Eq. (8) can be approximated by a 2<sup>nd</sup> order polynomial:

$$\Psi_{j}(x,y) = c_{j0}(x) + c_{j1}(x)y + c_{j2}(x)y^{2}, j=1,2,3,4,5$$

(23)

where,  $c_{j0}(x)$ ,  $c_{j1}(x)$  and  $c_{j2}(x)$  are arbitrary functions of x which can be solved using boundary conditions of Eqs. (9)-(21). Substituting y=0 in Eq. (23) we get

$$c_{j0}(x) = \Psi_j(x,0) = \Psi_{sj}(x)$$

(24)

Taking derivative of Eq. (23) and using Eqs. (9) and (10) we get,

$$\mathbf{c}_{j1}(\mathbf{x}) = \frac{\in_{\text{sio2}} \left[ \Psi_{sj}(\mathbf{x}) - V_{\text{GS}} + V_{\text{fbj}} \right]}{\in_{\text{si}} t_{\text{eff}}}$$

(25)

$$c_{j2}(x) = -\frac{\epsilon_{sio2} \left[ \Psi_{sj}(x) - V_{GS} + V_{fbj} \right]}{\epsilon_{si} t_{eff} t_{si}}$$

(26)

So, Eq. (25) becomes,

$$\Psi_{j}(x,y) = \Psi_{sj}(x) + \frac{\epsilon_{sio2} \left[ \Psi_{sj}(x) - V_{GS} + V_{fbj} \right]}{\epsilon_{si} t_{eff}} y - \frac{\epsilon_{sio2} \left[ \Psi_{sj}(x) - V_{GS} + V_{fbj} \right]}{\epsilon_{si} t_{eff} t_{si}} y^{2}$$

(27)

For more accurate modeling of channel potential we need to consider characteristic length,  $\lambda$ . It indicates how much electric field from drain region is penetrated into channel and hence how much it is controlled by drain.

But solving Poisson's equation at semiconductor-oxide interface does not give reasonable value of  $\lambda$  and so cannot measure short channel effects properly [26]. Rather, solving Poisson's equation at mid-channel provides a better value of  $\lambda$  [26] and  $\lambda$  is expressed as:

$$\lambda = \sqrt{\frac{t_{si}^{2} \left(1 + \frac{r_{oc}}{4}\right)}{2r_{oc}}}$$

Now, the mid-channel potential:

$$\Psi_{cj}(x) = \Psi_{j}(x,y) \bigg|_{y=\frac{t_{si}}{2}}$$

(28)

From Eqs. (25)-(27),

$$\Psi_{cj}(\mathbf{x}) = \Psi_{sj}(\mathbf{x}) \left(1 + \frac{r_{oc}}{4}\right) - \frac{r_{oc}}{4} \left(V_{GS} - V_{fbj}\right)$$

<sup>(29)</sup>

here,  $r_{oc}$  is the ratio of gate oxide capacitance to channel capacitance and is given by:

$$r_{oc} = \frac{\in_{sio2} t_{si}}{\in_{si} t_{eff}}$$

Differential equation for solving Eq. (8) at mid-channel:

$$\frac{\partial^2 \Psi_{cj}(\mathbf{x})}{\partial x^2} - \frac{\Psi_{cj}(\mathbf{x})}{\lambda^2} = \frac{q N_{eff}}{\epsilon_{si}} - \left(\frac{V_{GS} - V_{fbj}}{\lambda^2}\right)$$

(30)

General solution for Eq. (30) can be written as

$$\Psi_{cj}(x) = G_{j}e^{\tau x} + H_{j}e^{-\tau x} - \frac{\alpha_{j}}{\tau^{2}}$$

(31)

where,

$$\alpha_{j} = \frac{qN_{eff}}{\epsilon_{si}} - \left(\frac{V_{GS} - V_{fbj}}{\lambda^{2}}\right)$$

(32)

$$\tau = \frac{1}{\lambda} \tag{33}$$

The coefficients  $G_j$  and  $H_j$  (j=1,2,3,4,5) can be found using boundary conditions of Eqs. (9)-(21). Solving, we get,

$$G_{1} = \frac{1}{2\sinh(\tau L)} [V_{FD} + V_{bi} + V_{DS} + \frac{\alpha_{5}}{\tau^{2}} - \left(V_{bi} + V_{FS} + \frac{\alpha_{1}}{\tau^{2}}\right) e^{-\tau L} + \left(\frac{\alpha_{1} - \alpha_{2}}{\tau^{2}}\right) \cosh\{\tau(L_{2} + L_{3} + L_{4} + L_{5})\} + \left(\frac{\alpha_{2} - \alpha_{3}}{\tau^{2}}\right) \cosh\{\tau(L_{3} + L_{4} + L_{5})\} + \left(\frac{\alpha_{3} - \alpha_{4}}{\tau^{2}}\right) \cosh\{\tau(L_{4} + L_{5})\} + \left(\frac{\alpha_{4} - \alpha_{5}}{\tau^{2}}\right) \cosh\{\tau(L_{5})]$$

(34)

$$G_2 = G_1 - \left(\frac{\alpha_1 - \alpha_2}{2\tau^2}\right) e^{-\tau L_1}$$

(35)

$$G_{3} = G_{1} - \left(\frac{\alpha_{1} - \alpha_{2}}{2\tau^{2}}\right) e^{-\tau L_{1}} - \left(\frac{\alpha_{2} - \alpha_{3}}{2\tau^{2}}\right) e^{-\tau (L_{1} + L_{2})}$$

(36)

$$G_{4} = G_{1} - \left(\frac{\alpha_{1} - \alpha_{2}}{2\tau^{2}}\right) e^{-\tau L_{1}} - \left(\frac{\alpha_{2} - \alpha_{3}}{2\tau^{2}}\right) e^{-\tau (L_{1} + L_{2})} - \left(\frac{\alpha_{3} - \alpha_{4}}{2\tau^{2}}\right) e^{-\tau (L_{1} + L_{2} + L_{3})}$$

(37)

$$G_{5} = G_{1} - \left(\frac{\alpha_{1} - \alpha_{2}}{2\tau^{2}}\right)e^{-\tau L_{1}} - \left(\frac{\alpha_{2} - \alpha_{3}}{2\tau^{2}}\right)e^{-\tau (L_{1} + L_{2})} - \left(\frac{\alpha_{3} - \alpha_{4}}{2\tau^{2}}\right)e^{-\tau (L_{1} + L_{2} + L_{3})} - \left(\frac{\alpha_{4} - \alpha_{5}}{2\tau^{2}}\right)e^{-\tau (L_{1} + L_{2} + L_{3} + L_{4})}$$

(38)

$$H_{1} = V_{bi} - G_{1} + \frac{\alpha_{1}}{\tau^{2}} + V_{FS}$$

(39)

$$H_2 = H_1 - \left(\frac{\alpha_1 - \alpha_2}{2\tau^2}\right) e^{\tau L_1}$$

(40)

$$H_{3} = H_{1} - \left(\frac{\alpha_{1} - \alpha_{2}}{2\tau^{2}}\right) e^{\tau L_{1}} - \left(\frac{\alpha_{2} - \alpha_{3}}{2\tau^{2}}\right) e^{\tau (L_{1} + L_{2})}$$

(41)

$$H_{4} = H_{1} - \left(\frac{\alpha_{1} - \alpha_{2}}{2\tau^{2}}\right) e^{\tau L_{1}} - \left(\frac{\alpha_{2} - \alpha_{3}}{2\tau^{2}}\right) e^{\tau (L_{1} + L_{2})} - \left(\frac{\alpha_{3} - \alpha_{4}}{2\tau^{2}}\right) e^{\tau (L_{1} + L_{2} + L_{3})}$$

(42)

$$H_{5} = H_{1} - \left(\frac{\alpha_{1} - \alpha_{2}}{2\tau^{2}}\right) e^{\tau L_{1}} - \left(\frac{\alpha_{2} - \alpha_{3}}{2\tau^{2}}\right) e^{\tau (L_{1} + L_{2})} - \left(\frac{\alpha_{3} - \alpha_{4}}{2\tau^{2}}\right) e^{\tau (L_{1} + L_{2} + L_{3})} - \left(\frac{\alpha_{4} - \alpha_{5}}{2\tau^{2}}\right) e^{\tau (L_{1} + L_{2} + L_{3} + L_{4})}$$

(43)

Using Eqs. (27), (29) and (31) and Eqs. (34)-(43), the channel potential equation is:

$$\Psi_{j}(\mathbf{x},\mathbf{y}) = \left[\frac{G_{j}e^{\tau \mathbf{x}} + H_{j}e^{-\tau \mathbf{x}} - \frac{\alpha_{j}}{\tau^{2}} + \frac{\mathbf{r}_{oc}}{4}(\mathbf{V}_{GS} - \mathbf{V}_{fbj})}{\left(1 + \frac{\mathbf{r}_{oc}}{4}\right)}\right] \times \left(1 + \frac{\mathbf{r}_{oc}}{\mathbf{t}_{si}}\mathbf{y} - \frac{\mathbf{r}_{oc}}{\mathbf{t}_{si}^{2}}\mathbf{y}^{2}\right) - \frac{\mathbf{r}_{oc}}{\mathbf{t}_{si}}\left(\mathbf{V}_{GS} - \mathbf{V}_{fbj}\right)\mathbf{y} + \frac{\mathbf{r}_{oc}}{\mathbf{t}_{si}^{2}}\left(\mathbf{V}_{GS} - \mathbf{V}_{fbj}\right)\mathbf{y}^{2}; \mathbf{j} = 1, 2, 3, 4, 5$$

(44)

Expression of surface potential can be found as :

$$\Psi_{sj}(x) = \frac{G_{j}e^{\tau x} + H_{j}e^{-\tau x} - \frac{\alpha_{j}}{\tau^{2}} + \frac{r_{oc}}{4}(V_{GS} - V_{fbj})}{\left(1 + \frac{r_{oc}}{4}\right)}$$

(45)

#### **3.5 Threshold Voltage :**

The channel region is under three different material gate electrodes. Since, the work function of metal 1,  $\phi_{m1}$  is the highest of the three, from Eqs. (14) and (45), the minimum surface potential will be found in the channel region under metal 1. So, the energy barrier level will be the highest in this region [16]. That is why the channel will not conduct until this highest barrier is lowered. Threshold voltage condition of the device is thus dependent on this channel region.

Since, the flatband voltage in region 1 and 2 are same (since they are under same metal),taking derivative of Eq. (45) for region 2 and equating it to zero, we find the channel position  $x_{min}$  where, the surface potential is minimum and it is given by :

$$x_{\min} = 0.5\lambda \ln \frac{H_2}{G_2}$$

(46)

And the minimum surface potential can be found using Eq. (45):

$$\Psi_{s,min} = 2\sqrt{G_2H_2} - \frac{qN_{eff}}{\epsilon_{si}\tau^2} + (V_{GS} - V_{fb2})$$

$$\tag{47}$$

For threshold condition,

$$\Psi_{s,\min} = 2\phi_F \tag{48}$$

$$V_{GS} = V_{th}$$

(49)

usingEqs. (47)-(49), we can write for threshold condition,

$$2\sqrt{G_2^{\text{th}}H_2^{\text{th}}} - \frac{qN_{\text{eff}}}{\epsilon_{\text{si}}\tau^2} + (V_{\text{th}} - V_{\text{fb}2}) = 2\varphi_F$$

(50)

where,  $G_2^{th} = G_2$  at  $V_{GS} = V_{th}$  and  $H_2^{th} = H_2$  at  $V_{GS} = V_{th}$

Now, using Eq. (50), a quadratic equation of threshold voltage,  $V_{th}$  can be approximated as:

$$AV_{th}^{2} + BV_{th} + C = 0$$

(51)

$$A = 1 + 4 \left( U_2 + \sqrt{U_2} \right) - U_7 - U_8$$

(52)

$$B = -2V_{thL} - 4U_1 - U_6 - 2U_5U_7 - U_5U_8$$

(53)

$$C = V_{thL}^{2} - 4U_{3} - U_{4} - U_{5}U_{6} - U_{5}^{2}U_{7}$$

(54)

$$V_{thL} = \frac{qN_{eff}}{\epsilon_{si}\tau^2} + V_{fb2} + 2\phi_F$$

(55)

$$U_{1} = \frac{V_{1}(e^{-\tau L} - 1)}{2\sinh(\tau L)} - \frac{V_{6}(e^{-\tau L} - 1)}{\sinh(\tau L)} - V_{6} - \frac{V_{FD}^{th}(e^{-\tau L} - 1)}{2\{\sinh(\tau L)\}^{2}} - \frac{V_{FD}^{th}}{2\sinh(\tau L)}$$

(56)

$$U_{2} = \left\{ \frac{\left(e^{-\tau L} - 1\right)}{2\sinh(\tau L)} \right\}^{2}$$

(57)

$$U_3 = V_1 V_6 - V_6^2$$

(58)

$$U_{4} = \frac{2V_{1}V_{FD}^{\text{th}}}{\sinh(\tau L)} + 4\left[\left\{\frac{V_{FD}^{\text{th}}}{2\sinh(\tau L)}\right\}^{2} + \frac{V_{6}V_{FD}^{\text{th}}}{\sinh(\tau L)}\right]$$

(59)

$$U_5 = V_{fb1} + 2\phi_F + \gamma \sqrt{2\phi_F}$$

(60)

$$U_{6} = \frac{2V_{FD}^{\text{th}}e^{-\tau L}}{\left\{\sinh(\tau L)\right\}^{2}} - \frac{4V_{6}e^{-\tau L}}{\sinh(\tau L)} - \frac{2V_{1}e^{-\tau L}}{\sinh(\tau L)}$$

(61)

$$U_{7} = \left\{ \frac{e^{-\tau L}}{\sinh(\tau L)} \right\}^{2}$$

(62)

$$U_{8} = \frac{2e^{-\tau L} \left(e^{-\tau L} - 1\right)}{\left\{\sinh\left(\tau L\right)\right\}^{2}} + \frac{2e^{-\tau L}}{\sinh\left(\tau L\right)}$$

(63)

where,  $V_{FD}^{\ th} = V_{FD}$  at  $V_{GS} = V_{th}$  and  $V_{thL}$  is the long channel threshold voltage which is independent of channel length.

$$V_{j} = V_{bi} + \frac{qN_{eff}}{\epsilon_{si} \tau^{2}} + V_{fbj}; j = 1, 2, 3, 4, 5$$

(64)

$$V_{6} = \frac{1}{2\sinh(\tau L)} [V_{DS} + V_{5} - V_{1} e^{-\tau L} + (V_{1} - V_{2})\cosh\{\tau(L_{2} + L_{3} + L_{4} + L_{5})\} + (V_{2} - V_{3})\cosh\{\tau(L_{3} + L_{4} + L_{5})\} + (V_{3} - V_{4})\cosh\{\tau(L_{4} + L_{5})\} + (V_{4} - V_{5})\cosh(\tau L_{5})]$$

(65)

Using Eqs. (51)-(65), the expression of the threshold voltage is given by:

$$V_{\rm th} = \frac{-B + \sqrt{\left(B^2 - 4AC\right)}}{2A} \tag{66}$$

### **3.6 Drain to Source Current :**

For modeling of drain to source current, mid-channel potential has been considered instead of surface potential in basic drift and diffusion current equation, because considering surface potential in this case assumes punch-through current to flow only at surface [2], which is invalid

for double gate fully depleted MOSFET [27]. Thus the inclusion of center potential in current equation provides better result in measuring short channel effects.

Drain to source current can be expressed as a combination of drift and diffusion current [20] for all the regions which can be given as:

$$I_{DRIFT_{j}} = W \cdot \mu_{j}(x) \cdot Q_{lj}(x) \frac{d\Psi_{cj}(x)}{dx}$$

(67)

$$I_{DIFF_{j}} = W \cdot \mu_{j}(x) \cdot V_{T} \frac{dQ_{Ij}(x)}{dx}$$

(68)

where,  $W, V_T, \mu_j(x)$  and  $Q_{ij}(x)$  are channel width, thermal voltage, carrier mobility and inversion layer charge, respectively for j=1,2,3,4,5 and are given by:

$$\mu_{j}(\mathbf{x}) = \frac{\mu_{0}}{\sqrt{\left[1 + \left\{\frac{E_{j}(\mathbf{x})}{E_{c}}\right\}^{2}\right]}}$$

(69)

$$Q_{ij}(\mathbf{x}) = 2\left\{Q_{sj}(\mathbf{x}) - Q_{Dj}\right\}$$

(70)

where,  $\mu_0$ ,  $E_j(x)$ ,  $E_c$ ,  $Q_{sj}(x)$  and  $Q_{Dj}$  are low carrier mobility, electric field, critical electric field, surface charge and depletion layer charge, respectively [28]-[29] and are given by:

$$E_{j}(\mathbf{x}) = \frac{C_{ox} \left[ \Psi_{cj}(\mathbf{x}) - V_{GS} + V_{fbj} \right]}{\epsilon_{si}}$$

(71)

$$E_{c} = 6.01 \times 10^{2} \cdot T^{\frac{3}{2}}$$

(72)

$$Q_{sj}(x) = -C_{ox} \left[ V_{GS} - V_{fbj} - \Psi_{cj}(x) \right]$$

(73)

$$Q_{Dj} = C_{ox} \left( \phi_F - V_{th} + V_{fbj} \right)$$

(74)

The model has been developed considering constant room temperature (300K) and the value of low carrier mobility,  $\mu_0$  at this temperature is 1350 cm<sup>2</sup>/V-s.

Now, integrating both sides of the Eq. (67) and using Eqs. (69), (70), (73) and (74),

$$\int_{L_{j-1}^{*}}^{L_{j}^{*}} I_{\text{DRIFT}_{j}} dx = \int_{\Psi_{cj-1}}^{\Psi_{cj}} \frac{W\mu_{0} \left[ -2C_{\text{ox}} \left\{ V_{\text{GS}} - \Psi_{cj}(x) + \varphi_{\text{F}} - V_{\text{th}} \right\} \right]}{\sqrt{\left[ 1 + \left\{ \frac{E_{j}(x)}{E_{c}} \right\}^{2} \right]}} d\Psi_{cj}$$

(75)

where,

$$\begin{cases} L_{0}^{*} = 0, \\ L_{1}^{*} = L_{1}, \\ L_{2}^{*} = L_{1} + L_{2}, \\ L_{3}^{*} = L_{1} + L_{2} + L_{3}, \\ L_{4}^{*} = L_{1} + L_{2} + L_{3} + L_{4}, \\ L_{5}^{*} = L_{1} + L_{2} + L_{3} + L_{4} + L_{5} \end{cases}$$

and

$$\begin{cases} \Psi_{c0} = \Psi_{cj}(x) \big|_{x=L_{0}^{*}} \\ \Psi_{c1} = \Psi_{cj}(x) \big|_{x=L_{1}^{*}} \\ \Psi_{c2} = \Psi_{cj}(x) \big|_{x=L_{2}^{*}} \\ \Psi_{c3} = \Psi_{cj}(x) \big|_{x=L_{3}^{*}} \\ \Psi_{c4} = \Psi_{cj}(x) \big|_{x=L_{4}^{*}} \\ \Psi_{c5} = \Psi_{cj}(x) \big|_{x=L_{5}^{*}} \\ \text{and } j=1,2,3,4,5 \end{cases}$$

From Eqs.(71), (73) and (75), we get,

$$I_{DRIFT_{j}} = \frac{S_{4}}{L_{j} - L_{j-1}} [(S_{1} + S_{3}) ln \left\{ \frac{(S_{3} + \Psi_{cj}) + \sqrt{S_{2}^{2} + (S_{3} + \Psi_{cj})^{2}}}{(S_{3} + \Psi_{cj-1}) + \sqrt{S_{2}^{2} + (S_{3} + \Psi_{cj-1})^{2}}} \right\} - \left\{ \sqrt{S_{2}^{2} + (S_{3} + \Psi_{cj})^{2}} - \sqrt{S_{2}^{2} + (S_{3} + \Psi_{cj-1})^{2}} \right\}]$$

$$(76)$$

$$S_1 = V_{GS} + \varphi_F - V_{th} \tag{77}$$

$$S_2 = \frac{\epsilon_{si} E_c}{C_{ox}}$$

(78)

$$\mathbf{S}_3 = \mathbf{V}_{\text{fbj}} - \mathbf{V}_{\text{GS}} \tag{79}$$

$$S_4 = -2 \in_{si} \mu_0 WE_c \tag{80}$$

Now, integrating both sides of the Eq. (68) and using Eqs.(69), (70), (71) and (72),

$$\int_{L_{j-1}}^{L_{j}^{*}} I_{DIFF_{j}} dx = \int_{Q_{ij-1}}^{Q_{ij}} \frac{W\mu_{0}V_{T}}{\sqrt{\left[1 + \left\{\frac{E_{j}(x)}{E_{c}}\right\}^{2}\right]}} dQ_{ij}$$

(81)

where,

$$\begin{cases} Q_{10} = Q_{1j}(x) \big|_{x=L_{0}^{*}} \\ Q_{11} = Q_{1j}(x) \big|_{x=L_{1}^{*}} \\ Q_{12} = Q_{1j}(x) \big|_{x=L_{2}^{*}} \\ Q_{13} = Q_{1j}(x) \big|_{x=L_{3}^{*}} \\ Q_{14} = Q_{1j}(x) \big|_{x=L_{4}^{*}} \\ Q_{15} = Q_{1j}(x) \big|_{x=L_{5}^{*}} \\ and j=1,2,3,4,5 \end{cases}$$

From Eqs.(70), (71), (72) and (81), we get,

$$I_{DIFF_{j}} = \frac{S_{7}}{L_{j} - L_{j-1}} \left[ ln \left\{ \frac{\left(S_{5} + Q_{I_{j}}\right) + \sqrt{S_{6}^{2} + \left(S_{5} + Q_{I_{j}}\right)^{2}}}{\left(S_{5} + Q_{I_{j-1}}\right) + \sqrt{S_{6}^{2} + \left(S_{5} + Q_{I_{j-1}}\right)^{2}}} \right\} \right]$$

(82)

$$S_{5} = 2C_{ox} \left[ V_{tbj} + \varphi_{F} - V_{th} \right]$$

(83)

$$S_6 = 2 \in_{si} E_c \tag{84}$$

$$\mathbf{S}_7 = \mathbf{S}_6 \mathbf{W} \mathbf{V}_{\mathrm{T}} \mathbf{\mu}_0 \tag{85}$$

So, the drain to source current can be expressed as,

$$\mathbf{I}_{\mathrm{DS}} = \sum_{j=1}^{5} \left[ \mathbf{I}_{\mathrm{DRIFT}_{j}} + \mathbf{I}_{\mathrm{DIFF}_{j}} \right]$$

(86)