## VARIABILITY AND SELF-HEATING ANALYSIS OF SPIN TRANSFER TORQUE MAGNETIC RANDOM ACCESS MEMORY DEVICES

by

BEJOY SIKDER 0419062224

# MASTER OF SCIENCE IN ELECTRICAL AND ELECTRONIC ENGINEERING

Department of Electrical and Electronic Engineering Bangladesh University of Engineering and Technology

Dhaka, Bangladesh

May 06, 2023

The thesis titled, "VARIABILITY AND SELF-HEATING ANALYSIS OF SPIN TRANSFER TORQUE MAGNETIC RANDOM ACCESS MEM-ORY DEVICES", submitted by Bejoy Sikder, Roll No.: 0419062224, Session: April 2019, has been accepted as satisfactory in partial fulfillment of the requirements for the degree of Master of Science in Electrical and Electronic Engineering on May 06, 2023.

### BOARD OF EXAMINERS

Dr. Md. Zunaid Baten Associate Professor Dept. of EEE, BUET, Dhaka

Dr. Md. Aynal Haque Professor and Head Dept. of EEE, BUET, Dhaka

9

Dr. Samia Subrina Professor Dept. of EEE, BUET, Dhaka

Dr. Orchi Hassan Assistant Professor Dept. of EEE, BUET, Dhaka

Dr. Md. Anwarul Abedin Professor Department of EEE, Dhaka University of Engineering & Technology, Gazipur

Chairman (Supervisor)

Member (Ex-Officio)

Member

Member

Member (External)

## DECLARATION

This is to certify that the work presented in this thesis paper, titled, "VARIABILITY AND SELF-HEATING ANALYSIS OF SPIN TRANSFER TORQUE MAGNETIC RANDOM ACCESS MEMORY DEVICES", is the outcome of the investigation and research carried out by BEJOY SIKDER under the supervision of Dr. Md. Zunaid Baten, Associate Professor, Department of Electrical and Electronic Engineering (EEE), Bangladesh University of Engineering and Technology (BUET).

It is also declared that neither this thesis book nor any part thereof has been submitted anywhere else for the award of any degree, diploma or other qualifications.

Bejoy Sixder

BEJOY SIKDER Roll: 0419062224 May 06, 2023

## ACKNOWLEDGEMENT

I am thankful to Almighty for His blessings for the successful completion of my thesis. My heartiest gratitude, profound indebtedness, and deep respect go to our supervisor, Dr. Md. Zunaid Baten, Associate Professor, Department of Electrical and Electronic Engineering (EEE), Bangladesh University of Engineering and Technology for his constant supervision, affectionate guidance, and great encouragement and motivation. His keen interest in the topic and valuable advice throughout the study were of great help in completing the thesis.

I am especially grateful to Dr. Md. Aynal Haque, Dr. Anwarul Abedin, Dr. Samia Subrina, and Dr. Orchi Hassan for their consent to be on my board of examiners. I would also like to thank my collaborators Uday Kamal, Mondal Anik Kumar, Dr. Jia Hao Lim, Joel Tan, Dr. Nagarajan Raghavan, Dr. Kin-Leong Pey, Dr. Andrea Padovani, and Dr. Luca Larcher for providing their assistance in my research papers published from this thesis work. I appreciate the support from the Department of Electrical and Electrical Engineering (EEE) of Bangladesh University of Engineering and Technology (BUET) during my M.Sc. courses and thesis work. Finally, I would like to thank my family members, especially my mother, Provati Sikder, and sister, Projecta Sikder, for supporting me through many sleepless nights during my academic career. I extend my appreciation to Brishty Karmakar for her consistent and invaluable assistance over the past several years. My sincere thanks to Mr. Shahnewaz Ahmed for his useful suggestions and helps regarding simulation work.

## ABSTRACT

Spin Transfer Torque Magnetic Random Access Memories (STT-MRAMs) are promising candidates for next-generation data storage due to their non-volatility, fast access times, scalability, low power consumption, and compatibility with conventional CMOS technologies. The primary building block of an STT MRAM is the Magnetic Tunnel Junction (MTJ), which consists of two ferromagnetic layers separated by an insulating layer. However, owing to the small dimensionalities, STT-MRAMs are significantly prone to device-to-device and cycle-to-cycle variations. Moreover, the high current density required to program the MTJ invariably leads to self-heating, which significantly influences the device's performance and may even cause the breakdown of the insulating layer, thereby significantly limiting their reliability. In this thesis, a simulation framework for studying the device-to-device variability along with the self-heating analysis capability of the STT MRAM device has been developed. The proposed framework has been validated against reported experimental results in the literature. Within this framework, device-to-device variability of CoFeB/MgO-based STT-MRAMs is studied, considering the influence of interface quality, temperature variation, and device dimensionality. Metal-induced gap states resulting from electron transfer at the ferromagnet-tunnel barrier interface significantly influence these devices' effective energy barrier height, irrespective of their diameters. Switching voltage and parallel-antiparallel resistance values vary by as much as 43% and 30%. respectively, for about 13% variation of the energy barrier, whereas the tunneling magnetoresistance remains typically unaffected. WRITE cycles of highly scaled STT-MRAMs are, therefore, more susceptible to device-to-device variations resulting from microscopic variations in the interface quality rather than the READ cycles. Such variations are observed to be independent of temperature as well as the spatial distribution of the defects. Moreover, in this thesis, our proposed simulation framework has been extended to present a theoretical study of self-heating, taking into account the magnetic switching dynamics and threedimensional heat transfer characteristics of STT MRAM devices. The impact of self-heating has been explored for different dimensions, geometrical aspects, and bias conditions of the device. The temperature rise of the MTJ stack is observed to be strongly dependent on the choice of the encapsulating material and top metal layer thickness. Because of the asymmetry of the stack, device-to-device self-heating variability is expected to be more prominent in undercut structures than in overcut ones. From transient analysis, it is observed that during both unipolar and bipolar pulsing conditions, MRAM switching is accompanied by an abrupt temperature change of around 25-30 K. The results of this work suggest that consideration of magnetic switching dynamics is essential to accurately estimate self-heating during transient and steady-state operations of STT-based MTJ devices.

# TABLE OF CONTENTS

| Ce          | ertifi | cation                                      | i   |

|-------------|--------|---------------------------------------------|-----|

| De          | eclar  | ation                                       | ii  |

| A           | CKN    | OWLEDGEMENT                                 | iii |

| $A_{\cdot}$ | BST.   | RACT                                        | iv  |

| TÆ          | ABL]   | E OF CONTENTS                               | v   |

| LI          | ST (   | OF FIGURES                                  | x   |

| LI          | ST (   | OF TABLES                                   | xi  |

| LI          | ST (   | OF ABBREVIATION                             | 1   |

| 1           | Intr   | roduction                                   | 2   |

|             | 1.1    | Introduction                                | 2   |

|             |        | 1.1.1 Spin Transfer Torque MRAM (STT-MRAM)  | 4   |

|             | 1.2    | Literature Review                           | 5   |

|             | 1.3    | Motivation of the Work                      | 9   |

|             | 1.4    | Objectives of the Work                      | 9   |

|             | 1.5    | Thesis Outline                              | 10  |

| <b>2</b>    | The    | eory of Magnetic Tunnel Junction            | 11  |

|             | 2.1    | Introduction to Spintronics                 | 11  |

|             | 2.2    | Historical Advances in Spintronics Research | 11  |

|             | 2.3    | Basic Concepts of Spintronics               | 13  |

|             | 2.4    | MTJ Working Principle                       | 13  |

|             | 2.5    | MTJ Switching Mechanisms                    | 16  |

|              | 2.6 | Model    | ing of MTJ                                             | 19 |

|--------------|-----|----------|--------------------------------------------------------|----|

|              |     | 2.6.1    | Magnetization Dynamics: LLGS Equation                  | 20 |

|              |     | 2.6.2    | Effective Magnetic Field                               | 21 |

|              |     | 2.6.3    | Demagnetization Field                                  | 21 |

|              |     | 2.6.4    | Voltage Controlled Magnetic Anisotropy                 | 22 |

|              |     | 2.6.5    | Resistance Calculation                                 | 23 |

|              |     | 2.6.6    | Trap Assisted Tunneling (TAT)                          | 24 |

| 3            | Dev | vice-to- | Device Variability in STT-MRAM                         | 27 |

|              | 3.1 | Descri   | ption of the Simulation Framework                      | 28 |

|              | 3.2 | Result   | s and Discussions                                      | 28 |

|              |     | 3.2.1    | Experimental Reports on Device-to-Device Variability   | 28 |

|              |     | 3.2.2    | Analysis of Origin of the Device-to-Device Variability | 29 |

| 4            | Var | iability | y of Self-Heating in STT MRAM                          | 38 |

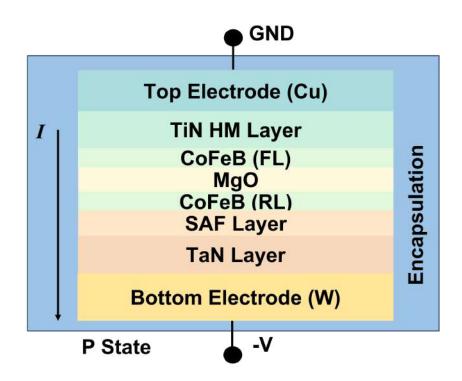

|              | 4.1 | STT N    | MRAM Stack and Self-Heating Model                      | 39 |

|              | 4.2 | Under    | cut and Overcut structures                             | 40 |

|              | 4.3 | Result   | s and Discussions                                      | 42 |

|              |     | 4.3.1    | Spatial and Temporal Heat Distribution of MRAM Stack   | 42 |

|              |     | 4.3.2    | Impact of Size Variations                              | 43 |

|              |     | 4.3.3    | Impact of Shape Variation                              | 45 |

|              |     | 4.3.4    | Impact of Variation of Encapsulation                   | 45 |

|              |     | 4.3.5    | Self-Heating under different pulsed operations         | 46 |

| <b>5</b>     | Cor | nclusio  | ns                                                     | 51 |

|              | 5.1 | Summ     | ary of the Present Work                                | 51 |

|              | 5.2 | Sugge    | stions for Future Works                                | 52 |

| $\mathbf{R}$ | EFE | RENC     | ES                                                     | 53 |

# LIST OF FIGURES

| 1.1 | Memory hierarchy in a conventional computer architecture [1]                                                                                                                                                                                                                                                                     | 3  |

|-----|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

| 1.2 | Processor Memory Performance Gap [5]                                                                                                                                                                                                                                                                                             | 3  |

| 1.3 | MJT cell of an STT-MRAM [6]                                                                                                                                                                                                                                                                                                      | 4  |

| 2.1 | Spin-dependent tunneling of electrons in an MTJ while the magneti-<br>zation directions in two FM layers are parallel (bottom left) and anti-<br>parallel (bottom right) [52].                                                                                                                                                   | 15 |

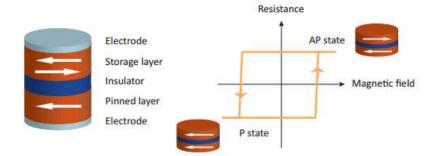

| 2.2 | MTJ consists of three layers: two FM layer separated by an oxide bar-<br>rier. The device resistance $(R_P \text{ and } R_{AP})$ depends on the correspond-<br>ing state of the magnetization of the two FM layers, Parallel(P) or<br>Anti-parallel (AP). The MTJ state can be switched by modulating the<br>magnetic field [53] | 16 |

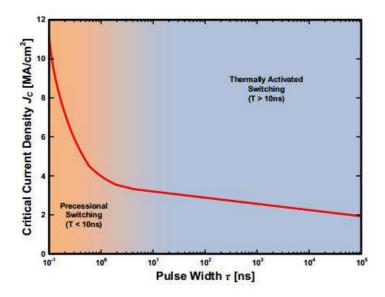

| 2.3 | MTJ Switching Regimes [57].                                                                                                                                                                                                                                                                                                      | 17 |

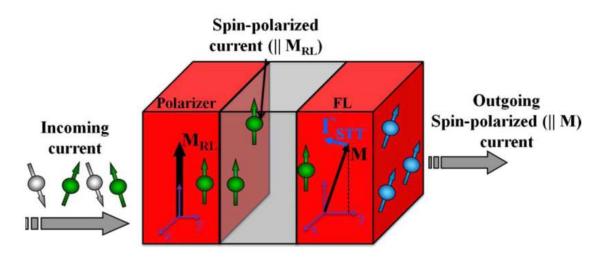

| 2.4 | Spin Transfer torque switching mechanism from anti-parallel (AP) to parallel (P) configuration [61].                                                                                                                                                                                                                             | 18 |

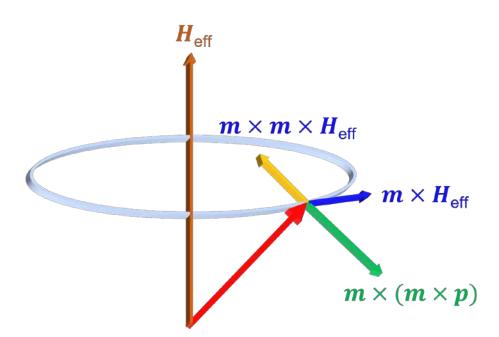

| 2.5 | Illustration of different terms in LLGS equation                                                                                                                                                                                                                                                                                 | 19 |

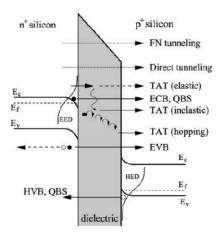

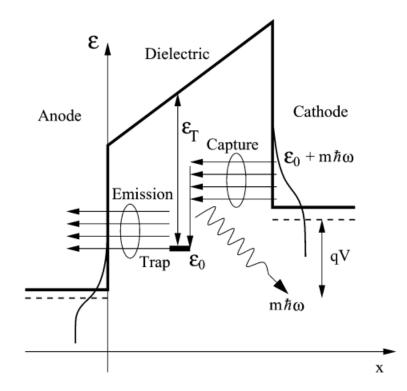

| 2.6 | Tunneling processes in a MOS transistor [75].                                                                                                                                                                                                                                                                                    | 24 |

| 2.7 | Inelastic phonon emission model of trap assisted tunneling. Electrons, after being captured from the cathode, are relaxed to the trap energy level by phonon emission and then emitted to the anode [75,81]                                                                                                                      | 25 |

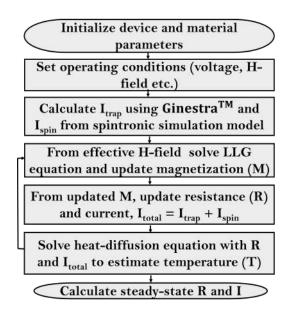

| 3.1 | Flowchart of the developed simulation framework                                                                                                                                                                                                                                                                                  | 28 |

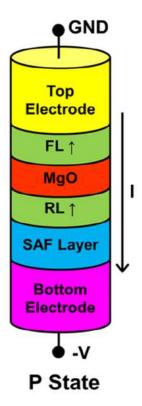

| 3.2 | Schematic illustration of considered MTJ pillar.                                                                                                                                                                                                                                                                                 | 29 |

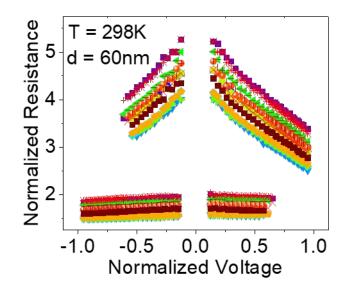

| 3.3 | Measured R-V loops of $d = 60$ nm devices fabricated on the same wafer [94].                                                                                                                                                                                                                                                     | 30 |

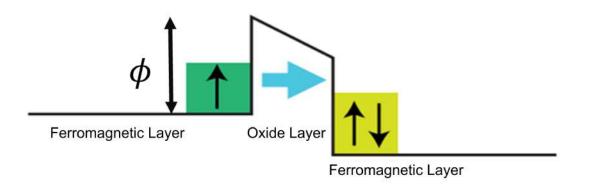

| 3.4 | Schematic of the definition of Oxide Barrier Height                                                                                                                                                                                                                                                                              | 30 |

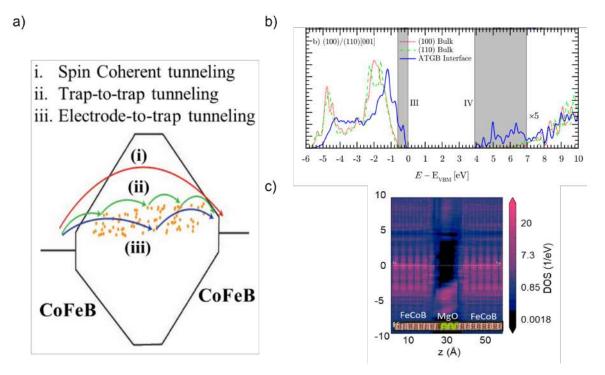

| 3.5 | a) Proposed Band diagram of the MTJ device involving MIGS. b)-c)<br>Reported Ab-initio calculations showing the density of states (DOS) in<br>C = D / M = O / C = D = [0.4, 10.2]                                                                                                                                                | 01 |

|     | CoFeB/MgO/CoFeB [94, 102]                                                                                                                                                                                                                                                                                                        | 31 |

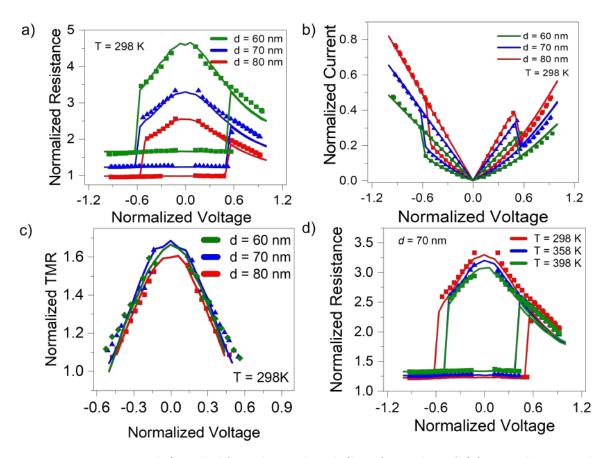

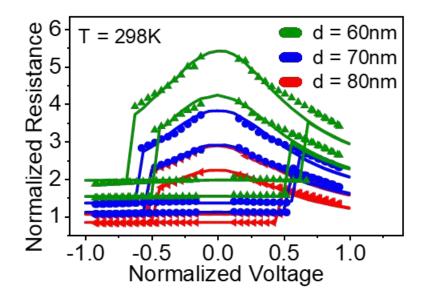

| 3.6  | Measured (symbols) and simulated (lines) results of (a) R-V loops and<br>(b) I-V loops (c) TMR vs. voltage characteristics and (d) R-V loops at<br>different temperature for $d = 70$ nm                                                                                                                                                                                                                                          | 32 |

|------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

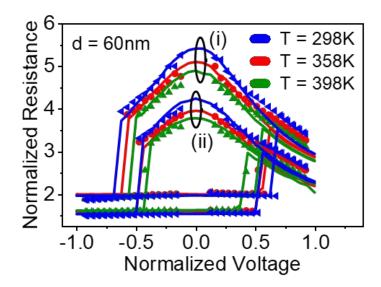

| 3.7  | Measured (symbols) and simulated (lines) R-V loops for highest and lowest resistance values of each diameter.                                                                                                                                                                                                                                                                                                                     | 33 |

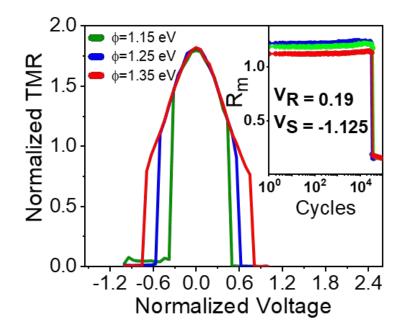

| 3.8  | Effect of $\phi$ on TMR of the device; inset shows $R_{\rm m}$ obtained for multiple READ cycles during TDDB measurements where $V_{\rm R}$ and $V_{\rm S}$ refer to normalized READ and stress voltages respectively.                                                                                                                                                                                                            | 34 |

| 3.9  | Effect of operating temperature variation on R-V loops corresponding to extracted values of (i) $\phi$ = 1.35-1.36 eV and (ii) $\phi$ = 1.20-1.23 eV                                                                                                                                                                                                                                                                              | 35 |

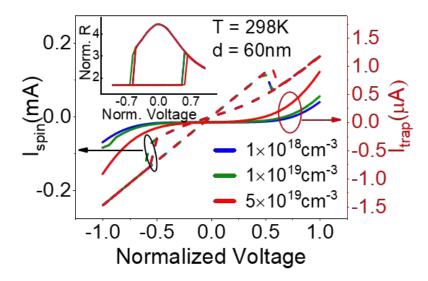

| 3.10 | Comparison of spin (solid lines) and trap current (dashed lines) densities<br>for different concentrations of bulk defects (effect on R-V loop shown<br>as inset)                                                                                                                                                                                                                                                                 | 35 |

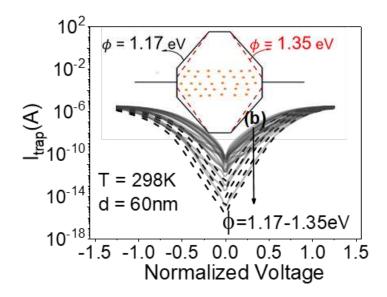

| 3.11 | Trap currents calculated from linear (dashed lines) and statistical (solid lines) variation of $\phi$ ; inset shows energy band diagram illustrating the physical significance of $\phi$                                                                                                                                                                                                                                          | 36 |

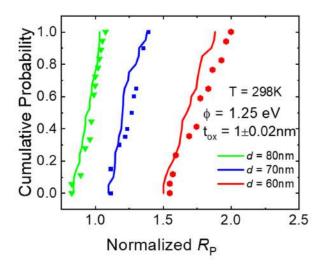

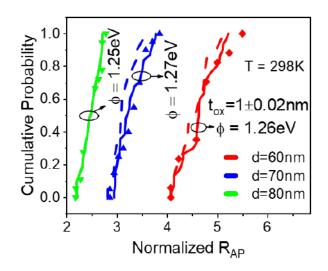

| 3.12 | CDF plot of zero-bias $R_{\rm P}$ considering the statistical variation of $t_{\rm ox}$ (experimental results shown as symbols whereas dashed lines show fits with a fixed value of $\phi = 1.25$ eV for all devices)                                                                                                                                                                                                             | 37 |

| 3.13 | CDF plot of zero-bias $R_{\rm AP}$ considering the statistical variation of $t_{\rm ox}$ (experimental results are shown as symbols whereas dashed lines show fits with a fixed values of $\phi = 1.25$ eV and continuous line shows fit with corresponding values of $\phi$ for all devices)                                                                                                                                     | 37 |

| 4.1  | 2D schematic of the STT-MRAM stacks considered in this study for self-heating analysis.                                                                                                                                                                                                                                                                                                                                           | 40 |

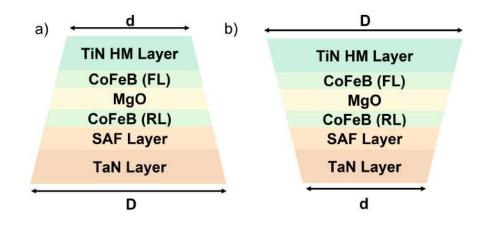

| 4.2  | 2D Schematic of a) Overcut and b) Undercut Structures. Here $D$ is the nominal diameter, and $d$ is the diameter of the upper (lower) layer for overcut(undercut) structure. $D$ - $d$ is the amount of overcut or undercut.                                                                                                                                                                                                      | 41 |

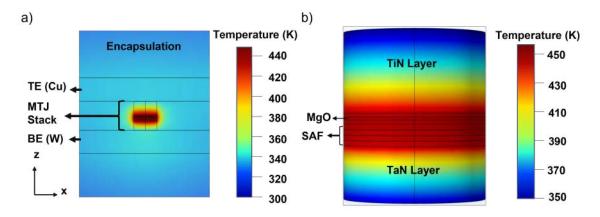

| 4.3  | a) Spatial temperature distribution of the whole STT-MRAM Stack<br>along with the electrodes and encapsulation and b) temperature distri-<br>bution of the MTJ stack along the z-x plane under the application of<br>-0.8 V pulse for 5 $\mu$ s. The diameter of the cylindrical MTJ is 70 nm.<br>From the distribution, it is evident that most of the heating occurs at<br>the MgO layer, and it reaches up to 450K temperature | 42 |

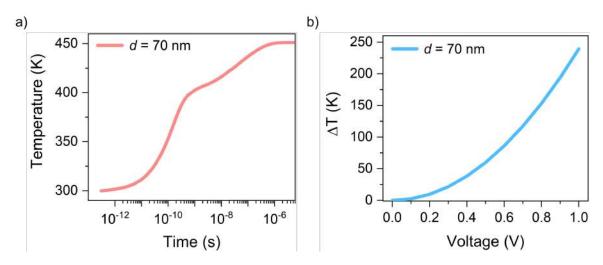

| 4.4  | a) Temporal Temperature profile for 70 nm MTJ under the application<br>of -0.8V for 5 $\mu$ s. b) Temperature Rise $\Delta T$ vs. Applied negative bias<br>voltage (UNI-) curve for MTJ with 70 nm diameter. The curve resem-<br>bles a parabola. Fitting this curve to the equation $\Delta T = R_{\rm th} \frac{V^2}{R_{\rm MTJ}}$ , we<br>can obtain $R_{\rm th}$ .                                                                                                                                                                                                                                                                                    | 43 |

|------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

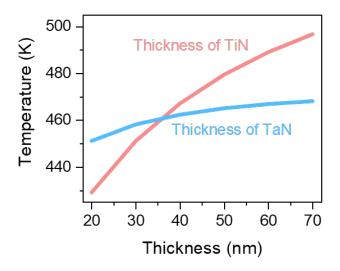

| 4.5  | Variation of the steady-state temperature with the thickness of TiN and TaN layers. In both cases, the steady-state temperature increases with the thickness of the TiN and TaN layers. But in the case of the TiN layer, the change is more prominent than the TaN layer                                                                                                                                                                                                                                                                                                                                                                                 | 44 |

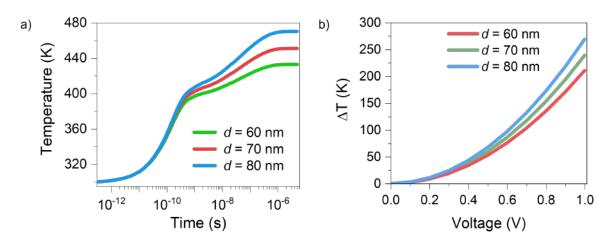

| 4.6  | a) The temporal temperature profile of MTJ stack with diameter 60,<br>70, and 80 nm under the application of -0.8 V pulse for 5 $\mu$ s. b) steady-<br>state temperature rise $\Delta$ T vs bias voltage (V). Here the bias voltage is<br>UNI- as per our convention.                                                                                                                                                                                                                                                                                                                                                                                     | 44 |

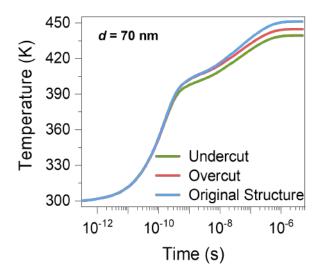

| 4.7  | Temporal temperature profile for undercut, overcut, and original struc-<br>ture for the nominal diameter of 70 nm                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 45 |

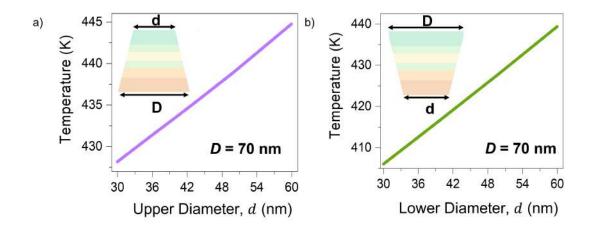

| 4.8  | Steady-state temperature for a) different upper diameter for Overcut<br>and b) different lower diameter for Undercut structure. The tempera-<br>ture rise is always lower in the case of the undercut. However, the range<br>of the temperature rise is larger for the undercut than the overcut struc-<br>ture for the same diameter values                                                                                                                                                                                                                                                                                                              | 46 |

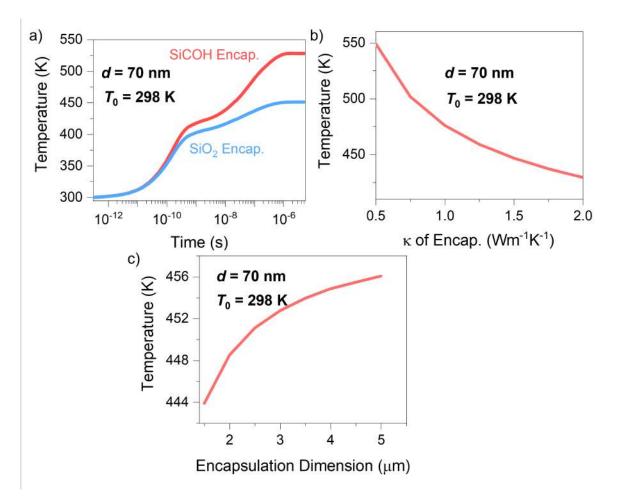

| 4.9  | a)Effect of encapsulation on the temporal temperature profile of an MTJ. Temperature increases more for lower thermal conductivity encapsulation, i.e. SiCOH than SiO2 b) Steady-state Temperature vs thermal conductivity ( $\kappa$ ) of encapsulation. c) Steady-state temperature for different encapsulation dimensions which shows an upward but very gradual rise. The initial and boundary temperatures for all cases are 298 K, as shown in the figure.                                                                                                                                                                                          | 47 |

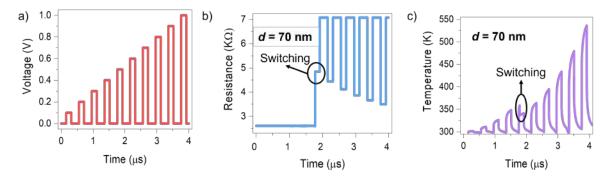

| 4.10 | a) Applied ramped positive voltage pulse with period 4 $\mu$ s and duty cy-<br>cle 40%. Here only one period is shown. b) The corresponding resistance<br>state of MTJ. Around 2 $\mu$ s, i.e. at 0.5V, there is a change in resistance<br>values which indicates the switching of MTJ from $R_{\rm P}$ to $R_{\rm AP}$ . c) Tem-<br>perature vs. time curve for ramped positive bias. The spike around 2 $\mu$ s<br>corresponds to the switching of MTJ. Also, the temperature initially<br>increases with the bias, but after switching, it gets decreased as the<br>resistance after switching is higher ( $R_{\rm AP}$ ), which results in lower heat |    |

|      | and lower temperature before switching                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 48 |

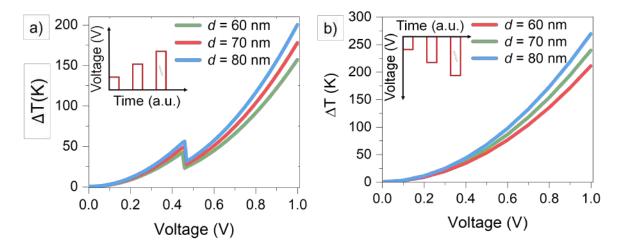

4.11 Steady state temperature under the application of a) positive ramped pulses and b) negative ramped pulses for different diameters. According to our convention, positive ramped pulses switch MTJ from  $R_{\rm P}$  to  $R_{\rm AP}$ , and so a discontinuity in Figure a) is observed. Also, due to the higher resistance of smaller devices, the temperature rise is lowest for 60 nm diameter.

48

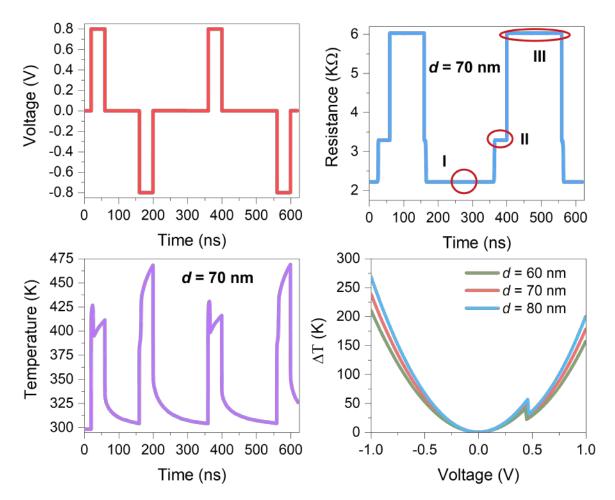

4.12 a) Applied bipolar voltage pulse with magnitude 0.8 V with period 310 ns. Here two periods are shown. b) The corresponding resistance state of MTJ. Three distinct resistance states are evident from this figure. The lowest one is the RP state (marked by I), the middle one is the resistance in the AP state at 0.8V (marked by II), and the highest one is the resistance in the AP state at 0.8V (marked by III). c) Temperature vs. time curve for the application of the bipolar pulse. The spikes correspond to the switching between different R states of MTJ, as mentioned in Fig. 4b). d) Steady-state temperature rise for the application of bipolar ramped pulse from -1V to 1V.

# LIST OF TABLES

| 1.1 | Comparison of existing, prototypical, and emerging embedded memory<br>technologies .*Energy only refers to single cell, without considering the                                              |    |

|-----|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

|     | bit lines and peripheral circuits [7]                                                                                                                                                        | 5  |

| 1.2 | Different types of defects in STT-MRAM [36, 37, 43]                                                                                                                                          | 9  |

| 2.1 | Historical Advances in Spintronics Research [47]                                                                                                                                             | 12 |

| 2.2 | Defect parameters used to calculate trap current and comparison with ab-initio calculations and experiments.                                                                                 | 26 |

| 3.1 | Average Barrier Height Used to calculate $R_p$ and comparison with ab-<br>initio calculations and experiments $\ldots \ldots \ldots \ldots \ldots \ldots \ldots \ldots \ldots \ldots \ldots$ | 32 |

| 3.2 | Extracted values of $\phi$ , and measured percentage (%) variation and per-<br>centage standard deviation (% $\sigma$ ) of $R_{\rm p}$ and $R_{\rm AP}$ .                                    | 33 |

| 4.1 | Material Parameters used for Simulation                                                                                                                                                      | 41 |

| 4.2 | Extracted $R_{\rm th}$ for different diameters $\ldots \ldots \ldots \ldots \ldots \ldots \ldots$                                                                                            | 44 |

# LIST OF ABBREVIATIONS

| DRAMDynamic Random Access MemoryFLFree LayerFMFerromagneticHDDHard Disk DriveLLGLandau Lifshitz GilbertLLGSLandau Lifshitz Gilbert SlocnzewskiMIGSMetal Induced Gap States |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| FMFerromagneticHDDHard Disk DriveLLGLandau Lifshitz GilbertLLGSLandau Lifshitz Gilbert Slocnzewski                                                                         |

| HDDHard Disk DriveLLGLandau Lifshitz GilbertLLGSLandau Lifshitz Gilbert Slocnzewski                                                                                        |

| LLGLandau Lifshitz GilbertLLGSLandau Lifshitz Gilbert Slocnzewski                                                                                                          |

| <b>LLGS</b> Landau Lifshitz Gilbert Slocnzewski                                                                                                                            |

|                                                                                                                                                                            |

| MIGS Metal Induced Gap States                                                                                                                                              |

| Mildo Mildar Maded Cap States                                                                                                                                              |

| MRAM Magnetic Random Access Memory                                                                                                                                         |

| MTJ Magnetic Tunnel Junction                                                                                                                                               |

| <b>NEGF</b> Non-equilibrium Green's Function                                                                                                                               |

| PDOS Projected Density of States                                                                                                                                           |

| <b>RL</b> Reference Layer                                                                                                                                                  |

| <b>SAF</b> Synthetic Anti-Ferromagnetic                                                                                                                                    |

| SH Self-Heating                                                                                                                                                            |

| SOT Spin Orbit Torque                                                                                                                                                      |

| SRAM Static Random Access Memory                                                                                                                                           |

| <b>STT</b> Spin Transfer Torque                                                                                                                                            |

| <b>TAS</b> Thermally Assisted Switching                                                                                                                                    |

| <b>TAT</b> Trap Assisted Tunneling                                                                                                                                         |

| <b>TDDB</b> Time Dependent Dielectric Breakdown                                                                                                                            |

| <b>TMR</b> Tunnel Magnetoresistance                                                                                                                                        |

| VCMA Voltage Controlled Magnetic Anisotropy                                                                                                                                |

# CHAPTER 1 INTRODUCTION

### 1.1 Introduction

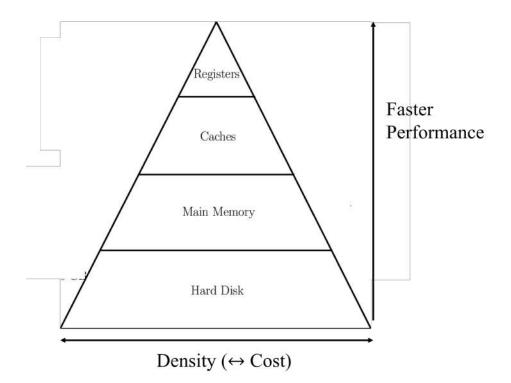

Conventional memory architecture consists of different types of memory technologies, each having its own performance attributes. The memory hierarchy is shown in Fig. 1.1. Computers usually store a small amount of frequently used data in the fast SRAM caches, while a large amount of seldom used data are stored in the slow hard disk drive (HDD). Thus conventional architectures combine the high speed of the cache memory and the low cost of the HDD. The memory devices used in traditional devices can largely be categorized as: i) Volatile and ii) Non-volatile Memory. Volatile memories cannot retain their data after the power is cut. On the other hand, non-volatile memories can retain their data for a long period of time, even after the power is off. Static Random Access Memory (SRAM) and Dynamic Random Access Memory (DRAM) are two of the most notable examples of volatile memory. On the other hand, Flash, EPROM, HDD, etc., are non-volatile ones.

SRAMs are usually used as CPU registers and cache (L1-L3) and store data statistically. On the other hand, DRAMs are usually used as the main working memory and require a periodical refresh. Flash is used as portable and integrated storage for consumer electronics and magnetic hard disks. Every memory device has its own pros and cons. SRAM has a lower access time, so it is fast. However, SRAM requires a constant power supply and so consumes higher static power. The circuitry required for SRAM is also very complex and costly. On the other hand, DRAM is slower than SRAM. But it offers reduced power consumption and requires small internal circuitry. It also has a high packaging density. On the other side of the spectrum, flash and HDD are non-volatile memory, but they have much lower access speeds and larger energy consumption for memory operations. But both of them have low cost and high density. However, during the last few decades, electronic device usage has increased immensely, ranging from computing devices to wearable ones. The major drive behind this growth is the ever-increasing logic computational capabilities which result in doubling computer chip transistor density every 18 months, popularly known as Moore's law. Despite the tremendous development of logic units in an electronic devices, the memory performance has not been on the same par. This created the

Figure 1.1: Memory hierarchy in a conventional computer architecture [1].

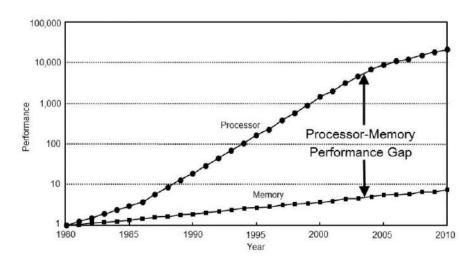

processor-memory gap, memory wall, or memory bottleneck, as shown in Fig. 1.2. Existing electronic memory devices cannot provide high speed, bandwidth, and less power consumption simultaneously. Various physical mechanisms have been proposed to resolve this memory wall issue. Several emerging non-volatile memory (NVM) technologies have been explored to improve speed, bandwidth, and power consumption. Magnetic Random Access Memory (MRAM) is one of the most promising candidates for this purpose. Spin Transfer Torque MRAM (STT-MRAM) is a type of MRAM considered universal memory owing to high endurance, faster access time, low power consumption, and CMOS compatibility [2–4].

Figure 1.2: Processor Memory Performance Gap [5].

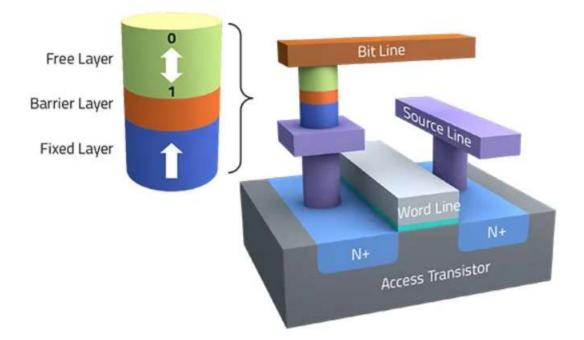

Figure 1.3: MJT cell of an STT-MRAM [6].

### 1.1.1 Spin Transfer Torque MRAM (STT-MRAM)

Spin Transfer Torque MRAM is a type of non-volatile memory that is considered to be one of the most significant inventions of spintronics. An STT-MRAM device with its primary component Magnetic Tunnel Junction (MTJ) along with Bit Line, Source Line and Write Line is shown in Fig. 1.3. Prior to STT-MRAM, spintronic devices were solely controlled by magnetic fields, which was a hindrance to the scaling of spintronics devices. In STT-MRAM, the spin-polarized current is used to apply spin transfer torque on the electron spins of a magnetic material which causes the device to switch between two states. STT-MRAM can replace embedded Flash, lower SRAM cache (L2-L3), and can be used in neuromorphic computing and Internet-of-things (IoT) due to its low power consumption. The comparison between different memory devices is given in Table 1.1.

The primary element in the MRAM technology is the magnetic tunnel junction (MTJ). In MTJ, two ferromagnetic layers are separated by an insulating layer which is called the tunnel barrier. One of the ferromagnetic layers is called the reference layer (RL) whose magnetization orientation is kept fixed and the other one's magnetization can vary in space which is called free layer (FL). For ensuring the stability of RL, other layers such as SAF (Synthetic Anti-Ferromagnetic) layer, Hard Layer etc. are used. These layers are described in detail in chapter 4. MTJ can have two stable orientations: i) when both magnetization vectors of RL and FL are in parallel and ii) when they are in anti-parallel orientations. Depending on these two orientations, the MTJ can have

Table 1.1: Comparison of existing, prototypical, and emerging embedded memory technologies .\*Energy only refers to single cell, without considering the bit lines and peripheral circuits [7].

|                             | Existing                   | Emerging            | Existing  | Prototype |

|-----------------------------|----------------------------|---------------------|-----------|-----------|

| Technology                  | e Flash                    | eReRAM              | eDRAM     | STT-MRAM  |

| Endurance (Cycles)          | 105                        | $10^{5}$            | $10^{15}$ | $10^{15}$ |

| Read Time (ns)              | 10                         | 3-10                | 1-2       | 1-5       |

| Write/Erase Time (ns)       | $25 \ \mu { m s}/2{ m ms}$ | $500/100~\mu{ m s}$ | 1-2       | 5-10      |

| Cell Size (area in $F^2$ )  | 40-100                     | 15-30               | 40-100    | 40-50     |

| Bit Density $(Gb/cm^2)$     | 0.5-1                      | 1.5-3               | 0.5-1     | 1         |

| Read Energy/Bit (fJ)        | $10^{6}$                   | 1000                | 100       | 10-20     |

| Write/Erase Energy/bit (fJ) | $10^{6}$                   | $1000/10^{6}$       | 1000      | 100-200   |

| Non Volatile                | Yes                        | Yes                 | No        | Yes       |

| Standby Power               | None                       | None                | Refresh   | None      |

two resistance states. Switching from one state to another is possible by the application of current or external bias fields. In STT-MRAM, spin transfer torque switching mechanism is used. Detailed theoretical backgrounds are provided in Chapter 2 of this thesis.

### 1.2 Literature Review

STT-MRAM is one of the most promising devices Spintronics has offered. Over the last few years, there has been several research works focusing on the modeling and device physics-related aspects of MTJ and STT-MRAM. Although this work does not include the neuromorphic application of these devices, a lot of research focus has been on this particular application field. Overall, STT-MRAM has been an active field of research in recent years. An accurate physics-based device model for the MTJ is required to investigate its electrical behavior along with stochastic switching and device-to-device variability. There exist two types of models for MTJ: static and dynamic.

Static models explain the switching of an MTJ with the concept of a threshold current or switching time. It utilizes the Julliere model to determine the stable state depending on whether switching has been occurred or not. W. Zhao et al. proposed a macromodel implemented in Verilog-A, which utilizes a combination of the Juliere model and Brinkman's model to determine the bias-dependent conductance of different MTJ states [8]. They derived a simplified expression using Slonczweski for switching current based on which the different states of MTJ are determined [9,10]. But this model only considers switching due to thermal fluctuations and constant current amplitude. Also, it does not consider the temperature dependence of different parameters and the stochastic switching nature of MTJ. S.S. Mukherjee et al. proposed a SPICE micro static model utilizing the hysteresis behavior of MTJ [11]. However, this model fails to capture the transient behavior and stochastic switching of MTJ. Another SPICE model proposed by J.D. Harms includes a decision circuit [12]. Based on its decision, MTJ switches for a given bias and its duration. Switching of MTJ is accomplished by utilizing the charging time of a capacitor for a given constant current. However, such a simplified model based on capacitor charging is inadequate to capture the magnetization dynamics in an MTJ.

The static models fail to capture the dynamics of the magnetization of an MTJ upon the application of bias. To solve this issue, several dynamic models have been proposed. L. Faber et al. [13] proposed an extended and modified version of the static model developed by W.Zhao [8], which includes heating effect and stochastic switching behavior. The model captures the dynamic nature of magnetization by considering two regions. When the applied current is lower than the critical current, the switching time is calculated by Neel-Brown Model [14]:

$$\tau_1 = \tau_0 \exp\left\{\left(\frac{\Delta E}{k_B T} \left(1 - \frac{I}{I_{C0}}\right)\right)\right\}$$

(1.1)

where T is the temperature,  $k_B$  is the Boltzmann constant,  $1/\tau_0$  is the attempt frequency and  $\Delta E$  is the energy barrier. For higher bias current, the model utilizes Sun's proposed model to compute the switching time:

$$\tau_2 = \frac{1}{\alpha \mu_0 \gamma M_s} \frac{I_{C0}}{I - I_{C0}} \ln \frac{\pi}{2\theta_0}$$

(1.2)

where  $\theta_0$  is the initial angle of the magnetization vector from the easy axis. This model also includes the heating effect by calculating temperature rise and fall, considering voltage across MTJ, current amplitude, and material thermal conductivity. This model utilizes equation 1.1 and 1.2, which are derived from the LLGS equation using some assumptions [15]. It assumes the small deviation of the initial angle  $\theta_0$ from the easy axis and constant amplitude for the applied current pulse, which are not always the case. As a result, this model fails to capture the transient behavior of MTJ switching under STT. M. Madec et al. [16–18] developed an improved dynamic model which incorporates both magnetic and non-linear electronic transport phenomena. LLGS equation is used to model the magnetic dynamics. The conductance is calculated using Julliere and Brinkmann's formalism, taking the bias dependence of conductance G and TMR into account. This model is implemented in VHDL. The self-heating effect is not considered in this work.

A. Nigam et al. [19] proposed a SPICE model that solved the LLG equation and ob-

tained the transient behaviors of MTJ. To capture the steady state properties, the Simmons tunnel current model is used [20]. Transmission probabilities of the carrier tunneling through the barrier and the available density of states are used to compute the I-V characteristics. The models discussed so far considered MTJ with in-plane magnetic anisotropy only. Zhang et al. [21] developed a device model of an MTJ with perpendicular magnetic anisotropy (p-MTJ) switched by STTs for the first time. MTJ conductances were calculated using Brinkman's model along with the voltagedependent TMR model. Switching behavior is captured by utilizing a threshold current and average switching time obtained from the approximated solution of LLG equation [22, 23].

C. Augustine et al. [24] presented a coupled Non-equilibrium Green's Function (NEGF) and LLG framework for the numerical analysis of STT MTJ stacks for 1T-1R memory arrays. The authors utilized a set of experimentally calibrated MTJ parameters to obtain the charge and spin current density using NEGF. The STT is calculated from the differences of spin currents in the free layer of MTJ and used to solve LLG. The model was capable of predicting switching current density, TMR, etc., and electrical properties of MTJ. In the initial stages of the model described here, they were only simulating the static and dynamic behavior of an MTJ switched by STT. Later several models were proposed or modified to include the variability study of the devices. G. Panagopoulous et al. [25] modified the coupled LLG+NEGF model proposed in [24] to simulate time-dependent dielectric breakdown following the analysis developed for MOSFET gate dielectric models. In this work, the soft breakdown is modeled as a voltage-dependent current source parallel to the MTJ. The percolation current is assumed to be independent of the MTJ state and following a power law [25]. This model is able to model the TMR, switching performance, and lifetime degradation of STT MRAM due to breakdown. Later the same group published several papers to explore the device performance and analysis under geometrical, process, and CMOS parameter variations along with design space and scalability analysis of the device [26-28]. All these frameworks are implemented in SPICE, and the components include several bias-dependent sources and other passive elements.

In [29], the authors proposed a physics-based statistical model that evaluates the TDDB impact of device performances considering oxide thickness. The percolation model is used for statistical analysis of breakdown behavior. In [30], the reliability and variability of STT-MRAM cell are studied under the fabrication and aging-induced process, supply voltage, and operating temperature (PVT) variation. Bit-cells with different thermal stability coefficients are analyzed for stochastic thermal effect. A. Chintaluri et al. [31] presented a systematic analysis of all possible defect and fault models. Process-induced variability study is carried out in this work considering the variation of MTJ material parameters such as magnetic anisotropy,  $H_{\rm k}$ , saturation

magnetization, *M*s, TMR, etc., transistor electrical parameters such as threshold voltage, lithographic variation, and thermal fluctuations. In this work, both inter and intra-cell defects and faults are modeled by resistive shorts and open. Interconnect faults are also included. Few other papers also focused on the device performances of an STT-MRAM under process, material parameters, and operational conditioninduced variations by utilizing Monte-Carlo or other statistical frameworks [32,33]. Defect analysis is very crucial for the variability and reliability study of STT-MRAM.

In an STT-MRAM, several defects can be present such as manufacturing defects, material defects, the presence of oxygen vacancies, traps, etc. Different types of defects and their origins are given in table 1.2. Conventionally, spot defects in STT-MRAM are modeled as a linear resistor whose resistance value represents defect strength [34–36]. Typically, open, short, and bridge resistors are used for modeling defects.

In [37], the authors proposed a methodology for physical defect modeling by considering the modification of the affected technology parameters of the MTJ. Their methodology includes extraction of the defect-free and defective device parameters such as resistance-area (RA) product, TMR, barrier height,  $H_k$ ,  $M_s$ , etc. The affected experimentally obtained parameters are then used to calculate the electrical properties such as resistance, switching current, and R-V hysteresis loop of an MTJ. The simulation framework is validated against the experimental results. However, the existing models fail to consider the impact of traps, material defects, and the interface between oxide and ferromagnetic materials on the device-to-device variability of an STT-based MTJ device. Modeling and influences of such effects constitute the first part of the thesis.

Self-heating (SH) is another factor that controls the reliability of a device. Due to the small dimensions of an MTJ, direct experimental measurement of the temperature rise due to SH is a pretty difficult task. As a result, a simulation framework is required. Early works modeled the temperature rise by modeling the phenomenon by circuit elements such as resistors and capacitors [28,38]. Indirect measurements of temperature rise are reported by studying the TDDB and reliability of an MTJ [39,40]. Van Beek presented a simulation-based study of temperature rise and the impact of different parameters on SH [41]. Hadámek et al. [42] developed a 3D simulation model for solving the heat diffusion equation in an STT-MRAM stack coupled with the LLG equation. However, a theoretical study that reconciles the switching dynamics of the STT-MRAM with the heat transfer characteristics of the entire stack is currently missing. Moreover, it remains to be seen how an STT-MRAM's heat transfer characteristics will be influenced by its shape, size, surrounding, and biasing scheme. These aspects are considered in detail in the second part of the thesis.

| FEOL (Front End of Line)                                                                        | BEOL                                                                        | (Back End of Line)                                                                                                                                                                               |

|-------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Transistor                                                                                      | Interconnect                                                                | MTJ Device                                                                                                                                                                                       |

| Material and Crystal defects,<br>Pinholes in gate oxide,<br>variation in dopants' position etc. | Open contacts,<br>Shape irregularities,<br>Presence of small particles etc. | Pinholes in Tunnel Barrier,<br>MTJ Sidewall redepositions,<br>Magnetization flipping in reference Layer,<br>Backhopping,<br>Material parameter variations,<br>MgO/CoFeB interface roughness etc. |

Table 1.2: Different types of defects in STT-MRAM [36, 37, 43].

## 1.3 Motivation of the Work

Variability and reliability studies of STT-MRAMs are essential to fully understand the utility of these devices for future memory and neuromorphic applications. Previous studies on STT-MRAM variability primarily focused on variations arising from process, operating temperature, and operating conditions in MRAM circuits or arrays. Though significant insights on the variability and reliability of STT-MRAMs have been obtained from these studies, the ongoing drive towards utilizing highly-scaled variants of these devices for memory and neuromorphic applications necessitates variability analysis from a microscopic point of view. In particular, aspects related to the role of interface quality and defects on device-to-device variation need to be investigated to have a better understanding of the source of variability in these devices. Moreover, a detailed analysis of self-heating, taking into account the magnetization dynamics of STT-MRAMs, is currently missing in the literature. To better understand the phenomenon, a coupled simulation framework is required, which may correlate the heat transfer with the switching dynamics of these devices under static and pulsed operations.

## 1.4 Objectives of the Work

The main objectives of the work are:

- 1. To gain insight into the origin of the variability of STT-MRAMs by analyzing the impact of device and materials parameters on the static and dynamic performances of these devices.

- 2. To evaluate the impact of interface quality and defects on the device-to-device variability of STT-MRAMs.

- 3. To analyze self-heating in STT-MRAMs taking into account the magnetization dynamics of these devices under both steady-state and transient conditions.

- 4. To investigate self-heating considering device-to-device variability of STT-MRAMs.

### 1.5 Thesis Outline

The rest of this thesis is organized as follows: Chapter 2 begins with a brief discussion of the history and origin of Spintronics. Then the fundamental theory of a magnetic tunnel junction, along with different spin transport and switching mechanisms, has been explained. Finally, the governing equations required to model an MTJ with STT switching effect are described along with the theory of trap-assisted transport mechanism.

Chapter 3 describes the simulation framework developed in this work to investigate the device-to-device variability of an STT-MRAM. Then the reported experimental results on device variability have been discussed. Finally, the impact of barrier height at the interface of oxide and ferromagnetic materials have been elucidated.

Chapter 4 reports the modeling and results of the variability of self-heating in an STT-MRAM stack due to size, shape, and different pulsed switching mechanisms. First, the necessary equations required to determine the self-heating resulting temperature rise are explained with necessary material parameters and boundary conditions. Finally, the sources and their impact on the self-heating variability of STT-MRAM have been investigated.

Chapter 5 concludes the work. It summarizes the work presented herein and highlights the possible impact of this thesis in future studies. A brief discussion on future scopes of experimental and theoretical research in this direction is presented as well.

# CHAPTER 2 THEORY OF MAGNETIC TUNNEL JUNCTION

The focus of this chapter is to introduce the basic concept related to the Magnetic Tunnel Junction device(MTJ) and the field of spintronics. The first section briefly details the spintronics-its history and fundamental physical operation. The second section of this chapter covers the characteristics and unique properties of the MTJ device. In the third section, we shall discuss the governing equations of an MTJ and how to use them to model this device's electrical behavior under applied bias.

### 2.1 Introduction to Spintronics

The word "Spintronics" is the amalgamation of the words "spin" and "electronics." According to the Oxford Dictionary, "Spintronics is the field of electronics in which electron spin is manipulated to yield the desired outcome." In conventional electronic devices, information processing works on the principle of control over the flow of charge through a material. On the contrary, spintronics involves the control and manipulation of both electron spin and charge in solid-state electronics [44, 45]. Large-scale nonvolatile memories (e.g., hard disk drives or HDDs) exploit ferromagnetism to store information by controlling the spin alignment of the electrons applying external means of the magnetic field [46].

### 2.2 Historical Advances in Spintronics Research

Table 2.1 shows the key milestones in spintronics research classified into the following four categories: discoveries, key experiments, device concept proposals, and chip-level demonstrations. At first, the electron was discovered in 1897 by J.J. Thomson. An electron has both charge and spin. The electron charge was measured with perfection by R.Millikan. Spin is an intrinsic conserved property of elementary particles with no classical electron counterpart. Owing to having spin properties, electrons possess a magnetic moment akin to a rotating charged body in classical electrodynamics. This fact was discovered in 1922 by Otto Stern and Walther Gerlach, famously known as the Stern-Gerlach experiment. The resulting intrinsic magnetic moment  $\mu$  of electron

|                                      | 1970                 | 1980                                                                       | 1990                                                                                         | 2000                                                                                                                                                                          | 2010                                                                                                                  |

|--------------------------------------|----------------------|----------------------------------------------------------------------------|----------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------|

| Discovery of<br>Phenomena/<br>Theory | 1971 SHE<br>1975 TMR | 1985 Spin injection<br>1988 GMR                                            | 1992 GMR based two<br>current model<br>1996 Spin torque transfer                             | 2001 MgO based MTJ<br>2007 Magnetoelectric effect                                                                                                                             |                                                                                                                       |

| Lab<br>Experiments                   |                      |                                                                            | 1991 GMR at room temp.<br>(1 <sup>st</sup> spin valve)<br>1995 TMR at room temp.             | 2000 STT switching at room temp.<br>2002 Perpendicular MTJ<br>2004 STT switching in MgO-MTJ<br>2007 Spin injection into spin channel<br>2008 Lateral spin valve switching     | 2010 Interfacial perpendicular MT,<br>2010 Multi-level MTJ<br>2012 Voltage-assisted switching,<br>Giant SHE switching |

| Device Concept<br>Proposal           |                      |                                                                            | 1990 Spin transistor<br>1997 GMR-MRAM<br>1998 TMR-MRAM                                       | 2000 Nano magnet logic<br>2003 Spin oscillator<br>2008 Racetrack domain wall memory                                                                                           | 2010 All spin logic<br>2012 Domain wall logic<br>2013 Spin random number<br>generator                                 |

| Circuit/Chip<br>Demonstration        | GMR: Giant N         | Il Effect<br>Magneto Resistance<br>lagneto Resistance<br>c Tunnel Junction | 1994 GMR field sensor<br>(1 <sup>st</sup> GMR product),<br>GMR Hard Disk<br>Drive (HDD) head | 2003 0.6µm 1Mb 1T-1MTJ<br>field-based MRAM<br>2005 1 <sup>st</sup> commercial MRAM,<br>180nm 4Kb STT-MRAM<br>2007 MgO-TMR HDD head<br>2009 45nm 32Mb STT-MRAM,<br>4Kb DW-MRAM | 2012 64Mb DDR3 STT-MRAM<br>(Everspin)                                                                                 |

Table 2.1: Historical Advances in Spintronics Research [47]

having spin angular momentum  $\mathbf{S}$  is:

$$\mu = \frac{g_s q}{2m} \mathbf{S} \tag{2.1}$$

where  $g_s$  is a dimensionless quantity called the *g*-factor. Later it was found that, like charge, spin is also quantized. The allowed values of **S** are:

$$S = \frac{\hbar}{2}\sqrt{n(n+2)} \tag{2.2}$$

where  $\hbar$  is the reduced Planck constant and n is an integer. Wolfgang Pauli provided the theory of spin in 1927 by using the basic foundations of quantum mechanics. Spin states in quantum mechanics are represented by "Pauli Matrices" given by the following representations:

$$\sigma_{\mathbf{x}} = \begin{pmatrix} 0 & 1 \\ 1 & 0 \end{pmatrix}$$

$$\sigma_{\mathbf{y}} = \begin{pmatrix} 0 & -i \\ i & 0 \end{pmatrix}$$

$$\sigma_{\mathbf{z}} = \begin{pmatrix} 1 & 0 \\ 0 & -1 \end{pmatrix}$$

(2.3)

In the early 1970s, a study on spin polarization tunneling on ferromagnet/insulator/superconducting aluminum junction was conducted [48]. This study showed that electron spin remains conserved in electron tunneling through insulators. This result created the possibility of spin-sensitive tunneling between two ferromagnetic films.

Later, Mikhail D'yakonov and Vladimir Petel' predicted the spin Hall effect in 1971- a spin flow perpendicular to the current flow direction. In 1975, Julliere gave his famous

formula for calculating the Tunneling Magnetoresistance (TMR) ratio in terms of polarization of the two ferromagnetic layers of Fe/Ge/Co stack [49]. At that time, a ten % increase in anti-parallel state resistance was observed at 4.2K temperature. The next big thing came after a long time in the mid-to-late 1980s. Room temperature TMR effects were discovered. Anisotropic magnetoresistive (AMR) layers were first used to construct AMR-MRAM to replace bulky and heavy plated-wire radiation-hard memories [50]. With the discovery of Giant Magnetoresistance (GMR) in 1988, this AMR-MRAM became obsolete. After that, electron spin became a significant basis of almost all electronic information storage. The main difference between TMR and GMR is that in TMR, an insulator is used to transmit current by tunneling, while GMR uses a metallic layer. Generally, TMR shows a more considerable impedance change between parallel and anti-parallel states than GMR. In 1996, Slonzewski at IBM gave a theoretical prediction that the magnetization of a free layer can be toggled using spinpolarized current rather than an external magnetic field. This effect is termed spin transfer torque (STT). This has been verified by experiments and proven to consume low power and simplify the memory cell design compared to field-based switching [9].

### 2.3 Basic Concepts of Spintronics

An electron can have two possible values of spin quantum number:  $+\frac{\hbar}{2}$  and  $-\frac{\hbar}{2}$  which are conventionally termed as up and down spin. Information is coded as one of these two possible spin orientations in a conventional spintronic circuit. In traditional electronic circuits, electrons carry their spins along the wire, but the difference between up and down spin cannot be distinguished. On the other hand, spintronic circuits usually have two current channels: one for spin up electrons and one for spin down electrons. This can be obtained by utilizing a magnetic material with appropriate magnetic moment orientations.

### 2.4 MTJ Working Principle

In a magnetic tunnel junction, a thin non-magnetic insulating material is sandwiched between two ferromagnetic (FM) layers. The phenomenon can be microscopically explained by band structure. In any FM layer, the number of spin-up (majority) and spin-down (minority) electrons are not the same giving rise to net spin polarization. Spin polarization, P is defined as:

$$P = \frac{\mathbf{n} \uparrow -\mathbf{n} \downarrow}{\mathbf{n} \uparrow +\mathbf{n} \downarrow} \tag{2.4}$$

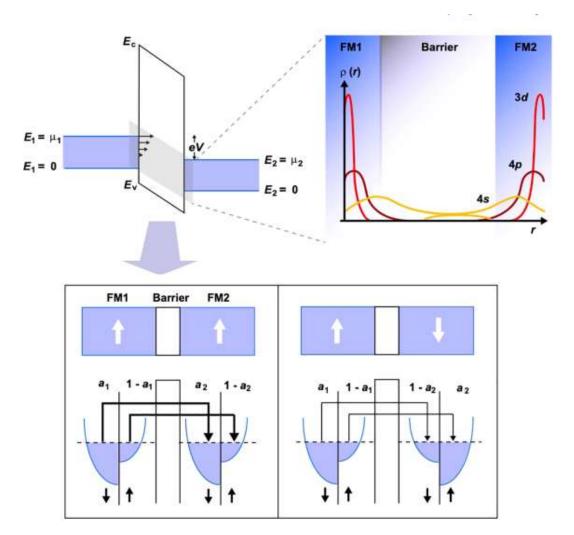

where  $n\uparrow$  and  $n\downarrow$  are the numbers of spin-up and spin-down electrons, respectively. In FM materials, the number of spin-up and spin-down electrons are different at the Fermi energy level. Consequently, the available density of states is also different for each [51]. The net magnetization depends on the difference,  $\delta n = n \uparrow -n \downarrow$  of two spin electrons. The more the difference, the stronger the magnetic moment. As the numbers differ in an FM layer, the material is magnetized due to the net magnetic moment generated by this non-equilibrium.  $\delta n$  near the Fermi level is important because these electrons act as carriers during transport. Electrons, while tunneling through the nonmagnetic insulating barrier, follow the spin-state conservation principle. For example, a spin-up electron will tunnel if there is an available spin-up state for it in the Fermi level of the other FM layer. Therefore, the tunneling probability and hence current will depend on the relative orientation of the two FM layers. If the two layers are magnetized in the same direction, i.e., parallel state (P), then all the spin-up electrons can easily find a corresponding state after tunneling through the barrier because the band structures, as a rule, of the two FM layers are almost the same. However, if the two FM layers have antiparallel (AP) magnetization, only partial electrons can act as carriers for the tunneling current. For this reason, conductance (resistance) remains high (low) in the P-state and low(high) in AP-state. In other words, the resistance of the trilayer stack depends on the orientation of the magnetization of the FM layers. This is illustrated in Fig. 2.1.

This idea is implemented in Magnetic Tunnel Junction (MTJ). Fig. 2.2 shows a typical structure of an MTJ stack. As previously stated, the MTJ block has three layers: a thin insulator (usually oxide barriers such as  $Al_xO_y$  and MgO) sandwiched by two ferromagnetic layers. The spin magnetization configuration of the two ferromagnetic layers is different. Spin magnetization of one layer is fixed, and the other one can switch between two spin magnetization states, i.e., either parallel or antiparallel to the fixed layers. This layer is called the free layer, storage layer, or switching layer. Parallel (P) and antiparallel (AP) are usually used to indicate the two possible states of the free layer. The characteristics of the MTJ block can be tuned by changing the state of this free layer. And this can be achieved by applying an external magnetic field having a value greater than a certain threshold with an opposite directions. When the two FM layers are in parallel states, current passes through the MTJ block undisturbed, indicating a low resistance state  $(R_P)$ . However, in the antiparallel state, the other layer will block the current generated by the first layer indicating a high resistance state  $R_{AP}$ . The TMR ratio is one of the most important parameters which determines the performance of an MTJ device. It is defined as:

$$TMR = \frac{R_{AP} - R_P}{R_P}$$

(2.5)

Figure 2.1: Spin-dependent tunneling of electrons in an MTJ while the magnetization directions in two FM layers are parallel (bottom left) and anti-parallel (bottom right) [52].

TMR is also defined in terms of polarization of the two FM layers as follows:

$$TMR = \frac{2P_1 P_2}{1 - P_1 P_2}$$

(2.6)

where  $P_1$  and  $P_2$  are the spin polarization of the two FM layers. They can be calculated from equation (2.4)(2.4). Increasing the value of TMR and the effect of defects on TMR has been a great research interest in recent years. The more the value of TMR, the more efficiently the two states of the MTJ block at any given voltage can be distinguished.

Figure 2.2: MTJ consists of three layers: two FM layer separated by an oxide barrier. The device resistance ( $R_P$  and  $R_{AP}$ ) depends on the corresponding state of the magnetization of the two FM layers, Parallel(P) or Anti-parallel (AP). The MTJ state can be switched by modulating the magnetic field [53].

### 2.5 MTJ Switching Mechanisms

The switching of the MTJ state can be realized by changing the spin magnetization orientation of the free layer. Several switching approaches have been proposed since the appearance of MTJ. For example:

- Field-induced magnetic switching (FIMS)

- Thermally assisted switching (TAS)

- Spin Transfer Torque (STT)

- Spin-Orbit Torque (SOT)

There are various versions of STT switching, like Spin Hall effect spin transfer torque, etc. However, in this thesis, we're discussing only Spin Transfer Torque MRAM (STT-MRAM), so we'll discuss the basic STT switching mechanism. In 1996 both Berger and Slonczewski independently predicted Spin Transfer Torque (STT) [9, 54]. STT switching mechanism is superior to other mechanisms like FIMS and TAS in case of better energy efficiency and scalability. STT switching method only requires a bidirectional current I higher than the threshold current to change the state of MTJ. In MTJs, two types of magnetic switching occur due to spin transfer torque: precessional and thermally activated switching [14] [55]. Precessional switching occurs on a nanosecond time scale, while thermally activated switching occurs at a much larger time scale [56]. The transition between these two switching regions lies between 1 and 10 ns which is depicted in Fig.2.3. It was observed that a spin-polarized current injected perpendicularly to the plane transfers spin angular momentum to a local magnetization of the FM layer. Thus a large torque known as 'Spin Transfer Torque' is generated. This torque efficiently facilitates the magnetic manipulations of FM layers

Figure 2.3: MTJ Switching Regimes [57].

in MTJ. If the current density is greater than the threshold value, the torque applied by the spin-polarized current will alter the magnetization of the free layer (FL) of MTJ [58].

In STT switching-based MTJ, the electrons injected into the pinned layer (PL) become spin polarized according to the spin of PL. Then these electrons tunnel through the oxide barrier. Then they transfer their angular momentum by applying a torque on the magnetization of FL as shown in Fig.2.4.To describe the switching of MTJ from an antiparallel configuration to a parallel configuration, a current is passed from the free layer to the fixed layer, which results in electrons flowing from the fixed layer to the free layer. The electrons in the fixed layer experience a torque, causing their spin magnetic moments to align with the magnetization of the fixed layer. Consequently, the current becomes spin-polarized along the direction of the fixed layer's magnetization. The magnetization of the fixed layer experiences an equal and opposite torque according to Newton's third law, but due to its rigidity, its magnetization is not significantly altered. The spin-polarized current then passes through the oxide barrier and enters the free layer. Next, the current's polarization encounters a torque that aligns it with the magnetization of the free layer. Concurrently, the magnetization of the free layer experiences an equal and opposite torque, which aligns it with the direction of the fixed layer. This process involves torque transfer between spins, and the torque experienced by the free layer due to the spin-polarized current is referred to as spin-transfer torque (STT).

To switch from a parallel configuration to an antiparallel configuration, the polarity of the voltage source must be reversed so that the now current flows from the fixed layer to the free layer, implying the electrons flow from the free layer to the fixed layer. When the electrons enter the free layer, their spins align with the magnetization of

Figure 2.4: Spin Transfer torque switching mechanism from anti-parallel (AP) to parallel (P) configuration [61].

the free layer. They then traverse the oxide barrier before entering the fixed layer. Due to the fixed nature of the magnetization in this layer, the torque exerted by the spin-polarized current on the layer has no appreciable effect on the magnetization of the layer. Instead, a torque equal and opposite to the torque required to polarize the current acts on the free layer, eventually flipping the magnetization of the free layer and resulting in the two layers becoming antiparallel to one another [59,60]. The basic idea of STT devices can be described in a single domain model, which assumes that the layers are uniformly magnetized [15] [62]. The dynamics of the magnetization of FL can be described by a Landau-Lifshitz-Gilbert(LLG) equation, including the spin transfer torque term [63] [64] as the following equation:

$$\frac{\partial \vec{m}}{\partial t} = -\gamma \mu_0 \vec{m} \times H_{eff} + \alpha \vec{m} \times \frac{\partial \vec{m}}{\partial t} - \beta J \vec{m} \times (\vec{m} \times \vec{m}_r)$$

(2.7)

The detail of this equation will be discussed in the modeling section. However, here the meaning of the equation will be discussed through a picture in Fig. 2.5. On the right-hand side of the equation, the first term represents the precession of the fieldinduced magnetization, and the second describes the intrinsic Gilbert damping torque, which reduces the precessional angle as a function of time and leads to the relaxation of the precession. The last term is the STT term with the opposite direction of the damping vector, which induces the switching of magnetization momentum. In such a current-induced magnetization switching of MTJ, the switching is determined by the competition between damping and STT term. For instance, if the STT term generated by a small current is relatively weaker than the damping term, then the magnetization direction remains unaltered. On the other hand, if the STT term generated by a higher current is stronger than the damping term, resulting in larger precessional angles and

Figure 2.5: Illustration of different terms in LLGS equation

eventual state switching. The two regimes are distinguished by the threshold current, which is commonly known as critical switching current  $I_{cO}$ .

Switching occurs on a much longer time scale when the current through the MTJ is less than the critical switching current [14]. In the thermally activated regime, the switching current is a function of pulse duration  $\tau$ :

$$I_C = I_{C0} \left[ 1 - \frac{\ln \left( \tau / \tau_0 \right)}{\Delta} \right]$$

(2.8)

where  $\Delta$  is the thermal stability of the MTJ,  $\tau_0$  is the natural time constant.

### 2.6 Modeling of MTJ

Small dimensionalities, in addition to the intrinsically stochastic switching properties of STT-MRAMs, make them highly susceptible to device-to-device and cycle-to-cycle variations. In order to study the origin of these variations, a physics model is required to capture the overall effects of the metal-insulator interface, defects, device dimension, and operating temperature. In this section, a physics-based model of MTJ considering the impact of interface and defects has been developed. The effect of current-induced joule heating, i.e., self-heating, is considered in chapter 4. First, the magnetization dynamics are captured by solving the Landau–Lifshitz–Gilbert-Slonczewski equation numerically, considering spin transfer torque (STT). Then the magnetization is used to compute the electrical property of the MTJ, such as resistance, current, etc., under the application of bias voltage.

#### 2.6.1 Magnetization Dynamics: LLGS Equation

As mentioned earlier, an MTJ consists of two ferromagnetic materials (free layer and reference layer) with an insulator in between them. The magnetization  $\vec{M}$  in a ferromagnet might change internally due to thermal excitation or external torque, but its magnitude is always equal to the saturation magnetization  $M_s$ . The precessional motion of magnetization  $\vec{M}$  of the free layer (FL) of an MTJ, in the presence of an external magnetic field  $\vec{H}_{\text{eff}}$ , can be very accurately modeled by the LLGS equation [9,38,65,66]. Initially, the equation was named LLG (Landau–Lifshitz–Gilbert) equation which predicts the dynamics of magnetization vector in the presence of torque. Later in 1996, John Slonczewski included an additional term to account for the spin transfer torque. The conventional way of writing the LLGS equation is as follows: