# HIGH PERFORMANCE NVRAM CIRCUIT DESIGN USING MEMRISTOR-MOS HYBRID ARCHITECTURE

A thesis submitted to

the Department of Electrical and Electronic Engineering

of

Bangladesh University of Engineering and Technology

in partial fulfillment of the requirements

for the degree of

### MASTER OF SCIENCE IN ELECTRICAL AND ELECTRONIC ENGINEERING

by,

Syed Shakib Sarwar Student ID: 0412062230

**Department of Electrical and Electronic Engineering**

### BANGLADESH UNIVERSITY OF ENGINEERING AND TECHNOLOGY

May 2014

# **DECLARATION**

| It is hereby declared that this thesis or any part of it has not been submitted elsewhere for the awar of any degree or diploma. |

|----------------------------------------------------------------------------------------------------------------------------------|

|                                                                                                                                  |

|                                                                                                                                  |

|                                                                                                                                  |

|                                                                                                                                  |

|                                                                                                                                  |

|                                                                                                                                  |

|                                                                                                                                  |

|                                                                                                                                  |

|                                                                                                                                  |

| (Syed Shakib Sarwar)                                                                                                             |

|                                                                                                                                  |

# APPROVAL CERTIFICATE

The thesis titled "High Performance NVRAM Circuit Design Using Memristor-MOS Hybrid Architecture" submitted by Syed Shakib Sarwar, Student ID: 0412062230, Session: April 2012 has been accepted as satisfactory in partial fulfillment of the requirement for the degree of MASTER OF SCIENCE IN ELECTRICAL AND ELECTRONIC ENGINEERING on May, 2014.

# **BOARD OF EXAMINERS**

| 1.                                                        | Chairman               |

|-----------------------------------------------------------|------------------------|

| Dr. A.B.M. Harun-ur Rashid                                | (Supervisor)           |

| Professor,                                                |                        |

| Department of EEE, BUET,                                  |                        |

| Dhaka-1000, Bangladesh                                    |                        |

|                                                           |                        |

|                                                           |                        |

| 2.                                                        | Manahan                |

|                                                           | Member<br>(Ex-Officio) |

| Dr. Pran Kanai Saha                                       | (Ex-Officio)           |

| Professor and Head,                                       |                        |

| Department of EEE, BUET,                                  |                        |

| Dhaka-1000, Bangladesh                                    |                        |

|                                                           |                        |

| 3.                                                        |                        |

| <i>3.</i>                                                 | Member                 |

| D 1417. D1 W                                              | 1410111001             |

| Dr. Md. Ziaur Rahman Khan                                 |                        |

| Professor, Department of EEE, BUET,                       |                        |

| Dhaka-1000, Bangladesh                                    |                        |

| Diaka 1000, Bangiadesii                                   |                        |

|                                                           |                        |

| 4.                                                        |                        |

|                                                           | Member                 |

| Dr. Zahid Hasan Mahmood                                   |                        |

| Professor, Department of Applied Physics, Electronics and |                        |

| Communication Engineering,                                |                        |

| University of Dhaka                                       |                        |

# **CONTENTS**

| TITL               | $oldsymbol{E}$                                    | Page     |

|--------------------|---------------------------------------------------|----------|

|                    |                                                   | no:      |

| Declaration        |                                                   | 11<br>   |

| Approval Certifica | te                                                | 111<br>· |

| Table of Contents  |                                                   | 1V       |

| List of Figures    |                                                   | V1<br>   |

| List of Tables     |                                                   | vii<br>  |

| Acknowledgement    |                                                   | VIII     |

| Abstract           |                                                   | ix       |

| Chapter 01         | Introduction                                      | 1        |

| 1.1 Memr           | istor                                             | 1        |

| 1.2 SRAN           |                                                   | 3        |

|                    | ation of our work                                 | 4        |

|                    | Outline                                           | 6        |

| Chapter 02         | Memristor Basics                                  | 7        |

| 2.1 A Sing         | gle Memristor                                     | 7        |

| •                  | cal Memristor: Model of Non-Linear Dopant Drift   | 12       |

|                    | E Model of Memristor with Non-Linear Dopant Drift | 14       |

| Chapter 03         | SRAM Basics                                       | 18       |

| 3.1 SRAN           | 1                                                 | 18       |

| 3.2 Conve          | entional SRAM Types                               | 20       |

| 3.2.1              | 4T-SRAM                                           | 20       |

| 3.2.2              | 6T-SRAM                                           | 21       |

| 3.2.3              | 4T2M-SRAM                                         | 23       |

| 3.2.4              | 3T-2M SRAM                                        | 24       |

| Chapter 04         | Memristor Based SRAM Cell                         | 25       |

| 4.1 Memr           | istor as A Memory Component                       | 25       |

| 4.2.1              | Two-Transistor Two-Memristor Memory Cell          | 28       |

| 4.2.2              | Simulation of 2×2 Array Of Memory                 | 32       |

| 4.3.1              | Residual Voltage Effect                           | 34       |

|        | 4.3.2   | Contamination of Stored Data Due to Leakage                            | 36  |  |

|--------|---------|------------------------------------------------------------------------|-----|--|

|        | 4.3.3   | Change of Stored Data Due to Consecutive Read                          | 37  |  |

|        |         | Operations                                                             |     |  |

| 4.4    | Pro     | posed 2-T 2-M SRAM                                                     | 38  |  |

|        | 4.4.1   | Leaf Cell Connected with Peripheral Circuit with                       | 38  |  |

|        |         | Complete Source Isolation                                              |     |  |

|        | 4.4.2   | Array Structure                                                        | 39  |  |

| 4.5    | Sim     | nulation and Analysis                                                  | 40  |  |

|        | 4.5.1   | Functional Verification of 16×16 Array Structure                       | 41  |  |

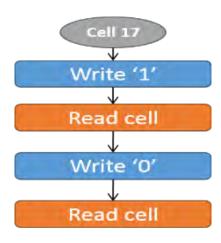

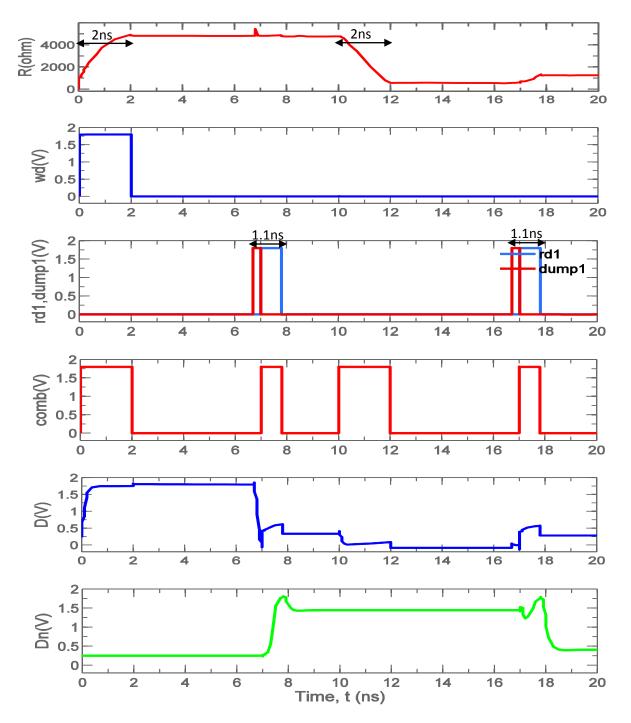

|        | 4.5.1.1 | Write and Read Different Cells and Observe The Effect on a Single Cell | 42  |  |

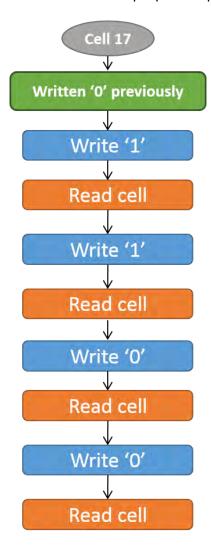

|        | 4.5.1.2 | Write and Read Different Cells and Check the Output Values             | 44  |  |

|        | 4.5.2   | SRAM Array with Sense Amplifier                                        | 45  |  |

|        | 4.5.2.1 | Sense Amplifier                                                        | 45  |  |

|        | 4.5.2.2 | Array with Sense Amplifier                                             | 46  |  |

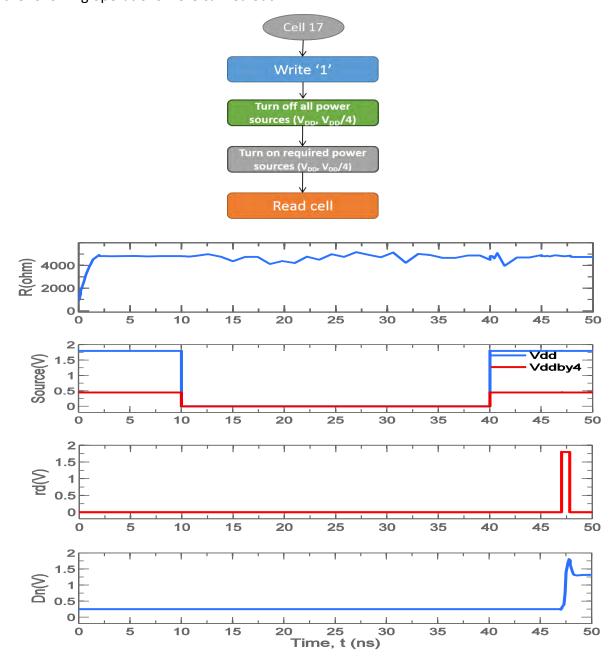

|        | 4.5.3   | Non-Volatility                                                         | 49  |  |

| Chapte | er 05   | ANALYSIS AND COMPARISON                                                | 50  |  |

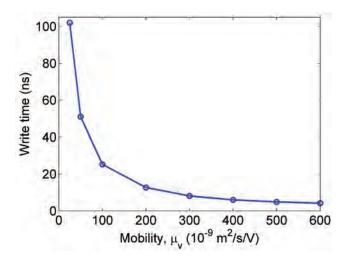

| 5.1    |         | ning Analysis                                                          | 50  |  |

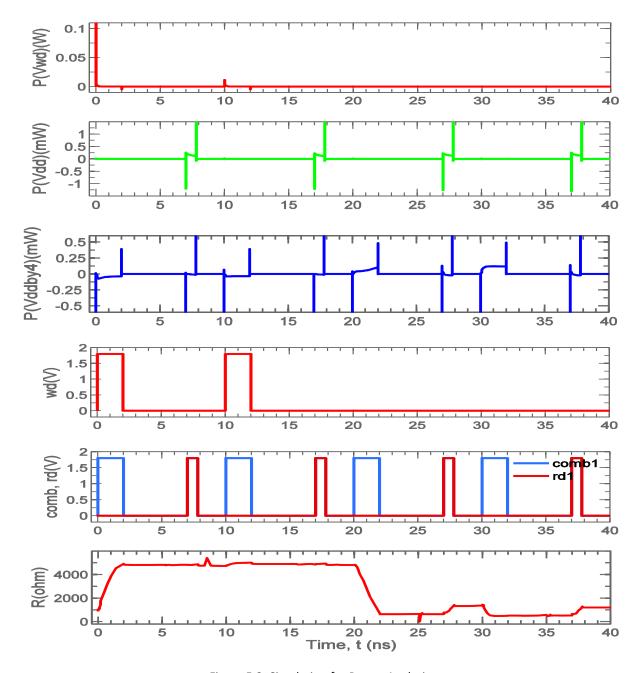

| 5.2    |         | ver Analysis                                                           | 52  |  |

| 5.3    | Lay     | •                                                                      | 55  |  |

| 3.3    | Lay     | out -                                                                  | 33  |  |

| Chapt  | er 06   | CONCLUSION AND FUTURE WORK                                             | 57  |  |

| 6.1    | Cor     | nclusion                                                               | 57  |  |

| 6.2    |         | ure Work                                                               | 58  |  |

|        |         |                                                                        | 60  |  |

| Chapt  | er 07   | REFERENCES                                                             | 60  |  |

|        |         |                                                                        |     |  |

| Appen  | dix A:  | Simulation Codes                                                       | 63  |  |

| Appen  | dix B:  | Memristor Modeling in MATLAB                                           | 111 |  |

| Appen  | dix C:  | Exporting Data from PSPICE to MATLAB                                   | 113 |  |

| Appen  |         | SPICE Convergence Problem Elimination Techniques                       | 114 |  |

| Appen  | dix E:  | Related publication                                                    | 116 |  |

# List of Figures

| Figure no   |                                                                                                                                                                                                              | Page |

|-------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|

| Figure 1.1  | Relations between four variables of basic electrical circuit theory                                                                                                                                          | 3    |

| Figure 2.1  | A single memristor with the definition of R <sub>ON</sub> and R <sub>OFF</sub>                                                                                                                               | 7    |

| Figure 2.2  | Theoretical i-v characteristics of a memristor with applied voltage                                                                                                                                          | 11   |

| Figure 2.3  | Theoretical i-v curves for a memristor with (realistic) dopant drift modeled by window functions                                                                                                             | 13   |

| Figure 2.4  | Block diagram of the memristor model                                                                                                                                                                         | 15   |

| Figure 2.5  | Structure of the SPICE model                                                                                                                                                                                 | 16   |

| Figure 2.6  | Memristor with the parameters $R_{ON}=100 \Omega$ , $p=10$ , driven by a voltage                                                                                                                             | 17   |

| Figure 3.1  | Conventional SRAM cell                                                                                                                                                                                       | 19   |

| Figure 3.2  | 4T SRAM                                                                                                                                                                                                      | 21   |

| Figure 3.3  | 6T SRAM                                                                                                                                                                                                      | 22   |

| Figure 3.4  | Structure of Non-volatile 4T SRAM cell with memristors                                                                                                                                                       | 23   |

| Figure 3.5  | 3T-2M SRAM                                                                                                                                                                                                   | 24   |

| Figure 4.1  | A pulsed source applied across a memristor                                                                                                                                                                   | 26   |

| Figure 4.2  | V vs Time and Rmem vs Time plot                                                                                                                                                                              | 26   |

| Figure 4.3  | V vs Time and Rmem vs Time plot with new memristor parameters                                                                                                                                                | 27   |

| Figure 4.4  | The 2-Memristor 2-Transistor SRAM cell                                                                                                                                                                       | 28   |

| Figure 4.5  | (a) circuit when rd=0, comb=1 (b) circuit when rd=1, comb=1                                                                                                                                                  | 28   |

| Figure 4.6  | A CMOS pass gate is introduced for simulation                                                                                                                                                                | 29   |

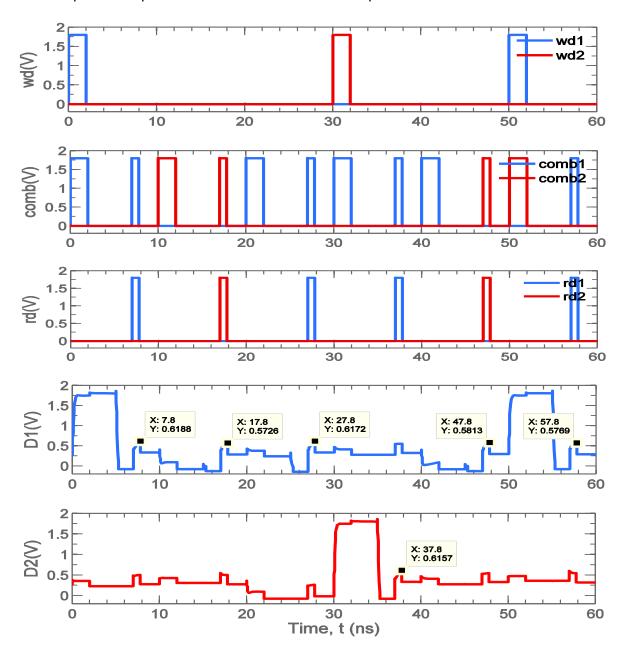

| Figure 4.7  | After writing '1' (WD=1, COMB=1,RD=0), VD was read as 0.619V (COMB =1,RD=1) and After writing '0' (WD=0, COMB =1,RD=0), VD was read as 0.5727V (COMB =1,RD=1)                                                | 31   |

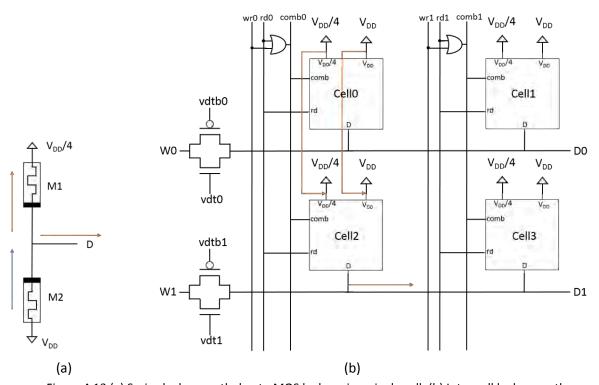

| Figure 4.8  | (a) basic building block of a single cell (b) 2x2 array of memory                                                                                                                                            | 32   |

| Figure 4.9  | Plot of the read-write cycles in 2x2 array                                                                                                                                                                   | 33   |

| Figure 4.10 | '0' written on cell0 and read. Then '1' was written on cell1 and cell0 was read. This time cell0 gives 0.9478 V much larger than '0' should give due to addition of the residual voltage.                    | 34   |

| Figure 4.11 | A NMOS controlled by Vdump signal is used to create a path to the ground for discharging the wordlines.                                                                                                      | 35   |

| Figure 4.12 | '0' written on cell0 and after using Vdump for 0.3ns cell0 is read. Then '1' was written on cell1 and after using Vdump for 0.3ns cell0 was read. This time cell0 gives 0.5588 V which is equivalent to '0'. | 35   |

| Figure 4.13 | (a) Series leakage path due to MOS leakage in a single cell. (b) Intra cell leakage path.                                                                                                                    | 36   |

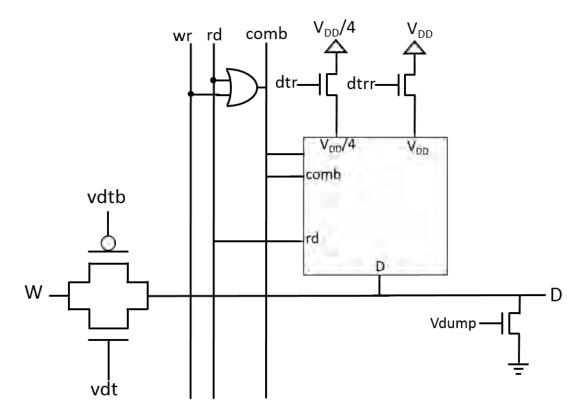

| Figure 4.14 | Leaf cell connected with peripheral circuit containing complete source isolation option                                                                                                                      | 37   |

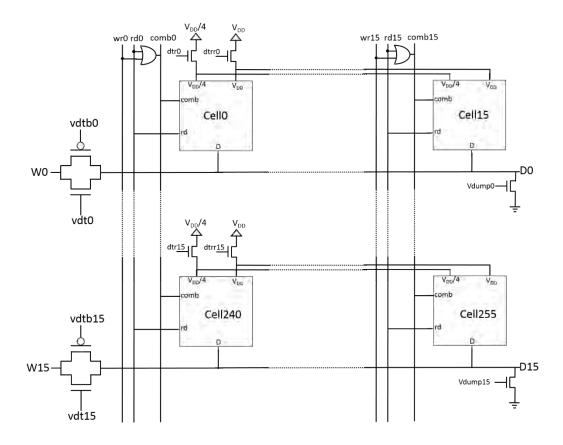

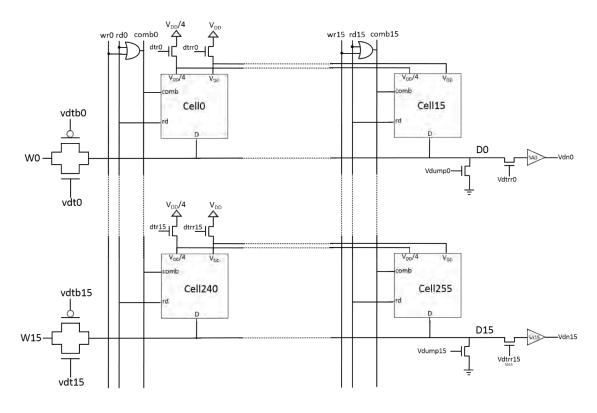

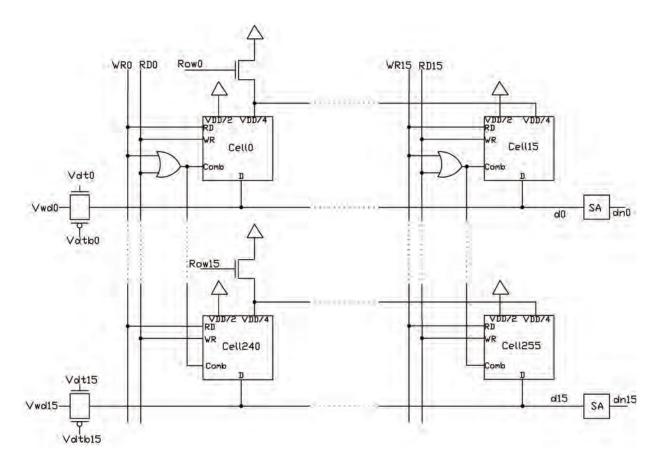

| Figure 4.15 | 16×16 Array Structure of the proposed memristor based SRAM                                                                                                                                                   | 39   |

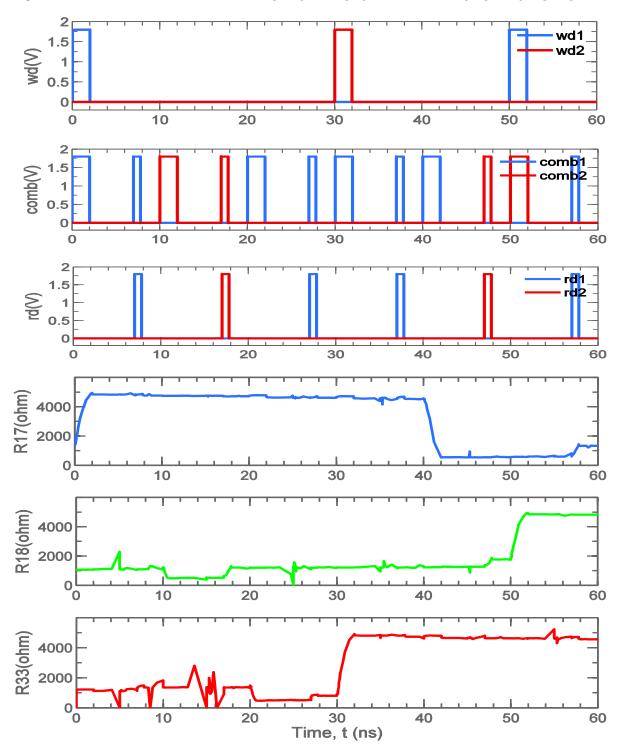

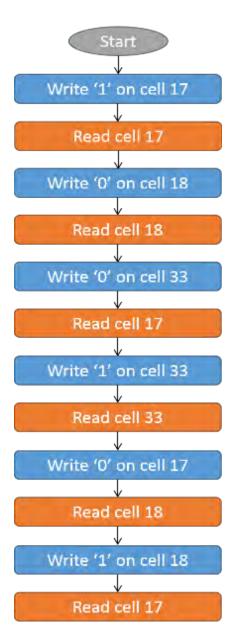

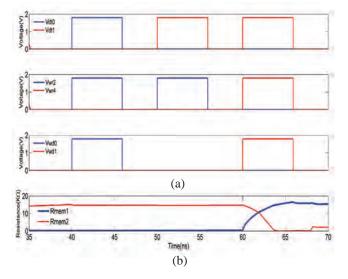

| Write and read different cells and observe the effect on a single cell | 42                                                                                                                                                                                                                                                                                                                                                                                                                  |

|------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

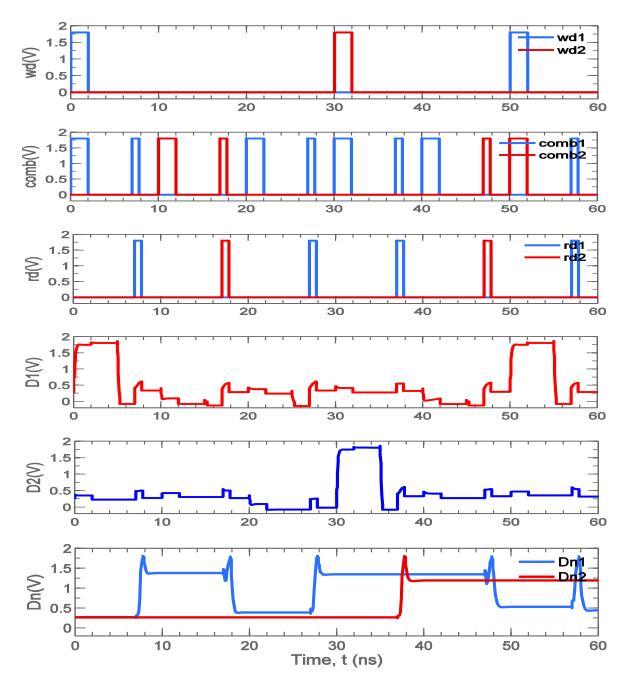

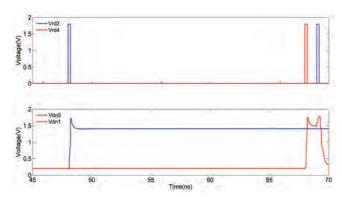

| write and read different cells and check the output values             | 44                                                                                                                                                                                                                                                                                                                                                                                                                  |

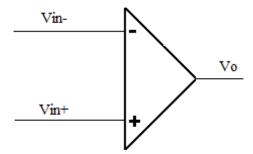

| A simple voltage comparator                                            | 45                                                                                                                                                                                                                                                                                                                                                                                                                  |

| Comparator design specification                                        | 45                                                                                                                                                                                                                                                                                                                                                                                                                  |

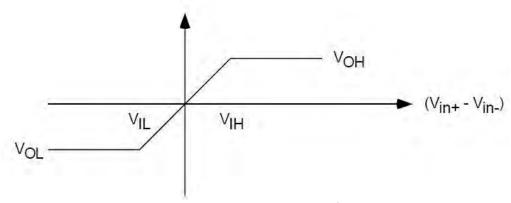

| CMOS comparator with PMOS input drivers.                               | 46                                                                                                                                                                                                                                                                                                                                                                                                                  |

| 16×16 Array Structure of the proposed memristor based SRAM with        | 46                                                                                                                                                                                                                                                                                                                                                                                                                  |

| sense amplifier                                                        |                                                                                                                                                                                                                                                                                                                                                                                                                     |

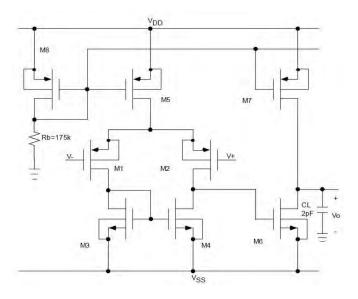

| Functionality test of sense amplifier in the SRAM array circuit        | 48                                                                                                                                                                                                                                                                                                                                                                                                                  |

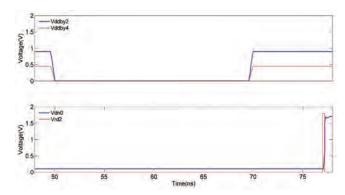

| Evidence of non-volatility of the Memristor SRAM cell                  | 49                                                                                                                                                                                                                                                                                                                                                                                                                  |

| Timing Analysis                                                        | 51                                                                                                                                                                                                                                                                                                                                                                                                                  |

| Simulation for Power Analysis                                          | 53                                                                                                                                                                                                                                                                                                                                                                                                                  |

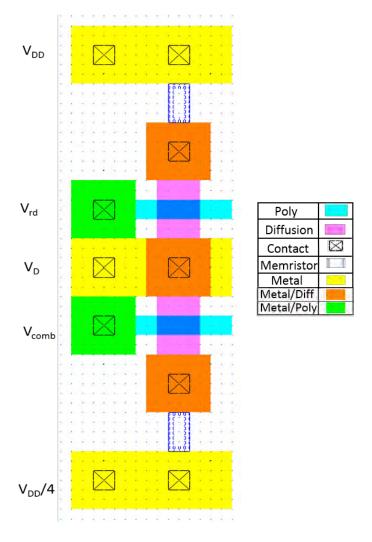

| Layout of the SRAM cell                                                | 55                                                                                                                                                                                                                                                                                                                                                                                                                  |

|                                                                        | write and read different cells and check the output values A simple voltage comparator Comparator design specification CMOS comparator with PMOS input drivers. 16×16 Array Structure of the proposed memristor based SRAM with sense amplifier Functionality test of sense amplifier in the SRAM array circuit Evidence of non-volatility of the Memristor SRAM cell Timing Analysis Simulation for Power Analysis |

# List of Tables

| Table no. |                                                  | Page no. |

|-----------|--------------------------------------------------|----------|

| Table 5.1 | Write and spread cycle time comparison           | 51       |

| Table 5.2 | Write and read cycle average energy estimation   | 54       |

| Table 5.3 | Write-read cycle average power comparison        | 54       |

| Table 5.4 | Write-read cycle average energy comparison       | 54       |

| Table 5.5 | Area estimation and comparison for 180nm process | 56       |

| Table 5.6 | Area estimation and comparison for 45nm process  | 56       |

|           |                                                  |          |

#### **ACKNOWLEDGEMENT**

First of all, I would like to thank the Almighty Allah for bringing me to the position where I am at this moment.

A huge amount of gratitude goes to my thesis supervisor Dr. A.B.M Harun-ur Rashid for his never ending support and guidance. His vast knowledge and expertise in the field of research always inspired me when I needed to lift my spirit. He always encouraged me to look for new technologies and scopes. He was inspirational in making me come up with the idea of my thesis work on memristor based memory element. I consider myself very lucky to have a thesis supervisor like Dr. A.B.M Harun-Ur-Rashid. And I earnestly hope to maintain an active relation with him for our future research works in the days to come.

Then, I would like to express my gratitude to my teachers and classmates who helped me along the way last one year. I would also like to thank my parents for their love and support. They always provided me with proper guidance and also gave me the freedom to choose what interested me the most.

Finally, I have tried my best to represent this thesis dissertation as appropriate as possible. I am feeling myself fortunate to finish the thesis on such an interesting topic which is really a great experience.

#### **ABSTRACT**

Scaling conventional SRAM technologies with respect to number of transistors is a big challenge and volatile memory nature of this technology is one of the biggest deficiencies. A new Memristor-MOS hybrid architecture based RAM structure has been proposed in this thesis which consumes less power and achieves nonvolatile operation (NVRAM) with less number of transistors. The thesis contains the operating procedure and the simulated results of proposed two transistors and two memristors NVRAM using TSMC 180nm CMOS technology simulated in ORCAD PSPICE 9.2. Memristors cover very little area and with only two transistors as opposed to six transistors of conventional SRAMs, the area is substantially reduced by 20.5 times. The proposed NVRAM operated with energy per cycle which is ~40 times smaller than conventional SRAMs. Though the write cycle time is higher but is still comparable, and the read cycle time is slightly lower than the conventional 6T SRAM cell. Again memristors give the circuit non-volatility which is a vital characteristic for any memory circuit. With these advantages our proposed cell can prove to have a very promising future in the field of computer memory.

# **INTRODUCTION**

Greater need for larger cache memories is growing very fast. Till date SRAM satisfies this need almost exclusively. Conventional SRAM technologies have reached a certain point where it is impossible to decrease the area of the memory in terms of number of transistors. SRAMS are also volatile in nature, they lose what was stored in them if the power is turned off. This thesis work focuses on studying a novel circuit structure for Memristor-MOS hybrid architecture NVRAM to enhance the read/write speed, reduce power consumption and minimize area.

#### 1.1 MEMRISTOR

The properties of basic electrical circuits, constructed from three ideal elements, a resistor, a capacitor, an inductor, and an ideal voltage source v(t), are integral part of physics and engineering courses. These circuits show a wide variety of phenomena such as the exponential charging and discharging of a resistor-capacitor (RC) circuit with time constant  $\tau_{RC}$  = RC, the exponential rise and decay of the current in a resistor-inductor (RL) circuit with time constant  $\tau_{RL} = L/R$ , the non-dissipative oscillations in an inductor-capacitor (LC) circuit with frequency  $\omega_{LC} = \frac{1}{\sqrt{LC}}$ , as well as resonant oscillations in a resistor-capacitor- inductor (RCL) circuit induced by an alternating-current (AC) voltage source with frequency  $\omega \sim \omega_{LC}$  [1,2,3,4] The behavior of these ideal circuits is determined by Kirchoff's current law and Kirchoff's voltage law. As Kirchoff's voltage law follows from Maxwell's second equation only when the time-dependence of the magnetic field created by the current in the circuit is ignored,  $\oint E \cdot dl = 0$  where the line integral of the electric field E is taken over any closed loop in the circuit [5] The study of elementary circuits with ideal elements provides us with a recipe to understand real-world circuits where every capacitor has a finite resistance, every battery has an internal resistance, and every resistor has an inductive component. We assume that the real-world circuits can be modeled using only the three ideal elements and an ideal

voltage source. An ideal capacitor is defined by the single-valued relationship between the charge q(t) and the voltage v(t) via dq = Cdv. Similarly, an ideal resistor is defined by a single valued relationship between the current i(t) and the voltage v(t) via dv = Rdi, and an ideal inductor is defined by a single-valued relationship between the magnetic flux  $\phi(t)$  and the current i(t) via  $d\varphi = Ldi$ . These three definitions provide three relations between the four fundamental constituents of the circuit theory, namely the charge q, current i, voltage v, and magnetic flux  $\phi$  (See Figure 1). The definition of current, i = dq/dt, and the Lenz's law, v = $+d\varphi/dt$ , give two more relations between the four constituents. (We define the flux such that the sign in the Lenz's law is positive). These five relations, shown in Fig. 1, raise a natural question: Why is an element relating the charge q(t) and magnetic flux  $\phi(t)$  missing? Based on this symmetry argument, in 1971 Leon Chua postulated that a new ideal element defined by the single-valued relationship  $d\varphi = Mdq$  must exist. He called this element memristor M, a short for memory-resistor [6]. This ground-breaking hypothesis meant that the trio of ideal circuit elements (R,C,L) were not sufficient to model a basic real-world circuit (that may have a memristive component as well). In 1976, Leon Chua and Sung Kang extended the analysis further to memristive systems [7,8]. These seminal articles studied the properties of a memristor, the fourth ideal circuit element, and showed that diverse systems such as thermistors, Josephson junctions, and ionic transport in neurons, are special cases of memristive systems [6,7,8]. Despite the simplicity and the soundness of the symmetry argument that predicts the existence of the fourth ideal element, experimental realization of a quasi-ideal memristor-defined by the single-valued relationship  $d\varphi = Mdq$  - remained elusive [9,10]. Early in 2009, Strukov and co-workers [11,12] created, using a nano-scale thinfilm device, the first realization of a memristor. They presented an elegant physical model in which the memristor is equivalent to a time-dependent resistor whose value at time t is linearly proportional to the amount of charge q that has passed through it before. This equivalence follows from the memristor's definition and Lenz's law,  $d\varphi = Mdq \Leftrightarrow v = M(q)i$ . It also implies that the memristor value - memristance - is measured in the same units as the resistance.

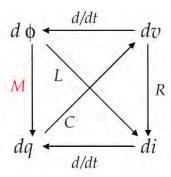

Figure 1.1: Relations between four variables of basic electrical circuit theory: the charge q, current i, voltage v and the magnetic flux  $\phi$ . Three well-known ideal circuit elements R, C and L are associated with pairs (dv, di), (dq, dv) and  $(d\phi, di)$  respectively. The top (bottom) horizontal pair is related by Lenz's law (definition). This leaves the pair  $(d\phi, dq)$  unrelated. Leon Chua postulated that, due to symmetry, a fourth ideal element (memristor) that relates this pair,  $d\phi = Mdq$ , must exist.

#### **1.2 SRAM**

One of the main features of computers these days is their capability to store data. Computer memory or storage refers to the physical device that stores data or programs on a temporary or permanent basis. Typically computer memory refers to RAM (Random Access Memory) where data is accessed with minimal amount of delay. RAMs can be of two types. Firstly DRAM (Dynamic Random Access Memory) where the data is stored using a transistor and a capacitance. Since capacitors leak charge, there is a need for refreshing the data periodically. Secondly there is SRAM (Static Random Access Memory), where data to be stored is latched in using cross-coupled inverters. As no capacitance is used to store data in SRAM, there is no necessity of refreshing. And it is for this reason mainly that SRAM is preferred over DRAM in many operations even though SRAM has a more complex structure and is more costly. Another advantage of SRAM over DRAM is its speed. SRAM is nearly five times faster than DRAM as it does not need any delays between accesses. But SRAMs are much more costly than DRAM due to their complex structure. So till now, SRAMs are only used in cache memory where high speed of operation is needed and a relatively small sized memory will suffice. Although SRAMs are free from the need of refreshing periodically, they are still volatile, as in they lose the stored data if or when the power supply is turned off. Conventional SRAM cells use four to six transistors. So space is also a concern for a large array of SRAM cells.

Scientists and researchers are striving for the invention of a static memory system that will be as fast as SRAM, but will be non-volatile and require less space. If these features can be combined, then it will be possible to attain a large static memory with small area which will hold data even without the power supply. So that memory will be perfectly suitable to be used as cache memory as well as flash memory for storing large amount of data. Our target was to design a new type of memory containing these advantages.

#### 1.3 MOTIVATION OF OUR WORK

Both DRAM and SRAM must have continual power supply to hold their data. As soon as they lose power, their data are gone. One alternative approach would be to use flash memory. But it has a limited number of read-write cycles it could sustain. This characteristic clearly is not suited for random access memory (RAM) because a huge number of read-write cycles occur on them regularly. Besides, flash memory consumes a great amount of power whereas DRAM and SRAM are low power devices. Many research works have already been done on nonvolatile random access memory or NVRAM. Most notable NVRAMs are Ferroelectric RAM (FeRAM), Magnetoresistive RAM (MRAM), Phase-change RAM (PRAM). Some of them broke into the market but neither of them was able to last long. There was always a concern of dimension, speed and power consumption which left conventional volatile DRAM and SRAM technology a better choice. There are also some differences between DRAM and SRAM. DRAM requires the data to be refreshed periodically in order to retain the data. SRAM does not need to be refreshed as the transistors inside would continue to hold the data as long as the power supply is not cut off. This behavior leads to a few advantages, such as much faster speed that data can be written and read. The additional circuitry and timing needed to introduce the refresh creates some complications that make DRAM memory slower and less desirable than SRAM. One complication is the much higher power used by DRAM memory. This difference is very significant in battery powered devices. SRAM modules are also much simpler compared to DRAM, which makes it easier for most people to create an interface to access the memory. This makes it easier to work with for hobbyists and even for prototyping.

Structurally, SRAM needs a lot more transistors in order to store a certain amount of memory. A DRAM module only needs a transistor and a capacitor for every bit of data where SRAM needs 6 transistors. Because the number of transistors in a memory module determines its capacity, a DRAM module can have almost 6 times more capacity with a similar transistor count to an SRAM module. This ultimately boils down to price, which is what most buyers are really concerned with. Because of its lower price, DRAM has become the mainstream in computer main memory despite being slower and more power hungry compared to SRAM. SRAM memory is still used in a lot of devices where speed is more crucial than capacity. The most prominent use of SRAM is in the cache memory of processors where speed is very essential, and the low power consumption translates to less heat that needs to be dissipated. So to fight against DRAM to be the computer main memory, SRAM needs to be smaller in area i.e. reduction in the number of transistors in a single cell. Recent emergence of memristor and their capability of storing non-volatile memory have given a boost to the researchers. In some memristor symposiums, it has been hypothesized that memristor in a crossbar structure can hold enormous amount of data in a small area. This devices is very small, could be less than 10nm of length. Some works on crossbar structure have already been done [13,14]. It can also be implemented with conventional CMOS technology which is called Memristor-CMOS Hybrid circuits. In 2010, Kamran Eshraghian et. al. successfully implemented memristor-mos content addressable memory [15]. So, it might be possible to design SRAM cells with memristor as memory element and MOS which might need fewer transistors than conventional SRAM cell and also possess the non-volatility characteristic.

#### 1.4 THESIS ORGANIZATION

This thesis proposes a SRAM structure for retaining the feature of needlessness of periodic refreshing and combining with it the features of less area and non-volatility. The thesis paper has been organized in the following manner:

Chapter 2: Gives an idea of the memristor basics, mentions the model of non-linear dopant drift in practical memristors, shows the SPICE modeling of a memristor,

Chapter 3: Introduces the SRAM, different structures of conventional SRAM systems and Memristor based SRAM systems.

Chapter 4: First introduces initially proposed SRAM cell with two transistors and two memristors, then shows the residual voltage problem and leakage problem in array structure, and describes how the problems were overcome in final proposed structure. Then introduces sense amplifier, shows the non-volatility characteristics of the memory circuit, and verifies and explains the final array structure with simulation results.

Chapter 5: Gives the timing analysis, power analysis, area estimation from layout of leaf cell and finally compares the obtained results with conventional SRAM cell characteristics.

Chapter 6: Summarizes the outcome of our proposed non-volatile SRAM cell and discusses the future improvements or works to be done on this circuit.

#### **MEMRISTOR BASICS**

Memristors have been studied intensively among many researchers because of their possibilities, especially as a strong candidate for future memories. Non-volatile property and high packing density in a crossbar array particularly excites the researchers.

#### 2.1 A SINGLE MEMRISTOR

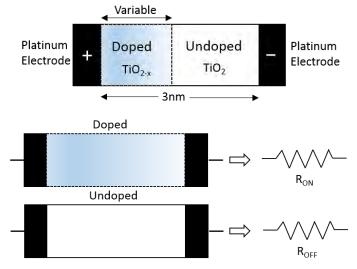

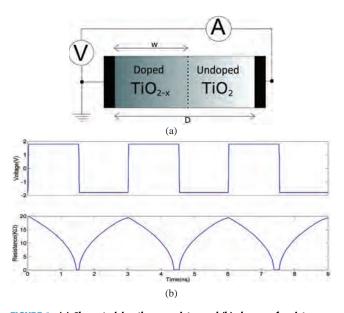

We start this chapter with the elegant model of a memristor presented in Ref 11 and 12. It consisted of a thin film (5 nm thick) with one layer of insulating  $TiO_2$  and one layer of oxygen-poor  $TiO_{2-x}$ , each sandwiched between platinum contacts. The oxygen vacancies in the second layer behave as charge +2 mobile dopants. These dopants create a doped  $TiO_2$  region, whose resistance is significantly lower than the resistance of the undoped region. The boundary between the doped and undoped regions, and therefore the effective resistance of the thin film, depends on the position of these dopants. It, in turn, is determined by their mobility  $\mu_V$  (~10<sup>-10</sup> cm²/V.s) and the electric field across the doped region [2] Figure 2.1 shows a schematic of a memristor of size D (D~10 nm) modeled as two resistors in series, the doped region with size w and the undoped region with size (D–w).

Figure 2.1: A single memristor with the definition of Ron and Roff

The effective resistance of such a device is

$$M(w) = R_{ON} \frac{w}{D} + R_{OFF} \left( 1 - \frac{w}{D} \right)$$

(2.1)

where  $R_{ON}$  (~1k) is the resistance of the memristor if it is completely doped, and  $R_{OFF}$  is its resistance if it is undoped. Although Eq.(2.1) is valid for arbitrary values of  $R_{ON}$  and  $R_{OFF}$ , experimentally, the resistance of the doped TiO<sub>2</sub> film is significantly smaller than the undoped film,  $R_{OFF}/R_{ON} \sim 10^2 \gg 1$  and therefore  $\Delta R = (R_{OFF} - R_{ON}) \approx R_{OFF}$ . In the presence of a voltage v(t) the current in the memristor is determined by Kirchoff's voltage law v(t) = M(w)i(t). The memristive behavior of this system is reflected in the time-dependence of size of the doped region w(t). In the simplest model - the linear-drift model - the boundary between the doped and the undoped regions drifts at a constant speed  $v_D$  given by

$$v_D = \frac{dw}{dt} = \eta \frac{\mu_D R_{ON}}{D} i(t)$$

(2.2)

where we have used the fact that a current i(t) corresponds to a uniform electric field  $R_{ON}i(t)/D$  across the doped region. Since the (oxygen vacancy) dopant drift can either expand or contract the doped region, we characterize the "polarity" of a memristor by  $\eta = \pm 1$ , where  $\eta = +1$  corresponds to the expansion of the doped region. We note that "switching the memristor polarity" means reversing the battery terminals, or the  $\pm$  plates of a capacitor (in an MC circuit) or reversing the direction of the initial current (in an ML circuit). Equations (2.1), (2.2) are used to determine the i-v characteristics of a memristor. Integration of Eq.(2.2) gives

$$w(t) = w_0 + \eta \frac{\mu_D R_{ON}}{D} q(t) = w_0 + \eta \frac{D}{Q_0} q(t)$$

(2.3)

where  $w_0$  is the initial size of the doped region. Thus, the width of the doped region w(t) changes linearly with the amount of charge that has passed through it  $Q_0 = D^2/\mu_D R_{ON}$  is the charge that is required to pass through the memristor for the dopant boundary to move through distance D (typical parameters [11,12] imply  $Q_0 \sim 10^{-2}$  C). It provides the natural scale for charge in a memristive circuit. Using this result in Eq.(2.1) gives

$$M(q) = R_0 + \eta \frac{\Delta Rq}{Q_0} \tag{2.4}$$

where,  $R_0 = R_{ON}(w_0/D) + R_{OFF}(1-w_0/D)$  is the effective resistance (memristance) at time t=0. Eq.(2.4) shows explicitly that the memristance M(q) depends purely on the charge q that has passed through it. Combined with v(t) = M(q)i(t), Eq.(2.4) implies that the model presented here is an ideal memristor. (We recall that v = M(q)i is equivalent to  $d\phi = Mdq$ ). The factor of the q-dependent term is proportional to  $1/D^2$  and becomes increasingly important when D is small. In addition, for a given D, the memristive effects become important only when  $\Delta R \gg R0$ . Now that we have discussed the memristor model from Ref. 2.1, in the following paragraphs we obtain analytical results for its i-v characteristics. For an ideal circuit with a single memristor and a voltage supply, Kirchoff's voltage law implies

$$(R_0 + \eta \frac{\Delta Rq(t)}{Q_0}) \frac{dq}{dt} = \frac{d}{dt} \left( R_0 q + \eta \frac{\Delta Rq^2}{2Q_0} \right) = v(t)$$

(2.5)

The solution of this equation, subject to the boundary condition q(0) = 0 is,

$$q(t) = \frac{Q_0 R_0}{\Delta R} \left[ 1 - \sqrt{1 - \eta \frac{2\Delta R}{Q_0 R_0^2}} \phi(t) \right]$$

(2.6)

$$q(t) = \frac{v(t)}{R_0} \frac{1}{\sqrt{1 - 2\eta \Delta R \phi(t)/Q_0 R_0^2}} = \frac{v(t)}{M(q(t))}$$

(2.7)

where  $\phi(t) = \int_0^t d\tau v(\tau)$  is the magnetic flux associated with the voltage v(t). Equations (2.6)-(2.7) provide analytical results for i-v characteristics of an ideal memristor circuit. Eq.(2.6) shows that the charge is an invertible function of the magnetic flux [6,7] consistent with the defining equation  $d\varphi = M(q)dq$ . Eq.(2.7) shows that a memristor does not introduce a phase-shift between the current and the voltage, i = 0 if and only if v = 0. Therefore, unlike an ideal capacitor or an inductor, is a purely dissipative element [16]. For an AC voltage v(t) = v<sub>0</sub> sin( $\omega$ t),

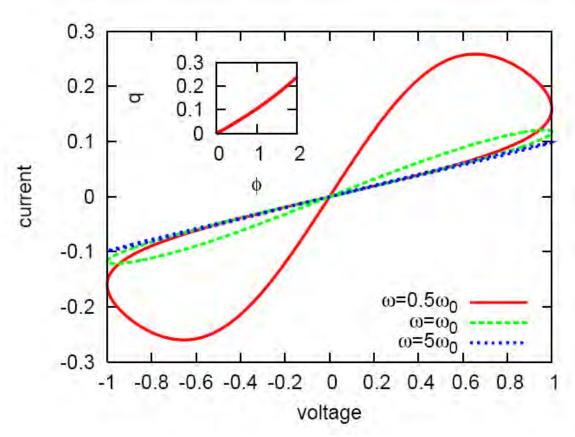

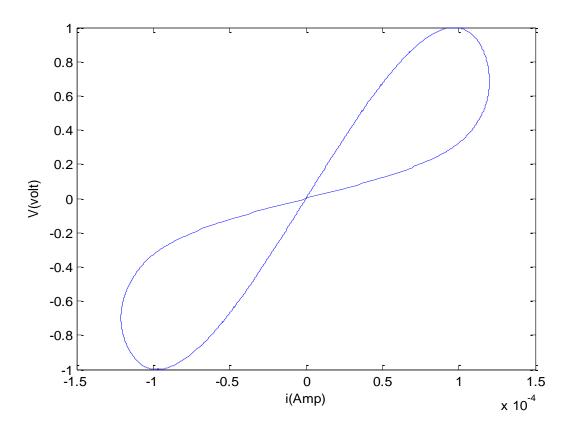

the magnetic flux is  $\phi(t) = v_0[1 - \cos(\omega t)]/\omega$ . Note that although  $v(\pi/\omega - t) = v(t)$ ,  $\phi(\pi/\omega - t)$  $\neq \phi(t)$ . Therefore, it follows from Eq.(2.7) that the current i(v) will be a multivalued function of the voltage v. It also follows that since  $\phi \propto 1/\omega$ , the memristive behavior is dominant only at low frequencies  $\omega << \omega_0 = 2\pi/t_0$ . Here  $t_0 = D^2/\mu_D v_0$  is the time that the dopants need to travel distance D under a constant voltage  $v_0$ .  $t_0$  and  $\omega_0$  provide the natural time and frequency scales for a memristive circuit (typical parameters [11,12] imply  $t_0$ ~0.1 ms and  $\omega_0$  ~ 50 KHz). We emphasize that Eq.(2.6) is based on the linear-drift model, Eq.(2.2), and is valid [2] only when the charge flowing through the memristor is less than  $q_{max}(t) = Q_0(1-w_0/D)$  when  $\eta =$ +1 or  $q_{max}(t) = Q_0 w_0/D$  when  $\eta = -1$ . It is easy to obtain a diversity of i-v characteristics using Eqns.(2.6) and (2.7), including those presented in Ref. 2.1 and 2.2 by choosing appropriate functional forms of v(t). Figure 3 shows the theoretical i-v curves for v(t) =  $v_0$  sin( $\omega$ t) for  $\omega$  =  $0.5\omega_0$  (red solid),  $\omega = \omega_0$  (green dashed), and  $\omega = 5\omega_0$  (blue dotted). In each case, the high initial resistance  $R_0$  leads to the small slope of the i-v curves at the beginning. For  $\omega \leq \omega_0$  as the voltage increases, the size of the doped region increases and the memristance decreases. Therefore, the slope of the i-v curve on the return sweep is large creating a hysteresis loop. The size of this loop varies inversely with the frequency  $\omega$ . At high frequencies,  $\omega = 5\omega_0$ , the size of the doped region barely changes before the applied voltage begins the return sweep. Hence the memristance remains essentially unchanged and the hysteretic behavior is suppressed. The inset in Fig. 2.2 shows the theoretical q- $\phi$  curve for  $\omega = 0.5\omega_0$  that follows from Eq.(2.6). Thus, a single memristor shows a wide variety of i-v characteristics based on the frequency of the applied voltage. Since the mobility of the (oxygen vacancy) dopants is low, memristive effects are appreciable only when the memristor size is nano-scale. Now, we consider an ideal circuit with two memristors in series (Fig. 2.1). It follows from Kirchoff's laws that if two memristors M1 and M2 have the same polarity,  $\eta_1 = \eta_2$ , they add like regular resistors,  $M(q) = (R_{01} + R_{02}) - \eta(\Delta R_1 + \Delta R_2)q(t)/Q_0$  whereas when they have opposite polarities,  $\eta_1\eta_2 = -1$ , the q-dependent component is suppressed,  $M(q) = (R_{01} + R_{02}) - \eta(\Delta R_1 - \Delta R_2)q(t)/Q_0$ . The fact that memristors with same polarities add in series leads to the possibility of a superlattice of memristors with micron dimensions instead of the nanoscale dimensions. We emphasize that a single memristor cannot be scaled up without losing the memristive effect

because the relative change in the size of the doped region decreases with scaling. A superlattice(large chain of series connected memristors) of nano-scale memristors, on the other hand, will show the same memristive effect when scaled up.

Figure 2.2: Theoretical i-v characteristics of a memristor with applied voltage  $v(t) = v_0 \sin(\omega t)$  for  $\omega = 0.5 \omega_0$  (red solid),  $\omega = \omega_0$  (green dashed), and  $\omega = 5 \omega_0$  (blue dotted). The memristor parameters are  $w_0/D = 0.5$  and  $R_{OFF}/R_{ON} = 20$ . The unit of resistance is RON, the unit of voltage is  $v_0$ , and the unit of current is  $I_0 = Q_0/t_0$ . We see that the hysteresis is pronounced for  $\omega \le \omega_0$  and suppressed when  $\omega \gg \omega_0$ . The inset is a typical q-  $\varphi$  graph showing that the charge q is an invertible function of the flux  $\varphi$ . The unit of flux  $\varphi_0 = v_0t_0 = D^2/\mu_D$  is determined by the memristor properties alone (typical parameters imply  $\varphi_0 = 10^{-2}$  Wb).[2]

#### 2.2 PRACTICAL MEMRISTOR: MODEL OF NON-LINEAR DOPANT DRIFT

The linear-drift model used in preceding sections captures the majority of salient features of a memristor. The linear drift model suffers from one serious drawback: it does not take into account the boundary effects. Qualitatively, the boundary between the doped and undoped regions moves with speed  $v_D$  in the bulk of the memristor, but that speed is strongly suppressed when it approaches either edge,  $w \sim 0$  or  $w \sim D$ . We modify Eq.(2.2) to reflect this suppression as follows Ref. 11

$$\frac{dw}{dt} = \eta \frac{\mu_D R_{ON}}{D} i(t) F\left(\frac{w}{D}\right)$$

(2.8)

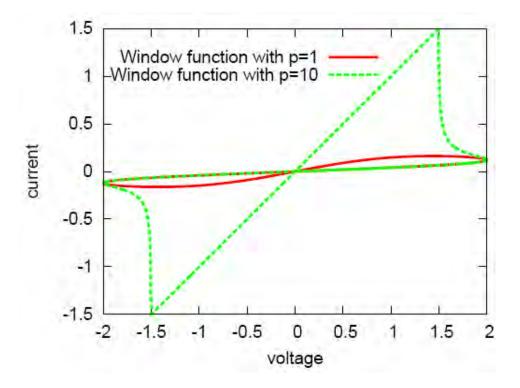

The window function F(x) satisfies F(0) = F(1) = 0 to ensure no drift at the boundaries. The function F(x) is symmetric about x = 1/2 and monotonically increasing over the interval  $0 \le x \le 1/2$ ,  $0 \le F(x) \le 1 = F(x = 1/2)$ . These properties guarantee that the difference between this model and the linear-drift model, Eq.(2.2), vanishes in the bulk of the memristor as  $w \to D/2$ . Motivated by this physical picture, we consider a family of window functions parameterized by a positive integer p,  $F_p(x) = 1 - (2x - 1)^{2p}$ . Note that Fp(x) satisfies all the constraints for any p. The equation  $F_p(x) = 0$  has 2 real roots at  $x = \pm 1$ , and 2(p-1) complex roots that occur in conjugate pairs. As p increases  $F_p(x)$  is approximately constant over an increasing interval around x = 1/2 and as  $p \to \infty$ ,  $F_p(x) = 1$  for all x except at x = 0, 1.

Thus,  $F_p(x)$  with large p provides an excellent non-linear generalization of the linear-drift model without suffering from its limitations. We note that at finite p Eq.(2.8) describes a memristive system [7,11] that is equivalent to an ideal memristor [11,6] when  $p \to \infty$  or when the linear-drift approximation is applicable. It is instructive to compare the results for large p with those for p = 1,  $F_{p=1}(x) = 4x(1-x)$ , when the window function imposes a non-linear drift over the entire region  $0 \le w \le D$  [11]. For p = 1 it is possible to integrate Eq.(2.8) analytically and we obtain

$$w_{p=1}(q) = w_0 \frac{D \exp(\frac{4\eta q(t)}{Q_0})}{D + w_0 [\exp(\frac{4\eta q(t)}{Q_0}) - 1]}$$

(2.9)

Figure 2.3: Theoretical i-v curves for a memristor with (realistic) dopant drift modeled by window functions  $F_p(x) = 1 - (2x - 1)^{2p}$  with p = 1 (red solid) and p = 10 (green dashed), in the presence of an external voltage  $v(t) = 2v_0 \sin(\omega_0 t/2)$ . The memristor parameters are  $w_0/D = 0.5$  and  $R_{OFF}/R_{ON} = 50.[2]$

#### 2.3 Spice Model of Memristor with Non-linear Dopant Drift:

Zdeněk BIOLEK et. al. showed an efficient technique of modeling the memristor with active circuit elements [16]. The Ohm's law relation is applicable between the memristor voltage and current:

$$v(t) = R_{MEM}(w) i(t)$$

(2.10)

The speed of the movement of the boundary between the doped and undoped regions depends on the resistance of doped area, on the passing current, and on other factors according to the state equation

$$\frac{dx}{dt} = ki(t)f(x) \tag{2.11}$$

Which can be found letting  $x = \frac{w}{D}$  and  $= \frac{\mu_D \, R_{ON}}{D^2}$ . The window function is then

$$f(x) = 1 - (2x - 1)^{2p} (2.12)$$

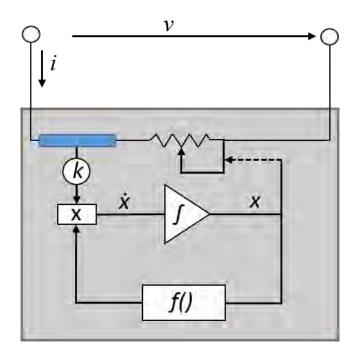

State equation (2.10) and port equation (2.11) of the memristor can be modeled by the block oriented diagram in Fig. 2.4. The memory effect of the memristor is modeled via a feedback controlled integrator. With regard to the limiting boundary conditions, it stores the effects of the passing current, and controls the memristor resistance via modifying the boundary position. The nonlinear drift and the influence of the boundary conditions are modeled by the feedback via the nonlinear window function f( ).

Figure 2.4: Block diagram of the memristor model

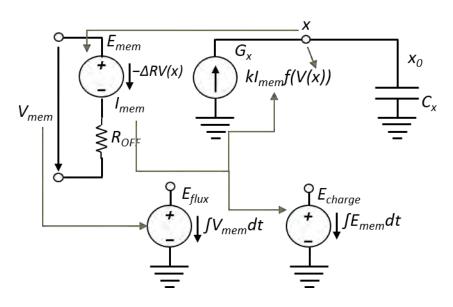

The structure of the SPICE model is shown in Fig. 2.5. The relation between the memristor voltage and current is modeled on the basis of the modified equation (2.11):

$$R_{MEM}(x) = R_{OFF} - x\Delta R \tag{2.13}$$

In Fig. 2.5, equation (2.13) corresponds to the  $R_{OFF}$  resistor in series with the E-type voltage source whose terminal voltage is controlled according to the formula "- $x\Delta R$ ". The normalized width x of the doped layer is modeled by the voltage V(x) of the capacitor  $C_x$ , which serves as an integrator of the quantities on the right side of state equation (2.11). The initial state of the normalized width of the doped layer  $x_0$ , which is modeled as initial voltage of the capacitor, is determined by the initial resistance  $R_{INIT}$  of the memristor according to the formula, derived from (2.13):

$$x_0 = \frac{R_{OFF} - R_{INIT}}{\Delta R} \tag{2.14}$$

The model is implemented as a SPICE subcircuit with parameters which can pass the following values into the subcircuit as arguments: the initial *RINIT* resistance, the *ROFF* and *RON* resistances, the width of the thin film D, the dopant mobility  $\mu_{\nu}$ , and the exponent p of the window function. The list of the SPICE subcircuit mentioned below includes conventional model of the window function according to Joglekar [17], which is open to any modifications of the functions describing the nonlinear drift, including the import of experimentally acquired data. The SPICE model is also complemented with direct computation of the integral quantities which define the memristor, i.e. the time integrals of electrical voltage (flux) and of electric current (charge). These quantities belong to the results of the SPICE analysis, being available as voltages of the internal controlled sources  $E_{flux}$  and  $E_{charge}$ .

Figure 2.5: Structure of the SPICE model

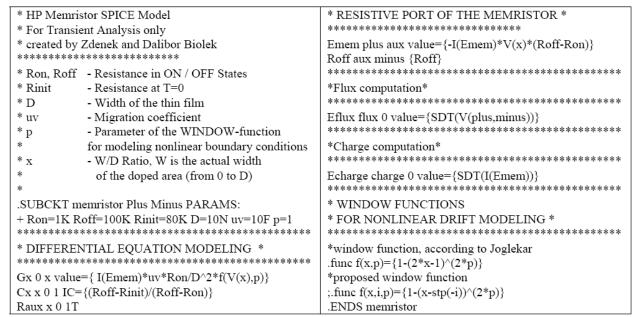

### According to the structure shown in Figure 2.5, a SPICE code was developed [16] as follows:

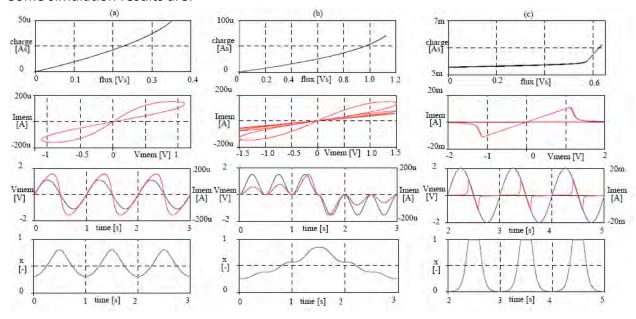

#### Some simulation results are:

Figure 2.6: Memristor with the parameters  $R_{ON}=100~\Omega$ , p=10, driven by a voltage: (a) harmonic with an amplitude of 1.2 V and a frequency of 1 Hz, (b)  $\pm V_0$  (sin  $\omega_0 t$ )<sup>2</sup> with  $V_0=1.5$  V and  $f_0=1$  Hz, (c) harmonic with an amplitude of 2 V and a frequency of 1 Hz. Other parameters are: (a)  $R_{OFF}=16~\mathrm{k}\Omega$ ,  $R_{INIT}=11~\mathrm{k}\Omega$ , (b)  $R_{OFF}=38~\mathrm{k}\Omega$ ,  $R_{INIT}=28~\mathrm{k}\Omega$ , (c)  $R_{OFF}=5~\mathrm{k}\Omega$ ,  $R_{INIT}=1~\mathrm{k}\Omega$ . Simulation in Fig. (c) confirms the hard switching effects[1]. [16]

#### SRAM BASICS

Static Random Access Memory or SRAM is the most commonly used cache memory. SRAM is generally used in personal computers, workstations, routers and peripheral equipment: CPU register files, internal CPU caches and external burst mode SRAM caches, hard disk buffers, router buffers, etc. LCD screens and printers also normally employ static RAM to hold the image displayed.

#### **3.1 SRAM**

SRAM is a form of semiconductor memory widely used in electronics, microprocessor and general computing applications. This form of semiconductor memory gains its name from the fact that data is held in there in a static fashion, and does not need to be dynamically updated as in the case of DRAM (dynamic RAM) memory. While the data in the SRAM memory does not need to be refreshed dynamically, it is still volatile, meaning that when the power is removed from the memory device, the data is not held, and will disappear. SRAM is faster and more reliable than the DRAM. DRAM access times are few times higher than SRAM access times due to recharging necessity. In addition, its cycle time is much shorter than that of DRAM because it does not need to pause between accesses. Unfortunately, it is also much more expensive to produce than DRAM. Due to its high cost, SRAM is often used only as a memory cache.

SRAMs are used for specific applications within the PC, where their strengths outweigh their weaknesses compared to DRAM:

- Simplicity: SRAMs do not require external refresh circuitry or other work in order to keep stored data intact.

- Speed: SRAM is faster than DRAM.

In contrast, SRAMs have the following weaknesses, compared to DRAMs:

- Cost: SRAM is, byte for byte, several times more expensive than DRAM.

- Size: SRAMs take up much more space than DRAMs (which is part of why the cost is higher).

These advantages and disadvantages taken together obviously show that performance-wise, SRAM is superior to DRAM, and we would use it exclusively if only we could do so economically. Unfortunately, 32 MB of SRAM would be prohibitively large and costly, which is why DRAM is used for system memory. SRAMs are perfectly suitable for level 1 and level 2 cache memory as cache memory needs to be very fast, and not very large.

SRAM is manufactured in a way rather similar to how processors are: highly-integrated transistor patterns photo-etched into silicon. Each SRAM bit is comprised of between four and six transistors, which is why SRAM takes up much more space compared to DRAM, which uses only one (plus a capacitor). Because an SRAM chip is comprised of thousands or millions of identical cells, it is much easier to make than a CPU, which is a large die with a non-repetitive structure. This is one reason why RAM chips cost much less than processors do.

Figure 3.1: Conventional SRAM cell

The operation of the SRAM memory cell is relatively straightforward. When the cell is selected, the value to be written is stored in the cross-coupled inverters. The cells are arranged in a matrix, with each cell individually addressable. Most SRAM memories select an entire row of cells at a time, and read out the contents of all the cells in the row along the column lines. While it is not necessary to have two bit lines, using the signal and its inverse, this is normal practice which improves the noise margins and improves the data integrity. The

two bit lines are passed to two input ports on a comparator to enable the advantages of the differential data mode to be accessed, and the small voltage swings that are present can be more accurately detected. Access to the SRAM memory cell is enabled by the Word Line. This controls the two access control transistors which control whether the cell should be connected to the bit lines. These two lines are used to transfer data for both read and write operations.

#### **3.2 CONVENTIONAL SRAM TYPES:**

There are different variations of SRAM. Most common are discussed here:

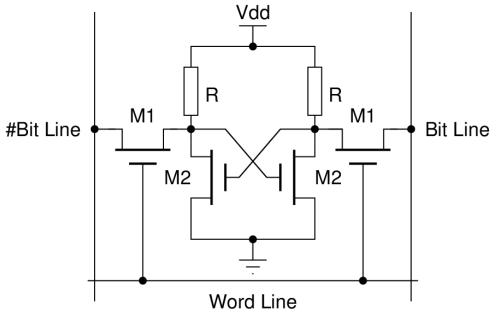

#### 3.2.1 4T-SRAM:

4T-SRAM cell consists of four NMOS transistors plus two poly-load resistors. Two NMOS transistors are pass-transistors. These transistors have their gates tied to the word line and connect the cell to the columns. The two other NMOS transistors are the pull-downs of the flip-flop inverters. The loads of the inverters consist of a very high polysilicon resistor. This design is the most popular because of its size compared to a 6T cell. The cell needs room only for the four NMOS transistors. The poly loads are stacked above these transistors. Although the 4T SRAM cell may be smaller than the 6T cell, it is still about four times as large as the cell of a comparable generation DRAM cell. The complexity of the 4T cell is to make a resistor load high enough (in the range of giga-ohms) to minimize the current. However, this resistor must not be too high to guarantee good functionality. Despite its size advantage, the 4T cells have several limitations. These include the fact that each cell has current flowing in one resistor (i.e., the SRAM has a high standby current), the cell is sensitive to noise and soft error because the resistance is so high, and the cell is not as fast as the 6T cell.

Figure 3.2: 4T SRAM

#### 3.2.2 6T-SRAM

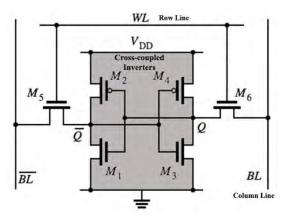

6T -SRAM is the most commonly used type of SRAM. This type SRAM cells are composed of six transistors, one NMOS transistor and one PMOS transistor for each inverter, plus two NMOS transistors connected to the row line. This configuration is called a 6T Cell. This cell offers better electrical performances (speed, noise immunity, standby current) than a 4T structure. The main disadvantage of this cell is its large size.

The four transistors in the center form two cross-coupled inverters. In actual devices, these transistors are made as small as possible to save chip-area, and are very weak. Due to the feedback structure, a low input value on the first inverter will generate a high value on the second inverter, which amplifies (and stores) the low value on the second inverter. Similarly, a high input value on the first inverter will generate a low input value on the second inverter, which feeds back the low input value onto the first inverter. Therefore, the two inverters will store their current logical value, whatever value that is.

Figure 3.3: 6T SRAM

The two lines between the inverters are connected to two separate bitlines via two n-channel pass-transistors (left and right of the cell). The gates of those transistors are driven by a wordline. In a larger SRAM, the wordline is used to address and enable all bits of one memory word. As long as the wordline is kept low, the SRAM cell is disconnected from the bitlines. The inverters keep feeding themselves, and the SRAM stores its current value.

When the wordline is high, both n-channel transistors are conducting and connect the inverter inputs and outputs to the two vertical bitlines. That is, the two inverters drive the current data value stored inside the memory cell onto the bitline (left) and the inverted data value on the inverted-bitline (right). This data can then be amplified and generates the output value of the SRAM cell during a read operation.

To write new data into the memory, the wordline is activated, and the strong bitline input-drivers (on top of the schematics) are activated. Depending on the current value stored inside the SRAM cell there might be a short-circuit condition, and the value inside the SRAM cell is literally overwritten. This only works because the transistors inside the SRAM cell are very weak.

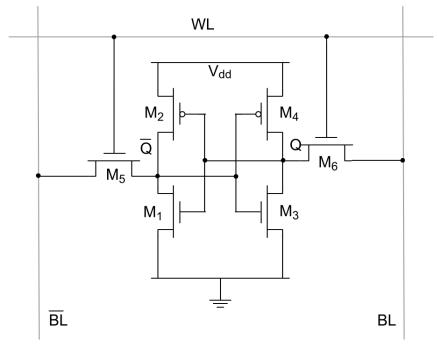

### 3.2.3 4T2M-SRAM [18]

The conventional SRAM cell is modified to implement the non-volatile functionality through replacement of the two pMOS load transistors in SRAM cell by memristors as illustrated in Fig. 3.4 SRAM cell when the power is turned off to save the data on the latch of the memristor device and two pull-down transistor and consists of two pass transistor.

Figure 3.4: Structure of Non-volatile 4T SRAM cell with memristors

For the forward direction it has around 100K ohms: let this state correspond to the high bias condition. It is also about 50 ohms for the reverse direction: this is defined to be the low bias. Two load devices of a SRAM cell flow current in the forward direction making memristors in the high bias state. By making a cell discharge through power lines for power down events, one of the memristors will flow current in the reverse direction. The memristor will have the low bias state during the power off period. The resistivity mismatch between the two current paths is used for information storage. The mismatch will bring back the data stored just before the power down. When the power is on, the load device of the current path having the low bias state will have higher voltage than that of the other path having the high bias state. The latch mechanism of the SRAM cell instantly recovers the original data before the power down.

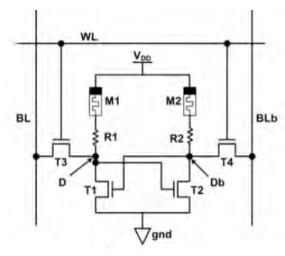

## 3.2.4 3T-2M SRAM [19]

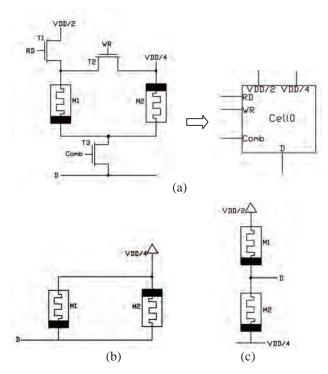

Figure 3.5: 3T-2M SRAM

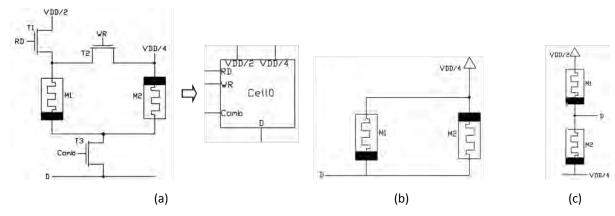

A Memristor based SRAM cell is presented in ref 3.6. Electrical scheme of the 3T-2M leaf cell is shown in Fig. 3.5(a). Two memristors are used as memory element. The arrangement is in such a way that during write cycle, they are connected in parallel but in opposite polarity [Fig. 3.5 (b)] and during read cycle, they are connected in series [Fig. 3.5 (c)]. These connections are established by two NMOS pass transistors T1 and T2. A third transistor T3 is used to isolate a cell from other cells of the memory array during read and write operations. The gate input of T3 is the Comb signal which is the OR of RD and WR signals. If a bit is to be written, RD is taken to the LOW state and WR and Comb are taken to the HIGH state. As a result, circuit of Fig. 3.5 (b) is formed. The voltage across the memristors is  $(V_D-V_{DD}=4)$ . Depending on the data, it can be positive (if D=1 i.e.  $V_D=V_{DD}$ ) or negative (if D=0 i.e.  $V_D=0$  V). As polarities of the memristors are opposite, change of memristances (or resistances) will also take place in the opposite direction. Now if the data is to be read, RD and Comb are taken to the HIGH state and this forms the circuit shown in Fig. 3.4 (c). Voltage at D is now:

$$V_D = \left(\frac{V_{DD}}{2} - \frac{V_{DD}}{4}\right) \times \frac{R_2}{R_1 + R_2} + \frac{V_{DD}}{4} \tag{5}$$

where, R1 and R2 are the resistances of M1 and M2 respectively. If '1' was written during write cycle, R2 becomes significantly greater than R1 and then  $V_D$  is greater than  $V_{DD}$ =4. If '0' was written, R1 becomes significantly greater than R2 which makes  $V_D$  to be as close as  $V_{DD}$ =4. A comparator can be used as a sense amplifier to interpret these voltages as HIGH or LOW correctly.

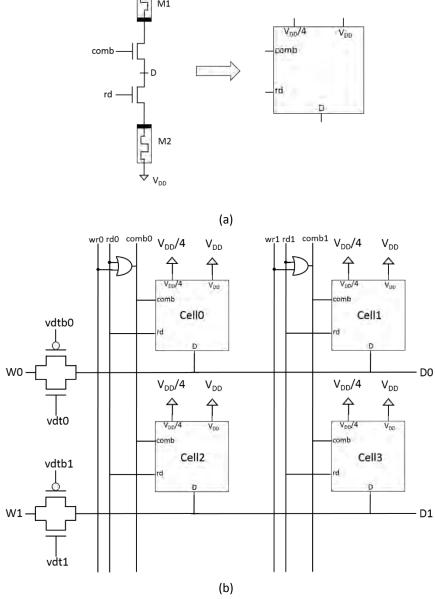

#### MEMRISTOR BASED SRAM CELL

Non-volatile SRAMs, or NVSRAMs, have standard SRAM functionality, but they save the data when the power supply is lost, ensuring preservation of critical information. NVSRAMs are used in a wide range of situations—networking, aerospace, and medical, among many others — where the preservation of data is critical and where batteries are impractical. In our work memristor is used to give the non-volatile property to the memory circuit. In this chapter the development of proposed NVRAM is presented sequentially.

#### 4.1 MEMRISTOR AS A MEMORY COMPONENT

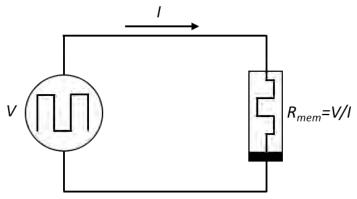

Hysteresis in the *i-v* characteristic of memristor shown in the previous chapter (Figure 2.2, 2.3) suggests the property of keeping memory in the form of resistance. From Eq. 2.1, it can be seen that, effective resistance or memristance of a memristor depends on the diffusion length w. Again w is governed by the differential equation stated in Eq. 2.2 which led us the solution of w at any time t. It shows that the time dependent value of the diffusion length w depends on the time dependent charge q or in other word, current. So it can be concluded that the effective resistance is a function of current flowing through the memristor. Current flowing from positive to negative terminal of the memristor increases the diffusion length w and thereby decreases the effective resistance of the memristor (Eq. 2.1). Current flowing from the opposite direction causes increment of resistance. A quick simulation could demonstrate the scenario clearly. Figure 4.1 shows a memristor under application of pulses across it.

Figure 4.1: A pulsed source applied across a memristor

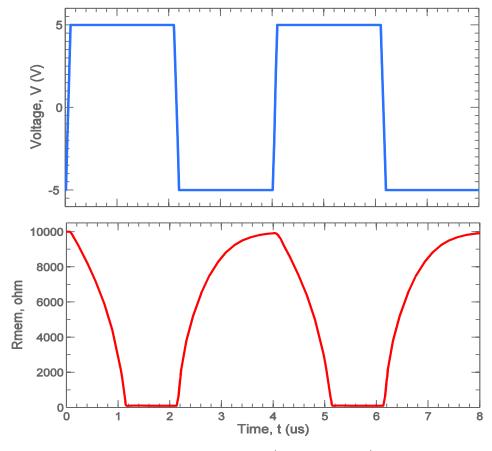

Simulation was done in PSPICE v9.2 with memristor parameters  $R_{OFF}=10K\Omega$ ,  $R_{ON}=100\Omega$ , D=10nm,  $\mu_D$ =10<sup>-9</sup> m²/s/V. Figure 4.2 shows the plot of the voltage and resistance of the memristor. Resistance is found by plotting V/I against time. The plot shows the decrement of resistance when applied a positive pulse and increment of resistance when applied a negative pulse.

Figure 4.2: V vs Time and Rmem vs Time plot

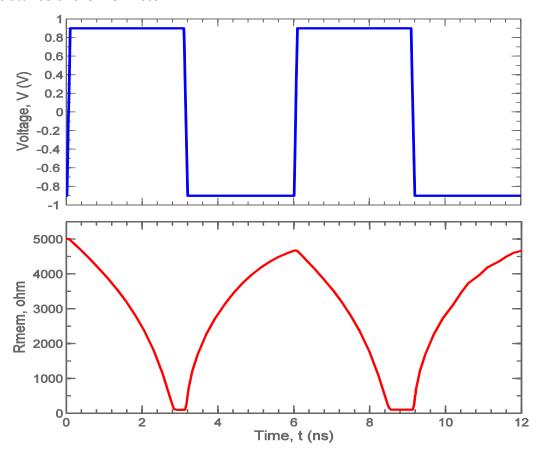

This result clearly indicates that a memristor can hold memory in the form of resistance and a single memristor could be enough to hold 1-bit memory provided that both positive and negative pulses are available. However, generation of negative voltage can be a tough job in integrated circuits sometimes. To eliminate the need of negative source, we developed a good technique of using two different positive voltages connected with the memristor in opposite directions. Higher one is  $V_{DD}$  and the lower one is  $V_{DD}/x$ , where x>1. Also from recent developments we know that memristors can be as small as 3nm [20] and  $\mu_D$  can be increased by  $10^{\sim}10^3$  times. For example, simulation was done with memristor parameters  $R_{OFF} = 5K\Omega$ ,  $R_{ON} = 100\Omega$ , D=3nm,  $\mu_D=100\times10^{-9}$  m²/s/V and x=2. Figure 4.3 shows the plot of the voltage and resistance of the memristor.

Figure 4.3: V vs Time and Rmem vs Time plot with new memristor parameters

This result also shows that the speed of change of resistance of a memristor is not same for current flow in either directions for same potential difference. To make the speed equal we had to use different potential differences for the two cases.

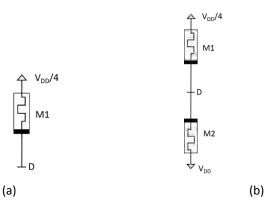

#### 4.2.1 Two-Transistor Two-Memristor Memory Cell

As shown, one memristor can independently act as a memory element. It is sufficient for holding 1 bit memory. But to read it back, the resistance of the memristor have to be measured. To measure resistance, we have to apply a voltage across it and measure the current through it, which is very much inconvenient. A better approach is to use the voltage divider rule for which another resistive element is necessary. For this purpose another memristor can be used in reverse bias, whose memristance will never change and will act as fixed resistance. To control write and read operations our cell also needs two NMOSes. Transistors do the switching tasks to make different circuit combinations in reading and writing operation. Figure 4.4 shows our basic SRAM cell consisting of 2-NMOS and 2-memristor.

Figure 4.4: The 2-Memristor 2-Transistor SRAM cell

The arrangement is in such a way that during write cycle current will flow through only one memristor (Fig.4.5a) and during read cycle the memristors are connected in series (Fig.4.5b). These connections are established by two NMOS pass transistors T1 and T2.

Figure 4.5: (a) circuit when rd=0, comb=1 (b) circuit when rd=1, comb=1

The COMB signal is logical ORed signal of WR(write) and RD(read) signal. If a bit is to be written, RD is taken to the LO state and COMB is taken to the HI state. As a result, circuit of Figure 4.5a is formed. The voltage across the memristors is  $(V_D-V_{DD}/4)$ . Depending on the data, it can be positive (if D=1 i.e.  $V_D=V_{DD}$ ) or negative (if D=0 i.e. VD=0V). According to 'write data' the polarity of the potential difference across M1 can be positive or negative, change of memristances (or resistances) will also take place in both way respectively. If D=1 i.e.  $V_D=V_{DD}$ , current will flow from  $V_D$  to  $V_{DD}/4$  causing resistance of M1 to increase and vice versa. Period of the write cycle should be sufficient to make maximum resistance change in one direction. After completing the write cycle, COMB is taken to the LO state and the data will be stored encoded in the resistances of M1. Now if the data is to be read, RD and COMB both are taken to the HI state and this forms the circuit shown in Fig.4.5(b). Voltage at D is now:

$$V_D = \left(V_{DD} - \frac{V_{DD}}{4}\right) \times \frac{R1}{R1 + R2}$$

(4.1)

Where, R1 and R2 are the resistances of M1 and M2 respectively. If '0' was written, R2 was significantly greater than R1 and  $V_D$  was close to  $V_{DD}/4$ . If '1' was written during write cycle, R1 is significantly greater than R2 and  $V_D$  is greater than  $V_{DD}/4$ . But as  $V_D$  exceeds a certain value the source voltage of nMOS controlled by the READ signal becomes significantly high and moves the nMOS out of saturation. For this reason we don't get very high voltage at D node when we read '1'. To simulate the circuit, a CMOS transmission gate is used to make the READ and WRITE mutually exclusive on the data line D (figure 4.6).

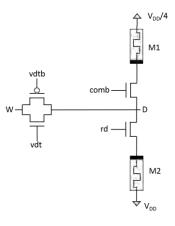

Figure 4.6: A CMOS pass gate is introduced for simulation

A pulse of 2 ns is applied to COMB for writing and a pulse of 0.8 ns is applied to RD and COMB for reading purpose. In the first read/write cycle, COMB=1 and RD=0 for 2ns. During this time, write data WD=1. After writing, COMB is made LO. Again COMB and RD are made high. Then the measured voltage at D is 0.619V (Figure 4.7). The read time here is 0.8ns. In the next cycle, a '0' is written making WD=0 during write cycle. After this, the measured voltage at D is 0.5727V (Figure 4.7). A comparator can be used as a sense amplifier to interpret these voltages as HI or LO correctly. Use of comparator is described later in section 4.5.2. The reference of the comparator should be tied to 0.59V. Simulations of the circuits are based on the following parameters:  $R_{ON}$  =100 $\Omega$ ,  $R_{OFF}$  =5k $\Omega$ , p =10, D =3nm and  $\mu_{v}$  =100×10<sup>-9</sup> m²/s/V. SRAM cell has been implemented using CMOS 0.18 $\mu$ m technology. Using the above memristor parameters satisfactory operation of the SRAM cell was achieved at 1.8 Volts. We have referred to this voltage as the nominal voltage for the SRAM cell. Furthermore, the initial state of the memristors is determined by initial resistance,  $R_{INIT}$ .

Figure 4.7: After writing '1' (WD=1, COMB=1,RD=0),  $V_D$  was read as 0.619V (COMB =1,RD=1) and After writing '0' (WD=0, COMB =1,RD=0),  $V_D$  was read as 0.5727V (COMB =1,RD=1)

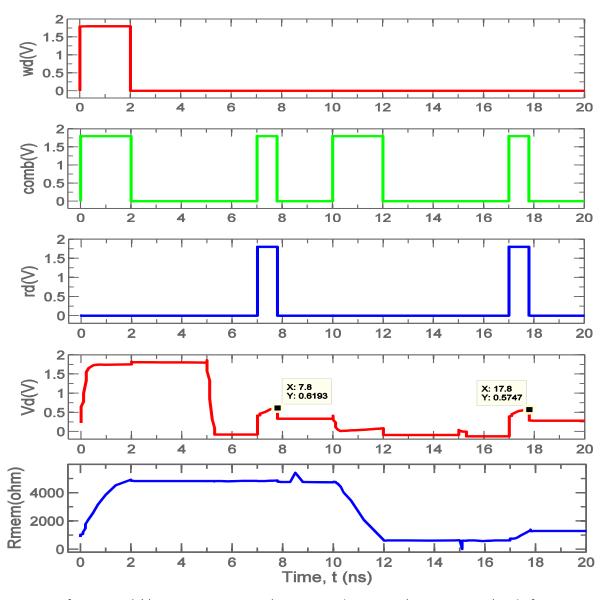

#### 4.2.2 SIMULATION OF 2×2 ARRAY OF MEMORY

In the previous section, we successfully demonstrated read and write operation of a single SRAM cell. For the implementation of SRAM array, it is equally important to build a memory architecture. For our cell, we have introduced a slightly different technique of organizing the memory in an array than it is conventionally done. Organization of 2x2 array is shown in figure 4.8(b). First, a little modification was needed for the single cell. It is shown in figure 4.8(a).

Figure 4.8 (a) basic building block of a single cell (b) 2x2 array of memory

Columns are selected by traditional read write encoder technique.  $V_{DD}/4$  and  $V_{DD}$  pins are common in a column. Suppose we want to select row-1 column-0 cell. For this, RD0, COMB0 and Vdt1, Vdtb1 should be used. Data is read or written through D1 line. Simulation of this structure was done in PSPICE v9.2 with tsmc018 mos model. The nominal voltage is 1.8V and memristor parameters are  $R_{OFF} = 5K\Omega$ ,  $R_{ON} = 100\Omega$ , D=3nm,  $\mu_D=100\times10^{-9}$  m<sup>2</sup>/s/V.

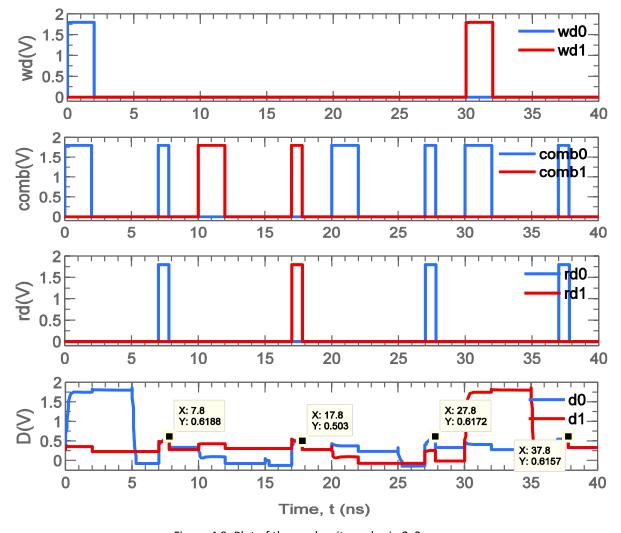

Four read-write cycles are shown in the plot. In the first cycle, '1' was written to cello. Then it was read and found to be 0.6188 V and can be interpreted as HI with the aid of a sense amplifier. Then a '0' was written to the cell1 and read as 0.503 V (close to VDD/4). Again '0' was written on cell3 and cello was read as 0.6172 V. Finally '1' was written to the cell3 and found 0.6157V after reading. The write-read cycles are shown in figure 4.9.

Figure 4.9: Plot of the read-write cycles in 2x2 array

#### 4.3.1 RESIDUAL VOLTAGE EFFECT

After writing '1' to a cell we have to disconnect the wordline. Some residual voltage remains in the wordline with no path to discharge. If we try to read '0' on a different cell which is on the same row, we would not be able to do it due the residual voltage. Figure 4.10 depicts the problem.

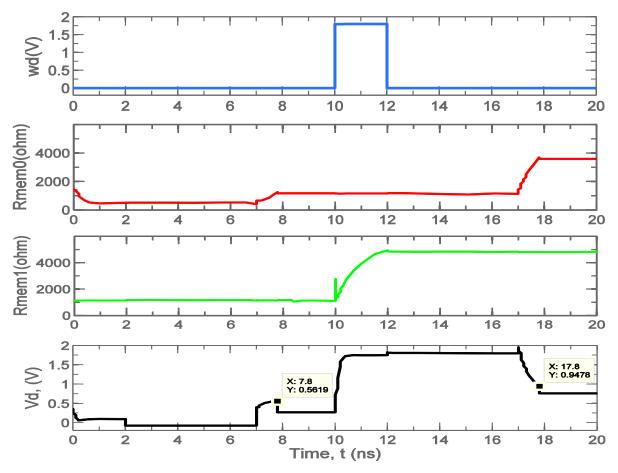

Figure 4.10: '0' written on cell0 and read. Then '1' was written on cell1 and cell0 was read. This time cell0 gives 0.9478 V much larger than '0' should give due to addition of the residual voltage.

This problem was not evident in single cell. But in array structure it shows severe discrepancy in reading cells. To solve this problem a new charge dumping technique (through resistor) was introduced.

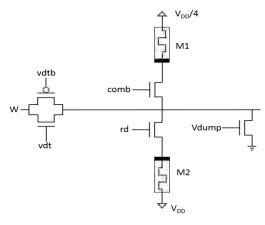

Figure 4.11: A NMOS controlled by Vdump signal is used to create a path to the ground for discharging the wordlines.

As shown in figure 4.11 a NMOS controlled by Vdump signal is introduced in the wordlines. Before every read operation Vdump signal turns the NMOS ON and a path to ground is created for 0.3 ns for the residual voltage to discharge completely. The effect is shown in figure 4.12

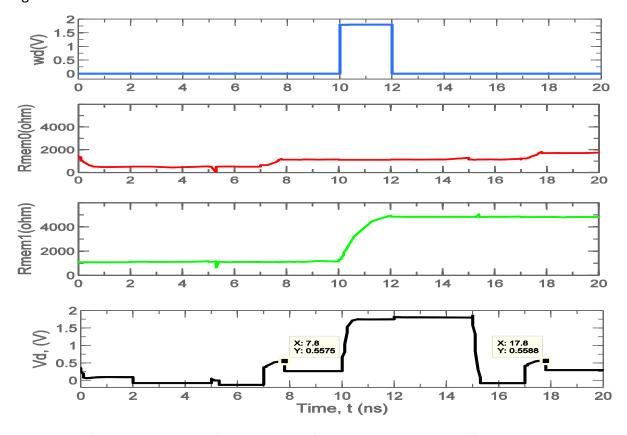

Figure 4.12: '0' written on cell0 and after using Vdump for 0.3ns cell0 is read. Then '1' was written on cell1 and after using Vdump for 0.3ns cell0 was read. This time cell0 gives 0.5588 V which is equivalent to '0'. This solves the residual voltage problem but introduces 0.3 ns read time increase.

#### 4.3.2 CONTAMINATION OF STORED DATA DUE TO LEAKAGE